半導体装置

【課題】電力増幅モジュールの性能を向上させる。

【解決手段】多段接続された複数の増幅回路を有する半導体チップと整合回路用受動部品が配線基板に搭載されて、電力増幅モジュールが構成される。最終段の増幅回路はLDMOSFET形成領域22に形成された複数の単位LDMOSFETを並列接続して構成される。半導体チップにおいて、LDMOSFET形成領域22の辺61aに沿って、複数の単位LDMOSFETの各ゲート電極に電気的に接続された連結配線部M2G1が延在し、同層の配線部M2G2を介して同層のゲートパッド電極51Gに接続される。LDMOSFET形成領域22の辺61bに沿って、複数の単位LDMOSFETの各ドレインと電気的に接続された連結配線部M2D2が延在し、同層のドレイン用パッド電極51Dが接続される。連結配線部M2G1の幅W1は、LDMOSFET形成領域22の長さL1の1/10以上である。

【解決手段】多段接続された複数の増幅回路を有する半導体チップと整合回路用受動部品が配線基板に搭載されて、電力増幅モジュールが構成される。最終段の増幅回路はLDMOSFET形成領域22に形成された複数の単位LDMOSFETを並列接続して構成される。半導体チップにおいて、LDMOSFET形成領域22の辺61aに沿って、複数の単位LDMOSFETの各ゲート電極に電気的に接続された連結配線部M2G1が延在し、同層の配線部M2G2を介して同層のゲートパッド電極51Gに接続される。LDMOSFET形成領域22の辺61bに沿って、複数の単位LDMOSFETの各ドレインと電気的に接続された連結配線部M2D2が延在し、同層のドレイン用パッド電極51Dが接続される。連結配線部M2G1の幅W1は、LDMOSFET形成領域22の長さL1の1/10以上である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、移動体通信装置に搭載される電力増幅モジュールなどに使用される半導体装置に適用して有効な技術に関する。

【背景技術】

【0002】

近年、GSM方式、PCS方式、PDC方式、CDMA方式といった通信方式に代表される移動体通信装置(いわゆる携帯電話)が世界的に普及している。

【0003】

一般に、この種の移動体通信装置は、電波の放射と受信をするアンテナ、電力変調された高周波信号を増幅してアンテナへ供給する高周波電力増幅器(RFパワーモジュール)、アンテナで受信した高周波信号を信号処理する受信部、これらの制御を行う制御部、そしてこれらに電源電圧を供給する電池(バッテリー)で構成される。

【0004】

特開2001−94094号公報(特許文献1)には、3つの半導体チップを配線基板上に搭載した高周波電力増幅器に関する技術が記載されている。

【0005】

国際公開05/015636号公報(特許文献2)には、配線基板上に搭載する半導体チップを1つのみとしたRFパワーモジュールに関する技術が記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2001−94094号公報

【特許文献2】国際公開05/015636号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明者の検討によれば、次のことが分かった。

【0008】

RFパワーモジュールは、配線基板上に半導体チップおよび受動部品を搭載し、これらを樹脂封止することで形成することができる。RFパワーモジュールに形成されている電力増幅回路は、複数の増幅回路を多段接続した多段構成を有しているが、複数の増幅回路をそれぞれ異なる半導体チップに形成した場合、配線基板上に搭載する半導体チップの数が多くなってしまうため、RFパワーモジュールの大型化(大面積化)やコストの上昇を招いてしまう。一方、複数の増幅回路を同じ半導体チップに形成した場合、配線基板上に搭載する半導体チップの数が少なくてすむため、RFパワーモジュールの小型化(小面積化)やコストの低減を図ることができる。

【0009】

複数の増幅回路を同じ半導体チップに形成した場合、各増幅回路の入力用のゲートパッド電極と出力用のドレインパッド電極とを半導体チップに設ける必要が生じ、半導体チップにおけるパッド電極の種類や数が多くなるが、これらのパッド電極を、配線基板上に搭載した受動部品などで構成される段間整合回路などに接続しやすくするためには、半導体チップにおける各パッド電極の配置を工夫する必要がある。例えば、増幅回路の入力用のゲートパッド電極と出力用のドレインパッド電極とを、半導体チップの主面の同じ辺に沿って並んで配置させれば、半導体チップ内の増幅回路と配線基板上に搭載した受動部品などで構成される段間整合回路とを接続しやすくなる。

【0010】

しかしながら、半導体チップにおいて、ある増幅回路を形成した領域から、その増幅回路のゲートに電気的に接続されたゲートパッド電極を離して配置させた場合、その増幅回路のゲートとゲートパッド電極とをつなぐゲート配線が長距離配線となる。各増幅回路は、並んで形成された複数の単位MISFETを並列接続することで形成されているが、増幅回路を形成した領域からゲートパッド電極を離して配置させた場合、ゲート配線の寄生インダクタンス成分に起因して、増幅回路を構成する複数の単位MISFETの各ゲート電極での位相差が大きくなってしまう。このため、増幅回路のドレインに電気的に接続されたドレインパッド電極からの出力の電力合成ロスが増え、増幅回路での電力損失が高くなり、RFパワーモジュールの効率を低下させる可能性があることが、本発明者の検討により分かった。これは、RFパワーモジュールの性能を低下させてしまう。

【0011】

本発明の目的は、半導体装置の性能を向上させることができる技術を提供することにある。

【0012】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0013】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0014】

代表的な実施の形態による半導体装置は、配線基板上に半導体チップが搭載された、電力増幅回路を有する半導体装置であって、前記半導体チップには、前記電力増幅回路を構成するMISFET素子と、前記MISFET素子のゲートおよびドレインにそれぞれ電気的に接続されたゲート用パッド電極およびドレイン用パッド電極とを有している。そして、前記MISFET素子は、前記半導体チップの第1MISFET形成領域に形成された複数の単位MISFET素子を並列に接続して構成されており、前記複数の単位MISFET素子の各ゲート電極の延在方向である第1方向と交差する前記第1MISFET形成領域の第1の辺に沿って、前記複数の単位MISFET素子の前記各ゲート電極に電気的に接続された第1ゲート配線部が延在している。そして、前記第1ゲート配線部は、同層の第2ゲート配線部を介して同層の前記ゲート用パッド電極に接続され、前記第1ゲート配線部の幅は、前記第1MISFET形成領域の前記第1の辺の長さの1/10以上である。

【0015】

また、代表的な他の実施の形態による半導体装置は、配線基板上に半導体チップが搭載された、電力増幅回路を有する半導体装置であって、前記半導体チップには、前記電力増幅回路を構成するMISFET素子と、前記MISFET素子のゲートおよびドレインにそれぞれ電気的に接続されたゲート用パッド電極およびドレイン用パッド電極とを有している。そして、前記MISFET素子は、前記半導体チップの第1MISFET形成領域に形成された複数の単位MISFET素子を並列に接続して構成されており、前記複数の単位MISFET素子の各ゲート電極の延在方向である第1方向と交差する前記第1MISFET形成領域の第2の辺に沿って、前記複数の単位MISFET素子の各ドレイン領域と電気的に接続された第1ドレイン配線部が延在している。そして、前記ドレイン用パッド電極は、同層の前記第1ドレイン配線部に接続され、前記第1ドレイン配線部の幅は、前記第1MISFET形成領域の前記第2の辺の長さの1/10以上である。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

代表的な実施の形態によれば、半導体装置の性能を向上させることができる。

【図面の簡単な説明】

【0018】

【図1】デジタル携帯電話機の一例を示すブロック図である。

【図2】図1に示されるデジタル携帯電話機に用いられている電力増幅モジュールの構成例を模式的に示した回路ブロック図である。

【図3】本発明の一実施の形態である電力増幅モジュールの構造を示す概念的な断面図である。

【図4】比較例の電力増幅モジュールの概念的な平面図である。

【図5】本発明の一実施の形態の電力増幅モジュールの構造を示す概念的な平面図である。

【図6】本発明の一実施の形態の電力増幅モジュールの変形例を示す概念的な平面図である。

【図7】本発明の一実施の形態の半導体チップの要部断面図である。

【図8】本発明の一実施の形態の半導体チップの要部断面図である。

【図9】本発明の一実施の形態の半導体チップの要部断面図である。

【図10】本発明の一実施の形態の半導体チップの他の要部断面図である。

【図11】本発明の一実施の形態の半導体チップの要部平面図である。

【図12】本発明の一実施の形態の半導体チップの要部平面図である。

【図13】本発明の一実施の形態の半導体チップの要部平面図である。

【図14】本発明の一実施の形態の半導体チップの要部平面図である。

【図15】本発明の一実施の形態の半導体チップの要部平面図である。

【図16】本発明の一実施の形態の半導体チップの要部平面図である。

【図17】本発明の一実施の形態の半導体チップの要部平面図である。

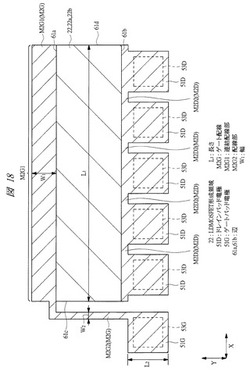

【図18】本発明の一実施の形態の半導体チップの要部平面図である。

【図19】比較例の半導体チップの要部平面図である。

【図20】ゲートパッド電極とドレインパッド電極とを半導体チップの同じ辺に配置した場合の半導体チップの要部平面図である。

【図21】シミュレーションに用いた等価回路図である。

【図22】ゲート配線の連結配線部の幅を変えたときの、電力増幅モジュールの効率の向上量を示すグラフである。

【図23】本発明の他の実施の形態の半導体チップの要部平面図である。

【図24】本発明の他の実施の形態の半導体チップの要部平面図である。

【図25】本発明の他の実施の形態の半導体チップの要部平面図である。

【発明を実施するための形態】

【0019】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0021】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。

【0022】

(実施の形態1)

<デジタル携帯電話機の構成について>

図1は、標準的なデジタル携帯電話機(デジタル携帯電話機システム、移動体通信装置)DPSの一例を示すブロック図(説明図)である。

【0023】

図1に示されるデジタル携帯電話機DPSにおいては、アンテナANTより受信した信号は、アンテナスイッチANT−SWを通って低雑音アンプLNAにより増幅され、受信ミクサRX−MIXにより150〜250MHz程度のIF周波数(中間周波数)に変換された後、IF回路IFCで更に周波数変換され、455kHz程度の第2IF周波数としてベースバンド部BBPへ導かれて復調回路DMDLで復調される。なお、図1において、符号COD1は音声CODEC(コーデック)、符号SPはスピーカ、符号MICはマイク、符号COD2はチャネルCODEC(コーデック)、符号MDLは変調回路である。

【0024】

また、音声をデジタル化した信号は、ベースバンド部BBPのD/A変換回路DACでD−A変換(デジタル−アナログ変換)され、I/Q信号としてRFブロック部RFBPへ導かれ、直交変調器QMDによりIF周波数へ変調され、送信ミクサTX−MIXにより送信信号に変換された後、電力増幅モジュールPA1で増幅され、アンテナスイッチANT−SWを通してアンテナANTから送信される。受信ミクサRX−MIXおよび送信ミクサTX−MIXへは、発振器とPLL(位相同期回路)により構成されたシンセサイザよりローカル信号が供給されている。なお、図1において、符号AGCAMPはAGC(Automatic Gain Control)アンプ、符号FPL1はRF−PLL(RF周波数位相同期回路)、符号FPL2はIF−PLL(IF周波数位相同期回路)である。また、デジタル携帯電話機DPSは、液晶表示部LCD、マイコンMCNおよびメモリMRYなどで構成された表示・制御部CDPも備えている。

【0025】

<電力増幅モジュールの回路構成について>

図2は、図1に示されるデジタル携帯電話機DPSのような移動体通信装置に用いられている電力増幅モジュール(半導体装置、電子装置、電力増幅器、高出力増幅器、高周波電力増幅器、高周波電力増幅装置、電力増幅器モジュール、RFパワーモジュール)PA1の構成例を模式的に示した回路ブロック図(説明図)である。

【0026】

電力増幅モジュールPA1は、電力回路を有する半導体装置(または電子装置)であり、図2に示されるように、電力増幅モジュールPA1の回路構成は、複数段、ここでは2段(2つ)の増幅回路(増幅段、電力増幅回路)AMP1,AMP2と、インピーダンス整合用の整合回路AJC1,AJC2,AJC3とを有している。整合回路AJC1は、入力端子IPT1と1段目の増幅回路AMP1(のゲート)の間の整合回路(入力整合回路)である。整合回路AJC2は、1段目の増幅回路AMP1(のドレイン)と2段目の増幅回路AMP2(のゲート)の間の整合回路(段間整合回路)である。整合回路AJC3は、2段目の増幅回路AMP2(のドレイン)と出力端子OPT1の間の整合回路(出力整合回路)である。また、各増幅回路AMP1,AMP2のドレインには電源電圧VDD1が印加され、各増幅回路AMP1,AMP2のゲートには、電源電圧VDD2を抵抗分割して得られた電圧(バイアス電圧)が印加されるようになっている。

【0027】

電力増幅モジュールPA1の入力端子IPT1に入力されたRF入力信号(送信信号)は、整合回路AJC1を経て増幅回路AMP1で増幅され、更に整合回路AJC2を経て増幅回路AMP2で増幅されて、整合回路AJC3を経て出力端子OPT1からRF出力信号(増幅された送信信号)として出力される。

【0028】

このように、電力増幅モジュールPA1が有する電力増幅回路は、複数の増幅回路AMP1,AMP2を多段接続した多段構成を有している。

【0029】

また、図示は省略するが、整合回路AJC3と出力端子OPT1の間にローパスフィルタやアンテナスイッチ回路を設けることもできる。ローパスフィルタは高調波成分を減衰させる回路である。

【0030】

<電力増幅モジュールの構造について>

図3は、電力増幅モジュールPA1の構造を示す概念的な断面図(側面断面図)である。

【0031】

図3に示される電力増幅モジュールPA1は、配線基板(多層基板、多層配線基板、モジュール基板)11と、配線基板11上に搭載(実装)された半導体チップ(半導体素子、能動素子)CP1と、配線基板11上に搭載(実装)された受動部品(受動素子、チップ部品)12と、半導体チップCP1および受動部品12を含む配線基板11の上面11aを覆う封止樹脂(封止樹脂部)13とを有している。半導体チップCP1および受動部品12は、配線基板11の導体層(伝送線路)に電気的に接続されている。また、電力増幅モジュールPA1は、例えば図示しない外部回路基板またはマザーボードなどに実装することもできる。電力増幅モジュールPA1は、半導体チップCP1を有しているので半導体装置とみなすことができるが、電子装置とみなすこともできる。

【0032】

配線基板11は、例えば、複数の絶縁体層(誘電体層)14と、複数の導体層(配線層)とを積層して一体化した多層配線基板(多層基板)である。図3では、4つの絶縁体層14が積層されて配線基板11が形成されているが、積層される絶縁体層14の数はこれに限定されるものではなく種々変更可能である。配線基板11を構成する各導体層(配線層)は、必要に応じて絶縁体層14に形成されたビアホール(スルーホール)16内の導体(導体膜)を通じて電気的に接続されている。配線基板11の絶縁体層14を形成する材料としては、例えばアルミナ(酸化アルミニウム、Al2O3)などのようなセラミック材料を用いることができる。この場合、配線基板11はセラミック多層基板である。配線基板11の絶縁体層14の材料は、セラミック材料に限定されるものではなく種々変更可能であり、例えばガラスエポキシ樹脂などを用いても良い。

【0033】

配線基板11の上面(表面)11a上と下面(裏面)11b上と絶縁体層14間とには、配線形成用の導体層(配線層、配線パターン、導体パターン)が形成されている。配線基板11の最上層の導体層によって、配線基板11の上面11aに導電体からなる基板側端子(端子、電極)15aが形成され、配線基板11の最下層の導体層によって、配線基板11の下面11bに導電体からなる外部接続用端子(端子、電極、モジュール電極)15bが形成されている。

【0034】

外部接続用端子15bは、上記入力端子IPT1に対応する端子と上記出力端子OPT1に対応する端子とを含んでいる。配線基板11の内部、すなわち絶縁体層14の間にも導体層(配線層、配線パターン、導体パターン)が形成されているが、図3では簡略化のために図示を省略している。また、配線基板11の導体層により形成される配線パターンのうち、基準電位供給用の配線パターン(例えば配線基板11の下面11bの基準電位供給用端子15cなど)は、絶縁体層14の配線形成面の大半の領域を覆うような矩形パターンで形成し、伝送線路用の配線パターンは帯状のパターンで形成することができる。

【0035】

半導体チップCP1は、単結晶シリコンなどからなる半導体基板(半導体ウエハ)に半導体集積回路を形成した後、必要に応じて半導体基板の裏面研削を行ってから、ダイシングなどにより半導体基板を各半導体チップCP1に分離したものである。半導体チップCP1の表面(上面)には、複数のパッド電極(電極、ボンディングパッド)PDが形成されており、各パッド電極PDは、半導体チップCP1に形成された半導体素子または半導体集積回路に電気的に接続されている。半導体チップCP1の構成については、後でより詳細に説明する。

【0036】

図3に示されるように、半導体チップCP1は配線基板11の上面11aの導体層17に、例えば半田18などの接合材(接着材)によりフェイスアップでダイボンディングされている。半導体チップCP1のダイボンディングには、半田18の代わりに銀ペーストなどを用いることもできる。半導体チップCP1の表面(上面)に形成されたパッド電極PDは、導電性のワイヤ(ボンディングワイヤ)WAを介して配線基板11の上面11aの基板側端子15aに電気的に接続されている。また、半導体チップCP1の裏面全面には裏面電極BE1が形成されており、この半導体チップCP1の裏面電極BE1は、配線基板11の上面11aの導体層17に半田18などの導電性の接合材により接合されて電気的に接続され、更にビアホール16(16a)内の導体などを介して、配線基板11の下面11bの基準電位供給用端子15cに電気的に接続されている。なお、ビアホール16のうち、半導体チップCP1の下方に設けられたビアホール16aは、半導体チップCP1で生じた熱を配線基板11の下面11b側に伝導させるためのサーマルビアとして機能することもできる。

【0037】

受動部品12は、抵抗素子(例えばチップ抵抗)、容量素子(例えばチップコンデンサ)またはインダクタ素子(例えばチップインダクタ)などの受動素子からなり、例えばチップ部品からなる。受動部品12は、例えば上記整合回路AJC1,AJC2,AJC3などを構成する受動部品である。受動部品12の電極は、配線基板11の上面11aの基板側端子15aに半田18などの導電性の接合材により接合されて電気的に接続されている。

【0038】

半導体チップCP1または受動部品12が電気的に接続された配線基板11の上面11aの基板側端子15aは、必要に応じて配線基板11の上面11aまたは内部の配線層やビアホール16内の導体などを介して結線され、また、必要に応じて配線基板11の下面11bの外部接続用端子15bまたは基準電位供給用端子15cに電気的に接続されている。

【0039】

封止樹脂13は、半導体チップCP1、受動部品12およびワイヤWAを覆うように配線基板11の上面11a上に形成されている。封止樹脂11は、例えばエポキシ樹脂などの樹脂材料からなり、フィラーなどを含有することもできる。

【0040】

本実施の形態では、上記増幅回路AMP1および上記増幅回路AMP2を、1つの半導体チップCP1内に形成している。半導体チップCP1内に増幅回路AMP1,AMP2を設けることで、増幅回路AMP1を内蔵した半導体チップと増幅回路AMP2を内蔵した半導体チップとを別個に用意する場合に比べて、電力増幅モジュールPA1を小型化(小面積化)することができ、また、電力増幅モジュールPA1のコストを低減できる。

【0041】

更に、本実施の形態では、増幅回路AMP1,AMP2だけでなく、増幅回路AMP1,AMP2の増幅動作の制御や補佐などを行う制御回路(後述の制御回路CTC1に対応)も半導体チップCP1内に形成している。

【0042】

<比較例の電力増幅モジュールについて>

図4は、比較例の電力増幅モジュールPA101の概念的な平面図(上面図)であり、上記封止樹脂13に対応する封止樹脂を透視してある。

【0043】

図4に示される比較例の電力増幅モジュールPA101は、全体の回路構成は上記図2の回路構成とほぼ同様であるが、本実施の形態とは異なり、増幅回路AMP1を内蔵した半導体チップCP101と増幅回路AMP2を内蔵した半導体チップCP102とを別個に用意して配線基板111の上面111a上に搭載している。そして、半導体チップCP101,CP102のパッド電極PD101G,PD101D,PD102G,PD102Dをそれぞれ導電性のワイヤWA101を介して配線基板111の上面111aの基板側端子115aに電気的に接続している。また、配線基板111の上面111a上には、半導体チップCP101,102および受動部品112が搭載されているだけでなく、上記整合回路AJC1,AJC2,AJC3を構成する受動部品も搭載されているが、図面の簡略化のために、図4では、各整合回路AJC1,AJC2,AJC3を構成する受動部品が配置された領域を、符号AJC1,AJC2,AJC3を付したブロックで示してある。また、比較例の電力増幅モジュールPA101では、後述の制御回路CTC1に対応するものは、半導体チップCP101,CP102以外の半導体チップ(図示せず)に形成され、その半導体チップは、電力増幅モジュールPA101を構成する配線基板111の上面111a上に配置されるか、あるいは電力増幅モジュールPA101の外部に配置されている。

【0044】

なお、図4において、符号115bは、電力増幅モジュールPA101の外部接続用端子であり、理解を簡単にするために、配線基板111の上面111aに図示しているが、実際には配線基板111の下面に配置されている。また、符号115dは、配線基板111の配線パターンである。また、図4は、平面図であるが、図面を見やすくするために、半導体チップCP101,102におけるパッド電極PD101G,PD101D,PD102G,PD102Dとそれにつながるゲート配線およびドレイン配線を、ハッチングを付して示してある。

【0045】

図4に示される比較例の電力増幅モジュールPA101は、上記図2のように、整合回路AJC1と、半導体チップCP101内の増幅回路AMP1と、整合回路AJC2と、半導体チップCP102内の増幅回路AMP2と、整合回路AJC3とが順に直列に接続された回路構成を有している。

【0046】

このため、図4に示されるように、半導体チップCP101の主面(上面)において、ゲート用のパッド電極PD101Gとドレイン用のパッド電極PD101Dとを、半導体チップCP101の対向する辺にそれぞれ配置し、また、半導体チップCP102の主面(上面)において、ゲート用のパッド電極PD102Gとドレイン用のパッド電極PD102Dとを、半導体チップCP101の対向する辺にそれぞれ配置している。そして、配線基板111の上面111aにおいて、整合回路AJC1、半導体チップCP101、整合回路AJC2、半導体チップCP102および整合回路AJC3を順に並んで配置し、半導体チップCP101のゲート用のパッド電極PD101Gを整合回路AJC1にワイヤWA101で接続し、半導体チップCP101のドレイン用のパッド電極PD101Dを整合回路AJC2にワイヤWA101で接続している。また、半導体チップCP102のゲート用のパッド電極PD102Gを整合回路AJC2にワイヤWA101で接続し、半導体チップCP102のドレイン用のパッド電極PD102Dを整合回路AJC3にワイヤWA101で接続している。このような配置にすることで、配線基板111の上面111aでの各部品(半導体チップCP101,CP102および整合回路AJC1,AJC2,AJC3を構成する受動部品)の配置効率を高めることができる。

【0047】

しかしながら、図4に示される比較例の電力増幅モジュールPA101では、増幅回路AMP1を内蔵した半導体チップCP101と増幅回路AMP2を内蔵した半導体チップ102とを別個に用意している分、配線基板111上に搭載する半導体チップの数が多くなるため、電力増幅モジュールPA101が大型化(大面積化)し、またコストも増大してしまう。このため、本実施の形態のように、増幅回路AMP1および増幅回路AMP2を、1つの半導体チップCP1内に内蔵させることが好ましい。

【0048】

<電力増幅モジュールのレイアウトおよび接続関係について>

図5は、本実施の形態の電力増幅モジュールPA1の構造を示す概念的な平面図(上面図)であり、封止樹脂13を透視し、配線基板11の上面11a上における半導体チップCP1および上記整合回路AJC1,AJC2,AJC3(を構成する受動部品12)の配置状態が模式的に示されている。

【0049】

なお、配線基板11の上面11a上には、上記整合回路AJC1,AJC2,AJC3を構成する上記受動部品12も搭載されているが、図面の簡略化のために、図5では、各整合回路AJC1,AJC2,AJC3を構成する上記受動部品12が配置された領域を、各整合回路を示す符号AJC1,AJC2,AJC3を付したブロックで示してある。また、図5において、理解を簡単にするために、配線基板11の上面11aに外部接続用端子15bを図示しているが、実際には、上記図3にも示されるように、外部接続用端子15bは配線基板11の下面11bに配置されている。また、図5において、符号15dは、配線基板11の配線パターンである。

【0050】

上記図2および図5に示されるように、本実施の形態の電力増幅モジュールPA1は、整合回路AJC1と、半導体チップCP1内の増幅回路AMP1と、整合回路AJC2と、半導体チップCP1内の増幅回路AMP2と、整合回路AJC3とが順に直列に接続された回路構成を有している。増幅回路AMP1,AMP2および制御回路CTC1は半導体チップCP1内に形成され、整合回路AJC1,AJC2,AJC3は、配線基板11上に搭載された上記受動部品12や配線基板11の導体パターン(配線パターン)などによって形成されている。

【0051】

制御回路CTC1は、増幅回路AMP1,AMP2の増幅動作の制御や補佐などを行う回路である。制御回路CTC1には、電源電圧VDD1,VDD2が入力され、増幅回路AMP1,AMP2に印加するバイアス電圧や、増幅回路AMP1,AMP2のドレインに印加する電圧を制御する機能などを有している。

【0052】

半導体チップCP1に増幅回路AMP1,AMP2および制御回路CTC1を内蔵させることで、電力増幅モジュールPA1を構成するのに必要な半導体チップの数(すなわち配線基板11上に搭載する半導体チップの数)を少なくすることができるため、電力増幅モジュールPA1を小型化(小面積化)することができ、また、電力増幅モジュールPA1のコストを低減できる。

【0053】

増幅回路AMP1,AMP2のそれぞれは、半導体チップCP1内に形成されたMISFET素子、より特定的にはLDMOSFET(Laterally Diffused Metal-Oxide-Semiconductor Field Effect Transistor、横方向拡散MOSFET)素子、により形成されている。そして、増幅回路AMP1を構成するLDMOSFETと増幅回路AMP2を構成するLDMOSFETとが従属接続(多段接続)されて、電力増幅モジュールPA1の電力増幅回路を構成している。

【0054】

図5では、半導体チップCP1において、1段目の増幅回路AMP1を構成するLDMOSFET素子が形成された領域を、符号21を付してLDMOSFET形成領域21として示し、2段目の増幅回路AMP2を構成するLDMOSFET素子が形成された領域を、符号22を付してLDMOSFET形成領域22として示し、制御回路CTC1を構成する素子が形成された領域を、符号23を付して制御回路領域23として示してある。

【0055】

また、図5は、平面図であるが、図面を見やすくするために、半導体チップCP1におけるパッド電極PDと、半導体チップCP1においてLDMOSFET形成領域21(増幅回路AMP1)、LDMOSFET形成領域22(増幅回路AMP2)、制御回路領域23(制御回路CTC1)およびパッド電極PDの間を電気的に接続する配線とを、ハッチングを付して示してある。但し、このハッチングを付した配線と、LDMOSFET形成領域21、21および制御回路領域23は、実際には、半導体チップCP1の表面保護膜(後述の絶縁膜52)で覆われている。

【0056】

なお、本実施の形態では、2段の増幅回路AMP1,AMP2が接続(多段接続)されて電力増幅モジュールPA1の電力増幅回路が形成されているが、他の形態として、3段以上の増幅回路を接続(多段接続)して電力増幅モジュールPA1の電力増幅回路を形成することも可能であり、この場合、3段以上の増幅回路(LDMOSFET)が半導体チップCP1内に形成されることになる。

【0057】

図5に示されるように、半導体チップCP1は、パッド電極PDとして、ゲートパッド電極PD1G、ドレインパッド電極PD1D、ゲートパッド電極PD2G、ドレインパッド電極PD2Dおよび電源入力用パッド電極PD3,PD4を有している。

【0058】

このうち、ゲートパッド電極PD1Gは、増幅回路AMP1用のLDMOSFET(半導体チップCP1のLDMOSFET形成領域21に形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、かつ、整合回路AJC1を介してRF信号を半導体チップCP1に入力するための入力用のパッド電極PDである。また、ドレインパッド電極PD1Dは、増幅回路AMP1用のLDMOSFET(半導体チップCP1のLDMOSFET形成領域21に形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDであり、かつ、増幅回路AMP1で増幅したRF信号を半導体チップCP1から出力するための出力用のパッド電極PDである。また、ゲートパッド電極PD2Gは、増幅回路AMP2用のLDMOSFET(半導体チップCP1のLDMOSFET形成領域22に形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、かつ、ドレインパッド電極PD1Dから出力したRF信号を整合回路AJC2を介して半導体チップCP1に再入力するための入力用のパッド電極PDである。また、ドレインパッド電極PD2Dは、増幅回路AMP2用のLDMOSFET(半導体チップCP1のLDMOSFET形成領域22に形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDであり、かつ、増幅回路AMP2で増幅したRF信号を半導体チップCP1から出力するための出力用のパッド電極PDである。また、電源入力用パッド電極PD3,PD4は、半導体チップCP1内に形成された制御回路CTC1(制御回路領域23に形成された回路)に電気的に接続されており、電源入力用パッド電極PD3は、電源電圧VDD1を半導体チップCP1(の制御回路CTC1)に入力するための入力用のパッド電極PDである。また、電源入力用パッド電極PD4は、電源電圧VDD2を半導体チップCP1(の制御回路CTC1)に入力するための入力用のパッド電極PDである。

【0059】

このため、配線基板11上に搭載された半導体チップCP1のゲートパッド電極PD1Gを、整合回路AJC1に電気的に接続された基板側端子15aにワイヤWAで接続し、ドレインパッド電極PD1Dを、整合回路AJC2に電気的に接続された基板側端子15aにワイヤWAで接続している。そして、この整合回路AJC2に電気的に接続された他の基板側端子15aにゲートパッド電極PD2GをワイヤWAで接続し、ドレインパッド電極PD2Dを整合回路AJC3に電気的に接続された基板側端子15aにワイヤWAで接続している。また、電源電圧VDD1に電気的に接続される基板側端子15aに半導体チップCP1の電源入力用パッド電極PD3をワイヤWAで接続し、電源電圧VDD2に電気的に接続される基板側端子15aに半導体チップCP1の電源入力用パッド電極PD4をワイヤWAで接続している。

【0060】

本実施の形態の電力増幅モジュールPA1では、多段接続された複数の増幅回路AMP1,AMP2のうちの最終段の増幅回路AMP2とそれよりも1段前の増幅回路AMP1との間の段間整合回路用の受動部品12(ここでは整合回路AJC2用の受動部品12)が、配線基板11上に搭載されている。このため、最終段の増幅回路AMP2のゲートに接続されたゲートパッド電極PD2Gを半導体チップCP1に設け、整合回路AJC2を経たRF信号(送信信号)を、ゲートパッド電極PD2Gから半導体チップCP1内に再入力する必要がある。

【0061】

すなわち、電力増幅モジュールPA1の入力端子IPT1に対応する外部接続用端子15bに入力されたRF入力信号(送信信号)は、整合回路AJC1を経て半導体チップCP1のゲートパッド電極PD1Gに入力され、半導体チップCP1内の増幅回路AMP1(LDMOSFET形成領域21に形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD1Dから半導体チップCP1外に出力される。このドレインパッド電極PD1Dから出力されたRF信号(送信信号)は、半導体チップCP1外の整合回路AJC2を経て半導体チップCP1のゲートパッド電極PD2Gに再入力され、半導体チップCP1内の増幅回路AMP2(LDMOSFET形成領域22に形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD2Dから半導体チップCP1外に出力される。このドレインパッド電極PD2Dから出力されたRF信号(送信信号)は、整合回路AJC3を経て、出力端子OPT1に対応する外部接続用端子15bからRF出力信号(増幅された送信信号)として出力される。

【0062】

本実施の形態では、図5に示されるように、半導体チップCP1の主面(上面)において、ゲートパッド電極PD1Gとドレインパッド電極PD1Dとを半導体チップCP1の同じ辺に沿って配置し、ゲートパッド電極PD2Gとドレインパッド電極PD2Dとを半導体チップCP1の他の同じ辺に沿って配置し、電源入力用パッド電極PD3と電源入力用パッド電極PD4とを半導体チップCP1の更に他の同じ辺に沿って配置している。半導体チップCP1のパッド電極PDをこのような配置にすることで、半導体チップCP1の各パッド電極PDと整合回路AJC1,AJC2,AJC3とを接続しやすくし、配線基板11の上面11aでの各部品(半導体チップCP1および整合回路AJC1,AJC2,AJC3を構成する上記受動部品12)の配置効率を高め、また配線基板11における配線の引き回しのしやすさを高めることができる。特に、ゲートパッド電極PD2Gとドレインパッド電極PD2Dとを半導体チップCP1の主面(上面)の同じ辺に沿って配置することが重要である。

【0063】

図6は、本実施の形態の電力増幅モジュールPA1の変形例(すなわち電力増幅モジュールPA1a)を示す概念的な平面図(上面図)であり、上記図5に対応するものであり、封止樹脂13を透視してある。

【0064】

図6に示される、本実施の形態の変形例の電力増幅モジュールPA1aは、2系統(ここではGSM900用およびDCS1800用)の電力増幅回路を有し、2系統の電力増幅回路の送信周波数帯は、それぞれ0.9GHz帯(824〜915MHz)と1.8GHz帯(1710〜1910MHz)である。

【0065】

ここで、GSM(Global System for Mobile Communication)は、デジタル携帯電話に使用されている無線通信方式の1つまたは規格をいう。GSMには、使用する電波の周波数帯が3つあり、900MHz帯をGSM900または単にGSM、1800MHz帯をGSM1800またはDCS(Digital Cellular System)1800若しくはPCN、1900MHz帯をGSM1900またはDCS1900若しくはPCS(Personal Communication Services)という。

【0066】

図6に示される電力増幅モジュールPA1aの回路構成は、2つの増幅回路(増幅段)AMP1a,AMP2aと整合回路AJC1a,AJC2a,AJC3aとからなるGSM900用の電力増幅回路と、2つの増幅回路(増幅段)AMP1b,AMP2bと整合回路AJC1b,AJC2b,AJC3bとからなるDCS1800用の電力増幅回路と、それら電力増幅回路の増幅動作の制御や補佐などを行う制御回路CTC1とを有している。

【0067】

具体的には、電力増幅モジュールPA1aは、GSM900用の入力端子IPT1a用の外部接続用端子15bと出力端子OPT1a用の外部接続用端子15bとの間に、入力用の整合回路AJC1aと、GSM900用の1段目の増幅回路AMP1aと、段間用の整合回路AJC2aと、GSM900用の2段目の増幅回路AMP2aと、出力用の整合回路AJC3aとが順に直列に接続されたGSM900用の電力増幅回路を有している。また、電力増幅モジュールPA1aは、DCS1800用の入力端子IPT1b用の外部接続用端子15bと出力端子OPT1b用の外部接続用端子15bとの間に、入力用の整合回路AJC1bと、DCS1800用の1段目の増幅回路AMP1bと、段間用の整合回路AJC2bと、DCS1800用の2段目の増幅回路AMP2bと、出力用の整合回路AJC3bとが順に直列に接続されたDCS1800用の電力増幅回路を有している。増幅回路AMP1a,AMP2a,AMP1b,AMP2bおよび制御回路CTC1は半導体チップCP1内に形成され、整合回路AJC1a,AJC2a,AJC3a,AJC1b,AJC2b,AJC3bは、配線基板11上に搭載された上記受動部品12や配線基板11の導体パターンなどによって形成されている。

【0068】

なお、配線基板11の上面11a上には、上記整合回路AJC1a〜AJC3a,AJC1b〜AJC3bを構成する上記受動部品12も搭載されているが、図面の簡略化のために、図6では、各整合回路AJC1a〜AJC3a,AJC1b〜AJC3bを構成する上記受動部品12が配置された領域を、整合回路を示す符号AJC1a〜AJC3a,AJC1b〜AJC3bを付したブロックで示してある。また、図5と同様に、図6においても、理解を簡単にするために、配線基板11の上面11aに外部接続用端子15bを図示しているが、実際には、上記図3にも示されるように、外部接続用端子15bは配線基板11の下面11bに配置されている。

【0069】

増幅回路AMP1a,AMP2a,AMP1b,AMP2bのそれぞれは、半導体チップCP1内に形成されたMISFET素子、より特定的にはLDMOSFET素子、により形成されている。そして、増幅回路AMP1aを構成するLDMOSFETと増幅回路AMP2aを構成するLDMOSFETとが従属接続(多段接続)されて、GSM900用の電力増幅回路が形成され、また、増幅回路AMP1bを構成するLDMOSFETと増幅回路AMP2bを構成するLDMOSFETとが従属接続(多段接続)されて、DCS1800用の電力増幅回路が形成されている。

【0070】

図6では、半導体チップCP1において、GSM900用の1段目の増幅回路AMP1aを構成するLDMOSFET素子が形成された領域を、符号21aを付してLDMOSFET形成領域21aとして示し、GSM900用の2段目の増幅回路AMP2aを構成するLDMOSFET素子が形成された領域を、符号22aを付してLDMOSFET形成領域22aとして示している。また、DCS1800用の1段目の増幅回路AMP1bを構成するLDMOSFET素子が形成された領域を、符号21bを付してLDMOSFET形成領域21bとして示し、DCS1800用の2段目の増幅回路AMP2bを構成するLDMOSFET素子が形成された領域を、符号22bを付してLDMOSFET形成領域22bとして示している。また、図6は、平面図であるが、図面を見やすくするために、半導体チップCP1におけるパッド電極PDと、半導体チップCP1において増幅回路AMP1a,AMP2a,AMP1b,AMP2b、制御回路CTC1およびパッド電極PDの間を電気的に接続する配線とに、ハッチングを付して示してある。

【0071】

図6に示される半導体チップCP1は、パッド電極PDとして、ゲートパッド電極PD1Ga,PD2Ga,PD1Gb,PD2Gb、ドレインパッド電極PD1Da,PD2Da,PD1Db,PD2Dbおよび電源入力用パッド電極PD3,PD4を有している。

【0072】

このうち、ゲートパッド電極PD1Gaは、増幅回路AMP1a用のLDMOSFET(LDMOSFET形成領域21aに形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、ドレインパッド電極PD1Daは、増幅回路AMP1a用のLDMOSFET(LDMOSFET形成領域21aに形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDである。また、ゲートパッド電極PD2Gaは、増幅回路AMP2a用のLDMOSFET(LDMOSFET形成領域22aに形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、ドレインパッド電極PD2Daは、増幅回路AMP2a用のLDMOSFET(LDMOSFET形成領域22aに形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDである。また、ゲートパッド電極PD1Gbは、増幅回路AMP1b用のLDMOSFET(LDMOSFET形成領域21bに形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、ドレインパッド電極PD1Dbは、増幅回路AMP1b用のLDMOSFET(LDMOSFET形成領域21bに形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDである。また、ゲートパッド電極PD2Gbは、増幅回路AMP2b用のLDMOSFET(LDMOSFET形成領域22bに形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、また、ドレインパッド電極PD2Dbは、増幅回路AMP2b用のLDMOSFET(LDMOSFET形成領域22bに形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDである。電源入力用パッド電極PD3,PD4については、上記図5の場合と同様であるので、ここではその説明は省略する。

【0073】

このため、配線基板11上に搭載された半導体チップCP1のゲートパッド電極PD1Gaを、整合回路AJC1aに電気的に接続された基板側端子15aにワイヤWAで接続し、ドレインパッド電極PD1Daを、整合回路AJC2aに電気的に接続された基板側端子15aにワイヤWAで接続している。そして、この整合回路AJC2aに電気的に接続された他の基板側端子15aに、ゲートパッド電極PD2GaをワイヤWAで接続し、ドレインパッド電極PD2Daを、整合回路AJC3aに電気的に接続された基板側端子15aにワイヤWAで接続している。

【0074】

また、配線基板11上に搭載された半導体チップCP1のゲートパッド電極PD1Gbを、整合回路AJC1bに電気的に接続された基板側端子15aにワイヤWAで接続し、ドレインパッド電極PD1Dbを、整合回路AJC2bに電気的に接続された基板側端子15aにワイヤWAで接続している。そして、この整合回路AJC2bに電気的に接続された他の基板側端子15aに、ゲートパッド電極PD2GbをワイヤWAで接続し、ドレインパッド電極PD2Dbを、整合回路AJC3bに電気的に接続された基板側端子15aにワイヤWAで接続している。

【0075】

また、電源電圧VDD1に電気的に接続される基板側端子15aに、半導体チップCP1の電源入力用パッド電極PD3をワイヤWAで接続し、電源電圧VDD2に電気的に接続される基板側端子15aに、半導体チップCP1の電源入力用パッド電極PD4をワイヤWAで接続している。

【0076】

本実施の形態の電力増幅モジュールPA1aでは、多段接続された複数の増幅回路AMP1a,AMP2aのうちの最終段の増幅回路AMP2aとそれよりも1段前の増幅回路AMP1aとの間の段間整合回路用の受動部品12(ここでは整合回路AJC2a用の受動部品12)が配線基板11上に搭載されている。また、多段接続された複数の増幅回路AMP1b,AMP2bのうちの最終段の増幅回路AMP2bとそれよりも1段前の増幅回路AMP1bとの間の段間整合回路用の受動部品12(ここでは整合回路AJC2b用の受動部品12)が配線基板11上に搭載されている。このため、最終段の増幅回路AMP2a,AMP2bの各ゲートに接続されたゲートパッド電極PD2Ga,PD2Gbを半導体チップCP1に設け、各整合回路AJC2a,AJC2bを経たRF信号(送信信号)を、ゲートパッド電極PD2Ga,PD2Gbから半導体チップCP1内に再入力する必要がある。

【0077】

すなわち、電力増幅モジュールPA1aの入力端子IPT1aに対応する外部接続用端子15bに入力されたGSM900用RF入力信号(送信信号)は、整合回路AJC1aを経て半導体チップCP1のゲートパッド電極PD1Gaに入力され、半導体チップCP1内の増幅回路AMP1a(LDMOSFET形成領域21aに形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD1Daから出力される。このドレインパッド電極PD1Daから出力されたGSM900用のRF信号(送信信号)は、半導体チップCP1外の整合回路AJC2aを経て半導体チップCP1のゲートパッド電極PD2Gaに再入力され、半導体チップCP1内の増幅回路AMP2a(LDMOSFET形成領域22aに形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD2Daから出力される。このドレインパッド電極PD2Daから出力されたRF信号(送信信号)は、整合回路AJC3aを経て、出力端子OPT1aに対応する外部接続用端子15bからGSM900用のRF出力信号(増幅された送信信号)として出力される。

【0078】

また、電力増幅モジュールPA1aの入力端子IPT1bに対応する外部接続用端子15bに入力されたDCS1800用RF入力信号(送信信号)は、整合回路AJC1bを経て半導体チップCP1のゲートパッド電極PD1Gbに入力され、半導体チップCP1内の増幅回路AMP1b(LDMOSFET形成領域21bに形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD1Dbから出力される。このドレインパッド電極PD1Dbから出力されたDCS1800用のRF信号(送信信号)は、半導体チップCP1外の整合回路AJC2bを経て半導体チップCP1のゲートパッド電極PD2Gbに再入力され、半導体チップCP1内の増幅回路AMP2b(LDMOSFET形成領域22bに形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD2Dbから出力される。このドレインパッド電極PD2Dbから出力されたRF信号(送信信号)は、整合回路AJC3bを経て、出力端子OPT1bに対応する外部接続用端子15bからDCS1800用のRF出力信号(増幅された送信信号)として出力される。

【0079】

図6に示される電力増幅モジュールPA1aでは、GSM900用の増幅回路AMP1a,AMP2aとDCS1800用の増幅回路AMP1b,AMP2bと制御回路CTC1とを、1つの半導体チップCP1内に内蔵させている。これにより、電力増幅モジュールPA1aに使用する半導体チップの数を少なくして電力増幅モジュールPA1aを小型化(小面積化)することができ、また、電力増幅モジュールPA1aのコストを低減できる。

【0080】

更に、図6の電力増幅モジュールPA1aでは、半導体チップCP1の主面(上面)において、GSM900用の増幅回路AMP2aに接続されたゲートパッド電極PD2Gaとドレインパッド電極PD2Daとを半導体チップCP1の同じ辺に沿って配置し、DCS1800用の増幅回路AMP2bに接続されたゲートパッド電極PD2Gbとドレインパッド電極PD2Dbとを半導体チップCP1の他の同じ辺に沿って配置している。ここで、GSM900用のゲートパッド電極PD2Gaおよびドレインパッド電極PD2Daが配置された半導体チップCP1の辺と、DCS1800用のゲートパッド電極PD2Gbおよびドレインパッド電極PD2Dbが配置された半導体チップCP1の辺とは、半導体チップCP1の主面(上面)において、互いに対向する辺である。半導体チップCP1のパッド電極PDをこのような配置にすることで、半導体チップCP1の各パッド電極PDと整合回路AJC1a〜AJC3a,AJC1b〜AJC3bとを接続しやすくし、配線基板11の上面11aでの各部品(半導体チップCP1および受動部品12)の配置効率を高め、また配線基板11における配線の引き回しのしやすさを高めることができる。

【0081】

このように、電力増幅モジュールPA1,PA1aにおいては、複数段の増幅回路を1つの半導体チップCP1に内蔵させているため、半導体チップCP1におけるパッド電極PDの種類や数が多い。このため、整合回路との接続しやすさを考慮すると、半導体チップCP1に設けられた複数段の増幅回路のうち、特に最終段の増幅回路(上記増幅回路AMP2,AMP2a,AMP2bに対応)に接続されたゲートパッド電極とドレインパッド電極とを半導体チップCP1の主面(上面)の同じ辺に沿って配置することが望ましい。すなわち、図5のように、ゲートパッド電極PD2Gとドレインパッド電極PD2Dとを半導体チップCP1の主面(上面)の同じ辺に沿って配置することが望ましい。あるいは、図6のように、ゲートパッド電極PD2Gaとドレインパッド電極PD2Daとを半導体チップCP1の主面(上面)の同じ辺に沿って配置し、ゲートパッド電極PD2Gbとドレインパッド電極PD2Dbとを半導体チップCP1の主面(上面)の他の同じ辺に沿って配置することが望ましい。

【0082】

しかしながら、半導体チップの主面において、同じ辺に沿ってゲートパッド電極とドレインパッド電極とを配置した場合、ドレインパッド電極が配置されている辺まで配線でゲートパッド電極を引き回す必要があるため、半導体チップにおけるゲートパッド電極用の配線が長くなってしまう。本発明者が検討したところ、これは、電力損失を高め、電力増幅モジュールの効率を低下させる可能性があることが分かった。そこで、本実施の形態では、半導体チップCP1の構成を以下のように工夫している。

【0083】

<半導体チップの構成について>

図7〜図10は、半導体チップCP1の要部断面図である。図7には、半導体チップCP1において、上記LDMOSFET形成領域22,22a,22bの要部断面図が示されている。図8は、図7とは異なる断面位置が示され、素子分離領域32上においてゲート電極35をゲート配線M1G,M2Gに引き上げている領域の断面図に対応する。図9は、図7および図8とは異なる断面位置が示され、ドレインパッド電極PD2D,PD2Da,PD2Dbが形成された領域の断面図に対応する。図10は、図7〜図9とは異なる断面位置が示され、ゲートパッド電極PD2G,PD2Ga,PD2Gbが形成された領域の断面図に対応する。

【0084】

図7〜図10に示されるように、半導体チップCP1を構成するp+型単結晶シリコンからなる半導体基板30の主面には、p−型単結晶シリコンからなるエピタキシャル層31が形成されている。エピタキシャル層31には、絶縁体からなる素子分離領域32が形成されている。なお、図7は、素子分離領域32に囲まれた活性領域(後述の活性領域AR1に対応)を横切る断面図に対応するため、図7には素子分離領域32は示されておらず、図8〜図10は、活性領域を囲む素子分離領域32を横切る断面図に対応するため、図8〜図12には素子分離領域32が示されている。

【0085】

素子分離領域32は、例えばSTI(Shallow Trench Isolation)法またはLOCOS(Local Oxidization of Silicon )法などにより形成されている。素子分離領域32により、半導体基板30の主面(エピタキシャル層31の主面)に後述の活性領域AR1が規定され、この活性領域AR1にLDMOSFETのセル(単位LDMOSFET素子)が複数形成される。活性領域AR1は、周囲を素子分離領域32によって囲まれている。

【0086】

エピタキシャル層31の主面の一部には、LDMOSFETのドレインからソースへの空乏層の延びを抑えるパンチスルーストッパとして機能するp型ウエル33が形成されている。p型ウエル33の表面には、酸化シリコンなどからなるゲート絶縁膜34を介してLDMOSFETのゲート電極35が形成されている。ゲート電極35は、例えばn型の多結晶シリコン膜の単体膜あるいはn型の多結晶シリコン膜と金属シリサイド膜との積層膜などからなり、ゲート電極35の側壁には、酸化シリコンなどからなるサイドウォールスペーサ(側壁絶縁膜)36が形成されている。

【0087】

エピタキシャル層31の内部のチャネル形成領域(ゲート電極35の直下の領域)を挟んで互いに離間する領域には、LDMOSFETのソース、ドレインが形成されている。ドレインは、チャネル形成領域に接するn−型ドリフト領域(n−型オフセットドレイン領域)37と、n−型ドリフト領域37に接し、チャネル形成領域から離間して形成されたn型ドリフト領域(n型オフセットドレイン領域、ドレイン高濃度領域)38と、n型ドリフト領域38に接し、チャネル形成領域からさらに離間して形成されたn+型ドレイン領域(ドレイン高濃度領域)39とからなる。

【0088】

これらn−型ドリフト領域37、n型ドリフト領域38およびn+型ドレイン領域39のうち、ゲート電極35に最も近いn−型ドリフト領域37は不純物濃度が最も低く、ゲート電極35から最も離間したn+型ドレイン領域39は不純物濃度が最も高い。また、n型ドリフト領域38の接合深さは、n−型ドリフト領域37の接合深さとほぼ同じであるが、n+型ドレイン領域39は、n型ドリフト領域38およびn−型ドリフト領域37に比べて浅く形成されている。

【0089】

n−型ドリフト領域37は、ゲート電極35に対して自己整合的に形成され、n−型ドリフト領域37は、その端部がチャネル形成領域と接するように、ゲート電極35の側壁下部で終端している。また、n型ドリフト領域38は、ゲート電極35のドレイン側の側壁に形成されたサイドウォールスペーサ36に対して自己整合的に形成されることから、n型ドリフト領域38は、ゲート長方向に沿ったサイドウォールスペーサ36の膜厚に相当する分、ゲート電極35から離間して形成される。

【0090】

LDMOSFETのソースは、チャネル形成領域に接するn−型ソース領域40と、n−型ソース領域40に接し、チャネル形成領域から離間して形成され、n−型ソース領域40よりも不純物濃度が高いn+型ソース領域41とからなる。

【0091】

n−型ソース領域40は、ゲート電極35に対して自己整合的に形成され、その端部がチャネル形成領域と接するように、ゲート電極35の側壁下部で終端している。また、n−型ソース領域40の下部に、p型ハロー領域(図示せず)を形成することもでき、このp型ハロー領域は、必ずしも形成する必要はないが、これを形成した場合は、ソースからチャネル形成領域への不純物の広がりがさらに抑制され、さらに短チャネル効果が抑制されるので、しきい値電圧の低下をさらに抑制することができる。

【0092】

n+型ソース領域41は、ゲート電極35のソース側の側壁に形成されたサイドウォールスペーサ36に対して自己整合的に形成されているため、n+型ソース領域41は、n−型ソース領域40に接して形成され、かつ、ゲート長方向に沿ったサイドウォールスペーサ36の膜厚に相当する分、チャネル形成領域から離間して形成されている。n+型ソース領域41の底部の位置は、n−型ソース領域40の底部の位置よりも深い。

【0093】

このように、ゲート電極35とn+型ドレイン領域39との間に介在するドリフト領域(LDD領域、オフセットドレイン領域)を二重オフセット構造とし、ゲート電極35に最も近いn−型ドリフト領域37の不純物濃度を相対的に低く、ゲート電極35から離間したn型ドリフト領域38の不純物濃度を相対的に高くしている。これにより、ゲート電極35とドレインとの間に空乏層が広がるようになる結果、ゲート電極35とその近傍のn−型ドリフト領域37との間に形成される帰還容量(ドレインとゲート電極間の寄生容量、Cgd)は小さくなる。また、n型ドリフト領域38の不純物濃度が高いことから、オン抵抗(Ron)も小さくなる。n型ドリフト領域38は、ゲート電極35から離間した位置に形成されているために、n型ドリフト領域38の不純物濃度を高くしても、帰還容量(Cgd)に及ぼす影響は僅かである。このため、オン抵抗(Ron)と帰還容量(Cgd)を共に小さくすることができるので、増幅回路の電力付加効率を向上させることができる。

【0094】

なお、本願において、MOSFETまたはLDMOSFETというときは、ゲート絶縁膜に酸化膜(酸化シリコン膜)を用いたMISFETだけでなく、酸化膜(酸化シリコン膜)以外の絶縁膜をゲート絶縁膜に用いたMISFETも含むものとする。

【0095】

ここで、LDMOSFETは、MISFET(Metal Insulator Semiconductor Field Effect Transistor:MIS型電界効果トランジスタ)素子であるが、次のような特徴(第1〜第3の特徴)を有するMISFET素子である。

【0096】

第1の特徴として、LDMOSFETは、短いチャネル長で高電圧動作を可能とするために、ゲート電極35のドレイン側にLDD(Lightly doped drain)領域が形成されている。すなわち、LDMOSFETのドレインは、高不純物濃度のn+型領域(ここではn+型ドレイン領域39)と、それよりも低不純物濃度のLDD領域(ここではn−型ドリフト領域37およびn型ドリフト領域38)とから構成され、n+型領域(n+型ドレイン領域39)はLDD領域を介してゲート電極35(またはゲート電極35の下のチャネル形成領域)から離間して形成されている。これにより、高耐圧を実現することができる。ドレイン側のLDD領域における電荷量(不純物濃度)、およびゲート電極35の端部とn+型ドレイン領域(ドレイン高濃度領域)39との間の平面(エピタキシャル層31の主面)に沿った距離は、LDMOSFETのブレークダウン電圧が最大値となるように最適化しなければならない。

【0097】

第2の特徴として、LDMOSFETは、ソース側のソース形成領域(n−型ソース領域40およびn+型ソース領域41)とチャネル形成領域とに、パンチスルーストッパ用のp型ウエル(p型ベース領域)33が形成されている。LDMOSFETのドレイン側(ドレイン形成領域)では、このp型ウエル33は、形成されていないか、あるいはチャネル領域に近い側のドレイン形成領域の一部に接するようにしか形成されていない。

【0098】

第3の特徴として、LDMOSFETは、ソース(ここではn−型ソース領域40およびn+型ソース領域41からなるソース領域)とドレイン(ここではn−型ドリフト領域37、n型ドリフト領域38およびn+型ドレイン領域39からなるドレイン領域)とが、ゲート電極35に対して非対称な構造を有している。

【0099】

n+型ソース領域41の端部(n−型ソース領域40と接する側とは反対側の端部)には、n+型ソース領域41と接するp型打抜き層(p型半導体領域)44が形成されている。p型打抜き層44の表面近傍には、p型打抜き層44よりも高不純物濃度のp+型半導体領域45が形成されている。p型打抜き層44は、LDMOSFETのソースと半導体基板30とを電気的に接続するための導電層であり、例えばエピタキシャル層31に形成した溝の内部に埋め込んだp型多結晶シリコン膜によって形成される。p型打抜き層44の先端部(底部)は、半導体基板30に達している。

【0100】

エピタキシャル層31の主面上には、ゲート電極35およびサイドウォールスペーサ36を覆うように、絶縁膜(層間絶縁膜)46が形成されている。絶縁膜46は、例えば、薄い窒化シリコン膜とその上の厚い酸化シリコン膜の積層膜などからなる。絶縁膜46の上面は平坦化されている。

【0101】

絶縁膜46には、コンタクトホール(開口部、スルーホール、貫通孔)47が形成され、コンタクトホール47内には、タングステン(W)膜を主体とするプラグ(接続用埋込導体)48が埋め込まれている。コンタクトホール47およびそれを埋め込むプラグ48

は、p型打抜き層44(p+型半導体領域45)、ソース(n+型ソース領域41)、ドレイン(n+型ドレイン領域39)、およびゲート電極35のそれぞれの上部に形成されている。

【0102】

プラグ48が埋め込まれた絶縁膜46上には、タングステン(W)などを主体とする導電体膜(タングステン膜)からなる配線(第1層配線)M1が形成されている。配線M1は、プラグ48が埋め込まれた絶縁膜46上に形成した導電体膜(タングステン膜)をパターニングすることにより形成されている。配線M1は、タングステン配線に限定されず、アルミニウム配線など他の金属材料を用いた配線とすることもできる。

【0103】

配線M1は、プラグ48を介してn+型ソース領域41およびp+型半導体領域45の両者に電気的に接続するソース配線(ソース電極)M1Sと、プラグ48を介してn+型ドレイン領域39に電気的に接続するドレイン配線(ドレイン電極)M1Dと、プラグ48を介してゲート電極35に電気的に接続するゲート配線M1Gとを有している。

【0104】

絶縁膜46上に、配線M1を覆うように、酸化シリコン膜などからなる絶縁膜(層間絶縁膜)49が形成されている。絶縁膜49には、底部で配線M1の一部を露出するスルーホール(開口部、貫通孔)50が形成されている。スルーホール50内を含む絶縁膜49上には、アルミニウム(Al)またはアルミニウム合金などを主体とする導電体膜からなる配線M2およびパッド電極51が形成されている。

【0105】

配線M2およびパッド電極51は、例えば、スルーホール50内を含む絶縁膜49上に、バリア導体膜(例えばチタン膜と窒化チタン膜の積層膜)、アルミニウム膜(またはアルミニウム合金膜)およびバリア導体膜(例えばチタン膜と窒化チタン膜の積層膜)の積層膜からなる導電体膜を形成してから、この導電体膜をパターニングすることで形成されている。この積層膜では、主導体膜であるアルミニウム膜の膜厚に比べて、その上下のバリア導体膜の膜厚は薄い。この積層膜におけるアルミニウム膜の下側のバリア導体膜は、アルミニウム膜と下層の配線M1との反応を抑制する機能や、配線M2と絶縁膜49との密着性を向上させる機能などを有している。一方、この積層膜におけるアルミニウム膜の上側のバリア導体膜は、配線M2と絶縁膜(表面保護膜)52との密着性を向上させる機能や、フォトリソグラフィ処理の露光時の反射防止膜としての機能などを有している。このように、配線M2とパッド電極51とは、同じ導電体膜をパターニングすることにより形成されているため、半導体チップCP1において配線M2とパッド電極51とは同層に形成されている。

【0106】

配線M2は、絶縁膜49上に延在するとともに、一部がスルーホール50内を埋め、スルーホール50の底部で配線M1と電気的に接続されている。従って、配線M2は、絶縁膜49上を延在する配線部と、スルーホール50内を埋めるビア部(接続部)とが一体的に形成されている。パッド電極51は、絶縁膜49上に延在し、配線M2と同層の導電体膜により配線M2と一体的に形成されている。

【0107】

配線M2は、ビア部(スルーホール50を埋める部分)を介してドレイン配線M1Dに電気的に接続するドレイン配線M2Dと、ビア部(スルーホール50を埋める部分)を介してゲート配線M1Gに電気的に接続するゲート配線M2Gと、ビア部(スルーホール50を埋める部分)を介してソース配線M1Sに電気的に接続するソース配線M2Sとを有している。また、パッド電極51は、ドレイン配線M2Dと一体的に形成されたドレインパッド電極51Dと、ゲート配線M2Gと一体的に形成されたゲートパッド電極51Gとを有している。

【0108】

また、他の形態として、スルーホール50内に上記プラグ48と同様のプラグ埋め込み、このプラグが埋め込まれた絶縁膜49上に配線M2形成用の導電体膜を形成し、この導電体膜をパターニングして配線M2およびパッド電極51を形成することもでき、この場合、配線M2は、スルーホール50内を埋めるプラグを介して配線M1と電気的に接続されることになる。

【0109】

絶縁膜49上に、配線M2を覆うように、絶縁膜(表面保護膜)52が形成されている。この絶縁膜52は、例えば、酸化シリコン膜とその上の窒化シリコン膜の積層膜などからなり、半導体チップCP1の最表面の保護膜として機能することができる。絶縁膜52には、パッド電極用の開口部(スルーホール、貫通孔)53が形成されており、開口部53の底部でパッド電極51が露出されている。すなわち、各パッド電極51上に開口部53が形成され、その開口部53から各パッド電極51の一部が露出されている。パッド電極51と開口部53の平面形状および位置は、開口部53がパッド電極51に平面的に内包されるような関係にある。好ましくは、開口部53およびパッド電極51は、それぞれ矩形の平面形状を有しており、開口部53の平面形状はパッド電極51の平面形状よりも若干小さい。

【0110】

開口部53から露出するパッド電極51が、上記パッド電極PDに対応する。開口部53のうち、ドレインパッド電極51D上に形成されてドレインパッド電極51Dの一部を露出する開口部53をドレインパッド用開口部53Dと称し、ゲートパッド電極51G上に形成されてゲートパッド電極51Gの一部を露出する開口部をゲートパッド用開口部53Gと称するものとする。従って、ドレインパッド用開口部53Dから露出するドレインパッド電極51Dが、上記ドレインパッド電極PD2D,PD2Da,PD2Dbに対応する。また、ゲートパッド用開口部53Gから露出するゲートパッド電極51Gが、上記ゲートパッド電極PD2G,PD2Ga,PD2Gbに対応する。開口部53から露出するパッド電極51(すなわち上記パッド電極PD)には、上述のように、半導体チップCP1を上記配線基板11に搭載してから上記ワイヤWAが接続される。

【0111】

また、上述のように、配線M2およびパッド電極51を、バリア導体膜、アルミニウム膜およびバリア導体膜の積層膜からなる導電体膜をパターニングすることで形成した場合には、絶縁膜52に開口部53を形成する際のドライエッチングで、最上層のバリア導体膜を除去することもできる。この場合、パッド電極51のうち開口部53から露出する部分は、バリア導体膜とその上のアルミニウム膜との積層膜からなり、開口部53からは、パッド電極51を構成するアルミニウム膜(またはアルミニウム合金膜)の表面が露出されており、一方、絶縁膜52で覆われている部分のパッド電極51と配線M2とは、バリア導体膜とその上のアルミニウム膜とその上のバリア導体膜との積層膜からなる。

【0112】

半導体基板30の裏面(エピタキシャル層31が形成されている側の主面とは反対側の主面)には、ソース裏面電極(裏面電極)54が形成されている。ソース裏面電極(裏面電極)54は、半導体チップCP1を構成する半導体基板30の裏面全体に形成されており、上記裏面電極BE1に対応するものである。

【0113】

エピタキシャル層31に形成されたLDMOSFETのソース(n−型ソース領域40およびn+型ソース領域41)は、プラグ48(n+型ソース領域41上に配置されたプラグ48)、ソース配線(ソース電極)M1S、プラグ48(p+型半導体領域45上に配置されたプラグ48)、p+型半導体領域45、p型打抜き層44および半導体基板30を介して、ソース裏面電極54(裏面電極BE1)に電気的に接続されている。

【0114】

他の形態として、更に、n+型ソース領域41およびp+型半導体領域45の表面(上部)に金属シリサイド層(例えばコバルトシリサイド層、図示せず)を形成し、この金属シリサイド層を介して、n+型ソース領域41とp+型半導体領域45とを電気的に接続することもでき、これによりソース抵抗を更に低減することができる。

【0115】

エピタキシャル層31に形成されたLDMOSFETのドレイン(n−型ドリフト領域37、n型ドリフト領域38およびn+型ドレイン領域39)は、プラグ48(n+型ドレイン領域39上に配置されたプラグ48)、ドレイン配線(ドレイン電極)M1Dおよびドレイン配線M2Dを介して、ドレインパッド電極51Dに電気的に接続されている。

【0116】

エピタキシャル層31に形成されたLDMOSFETのゲート電極35は、プラグ48(ゲート電極35上に配置されたプラグ48)、ゲート配線M1Gおよびゲート配線M2Gを介して、ゲートパッド電極51Gに電気的に接続されている。

【0117】

<LDMOSFET形成領域近傍のレイアウトについて>

次に、上記LDMOSFET形成領域22,22a,22bおよびその近傍における各構成要素の平面レイアウトについて説明する。以降(後述の実施の形態2〜4も含む)の説明では、主としてLDMOSFET形成領域22について説明するが、LDMOSFET形成領域22a,22bについても同様であり、LDMOSFET形成領域22をLDMOSFET形成領域22aまたはLDMOSFET形成領域22bに読み替えればよい。なお、LDMOSFET形成領域22をLDMOSFET形成領域22aに読み替えた場合は、増幅回路AMP1、増幅回路AMP2、ドレインパッド電極PD2D、ゲートパッド電極PD2Gおよび電力増幅モジュールPA1を、それぞれ増幅回路AMP1a、増幅回路AMP2a、ドレインパッド電極PD2Da、ゲートパッド電極PD2Gaおよび電力増幅モジュールPA1aに読み替える。また、LDMOSFET形成領域22をLDMOSFET形成領域22bに読み替えた場合は、増幅回路AMP1、増幅回路AMP2、ドレインパッド電極PD2D、ゲートパッド電極PD2Gおよび電力増幅モジュールPA1を、それぞれ増幅回路AMP1b、増幅回路AMP2b、ドレインパッド電極PD2Db、ゲートパッド電極PD2Gbおよび電力増幅モジュールPA1aに読み替える。

【0118】

図11〜図13は、半導体チップCP1の要部平面図であり、半導体チップCP1において、上記LDMOSFET形成領域22(または上記LDMOSFET形成領域22aあるいは上記LDMOSFET形成領域22b)の平面図が示されている。図11〜図13は、互いに同じ領域の平面図が示されているが、図11には、活性領域AR1の平面レイアウトが示され、図12には、配線M1(すなわちソース配線M1S、ドレイン配線M1Dおよびゲート配線M1G)の平面レイアウトが示され、図13には、ゲート配線M1G、配線M2(すなわちソース配線M2S、ドレイン配線M2Dおよびゲート配線M2G)およびパッド電極51の平面レイアウトが示されている。なお、図11〜図13の平面位置を相互に比較しやすくするために、図11および図12では、ゲートパッド電極51G、ゲート配線M2G、ドレインパッド用開口部53Dおよびゲートパッド用開口部53Gを点線で示してある。また、図13では、ドレインパッド用開口部53Dおよびゲートパッド用開口部53Gを点線で示してある。なお、図13のA3−A3線の断面図が上記図9にほぼ対応し、図13のA4−A4線の断面図が上記図10にほぼ対応する。

【0119】

また、図14〜図17は、半導体チップCP1の要部平面図であり、図11の一点鎖線で囲まれた領域55の拡大図である。図14〜図17は、互いに同じ領域(すなわち図11の領域55)の平面図が示されているが、図14には活性領域AR1の平面レイアウトが示され、図15には、ゲート電極35、n+型ドレイン領域39、n+型ソース領域41およびp型打抜き層44の平面レイアウトが示されている。また、図16には、配線M1(すなわちソース配線M1S、ドレイン配線M1Dおよびゲート配線M1G)の平面レイアウトが示され、図17には、配線M2(すなわちソース配線M2S、ドレイン配線M2Dおよびゲート配線M2G)の平面レイアウトが示されている。なお、図14〜図17の平面位置を相互に比較しやすくするために、図14、図16および図17では、ゲート電極35を点線で示してある。また、図16では、配線M1(すなわちソース配線M1S、ドレイン配線M1Dおよびゲート配線M1G)の下に位置するコンタクトホール47の位置も図示し、図17では、配線M2(すなわちソース配線M2S、ドレイン配線M2Dおよびゲート配線M2G)の下に位置するスルーホール50の位置も図示している。

【0120】

また、図14〜図17は、平面図であるが、図面を見易くするために、図14においては、活性領域AR1にドットのハッチングを付し、図15においては、ゲート電極35にドットのハッチングを付してある。また、図16においては、配線M1(すなわちソース配線M1S、ドレイン配線M1Dおよびゲート配線M1G)にドットのハッチングを付し、図17においては、配線M2(すなわちソース配線M2S、ドレイン配線M2Dおよびゲート配線M2G)にドットのハッチングを付してある。また、図14のA1−A1線の断面図が上記図7にほぼ対応し、図17のA2−A2線の断面図が上記図8にほぼ対応する。

【0121】

また、図11〜図17の平面図に示されるY方向(第1方向)は、LDMOSFET形成領域22(あるいはLDMOSFET形成領域22aまたは22b)に形成されたLDMOSFETのゲート電極35、ドレイン領域(n−型ドリフト領域37、n型ドリフト領域38およびn+型ドレイン領域39)、およびソース領域(n−型ソース領域40およびn+型ソース領域41)の延在方向に対応する。図11〜図17の平面図に示されるX方向(第2方向)は、Y方向に交差(好ましくは直交)する方向であり、後述するLDMOSFET形成領域22の辺61a,61bに沿った方向である。X方向およびY方向に関しては、図11〜図17以外の平面図についても同様である。

【0122】

上記素子分離領域32によって、図11および図14に示されるような活性領域AR1が規定され、活性領域AR1は、周囲を上記素子分離領域32によって囲まれている。活性領域AR1にLDMOSFETのドレイン領域(n−型ドリフト領域37、n型ドリフト領域38およびn+型ドレイン領域39)およびソース領域(n−型ソース領域40およびn+型ソース領域41)が形成され、また、ゲート絶縁膜34を介してゲート電極35が形成されている。

【0123】

図15に示されるように、LDMOSFETのゲート電極35はY方向に延在している。そして、LDMOSFETのドレイン領域(n−型ドリフト領域37、n型ドリフト領域38およびn+型ドレイン領域39)は、活性領域AR1において、隣り合うゲート電極35の間の領域に形成されてY方向に延在している。また、LDMOSFETのソース領域(n−型ソース領域40およびn+型ソース領域41)は、活性領域AR1において、隣り合うゲート電極35の他の間の領域に形成されてY方向に延在している。また、p型打抜き層44は、隣り合うLDMOSFETのn+型ソース領域41の間の領域に形成されている。

【0124】

また、LDMOSFET形成領域22(活性領域AR1)では、図7および図15に示されるような単位セル(繰り返し単位、繰り返しピッチ、基本セル、単位領域、LDMOSFETの単位セル)60の構造(レイアウト)がX方向に繰り返されている。一つの単位セル60により2つの単位LDMOSFET(単位LDMOSFET素子、LDMOSFETセル、単位MISFET素子)60aが形成される。すなわち、繰り返しの単位は単位セル60であるが、各単位セル60は、n+型ドレイン領域39を共通にしてX方向に対称な構造の2つの単位LDMOSFET60aにより構成されている。なお、LDMOSFETは、MISFET素子であるため、単位LDMOSFET60aを単位MISFET素子とみなすこともできる。

【0125】

LDMOSFET形成領域22(またはLDMOSFET形成領域22a,22b)においては、単位セル60の構造(レイアウト)がX方向に繰り返されることで、多数(複数)の単位LDMOSFET60aが形成(配列)され、それら多数(複数)の単位LDMOSFET60aが並列に接続されている。すなわち、LDMOSFET形成領域22においては、単位LDMOSFET60aがX方向に繰り返し配列し、LDMOSFET形成領域22に配列したこれら複数の単位LDMOSFET60aが並列に接続されているのである。

【0126】

LDMOSFET形成領域22に形成されている複数の単位LDMOSFET60aを並列に接続するために、LDMOSFET形成領域22のそれら複数の単位LDMOSFET60aのゲート電極35同士は、プラグ48およびゲート配線M1G,M2Gを介して互いに電気的に接続され、ドレイン領域(n+型ドレイン領域39)同士は、プラグ48およびドレイン配線M1D,M2Dを介して互いに電気的に接続されている。また、LDMOSFET形成領域22に形成されている複数(多数)の単位LDMOSFET60aにおいて、ソース領域(n+型ソース領域41)同士は、プラグ48、ソース配線M1S,M2S、p+型半導体領域45、p型打抜き層44、半導体基板30およびソース裏面電極54を介して互いに電気的に接続されている。

【0127】

LDMOSFET形成領域22は、多段接続された複数の増幅回路AMP1,AMP2のうちの最終段の増幅回路AMP2を構成するMISFET素子が形成された領域に対応しており、LDMOSFET形成領域22に形成されている複数の単位LDMOSFET60aが並列に接続されて、増幅回路AMP2が構成されている。また、上記LDMOSFET形成領域21においても、LDMOSFET形成領域22と同様に単位セル60の構造(レイアウト)が繰り返されることで、多数(複数)の単位LDMOSFET60aが形成(配列)されており、上記LDMOSFET形成領域21に形成された複数(多数)の単位LDMOSFET60aが並列に接続されることで、上記増幅回路AMP1が構成されている。従って、各増幅回路AMP1,AMP2を構成するMISFET素子は、複数の単位LDMOSFET60aを並列に接続して構成されている。

【0128】

また、上述のように、活性領域AR1に形成されたLDMOSFETのドレイン領域(n+型ドレイン領域39)上にドレイン配線M1Dが形成され、n+型ドレイン領域39上に配置されたプラグ48を介して、ドレイン配線M1Dとその下方のLDMOSFETのドレイン領域(n+型ドレイン領域39)とが電気的に接続されている。活性領域AR1において、ドレイン領域はY方向に延在しているので、ドレイン配線M1Dも活性領域AR1上をY方向に延在しているが、活性領域AR1の間の素子分離領域32上にはドレイン配線M1Dは形成されていない。このため、ドレイン配線M1Dは、各活性領域AR1上にのみ形成された孤立パターンであるが、図7、図16および図17などに示されるように、ドレイン配線M1Dの上部をY方向に延在する最上層のドレイン配線M2Dと、ドレイン配線M2Dのビア部(スルーホール50を埋める部分)を介して電気的に接続されている。

【0129】

図11、図13および図17に示されるように、最上層のドレイン配線M2Dは、Y方向に配列する複数の活性領域AR1(ドレイン領域)にまたがってY方向に延在する配線部(第2ドレイン配線部)M2D1と、X方向に延在して複数の配線部M2D1の一方の端部同士を連結する連結配線部(第1ドレイン配線部)M2D2とを有している。これら複数の配線部M2D1と連結配線部M2D2とが一体的に形成されてドレイン配線M2Dが構成されている。従って、ドレイン配線M2Dは、いわゆる櫛歯状のパターンとなっている。各配線部M2D1は、LDMOSFET形成領域22に形成された複数の単位LDMOSFET60aの各ドレイン領域上に位置するようにY方向に延在し、かつドレイン配線M1Dおよびプラグ48を介して、複数の単位LDMOSFET60aの各ドレイン領域と電気的に接続されている。ドレイン配線M2Dの連結配線部M2D2において、配線部M2D1が接続されている側とは反対側には、少なくとも1つ、好ましくは複数のドレインパッド電極51Dが接続されている。半導体チップCP1において、複数の配線部M2D1と連結配線部M2D2とドレインパッド電極51Dとは、同層に一体的に形成されている。

【0130】

すなわち、LDMOSFET形成領域22において、上記各単位セル60のドレイン領域(n+型ドレイン領域39)を、プラグ48およびドレイン配線M1Dを介して、最上層のドレイン配線M2Dの配線部M2D1まで引き上げてから、ドレイン配線M2Dの連結配線部M2D2によって互いに電気的に接続させ、このドレイン配線M2Dと一体的にドレインパッド電極51Dを形成しているのである。

【0131】

また、上述のように、活性領域AR1に形成されたLDMOSFETのソース領域(n+型ソース領域41)に電気的に接続されたソース配線M1Sが、活性領域AR1のソース領域(n+型ソース領域41)およびp+型半導体領域45上に形成されている。活性領域AR1において、ソース領域はY方向に延在しているので、ソース配線M1Sも活性領域AR1上をY方向に延在しているが、活性領域AR1の間の素子分離領域32上にはソース配線M1Sは形成されていない。このため、ソース配線M1Sは、各活性領域AR1上にのみ形成された孤立パターンであるが、図7、図16および図17などに示されるように、ソース配線M1Sの上部をY方向に延在する最上層のソース配線M2Sと、ソース配線M2Sのビア部(スルーホール50を埋める部分)を介して電気的に接続されている。

【0132】

図11、図13および図17に示されるように、最上層のソース配線M2Sは、Y方向に配列する複数の活性領域6(ソース領域)にまたがってY方向に延在しているが、各ソース配線M2S同士は連結されていない。また、ソース配線M2Sには、パッド電極51は接続されていないが、これは、LDMOSFETのソースは、p型打抜き層44などを介して、半導体基板30の裏面のソース裏面電極54から引き出しているためである。

【0133】

図8および図14〜図17に示されるように、ゲート電極35はY方向に延在し、活性領域AR1の周囲または間の素子分離領32上に位置する部分で、コンタクトホール47に埋め込まれたプラグ48を介して、ゲート配線M1Gに電気的に接続されている。ゲート配線M1Gは、活性領域AR1の周囲および間の素子分離領域32上をX方向およびY方向に延在している。LDMOSFET形成領域22において、Y方向に延在する各ゲート電極35は、ゲート配線M1GのX方向に延在する部分とプラグ48を介して電気的に接続され、ゲート配線M1GのX方向に延在する部分とY方向に延在する部分とが一体的に連結されていることで、各ゲート電極35は、ゲート配線M1Gを介して互いに電気的に接続されている。

【0134】

ゲート配線M1Gはドレイン配線M1Dおよびソース配線M1Sと同層の配線であるが、図12および図16に示されるように活性領域AR1の間の素子分離領域32上にはドレイン配線M1Dおよびソース配線M1Sが形成されておらず、そこでゲート配線M1GがX方向に延在している。従って、ゲート配線M1GのX方向に延在する部分同士の間に、Y方向に延在するドレイン配線M1Dおよびソース配線M1Sが配置された状態となっている。

【0135】

図8、図12、図16および図17に示されるように、ゲート配線M1Gは、ドレイン配線M2Dの連結配線部M2D2と反対側(連結配線部M2D2から遠い側)に位置しかつX方向に延在する部分において、素子分離領域32上をX方向に延在するゲート配線M2Gと、ゲート配線M2Gのビア部(スルーホール50を埋める部分)を介して電気的に接続されている。すなわち、X方向に延在するゲート配線M2Gの少なくとも一部が、X方向に延在する部分のゲート配線M1Gと平面的に重なっており、その重なり領域において、ゲート配線M2Gのビア部(スルーホール50を埋める部分)を介して上層のゲート配線M2Gと下層のゲート配線M1Gとが電気的に接続されている。

【0136】

このように、活性領域AR1の周囲または間の素子分離領域32上で、上記各単位LDMOSFET60aのゲート電極35を、プラグ48を介してゲート配線M1Gまで引き上げ、このゲート配線M1Gを最上層のゲート配線M2Gに接続し、このゲート配線M2Gをゲートパッド電極51Gまで延在させている。

【0137】

<ゲート配線およびドレイン配線について>

図18は、半導体チップCP1の要部平面図であり、上記図11〜図13と同じ領域が示されている。但し、図18では、LDMOSFET形成領域22(またはLDMOSFET形成領域22aあるいはLDMOSFET形成領域22b)、ドレイン配線M2Dの連結配線部M2D2、ドレインパッド電極51D、ドレインパッド用開口部53D、ゲート配線M2G、ゲートパッド電極51Gおよびゲートパッド用開口部53Gのレイアウト(配置)を示し、他の構成要素の図示を省略したものである。従って、図13に示されていたソース配線M2Sと、ドレイン配線M2Dの配線部M2D1と、ゲート配線M1Gとは、図18では図示を省略してある。なお、図18は、平面図であるが、図面を見やすくするために、LDMOSFET形成領域22(またはLDMOSFET形成領域22aあるいはLDMOSFET形成領域22b)と、ゲートパッド電極51Gおよびそれにつながるゲート配線M2Gと、ドレインパッド電極51Dおよびそれにつながるドレイン配線M2Dの連結配線部M2D2とを、ハッチングを付して示してある。また、図18では、ゲートパッド用開口部53Gおよびドレインパッド用開口部53Dを点線で示してある。

【0138】

上記図13や図18に示されるように、ゲート配線M2Gは、LDMOSFET形成領域22の辺(第1の辺)61aに沿ってX方向に延在する連結配線部(第1ゲート配線部)M2G1と、連結配線部M2G1とゲートパッド電極51Gとの間をつなぐ配線部(第2ゲート配線部)M2G2とを有している。すなわち、連結配線部M2G1は、連結配線部M2G1と同層の配線部M2G2を介して、連結配線部M2G1および配線部M2G2と同層のゲートパッド電極51Gに接続されている。連結配線部M2G1と配線部M2G2とゲートパッド電極51Gとは、半導体チップCP1において同層に一体的に形成されている。連結配線部M2G1は、上述のように、連結配線部M2G1のビア部(スルーホール50を埋める部分)を介してゲート配線M1Gに電気的に接続され、更にプラグ48を介して、LDMOSFET形成領域22に形成されている複数の単位LDMOSFET60aの各ゲート電極35に電気的に接続されている。このため、連結配線部M2G1は、LDMOSFET形成領域22に形成されている複数の単位LDMOSFET60aの各ゲート電極35を束ねるシャント配線とみなすこともできる。

【0139】

また、上記図13や図18に示されるように、ドレイン配線M2Dは、LDMOSFET形成領域22の辺(第2の辺)61bに沿ってX方向に延在する連結配線部(第1度レイン配線部)M2D2を有しており、この連結配線部M2D2には少なくとも1つ、好ましくは複数のドレインパッド電極51Dが接続され、半導体チップCP1において連結配線部M2D2とドレインパッド電極51Dとは同層に一体的に形成されている。連結配線部M2D2は、上述のように、配線部M2D1、ドレイン配線M1Dおよびプラグ48を介して、LDMOSFET形成領域22に形成されている複数の単位LDMOSFET60aの各ドレイン領域(n+型ドレイン領域39)に電気的に接続されている。

【0140】

なお、LDMOSFET形成領域22の辺61a,61bは、LDMOSFET形成領域22に形成された複数の単位LDMOSFET60aの各ゲート電極35の延在方向であるY方向と交差(好ましくは直交)する辺であり、また、辺61aと辺61bとは互いに対向する辺である。また、X方向(第2方向)は、LDMOSFET形成領域22の辺61a,61bに沿った方向(すなわち辺61a,61bに平行な方向)である。

【0141】

ここで、LDMOSFET形成領域22は、上記単位セル60がX方向に繰り返し配列した領域であり、多段接続された複数の増幅回路AMP1,AMP2のうちの最終段の増幅回路AMP2を構成するために並列に接続された複数の単位LDMOSFET60aが形成されている領域に相当する。このため、LDMOSFET形成領域22の範囲は、増幅回路AMP2を構成するために並列に接続される複数の単位LDMOSFET60a(単位セル60)を形成するための一群のソース領域、ドレイン領域およびゲート電極35が形成されている領域にほぼ対応する。このソース領域およびドレイン領域は活性領域AR1に形成されるので、上記図11に示されるように、LDMOSFET形成領域22の範囲は、増幅回路AMP2を構成するために並列に接続される複数の単位LDMOSFET60a(単位セル60)が形成される一群の活性領域AR1が形成されている領域とみなすこともできる。

【0142】

図19は、上記比較例の半導体チップCP102の要部平面図であり、本実施の形態の図18に対応するものである。なお、図19に示されるLDMOSFET形成領域122は、上記比較例の半導体チップCP102において増幅回路AMP2を構成するLDMOSFETが形成された領域であり、本実施の形態のLDMOSFET形成領域22に相当する領域である。

【0143】

上記図4に示される比較例の半導体チップCP102は、上記比較例の電力増幅モジュールPA101に使用され、半導体チップCP102においては、ゲート用のパッド電極PD102Gとドレイン用のパッド電極PD102Dとを、半導体チップCP102主面(上面)の対向する辺にそれぞれ配置している。このため、図19に示されるように、LDMOSFET形成領域122を挟んで、ドレインパッド電極PD102Dとゲートパッド電極PD102Gとを互いに反対側に位置させることができる。従って、本実施の形態におけるゲート配線M2Gの連結配線部M2G1に相当するゲート配線M102Gに、図19のように、直接、ゲート用のパッド電極PD102Gを連結させることができるため、LDMOSFET形成領域122の中央に近い位置にゲート用のパッド電極PD102Gを配置させることができる。

【0144】

図20は、ゲートパッド電極51Gとドレインパッド電極51Dとを半導体チップCP1の同じ辺に配置した場合の半導体チップの要部平面図であり、上記図18や図19に対応するものであるが、図20では、ゲート配線M2Gの連結配線部M2G1の幅W0を、上記図19のゲート配線M102Gの幅と同程度にしている。

【0145】

本実施の形態では、複数段の増幅回路AMP1,AMP2を1つの半導体チップCP1内に内蔵させている。半導体チップCP1外の整合回路との接続しやすさを考慮すると、半導体チップCP1内に設けた複数段の増幅回路AMP1,AMP2のうち、特に最終段の増幅回路AMP2に接続されたゲートパッド電極51G(上記ゲートパッド電極PD2Gに対応)とドレインパッド電極51D(上記ドレインパッド電極PD2Dに対応)とを、半導体チップCP1の主面(上面)の同じ辺に沿って配置することが望ましい。このため、図18または図20のように、ゲートパッド電極51Gとドレインパッド電極51Dとを、LDMOSFET形成領域22の同じ辺61b側に並べて配置する必要がある。図18および図20では、ゲートパッド電極51Gと複数のドレインパッド電極51Dとが一列に並んで配置されている。従って、LDMOSFET形成領域22の辺61aに沿ってX方向に延在する連結配線部M2G1に、ゲートパッド電極51Gを直接連結させることはできず、図18または図20のように、ドレインパッド電極51Dと同じ列に並んだゲートパッド電極51Gまで、連結配線部M2G1を配線部M2G2で引き回すことになる。

【0146】

このため、本実施の形態の半導体チップCP1では、LDMOSFET形成領域22内の各ゲート電極35からゲートパッド電極51Gまでの配線距離(ゲートパッド電極51Gに到達するまでに経由する配線の距離)が、ゲート電極35毎にかなり差ができてしまう。例えば、図18および図20に示されるLDMOSFET形成領域22の辺61cに最も近いゲート電極35が、ゲートパッド電極51Gまでの配線距離が短く、LDMOSFET形成領域22の辺61dに最も近いゲート電極35が、ゲートパッド電極51Gまでの配線距離が長くなるが、両者の配線距離の差は、LDMOSFET形成領域22のX方向の長さ(寸法)L1にほぼ相当する値となる。ゲート電極35同士でのゲートパッド電極51Gまでの配線距離の差が大きくなると、ゲート電極35同士での位相差が大きくなるため、ドレインパッド電極51D(ドレインパッド電極PD2D)からの出力の電力合成ロスが増え、最終段の電力増幅回路AMP2での電力損失が高くなり、電力増幅モジュールPA1の効率を低下させる可能性があることが、本発明者の検討により分かった。複数の増幅回路を多段接続している場合、電力増幅モジュールの効率向上の観点からは、最終段の増幅回路での電力損失を少なくすることが最も重要である。

【0147】

なお、このようなゲート電極同士での位相差に起因した電力合成ロスの課題は、上記図4に示される比較例の電力増幅モジュールPA101のように、増幅回路AMP1を内蔵した半導体チップCP101と増幅回路AMP2を内蔵した半導体チップCP102とを別個に用意して配線基板111の上面111a上に搭載した場合には、見出すことができなかった課題である。

【0148】

すなわち、上記比較例の電力増幅モジュールPA101のように、増幅回路AMP1,AMP2毎に別個の半導体チップを用いた場合、各半導体チップには増幅回路は1つしか形成されていないため、上記図4のように、各半導体チップの主面において、ゲートパッド電極とドレインパッド電極とを、対向する辺にそれぞれ配置することができる。換言すれば、各半導体チップの主面において、対向する辺にゲートパッド電極とドレインパッド電極とをそれぞれ配置しても、各半導体チップには増幅回路は1つしかなく、ゲートパッド電極およびドレインパッド電極も一組しか配置されないため、半導体チップ外の各整合回路と半導体チップの各パッド電極との接続が容易である。このため、上記比較例の電力増幅モジュールPA101のように、増幅回路AMP1,AMP2毎に別個の半導体チップCP101,CP102を用いた場合には、ゲートパッド電極(PD102G)とドレインパッド電極(PD102D)とを上記図19のような配置にすることができるため、ゲート電極同士での位相差は小さくて済み、ゲート電極同士での位相差に起因した電力合成ロスの課題は、見出されていなかった。

【0149】

一方、本実施の形態では、複数の増幅回路AMP1,AMP2を1つの半導体チップCP1に内蔵させており、半導体チップCP1において増幅回路AMP1,AMP2毎にゲート用パッド電極およびドレイン用パッド電極を設ける必要がある。このため、半導体チップCP1における各増幅回路AMP1,AMP2およびそれに接続されたゲートパッド電極およびドレインパッド電極のレイアウトを工夫しないと、半導体チップCP1の各パッド電極を半導体チップCP1外の整合回路AJC1,AJC2,AJC3に接続しづらくなる。同じ増幅回路に接続されたゲートパッド電極とドレインパッド電極とを半導体チップCP1の主面の同じ辺に配置できれば、半導体チップCP1の各パッド電極PDと半導体チップCP1外の整合回路AJC1,AJC2,AJC3とが接続しやすくなり、配線基板11の上面11aでの各部品の配置効率を高め、また配線基板11における配線の引き回しのしやすさを高めることができるようになる。

【0150】

また、パッド電極を半導体チップの主面の中央部付近に配置すると、そのパッド電極に対してはワイヤボンディングを行い難くなる。本実施の形態のように、複数の増幅回路AMP1,AMP2と制御回路CTC1とを1つの半導体チップCP1に内蔵させた場合には、ワイヤボンディングを容易にするために、半導体チップCP1の主面の中央部付近にパッド電極PDが配置されるのを避けようとすると、上記図5や上記図6のように、同じ増幅回路に接続されたゲートパッド電極とドレインパッド電極とを半導体チップCP1の主面の同じ辺に配置する必要が生じる。

【0151】

しかしながら、同じ増幅回路に接続されたゲートパッド電極とドレインパッド電極とを半導体チップの主面の同じ辺に配置することを本発明者が検討した結果、上述のようなゲート電極同士での位相差に起因した電力合成ロスの課題を見出したのである。従って、ゲート電極同士での位相差に起因した電力合成ロスの課題は、上記図4に示される比較例の電力増幅モジュールPA101の構造では見出すことができず、半導体チップ内に複数の増幅回路を内蔵させて同じ増幅回路に接続されたゲートパッド電極とドレインパッド電極とを半導体チップの主面の同じ辺に配置することを本発明者が検討した結果、見出すことができた課題であると言うことができる。

【0152】

そこで、本実施の形態では、図20のようにゲート配線M2Gの連結配線部M2G1の幅W0を細くするのではなく、図18のようにゲート配線M2Gの連結配線部M2G1の幅W1を太くし、図18に示されるゲート配線M2Gの連結配線部M2G1の幅W1を、LDMOSFET形成領域22のX方向の長さ(寸法)L1の1/10以上にしている(すなわちW1≧L1/10)。換言すれば、LDMOSFET形成領域22のX方向の長さL1をゲート配線M2Gの連結配線部M2G1の幅W1で割った(除した)値L1/W1を10以下としている(すなわちL1/W1≦10)。例えば、LDMOSFET形成領域22のX方向の長さL1が500μmの場合は、ゲート配線M2Gの連結配線部M2G1の幅W1を50μm以上とするのである。なお、ゲート配線M2Gの連結配線部M2G1の幅W1は、ゲート配線M2Gの連結配線部M2G1のY方向の寸法(幅)である。また、LDMOSFET形成領域22の長さL1は、LDMOSFET形成領域22のX方向の寸法(長さ)である。

【0153】

なお、LDMOSFET形成領域22の各辺61a,61bの長さは、LDMOSFET形成領域22の長さL1と同じである。従って、LDMOSFET形成領域22の長さL1は、LDMOSFET形成領域22の辺61aの長さとみなすこともでき、また、LDMOSFET形成領域22の辺61bの長さとみなすこともできる。

【0154】

図21は、シミュレーションに用いた等価回路図である。図21の等価回路図(回路図)では、LDMOSFET形成領域22に形成されたLDMOSFETは、並列に接続したトランジスタ71で表し、ゲート配線M2Gの連結配線部M2G1は、位相ずれを考慮して抵抗72とインダクタ(寄生インダクタンス成分)73の直列回路で表し、ゲート配線M2Gの配線部M2G2は、位相ずれを考慮する必要がないので抵抗74で表している。

【0155】

図22は、ゲート配線M2Gの連結配線部M2G1の幅W1を変えたときの、電力増幅モジュールPA1の効率の向上量を示すグラフである。図22の横軸は、LDMOSFET形成領域22のX方向の長さL1をゲート配線M2Gの連結配線部M2G1の幅W1で割った(除した)値L1/W1に対応する。図22の縦軸は、電力増幅モジュールPA1の効率の向上量に対応するが、例えば、縦軸の効率向上量が2%の場合は、電力増幅モジュールPA1の効率(電力効率)がα%から(α+2)%に向上したことに対応する。図22のグラフには、図21の等価回路を用いたシミュレーションによって得られた結果を点線(図22の「Sim(全体)」に対応)で示し、また、実際に測定して得られた結果(実測値)を実線(図22の「実測(全体)」に対応)で示してある。なお、シミュレーションによる結果のうち、インダクタ成分(インダクタ73)による寄与分を一点鎖線(図22の「Sim(L分)」に対応)で示し、抵抗成分(抵抗72)による寄与分を二点鎖線(図22の「Sim(R分)」に対応)で示してある。

【0156】

図21の結果から、シミュレーションは、実測値をよく反映しており、連結配線部M2G1のインダクタ成分による寄与が抵抗成分による寄与よりも支配的であることから、効率の変化は位相ずれが主原因であることが分かる。

【0157】

ゲート配線M2Gの連結配線部M2G1の幅W1を太くして、L1/W1を10以下(すなわちW1≧L1/10)とすることにより、ゲート配線M2Gの連結配線部M2G1の寄生インダクタンスを抑制し、寄生インダクタンス起因の位相ずれを低減することができる。すなわち、LDMOSFET形成領域22に形成されたゲート電極35同士での位相差を低減することができる。これにより、ドレインパッド電極51D(ドレインパッド電極PD2D)からの出力の電力合成ロスを抑制できるので、図22に示されるように、最終段の電力増幅回路AMP2での電力損失を抑制し、電力増幅モジュールPA1の効率(電力効率)を向上させる(例えば2%以上向上させる)ことができる。

【0158】

このように、本実施の形態では、ゲート配線M2Gの連結配線部M2G1の幅W1を、LDMOSFET形成領域22のX方向の長さL1(すなわちLDMOSFET形成領域22の辺61aの長さ)の1/10以上(すなわちW1≧L1/10)とすることで、半導体チップCP1に設けた電力増幅回路AMP2での電力損失を抑制でき、半導体チップCP1を用いた電力増幅モジュールPA1の効率を向上させることができる。

【0159】

また、本実施の形態では、ゲート配線M2Gの連結配線部M2G1の幅W1を、LDMOSFET形成領域22のX方向の長さL1(すなわちLDMOSFET形成領域22の辺61aの長さ)の1/10以上で、かつ1/5以下(すなわちL1/5≧W1≧L1/10)とすることが好ましい。ゲート配線M2Gの連結配線部M2G1の幅W1を太くしすぎると、半導体チップCP1に占める連結配線部M2G1の面積が大きくなるため、半導体チップCP1の大面積化を招き、それによって、電力増幅モジュールPA1の大型化(大面積化)やコストの増大を招く可能性がある。それに対して、ゲート配線M2Gの連結配線部M2G1の幅W1を、LDMOSFET形成領域22のX方向の長さL1の1/5以下(すなわちW1≦L1/5)とすることで、半導体チップCP1に占める連結配線部M2G1の面積を抑制して、半導体チップCP1の大面積化を防止できる。このため、電力増幅モジュールPA1の効率を向上させながら、電力増幅モジュールPA1の小型化(小面積化)やコストの低減を図ることができる。

【0160】

また、ゲート配線M2Gの連結配線部M2G1の幅W1は、ゲートパッド電極51GのY方向の寸法(幅、長さ)L2以下(すなわちW1≦L2)であることが好ましい。なお、ゲートパッド電極51GのY方向の寸法L2は、図18に図示されている。ゲート配線M2Gの連結配線部M2G1の幅W1を、ゲートパッド電極51GのY方向の寸法L2よりも大きくした場合、LDMOSFET形成領域22、ゲート配線M2G、ゲートパッド電極51G、ドレイン配線M2Dおよびドレインパッド電極51Dを配置するのに要した平面領域のY方向の寸法が、図19の比較例の場合に比べて、大きくなってしまう。

【0161】

それに対して、ゲート配線M2Gの連結配線部M2G1の幅W1を、ゲートパッド電極51GのY方向の寸法L2以下(すなわちW1≦L2)とすることで、LDMOSFET形成領域22、ゲート配線M2G、ゲートパッド電極51G、ドレイン配線M2Dおよびドレインパッド電極51Dを配置するのに要した平面領域のY方向の寸法を、図19の比較例の場合に比べて小さくすることができる。これにより、半導体チップCP1の面積縮小(Y方向の寸法縮小)を図ることができる。

【0162】

また、他の形態として、第1層配線である配線M1と第2層配線である配線M2との間に、更に配線層を追加することもできる。この場合、LDMOSFET形成領域22(およびその近傍)においては、第1層配線(配線M1)と第2層配線(配線M2)との間に追加した配線層として、ドレイン配線M1D、ソース配線M1Sおよびゲート配線M1Gとそれぞれ同様のパターン(レイアウト)を有するドレイン配線、ソース配線およびゲート配線を、例えばアルミニウム配線などにより形成することができる。この場合、ドレイン配線M1Dは、ドレイン配線M1Dとドレイン配線M2Dとの間の層に配置されかつドレイン配線M1Dと同様のパターン(レイアウト)を有するドレイン配線(追加した配線層のドレイン配線)を介して、ドレイン配線M2Dと電気的に接続されることになる。また、ソース配線M1Sは、ソース配線M1Sとソース配線M2Sとの間の層に配置されかつソース配線M1Sと同様のパターン(レイアウト)を有するソース配線(追加した配線層のソース配線)を介して、ソース配線M2Sと電気的に接続されることになる。また、ゲート配線M1Gは、ゲート配線M1Gとゲート配線M2Gとの間の層に配置されかつゲート配線M1Gと同様のパターン(レイアウト)を有するゲート配線(追加した配線層のゲート配線)を介して、ゲート配線M2Gと電気的に接続されることになる。

【0163】

また、本実施の形態1および以下の実施の形態2〜4は、上記図6に示されるような、2系統の電力増幅回路を有する電力増幅モジュールPA1aに適用すれば、その効果が極めて大きい。その理由は、以下の通りである。

【0164】

すなわち、2系統の電力増幅回路を有する電力増幅モジュールPA1aでは、2系統の増幅回路、ここではGSM900用の増幅回路AMP1a,AMP2aと、DCS1800用の複数の増幅回路AMP1b,AMP2bと、これら増幅回路の制御や補佐などを行う制御回路CTC1とを1つの半導体チップCP1に内蔵させている。この場合、半導体チップCP1内の各回路間を配線で接続しやすくするには、上記図6に示されるように、半導体チップCP1において、GSM900用の増幅回路AMP1a,AMP2a(LDMOSFET形成領域21a,22a)とDCS1800用の増幅回路AMP1b,AMP2b(LDMOSFET形成領域21b,22b)との間(中央)に制御回路CTC1(制御回路領域23)を配置することが好ましい。しかしながら、半導体チップCP1において、そのような位置に制御回路CTC1(制御回路領域23)を配置すると、同じ増幅回路に接続されたゲートパッド電極とドレインパッド電極とを、上記図4や図19のような配置にすることが、ますます困難になる。これは、パッド電極PDにワイヤボンディングする際のダメージを考慮して、アクティブ素子上にはパッド電極PDを配置しないため、上記図6のように、制御回路領域23を避けてパッド電極PDを配置する必要があるからである。

【0165】

このため、電力増幅モジュールPA1aのように電力増幅回路を1系統ではなく2系統にすると、これに使用する半導体チップCP1において、同じ増幅回路に接続されたゲートパッド電極とドレインパッド電極とを、上記図18(または後述の図23〜図25)のような配置にする必要性が、ますます大きくなる。従って、2系統の電力増幅回路を有する電力増幅モジュールPA1aでは、上述のゲート電極同士での位相差に起因した電力合成ロスの課題を解決できる本実施の形態1および以下の実施の形態2〜4を適用する効果は、極めて大きい。

【0166】

(実施の形態2)

図23は、半導体チップCP1の要部平面図であり、上記図18に対応するものである。上記実施の形態1では、ゲート配線M2Gにおいて配線部M2G2の幅W2を連結配線部M2G1の幅W1よりも小さく(すなわちW2<W1)していたが、本実施の形態では、ゲート配線M2Gにおいて配線部M2G2の幅W2を連結配線部M2G1の幅W1とほぼ同じにしている(すなわちW2=W1)。なお、配線部M2G2の幅W2は、配線部M2G2において、配線部M2G2が延在する方向に直交する方向の寸法(幅)に対応する。本実施の形態の他の構成は、上記実施の形態1と同様であるので、ここではその説明は省略する。

【0167】

上記実施の形態1では、ゲート配線M2Gにおいて配線部M2G2の幅W2を連結配線部M2G1の幅W1よりも小さく(すなわちW2<W1)したことにより、ゲートパッド電極51Gとゲート配線M2Gの連結配線部M2G1との間をつなぐ配線部M2G2が占める面積を小さくすることができるため、半導体チップCP1の小面積化に有利である。

【0168】

一方、本実施の形態では、ゲート配線M2Gにおいて配線部M2G2の幅W2を連結配線部M2G1の幅W1と同じ(すなわちW2=W1)にしたことにより、配線部M2G2の抵抗を低減できるため、配線部M2G2の抵抗成分によるゲートパッド電極51G(上記ゲートパッド電極PD2Gに対応)からの入力電力の低下を抑制することができる。このため、半導体チップCP1に設けた電力増幅回路AMP2での効率(電力効率)を更に向上させることができ、半導体チップCP1を用いた電力増幅モジュールPA1の効率(電力効率)を更に向上させることができる。

【0169】

(実施の形態3)

図24は、半導体チップCP1の要部平面図であり、上記図18や図23に対応するものである。本実施の形態では、ゲート配線M2Gの連結配線部M2G1の幅W1だけではなく、ドレイン配線M2Dの連結配線部M2D2の幅W3も、LDMOSFET形成領域22のX方向の長さL1の1/10以上としている(すなわちW1,W3≧L1/10)。本実施の形態の他の構成は、上記実施の形態2と同様であるので、ここではその説明は省略する。なお、ドレイン配線M2Dの連結配線部M2D2の幅W3は、ドレイン配線M2Dの連結配線部M2D2のY方向の寸法(幅)であり、図24に示されるように、ドレインパッド電極51Dが連結されていない領域における連結配線部M2D2のY方向の寸法(幅)に対応する。

【0170】

ゲート配線M2Gの連結配線部M2G1は、配線部M2G2を経由してゲートパッド電極51Gに接続しなければならないのに対して、ドレイン配線M2Dの連結配線部M2D2には、直接ドレインパッド電極51Dを接続することができるため、寄生インダクタンスに起因した位相ずれは、ドレイン配線M2Dよりもゲート配線M2Gで生じやすい。従って、半導体チップCP1(の電力増幅回路AMP2)およびそれを用いた電力増幅モジュールPA1の効率(電力効率)を向上させるためには、上記実施の形態1,2のようにゲート配線M2Gの連結配線部M2G1の幅W1を太くすることが、極めて有効である。

【0171】

しかしながら、半導体チップCP1(の電力増幅回路AMP2)およびそれを用いた電力増幅モジュールPA1の効率(電力効率)を更に向上させるためには、ゲート配線M2Gだけでなく、レイン配線M2Dでも寄生インダクタンスに起因した位相ずれをできるだけ低減させることが望ましい。

【0172】

そこで、本実施の形態では、ドレイン配線M2Dの連結配線部M2D2の幅W3を太くして、ドレイン配線M2Dの連結配線部M2D2の幅W3を、LDMOSFET形成領域22のX方向の長さL1(すなわちLDMOSFET形成領域22の辺61bの長さ)の1/10以上としている(すなわちW3≧L1/10)。これにより、ゲート配線M2Gの連結配線部M2G1だけでなく、ドレイン配線M2Dの連結配線部M2D2においても寄生インダクタンスを抑制でき、寄生インダクタンス起因の位相ずれを低減することができる。このため、ドレインパッド電極51D(ドレインパッド電極PD2D)からの出力の電力合成ロスを更に抑制することができるので、半導体チップCP1に設けた電力増幅回路AMP2での電力損失を更に抑制でき、半導体チップCP1を用いた電力増幅モジュールPA1の効率(電力効率)を更に向上させることができる。

【0173】

また、ドレイン配線M2Dの連結配線部M2D2の幅W3を、連結配線部M2D2の端部81(LDMOSFET形成領域22から遠い側の端部81)がドレインパッド電極51Dの端部82(LDMOSFET形成領域22から遠い側の端部82)を越えてしまうような太さにすると、連結配線部M2D2およびドレインパッド電極51Dを配置するのに要する平面領域のY方向の寸法を増大させてしまう。このため、ドレイン配線M2Dの連結配線部M2D2の幅W3は、ドレインパッド電極51DのY方向の寸法以下であることが好ましい。これにより、連結配線部M2D2の端部81がドレインパッド電極51Dの端部82を越えることがなくなり、半導体チップCP1の面積縮小(Y方向の寸法縮小)を図ることができる。このことは、以下の実施の形態4でも同様である。

【0174】

(実施の形態4)

図25は、半導体チップCP1の要部平面図であり、上記図18、図23および図24に対応するものである。

【0175】

本実施の形態では、ドレイン配線M2Dおよびドレインパッド電極51Dについては、上記実施の形態3と同様である。このため、本実施の形態でも、上記実施の形態3と同様に、ドレイン配線M2Dの連結配線部M2D2の幅W3を、LDMOSFET形成領域22のX方向の長さL1の1/10以上としている(すなわちW3≧L1/10)。

【0176】

しかしながら、本実施の形態では、上記実施の形態1〜3に比べて、ゲート配線M2Gの連結配線部M2G1の幅W1を細くし、ゲート配線M2Gの連結配線部M2G1の幅W1をLDMOSFET形成領域22のX方向の長さL1の1/10未満としている(すなわちW1<L1/10)。ゲート配線M2Gの配線部M2G2の幅W2は連結配線部M2G1の幅W1とほぼ同程度である(すなわちW2=W1)。本実施の形態の他の構成は、上記実施の形態1と同様であるので、ここではその説明は省略する。

【0177】

本実施の形態では、上記実施の形態1とは異なり、ゲート配線M2Gの連結配線部M2G1の幅W1をLDMOSFET形成領域22のX方向の長さL1の1/10未満(すなわちW1<L1/10)としているため、ゲート配線M2Gの連結配線部M2G1での寄生インダクタンスを抑制することはできない。しかしながら、本実施の形態では、上記実施の形態3と同様に、ドレイン配線M2Dの連結配線部M2D2の幅W3を太くして、ドレイン配線M2Dの連結配線部M2D2の幅W3を、LDMOSFET形成領域22のX方向の長さL1(すなわちLDMOSFET形成領域22の辺61bの長さ)の1/10以上としている(すなわちW3≧L1/10)。これにより、ドレイン配線M2Dの連結配線部M2D2の幅W3が細い場合に比べて、ドレイン配線M2Dの連結配線部M2D2における寄生インダクタンスを抑制でき、寄生インダクタンス起因の位相ずれを低減することができる。このため、ドレイン配線M2Dの連結配線部M2D2における寄生インダクタンスに起因した位相ずれによるドレインパッド電極51D(ドレインパッド電極PD2D)からの出力電力合成ロスを抑制することができる。従って、半導体チップCP1に設けた電力増幅回路AMP2での電力損失を抑制でき、半導体チップCP1を用いた電力増幅モジュールPA1の効率(電力効率)を向上させることができる。

【0178】

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0179】

本発明は、半導体装置に適用して有効である。

【符号の説明】

【0180】

11 配線基板

11a 上面

11b 下面

12 受動部品

13 封止樹脂

14 絶縁体層

15a 基板側端子

15b 外部接続用端子

15c 基準電位供給用端子

15d 配線パターン

16,16a ビアホール

17 導体層

18 半田

21,21a,21b,22,22a,22b LDMOSFET形成領域

23 制御回路領域

30 半導体基板

31 エピタキシャル層

32 素子分離領域

33 p型ウエル

34 ゲート絶縁膜

35 ゲート電極

36 サイドウォールスペーサ

37 n−型ドリフト領域

38 n型ドリフト領域

39 n+型ドレイン領域

40 n−型ソース領域

41 n+型ソース領域

44 p型打抜き層

45 p+型半導体領域

46 絶縁膜

47 コンタクトホール

48 プラグ

49 絶縁膜

50 スルーホール

51 パッド電極

51D ドレインパッド電極

51G ゲートパッド電極

52 絶縁膜

53 開口部

53D ドレインパッド用開口部

53G ゲートパッド用開口部

54 ソース裏面電極

55 領域

60 単位セル

60a 単位LDMOSFET

61a,61b,61c,61d 辺

71 トランジスタ

72 抵抗

73 インダクタ

74 抵抗

81,82 端部

111 配線基板

111a 上面

112 受動部品

115a 基板側端子

115b 外部接続用端子

115d 配線パターン

AGCAMP AGCアンプ

AJC1,AJC2,AJC3 整合回路

AJC1a,AJC1b,AJC2a,AJC2b,AJC3a,AJC3b 整合回路

AMP1,AMP1a,AMP1b,AMP2,AMP2a,AMP2b 増幅回路

ANT アンテナ

ANT−SW アンテナスイッチ

AR1 活性領域

BBP ベースバンド部

BE1 裏面電極

CDP 表示・制御部

COD1 音声CODEC

COD2 チャネルCODEC

CP1,CP1b 半導体チップ

CP101,CP102 半導体チップ

CTC1 制御回路

DAC D/A変換回路

DMDL 復調回路

DPS デジタル携帯電話機

FPL1 RF−PLL(RF周波数位相同期回路)

FPL2 IF−PLL(IF周波数位相同期回路)

IFC IF回路

IPT1,IPT1a,IPT1b 入力端子

L1 長さ

LCD 液晶表示部

LNA 低雑音アンプ

M1 配線

M1S ソース配線

M1D ドレイン配線

M1G ゲート配線

M2 配線

M2G ゲート配線

M2G1 連結配線部

M2G2 配線部

M2D ドレイン配線

M2D1 配線部

M2D2 連結配線部

M2S ソース配線

M102G ゲート配線

MCN マイコン

MDL 変調回路

MIC マイク

MRY メモリ

OPT1,OPT1a,OPT1b 出力端子

PA1,PA1a 電力増幅モジュール

PA101 電力増幅モジュール

PD パッド電極

PD1D,PD2D ドレインパッド電極

PD1Da,PD1Db,PD2Da,PD2Db ドレインパッド電極

PD1G,PD2G ゲートパッド電極、

PD1Ga,PD1Gb,PD2Ga,PD2Gb ゲートパッド電極

PD3,PD4 電源入力用パッド電極

PD101G,PD101D,PD102G,PD102D パッド電極

QMD 直交変調器

RFBP RFブロック部

RX−MIX 受信ミクサ

SP スピーカ

TX−MIX 送信ミクサ

VDD1,VDD2 電源電圧

W0,W1,W2,W3 幅

WA,WA101 ワイヤ

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、移動体通信装置に搭載される電力増幅モジュールなどに使用される半導体装置に適用して有効な技術に関する。

【背景技術】

【0002】

近年、GSM方式、PCS方式、PDC方式、CDMA方式といった通信方式に代表される移動体通信装置(いわゆる携帯電話)が世界的に普及している。

【0003】

一般に、この種の移動体通信装置は、電波の放射と受信をするアンテナ、電力変調された高周波信号を増幅してアンテナへ供給する高周波電力増幅器(RFパワーモジュール)、アンテナで受信した高周波信号を信号処理する受信部、これらの制御を行う制御部、そしてこれらに電源電圧を供給する電池(バッテリー)で構成される。

【0004】

特開2001−94094号公報(特許文献1)には、3つの半導体チップを配線基板上に搭載した高周波電力増幅器に関する技術が記載されている。

【0005】

国際公開05/015636号公報(特許文献2)には、配線基板上に搭載する半導体チップを1つのみとしたRFパワーモジュールに関する技術が記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2001−94094号公報

【特許文献2】国際公開05/015636号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明者の検討によれば、次のことが分かった。

【0008】

RFパワーモジュールは、配線基板上に半導体チップおよび受動部品を搭載し、これらを樹脂封止することで形成することができる。RFパワーモジュールに形成されている電力増幅回路は、複数の増幅回路を多段接続した多段構成を有しているが、複数の増幅回路をそれぞれ異なる半導体チップに形成した場合、配線基板上に搭載する半導体チップの数が多くなってしまうため、RFパワーモジュールの大型化(大面積化)やコストの上昇を招いてしまう。一方、複数の増幅回路を同じ半導体チップに形成した場合、配線基板上に搭載する半導体チップの数が少なくてすむため、RFパワーモジュールの小型化(小面積化)やコストの低減を図ることができる。

【0009】

複数の増幅回路を同じ半導体チップに形成した場合、各増幅回路の入力用のゲートパッド電極と出力用のドレインパッド電極とを半導体チップに設ける必要が生じ、半導体チップにおけるパッド電極の種類や数が多くなるが、これらのパッド電極を、配線基板上に搭載した受動部品などで構成される段間整合回路などに接続しやすくするためには、半導体チップにおける各パッド電極の配置を工夫する必要がある。例えば、増幅回路の入力用のゲートパッド電極と出力用のドレインパッド電極とを、半導体チップの主面の同じ辺に沿って並んで配置させれば、半導体チップ内の増幅回路と配線基板上に搭載した受動部品などで構成される段間整合回路とを接続しやすくなる。

【0010】

しかしながら、半導体チップにおいて、ある増幅回路を形成した領域から、その増幅回路のゲートに電気的に接続されたゲートパッド電極を離して配置させた場合、その増幅回路のゲートとゲートパッド電極とをつなぐゲート配線が長距離配線となる。各増幅回路は、並んで形成された複数の単位MISFETを並列接続することで形成されているが、増幅回路を形成した領域からゲートパッド電極を離して配置させた場合、ゲート配線の寄生インダクタンス成分に起因して、増幅回路を構成する複数の単位MISFETの各ゲート電極での位相差が大きくなってしまう。このため、増幅回路のドレインに電気的に接続されたドレインパッド電極からの出力の電力合成ロスが増え、増幅回路での電力損失が高くなり、RFパワーモジュールの効率を低下させる可能性があることが、本発明者の検討により分かった。これは、RFパワーモジュールの性能を低下させてしまう。

【0011】

本発明の目的は、半導体装置の性能を向上させることができる技術を提供することにある。

【0012】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0013】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0014】

代表的な実施の形態による半導体装置は、配線基板上に半導体チップが搭載された、電力増幅回路を有する半導体装置であって、前記半導体チップには、前記電力増幅回路を構成するMISFET素子と、前記MISFET素子のゲートおよびドレインにそれぞれ電気的に接続されたゲート用パッド電極およびドレイン用パッド電極とを有している。そして、前記MISFET素子は、前記半導体チップの第1MISFET形成領域に形成された複数の単位MISFET素子を並列に接続して構成されており、前記複数の単位MISFET素子の各ゲート電極の延在方向である第1方向と交差する前記第1MISFET形成領域の第1の辺に沿って、前記複数の単位MISFET素子の前記各ゲート電極に電気的に接続された第1ゲート配線部が延在している。そして、前記第1ゲート配線部は、同層の第2ゲート配線部を介して同層の前記ゲート用パッド電極に接続され、前記第1ゲート配線部の幅は、前記第1MISFET形成領域の前記第1の辺の長さの1/10以上である。

【0015】

また、代表的な他の実施の形態による半導体装置は、配線基板上に半導体チップが搭載された、電力増幅回路を有する半導体装置であって、前記半導体チップには、前記電力増幅回路を構成するMISFET素子と、前記MISFET素子のゲートおよびドレインにそれぞれ電気的に接続されたゲート用パッド電極およびドレイン用パッド電極とを有している。そして、前記MISFET素子は、前記半導体チップの第1MISFET形成領域に形成された複数の単位MISFET素子を並列に接続して構成されており、前記複数の単位MISFET素子の各ゲート電極の延在方向である第1方向と交差する前記第1MISFET形成領域の第2の辺に沿って、前記複数の単位MISFET素子の各ドレイン領域と電気的に接続された第1ドレイン配線部が延在している。そして、前記ドレイン用パッド電極は、同層の前記第1ドレイン配線部に接続され、前記第1ドレイン配線部の幅は、前記第1MISFET形成領域の前記第2の辺の長さの1/10以上である。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

代表的な実施の形態によれば、半導体装置の性能を向上させることができる。

【図面の簡単な説明】

【0018】

【図1】デジタル携帯電話機の一例を示すブロック図である。

【図2】図1に示されるデジタル携帯電話機に用いられている電力増幅モジュールの構成例を模式的に示した回路ブロック図である。

【図3】本発明の一実施の形態である電力増幅モジュールの構造を示す概念的な断面図である。

【図4】比較例の電力増幅モジュールの概念的な平面図である。

【図5】本発明の一実施の形態の電力増幅モジュールの構造を示す概念的な平面図である。

【図6】本発明の一実施の形態の電力増幅モジュールの変形例を示す概念的な平面図である。

【図7】本発明の一実施の形態の半導体チップの要部断面図である。

【図8】本発明の一実施の形態の半導体チップの要部断面図である。

【図9】本発明の一実施の形態の半導体チップの要部断面図である。

【図10】本発明の一実施の形態の半導体チップの他の要部断面図である。

【図11】本発明の一実施の形態の半導体チップの要部平面図である。

【図12】本発明の一実施の形態の半導体チップの要部平面図である。

【図13】本発明の一実施の形態の半導体チップの要部平面図である。

【図14】本発明の一実施の形態の半導体チップの要部平面図である。

【図15】本発明の一実施の形態の半導体チップの要部平面図である。

【図16】本発明の一実施の形態の半導体チップの要部平面図である。

【図17】本発明の一実施の形態の半導体チップの要部平面図である。

【図18】本発明の一実施の形態の半導体チップの要部平面図である。

【図19】比較例の半導体チップの要部平面図である。

【図20】ゲートパッド電極とドレインパッド電極とを半導体チップの同じ辺に配置した場合の半導体チップの要部平面図である。

【図21】シミュレーションに用いた等価回路図である。

【図22】ゲート配線の連結配線部の幅を変えたときの、電力増幅モジュールの効率の向上量を示すグラフである。

【図23】本発明の他の実施の形態の半導体チップの要部平面図である。

【図24】本発明の他の実施の形態の半導体チップの要部平面図である。

【図25】本発明の他の実施の形態の半導体チップの要部平面図である。

【発明を実施するための形態】

【0019】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0021】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。

【0022】

(実施の形態1)

<デジタル携帯電話機の構成について>

図1は、標準的なデジタル携帯電話機(デジタル携帯電話機システム、移動体通信装置)DPSの一例を示すブロック図(説明図)である。

【0023】

図1に示されるデジタル携帯電話機DPSにおいては、アンテナANTより受信した信号は、アンテナスイッチANT−SWを通って低雑音アンプLNAにより増幅され、受信ミクサRX−MIXにより150〜250MHz程度のIF周波数(中間周波数)に変換された後、IF回路IFCで更に周波数変換され、455kHz程度の第2IF周波数としてベースバンド部BBPへ導かれて復調回路DMDLで復調される。なお、図1において、符号COD1は音声CODEC(コーデック)、符号SPはスピーカ、符号MICはマイク、符号COD2はチャネルCODEC(コーデック)、符号MDLは変調回路である。

【0024】

また、音声をデジタル化した信号は、ベースバンド部BBPのD/A変換回路DACでD−A変換(デジタル−アナログ変換)され、I/Q信号としてRFブロック部RFBPへ導かれ、直交変調器QMDによりIF周波数へ変調され、送信ミクサTX−MIXにより送信信号に変換された後、電力増幅モジュールPA1で増幅され、アンテナスイッチANT−SWを通してアンテナANTから送信される。受信ミクサRX−MIXおよび送信ミクサTX−MIXへは、発振器とPLL(位相同期回路)により構成されたシンセサイザよりローカル信号が供給されている。なお、図1において、符号AGCAMPはAGC(Automatic Gain Control)アンプ、符号FPL1はRF−PLL(RF周波数位相同期回路)、符号FPL2はIF−PLL(IF周波数位相同期回路)である。また、デジタル携帯電話機DPSは、液晶表示部LCD、マイコンMCNおよびメモリMRYなどで構成された表示・制御部CDPも備えている。

【0025】

<電力増幅モジュールの回路構成について>

図2は、図1に示されるデジタル携帯電話機DPSのような移動体通信装置に用いられている電力増幅モジュール(半導体装置、電子装置、電力増幅器、高出力増幅器、高周波電力増幅器、高周波電力増幅装置、電力増幅器モジュール、RFパワーモジュール)PA1の構成例を模式的に示した回路ブロック図(説明図)である。

【0026】

電力増幅モジュールPA1は、電力回路を有する半導体装置(または電子装置)であり、図2に示されるように、電力増幅モジュールPA1の回路構成は、複数段、ここでは2段(2つ)の増幅回路(増幅段、電力増幅回路)AMP1,AMP2と、インピーダンス整合用の整合回路AJC1,AJC2,AJC3とを有している。整合回路AJC1は、入力端子IPT1と1段目の増幅回路AMP1(のゲート)の間の整合回路(入力整合回路)である。整合回路AJC2は、1段目の増幅回路AMP1(のドレイン)と2段目の増幅回路AMP2(のゲート)の間の整合回路(段間整合回路)である。整合回路AJC3は、2段目の増幅回路AMP2(のドレイン)と出力端子OPT1の間の整合回路(出力整合回路)である。また、各増幅回路AMP1,AMP2のドレインには電源電圧VDD1が印加され、各増幅回路AMP1,AMP2のゲートには、電源電圧VDD2を抵抗分割して得られた電圧(バイアス電圧)が印加されるようになっている。

【0027】

電力増幅モジュールPA1の入力端子IPT1に入力されたRF入力信号(送信信号)は、整合回路AJC1を経て増幅回路AMP1で増幅され、更に整合回路AJC2を経て増幅回路AMP2で増幅されて、整合回路AJC3を経て出力端子OPT1からRF出力信号(増幅された送信信号)として出力される。

【0028】

このように、電力増幅モジュールPA1が有する電力増幅回路は、複数の増幅回路AMP1,AMP2を多段接続した多段構成を有している。

【0029】

また、図示は省略するが、整合回路AJC3と出力端子OPT1の間にローパスフィルタやアンテナスイッチ回路を設けることもできる。ローパスフィルタは高調波成分を減衰させる回路である。

【0030】

<電力増幅モジュールの構造について>

図3は、電力増幅モジュールPA1の構造を示す概念的な断面図(側面断面図)である。

【0031】

図3に示される電力増幅モジュールPA1は、配線基板(多層基板、多層配線基板、モジュール基板)11と、配線基板11上に搭載(実装)された半導体チップ(半導体素子、能動素子)CP1と、配線基板11上に搭載(実装)された受動部品(受動素子、チップ部品)12と、半導体チップCP1および受動部品12を含む配線基板11の上面11aを覆う封止樹脂(封止樹脂部)13とを有している。半導体チップCP1および受動部品12は、配線基板11の導体層(伝送線路)に電気的に接続されている。また、電力増幅モジュールPA1は、例えば図示しない外部回路基板またはマザーボードなどに実装することもできる。電力増幅モジュールPA1は、半導体チップCP1を有しているので半導体装置とみなすことができるが、電子装置とみなすこともできる。

【0032】

配線基板11は、例えば、複数の絶縁体層(誘電体層)14と、複数の導体層(配線層)とを積層して一体化した多層配線基板(多層基板)である。図3では、4つの絶縁体層14が積層されて配線基板11が形成されているが、積層される絶縁体層14の数はこれに限定されるものではなく種々変更可能である。配線基板11を構成する各導体層(配線層)は、必要に応じて絶縁体層14に形成されたビアホール(スルーホール)16内の導体(導体膜)を通じて電気的に接続されている。配線基板11の絶縁体層14を形成する材料としては、例えばアルミナ(酸化アルミニウム、Al2O3)などのようなセラミック材料を用いることができる。この場合、配線基板11はセラミック多層基板である。配線基板11の絶縁体層14の材料は、セラミック材料に限定されるものではなく種々変更可能であり、例えばガラスエポキシ樹脂などを用いても良い。

【0033】

配線基板11の上面(表面)11a上と下面(裏面)11b上と絶縁体層14間とには、配線形成用の導体層(配線層、配線パターン、導体パターン)が形成されている。配線基板11の最上層の導体層によって、配線基板11の上面11aに導電体からなる基板側端子(端子、電極)15aが形成され、配線基板11の最下層の導体層によって、配線基板11の下面11bに導電体からなる外部接続用端子(端子、電極、モジュール電極)15bが形成されている。

【0034】

外部接続用端子15bは、上記入力端子IPT1に対応する端子と上記出力端子OPT1に対応する端子とを含んでいる。配線基板11の内部、すなわち絶縁体層14の間にも導体層(配線層、配線パターン、導体パターン)が形成されているが、図3では簡略化のために図示を省略している。また、配線基板11の導体層により形成される配線パターンのうち、基準電位供給用の配線パターン(例えば配線基板11の下面11bの基準電位供給用端子15cなど)は、絶縁体層14の配線形成面の大半の領域を覆うような矩形パターンで形成し、伝送線路用の配線パターンは帯状のパターンで形成することができる。

【0035】

半導体チップCP1は、単結晶シリコンなどからなる半導体基板(半導体ウエハ)に半導体集積回路を形成した後、必要に応じて半導体基板の裏面研削を行ってから、ダイシングなどにより半導体基板を各半導体チップCP1に分離したものである。半導体チップCP1の表面(上面)には、複数のパッド電極(電極、ボンディングパッド)PDが形成されており、各パッド電極PDは、半導体チップCP1に形成された半導体素子または半導体集積回路に電気的に接続されている。半導体チップCP1の構成については、後でより詳細に説明する。

【0036】

図3に示されるように、半導体チップCP1は配線基板11の上面11aの導体層17に、例えば半田18などの接合材(接着材)によりフェイスアップでダイボンディングされている。半導体チップCP1のダイボンディングには、半田18の代わりに銀ペーストなどを用いることもできる。半導体チップCP1の表面(上面)に形成されたパッド電極PDは、導電性のワイヤ(ボンディングワイヤ)WAを介して配線基板11の上面11aの基板側端子15aに電気的に接続されている。また、半導体チップCP1の裏面全面には裏面電極BE1が形成されており、この半導体チップCP1の裏面電極BE1は、配線基板11の上面11aの導体層17に半田18などの導電性の接合材により接合されて電気的に接続され、更にビアホール16(16a)内の導体などを介して、配線基板11の下面11bの基準電位供給用端子15cに電気的に接続されている。なお、ビアホール16のうち、半導体チップCP1の下方に設けられたビアホール16aは、半導体チップCP1で生じた熱を配線基板11の下面11b側に伝導させるためのサーマルビアとして機能することもできる。

【0037】

受動部品12は、抵抗素子(例えばチップ抵抗)、容量素子(例えばチップコンデンサ)またはインダクタ素子(例えばチップインダクタ)などの受動素子からなり、例えばチップ部品からなる。受動部品12は、例えば上記整合回路AJC1,AJC2,AJC3などを構成する受動部品である。受動部品12の電極は、配線基板11の上面11aの基板側端子15aに半田18などの導電性の接合材により接合されて電気的に接続されている。

【0038】

半導体チップCP1または受動部品12が電気的に接続された配線基板11の上面11aの基板側端子15aは、必要に応じて配線基板11の上面11aまたは内部の配線層やビアホール16内の導体などを介して結線され、また、必要に応じて配線基板11の下面11bの外部接続用端子15bまたは基準電位供給用端子15cに電気的に接続されている。

【0039】

封止樹脂13は、半導体チップCP1、受動部品12およびワイヤWAを覆うように配線基板11の上面11a上に形成されている。封止樹脂11は、例えばエポキシ樹脂などの樹脂材料からなり、フィラーなどを含有することもできる。

【0040】

本実施の形態では、上記増幅回路AMP1および上記増幅回路AMP2を、1つの半導体チップCP1内に形成している。半導体チップCP1内に増幅回路AMP1,AMP2を設けることで、増幅回路AMP1を内蔵した半導体チップと増幅回路AMP2を内蔵した半導体チップとを別個に用意する場合に比べて、電力増幅モジュールPA1を小型化(小面積化)することができ、また、電力増幅モジュールPA1のコストを低減できる。

【0041】

更に、本実施の形態では、増幅回路AMP1,AMP2だけでなく、増幅回路AMP1,AMP2の増幅動作の制御や補佐などを行う制御回路(後述の制御回路CTC1に対応)も半導体チップCP1内に形成している。

【0042】

<比較例の電力増幅モジュールについて>

図4は、比較例の電力増幅モジュールPA101の概念的な平面図(上面図)であり、上記封止樹脂13に対応する封止樹脂を透視してある。

【0043】

図4に示される比較例の電力増幅モジュールPA101は、全体の回路構成は上記図2の回路構成とほぼ同様であるが、本実施の形態とは異なり、増幅回路AMP1を内蔵した半導体チップCP101と増幅回路AMP2を内蔵した半導体チップCP102とを別個に用意して配線基板111の上面111a上に搭載している。そして、半導体チップCP101,CP102のパッド電極PD101G,PD101D,PD102G,PD102Dをそれぞれ導電性のワイヤWA101を介して配線基板111の上面111aの基板側端子115aに電気的に接続している。また、配線基板111の上面111a上には、半導体チップCP101,102および受動部品112が搭載されているだけでなく、上記整合回路AJC1,AJC2,AJC3を構成する受動部品も搭載されているが、図面の簡略化のために、図4では、各整合回路AJC1,AJC2,AJC3を構成する受動部品が配置された領域を、符号AJC1,AJC2,AJC3を付したブロックで示してある。また、比較例の電力増幅モジュールPA101では、後述の制御回路CTC1に対応するものは、半導体チップCP101,CP102以外の半導体チップ(図示せず)に形成され、その半導体チップは、電力増幅モジュールPA101を構成する配線基板111の上面111a上に配置されるか、あるいは電力増幅モジュールPA101の外部に配置されている。

【0044】

なお、図4において、符号115bは、電力増幅モジュールPA101の外部接続用端子であり、理解を簡単にするために、配線基板111の上面111aに図示しているが、実際には配線基板111の下面に配置されている。また、符号115dは、配線基板111の配線パターンである。また、図4は、平面図であるが、図面を見やすくするために、半導体チップCP101,102におけるパッド電極PD101G,PD101D,PD102G,PD102Dとそれにつながるゲート配線およびドレイン配線を、ハッチングを付して示してある。

【0045】

図4に示される比較例の電力増幅モジュールPA101は、上記図2のように、整合回路AJC1と、半導体チップCP101内の増幅回路AMP1と、整合回路AJC2と、半導体チップCP102内の増幅回路AMP2と、整合回路AJC3とが順に直列に接続された回路構成を有している。

【0046】

このため、図4に示されるように、半導体チップCP101の主面(上面)において、ゲート用のパッド電極PD101Gとドレイン用のパッド電極PD101Dとを、半導体チップCP101の対向する辺にそれぞれ配置し、また、半導体チップCP102の主面(上面)において、ゲート用のパッド電極PD102Gとドレイン用のパッド電極PD102Dとを、半導体チップCP101の対向する辺にそれぞれ配置している。そして、配線基板111の上面111aにおいて、整合回路AJC1、半導体チップCP101、整合回路AJC2、半導体チップCP102および整合回路AJC3を順に並んで配置し、半導体チップCP101のゲート用のパッド電極PD101Gを整合回路AJC1にワイヤWA101で接続し、半導体チップCP101のドレイン用のパッド電極PD101Dを整合回路AJC2にワイヤWA101で接続している。また、半導体チップCP102のゲート用のパッド電極PD102Gを整合回路AJC2にワイヤWA101で接続し、半導体チップCP102のドレイン用のパッド電極PD102Dを整合回路AJC3にワイヤWA101で接続している。このような配置にすることで、配線基板111の上面111aでの各部品(半導体チップCP101,CP102および整合回路AJC1,AJC2,AJC3を構成する受動部品)の配置効率を高めることができる。

【0047】

しかしながら、図4に示される比較例の電力増幅モジュールPA101では、増幅回路AMP1を内蔵した半導体チップCP101と増幅回路AMP2を内蔵した半導体チップ102とを別個に用意している分、配線基板111上に搭載する半導体チップの数が多くなるため、電力増幅モジュールPA101が大型化(大面積化)し、またコストも増大してしまう。このため、本実施の形態のように、増幅回路AMP1および増幅回路AMP2を、1つの半導体チップCP1内に内蔵させることが好ましい。

【0048】

<電力増幅モジュールのレイアウトおよび接続関係について>

図5は、本実施の形態の電力増幅モジュールPA1の構造を示す概念的な平面図(上面図)であり、封止樹脂13を透視し、配線基板11の上面11a上における半導体チップCP1および上記整合回路AJC1,AJC2,AJC3(を構成する受動部品12)の配置状態が模式的に示されている。

【0049】

なお、配線基板11の上面11a上には、上記整合回路AJC1,AJC2,AJC3を構成する上記受動部品12も搭載されているが、図面の簡略化のために、図5では、各整合回路AJC1,AJC2,AJC3を構成する上記受動部品12が配置された領域を、各整合回路を示す符号AJC1,AJC2,AJC3を付したブロックで示してある。また、図5において、理解を簡単にするために、配線基板11の上面11aに外部接続用端子15bを図示しているが、実際には、上記図3にも示されるように、外部接続用端子15bは配線基板11の下面11bに配置されている。また、図5において、符号15dは、配線基板11の配線パターンである。

【0050】

上記図2および図5に示されるように、本実施の形態の電力増幅モジュールPA1は、整合回路AJC1と、半導体チップCP1内の増幅回路AMP1と、整合回路AJC2と、半導体チップCP1内の増幅回路AMP2と、整合回路AJC3とが順に直列に接続された回路構成を有している。増幅回路AMP1,AMP2および制御回路CTC1は半導体チップCP1内に形成され、整合回路AJC1,AJC2,AJC3は、配線基板11上に搭載された上記受動部品12や配線基板11の導体パターン(配線パターン)などによって形成されている。

【0051】

制御回路CTC1は、増幅回路AMP1,AMP2の増幅動作の制御や補佐などを行う回路である。制御回路CTC1には、電源電圧VDD1,VDD2が入力され、増幅回路AMP1,AMP2に印加するバイアス電圧や、増幅回路AMP1,AMP2のドレインに印加する電圧を制御する機能などを有している。

【0052】

半導体チップCP1に増幅回路AMP1,AMP2および制御回路CTC1を内蔵させることで、電力増幅モジュールPA1を構成するのに必要な半導体チップの数(すなわち配線基板11上に搭載する半導体チップの数)を少なくすることができるため、電力増幅モジュールPA1を小型化(小面積化)することができ、また、電力増幅モジュールPA1のコストを低減できる。

【0053】

増幅回路AMP1,AMP2のそれぞれは、半導体チップCP1内に形成されたMISFET素子、より特定的にはLDMOSFET(Laterally Diffused Metal-Oxide-Semiconductor Field Effect Transistor、横方向拡散MOSFET)素子、により形成されている。そして、増幅回路AMP1を構成するLDMOSFETと増幅回路AMP2を構成するLDMOSFETとが従属接続(多段接続)されて、電力増幅モジュールPA1の電力増幅回路を構成している。

【0054】

図5では、半導体チップCP1において、1段目の増幅回路AMP1を構成するLDMOSFET素子が形成された領域を、符号21を付してLDMOSFET形成領域21として示し、2段目の増幅回路AMP2を構成するLDMOSFET素子が形成された領域を、符号22を付してLDMOSFET形成領域22として示し、制御回路CTC1を構成する素子が形成された領域を、符号23を付して制御回路領域23として示してある。

【0055】

また、図5は、平面図であるが、図面を見やすくするために、半導体チップCP1におけるパッド電極PDと、半導体チップCP1においてLDMOSFET形成領域21(増幅回路AMP1)、LDMOSFET形成領域22(増幅回路AMP2)、制御回路領域23(制御回路CTC1)およびパッド電極PDの間を電気的に接続する配線とを、ハッチングを付して示してある。但し、このハッチングを付した配線と、LDMOSFET形成領域21、21および制御回路領域23は、実際には、半導体チップCP1の表面保護膜(後述の絶縁膜52)で覆われている。

【0056】

なお、本実施の形態では、2段の増幅回路AMP1,AMP2が接続(多段接続)されて電力増幅モジュールPA1の電力増幅回路が形成されているが、他の形態として、3段以上の増幅回路を接続(多段接続)して電力増幅モジュールPA1の電力増幅回路を形成することも可能であり、この場合、3段以上の増幅回路(LDMOSFET)が半導体チップCP1内に形成されることになる。

【0057】

図5に示されるように、半導体チップCP1は、パッド電極PDとして、ゲートパッド電極PD1G、ドレインパッド電極PD1D、ゲートパッド電極PD2G、ドレインパッド電極PD2Dおよび電源入力用パッド電極PD3,PD4を有している。

【0058】

このうち、ゲートパッド電極PD1Gは、増幅回路AMP1用のLDMOSFET(半導体チップCP1のLDMOSFET形成領域21に形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、かつ、整合回路AJC1を介してRF信号を半導体チップCP1に入力するための入力用のパッド電極PDである。また、ドレインパッド電極PD1Dは、増幅回路AMP1用のLDMOSFET(半導体チップCP1のLDMOSFET形成領域21に形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDであり、かつ、増幅回路AMP1で増幅したRF信号を半導体チップCP1から出力するための出力用のパッド電極PDである。また、ゲートパッド電極PD2Gは、増幅回路AMP2用のLDMOSFET(半導体チップCP1のLDMOSFET形成領域22に形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、かつ、ドレインパッド電極PD1Dから出力したRF信号を整合回路AJC2を介して半導体チップCP1に再入力するための入力用のパッド電極PDである。また、ドレインパッド電極PD2Dは、増幅回路AMP2用のLDMOSFET(半導体チップCP1のLDMOSFET形成領域22に形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDであり、かつ、増幅回路AMP2で増幅したRF信号を半導体チップCP1から出力するための出力用のパッド電極PDである。また、電源入力用パッド電極PD3,PD4は、半導体チップCP1内に形成された制御回路CTC1(制御回路領域23に形成された回路)に電気的に接続されており、電源入力用パッド電極PD3は、電源電圧VDD1を半導体チップCP1(の制御回路CTC1)に入力するための入力用のパッド電極PDである。また、電源入力用パッド電極PD4は、電源電圧VDD2を半導体チップCP1(の制御回路CTC1)に入力するための入力用のパッド電極PDである。

【0059】

このため、配線基板11上に搭載された半導体チップCP1のゲートパッド電極PD1Gを、整合回路AJC1に電気的に接続された基板側端子15aにワイヤWAで接続し、ドレインパッド電極PD1Dを、整合回路AJC2に電気的に接続された基板側端子15aにワイヤWAで接続している。そして、この整合回路AJC2に電気的に接続された他の基板側端子15aにゲートパッド電極PD2GをワイヤWAで接続し、ドレインパッド電極PD2Dを整合回路AJC3に電気的に接続された基板側端子15aにワイヤWAで接続している。また、電源電圧VDD1に電気的に接続される基板側端子15aに半導体チップCP1の電源入力用パッド電極PD3をワイヤWAで接続し、電源電圧VDD2に電気的に接続される基板側端子15aに半導体チップCP1の電源入力用パッド電極PD4をワイヤWAで接続している。

【0060】

本実施の形態の電力増幅モジュールPA1では、多段接続された複数の増幅回路AMP1,AMP2のうちの最終段の増幅回路AMP2とそれよりも1段前の増幅回路AMP1との間の段間整合回路用の受動部品12(ここでは整合回路AJC2用の受動部品12)が、配線基板11上に搭載されている。このため、最終段の増幅回路AMP2のゲートに接続されたゲートパッド電極PD2Gを半導体チップCP1に設け、整合回路AJC2を経たRF信号(送信信号)を、ゲートパッド電極PD2Gから半導体チップCP1内に再入力する必要がある。

【0061】

すなわち、電力増幅モジュールPA1の入力端子IPT1に対応する外部接続用端子15bに入力されたRF入力信号(送信信号)は、整合回路AJC1を経て半導体チップCP1のゲートパッド電極PD1Gに入力され、半導体チップCP1内の増幅回路AMP1(LDMOSFET形成領域21に形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD1Dから半導体チップCP1外に出力される。このドレインパッド電極PD1Dから出力されたRF信号(送信信号)は、半導体チップCP1外の整合回路AJC2を経て半導体チップCP1のゲートパッド電極PD2Gに再入力され、半導体チップCP1内の増幅回路AMP2(LDMOSFET形成領域22に形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD2Dから半導体チップCP1外に出力される。このドレインパッド電極PD2Dから出力されたRF信号(送信信号)は、整合回路AJC3を経て、出力端子OPT1に対応する外部接続用端子15bからRF出力信号(増幅された送信信号)として出力される。

【0062】

本実施の形態では、図5に示されるように、半導体チップCP1の主面(上面)において、ゲートパッド電極PD1Gとドレインパッド電極PD1Dとを半導体チップCP1の同じ辺に沿って配置し、ゲートパッド電極PD2Gとドレインパッド電極PD2Dとを半導体チップCP1の他の同じ辺に沿って配置し、電源入力用パッド電極PD3と電源入力用パッド電極PD4とを半導体チップCP1の更に他の同じ辺に沿って配置している。半導体チップCP1のパッド電極PDをこのような配置にすることで、半導体チップCP1の各パッド電極PDと整合回路AJC1,AJC2,AJC3とを接続しやすくし、配線基板11の上面11aでの各部品(半導体チップCP1および整合回路AJC1,AJC2,AJC3を構成する上記受動部品12)の配置効率を高め、また配線基板11における配線の引き回しのしやすさを高めることができる。特に、ゲートパッド電極PD2Gとドレインパッド電極PD2Dとを半導体チップCP1の主面(上面)の同じ辺に沿って配置することが重要である。

【0063】

図6は、本実施の形態の電力増幅モジュールPA1の変形例(すなわち電力増幅モジュールPA1a)を示す概念的な平面図(上面図)であり、上記図5に対応するものであり、封止樹脂13を透視してある。

【0064】

図6に示される、本実施の形態の変形例の電力増幅モジュールPA1aは、2系統(ここではGSM900用およびDCS1800用)の電力増幅回路を有し、2系統の電力増幅回路の送信周波数帯は、それぞれ0.9GHz帯(824〜915MHz)と1.8GHz帯(1710〜1910MHz)である。

【0065】

ここで、GSM(Global System for Mobile Communication)は、デジタル携帯電話に使用されている無線通信方式の1つまたは規格をいう。GSMには、使用する電波の周波数帯が3つあり、900MHz帯をGSM900または単にGSM、1800MHz帯をGSM1800またはDCS(Digital Cellular System)1800若しくはPCN、1900MHz帯をGSM1900またはDCS1900若しくはPCS(Personal Communication Services)という。

【0066】

図6に示される電力増幅モジュールPA1aの回路構成は、2つの増幅回路(増幅段)AMP1a,AMP2aと整合回路AJC1a,AJC2a,AJC3aとからなるGSM900用の電力増幅回路と、2つの増幅回路(増幅段)AMP1b,AMP2bと整合回路AJC1b,AJC2b,AJC3bとからなるDCS1800用の電力増幅回路と、それら電力増幅回路の増幅動作の制御や補佐などを行う制御回路CTC1とを有している。

【0067】

具体的には、電力増幅モジュールPA1aは、GSM900用の入力端子IPT1a用の外部接続用端子15bと出力端子OPT1a用の外部接続用端子15bとの間に、入力用の整合回路AJC1aと、GSM900用の1段目の増幅回路AMP1aと、段間用の整合回路AJC2aと、GSM900用の2段目の増幅回路AMP2aと、出力用の整合回路AJC3aとが順に直列に接続されたGSM900用の電力増幅回路を有している。また、電力増幅モジュールPA1aは、DCS1800用の入力端子IPT1b用の外部接続用端子15bと出力端子OPT1b用の外部接続用端子15bとの間に、入力用の整合回路AJC1bと、DCS1800用の1段目の増幅回路AMP1bと、段間用の整合回路AJC2bと、DCS1800用の2段目の増幅回路AMP2bと、出力用の整合回路AJC3bとが順に直列に接続されたDCS1800用の電力増幅回路を有している。増幅回路AMP1a,AMP2a,AMP1b,AMP2bおよび制御回路CTC1は半導体チップCP1内に形成され、整合回路AJC1a,AJC2a,AJC3a,AJC1b,AJC2b,AJC3bは、配線基板11上に搭載された上記受動部品12や配線基板11の導体パターンなどによって形成されている。

【0068】

なお、配線基板11の上面11a上には、上記整合回路AJC1a〜AJC3a,AJC1b〜AJC3bを構成する上記受動部品12も搭載されているが、図面の簡略化のために、図6では、各整合回路AJC1a〜AJC3a,AJC1b〜AJC3bを構成する上記受動部品12が配置された領域を、整合回路を示す符号AJC1a〜AJC3a,AJC1b〜AJC3bを付したブロックで示してある。また、図5と同様に、図6においても、理解を簡単にするために、配線基板11の上面11aに外部接続用端子15bを図示しているが、実際には、上記図3にも示されるように、外部接続用端子15bは配線基板11の下面11bに配置されている。

【0069】

増幅回路AMP1a,AMP2a,AMP1b,AMP2bのそれぞれは、半導体チップCP1内に形成されたMISFET素子、より特定的にはLDMOSFET素子、により形成されている。そして、増幅回路AMP1aを構成するLDMOSFETと増幅回路AMP2aを構成するLDMOSFETとが従属接続(多段接続)されて、GSM900用の電力増幅回路が形成され、また、増幅回路AMP1bを構成するLDMOSFETと増幅回路AMP2bを構成するLDMOSFETとが従属接続(多段接続)されて、DCS1800用の電力増幅回路が形成されている。

【0070】

図6では、半導体チップCP1において、GSM900用の1段目の増幅回路AMP1aを構成するLDMOSFET素子が形成された領域を、符号21aを付してLDMOSFET形成領域21aとして示し、GSM900用の2段目の増幅回路AMP2aを構成するLDMOSFET素子が形成された領域を、符号22aを付してLDMOSFET形成領域22aとして示している。また、DCS1800用の1段目の増幅回路AMP1bを構成するLDMOSFET素子が形成された領域を、符号21bを付してLDMOSFET形成領域21bとして示し、DCS1800用の2段目の増幅回路AMP2bを構成するLDMOSFET素子が形成された領域を、符号22bを付してLDMOSFET形成領域22bとして示している。また、図6は、平面図であるが、図面を見やすくするために、半導体チップCP1におけるパッド電極PDと、半導体チップCP1において増幅回路AMP1a,AMP2a,AMP1b,AMP2b、制御回路CTC1およびパッド電極PDの間を電気的に接続する配線とに、ハッチングを付して示してある。

【0071】

図6に示される半導体チップCP1は、パッド電極PDとして、ゲートパッド電極PD1Ga,PD2Ga,PD1Gb,PD2Gb、ドレインパッド電極PD1Da,PD2Da,PD1Db,PD2Dbおよび電源入力用パッド電極PD3,PD4を有している。

【0072】

このうち、ゲートパッド電極PD1Gaは、増幅回路AMP1a用のLDMOSFET(LDMOSFET形成領域21aに形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、ドレインパッド電極PD1Daは、増幅回路AMP1a用のLDMOSFET(LDMOSFET形成領域21aに形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDである。また、ゲートパッド電極PD2Gaは、増幅回路AMP2a用のLDMOSFET(LDMOSFET形成領域22aに形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、ドレインパッド電極PD2Daは、増幅回路AMP2a用のLDMOSFET(LDMOSFET形成領域22aに形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDである。また、ゲートパッド電極PD1Gbは、増幅回路AMP1b用のLDMOSFET(LDMOSFET形成領域21bに形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、ドレインパッド電極PD1Dbは、増幅回路AMP1b用のLDMOSFET(LDMOSFET形成領域21bに形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDである。また、ゲートパッド電極PD2Gbは、増幅回路AMP2b用のLDMOSFET(LDMOSFET形成領域22bに形成されたLDMOSFET)のゲートに電気的に接続されたパッド電極PDであり、また、ドレインパッド電極PD2Dbは、増幅回路AMP2b用のLDMOSFET(LDMOSFET形成領域22bに形成されたLDMOSFET)のドレインに電気的に接続されたパッド電極PDである。電源入力用パッド電極PD3,PD4については、上記図5の場合と同様であるので、ここではその説明は省略する。

【0073】

このため、配線基板11上に搭載された半導体チップCP1のゲートパッド電極PD1Gaを、整合回路AJC1aに電気的に接続された基板側端子15aにワイヤWAで接続し、ドレインパッド電極PD1Daを、整合回路AJC2aに電気的に接続された基板側端子15aにワイヤWAで接続している。そして、この整合回路AJC2aに電気的に接続された他の基板側端子15aに、ゲートパッド電極PD2GaをワイヤWAで接続し、ドレインパッド電極PD2Daを、整合回路AJC3aに電気的に接続された基板側端子15aにワイヤWAで接続している。

【0074】

また、配線基板11上に搭載された半導体チップCP1のゲートパッド電極PD1Gbを、整合回路AJC1bに電気的に接続された基板側端子15aにワイヤWAで接続し、ドレインパッド電極PD1Dbを、整合回路AJC2bに電気的に接続された基板側端子15aにワイヤWAで接続している。そして、この整合回路AJC2bに電気的に接続された他の基板側端子15aに、ゲートパッド電極PD2GbをワイヤWAで接続し、ドレインパッド電極PD2Dbを、整合回路AJC3bに電気的に接続された基板側端子15aにワイヤWAで接続している。

【0075】

また、電源電圧VDD1に電気的に接続される基板側端子15aに、半導体チップCP1の電源入力用パッド電極PD3をワイヤWAで接続し、電源電圧VDD2に電気的に接続される基板側端子15aに、半導体チップCP1の電源入力用パッド電極PD4をワイヤWAで接続している。

【0076】

本実施の形態の電力増幅モジュールPA1aでは、多段接続された複数の増幅回路AMP1a,AMP2aのうちの最終段の増幅回路AMP2aとそれよりも1段前の増幅回路AMP1aとの間の段間整合回路用の受動部品12(ここでは整合回路AJC2a用の受動部品12)が配線基板11上に搭載されている。また、多段接続された複数の増幅回路AMP1b,AMP2bのうちの最終段の増幅回路AMP2bとそれよりも1段前の増幅回路AMP1bとの間の段間整合回路用の受動部品12(ここでは整合回路AJC2b用の受動部品12)が配線基板11上に搭載されている。このため、最終段の増幅回路AMP2a,AMP2bの各ゲートに接続されたゲートパッド電極PD2Ga,PD2Gbを半導体チップCP1に設け、各整合回路AJC2a,AJC2bを経たRF信号(送信信号)を、ゲートパッド電極PD2Ga,PD2Gbから半導体チップCP1内に再入力する必要がある。

【0077】

すなわち、電力増幅モジュールPA1aの入力端子IPT1aに対応する外部接続用端子15bに入力されたGSM900用RF入力信号(送信信号)は、整合回路AJC1aを経て半導体チップCP1のゲートパッド電極PD1Gaに入力され、半導体チップCP1内の増幅回路AMP1a(LDMOSFET形成領域21aに形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD1Daから出力される。このドレインパッド電極PD1Daから出力されたGSM900用のRF信号(送信信号)は、半導体チップCP1外の整合回路AJC2aを経て半導体チップCP1のゲートパッド電極PD2Gaに再入力され、半導体チップCP1内の増幅回路AMP2a(LDMOSFET形成領域22aに形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD2Daから出力される。このドレインパッド電極PD2Daから出力されたRF信号(送信信号)は、整合回路AJC3aを経て、出力端子OPT1aに対応する外部接続用端子15bからGSM900用のRF出力信号(増幅された送信信号)として出力される。

【0078】

また、電力増幅モジュールPA1aの入力端子IPT1bに対応する外部接続用端子15bに入力されたDCS1800用RF入力信号(送信信号)は、整合回路AJC1bを経て半導体チップCP1のゲートパッド電極PD1Gbに入力され、半導体チップCP1内の増幅回路AMP1b(LDMOSFET形成領域21bに形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD1Dbから出力される。このドレインパッド電極PD1Dbから出力されたDCS1800用のRF信号(送信信号)は、半導体チップCP1外の整合回路AJC2bを経て半導体チップCP1のゲートパッド電極PD2Gbに再入力され、半導体チップCP1内の増幅回路AMP2b(LDMOSFET形成領域22bに形成されたLDMOSFET)で増幅されて、半導体チップCP1のドレインパッド電極PD2Dbから出力される。このドレインパッド電極PD2Dbから出力されたRF信号(送信信号)は、整合回路AJC3bを経て、出力端子OPT1bに対応する外部接続用端子15bからDCS1800用のRF出力信号(増幅された送信信号)として出力される。

【0079】

図6に示される電力増幅モジュールPA1aでは、GSM900用の増幅回路AMP1a,AMP2aとDCS1800用の増幅回路AMP1b,AMP2bと制御回路CTC1とを、1つの半導体チップCP1内に内蔵させている。これにより、電力増幅モジュールPA1aに使用する半導体チップの数を少なくして電力増幅モジュールPA1aを小型化(小面積化)することができ、また、電力増幅モジュールPA1aのコストを低減できる。

【0080】

更に、図6の電力増幅モジュールPA1aでは、半導体チップCP1の主面(上面)において、GSM900用の増幅回路AMP2aに接続されたゲートパッド電極PD2Gaとドレインパッド電極PD2Daとを半導体チップCP1の同じ辺に沿って配置し、DCS1800用の増幅回路AMP2bに接続されたゲートパッド電極PD2Gbとドレインパッド電極PD2Dbとを半導体チップCP1の他の同じ辺に沿って配置している。ここで、GSM900用のゲートパッド電極PD2Gaおよびドレインパッド電極PD2Daが配置された半導体チップCP1の辺と、DCS1800用のゲートパッド電極PD2Gbおよびドレインパッド電極PD2Dbが配置された半導体チップCP1の辺とは、半導体チップCP1の主面(上面)において、互いに対向する辺である。半導体チップCP1のパッド電極PDをこのような配置にすることで、半導体チップCP1の各パッド電極PDと整合回路AJC1a〜AJC3a,AJC1b〜AJC3bとを接続しやすくし、配線基板11の上面11aでの各部品(半導体チップCP1および受動部品12)の配置効率を高め、また配線基板11における配線の引き回しのしやすさを高めることができる。

【0081】

このように、電力増幅モジュールPA1,PA1aにおいては、複数段の増幅回路を1つの半導体チップCP1に内蔵させているため、半導体チップCP1におけるパッド電極PDの種類や数が多い。このため、整合回路との接続しやすさを考慮すると、半導体チップCP1に設けられた複数段の増幅回路のうち、特に最終段の増幅回路(上記増幅回路AMP2,AMP2a,AMP2bに対応)に接続されたゲートパッド電極とドレインパッド電極とを半導体チップCP1の主面(上面)の同じ辺に沿って配置することが望ましい。すなわち、図5のように、ゲートパッド電極PD2Gとドレインパッド電極PD2Dとを半導体チップCP1の主面(上面)の同じ辺に沿って配置することが望ましい。あるいは、図6のように、ゲートパッド電極PD2Gaとドレインパッド電極PD2Daとを半導体チップCP1の主面(上面)の同じ辺に沿って配置し、ゲートパッド電極PD2Gbとドレインパッド電極PD2Dbとを半導体チップCP1の主面(上面)の他の同じ辺に沿って配置することが望ましい。

【0082】

しかしながら、半導体チップの主面において、同じ辺に沿ってゲートパッド電極とドレインパッド電極とを配置した場合、ドレインパッド電極が配置されている辺まで配線でゲートパッド電極を引き回す必要があるため、半導体チップにおけるゲートパッド電極用の配線が長くなってしまう。本発明者が検討したところ、これは、電力損失を高め、電力増幅モジュールの効率を低下させる可能性があることが分かった。そこで、本実施の形態では、半導体チップCP1の構成を以下のように工夫している。

【0083】

<半導体チップの構成について>

図7〜図10は、半導体チップCP1の要部断面図である。図7には、半導体チップCP1において、上記LDMOSFET形成領域22,22a,22bの要部断面図が示されている。図8は、図7とは異なる断面位置が示され、素子分離領域32上においてゲート電極35をゲート配線M1G,M2Gに引き上げている領域の断面図に対応する。図9は、図7および図8とは異なる断面位置が示され、ドレインパッド電極PD2D,PD2Da,PD2Dbが形成された領域の断面図に対応する。図10は、図7〜図9とは異なる断面位置が示され、ゲートパッド電極PD2G,PD2Ga,PD2Gbが形成された領域の断面図に対応する。

【0084】