半導体装置

【課題】異なる系統の電力増幅回路を含む半導体装置を小型にする。

【解決手段】2つの周波数帯の高周波信号を取り扱うことが可能なデュアル方式のデジタル携帯電話機のRFパワーモジュールを構成する系統の異なる電力増幅回路2A,2Bを同一のICチップ1C内に配置した。この場合、電力増幅回路2A,2BをICチップ1Cの周辺に配置し、周辺回路3を電力増幅回路2A,2Bの間に配置させた。これにより、異なる系統の電力増幅回路2A,2Bを同一のICチップ1C内に設けて小型化が図れる上、異なる系統の電力増幅回路2A,2Bを同一のICチップ1Cに設けても電力増幅回路2A,2B間の距離が確保されるので電力増幅回路2A,2B間の結合を抑制させることができ、電力増幅回路2A,2B間でのクロストークを抑制できる。

【解決手段】2つの周波数帯の高周波信号を取り扱うことが可能なデュアル方式のデジタル携帯電話機のRFパワーモジュールを構成する系統の異なる電力増幅回路2A,2Bを同一のICチップ1C内に配置した。この場合、電力増幅回路2A,2BをICチップ1Cの周辺に配置し、周辺回路3を電力増幅回路2A,2Bの間に配置させた。これにより、異なる系統の電力増幅回路2A,2Bを同一のICチップ1C内に設けて小型化が図れる上、異なる系統の電力増幅回路2A,2Bを同一のICチップ1Cに設けても電力増幅回路2A,2B間の距離が確保されるので電力増幅回路2A,2B間の結合を抑制させることができ、電力増幅回路2A,2B間でのクロストークを抑制できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置技術に関し、特に、RF(Radio Frequency)パワーモジュールに適用して有効な技術に関するものである。

【背景技術】

【0002】

本発明者が検討したRFパワーモジュールは、例えば携帯電話機等のような通信機器に用いられる信号増幅用の電子部品であり、信号増幅用のトランジスタを有する複数の半導体チップやチップ部品等をモジュール基板上に実装することで組み立てられている。各半導体チップとモジュール基板とは、ボンディングワイヤを通じて電気的に接続されている。また、チップ部品もその端子をはんだ付けによりモジュール基板のパッドに接続することでモジュール基板と電気的に接続されている。

【0003】

なお、例えば特開2000−332551号公報には、デュアルバンドシステム用の高周波電力増幅器のバイアス回路およびバイアススイッチ回路をHBT(Heterojunction Bipolar Transistor)で形成する構成が開示されている(特許文献1参照)。

【0004】

また、例えば特開2001−141756号公報には、デュアルバンドシステム用の高周波部品において、2つの出力間の干渉を防ぐため、出力用のマイクロストリップライン間に複数のGND線路を設ける構成が開示されている(特許文献2参照)。

【0005】

また、例えば特開2001−345400号公報には、デュアルバンドのパワーモジュールで2つの出力間の干渉を防ぐために、半導体チップと配線基板との双方の出力パッド間にそれぞれグランド用のパッドを設け、ワイヤボンディングする技術が開示されている(特許文献3参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−332551号公報

【特許文献2】特開2001−141756号公報

【特許文献3】特開2001−345400号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところが、上記RFパワーモジュールにおいては、小型化が急速に進められており、信頼性や性能等のような特性の低下を招くことなく、如何にして小型化するかが重要な課題となっている。

【0008】

本発明の目的は、半導体装置を小型にすることのできる技術を提供することにある。

【0009】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0011】

本発明は、高周波電力増幅回路の複数段の増幅回路の全段を、横型の電界効果トランジスタで形成し、シリコン系の半導体基板を有する同一の半導体チップに設けたものである。

【発明の効果】

【0012】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0013】

すなわち、高周波電力増幅回路の複数段の増幅回路の全段を、横型の電界効果トランジスタで形成し、シリコン系の半導体基板を有する同一の半導体チップに設けたことにより、半導体装置を小型にすることができる。

【図面の簡単な説明】

【0014】

【図1】本発明の一実施の形態である半導体装置の回路ブロック図である。

【図2】図1の半導体装置の要部回路図である。

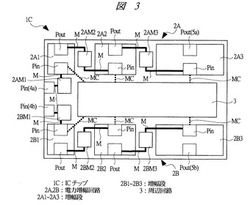

【図3】図1の半導体装置の回路配置例を示す半導体チップの全体平面図である。

【図4】距離と漏洩電力との関係を示すグラフ図である。

【図5】図1の半導体装置の半導体チップの要部平面図である。

【図6】図5の半導体チップの要部断面図である。

【図7】図5の半導体チップの増幅段の等価回路の回路図である。

【図8】図5の半導体チップをモジュール基板に搭載したRFパワーモジュールの一例の全体平面図である。

【図9】図8のRFパワーモジュールの断面図である。

【図10】図8のRFパワーモジュールの等価回路の回路図である。

【図11】図8のRFパワーモジュールを用いたデジタル携帯電話機システムの一例の説明図である。

【図12】図11のデジタル携帯電話機システムのRFパワーモジュールの実装例の要部側面図である。

【図13】本発明の他の実施の形態である半導体装置の回路配置例を示す半導体チップの全体平面図である。

【図14】図13の半導体チップをモジュール基板に搭載したRFパワーモジュールの一例の全体平面図である。

【図15】本発明のさらに他の実施の形態である半導体装置の回路配置例を示す半導体チップの全体平面図である。

【図16】図15の半導体チップをモジュール基板に搭載したRFパワーモジュールの一例の全体平面図である。

【図17】本発明のさらに別の実施の形態である半導体装置の回路配置例を示す半導体チップの全体平面図である。

【発明を実施するための形態】

【0015】

本願発明の実施の形態を詳細に説明する前に、本実施の形態における用語の意味を説明すると次の通りである。

1.GSM(Global System for Mobile Communication)は、デジタル携帯電話に使用されている無線通信方式の1つまたは規格をいう。GSMには、使用する電波の周波数帯が3つあり、900MHz帯をGSM900または単にGSM、1800MHz帯をGSM1800またはDCS(Digital Cellular System)1800若しくはPCN、1900MHz帯をGSM1900またはDCS1900若しくはPCS(Personal Communication Services)という。なお、GSM1900は主に北米で使用されている。北米ではその他に850MHz帯のGSM850を使用する場合もある。

2.GMSK変調方式は、音声信号の通信に用いる方式で搬送波の位相を送信データに応じて位相シフトする方式である。また、EDGE変調方式は、データ通信に用いる方式でGMSK変調の位相シフトにさらに振幅シフトを加えた方式である。

【0016】

また、以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。また、本実施の形態では、電界効果トランジスタであるMOS・FET(Metal Oxide Semiconductor・Field Effect Transistor)をMOSと略し、nチャネル型のMOSをnMOSと略す。

【0017】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0018】

(実施の形態1)

本実施の形態1では、例えばGSM方式のネットワークを利用して情報を伝送するデジタル携帯電話に使用されるRF(Radio Frequency)パワーモジュールに本実施の形態1の半導体装置を適用した場合について説明する。

【0019】

図1は、本実施の形態1のRFパワーモジュールを構成する増幅回路用のIC(Integrated circuit)チップ(半導体チップ)1Cの回路ブロック図を示している。この図1には、例えばGSM900とDCS1800との2つの周波数帯を使用可能(デュアルバンド方式)で、それぞれの周波数帯でGMSK(Gaussian filtered Minimum Shift Keying)変調方式とEDGE(Enhanced Data GSM Environment)変調方式との2つの通信方式を使用可能なRFパワーモジュールに使用される増幅回路用のICチップ(半導体チップ)1Cの回路ブロックが例示されている。

【0020】

このICチップ1Cは、GSM900用の電力増幅回路2Aと、DCS1800用の電力増幅回路2Bと、それら電力増幅回路2A,2Bの増幅動作の制御や補正等を行う周辺回路3とを有している。各電力増幅回路2A,2Bは、それぞれ3つの増幅段2A1〜2A3,2B1〜2B3と、3つの整合回路2AM1〜2AM3,2BM1〜2BM3とを有している。すなわち、ICチップ1Cの入力端子4a,4bは、入力用の整合回路2AM1,2BM1を介して1段目の増幅段2A1,2B1の入力に電気的に接続され、1段目の増幅段2A1,2B1の出力は段間用の整合回路2AM2,2BM2を介して2段目の増幅段2A2,2B2の入力に電気的に接続され、2段目の増幅段2A2,2B2の出力は段間用の整合回路2AM3,2BM3を介して最終段の増幅段2A3,2B3の入力に電気的に接続され、最終段の増幅段2A3,2B3の出力は出力端子5a,5bと電気的に接続されている。このように本実施の形態1では、1つのICチップ1Cの中に、電力増幅回路2A,2Bの全ての増幅段2A1〜2A3,2B1〜2B3が設けられている。一般的には3つの増幅段がそれぞれ別々のICチップに設けられているか、または、1段目および2段目の増幅段が1つのICチップに設けられ、最終段の増幅段はパワーが大きく動作時の発熱が高いことや他の増幅段への信号干渉が大きい等の理由から1段目および2段目の増幅段が設けられたICチップとは別のICチップに設けられている。このため、RFパワーモジュールの小型化が阻害されている。これに対して、本実施の形態1では、1つのICチップ1C内に、電力増幅回路2A,2Bの全ての増幅段2A1〜2A3,2B1〜2B3を設けたことにより、各増幅段2A1〜2A3,2B1〜2B3間の隣接間隔を大幅に短くすることができるので、そのICチップ1Cを内蔵するRFパワーモジュールの大幅な小型化を実現することが可能となっている。

【0021】

上記周辺回路3は、制御回路3Aと、上記増幅段2A1〜2A3,2B1〜2B3にバイアス電圧を印加するバイアス回路3B等を有している。制御回路3Aは、上記電力増幅回路2A,2Bに印加する所望の電圧を発生する回路であり、電源制御回路3A1およびバイアス電圧生成回路3A2を有している。電源制御回路3A1は、上記増幅段2A1〜2A3,2B1〜2B3の各々の出力用のパワーMOSのドレイン端子に印加される第1電源電圧を生成する回路である。また、上記バイアス電圧生成回路3A2は、上記バイアス回路3Bを制御するための第1制御電圧を生成する回路である。本実施の形態1では、電源制御回路3A1が、ICチップ1C外部のベースバンド回路から供給される出力レベル指定信号に基づいて上記第1電源電圧を生成すると、バイアス電圧生成回路3A2が電源制御回路3A1で生成された上記第1電源電圧に基づいて上記第1制御電圧を生成するようになっている。上記ベースバンド回路は、上記出力レベル指定信号を生成する回路である。この出力レベル指定信号は、電力増幅回路2A,2Bの出力レベルを指定する信号で、携帯電話と、基地局との間の距離、すなわち、電波の強弱に応じた出力レベルに基づいて生成されているようになっている。本実施の形態1では、このような周辺回路3を構成する素子も1つのICチップ1C内に設けられている。これにより、インターフェイス部(ICチップ1Cとモジュール基板(配線基板)との間のインターフェイス部およびICチップ1Cとモジュール基板との各々に必要であったインターフェイス部)を大幅に削減でき、ICチップ1Cやモジュール基板の面積を縮小できるので、RFパワーモジュールの大幅な小型化を実現することが可能となっている。

【0022】

次に、図2は、上記電力増幅回路2Aおよび上記バイアス回路3Bの回路構成の一例を示している。なお、上記電力増幅回路2A,2Bおよびその各々のバイアス回路3Bの回路構成は同じなので、ここでは上記電力増幅回路2Aおよび電力増幅回路2A用の回路構成の一例を代表して示す。

【0023】

本実施の形態1の電力増幅回路2Aは、上記3段の増幅段2A1〜2A3として3つのnMOSQn(Qn1,Qn2,Qn3)を順次従属接続した回路構成を有している。この電力増幅回路2Aの出力レベルは、上記バイアス回路3Bおよび電源制御回路3A1から供給される上記第1電源電圧Vdd1によって制御される。ここでは、その第1電源電圧Vdd1が3つのnMOSQn1,Qn2,Qn3の各々のドレイン電極に供給されるようになっている。

【0024】

整合回路2AM1〜2AM3は、インダクタ(受動素子)と、コンデンサ(受動素子)とを有している。インダクタは、配線で形成されており、1段目の増幅段2A1(nMOSQn1)の入力およびそれぞれの段間でのインピーダンス整合をとる機能を有している。また、上記コンデンサは、上記インダクタと各段のnMOSQnの入力との間に接続されており、上記インピーダンス整合の機能と、その他に第1電源電圧Vdd1とゲートバイアス電圧との直流電圧を遮断する機能とを有している。

【0025】

上記バイアス回路3Bは、複数の分圧回路を有している。各分圧回路は、一対の抵抗R1,R2で構成されている。各一対の抵抗R1,R2は、バイアス回路3Bの入力端子4cと、基準電位(例えば接地電位で0V)との間に直列に接続されている。各一対の抵抗R1,R2間を繋ぐ配線部分と、各段のnMOSQn1〜Qn3の入力(ゲート電極)とが電気的に接続されている。このバイアス回路3Bの入力端子4cに上記第1制御電圧または出力レベル制御電圧が入力されると、その電圧が上記一対の抵抗R1,R2で分圧されて所望のゲートバイアス電圧が生成され、そのゲートバイアス電圧が、各々のnMOSQn1〜Qn3のゲート電極に入力されるようになっている。

【0026】

次に、図3は、図1の増幅回路用のICチップ1Cの回路配置の一例を示し、図4は距離と漏洩電力との関係を示すグラフ図を示している。

【0027】

本実施の形態1では、図3に示すように、ICチップ1Cの主面(デバイス形成面)の周辺に電力増幅回路2A,2Bが配置され、その各々の電力増幅回路2A,2Bの間に周辺回路3が配置されている。特に、上記のように電力増幅回路2A,2Bの最終段の増幅段2A3,2B3は、パワーが大きく動作時の発熱が高いことや他の増幅段への信号干渉が大きい(特にここでは取り扱う高周波信号がそれぞれ900MHzと1800MHzというように各々の高調波の位相が逆なので信号間の干渉の問題が大きい)ので、相互間の距離が長くなるように、ICチップ1Cの相対する辺の近傍に配置されている。図4に示すように、2点間の信号伝搬量は概ね距離の2乗に反比例するので、上記のように電力増幅回路2A,2Bを離して配置することにより、例えば動作している電力増幅回路から動作していない電力増幅回路へのクロストーク(輻射あるいは干渉)を抑制することができ、また、動作していない電力増幅回路からの不要な出力発生を抑制することができる等、系統の異なる電力増幅回路2A,2Bを同一のICチップ1Cに設けても、電力増幅回路2A,2B間のクロスバンドアイソレーション特性を向上させることができる。したがって、RFパワーモジュールの動作の信頼性や安定性を向上させることが可能となる。

【0028】

図3中の符号のPinは入力用のボンディングパッド、Poutは出力用のボンディングパッドを示している。各増幅段2A1〜2A3や増幅段2B1〜2B3のボンディングパッドPinは、ICチップ1Cの中央側に配置され、各増幅段2A1〜2A3や増幅段2B1〜2B3のボンディングパッドPoutはICチップ1Cの辺側に配置されている。また、符号のMは入力用、出力用および増幅段間用の配線を示している。増幅段間用の配線Mは屈曲した状態でボンディングパッドPin,Pout間を接続している。また、符号のMcは増幅段2A1〜2A3,2B1〜2B3と周辺回路3を接続する配線を示している。

【0029】

次に、図5は、上記ICチップ1Cの要部平面図を示し、図6は、図5のICチップ1Cの左右方向に沿って切断した箇所の要部断面図を示している。なお、図5は平面図であるが、図面を見易くするために同層のものに同じハッチングを付している。

【0030】

ICチップ1Cを構成する半導体基板(以下、単に基板という)1Sは、例えばp+型のシリコン(Si)単結晶からなり、その抵抗率が、例えば1〜10mΩ・cm程度の低抵抗基板とされている。基板1S上には、例えばp−型のシリコン単結晶からなるエピタキシャル層1EPが形成されている。エピタキシャル層1EPの抵抗率は、上記基板1Sの抵抗率よりも高い。このエピタキシャル層1EPの主面には、上記増幅段2A1〜2A3,2B1〜2B3用のnMOSQnと、上記整合回路2AM1〜2AM3,2BM1〜2BM3用のインダクタL1、高Q(Quality factor)値のコンデンサC1およびストリップ線路が形成されている。ここでは、2段の増幅段のnMOSQn1,Qn2が示されているが、実際には上記のように2系統の1〜3段の全ての増幅段2A1〜2A3,2B1〜2B3が同一の基板1Sに形成されている。また、ここで示したnMOSQnは単位MOSを示しており、実際には、この単位MOSが複数個並列に接続されることで1つの増幅段2A1〜2A3,2B1〜2B3が形成されている。

【0031】

まず、nMOSQnは、例えばLDMOS(Laterally Diffused MOS)等のような横型のMOSで形成されている。nMOSQnの形成領域のエピタキシャル層1EPには、p型のウエルPWLが形成されている。このp型のウエルPWLは、例えばホウ素(B)などの不純物をエピタキシャル層1EPにイオン注入することなどにより形成されている。エピタキシャル層1EPの上記p型のウエルPWL上には、nMOSQnのゲート絶縁膜7が形成されている。このゲート絶縁膜7は、例えば酸化シリコン(SiO2等)からなり、例えば熱酸化法などによって形成されている。このゲート絶縁膜7上には、nMOSQnのゲート電極(入力)8が形成されている。このゲート電極8は、例えば多結晶シリコンとその上に形成された金属シリサイド層(例えばチタンシリサイド層またはコバルトシリサイド層)との積層導体膜で構成されている。nMOSQnのチャネルは、ゲート電極8下のp型のウエルPWLの上部に形成される。

【0032】

このゲート電極8の一方の端部近傍のp型のウエルPWLの領域内には、n+型の半導体領域9が形成されている。このn+型の半導体領域9は、nMOSQnのソースとして機能する領域であり、例えばリン(P)などの不純物をp型のウエルPWLにイオン注入することで形成されている。また、ゲート電極8の他方の端部近傍のエピタキシャル層1EPには、n−型の半導体領域10aが形成されている。そして、ゲート電極8の他方の端部からn−型の半導体領域10aの分だけ離れた箇所には、n+型の半導体領域10bがn−型の半導体領域10aと電気的に接続された状態で形成されている(LDD(Lightly Doped Drain)構造)。このn−型の半導体領域10aおよびn+型の半導体領域10bは、nMOSQnのドレイン(出力)として機能する領域であり、例えばリン(P)などの不純物をp型のウエルPWLにイオン注入することで形成されている。

【0033】

また、本実施の形態1では、各々のnMOSQnの形成領域のエピタキシャル層1EPにp++型の半導体領域11aが上記n+型の半導体領域9,10bと接するように形成されている。このp++型の半導体領域11aは、例えばホウ素(B)が導入されてなり、平面で見ると、nMOSQnを取り囲むように形成され、断面で見ると、エピタキシャル層1EPの主面から基板1Sに達するように形成されている。そして、本実施の形態1では、各nMOSQnのソース用のn+型の半導体領域9が、プラグPL1を通じてp++型の半導体領域11aと電気的に接続され、そのp++型の半導体領域11を通じて低抵抗なp+型の基板1Sと電気的に接続されている。後述のように、基板1Sは、基板1Sの裏面全面にメタルで形成された電極12を介して、ICチップ1Cが実装されるモジュール基板の配線と電気的に接続され、その配線を通じて基準電位(例えば接地電位GNDで0V程度:固定電位)に電気的に接続される。すなわち、基板1Sは、ICチップ1Cに形成された複数のnMOSQnの共通の接地部分とされている。

【0034】

図7は、この様子の等価回路を示している。この図7には、同一の電力増幅回路2A(または電力増幅回路2B)の2つの増幅段2A1,2A2(または増幅段2B1,2B2)のnMOSQn1,Q2が例示されている。符号のG1,G2はMOSQn1,Qn2のゲート電極8を示している。2つのnMOSQn1,Qn2のソースS1,S2(上記n+型の半導体領域9)は、p++型の半導体領域11aとp+型の基板1Sを介して接地電位GNDと電気的に接続されるため、p++型の半導体領域11aの抵抗成分R11,R21と、p+型の基板1Sの抵抗成分R12,R22,R3とを持つことになる。通常のCMOS・LSI(Complementary MOS・Large Scale Integrated circuit)用の基板では、その抵抗率が数10Ωcmと高いため、本実施の形態1のような構成とすると、上記の抵抗成分R11,R21,R12,R22,R3が高くなり、nMOSQn1のソースS1からnMOSQn2のソースS2に対して信号利得を持つために、nMOSQn1,Qn2間の干渉が発生し、発振や利得低下が生じる結果、入出力アイソレーションが劣化する。これに対して、本実施の形態1では、基板1Sの抵抗が低いため、上記抵抗成分R12,R22,R3を限りなくゼロ(0)に近づけることができる。言い換えれば、2つのnMOSQn1,Q2のソースS1,S2が共に安定な接地に直結されたのと等価になる。このため、基板1Sで接続されている素子間での干渉が生じないようにできる。例えば最終段の増幅段2A3,2B3のnMOSQn3から1段目および2段目の増幅段2A1,2A2,2B1,2B2や周辺回路3へのクロストークを低減することができる。すなわち、各々の増幅段2A1〜2A3,2B1〜2B3でのnMOSQn1〜Qn3間のアイソレーション特性を向上させることができるので、発振を抑制でき、各々のnMOSQn1〜Qn3の増幅特性の安定性を向上させることができる。これは、増幅段2A1〜2A3,2B1〜2B3間のみならず、他の回路素子同士についても同様のアイソレーション特性を得ることができ、その回路素子間のクロストークを低減することができる。

【0035】

次に、上記図5および図6のnMOSQn1,Qn2、インダクタL1およびコンデンサC1の接続関係と特徴等を説明する。

【0036】

前段のnMOSQn1のソース用のn+型の半導体領域9と接続されたプラグPL1は、第1層配線M11と電気的に接続されている。このnMOSQn1のゲート電極8は、プラグPL2および第1層配線M12(M)を介して第2層配線M21(M)と電気的に接続されている。第2層配線M21はnMISQn1の入力用の配線である。また、このnMOSQn1のドレイン用のn+型の半導体領域11は、プラグPL3を通じて第1層配線M13(M)と電気的に接続されている。この第1層配線M13は、インダクタL1の一端と電気的に接続されている。

【0037】

このインダクタL1は、例えばスパイラル状の第2層配線M22で形成されている。このインダクタL1の外周は、シールド用の第1層配線M14、第2層配線M23、プラグPL4およびp++型の半導体領域11bにより取り囲まれている。シールド用の第1層配線M14、第2層配線M23、プラグPL4およびp++型の半導体領域11bは、互いに電気的に接続されており(インダクタL1とは絶縁されている)、p++型の半導体領域11bを通じて低抵抗な基板1Sと電気的に接続されて接地電位GNDに設定されている。これにより、インダクタL1で発生した磁界が外部に漏れるのを抑制または防止できる。また、インダクタL1とその外部のnMOSQn等とのカップリングを抑制または防止できるので、外部からのクロストークの影響を抑制または防止できる。このインダクタL1の他端は、第2層配線M24(M)を通じてコンデンサC1の上部電極C1aと電気的に接続されている。

【0038】

コンデンサC1の上部電極C1aの下層の配線層には、絶縁膜を挟んで上部電極C1aと対向するように下部電極C1bが設けられている。この下部電極C1bは、プラグPL5を通じてp++型の半導体領域11cと電気的に接続され、さらにp++型の半導体領域11cを通じて低抵抗なp+型の基板1Sと電気的に接続されている。このコンデンサC1の外周も、シールド用の第1層配線M15、第2層配線M25、プラグPL6およびp++型の半導体領域11dにより取り囲まれている。シールド用の第1層配線M15、第2層配線M25、プラグPL6およびp++型の半導体領域11dは、互いに電気的に接続されており(コンデンサC1とは絶縁されている)、p++型の半導体領域11dを通じて低抵抗な基板1Sと電気的に接続されて接地電位GNDに設定されている。これにより、コンデンサC1とその外部のnMOSQn等とのカップリングを抑制または防止できるので、外部からのクロストークの影響を抑制または防止できる。したがって、基板1S上のコンデンサC1のQ値を高く設定することができる。このコンデンサC1の上部電極C1aは、第2層配線M26(M)を通じてnMOSQn2のゲート電極8と電気的に接続されている。なお、プラグPL1〜PL6は、例えばタングステン等のようなメタルで形成されている。また、第1層配線M11〜M15および第2層配線M21〜M26は、例えばアルミニウム(Al)または銅(Cu)を主配線材料とするメタルで形成されている。また、上記p++型の半導体領域11b〜11dは、上記p++型の半導体領域11aの形成工程時に同時に形成されている。

【0039】

次に、図8は上記ICチップ1Cをモジュール基板MCBに搭載したRFパワーモジュールPMの一例の全体平面図を示し、図9は図8のパワーモジュールPMの左右方向に沿って切断した面の断面図を示している。また、図10は、図8および図9のパワーモジュールの回路図を示している。なお、図8では、モジュール基板MCBのチップ搭載面が見えるように封止部材を取り除いて示す。

【0040】

ICチップ1Cは、基板1Sの裏面をモジュール基板MCBの主面に向けた状態で、モジュール基板MCBの主面に形成されたキャビティCBTと称する窪み内に収められた状態でモジュール基板MCBの主面上に搭載されている。ICチップ1Cは、モジュール基板MCBの主面の中央よりも若干入力(図8の左側)寄りに配置されており、モジュール基板MCBの主面の出力側の領域の方が入力側の領域よりも広くなっている。これにより,RFパワーモジュールPMのモジュール基板MCBに配置された出力用の整合回路を低損失に設計することができるので、RFパワーモジュールPAの出力損失を低減でき、高い出力を引き出すことが可能となっている。

【0041】

ICチップ1CのボンディングパッドPin,Poutは、ボンディングワイヤBWを通じてモジュール基板MCBの主面の伝送線路15a(15a1〜15a5),15b(15b1〜15b5),15cと電気的に接続されている。1段目の増幅段2A1,2B1のゲート電極(入力)にボンディングワイヤBWを通じて接続された伝送線路15a1,15b1は、それぞれコンデンサCm1,Cm2を介して入力端子17a,17bと電気的に接続されている。1段目の増幅段2A1,2B1のドレイン(出力)にボンディングワイヤBWを通じて電気的に接続された伝送線路15a2,15b2は、それぞれ高電位側の電源端子18a1,18b1と電気的に接続されてとともに、それぞれ電源端子18a1,18b1の近傍に配置されたコンデンサCm3,Cm4を介して接地電位GNDと電気的に接続されている。2段目の増幅段2A2,2B2のドレイン(出力)にボンディングワイヤBWを通じて電気的に接続された伝送線路15a3,15b3は、それぞれ高電位側の電源端子18a2,18b2と電気的に接続されてとともに、それぞれ電源端子18a2,18b2の近傍に配置されたコンデンサCm5,Cm6を介して接地電位GNDと電気的に接続されている。最終段目の増幅段2A3,2B3のドレイン(出力)にボンディングワイヤBWを通じて電気的に接続された伝送線路15a4,15b4は、それぞれ高電位側の電源端子18a3,18b3と電気的に接続されてとともに、それぞれ電源端子18a3,18b3の近傍に配置されたコンデンサCm7,Cm8を介して接地電位GNDと電気的に接続されている。さらに、最終段目の増幅段2A3,2B3のドレイン(出力)にボンディングワイヤBWを通じて電気的に接続された伝送線路15a5,15b5は、それぞれコンデンサCm9,Cm10を介して出力端子19a,19bと電気的に接続されているとともに、それぞれの線路途中に配置されたコンデンサCm11,Cm12を介して接地電位GNDと電気的に接続されている。周辺回路3の制御用のボンディングパッドPinにボンディングワイヤを通じて電気的に接続された伝送線路15cは、制御端子20と電気的に接続されている。なお、上記ボンディングワイヤBWは、例えば金(Au)等の細線からなり、インダクタとしての機能を有している。また、伝送線路15a,15bもインピーダンス整合用のインダクタとしての機能を有している。上記コンデンサCm1〜Cm12は、インピーダンス整合用のコンデンサとしての機能を有しており、チップ部品で構成されている。

【0042】

一方、ICチップ1Cの裏面の上記電極12は、モジュール基板MCBのキャビティCBT底面のチップ搭載用の電極21と接合されている。この電極21は、複数のサーマルビア22内の導体を通じてモジュール基板MCBの裏面の電極23Gと電気的かつ熱的に接合されている。この電極23Gには基準電位(例えば接地電位GNDで0V程度)が供給される。すなわち、モジュール基板MCBの裏面の電極23Gに供給された基準電位は、サーマルビア22および電極21を通じて低抵抗な基板1Sに供給されるようになっている。また、逆にICチップ1Cの動作時に発生した熱は、基板1Sの裏面から電極21およびサーマルビア22を通じてモジュール基板MCBの裏面の電極23Gに伝わり放散されるようになっている。モジュール基板MCBの裏面の外周近傍の電極23Sは、信号用の電極を示している。なお、モジュール基板MCBは、複数枚の絶縁体板を積層して一体化した多層配線構造を有している。この絶縁体板は、例えばミリ波域まで誘電損失の少ないアルミナ(酸化アルミニウム、Al2O3、比誘電率=9〜9.7)等のようなセラミックからなるが、これに限定されるものではなく種々変更可能であり、例えばガラスエポキシ樹脂等を用いても良い。

【0043】

次に、図11は、本実施の形態1のRFパワーモジュールPMを用いたデジタル携帯電話機システムDPSの一例を示している。図11の符号ANTは信号電波の送受信用のアンテナ、符号25はフロントエンド・モジュール、符号26は音声信号をベースバンド信号に変換したり、受信信号を音声信号に変換したり、変調方式切換信号やバンド切換信号を生成したりする前記ベースバンド回路、符号27は受信信号をダウンコンバートして復調しベースバンド信号を生成したり送信信号を変調したりする変復調用回路、FLT1,FLT2は受信信号からノイズや妨害波を除去するフィルタである。フィルタFLT1はGSM用、フィルタFLT2はDCS用である。ベースバンド回路26は、DSP(Digital Signal Processor)やマイクロプロセッサ、半導体メモリ等の複数の半導体集積回路で構成されている。フロントエンド・モジュール25は、インピーダンス整合回路MN1,MN2、ロウパスフィルタLPF1,LPF2、スイッチ回路28a,28b、コンデンサC5,C6および分波器29を有している。インピーダンス整合回路MN1,MN2は、RFパワーモジュールPMの送信出力端子に接続されてインピーダンスの整合を行う回路、ロウパスフィルタLPF1,LPF2は高調波を減衰させる回路、スイッチ回路28a,28bは送受信切り換え用のスイッチ回路、コンデンサC5,C6は受信信号から直流成分をカットする素子、分波器29は、GSM900帯の信号と、DCS1800帯の信号とを分波する回路であり、これら回路および素子は1つの配線基板上に搭載されてモジュールとされている。なお、スイッチ回路28a,28bの切換信号CNT1,CNT2は上記ベースバンド回路26から供給される。

【0044】

また、図12は、上記図11のデジタル携帯電話機システムDPSでのRFパワーモジュールPMの実装例を示している。マザーボード30は、例えば多層配線構造を有するプリント配線基板等からなり、その主面上には、RFパワーモジュールPMと、その他に複数のチップ部品31が搭載されている。RFパワーモジュールPMは、上記モジュール基板MCBの裏面の電極23G,23S等をマザーボード30の主面に向けた状態でマザーボード30上に搭載されている。こRFのパワーモジュールPMの電極23G,23S等は、半田等のような接合材32を介してそれぞれマザーボード30の配線パターンと接続されている。なお、RFパワーモジュールPMのモジュール基板MCBの主面は、例えばシリコーンゴム等からなる封止部材33により覆われており、これによりモジュール基板MCBの主面のICチップ1C等が封止されている。

【0045】

(実施の形態2)

本実施の形態2では、ICチップの同一系統の隣接する増幅段の出力用のボンディングパッド間に接地用のボンディングパッドを配置した場合の一例を説明する。

【0046】

図13は、本実施の形態2のICチップ1Cの全体平面図の一例を示している。本実施の形態2では、ICチップ1C内の電力増幅回路2A,2Bの各々において、隣接する複数の増幅段2A1〜2A3,2B1〜2B3の出力用のボンディングパッドPout間に、接地用のボンディングパッドPgが配置されている。接地用のボンディングパッドPgは、ICチップ1Cに基準電位(例えば接地電位GNDで0V)を供給するパッドである。これにより、信号増幅後の次段増幅素子から前段増幅素子への輻射による信号帰還を低減できるので、発振の抑制や増幅特性の安定化を図ることができる。

【0047】

また、図14は、図13のICチップ1Cをモジュール基板MCBに搭載してRFパワーモジュールPMを構成した一例の全体平面図を示している。この図14でも、モジュール基板MCBのチップ搭載面が見えるように封止部材を取り除いて示す。上記接地用のボンディングパッドPgは、ボンディングワイヤBWを介してモジュール基板MCBの接地端子35と電気的に接続されている。接地端子35には、基準電位(例えば接地電位GNDで0V)が供給される。このような構成とすることにより、RFパワーモジュールPMの動作時に空間に輻射された電力を、ボンディングパッドPgに電気的に接続され接地状態とされるボンディングワイヤBWにより吸収され大幅に減衰させることができるので、発振の抑制や増幅特性の安定化を図ることができる。これ以外は前記実施の形態1と同じなので説明を省略する。

【0048】

(実施の形態3)

本実施の形態3では、ICチップの同一系統の隣接する増幅段の入力用および出力用のボンディングパッドの配置の変形例について説明する。

【0049】

図15は、本実施の形態3のICチップ1Cの全体平面図の一例を示している。本実施の形態3では、ICチップ1C内の電力増幅回路2A,2Bの各々において、隣接する複数の増幅段2A1〜2A3,2B1〜2B3の入力用および出力用のボンディングパッドPin,Poutが180度反転するように配置されている。図15の例では、2段目の増幅段2A2,2B2の出力用のボンディングパッドPoutがICチップ1Cの中央よりに配置され、入力用のボンディングパッドPinがICチップ1Cの辺の近傍に配置されている。このような構成では、互いに隣接する増幅段2A1〜2A3,2B1〜2B3の入力用のボンディングパッドPinと、出力用のボンディングパッドPoutとを結ぶ段間の配線Mが屈曲せずにほぼ直線的に延在されている。このような構成とすることにより、段間の配線Mを短くすることができ、また、前記実施の形態1,2の場合よりも段間の配線Mおよび段間の整合回路2AM2,2AM3,2BM2,2BM3を次段の増幅段の出力用のボンディングパッドPoutから遠ざけることができるので、次段の増幅段から段間の配線Mや段間の整合回路2AM2,2AM3,2BM2,2BM3へのクロストークを低減できる。このため、発振の抑制や増幅特性の安定化を図ることができる。

【0050】

また、図16は、図15のICチップ1Cをモジュール基板MCBに搭載してパワーモジュールPMを構成した一例の全体平面図を示している。この図16でも、モジュール基板MCBのチップ搭載面が見えるように封止部材を取り除いて示す。上記のように本実施の形態3では、2段目の増幅段2A2,2B2の出力用のボンディングパッドPoutがICチップ1Cの中央より配置されているので、その2段目の増幅段2A2,2B2の出力用のボンディングパッドPoutと、モジュール基板MCBの電源供給用の伝送線路15a3,15b3とを結ぶ電源供給用のボンディングワイヤBWの長さが、他のボンディングワイヤBWよりも長くなっている。このため、2段目の増幅段2A2,2B2への電源ラインのインダクタンス成分をボンディングワイヤBWにより増やすことができるので、その分、モジュール基板MCB上の電源用の伝送線路15a3,15b3の長さを前記実施の形態1,2の場合よりも短くすることができる。したがって、RFパワーモジュールPMの全体寸法の小型化を推進することが可能となる。これ以外は前記実施の形態1と同じなので説明を省略する。

【0051】

(実施の形態4)

本実施の形態4では、ICチップの異なる系統の電力増幅回路の配置を逆向きにした例について説明する。

【0052】

図17は、本実施の形態4のICチップ1Cの全体平面図の一例を示している。本実施の形態4では、ICチップ1C内の異なる系統の電力増幅回路2A,2Bの入出力方向の向きが逆向きになるように配置されている。特に、異なる系統の電力増幅回路2A,2Bの最終段の増幅段2A3,2B3が、互いに点対称になるように、ICチップ1Cの対角に位置する端部近傍に配置されている。これにより、異なる系統の電力増幅回路2A,2Bの特に最終段の増幅段2A3,2B3の間の距離を長くすることができるので、前記実施の形態1と同様に、例えば動作している電力増幅回路から動作していない電力増幅回路へのクロストーク(輻射あるいは干渉)を抑制することができ、また、動作していない電力増幅回路からの不要な出力発生を抑制することができる等、系統の異なる電力増幅回路2A,2Bを同一のICチップ1Cに設けても、電力増幅回路2A,2B間のクロスバンドアイソレーション特性を向上させることができる。これ以外は前記実施の形態1と同じなので説明を省略する。

【0053】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0054】

例えば前記実施の形態1〜4では、GSM900とGSM1800の2つの周波数帯の電波を取り扱うことが可能なデュアルバンド方式に適用した場合について説明したが、これに限定されるものではなく、例えばGSM900、GSM1800およびGSM1900との3つの周波数帯の電波を取り扱うことが可能なトリプルバンド方式に適用しても良い。また、800MHz帯、850MHz帯でも対応できる。

【0055】

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野であるデジタル携帯電話機システムに適用した場合について説明したが、それに限定されるものではなく、例えば通信機能を有するPDA(Personal Digital Assistants)等のような移動体情報処理装置や通信機能を有するパーソナルコンピュータ等のような情報処理装置にも適用できる。

【産業上の利用可能性】

【0056】

本発明の半導体装置は、複数系統の電力増幅回路を有する半導体装置に適用できる。

【符号の説明】

【0057】

1C ICチップ(半導体チップ)

1S 半導体基板

1EP エピタキシャル層

2A,2B 電力増幅回路

2A1〜2A3,2B1〜2B3 増幅段

2AM1〜2AM3,2BM1〜2BM3 整合回路

3 周辺回路

3A 制御回路

3A1 電源制御回路

3A2 バイアス電圧生成回路

3B バイアス回路

4a,4b 入力端子

5a,5b 出力端子

7 ゲート絶縁膜

8 ゲート電極

9 n+型の半導体領域

10a n−型の半導体領域

10b n+型の半導体領域

11a〜11d p++型の半導体領域

12 電極

15a,15a1〜15a5 伝送線路

15b,15b1〜15b5 伝送線路

15c 伝送線路

17a、17b 入力端子

18a1〜18a3 電源端子

18b1〜18b3 電源端子

19a,19b 出力端子

20 制御端子

21 電極

22 サーマルビア

23G 電極

23S 電極

25 フロントエンド・モジュール

26 ベースバンド回路

27 変復調用回路

28a,28b スイッチ回路

29 分波器

30 マザーボード

31 チップ部品

32 接合材

33 封止部材

35 接地端子

Qn,Qn1〜Qn3 nチャネル型のMOS・FET

Pin,Pout ボンディングパッド

Pg ボンディングパッド

R1,R2 抵抗

L1 インダクタ(受動素子)

C1 コンデンサ(受動素子)

Cm1〜Cm12 コンデンサ

C5,C6 コンデンサ

C1a 上部電極

C1b 下部電極

PL1〜PL6 プラグ

M,Mc 配線

M11〜M15 第1層配線

M21〜M26 第2層配線

PM RFパワーモジュール

MCB モジュール基板(配線基板)

CBT キャビティ

BW ボンディングワイヤ

DPS デジタル携帯電話機システム

ANT アンテナ

FLT1,FLT2 フィルタ

LPF1,LPF2 ロウパスフィルタ

MN1,MN2 インピーダンス整合回路

【技術分野】

【0001】

本発明は、半導体装置技術に関し、特に、RF(Radio Frequency)パワーモジュールに適用して有効な技術に関するものである。

【背景技術】

【0002】

本発明者が検討したRFパワーモジュールは、例えば携帯電話機等のような通信機器に用いられる信号増幅用の電子部品であり、信号増幅用のトランジスタを有する複数の半導体チップやチップ部品等をモジュール基板上に実装することで組み立てられている。各半導体チップとモジュール基板とは、ボンディングワイヤを通じて電気的に接続されている。また、チップ部品もその端子をはんだ付けによりモジュール基板のパッドに接続することでモジュール基板と電気的に接続されている。

【0003】

なお、例えば特開2000−332551号公報には、デュアルバンドシステム用の高周波電力増幅器のバイアス回路およびバイアススイッチ回路をHBT(Heterojunction Bipolar Transistor)で形成する構成が開示されている(特許文献1参照)。

【0004】

また、例えば特開2001−141756号公報には、デュアルバンドシステム用の高周波部品において、2つの出力間の干渉を防ぐため、出力用のマイクロストリップライン間に複数のGND線路を設ける構成が開示されている(特許文献2参照)。

【0005】

また、例えば特開2001−345400号公報には、デュアルバンドのパワーモジュールで2つの出力間の干渉を防ぐために、半導体チップと配線基板との双方の出力パッド間にそれぞれグランド用のパッドを設け、ワイヤボンディングする技術が開示されている(特許文献3参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−332551号公報

【特許文献2】特開2001−141756号公報

【特許文献3】特開2001−345400号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところが、上記RFパワーモジュールにおいては、小型化が急速に進められており、信頼性や性能等のような特性の低下を招くことなく、如何にして小型化するかが重要な課題となっている。

【0008】

本発明の目的は、半導体装置を小型にすることのできる技術を提供することにある。

【0009】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0011】

本発明は、高周波電力増幅回路の複数段の増幅回路の全段を、横型の電界効果トランジスタで形成し、シリコン系の半導体基板を有する同一の半導体チップに設けたものである。

【発明の効果】

【0012】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0013】

すなわち、高周波電力増幅回路の複数段の増幅回路の全段を、横型の電界効果トランジスタで形成し、シリコン系の半導体基板を有する同一の半導体チップに設けたことにより、半導体装置を小型にすることができる。

【図面の簡単な説明】

【0014】

【図1】本発明の一実施の形態である半導体装置の回路ブロック図である。

【図2】図1の半導体装置の要部回路図である。

【図3】図1の半導体装置の回路配置例を示す半導体チップの全体平面図である。

【図4】距離と漏洩電力との関係を示すグラフ図である。

【図5】図1の半導体装置の半導体チップの要部平面図である。

【図6】図5の半導体チップの要部断面図である。

【図7】図5の半導体チップの増幅段の等価回路の回路図である。

【図8】図5の半導体チップをモジュール基板に搭載したRFパワーモジュールの一例の全体平面図である。

【図9】図8のRFパワーモジュールの断面図である。

【図10】図8のRFパワーモジュールの等価回路の回路図である。

【図11】図8のRFパワーモジュールを用いたデジタル携帯電話機システムの一例の説明図である。

【図12】図11のデジタル携帯電話機システムのRFパワーモジュールの実装例の要部側面図である。

【図13】本発明の他の実施の形態である半導体装置の回路配置例を示す半導体チップの全体平面図である。

【図14】図13の半導体チップをモジュール基板に搭載したRFパワーモジュールの一例の全体平面図である。

【図15】本発明のさらに他の実施の形態である半導体装置の回路配置例を示す半導体チップの全体平面図である。

【図16】図15の半導体チップをモジュール基板に搭載したRFパワーモジュールの一例の全体平面図である。

【図17】本発明のさらに別の実施の形態である半導体装置の回路配置例を示す半導体チップの全体平面図である。

【発明を実施するための形態】

【0015】

本願発明の実施の形態を詳細に説明する前に、本実施の形態における用語の意味を説明すると次の通りである。

1.GSM(Global System for Mobile Communication)は、デジタル携帯電話に使用されている無線通信方式の1つまたは規格をいう。GSMには、使用する電波の周波数帯が3つあり、900MHz帯をGSM900または単にGSM、1800MHz帯をGSM1800またはDCS(Digital Cellular System)1800若しくはPCN、1900MHz帯をGSM1900またはDCS1900若しくはPCS(Personal Communication Services)という。なお、GSM1900は主に北米で使用されている。北米ではその他に850MHz帯のGSM850を使用する場合もある。

2.GMSK変調方式は、音声信号の通信に用いる方式で搬送波の位相を送信データに応じて位相シフトする方式である。また、EDGE変調方式は、データ通信に用いる方式でGMSK変調の位相シフトにさらに振幅シフトを加えた方式である。

【0016】

また、以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。また、本実施の形態では、電界効果トランジスタであるMOS・FET(Metal Oxide Semiconductor・Field Effect Transistor)をMOSと略し、nチャネル型のMOSをnMOSと略す。

【0017】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0018】

(実施の形態1)

本実施の形態1では、例えばGSM方式のネットワークを利用して情報を伝送するデジタル携帯電話に使用されるRF(Radio Frequency)パワーモジュールに本実施の形態1の半導体装置を適用した場合について説明する。

【0019】

図1は、本実施の形態1のRFパワーモジュールを構成する増幅回路用のIC(Integrated circuit)チップ(半導体チップ)1Cの回路ブロック図を示している。この図1には、例えばGSM900とDCS1800との2つの周波数帯を使用可能(デュアルバンド方式)で、それぞれの周波数帯でGMSK(Gaussian filtered Minimum Shift Keying)変調方式とEDGE(Enhanced Data GSM Environment)変調方式との2つの通信方式を使用可能なRFパワーモジュールに使用される増幅回路用のICチップ(半導体チップ)1Cの回路ブロックが例示されている。

【0020】

このICチップ1Cは、GSM900用の電力増幅回路2Aと、DCS1800用の電力増幅回路2Bと、それら電力増幅回路2A,2Bの増幅動作の制御や補正等を行う周辺回路3とを有している。各電力増幅回路2A,2Bは、それぞれ3つの増幅段2A1〜2A3,2B1〜2B3と、3つの整合回路2AM1〜2AM3,2BM1〜2BM3とを有している。すなわち、ICチップ1Cの入力端子4a,4bは、入力用の整合回路2AM1,2BM1を介して1段目の増幅段2A1,2B1の入力に電気的に接続され、1段目の増幅段2A1,2B1の出力は段間用の整合回路2AM2,2BM2を介して2段目の増幅段2A2,2B2の入力に電気的に接続され、2段目の増幅段2A2,2B2の出力は段間用の整合回路2AM3,2BM3を介して最終段の増幅段2A3,2B3の入力に電気的に接続され、最終段の増幅段2A3,2B3の出力は出力端子5a,5bと電気的に接続されている。このように本実施の形態1では、1つのICチップ1Cの中に、電力増幅回路2A,2Bの全ての増幅段2A1〜2A3,2B1〜2B3が設けられている。一般的には3つの増幅段がそれぞれ別々のICチップに設けられているか、または、1段目および2段目の増幅段が1つのICチップに設けられ、最終段の増幅段はパワーが大きく動作時の発熱が高いことや他の増幅段への信号干渉が大きい等の理由から1段目および2段目の増幅段が設けられたICチップとは別のICチップに設けられている。このため、RFパワーモジュールの小型化が阻害されている。これに対して、本実施の形態1では、1つのICチップ1C内に、電力増幅回路2A,2Bの全ての増幅段2A1〜2A3,2B1〜2B3を設けたことにより、各増幅段2A1〜2A3,2B1〜2B3間の隣接間隔を大幅に短くすることができるので、そのICチップ1Cを内蔵するRFパワーモジュールの大幅な小型化を実現することが可能となっている。

【0021】

上記周辺回路3は、制御回路3Aと、上記増幅段2A1〜2A3,2B1〜2B3にバイアス電圧を印加するバイアス回路3B等を有している。制御回路3Aは、上記電力増幅回路2A,2Bに印加する所望の電圧を発生する回路であり、電源制御回路3A1およびバイアス電圧生成回路3A2を有している。電源制御回路3A1は、上記増幅段2A1〜2A3,2B1〜2B3の各々の出力用のパワーMOSのドレイン端子に印加される第1電源電圧を生成する回路である。また、上記バイアス電圧生成回路3A2は、上記バイアス回路3Bを制御するための第1制御電圧を生成する回路である。本実施の形態1では、電源制御回路3A1が、ICチップ1C外部のベースバンド回路から供給される出力レベル指定信号に基づいて上記第1電源電圧を生成すると、バイアス電圧生成回路3A2が電源制御回路3A1で生成された上記第1電源電圧に基づいて上記第1制御電圧を生成するようになっている。上記ベースバンド回路は、上記出力レベル指定信号を生成する回路である。この出力レベル指定信号は、電力増幅回路2A,2Bの出力レベルを指定する信号で、携帯電話と、基地局との間の距離、すなわち、電波の強弱に応じた出力レベルに基づいて生成されているようになっている。本実施の形態1では、このような周辺回路3を構成する素子も1つのICチップ1C内に設けられている。これにより、インターフェイス部(ICチップ1Cとモジュール基板(配線基板)との間のインターフェイス部およびICチップ1Cとモジュール基板との各々に必要であったインターフェイス部)を大幅に削減でき、ICチップ1Cやモジュール基板の面積を縮小できるので、RFパワーモジュールの大幅な小型化を実現することが可能となっている。

【0022】

次に、図2は、上記電力増幅回路2Aおよび上記バイアス回路3Bの回路構成の一例を示している。なお、上記電力増幅回路2A,2Bおよびその各々のバイアス回路3Bの回路構成は同じなので、ここでは上記電力増幅回路2Aおよび電力増幅回路2A用の回路構成の一例を代表して示す。

【0023】

本実施の形態1の電力増幅回路2Aは、上記3段の増幅段2A1〜2A3として3つのnMOSQn(Qn1,Qn2,Qn3)を順次従属接続した回路構成を有している。この電力増幅回路2Aの出力レベルは、上記バイアス回路3Bおよび電源制御回路3A1から供給される上記第1電源電圧Vdd1によって制御される。ここでは、その第1電源電圧Vdd1が3つのnMOSQn1,Qn2,Qn3の各々のドレイン電極に供給されるようになっている。

【0024】

整合回路2AM1〜2AM3は、インダクタ(受動素子)と、コンデンサ(受動素子)とを有している。インダクタは、配線で形成されており、1段目の増幅段2A1(nMOSQn1)の入力およびそれぞれの段間でのインピーダンス整合をとる機能を有している。また、上記コンデンサは、上記インダクタと各段のnMOSQnの入力との間に接続されており、上記インピーダンス整合の機能と、その他に第1電源電圧Vdd1とゲートバイアス電圧との直流電圧を遮断する機能とを有している。

【0025】

上記バイアス回路3Bは、複数の分圧回路を有している。各分圧回路は、一対の抵抗R1,R2で構成されている。各一対の抵抗R1,R2は、バイアス回路3Bの入力端子4cと、基準電位(例えば接地電位で0V)との間に直列に接続されている。各一対の抵抗R1,R2間を繋ぐ配線部分と、各段のnMOSQn1〜Qn3の入力(ゲート電極)とが電気的に接続されている。このバイアス回路3Bの入力端子4cに上記第1制御電圧または出力レベル制御電圧が入力されると、その電圧が上記一対の抵抗R1,R2で分圧されて所望のゲートバイアス電圧が生成され、そのゲートバイアス電圧が、各々のnMOSQn1〜Qn3のゲート電極に入力されるようになっている。

【0026】

次に、図3は、図1の増幅回路用のICチップ1Cの回路配置の一例を示し、図4は距離と漏洩電力との関係を示すグラフ図を示している。

【0027】

本実施の形態1では、図3に示すように、ICチップ1Cの主面(デバイス形成面)の周辺に電力増幅回路2A,2Bが配置され、その各々の電力増幅回路2A,2Bの間に周辺回路3が配置されている。特に、上記のように電力増幅回路2A,2Bの最終段の増幅段2A3,2B3は、パワーが大きく動作時の発熱が高いことや他の増幅段への信号干渉が大きい(特にここでは取り扱う高周波信号がそれぞれ900MHzと1800MHzというように各々の高調波の位相が逆なので信号間の干渉の問題が大きい)ので、相互間の距離が長くなるように、ICチップ1Cの相対する辺の近傍に配置されている。図4に示すように、2点間の信号伝搬量は概ね距離の2乗に反比例するので、上記のように電力増幅回路2A,2Bを離して配置することにより、例えば動作している電力増幅回路から動作していない電力増幅回路へのクロストーク(輻射あるいは干渉)を抑制することができ、また、動作していない電力増幅回路からの不要な出力発生を抑制することができる等、系統の異なる電力増幅回路2A,2Bを同一のICチップ1Cに設けても、電力増幅回路2A,2B間のクロスバンドアイソレーション特性を向上させることができる。したがって、RFパワーモジュールの動作の信頼性や安定性を向上させることが可能となる。

【0028】

図3中の符号のPinは入力用のボンディングパッド、Poutは出力用のボンディングパッドを示している。各増幅段2A1〜2A3や増幅段2B1〜2B3のボンディングパッドPinは、ICチップ1Cの中央側に配置され、各増幅段2A1〜2A3や増幅段2B1〜2B3のボンディングパッドPoutはICチップ1Cの辺側に配置されている。また、符号のMは入力用、出力用および増幅段間用の配線を示している。増幅段間用の配線Mは屈曲した状態でボンディングパッドPin,Pout間を接続している。また、符号のMcは増幅段2A1〜2A3,2B1〜2B3と周辺回路3を接続する配線を示している。

【0029】

次に、図5は、上記ICチップ1Cの要部平面図を示し、図6は、図5のICチップ1Cの左右方向に沿って切断した箇所の要部断面図を示している。なお、図5は平面図であるが、図面を見易くするために同層のものに同じハッチングを付している。

【0030】

ICチップ1Cを構成する半導体基板(以下、単に基板という)1Sは、例えばp+型のシリコン(Si)単結晶からなり、その抵抗率が、例えば1〜10mΩ・cm程度の低抵抗基板とされている。基板1S上には、例えばp−型のシリコン単結晶からなるエピタキシャル層1EPが形成されている。エピタキシャル層1EPの抵抗率は、上記基板1Sの抵抗率よりも高い。このエピタキシャル層1EPの主面には、上記増幅段2A1〜2A3,2B1〜2B3用のnMOSQnと、上記整合回路2AM1〜2AM3,2BM1〜2BM3用のインダクタL1、高Q(Quality factor)値のコンデンサC1およびストリップ線路が形成されている。ここでは、2段の増幅段のnMOSQn1,Qn2が示されているが、実際には上記のように2系統の1〜3段の全ての増幅段2A1〜2A3,2B1〜2B3が同一の基板1Sに形成されている。また、ここで示したnMOSQnは単位MOSを示しており、実際には、この単位MOSが複数個並列に接続されることで1つの増幅段2A1〜2A3,2B1〜2B3が形成されている。

【0031】

まず、nMOSQnは、例えばLDMOS(Laterally Diffused MOS)等のような横型のMOSで形成されている。nMOSQnの形成領域のエピタキシャル層1EPには、p型のウエルPWLが形成されている。このp型のウエルPWLは、例えばホウ素(B)などの不純物をエピタキシャル層1EPにイオン注入することなどにより形成されている。エピタキシャル層1EPの上記p型のウエルPWL上には、nMOSQnのゲート絶縁膜7が形成されている。このゲート絶縁膜7は、例えば酸化シリコン(SiO2等)からなり、例えば熱酸化法などによって形成されている。このゲート絶縁膜7上には、nMOSQnのゲート電極(入力)8が形成されている。このゲート電極8は、例えば多結晶シリコンとその上に形成された金属シリサイド層(例えばチタンシリサイド層またはコバルトシリサイド層)との積層導体膜で構成されている。nMOSQnのチャネルは、ゲート電極8下のp型のウエルPWLの上部に形成される。

【0032】

このゲート電極8の一方の端部近傍のp型のウエルPWLの領域内には、n+型の半導体領域9が形成されている。このn+型の半導体領域9は、nMOSQnのソースとして機能する領域であり、例えばリン(P)などの不純物をp型のウエルPWLにイオン注入することで形成されている。また、ゲート電極8の他方の端部近傍のエピタキシャル層1EPには、n−型の半導体領域10aが形成されている。そして、ゲート電極8の他方の端部からn−型の半導体領域10aの分だけ離れた箇所には、n+型の半導体領域10bがn−型の半導体領域10aと電気的に接続された状態で形成されている(LDD(Lightly Doped Drain)構造)。このn−型の半導体領域10aおよびn+型の半導体領域10bは、nMOSQnのドレイン(出力)として機能する領域であり、例えばリン(P)などの不純物をp型のウエルPWLにイオン注入することで形成されている。

【0033】

また、本実施の形態1では、各々のnMOSQnの形成領域のエピタキシャル層1EPにp++型の半導体領域11aが上記n+型の半導体領域9,10bと接するように形成されている。このp++型の半導体領域11aは、例えばホウ素(B)が導入されてなり、平面で見ると、nMOSQnを取り囲むように形成され、断面で見ると、エピタキシャル層1EPの主面から基板1Sに達するように形成されている。そして、本実施の形態1では、各nMOSQnのソース用のn+型の半導体領域9が、プラグPL1を通じてp++型の半導体領域11aと電気的に接続され、そのp++型の半導体領域11を通じて低抵抗なp+型の基板1Sと電気的に接続されている。後述のように、基板1Sは、基板1Sの裏面全面にメタルで形成された電極12を介して、ICチップ1Cが実装されるモジュール基板の配線と電気的に接続され、その配線を通じて基準電位(例えば接地電位GNDで0V程度:固定電位)に電気的に接続される。すなわち、基板1Sは、ICチップ1Cに形成された複数のnMOSQnの共通の接地部分とされている。

【0034】

図7は、この様子の等価回路を示している。この図7には、同一の電力増幅回路2A(または電力増幅回路2B)の2つの増幅段2A1,2A2(または増幅段2B1,2B2)のnMOSQn1,Q2が例示されている。符号のG1,G2はMOSQn1,Qn2のゲート電極8を示している。2つのnMOSQn1,Qn2のソースS1,S2(上記n+型の半導体領域9)は、p++型の半導体領域11aとp+型の基板1Sを介して接地電位GNDと電気的に接続されるため、p++型の半導体領域11aの抵抗成分R11,R21と、p+型の基板1Sの抵抗成分R12,R22,R3とを持つことになる。通常のCMOS・LSI(Complementary MOS・Large Scale Integrated circuit)用の基板では、その抵抗率が数10Ωcmと高いため、本実施の形態1のような構成とすると、上記の抵抗成分R11,R21,R12,R22,R3が高くなり、nMOSQn1のソースS1からnMOSQn2のソースS2に対して信号利得を持つために、nMOSQn1,Qn2間の干渉が発生し、発振や利得低下が生じる結果、入出力アイソレーションが劣化する。これに対して、本実施の形態1では、基板1Sの抵抗が低いため、上記抵抗成分R12,R22,R3を限りなくゼロ(0)に近づけることができる。言い換えれば、2つのnMOSQn1,Q2のソースS1,S2が共に安定な接地に直結されたのと等価になる。このため、基板1Sで接続されている素子間での干渉が生じないようにできる。例えば最終段の増幅段2A3,2B3のnMOSQn3から1段目および2段目の増幅段2A1,2A2,2B1,2B2や周辺回路3へのクロストークを低減することができる。すなわち、各々の増幅段2A1〜2A3,2B1〜2B3でのnMOSQn1〜Qn3間のアイソレーション特性を向上させることができるので、発振を抑制でき、各々のnMOSQn1〜Qn3の増幅特性の安定性を向上させることができる。これは、増幅段2A1〜2A3,2B1〜2B3間のみならず、他の回路素子同士についても同様のアイソレーション特性を得ることができ、その回路素子間のクロストークを低減することができる。

【0035】

次に、上記図5および図6のnMOSQn1,Qn2、インダクタL1およびコンデンサC1の接続関係と特徴等を説明する。

【0036】

前段のnMOSQn1のソース用のn+型の半導体領域9と接続されたプラグPL1は、第1層配線M11と電気的に接続されている。このnMOSQn1のゲート電極8は、プラグPL2および第1層配線M12(M)を介して第2層配線M21(M)と電気的に接続されている。第2層配線M21はnMISQn1の入力用の配線である。また、このnMOSQn1のドレイン用のn+型の半導体領域11は、プラグPL3を通じて第1層配線M13(M)と電気的に接続されている。この第1層配線M13は、インダクタL1の一端と電気的に接続されている。

【0037】

このインダクタL1は、例えばスパイラル状の第2層配線M22で形成されている。このインダクタL1の外周は、シールド用の第1層配線M14、第2層配線M23、プラグPL4およびp++型の半導体領域11bにより取り囲まれている。シールド用の第1層配線M14、第2層配線M23、プラグPL4およびp++型の半導体領域11bは、互いに電気的に接続されており(インダクタL1とは絶縁されている)、p++型の半導体領域11bを通じて低抵抗な基板1Sと電気的に接続されて接地電位GNDに設定されている。これにより、インダクタL1で発生した磁界が外部に漏れるのを抑制または防止できる。また、インダクタL1とその外部のnMOSQn等とのカップリングを抑制または防止できるので、外部からのクロストークの影響を抑制または防止できる。このインダクタL1の他端は、第2層配線M24(M)を通じてコンデンサC1の上部電極C1aと電気的に接続されている。

【0038】

コンデンサC1の上部電極C1aの下層の配線層には、絶縁膜を挟んで上部電極C1aと対向するように下部電極C1bが設けられている。この下部電極C1bは、プラグPL5を通じてp++型の半導体領域11cと電気的に接続され、さらにp++型の半導体領域11cを通じて低抵抗なp+型の基板1Sと電気的に接続されている。このコンデンサC1の外周も、シールド用の第1層配線M15、第2層配線M25、プラグPL6およびp++型の半導体領域11dにより取り囲まれている。シールド用の第1層配線M15、第2層配線M25、プラグPL6およびp++型の半導体領域11dは、互いに電気的に接続されており(コンデンサC1とは絶縁されている)、p++型の半導体領域11dを通じて低抵抗な基板1Sと電気的に接続されて接地電位GNDに設定されている。これにより、コンデンサC1とその外部のnMOSQn等とのカップリングを抑制または防止できるので、外部からのクロストークの影響を抑制または防止できる。したがって、基板1S上のコンデンサC1のQ値を高く設定することができる。このコンデンサC1の上部電極C1aは、第2層配線M26(M)を通じてnMOSQn2のゲート電極8と電気的に接続されている。なお、プラグPL1〜PL6は、例えばタングステン等のようなメタルで形成されている。また、第1層配線M11〜M15および第2層配線M21〜M26は、例えばアルミニウム(Al)または銅(Cu)を主配線材料とするメタルで形成されている。また、上記p++型の半導体領域11b〜11dは、上記p++型の半導体領域11aの形成工程時に同時に形成されている。

【0039】

次に、図8は上記ICチップ1Cをモジュール基板MCBに搭載したRFパワーモジュールPMの一例の全体平面図を示し、図9は図8のパワーモジュールPMの左右方向に沿って切断した面の断面図を示している。また、図10は、図8および図9のパワーモジュールの回路図を示している。なお、図8では、モジュール基板MCBのチップ搭載面が見えるように封止部材を取り除いて示す。

【0040】

ICチップ1Cは、基板1Sの裏面をモジュール基板MCBの主面に向けた状態で、モジュール基板MCBの主面に形成されたキャビティCBTと称する窪み内に収められた状態でモジュール基板MCBの主面上に搭載されている。ICチップ1Cは、モジュール基板MCBの主面の中央よりも若干入力(図8の左側)寄りに配置されており、モジュール基板MCBの主面の出力側の領域の方が入力側の領域よりも広くなっている。これにより,RFパワーモジュールPMのモジュール基板MCBに配置された出力用の整合回路を低損失に設計することができるので、RFパワーモジュールPAの出力損失を低減でき、高い出力を引き出すことが可能となっている。

【0041】

ICチップ1CのボンディングパッドPin,Poutは、ボンディングワイヤBWを通じてモジュール基板MCBの主面の伝送線路15a(15a1〜15a5),15b(15b1〜15b5),15cと電気的に接続されている。1段目の増幅段2A1,2B1のゲート電極(入力)にボンディングワイヤBWを通じて接続された伝送線路15a1,15b1は、それぞれコンデンサCm1,Cm2を介して入力端子17a,17bと電気的に接続されている。1段目の増幅段2A1,2B1のドレイン(出力)にボンディングワイヤBWを通じて電気的に接続された伝送線路15a2,15b2は、それぞれ高電位側の電源端子18a1,18b1と電気的に接続されてとともに、それぞれ電源端子18a1,18b1の近傍に配置されたコンデンサCm3,Cm4を介して接地電位GNDと電気的に接続されている。2段目の増幅段2A2,2B2のドレイン(出力)にボンディングワイヤBWを通じて電気的に接続された伝送線路15a3,15b3は、それぞれ高電位側の電源端子18a2,18b2と電気的に接続されてとともに、それぞれ電源端子18a2,18b2の近傍に配置されたコンデンサCm5,Cm6を介して接地電位GNDと電気的に接続されている。最終段目の増幅段2A3,2B3のドレイン(出力)にボンディングワイヤBWを通じて電気的に接続された伝送線路15a4,15b4は、それぞれ高電位側の電源端子18a3,18b3と電気的に接続されてとともに、それぞれ電源端子18a3,18b3の近傍に配置されたコンデンサCm7,Cm8を介して接地電位GNDと電気的に接続されている。さらに、最終段目の増幅段2A3,2B3のドレイン(出力)にボンディングワイヤBWを通じて電気的に接続された伝送線路15a5,15b5は、それぞれコンデンサCm9,Cm10を介して出力端子19a,19bと電気的に接続されているとともに、それぞれの線路途中に配置されたコンデンサCm11,Cm12を介して接地電位GNDと電気的に接続されている。周辺回路3の制御用のボンディングパッドPinにボンディングワイヤを通じて電気的に接続された伝送線路15cは、制御端子20と電気的に接続されている。なお、上記ボンディングワイヤBWは、例えば金(Au)等の細線からなり、インダクタとしての機能を有している。また、伝送線路15a,15bもインピーダンス整合用のインダクタとしての機能を有している。上記コンデンサCm1〜Cm12は、インピーダンス整合用のコンデンサとしての機能を有しており、チップ部品で構成されている。

【0042】

一方、ICチップ1Cの裏面の上記電極12は、モジュール基板MCBのキャビティCBT底面のチップ搭載用の電極21と接合されている。この電極21は、複数のサーマルビア22内の導体を通じてモジュール基板MCBの裏面の電極23Gと電気的かつ熱的に接合されている。この電極23Gには基準電位(例えば接地電位GNDで0V程度)が供給される。すなわち、モジュール基板MCBの裏面の電極23Gに供給された基準電位は、サーマルビア22および電極21を通じて低抵抗な基板1Sに供給されるようになっている。また、逆にICチップ1Cの動作時に発生した熱は、基板1Sの裏面から電極21およびサーマルビア22を通じてモジュール基板MCBの裏面の電極23Gに伝わり放散されるようになっている。モジュール基板MCBの裏面の外周近傍の電極23Sは、信号用の電極を示している。なお、モジュール基板MCBは、複数枚の絶縁体板を積層して一体化した多層配線構造を有している。この絶縁体板は、例えばミリ波域まで誘電損失の少ないアルミナ(酸化アルミニウム、Al2O3、比誘電率=9〜9.7)等のようなセラミックからなるが、これに限定されるものではなく種々変更可能であり、例えばガラスエポキシ樹脂等を用いても良い。

【0043】

次に、図11は、本実施の形態1のRFパワーモジュールPMを用いたデジタル携帯電話機システムDPSの一例を示している。図11の符号ANTは信号電波の送受信用のアンテナ、符号25はフロントエンド・モジュール、符号26は音声信号をベースバンド信号に変換したり、受信信号を音声信号に変換したり、変調方式切換信号やバンド切換信号を生成したりする前記ベースバンド回路、符号27は受信信号をダウンコンバートして復調しベースバンド信号を生成したり送信信号を変調したりする変復調用回路、FLT1,FLT2は受信信号からノイズや妨害波を除去するフィルタである。フィルタFLT1はGSM用、フィルタFLT2はDCS用である。ベースバンド回路26は、DSP(Digital Signal Processor)やマイクロプロセッサ、半導体メモリ等の複数の半導体集積回路で構成されている。フロントエンド・モジュール25は、インピーダンス整合回路MN1,MN2、ロウパスフィルタLPF1,LPF2、スイッチ回路28a,28b、コンデンサC5,C6および分波器29を有している。インピーダンス整合回路MN1,MN2は、RFパワーモジュールPMの送信出力端子に接続されてインピーダンスの整合を行う回路、ロウパスフィルタLPF1,LPF2は高調波を減衰させる回路、スイッチ回路28a,28bは送受信切り換え用のスイッチ回路、コンデンサC5,C6は受信信号から直流成分をカットする素子、分波器29は、GSM900帯の信号と、DCS1800帯の信号とを分波する回路であり、これら回路および素子は1つの配線基板上に搭載されてモジュールとされている。なお、スイッチ回路28a,28bの切換信号CNT1,CNT2は上記ベースバンド回路26から供給される。

【0044】

また、図12は、上記図11のデジタル携帯電話機システムDPSでのRFパワーモジュールPMの実装例を示している。マザーボード30は、例えば多層配線構造を有するプリント配線基板等からなり、その主面上には、RFパワーモジュールPMと、その他に複数のチップ部品31が搭載されている。RFパワーモジュールPMは、上記モジュール基板MCBの裏面の電極23G,23S等をマザーボード30の主面に向けた状態でマザーボード30上に搭載されている。こRFのパワーモジュールPMの電極23G,23S等は、半田等のような接合材32を介してそれぞれマザーボード30の配線パターンと接続されている。なお、RFパワーモジュールPMのモジュール基板MCBの主面は、例えばシリコーンゴム等からなる封止部材33により覆われており、これによりモジュール基板MCBの主面のICチップ1C等が封止されている。

【0045】

(実施の形態2)

本実施の形態2では、ICチップの同一系統の隣接する増幅段の出力用のボンディングパッド間に接地用のボンディングパッドを配置した場合の一例を説明する。

【0046】

図13は、本実施の形態2のICチップ1Cの全体平面図の一例を示している。本実施の形態2では、ICチップ1C内の電力増幅回路2A,2Bの各々において、隣接する複数の増幅段2A1〜2A3,2B1〜2B3の出力用のボンディングパッドPout間に、接地用のボンディングパッドPgが配置されている。接地用のボンディングパッドPgは、ICチップ1Cに基準電位(例えば接地電位GNDで0V)を供給するパッドである。これにより、信号増幅後の次段増幅素子から前段増幅素子への輻射による信号帰還を低減できるので、発振の抑制や増幅特性の安定化を図ることができる。

【0047】

また、図14は、図13のICチップ1Cをモジュール基板MCBに搭載してRFパワーモジュールPMを構成した一例の全体平面図を示している。この図14でも、モジュール基板MCBのチップ搭載面が見えるように封止部材を取り除いて示す。上記接地用のボンディングパッドPgは、ボンディングワイヤBWを介してモジュール基板MCBの接地端子35と電気的に接続されている。接地端子35には、基準電位(例えば接地電位GNDで0V)が供給される。このような構成とすることにより、RFパワーモジュールPMの動作時に空間に輻射された電力を、ボンディングパッドPgに電気的に接続され接地状態とされるボンディングワイヤBWにより吸収され大幅に減衰させることができるので、発振の抑制や増幅特性の安定化を図ることができる。これ以外は前記実施の形態1と同じなので説明を省略する。

【0048】

(実施の形態3)

本実施の形態3では、ICチップの同一系統の隣接する増幅段の入力用および出力用のボンディングパッドの配置の変形例について説明する。

【0049】

図15は、本実施の形態3のICチップ1Cの全体平面図の一例を示している。本実施の形態3では、ICチップ1C内の電力増幅回路2A,2Bの各々において、隣接する複数の増幅段2A1〜2A3,2B1〜2B3の入力用および出力用のボンディングパッドPin,Poutが180度反転するように配置されている。図15の例では、2段目の増幅段2A2,2B2の出力用のボンディングパッドPoutがICチップ1Cの中央よりに配置され、入力用のボンディングパッドPinがICチップ1Cの辺の近傍に配置されている。このような構成では、互いに隣接する増幅段2A1〜2A3,2B1〜2B3の入力用のボンディングパッドPinと、出力用のボンディングパッドPoutとを結ぶ段間の配線Mが屈曲せずにほぼ直線的に延在されている。このような構成とすることにより、段間の配線Mを短くすることができ、また、前記実施の形態1,2の場合よりも段間の配線Mおよび段間の整合回路2AM2,2AM3,2BM2,2BM3を次段の増幅段の出力用のボンディングパッドPoutから遠ざけることができるので、次段の増幅段から段間の配線Mや段間の整合回路2AM2,2AM3,2BM2,2BM3へのクロストークを低減できる。このため、発振の抑制や増幅特性の安定化を図ることができる。

【0050】

また、図16は、図15のICチップ1Cをモジュール基板MCBに搭載してパワーモジュールPMを構成した一例の全体平面図を示している。この図16でも、モジュール基板MCBのチップ搭載面が見えるように封止部材を取り除いて示す。上記のように本実施の形態3では、2段目の増幅段2A2,2B2の出力用のボンディングパッドPoutがICチップ1Cの中央より配置されているので、その2段目の増幅段2A2,2B2の出力用のボンディングパッドPoutと、モジュール基板MCBの電源供給用の伝送線路15a3,15b3とを結ぶ電源供給用のボンディングワイヤBWの長さが、他のボンディングワイヤBWよりも長くなっている。このため、2段目の増幅段2A2,2B2への電源ラインのインダクタンス成分をボンディングワイヤBWにより増やすことができるので、その分、モジュール基板MCB上の電源用の伝送線路15a3,15b3の長さを前記実施の形態1,2の場合よりも短くすることができる。したがって、RFパワーモジュールPMの全体寸法の小型化を推進することが可能となる。これ以外は前記実施の形態1と同じなので説明を省略する。

【0051】

(実施の形態4)

本実施の形態4では、ICチップの異なる系統の電力増幅回路の配置を逆向きにした例について説明する。

【0052】

図17は、本実施の形態4のICチップ1Cの全体平面図の一例を示している。本実施の形態4では、ICチップ1C内の異なる系統の電力増幅回路2A,2Bの入出力方向の向きが逆向きになるように配置されている。特に、異なる系統の電力増幅回路2A,2Bの最終段の増幅段2A3,2B3が、互いに点対称になるように、ICチップ1Cの対角に位置する端部近傍に配置されている。これにより、異なる系統の電力増幅回路2A,2Bの特に最終段の増幅段2A3,2B3の間の距離を長くすることができるので、前記実施の形態1と同様に、例えば動作している電力増幅回路から動作していない電力増幅回路へのクロストーク(輻射あるいは干渉)を抑制することができ、また、動作していない電力増幅回路からの不要な出力発生を抑制することができる等、系統の異なる電力増幅回路2A,2Bを同一のICチップ1Cに設けても、電力増幅回路2A,2B間のクロスバンドアイソレーション特性を向上させることができる。これ以外は前記実施の形態1と同じなので説明を省略する。

【0053】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0054】

例えば前記実施の形態1〜4では、GSM900とGSM1800の2つの周波数帯の電波を取り扱うことが可能なデュアルバンド方式に適用した場合について説明したが、これに限定されるものではなく、例えばGSM900、GSM1800およびGSM1900との3つの周波数帯の電波を取り扱うことが可能なトリプルバンド方式に適用しても良い。また、800MHz帯、850MHz帯でも対応できる。

【0055】

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野であるデジタル携帯電話機システムに適用した場合について説明したが、それに限定されるものではなく、例えば通信機能を有するPDA(Personal Digital Assistants)等のような移動体情報処理装置や通信機能を有するパーソナルコンピュータ等のような情報処理装置にも適用できる。

【産業上の利用可能性】

【0056】

本発明の半導体装置は、複数系統の電力増幅回路を有する半導体装置に適用できる。

【符号の説明】

【0057】

1C ICチップ(半導体チップ)

1S 半導体基板

1EP エピタキシャル層

2A,2B 電力増幅回路

2A1〜2A3,2B1〜2B3 増幅段

2AM1〜2AM3,2BM1〜2BM3 整合回路

3 周辺回路

3A 制御回路

3A1 電源制御回路

3A2 バイアス電圧生成回路

3B バイアス回路

4a,4b 入力端子

5a,5b 出力端子

7 ゲート絶縁膜

8 ゲート電極

9 n+型の半導体領域

10a n−型の半導体領域

10b n+型の半導体領域

11a〜11d p++型の半導体領域

12 電極

15a,15a1〜15a5 伝送線路

15b,15b1〜15b5 伝送線路

15c 伝送線路

17a、17b 入力端子

18a1〜18a3 電源端子

18b1〜18b3 電源端子

19a,19b 出力端子

20 制御端子

21 電極

22 サーマルビア

23G 電極

23S 電極

25 フロントエンド・モジュール

26 ベースバンド回路

27 変復調用回路

28a,28b スイッチ回路

29 分波器

30 マザーボード

31 チップ部品

32 接合材

33 封止部材

35 接地端子

Qn,Qn1〜Qn3 nチャネル型のMOS・FET

Pin,Pout ボンディングパッド

Pg ボンディングパッド

R1,R2 抵抗

L1 インダクタ(受動素子)

C1 コンデンサ(受動素子)

Cm1〜Cm12 コンデンサ

C5,C6 コンデンサ

C1a 上部電極

C1b 下部電極

PL1〜PL6 プラグ

M,Mc 配線

M11〜M15 第1層配線

M21〜M26 第2層配線

PM RFパワーモジュール

MCB モジュール基板(配線基板)

CBT キャビティ

BW ボンディングワイヤ

DPS デジタル携帯電話機システム

ANT アンテナ

FLT1,FLT2 フィルタ

LPF1,LPF2 ロウパスフィルタ

MN1,MN2 インピーダンス整合回路

【特許請求の範囲】

【請求項1】

複数の増幅回路を多段接続して構成される電力増幅回路を有する半導体装置であって、

前記複数の増幅回路の初段から最終段は、シリコンからなる同一の半導体基板上に形成され、

前記複数の増幅回路は電界効果トランジスタから構成され、

前記電界効果トランジスタのドレイン電極およびソース電極は、それぞれ前記半導体基板の主面および裏面に形成され、

複数の前記電界効果トランジスタの各ソース電極は前記半導体基板の裏面で電気的に接続され、

前記ソース電極は固定電位に接続され、

前記シリコンからなる前記半導体基板の抵抗率が10mΩ・cmより小さいことを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置において、前記電力増幅回路は、800MHz帯、900MHz帯、1800MHz帯または1900MHz帯で動作することを特徴とする半導体装置。

【請求項3】

請求項1記載の半導体装置において、前記半導体基板は配線基板に実装され、前記電界効果トランジスタのソースは、前記配線基板の固定電位に電気的に接続されていることを特徴とする半導体装置。

【請求項4】

請求項1記載の半導体装置において、前記半導体基板には整合回路用の受動素子も設けられていることを特徴とする半導体装置。

【請求項5】

請求項4記載の半導体装置において、前記半導体基板は配線基板に実装され、前記配線基板には前記増幅回路の入力および出力用の整合回路が設けられていることを特徴とする半導体装置。

【請求項6】

請求項4記載の半導体装置において、前記整合回路用の受動素子の周囲にシールド層を設け、そのシールド層が半導体領域を通じて前記半導体基板に電気的に接続され、前記半導体基板の裏面の電極を通じて固定電位に電気的に接続されていることを特徴とする半導体装置。

【請求項7】

請求項1記載の半導体装置において、前記半導体基板には、前記増幅回路に用いるバイアス回路および制御回路が設けられていることを特徴とする半導体装置。

【請求項8】

請求項1記載の半導体装置は、複数の周波数帯の高周波信号に対応可能なマルチバンド方式を採用していることを特徴とする半導体装置。

【請求項9】

請求項1記載の半導体装置において、前記増幅回路は3つの増幅段を持つことを特徴とする半導体装置。

【請求項1】

複数の増幅回路を多段接続して構成される電力増幅回路を有する半導体装置であって、

前記複数の増幅回路の初段から最終段は、シリコンからなる同一の半導体基板上に形成され、

前記複数の増幅回路は電界効果トランジスタから構成され、

前記電界効果トランジスタのドレイン電極およびソース電極は、それぞれ前記半導体基板の主面および裏面に形成され、

複数の前記電界効果トランジスタの各ソース電極は前記半導体基板の裏面で電気的に接続され、

前記ソース電極は固定電位に接続され、

前記シリコンからなる前記半導体基板の抵抗率が10mΩ・cmより小さいことを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置において、前記電力増幅回路は、800MHz帯、900MHz帯、1800MHz帯または1900MHz帯で動作することを特徴とする半導体装置。

【請求項3】

請求項1記載の半導体装置において、前記半導体基板は配線基板に実装され、前記電界効果トランジスタのソースは、前記配線基板の固定電位に電気的に接続されていることを特徴とする半導体装置。

【請求項4】

請求項1記載の半導体装置において、前記半導体基板には整合回路用の受動素子も設けられていることを特徴とする半導体装置。

【請求項5】

請求項4記載の半導体装置において、前記半導体基板は配線基板に実装され、前記配線基板には前記増幅回路の入力および出力用の整合回路が設けられていることを特徴とする半導体装置。

【請求項6】

請求項4記載の半導体装置において、前記整合回路用の受動素子の周囲にシールド層を設け、そのシールド層が半導体領域を通じて前記半導体基板に電気的に接続され、前記半導体基板の裏面の電極を通じて固定電位に電気的に接続されていることを特徴とする半導体装置。

【請求項7】

請求項1記載の半導体装置において、前記半導体基板には、前記増幅回路に用いるバイアス回路および制御回路が設けられていることを特徴とする半導体装置。

【請求項8】

請求項1記載の半導体装置は、複数の周波数帯の高周波信号に対応可能なマルチバンド方式を採用していることを特徴とする半導体装置。

【請求項9】

請求項1記載の半導体装置において、前記増幅回路は3つの増幅段を持つことを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2010−226120(P2010−226120A)

【公開日】平成22年10月7日(2010.10.7)

【国際特許分類】

【出願番号】特願2010−106357(P2010−106357)

【出願日】平成22年5月6日(2010.5.6)

【分割の表示】特願2005−513029(P2005−513029)の分割

【原出願日】平成16年8月6日(2004.8.6)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.GSM

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年10月7日(2010.10.7)

【国際特許分類】

【出願日】平成22年5月6日(2010.5.6)

【分割の表示】特願2005−513029(P2005−513029)の分割

【原出願日】平成16年8月6日(2004.8.6)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.GSM

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]