半導体装置

【課題】層構造の設計指針を得ることにより、窒化物半導体チャネル層としてInN(あるいはInGaN、InAlN、InAlGaN)を用いた、高性能のInN系ヘテロ構造電界効果トランジスタ(チャネル層がInN系であるヘテロ構造電界効果トランジスタ)を実現させること。

【解決手段】窒化物チャネル層半導体1の上に窒化物障壁層半導体2を重ねてなるヘテロ構造上に、ソース電極3、ゲート電極4、ドレイン電極5が配置されてなるInN系ヘテロ構造電界効果トランジスタにおいて、窒化物チャネル層半導体1としてInN、InGaN、InAlN、あるいはInAlGaNが用いられ、窒化物障壁層半導体2としてInXAl1−XN(ここに、0<X≦0.66である)が用いられていることを特徴とするInN系ヘテロ構造電界効果トランジスタを構成する。

【解決手段】窒化物チャネル層半導体1の上に窒化物障壁層半導体2を重ねてなるヘテロ構造上に、ソース電極3、ゲート電極4、ドレイン電極5が配置されてなるInN系ヘテロ構造電界効果トランジスタにおいて、窒化物チャネル層半導体1としてInN、InGaN、InAlN、あるいはInAlGaNが用いられ、窒化物障壁層半導体2としてInXAl1−XN(ここに、0<X≦0.66である)が用いられていることを特徴とするInN系ヘテロ構造電界効果トランジスタを構成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関し、特に、InN系半導体であるInN、InGaN、InAlNまたはInAlGaNが用いられているInN系ヘテロ構造電界効果トランジスタに関する。ここに、「InN系ヘテロ構造電界効果トランジスタ」とは、「チャネル層がInN系半導体であるヘテロ構造電界効果トランジスタ」の便宜上の表記である。

【背景技術】

【0002】

窒化物半導体を用いたヘテロ構造電界効果トランジスタ(Heterostructure Field Effect Transistor:HFET)は、次世代の高温・高出力・高耐圧の超高周波トランジスタとして非常に有望であり、実用化に向けて現在盛んに研究が行われている。

【0003】

しかし、現在行われているほとんどの研究は、チャネル層半導体としてGaN(あるいはGa組成の大きいAlGaN)を用いた、GaN系HFETに関するものであり(下記非特許文献1参照)、チャネル層半導体として、GaNに比べて電子移動度および飽和電子速度が高く、したがって、より高速動作が期待できる、InN(あるいは一般にIn組成の大きいInGaN、InAlN、あるいはInAlGaN)を用いた、InN系HFETに関しての研究の報告や、そのようなデバイスの作製の報告は、現在、事実上なされていない。

【0004】

InN系HFETが、理論的には、GaN系HFETを凌ぐ高速動作が期待されながら(下記非特許文献2参照)、良質なInN結晶の成長が報告されつつある現在においても(下記非特許文献3参照)、その作製がほとんど報告されていない理由は、InN系HFETにおける障壁層半導体/チャネル層半導体ヘテロ構造の成長が一般に困難なことにあるが、同時にこれとあいまって、InN系半導体のバンド構造上の特徴を考慮した、InN系HFETに必要とされる層構造条件についての理論的考察が、そもそもなされていないことにある。

【0005】

このような状況のもと、InN系半導体バンド構造上の特徴を考慮した、InN系HFETに必要とされる層構造条件についての理論的考察を行い、InN系HFETの層構造の設計指針を得ることにより、高性能のInN系HFETを実現させることが強く望まれていた。

【0006】

なお、下記非特許文献1は、AlGaN/GaN HFETの実用化研究の報告であり(文献表題のHeterojunction FET はHFETに同じ)、非特許文献2は、InNの電子輸送特性に関する理論的検討の報告であって、電子デバイス材料として、InNがGaNを凌駕する、優れた電子輸送特性を有することを報告しており、非特許文献3は、高品質InNの結晶成長の報告であり、非特許文献4には、AlN、GaN、InN他、各種半導体のバンド・ラインアップ(伝導帯および価電子帯の相対位置)が示されており、非特許文献5は、InNにおける表面電荷蓄積の報告である。

【先行技術文献】

【非特許文献】

【0007】

【非特許文献1】Y. Okamoto et al., IEEE Trans. on Microwave Theory and Tech., Vol. 52, pp. 2536-2539 (2004).

【非特許文献2】S. K. O'Leary et al., J. Appl. Phys. Vol. 83, pp. 826-829 (1998).

【非特許文献3】Y. Nanishi et al., Jpn. J. Appl. Phys. Vol. 42, pp. 2549-2559 (2003).

【非特許文献4】C. G. Van de Walle and J. Neugebauer, Nature Vol. 423, pp. 626-628 (2003).

【非特許文献5】H. Lu et al., Appl. Phys. Lett., Vol. 82, pp. 1736-1738 (2003).

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、窒化物半導体チャネル層として、GaNに比べて電子移動度および飽和電子速度が高く、したがって、より高速動作が期待できる、InN(あるいはInGaN、InAlN、InAlGaN)を用いたInN系HFET(チャネル層がInN系であるHFET)を、層構造の設計指針を得ることにより、実現させることを目標とする。

【0009】

すなわち、本発明が解決しようとする課題は、層構造の設計指針を得ることにより、窒化物半導体チャネル層としてInN(あるいはInGaN、InAlN、InAlGaN)を用いた、高性能のInN系HFET(チャネル層がInN系であるHFET)を実現させることである。

【課題を解決するための手段】

【0010】

上記課題を解決するために、本発明は、特許請求の範囲の請求項1に記載のように、

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、障壁層半導体としてInXAl1−XN(ここに、0<X≦0.66である)が用いられていることを特徴とする半導体装置を構成する。

【0011】

また、本発明においては、特許請求の範囲の請求項2に記載のように、

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、障壁層半導体としてInYGa1−YN(ここに、0<Y≦0.46である)が用いられていることを特徴とする半導体装置を構成する。

【0012】

また、本発明においては、特許請求の範囲の請求項3に記載のように、

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、障壁層半導体としてInZAlWGa1−Z−WN(ここに、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1である)が用いられていることを特徴とする半導体装置を構成する。

【0013】

また、本発明においては、特許請求の範囲の請求項4に記載のように、

請求項1、2または3に記載の半導体装置において、前記障壁層半導体およびチャネル層半導体の少なくとも一方の少なくとも一部分にMgのドーピングが施されていることを特徴とする半導体装置を構成する。

【発明の効果】

【0014】

上記本発明の構成要件を満足するInN系HFET(チャネル層がInN系であるHFET)を構成することによって、当該のHFETにおいてトランジスタ動作が実現し、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【図面の簡単な説明】

【0015】

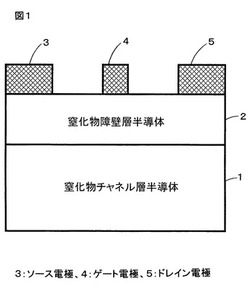

【図1】窒化物半導体を用いたヘテロ構造電界効果トランジスタ(HFET)の層構造および電極配置を模式的に示した図である。

【図2】障壁層半導体としてAlGaN、チャネル層半導体としてGaNが用いられているAlGaN/GaN HFETのポテンシャル形状を模式的に示した図である。

【図3】AlN、GaN、およびInNのバンド構造を、電荷中性位置に対して示した図である。

【図4】AlN、AlGaN、あるいはGaN上に、たとえばNi等のショットキー金属を積層することにより、金属/半導体接合を形成した際のポテンシャル形状を模式的に示した図である。

【図5】InNにおいて、金属/半導体接合を形成した際のポテンシャル形状を模式的に示した図である。

【図6】障壁層半導体としてIn0.9Al0.1N、チャネル層半導体としてInNを用いた、In0.9Al0.1N/InN HFETにおける、ゲート電極下におけるポテンシャル形状を模式的に示した図である。

【図7】障壁層半導体としてIn0.4Al0.6N、チャネル層半導体としてInNを用いた、In0.4Al0.6N/InN HFETにおける、ゲート電極下におけるポテンシャル形状を模式的に示した図である。

【図8】電荷中性位置を基準としたときの、InXAl1−XNの伝導帯エネルギー位置のIn組成(X)依存性を示した図である。

【図9】電荷中性位置を基準としたときの、InYGa1−YNの伝導帯エネルギー位置のIn組成(Y)依存性を示した図である。

【図10】電荷中性位置を基準としたときの、InZAlWGa1−Z−WNの伝導帯エネルギー位置のIn組成(Z)依存性を示した図である。

【図11】図10の領域に対応する、InZAlWGa1−Z−WNのIn組成(Z)およびAl組成(W)の領域を示した図である。

【発明を実施するための形態】

【0016】

本発明においては、窒化物半導体を用いたヘテロ構造電界効果トランジスタ(HFET)において、チャネル層半導体として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられ、障壁層半導体として、InN系半導体であるInXAl1−XN(ここに、0<X≦0.66である)、InYGa1−YN(ここに、0<Y≦0.46である)、あるいはInZAlWGa1−Z−WN(ここに、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1である)が用いられていることを特徴とする、InN系障壁層を有するInN系HFETを構成する。

【0017】

さらに、本発明においては、上記のInN系HFETにおいて、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されていることを特徴とする、InN系障壁層を有するInN系HFETを構成する。

【0018】

ここで、InN系障壁層半導体に関する、InXAl1−XN(0<X≦0.66)、InYGa1−YN(0<Y≦0.46)、あるいはInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)なる組成条件は、当該の障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにするための条件である。

【0019】

また、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている状況は、上記の組成条件による、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにするための効果を、補助的に強化することになる状況である。

【0020】

このように、上記のInN系障壁層を有するInN系HFETを用いることにより、当該のHFETにおいてトランジスタ動作が実現し、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0021】

以下に、本発明による作用を、図1から図8を用いて説明する。

【0022】

図1は、窒化物半導体を用いたヘテロ構造電界効果トランジスタ(HFET)の層構造および電極配置を模式的に示したもので、窒化物半導体を用いた障壁層半導体/チャネル層半導体ヘテロ構造上、すなわち、窒化物チャネル層半導体1の上に窒化物障壁層半導体2を重ねてなるヘテロ構造上に、ソース電極3、ゲート電極4、ドレイン電極5が配置され、電界効果トランジスタが構成されている様子が示されている。

【0023】

図1において、最も一般的な窒化物半導体HFETの層構造は、窒化物障壁層半導体2としてAlGaN、窒化物チャネル層半導体1としてGaNが用いられているAlGaN/GaN HFETであるが、障壁層半導体およびチャネル層半導体が、それぞれ障壁層およびチャネル層としての作用を有する条件は、障壁層半導体のバンドギャップがチャネル層半導体のそれよりも大きいことであり、一般にこの条件を満たすヘテロ構造であれば、障壁層半導体およびチャネル層半導体が上記以外の窒化物半導体であっても、電界効果トランジスタのデバイス動作を得ることができる。

【0024】

すなわち、障壁層半導体としてAlN、AlGaN、InAlN、InAlGaN等、また、チャネル層としてGaN、AlGaN、InN、InGaN、InAlN、InAlGaN等を用いて、障壁層半導体のバンドギャップがチャネル層半導体のそれよりも大きい、という条件のもとで、たとえば、AlN/AlGaN、AlGaN/AlGaN、AlGaN/InN、AlGaN/InGaN、InAlN/InN、InAlN/InGaN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまな障壁層半導体/チャネル層半導体ヘテロ構造を構成することが可能である。

【0025】

図2は、図1において、窒化物障壁層半導体2としてAlGaN、窒化物チャネル層半導体1としてGaNが用いられている最も一般的な窒化物半導体HFETであるAlGaN/GaN HFETのポテンシャル形状(ヘテロ構造における伝導帯形状)を模式的に示したもので、たとえばAlGaAs/GaAs HFET等の従来半導体HFETの場合と全く同様に、障壁層半導体であるAlGaNの伝導帯は、チャネル層半導体であるGaNの伝導帯よりも高い位置にあると同時に、フェルミ準位よりも高い位置にある様子が示されている。また、図2には、チャネル層のヘテロ界面近傍に2次元電子ガス(チャネル電子として作用)が存在する様子が示されている。

【0026】

図2においては、前述のように、障壁層半導体であるAlGaNの伝導帯はフェルミ準位よりも高い位置にあり、この状況は、障壁層半導体が電子に対する障壁層として作用するために必要不可欠な条件であるが、GaAs系の従来半導体HFETにおける障壁層半導体にせよ、GaN系HFETにおけるAlGaN障壁層にせよ、この条件は当該の半導体バンド構造の特徴として常に満たされているため、HFETの層構造設計において、前記の条件に関する配慮は全く必要がない状況であった。この状況は、InN系HFETにおいても、障壁層半導体としてAlN、AlGaNあるいはGaNを用いる場合には、全く同様であり、したがって、AlGaN系障壁層を用いたInN系HFETにおいては、障壁層半導体のバンドギャップがチャネル層半導体のそれよりも大きい限り、層構造に関して特別な配慮をすることなしにトランジスタの動作を得ることが理論上は可能である。

【0027】

このように、InN系HFETにおいて、障壁層半導体としてAlN、AlGaN、GaN等のAlN系半導体あるいはGaN系半導体を用いることもバンド構造上は理論的に可能であるが、しかし、AlN系半導体およびGaN系半導体と、InN系半導体とは、一般に格子不整合が大きく、また、結晶成長温度も大きく異なるため、実際にAlN系(あるいはGaN系)障壁層半導体/InN系チャネル層半導体ヘテロ構造を結晶成長により作製する場合、一般に困難が生じる。一方、InN系HFETにおいては、障壁層半導体としてInN系半導体を用いることで、ヘテロ構造作製上大きな優位性を獲得することが可能となるが、この場合には、層構造に関しての配慮が必要となる。

【0028】

そこで、InN系HFETにおいて、障壁層半導体としてInN系半導体を用いた、InN系障壁層半導体を有するInN系HFETにおいて、HFET動作が可能となるために必要とされる層構造の条件に関して、バンド構造上の特徴を配慮して考察する。その結果が、下記に作用を説明する本発明の構成要件を導きだすのに役立つ。

【0029】

図3は、AlN、GaN、およびInNのバンド構造(伝導帯および価電子帯の位置)を、電荷中性位置(フェルミ準位に相当)に対して示したもので、AlNおよびGaNにおいては、電荷中性位置が伝導帯と価電子帯の間に存在するのに対して、InNにおいては、電荷中性位置が伝導帯よりも高い位置に存在する様子が示されている(上記非特許文献4参照)。

【0030】

図4は、AlN系半導体あるいはGaN系半導体上に、すなわち、AlN、AlGaN、あるいはGaN上に、たとえばNi等のショットキー金属を積層することにより、金属/半導体接合を形成した際のポテンシャル形状を模式的に示したもので、いわゆるショットキー障壁を形成させている様子が示されている。したがって、HFETにおいて、障壁層半導体としてAlN、AlGaN、あるいはGaNを用いた場合にも、全く同様に、金属/半導体接合においてはショットキー障壁が形成され、HFETのトランジスタ動作を得ることができる。

【0031】

図5は、InNにおいて、金属/半導体接合を形成した際のポテンシャル形状を模式的に示したもので、いわゆるショットキー障壁は形成されず、むしろ、InN表面に電子の蓄積層(表面電荷蓄積層)が形成されている様子が示されている。実際、InNにおける表面電荷蓄積層の存在は実験的にも確認されたことが報告されている(上記非特許文献5参照)。

【0032】

上述のような表面電荷蓄積層の存在は、InN以外でも、InN系半導体であるInAlN、InGaN、あるいはInAlGaNにおいて、In組成が大きく、その結果、伝導帯の位置が電荷中性位置よりも低い位置に存在するならば、InNと全く同様であり、したがって、HFETにおいて、障壁層半導体として、伝導帯の位置が電荷中性位置よりも低い位置に存在するInAlN、InGaN、あるいはInAlGaNを用いた場合には、障壁層において表面電荷蓄積層が形成され、したがって、障壁層内にキャリアとなる電子が存在することとなり、HFETのトランジスタ動作を得ることができない。

【0033】

このような例として、図6は、障壁層半導体としてIn0.9Al0.1N、チャネル層半導体としてInNを用いた、In0.9Al0.1N/InN HFETにおける、ゲート電極(金属)下におけるポテンシャル形状を模式的に示したもので、In0.9Al0.1N障壁層内に、金属/In0.9Al0.1N界面で最大の濃度にて、キャリアとなる電子が存在することになり、したがって、In0.9Al0.1Nが障壁層として作用しない様子が示されている。In0.9Al0.1N/InNヘテロ構造は、In0.9Al0.1NとInNとの格子不整合が小さく、また、結晶成長の温度差も小さいため、ヘテロ構造の作製の観点からは大変魅力的であるが、上述のように、HFETの層構造として用いることができず、したがって、InNチャネルの優れた電子輸送特性を活用することはできない。

【0034】

以上のように、InN系半導体におけるバンド構造上の特徴の考察により、InN系HFETにおける障壁層半導体としてInN系半導体を用いる場合には、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないように、当該のInN系障壁層半導体の伝導帯の位置が電荷中性位置よりも高い位置に存在するように、InN系障壁層半導体を設計することが必要となる。

【0035】

このような例として、図7は、障壁層半導体としてIn0.4Al0.6N、チャネル層半導体としてInNを用いた、In0.4Al0.6N/InN HFETにおける、ゲート電極(金属)下におけるポテンシャル形状を模式的に示したもので、In0.4Al0.6N障壁層内にキャリアとなる電子が存在することなく、したがって、In0.4Al0.6Nが障壁層として作用する様子が示されている。すなわち、In0.4Al0.6N/InN HFETにおいて、トランジスタ動作が実現し、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0036】

以上のように、InN系HFETにおける障壁層半導体としてInN系半導体を用いる場合には、障壁層半導体の表面近傍を含めて当該のInN系障壁層半導体内にキャリアとなる電子が存在することがないようにするために、当該のInN系障壁層半導体の伝導帯の位置が電荷中性位置よりも高い位置に存在するように、InN系障壁層半導体を設計することによって、当該のInN系障壁層半導体がHFETの障壁層として作用し、その結果、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。これが、本発明による基本的な作用および効果である。

【0037】

InN系障壁層半導体の伝導帯の位置が電荷中性位置よりも高い位置に存在するための具体的条件は、実施例で示す。

【0038】

また、本発明において、上述のように、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている状況は、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、上述の本発明による基本的な作用を、補助的に強化することになる状況である。その理由を下記に説明する。

【0039】

一般に、InN系半導体には、いわゆるバックグラウンド・キャリア(キャリア供給のためのドーピングを施さないアンドープの半導体においても結晶欠陥によって生じてしまうキャリア)として、有意なる濃度の電子(バックグラウンド電子)が存在することが普通に起こる。このように、半導体中にバックグラウンド電子が存在する場合には、その半導体の伝導帯のフェルミ準位(あるいは電荷中性点)に対する相対的な位置は、より低い位置となる。このため、障壁層半導体がこのような状況にある場合はもちろんのこと、チャネル層半導体のみにおいてこのような状況にある場合も、ヘテロ構造全体のエネルギー位置がより低くなり、その結果、障壁層半導体内にキャリアとなる電子が存在しやすい状況となる。

【0040】

しかし、障壁層半導体あるいはチャネル層半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されることにより、アンドープの場合にバックグラウンド電子が存在する場合においても、電子が補償され、バックグラウンド電子が存在しない状況になる。また、バックグラウンド電子がもともと存在しない場合においては、伝導帯がより高い位置となる。結局、上述のようにMgのドーピングが施されることにより、バックグラウンド電子の有無に拘らず、いずれの場合においても、ヘテロ構造全体のエネルギー位置がより高い位置となり、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、上述の本発明による基本的な作用を、補助的に強化することになる。

【0041】

以上で、本発明による作用がすべて示された。

【実施例1】

【0042】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInXAl1−XN(0<X≦0.66)が用いられていることを特徴とするInN系障壁層を有するInN系HFETを実施例1とする。

【0043】

図8は、電荷中性位置を基準としたときの、InXAl1−XNの伝導帯エネルギー位置(正確には伝導帯下端のエネルギー位置)のIn組成(X)依存性を示したもので、破線はAlNおよびInNの伝導帯のエネルギー位置から線形近似を用いた依存性(参考)、実線は実験によって実測された依存性であり、0<X≦0.66において、InXAl1−XNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する様子が示されている。したがって、InXAl1−XN(0<X≦0.66)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0044】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.4Al0.6Nを用いた、In0.4Al0.6N/InNヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.4Al0.6N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0045】

ここで、本実施例のチャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInXAl1−XN(0<X≦0.66)が用いられている場合には、本発明の範囲内である。

【0046】

また、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0047】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInXAl1−XN(0<X≦0.66)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0048】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInXAl1−XN(0<X≦0.66)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例2】

【0049】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInXAl1−XN(0<X≦0.66)が用いられていることを特徴とするInN系障壁層を有するInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されていることを特徴とするInN系障壁層を有するInN系HFETを実施例2とする。

【0050】

本実施例は、実施例1のInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されているInN系HFETである。これは、InN系半導体においてアンドープの場合にしばしば存在する有意な濃度のバックグラウンド電子を補償することによって、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、本発明による基本的な作用を、補助的に強化するためである。

【0051】

すなわち、本実施例においては、アンドープの理想的なInN系半導体結晶においては本来存在しないバックグラウンド電子が仮に有意な濃度で存在する場合においても、図8に示されているInXAl1−XNの伝導帯エネルギー位置のIn組成(X)依存性において、0<X≦0.66において、InXAl1−XNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する状況が確実に保持され、したがって、InXAl1−XN(0<X≦0.66)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0052】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.5Al0.5Nを用いた、In0.5Al0.5N/InNヘテロ構造において、ドーピングの原子濃度が 2×1019cm−3なるMgのドーピングを、In0.5Al0.5N/InNヘテロ構造のすべての領域において施したヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.5Al0.5N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0053】

本実施例2を実施例1と比較すると、本実施例2は、Mgのドーピングを施すという、結晶成長上、より煩雑な手続きが必要となるという不利な点を有するが、(1)アンドープの場合には有意な濃度のバックグラウンド電子を発生するような、結晶として必ずしも理想的ではないInNチャネル層においても良好なトランジスタ動作が得られるという有利な点、また、(2)InAlN障壁層の成長において、一般にバックグラウンド電子が発生しやすい一方で、InNチャネル層との格子不整合がより小さく、したがってヘテロ構造の成長がより容易になる、より高いIn組成のInAlN(In組成が実施例1では0.4であるのに対して本実施例2では0.5)を用いることが可能となるという、ヘテロ構造成長上の有利な点、のふたつの有利な点を有する。

【0054】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInXAl1−XN(0<X≦0.66)が用いられており、かつ、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている場合には、本発明の範囲内である。

【0055】

ここで、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0056】

また、Mgのドーピング・プロファイルがいかなる場合、すなわち、いかなる領域にいかなる濃度でドーピングが施されている場合にも、本発明の効果が得られるので、Mgのドーピング・プロファイルは任意とする。

【0057】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInXAl1−XN(0<X≦0.66)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0058】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInXAl1−XN(0<X≦0.66)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例3】

【0059】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInYGa1−YN(0<Y≦0.46)が用いられていることを特徴とするInN系障壁層を有するInN系HFETを実施例3とする。

【0060】

図9は、電荷中性位置を基準としたときの、InYGa1−YNの伝導帯エネルギー位置(正確には伝導帯下端のエネルギー位置)のIn組成(Y)依存性を示したもので、破線はGaNおよびInNの伝導帯のエネルギー位置から線形近似を用いた依存性(参考)、実線は実験によって実測された依存性であり、0<Y≦0.46において、InYGa1−YNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する様子が示されている。したがって、InYGa1−YN(0<Y≦0.46)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0061】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.3Ga0.7Nを用いた、In0.3Ga0.7N/InNヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.3Ga0.7N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0062】

本実施例3を実施例1と比較すると、本実施例3において障壁層半導体として用いられるInYGa1−YNは、実施例1において障壁層半導体として用いられているInXAl1−XNに比べて、一般に障壁層のエネルギー高さが低いという不利な点を有するが、In組成の高いInN系チャネル層半導体と、一般に、格子定数の相異が小さく、また、結晶成長の温度の相異も小さいという、ヘテロ構造成長上の有利な点を有する。

【0063】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInYGa1−YN(0<Y≦0.46)が用いられている場合には、本発明の範囲内である。

【0064】

また、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0065】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInYGa1−YN(0<Y≦0.46)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0066】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInYGa1−YN(0<Y≦0.46)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例4】

【0067】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInYGa1−YN(0<Y≦0.46)が用いられていることを特徴とするInN系障壁層を有するInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されていることを特徴とするInN系障壁層を有するInN系HFETを実施例4とする。

【0068】

本実施例は、実施例3のInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されているInN系HFETである。これは、InN系半導体においてアンドープの場合にしばしば存在する有意な濃度のバックグラウンド電子を補償することによって、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、本発明による基本的な作用を、補助的に強化するためである。

【0069】

すなわち、本実施例においては、アンドープの理想的なInN系半導体結晶においては本来存在しないバックグラウンド電子が仮に有意な濃度で存在する場合においても、図9に示されているInYGa1−YNの伝導帯エネルギー位置のIn組成(Y)依存性において、0<Y≦0.46において、InYGa1−YNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する状況が確実に保持され、したがって、InYGa1−YN(0<Y≦0.46)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0070】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.4Ga0.6Nを用いた、In0.4Ga0.6N/InNヘテロ構造において、ドーピングの原子濃度が 2×1019cm−3なるMgのドーピングを、In0.4Ga0.6N/InNヘテロ構造のすべての領域において施したヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.4Ga0.6N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0071】

本実施例4を実施例3と比較すると、本実施例4は、Mgのドーピングを施すという、結晶成長上、より煩雑な手続きが必要となるという不利な点を有するが、(1)アンドープの場合には有意な濃度のバックグラウンド電子を発生するような、結晶として必ずしも理想的ではないInNチャネル層においても良好なトランジスタ動作が得られるという有利な点、また、(2)InGaN障壁層の成長において、一般にバックグラウンド電子が発生しやすい一方で、InNチャネル層との格子不整合がより小さく、したがってヘテロ構造の成長がより容易になる、より高いIn組成のInGaN(In組成が実施例3では0.3であるのに対して本実施例4では0.4)を用いることが可能となるという、ヘテロ構造成長上の有利な点、のふたつの有利な点を有する。

【0072】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInXGa1−XN(0<Y≦0.46)が用いられており、かつ、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている場合には、本発明の範囲内である。

【0073】

ここで、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0074】

また、Mgのドーピング・プロファイルがいかなる場合、すなわち、いかなる領域にいかなる濃度でドーピングが施されている場合にも、本発明の効果が得られるので、Mgのドーピング・プロファイルは任意とする。

【0075】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInYGa1−YN(0<Y≦0.46)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0076】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInYGa1−YN(0<Y≦0.46)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例5】

【0077】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられていることを特徴とするInN系障壁層を有するInN系HFETを実施例5とする。

【0078】

図10は、電荷中性位置を基準としたときの、InZAlWGa1−Z−WNの伝導帯エネルギー位置(正確には伝導帯下端のエネルギー位置)のIn組成(Z)依存性を示したもので、図8に示されているInXAl1−XNにおけるX依存性および図9に示されているInYGa1−YNにおけるY依存性をもとにして、InZAlWGa1−Z−WNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する領域が、実線内の斜線領域として示されている。

【0079】

図11は、前記の図10の領域に対応する、InZAlWGa1−Z−WNのIn組成(Z)およびAl組成(W)の領域を示したもので、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1なるInおよびAl組成領域において、InZAlWGa1−Z−WNの伝導帯のエネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在することが示されている。すなわち、InZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0080】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.3Al0.4Ga0.3Nを用いた、In0.3Al0.4Ga0.3N/InNヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.3Al0.4Ga0.3N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0081】

本実施例5を、InAlN障壁層を用いた実施例1あるいはInGaN障壁層を用いた実施例3と比較すると、結晶成長が4元系(In、Al、Ga、N)の成長となるため、組成制御の難易度が、一般に、より高くなるという欠点を有するが、格子定数および障壁層のエネルギー高さの設計自由度が増大する結果、ヘテロ構造の品質向上およびデバイス特性の向上への可能性が拡大するという利点を有する。

【0082】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられている場合には、本発明の範囲内である。

【0083】

また、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0084】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0085】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例6】

【0086】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられていることを特徴とするInN系障壁層を有するInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されていることを特徴とするInN系障壁層を有するInN系HFETを実施例6とする。

【0087】

本実施例は、実施例5のInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されているInN系HFETである。これは、InN系半導体においてアンドープの場合にしばしば存在する有意な濃度のバックグラウンド電子を補償することによって、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、本発明による基本的な作用を、補助的に強化するためである。

【0088】

すなわち、本実施例においては、アンドープの理想的なInN系半導体結晶においては本来存在しないバックグラウンド電子が仮に有意な濃度で存在する場合においても、図10および図11に示されているInZAlWGa1−Z−WNの伝導帯エネルギー位置のIn組成等の依存性において、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1において、InZAlWGa1−Z−WNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する状況が確実に保持され、したがって、InZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0089】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.4Al0.4Ga0.2Nを用いた、In0.4Al0.4Ga0.2N/InNヘテロ構造において、ドーピングの原子濃度が 2×1019cm−3なるMgのドーピングを、In0.4Al0.4Ga0.2N/InNヘテロ構造のすべての領域において施したヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.4Al0.4Ga0.2N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0090】

本実施例6を実施例5と比較すると、本実施例6においては、Mgのドーピングを施すという、結晶成長上、より煩雑な手続きが必要となるという不利な点を有するが、(1)アンドープの場合には有意な濃度のバックグラウンド電子を発生するような、結晶として必ずしも理想的ではないInNチャネル層においても良好なトランジスタ動作が得られるという有利な点、また、(2)InAlGaN障壁層の成長において、一般にバックグラウンド電子が発生しやすい一方で、InNチャネル層との格子不整合がより小さく、したがってヘテロ構造の成長がより容易になる、より高いIn組成のInAlGaN(In組成が実施例5では0.3であるのに対して本実施例6では0.4)を用いることが可能となるという、ヘテロ構造成長上の有利な点、のふたつの有利な点を有する。

【0091】

また、本実施例6を、やはりMgのドーピングが施されたヘテロ構造を用いた実施例2および実施例4と比較した場合の得失は、Mgのドーピングが施されていないヘテロ構造を用いた実施例5を、やはりMgのドーピングが施されていないヘテロ構造を用いた実施例1および実施例3と比較した場合の得失と同じである。すなわち、本実施例6は、結晶成長が4元系(In、Al、Ga、N)の成長となるため、組成制御の難易度が、一般に、より高くなるという欠点を有するが、格子定数および障壁層のエネルギー高さの設計自由度が増大する結果、ヘテロ構造の品質向上およびデバイス特性の向上への可能性が拡大するという利点を有する。

【0092】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられており、かつ、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている場合には、本発明の範囲内である。

【0093】

ここで、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0094】

また、Mgのドーピング・プロファイルがいかなる場合、すなわち、いかなる領域にいかなる濃度でドーピングが施されている場合にも、本発明の効果が得られるので、Mgのドーピング・プロファイルは任意とする。

【0095】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0096】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【符号の説明】

【0097】

1:窒化物チャネル層半導体、2:窒化物障壁層半導体、3:ソース電極、4:ゲート電極、5:ドレイン電極。

【技術分野】

【0001】

本発明は半導体装置に関し、特に、InN系半導体であるInN、InGaN、InAlNまたはInAlGaNが用いられているInN系ヘテロ構造電界効果トランジスタに関する。ここに、「InN系ヘテロ構造電界効果トランジスタ」とは、「チャネル層がInN系半導体であるヘテロ構造電界効果トランジスタ」の便宜上の表記である。

【背景技術】

【0002】

窒化物半導体を用いたヘテロ構造電界効果トランジスタ(Heterostructure Field Effect Transistor:HFET)は、次世代の高温・高出力・高耐圧の超高周波トランジスタとして非常に有望であり、実用化に向けて現在盛んに研究が行われている。

【0003】

しかし、現在行われているほとんどの研究は、チャネル層半導体としてGaN(あるいはGa組成の大きいAlGaN)を用いた、GaN系HFETに関するものであり(下記非特許文献1参照)、チャネル層半導体として、GaNに比べて電子移動度および飽和電子速度が高く、したがって、より高速動作が期待できる、InN(あるいは一般にIn組成の大きいInGaN、InAlN、あるいはInAlGaN)を用いた、InN系HFETに関しての研究の報告や、そのようなデバイスの作製の報告は、現在、事実上なされていない。

【0004】

InN系HFETが、理論的には、GaN系HFETを凌ぐ高速動作が期待されながら(下記非特許文献2参照)、良質なInN結晶の成長が報告されつつある現在においても(下記非特許文献3参照)、その作製がほとんど報告されていない理由は、InN系HFETにおける障壁層半導体/チャネル層半導体ヘテロ構造の成長が一般に困難なことにあるが、同時にこれとあいまって、InN系半導体のバンド構造上の特徴を考慮した、InN系HFETに必要とされる層構造条件についての理論的考察が、そもそもなされていないことにある。

【0005】

このような状況のもと、InN系半導体バンド構造上の特徴を考慮した、InN系HFETに必要とされる層構造条件についての理論的考察を行い、InN系HFETの層構造の設計指針を得ることにより、高性能のInN系HFETを実現させることが強く望まれていた。

【0006】

なお、下記非特許文献1は、AlGaN/GaN HFETの実用化研究の報告であり(文献表題のHeterojunction FET はHFETに同じ)、非特許文献2は、InNの電子輸送特性に関する理論的検討の報告であって、電子デバイス材料として、InNがGaNを凌駕する、優れた電子輸送特性を有することを報告しており、非特許文献3は、高品質InNの結晶成長の報告であり、非特許文献4には、AlN、GaN、InN他、各種半導体のバンド・ラインアップ(伝導帯および価電子帯の相対位置)が示されており、非特許文献5は、InNにおける表面電荷蓄積の報告である。

【先行技術文献】

【非特許文献】

【0007】

【非特許文献1】Y. Okamoto et al., IEEE Trans. on Microwave Theory and Tech., Vol. 52, pp. 2536-2539 (2004).

【非特許文献2】S. K. O'Leary et al., J. Appl. Phys. Vol. 83, pp. 826-829 (1998).

【非特許文献3】Y. Nanishi et al., Jpn. J. Appl. Phys. Vol. 42, pp. 2549-2559 (2003).

【非特許文献4】C. G. Van de Walle and J. Neugebauer, Nature Vol. 423, pp. 626-628 (2003).

【非特許文献5】H. Lu et al., Appl. Phys. Lett., Vol. 82, pp. 1736-1738 (2003).

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、窒化物半導体チャネル層として、GaNに比べて電子移動度および飽和電子速度が高く、したがって、より高速動作が期待できる、InN(あるいはInGaN、InAlN、InAlGaN)を用いたInN系HFET(チャネル層がInN系であるHFET)を、層構造の設計指針を得ることにより、実現させることを目標とする。

【0009】

すなわち、本発明が解決しようとする課題は、層構造の設計指針を得ることにより、窒化物半導体チャネル層としてInN(あるいはInGaN、InAlN、InAlGaN)を用いた、高性能のInN系HFET(チャネル層がInN系であるHFET)を実現させることである。

【課題を解決するための手段】

【0010】

上記課題を解決するために、本発明は、特許請求の範囲の請求項1に記載のように、

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、障壁層半導体としてInXAl1−XN(ここに、0<X≦0.66である)が用いられていることを特徴とする半導体装置を構成する。

【0011】

また、本発明においては、特許請求の範囲の請求項2に記載のように、

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、障壁層半導体としてInYGa1−YN(ここに、0<Y≦0.46である)が用いられていることを特徴とする半導体装置を構成する。

【0012】

また、本発明においては、特許請求の範囲の請求項3に記載のように、

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、障壁層半導体としてInZAlWGa1−Z−WN(ここに、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1である)が用いられていることを特徴とする半導体装置を構成する。

【0013】

また、本発明においては、特許請求の範囲の請求項4に記載のように、

請求項1、2または3に記載の半導体装置において、前記障壁層半導体およびチャネル層半導体の少なくとも一方の少なくとも一部分にMgのドーピングが施されていることを特徴とする半導体装置を構成する。

【発明の効果】

【0014】

上記本発明の構成要件を満足するInN系HFET(チャネル層がInN系であるHFET)を構成することによって、当該のHFETにおいてトランジスタ動作が実現し、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【図面の簡単な説明】

【0015】

【図1】窒化物半導体を用いたヘテロ構造電界効果トランジスタ(HFET)の層構造および電極配置を模式的に示した図である。

【図2】障壁層半導体としてAlGaN、チャネル層半導体としてGaNが用いられているAlGaN/GaN HFETのポテンシャル形状を模式的に示した図である。

【図3】AlN、GaN、およびInNのバンド構造を、電荷中性位置に対して示した図である。

【図4】AlN、AlGaN、あるいはGaN上に、たとえばNi等のショットキー金属を積層することにより、金属/半導体接合を形成した際のポテンシャル形状を模式的に示した図である。

【図5】InNにおいて、金属/半導体接合を形成した際のポテンシャル形状を模式的に示した図である。

【図6】障壁層半導体としてIn0.9Al0.1N、チャネル層半導体としてInNを用いた、In0.9Al0.1N/InN HFETにおける、ゲート電極下におけるポテンシャル形状を模式的に示した図である。

【図7】障壁層半導体としてIn0.4Al0.6N、チャネル層半導体としてInNを用いた、In0.4Al0.6N/InN HFETにおける、ゲート電極下におけるポテンシャル形状を模式的に示した図である。

【図8】電荷中性位置を基準としたときの、InXAl1−XNの伝導帯エネルギー位置のIn組成(X)依存性を示した図である。

【図9】電荷中性位置を基準としたときの、InYGa1−YNの伝導帯エネルギー位置のIn組成(Y)依存性を示した図である。

【図10】電荷中性位置を基準としたときの、InZAlWGa1−Z−WNの伝導帯エネルギー位置のIn組成(Z)依存性を示した図である。

【図11】図10の領域に対応する、InZAlWGa1−Z−WNのIn組成(Z)およびAl組成(W)の領域を示した図である。

【発明を実施するための形態】

【0016】

本発明においては、窒化物半導体を用いたヘテロ構造電界効果トランジスタ(HFET)において、チャネル層半導体として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられ、障壁層半導体として、InN系半導体であるInXAl1−XN(ここに、0<X≦0.66である)、InYGa1−YN(ここに、0<Y≦0.46である)、あるいはInZAlWGa1−Z−WN(ここに、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1である)が用いられていることを特徴とする、InN系障壁層を有するInN系HFETを構成する。

【0017】

さらに、本発明においては、上記のInN系HFETにおいて、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されていることを特徴とする、InN系障壁層を有するInN系HFETを構成する。

【0018】

ここで、InN系障壁層半導体に関する、InXAl1−XN(0<X≦0.66)、InYGa1−YN(0<Y≦0.46)、あるいはInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)なる組成条件は、当該の障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにするための条件である。

【0019】

また、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている状況は、上記の組成条件による、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにするための効果を、補助的に強化することになる状況である。

【0020】

このように、上記のInN系障壁層を有するInN系HFETを用いることにより、当該のHFETにおいてトランジスタ動作が実現し、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0021】

以下に、本発明による作用を、図1から図8を用いて説明する。

【0022】

図1は、窒化物半導体を用いたヘテロ構造電界効果トランジスタ(HFET)の層構造および電極配置を模式的に示したもので、窒化物半導体を用いた障壁層半導体/チャネル層半導体ヘテロ構造上、すなわち、窒化物チャネル層半導体1の上に窒化物障壁層半導体2を重ねてなるヘテロ構造上に、ソース電極3、ゲート電極4、ドレイン電極5が配置され、電界効果トランジスタが構成されている様子が示されている。

【0023】

図1において、最も一般的な窒化物半導体HFETの層構造は、窒化物障壁層半導体2としてAlGaN、窒化物チャネル層半導体1としてGaNが用いられているAlGaN/GaN HFETであるが、障壁層半導体およびチャネル層半導体が、それぞれ障壁層およびチャネル層としての作用を有する条件は、障壁層半導体のバンドギャップがチャネル層半導体のそれよりも大きいことであり、一般にこの条件を満たすヘテロ構造であれば、障壁層半導体およびチャネル層半導体が上記以外の窒化物半導体であっても、電界効果トランジスタのデバイス動作を得ることができる。

【0024】

すなわち、障壁層半導体としてAlN、AlGaN、InAlN、InAlGaN等、また、チャネル層としてGaN、AlGaN、InN、InGaN、InAlN、InAlGaN等を用いて、障壁層半導体のバンドギャップがチャネル層半導体のそれよりも大きい、という条件のもとで、たとえば、AlN/AlGaN、AlGaN/AlGaN、AlGaN/InN、AlGaN/InGaN、InAlN/InN、InAlN/InGaN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまな障壁層半導体/チャネル層半導体ヘテロ構造を構成することが可能である。

【0025】

図2は、図1において、窒化物障壁層半導体2としてAlGaN、窒化物チャネル層半導体1としてGaNが用いられている最も一般的な窒化物半導体HFETであるAlGaN/GaN HFETのポテンシャル形状(ヘテロ構造における伝導帯形状)を模式的に示したもので、たとえばAlGaAs/GaAs HFET等の従来半導体HFETの場合と全く同様に、障壁層半導体であるAlGaNの伝導帯は、チャネル層半導体であるGaNの伝導帯よりも高い位置にあると同時に、フェルミ準位よりも高い位置にある様子が示されている。また、図2には、チャネル層のヘテロ界面近傍に2次元電子ガス(チャネル電子として作用)が存在する様子が示されている。

【0026】

図2においては、前述のように、障壁層半導体であるAlGaNの伝導帯はフェルミ準位よりも高い位置にあり、この状況は、障壁層半導体が電子に対する障壁層として作用するために必要不可欠な条件であるが、GaAs系の従来半導体HFETにおける障壁層半導体にせよ、GaN系HFETにおけるAlGaN障壁層にせよ、この条件は当該の半導体バンド構造の特徴として常に満たされているため、HFETの層構造設計において、前記の条件に関する配慮は全く必要がない状況であった。この状況は、InN系HFETにおいても、障壁層半導体としてAlN、AlGaNあるいはGaNを用いる場合には、全く同様であり、したがって、AlGaN系障壁層を用いたInN系HFETにおいては、障壁層半導体のバンドギャップがチャネル層半導体のそれよりも大きい限り、層構造に関して特別な配慮をすることなしにトランジスタの動作を得ることが理論上は可能である。

【0027】

このように、InN系HFETにおいて、障壁層半導体としてAlN、AlGaN、GaN等のAlN系半導体あるいはGaN系半導体を用いることもバンド構造上は理論的に可能であるが、しかし、AlN系半導体およびGaN系半導体と、InN系半導体とは、一般に格子不整合が大きく、また、結晶成長温度も大きく異なるため、実際にAlN系(あるいはGaN系)障壁層半導体/InN系チャネル層半導体ヘテロ構造を結晶成長により作製する場合、一般に困難が生じる。一方、InN系HFETにおいては、障壁層半導体としてInN系半導体を用いることで、ヘテロ構造作製上大きな優位性を獲得することが可能となるが、この場合には、層構造に関しての配慮が必要となる。

【0028】

そこで、InN系HFETにおいて、障壁層半導体としてInN系半導体を用いた、InN系障壁層半導体を有するInN系HFETにおいて、HFET動作が可能となるために必要とされる層構造の条件に関して、バンド構造上の特徴を配慮して考察する。その結果が、下記に作用を説明する本発明の構成要件を導きだすのに役立つ。

【0029】

図3は、AlN、GaN、およびInNのバンド構造(伝導帯および価電子帯の位置)を、電荷中性位置(フェルミ準位に相当)に対して示したもので、AlNおよびGaNにおいては、電荷中性位置が伝導帯と価電子帯の間に存在するのに対して、InNにおいては、電荷中性位置が伝導帯よりも高い位置に存在する様子が示されている(上記非特許文献4参照)。

【0030】

図4は、AlN系半導体あるいはGaN系半導体上に、すなわち、AlN、AlGaN、あるいはGaN上に、たとえばNi等のショットキー金属を積層することにより、金属/半導体接合を形成した際のポテンシャル形状を模式的に示したもので、いわゆるショットキー障壁を形成させている様子が示されている。したがって、HFETにおいて、障壁層半導体としてAlN、AlGaN、あるいはGaNを用いた場合にも、全く同様に、金属/半導体接合においてはショットキー障壁が形成され、HFETのトランジスタ動作を得ることができる。

【0031】

図5は、InNにおいて、金属/半導体接合を形成した際のポテンシャル形状を模式的に示したもので、いわゆるショットキー障壁は形成されず、むしろ、InN表面に電子の蓄積層(表面電荷蓄積層)が形成されている様子が示されている。実際、InNにおける表面電荷蓄積層の存在は実験的にも確認されたことが報告されている(上記非特許文献5参照)。

【0032】

上述のような表面電荷蓄積層の存在は、InN以外でも、InN系半導体であるInAlN、InGaN、あるいはInAlGaNにおいて、In組成が大きく、その結果、伝導帯の位置が電荷中性位置よりも低い位置に存在するならば、InNと全く同様であり、したがって、HFETにおいて、障壁層半導体として、伝導帯の位置が電荷中性位置よりも低い位置に存在するInAlN、InGaN、あるいはInAlGaNを用いた場合には、障壁層において表面電荷蓄積層が形成され、したがって、障壁層内にキャリアとなる電子が存在することとなり、HFETのトランジスタ動作を得ることができない。

【0033】

このような例として、図6は、障壁層半導体としてIn0.9Al0.1N、チャネル層半導体としてInNを用いた、In0.9Al0.1N/InN HFETにおける、ゲート電極(金属)下におけるポテンシャル形状を模式的に示したもので、In0.9Al0.1N障壁層内に、金属/In0.9Al0.1N界面で最大の濃度にて、キャリアとなる電子が存在することになり、したがって、In0.9Al0.1Nが障壁層として作用しない様子が示されている。In0.9Al0.1N/InNヘテロ構造は、In0.9Al0.1NとInNとの格子不整合が小さく、また、結晶成長の温度差も小さいため、ヘテロ構造の作製の観点からは大変魅力的であるが、上述のように、HFETの層構造として用いることができず、したがって、InNチャネルの優れた電子輸送特性を活用することはできない。

【0034】

以上のように、InN系半導体におけるバンド構造上の特徴の考察により、InN系HFETにおける障壁層半導体としてInN系半導体を用いる場合には、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないように、当該のInN系障壁層半導体の伝導帯の位置が電荷中性位置よりも高い位置に存在するように、InN系障壁層半導体を設計することが必要となる。

【0035】

このような例として、図7は、障壁層半導体としてIn0.4Al0.6N、チャネル層半導体としてInNを用いた、In0.4Al0.6N/InN HFETにおける、ゲート電極(金属)下におけるポテンシャル形状を模式的に示したもので、In0.4Al0.6N障壁層内にキャリアとなる電子が存在することなく、したがって、In0.4Al0.6Nが障壁層として作用する様子が示されている。すなわち、In0.4Al0.6N/InN HFETにおいて、トランジスタ動作が実現し、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0036】

以上のように、InN系HFETにおける障壁層半導体としてInN系半導体を用いる場合には、障壁層半導体の表面近傍を含めて当該のInN系障壁層半導体内にキャリアとなる電子が存在することがないようにするために、当該のInN系障壁層半導体の伝導帯の位置が電荷中性位置よりも高い位置に存在するように、InN系障壁層半導体を設計することによって、当該のInN系障壁層半導体がHFETの障壁層として作用し、その結果、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。これが、本発明による基本的な作用および効果である。

【0037】

InN系障壁層半導体の伝導帯の位置が電荷中性位置よりも高い位置に存在するための具体的条件は、実施例で示す。

【0038】

また、本発明において、上述のように、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている状況は、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、上述の本発明による基本的な作用を、補助的に強化することになる状況である。その理由を下記に説明する。

【0039】

一般に、InN系半導体には、いわゆるバックグラウンド・キャリア(キャリア供給のためのドーピングを施さないアンドープの半導体においても結晶欠陥によって生じてしまうキャリア)として、有意なる濃度の電子(バックグラウンド電子)が存在することが普通に起こる。このように、半導体中にバックグラウンド電子が存在する場合には、その半導体の伝導帯のフェルミ準位(あるいは電荷中性点)に対する相対的な位置は、より低い位置となる。このため、障壁層半導体がこのような状況にある場合はもちろんのこと、チャネル層半導体のみにおいてこのような状況にある場合も、ヘテロ構造全体のエネルギー位置がより低くなり、その結果、障壁層半導体内にキャリアとなる電子が存在しやすい状況となる。

【0040】

しかし、障壁層半導体あるいはチャネル層半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されることにより、アンドープの場合にバックグラウンド電子が存在する場合においても、電子が補償され、バックグラウンド電子が存在しない状況になる。また、バックグラウンド電子がもともと存在しない場合においては、伝導帯がより高い位置となる。結局、上述のようにMgのドーピングが施されることにより、バックグラウンド電子の有無に拘らず、いずれの場合においても、ヘテロ構造全体のエネルギー位置がより高い位置となり、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、上述の本発明による基本的な作用を、補助的に強化することになる。

【0041】

以上で、本発明による作用がすべて示された。

【実施例1】

【0042】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInXAl1−XN(0<X≦0.66)が用いられていることを特徴とするInN系障壁層を有するInN系HFETを実施例1とする。

【0043】

図8は、電荷中性位置を基準としたときの、InXAl1−XNの伝導帯エネルギー位置(正確には伝導帯下端のエネルギー位置)のIn組成(X)依存性を示したもので、破線はAlNおよびInNの伝導帯のエネルギー位置から線形近似を用いた依存性(参考)、実線は実験によって実測された依存性であり、0<X≦0.66において、InXAl1−XNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する様子が示されている。したがって、InXAl1−XN(0<X≦0.66)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0044】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.4Al0.6Nを用いた、In0.4Al0.6N/InNヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.4Al0.6N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0045】

ここで、本実施例のチャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInXAl1−XN(0<X≦0.66)が用いられている場合には、本発明の範囲内である。

【0046】

また、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0047】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInXAl1−XN(0<X≦0.66)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0048】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInXAl1−XN(0<X≦0.66)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例2】

【0049】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInXAl1−XN(0<X≦0.66)が用いられていることを特徴とするInN系障壁層を有するInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されていることを特徴とするInN系障壁層を有するInN系HFETを実施例2とする。

【0050】

本実施例は、実施例1のInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されているInN系HFETである。これは、InN系半導体においてアンドープの場合にしばしば存在する有意な濃度のバックグラウンド電子を補償することによって、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、本発明による基本的な作用を、補助的に強化するためである。

【0051】

すなわち、本実施例においては、アンドープの理想的なInN系半導体結晶においては本来存在しないバックグラウンド電子が仮に有意な濃度で存在する場合においても、図8に示されているInXAl1−XNの伝導帯エネルギー位置のIn組成(X)依存性において、0<X≦0.66において、InXAl1−XNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する状況が確実に保持され、したがって、InXAl1−XN(0<X≦0.66)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0052】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.5Al0.5Nを用いた、In0.5Al0.5N/InNヘテロ構造において、ドーピングの原子濃度が 2×1019cm−3なるMgのドーピングを、In0.5Al0.5N/InNヘテロ構造のすべての領域において施したヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.5Al0.5N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0053】

本実施例2を実施例1と比較すると、本実施例2は、Mgのドーピングを施すという、結晶成長上、より煩雑な手続きが必要となるという不利な点を有するが、(1)アンドープの場合には有意な濃度のバックグラウンド電子を発生するような、結晶として必ずしも理想的ではないInNチャネル層においても良好なトランジスタ動作が得られるという有利な点、また、(2)InAlN障壁層の成長において、一般にバックグラウンド電子が発生しやすい一方で、InNチャネル層との格子不整合がより小さく、したがってヘテロ構造の成長がより容易になる、より高いIn組成のInAlN(In組成が実施例1では0.4であるのに対して本実施例2では0.5)を用いることが可能となるという、ヘテロ構造成長上の有利な点、のふたつの有利な点を有する。

【0054】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInXAl1−XN(0<X≦0.66)が用いられており、かつ、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている場合には、本発明の範囲内である。

【0055】

ここで、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0056】

また、Mgのドーピング・プロファイルがいかなる場合、すなわち、いかなる領域にいかなる濃度でドーピングが施されている場合にも、本発明の効果が得られるので、Mgのドーピング・プロファイルは任意とする。

【0057】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInXAl1−XN(0<X≦0.66)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0058】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInXAl1−XN(0<X≦0.66)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例3】

【0059】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInYGa1−YN(0<Y≦0.46)が用いられていることを特徴とするInN系障壁層を有するInN系HFETを実施例3とする。

【0060】

図9は、電荷中性位置を基準としたときの、InYGa1−YNの伝導帯エネルギー位置(正確には伝導帯下端のエネルギー位置)のIn組成(Y)依存性を示したもので、破線はGaNおよびInNの伝導帯のエネルギー位置から線形近似を用いた依存性(参考)、実線は実験によって実測された依存性であり、0<Y≦0.46において、InYGa1−YNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する様子が示されている。したがって、InYGa1−YN(0<Y≦0.46)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0061】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.3Ga0.7Nを用いた、In0.3Ga0.7N/InNヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.3Ga0.7N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0062】

本実施例3を実施例1と比較すると、本実施例3において障壁層半導体として用いられるInYGa1−YNは、実施例1において障壁層半導体として用いられているInXAl1−XNに比べて、一般に障壁層のエネルギー高さが低いという不利な点を有するが、In組成の高いInN系チャネル層半導体と、一般に、格子定数の相異が小さく、また、結晶成長の温度の相異も小さいという、ヘテロ構造成長上の有利な点を有する。

【0063】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInYGa1−YN(0<Y≦0.46)が用いられている場合には、本発明の範囲内である。

【0064】

また、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0065】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInYGa1−YN(0<Y≦0.46)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0066】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInYGa1−YN(0<Y≦0.46)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例4】

【0067】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInYGa1−YN(0<Y≦0.46)が用いられていることを特徴とするInN系障壁層を有するInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されていることを特徴とするInN系障壁層を有するInN系HFETを実施例4とする。

【0068】

本実施例は、実施例3のInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されているInN系HFETである。これは、InN系半導体においてアンドープの場合にしばしば存在する有意な濃度のバックグラウンド電子を補償することによって、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、本発明による基本的な作用を、補助的に強化するためである。

【0069】

すなわち、本実施例においては、アンドープの理想的なInN系半導体結晶においては本来存在しないバックグラウンド電子が仮に有意な濃度で存在する場合においても、図9に示されているInYGa1−YNの伝導帯エネルギー位置のIn組成(Y)依存性において、0<Y≦0.46において、InYGa1−YNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する状況が確実に保持され、したがって、InYGa1−YN(0<Y≦0.46)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0070】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.4Ga0.6Nを用いた、In0.4Ga0.6N/InNヘテロ構造において、ドーピングの原子濃度が 2×1019cm−3なるMgのドーピングを、In0.4Ga0.6N/InNヘテロ構造のすべての領域において施したヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.4Ga0.6N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0071】

本実施例4を実施例3と比較すると、本実施例4は、Mgのドーピングを施すという、結晶成長上、より煩雑な手続きが必要となるという不利な点を有するが、(1)アンドープの場合には有意な濃度のバックグラウンド電子を発生するような、結晶として必ずしも理想的ではないInNチャネル層においても良好なトランジスタ動作が得られるという有利な点、また、(2)InGaN障壁層の成長において、一般にバックグラウンド電子が発生しやすい一方で、InNチャネル層との格子不整合がより小さく、したがってヘテロ構造の成長がより容易になる、より高いIn組成のInGaN(In組成が実施例3では0.3であるのに対して本実施例4では0.4)を用いることが可能となるという、ヘテロ構造成長上の有利な点、のふたつの有利な点を有する。

【0072】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInXGa1−XN(0<Y≦0.46)が用いられており、かつ、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている場合には、本発明の範囲内である。

【0073】

ここで、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0074】

また、Mgのドーピング・プロファイルがいかなる場合、すなわち、いかなる領域にいかなる濃度でドーピングが施されている場合にも、本発明の効果が得られるので、Mgのドーピング・プロファイルは任意とする。

【0075】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInYGa1−YN(0<Y≦0.46)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0076】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInYGa1−YN(0<Y≦0.46)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例5】

【0077】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられていることを特徴とするInN系障壁層を有するInN系HFETを実施例5とする。

【0078】

図10は、電荷中性位置を基準としたときの、InZAlWGa1−Z−WNの伝導帯エネルギー位置(正確には伝導帯下端のエネルギー位置)のIn組成(Z)依存性を示したもので、図8に示されているInXAl1−XNにおけるX依存性および図9に示されているInYGa1−YNにおけるY依存性をもとにして、InZAlWGa1−Z−WNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する領域が、実線内の斜線領域として示されている。

【0079】

図11は、前記の図10の領域に対応する、InZAlWGa1−Z−WNのIn組成(Z)およびAl組成(W)の領域を示したもので、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1なるInおよびAl組成領域において、InZAlWGa1−Z−WNの伝導帯のエネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在することが示されている。すなわち、InZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0080】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.3Al0.4Ga0.3Nを用いた、In0.3Al0.4Ga0.3N/InNヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.3Al0.4Ga0.3N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0081】

本実施例5を、InAlN障壁層を用いた実施例1あるいはInGaN障壁層を用いた実施例3と比較すると、結晶成長が4元系(In、Al、Ga、N)の成長となるため、組成制御の難易度が、一般に、より高くなるという欠点を有するが、格子定数および障壁層のエネルギー高さの設計自由度が増大する結果、ヘテロ構造の品質向上およびデバイス特性の向上への可能性が拡大するという利点を有する。

【0082】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられている場合には、本発明の範囲内である。

【0083】

また、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0084】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0085】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【実施例6】

【0086】

図1に示される窒化物半導体を用いたHFET構造において、窒化物チャネル層半導体1として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系HFETであって、窒化物障壁層半導体2としてInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられていることを特徴とするInN系障壁層を有するInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されていることを特徴とするInN系障壁層を有するInN系HFETを実施例6とする。

【0087】

本実施例は、実施例5のInN系HFETにおいて、さらに、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されているInN系HFETである。これは、InN系半導体においてアンドープの場合にしばしば存在する有意な濃度のバックグラウンド電子を補償することによって、障壁層半導体の表面近傍を含めて当該の障壁層半導体内にキャリアとなる電子が存在することがないようにする、本発明による基本的な作用を、補助的に強化するためである。

【0088】

すなわち、本実施例においては、アンドープの理想的なInN系半導体結晶においては本来存在しないバックグラウンド電子が仮に有意な濃度で存在する場合においても、図10および図11に示されているInZAlWGa1−Z−WNの伝導帯エネルギー位置のIn組成等の依存性において、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1において、InZAlWGa1−Z−WNの伝導帯エネルギー位置が電荷中性点のエネルギー位置よりも高い位置に存在する状況が確実に保持され、したがって、InZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)を障壁層として用いることが可能であり、本実施例によって、InN系チャネル層半導体の優れた電子輸送特性が活用された、高性能のInN系HFETが実現する。

【0089】

実際、本実施例として、図1において、窒化物チャネル層半導体1として層厚 500nmのInN、窒化物障壁層半導体2として層厚 10nmのIn0.4Al0.4Ga0.2Nを用いた、In0.4Al0.4Ga0.2N/InNヘテロ構造において、ドーピングの原子濃度が 2×1019cm−3なるMgのドーピングを、In0.4Al0.4Ga0.2N/InNヘテロ構造のすべての領域において施したヘテロ構造を、MBE法(MBE:Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE:Metal Organic Vapor Phase Epitaxy)等の結晶成長法によってサファイア基板上に成長し、通常のHFETの作製方法によってIn0.4Al0.4Ga0.2N/InN HFETを作製したところ、良好なトランジスタ動作が得られ、ゲート長 0.05μmのデバイスにおいて、遮断周波数が 250GHzなる優れた高周波特性が実現した。

【0090】

本実施例6を実施例5と比較すると、本実施例6においては、Mgのドーピングを施すという、結晶成長上、より煩雑な手続きが必要となるという不利な点を有するが、(1)アンドープの場合には有意な濃度のバックグラウンド電子を発生するような、結晶として必ずしも理想的ではないInNチャネル層においても良好なトランジスタ動作が得られるという有利な点、また、(2)InAlGaN障壁層の成長において、一般にバックグラウンド電子が発生しやすい一方で、InNチャネル層との格子不整合がより小さく、したがってヘテロ構造の成長がより容易になる、より高いIn組成のInAlGaN(In組成が実施例5では0.3であるのに対して本実施例6では0.4)を用いることが可能となるという、ヘテロ構造成長上の有利な点、のふたつの有利な点を有する。

【0091】

また、本実施例6を、やはりMgのドーピングが施されたヘテロ構造を用いた実施例2および実施例4と比較した場合の得失は、Mgのドーピングが施されていないヘテロ構造を用いた実施例5を、やはりMgのドーピングが施されていないヘテロ構造を用いた実施例1および実施例3と比較した場合の得失と同じである。すなわち、本実施例6は、結晶成長が4元系(In、Al、Ga、N)の成長となるため、組成制御の難易度が、一般に、より高くなるという欠点を有するが、格子定数および障壁層のエネルギー高さの設計自由度が増大する結果、ヘテロ構造の品質向上およびデバイス特性の向上への可能性が拡大するという利点を有する。

【0092】

本実施例においては、チャネル層半導体および障壁層半導体から構成されるヘテロ構造が、サファイア基板上に形成されているが、前記のヘテロ構造が、サファイア基板上の他、SiC(シリコンカーバイド)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、障壁層半導体にInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられており、かつ、障壁層半導体あるいはチャネル層半導体として用いられているInN系半導体の一部あるいはすべての領域に、窒化物半導体のp型ドーパントであるMgのドーピングが施されている場合には、本発明の範囲内である。

【0093】

ここで、障壁層半導体およびチャネル層半導体の層厚がいかなる時にも本発明の効果が得られるので、前記の層厚の値は、トランジスタ動作が実現する限りにおいて、任意とする。

【0094】

また、Mgのドーピング・プロファイルがいかなる場合、すなわち、いかなる領域にいかなる濃度でドーピングが施されている場合にも、本発明の効果が得られるので、Mgのドーピング・プロファイルは任意とする。

【0095】

また、本実施例におけるチャネル層半導体としては、障壁層半導体に用いられているInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)よりもバンドギャップが小さいという、HFETのヘテロ構造に要求される条件が満たされている限り、InN、InGaN、InAlN、あるいはInAlGaNのいずれのInN系半導体を用いても差し支えなく、したがって、最も電子速度の高いInNの他、結晶成長の容易さ等の観点から、用いる基板や障壁層半導体に合わせてInGaN、InAlN、あるいはInAlGaNを用いることも有用であり、これらすべての場合が本発明の範囲内である。

【0096】

また、本実施例においては、図1に示されるような最も一般的なHFETのデバイス構造が用いられているが、デバイス構造として、ゲート電極と障壁層半導体の間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS:Metal-Insulator-Semiconductor))であっても、あるいはまた、ゲート電極下の障壁層半導体の一部が削除されてその層厚が低減されている、いわゆるリセスゲート構造であっても、HFETの障壁層半導体にInZAlWGa1−Z−WN(W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1)が用いられているInN系HFETは、すべて本発明の範囲内とする。

【符号の説明】

【0097】

1:窒化物チャネル層半導体、2:窒化物障壁層半導体、3:ソース電極、4:ゲート電極、5:ドレイン電極。

【特許請求の範囲】

【請求項1】

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、

チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、

障壁層半導体としてInXAl1−XN(ここに、0<X≦0.66である)が用いられていることを特徴とする半導体装置。

【請求項2】

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、

チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、

障壁層半導体としてInYGa1−YN(ここに、0<Y≦0.46である)が用いられていることを特徴とする半導体装置。

【請求項3】

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、

チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、

障壁層半導体としてInZAlWGa1−Z−WN(ここに、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1である)が用いられていることを特徴とする半導体装置。

【請求項4】

請求項1、2または3に記載の半導体装置において、

前記障壁層半導体およびチャネル層半導体の少なくとも一方の少なくとも一部分にMgのドーピングが施されていることを特徴とする半導体装置。

【請求項1】

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、

チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、

障壁層半導体としてInXAl1−XN(ここに、0<X≦0.66である)が用いられていることを特徴とする半導体装置。

【請求項2】

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、

チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、

障壁層半導体としてInYGa1−YN(ここに、0<Y≦0.46である)が用いられていることを特徴とする半導体装置。

【請求項3】

窒化物半導体を用いたヘテロ構造電界効果トランジスタである半導体装置において、

チャネル層半導体としてInN、InGaN、InAlNまたはInAlGaNが用いられ、

障壁層半導体としてInZAlWGa1−Z−WN(ここに、W≧1.70Z−0.78、W≦1−Z、0<Z≦1、かつ、0≦W≦1である)が用いられていることを特徴とする半導体装置。

【請求項4】

請求項1、2または3に記載の半導体装置において、

前記障壁層半導体およびチャネル層半導体の少なくとも一方の少なくとも一部分にMgのドーピングが施されていることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−238699(P2010−238699A)

【公開日】平成22年10月21日(2010.10.21)

【国際特許分類】

【出願番号】特願2009−81868(P2009−81868)

【出願日】平成21年3月30日(2009.3.30)

【出願人】(000004226)日本電信電話株式会社 (13,992)

【出願人】(593006630)学校法人立命館 (359)

【Fターム(参考)】

【公開日】平成22年10月21日(2010.10.21)

【国際特許分類】

【出願日】平成21年3月30日(2009.3.30)

【出願人】(000004226)日本電信電話株式会社 (13,992)

【出願人】(593006630)学校法人立命館 (359)

【Fターム(参考)】

[ Back to top ]