半導体装置

【課題】 半導体素子と回路基板との隙間を広いまま維持できる、半導体素子と回路基板とのバンプを介して接合された半導体装置およびその接合方法を提供する。

【解決手段】 半導体装置(101)において、半導体素子(101)は電極部(102)とバンプ(105)を有し、回路基板(103)は電極部(104)とバンプ(106)とを有し、バンプ(105、106)の融点よりも低い融点を有する導電性フィラー(108)はバンプ(105、106)同士を電気的に接合する。

【解決手段】 半導体装置(101)において、半導体素子(101)は電極部(102)とバンプ(105)を有し、回路基板(103)は電極部(104)とバンプ(106)とを有し、バンプ(105、106)の融点よりも低い融点を有する導電性フィラー(108)はバンプ(105、106)同士を電気的に接合する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子と回路基板とがバンプを介して接合された半導体装置およびその接合方法に関する。

【背景技術】

【0002】

今日、電子回路基板は、あらゆる製品に使用され、日増しにその性能が向上し、回路基板上で用いられる周波数も高くなっており、インピーダンスが低くなるフリップチップ実装は高周波を使用する電子機器に適した実装方法となっている。また、携帯機器の増加から、回路基板に半導体素子をパッケージではなく裸のまま搭載するフリップチップ実装が求められている。また、上記フリップチップ以外にもCSP(Chip Size Package)およびBGA(Ball Grid Array)等のパッケージが用いられるようになってきている。また、半導体素子は高密度化に伴い、小チップ化且つ多ピン化の対応が求められている。

【0003】

従来、半導体素子を回路基板に実装する方法として、フリップチップなど半導体素子に突設されたバンプを基板の電極に接合する方法が知られている。バンプとしては、はんだが多用されている。半導体素子の実装時に、加熱されてはんだ(バンプ)が溶融して、基板の電極にはんだ付けされる。その際に、はんだ付けを阻害する、はんだ表面の酸化膜は物理的に、或いはフラックスを用いて化学的に除去される。また、半導体素子と回路基板との隙間はアンダーフィル樹脂で封止される。アンダーフィルは、はんだ接合部を包み込んで補強すると共に異物の侵入を防ぐ。アンダーフィル樹脂には、エポキシ樹脂などの熱硬化性樹脂が用いられる。

【0004】

図4を参照して、バンプを用いた半導体素子の回路基板への従来の実装方法について、3つの行程に分けて簡単に説明する。

【0005】

まず、図4(A)に示すように、電極部402にバンプ405iが形成された半導体素子401と、電極部404にバンプ405cが形成された回路基板403とが、バンプ405iおよび405cが対向するように配される。なお、バンプ405iおよびバンプ405cのどちらか一方あるいは両方にはフラックス410が塗布される。半導体素子401および回路基板403は、バンプ405iおよびバンプ405cが当接するように互いに近づけられる。この状態で、バンプ405iおよびバンプ405cのはんだの融点以上まで加熱される。

【0006】

結果、図4(B)に示すように、互いに当接するバンプ405iとバンプ405cとは、1つのバンプ405に成り電気的に接合する。そして、回路基板403の電極部404の周囲に残留するフラックス410が洗浄除去された後に、絶縁性樹脂から成るアンダーフィル409が半導体素子401と回路基板403との隙間に注入される。そして、アンダーフィル409の硬化温度まで加熱されて、図4(C)に示す半導体装置が出来上がる。

【0007】

はんだによる接合部を補強するために様々な対策が採られている。例えば、特許文献1の例では、接合部のはんだと基板とが絶縁性樹脂で接合されている。特許文献2では、はんだによる接合部全体が絶縁性樹脂で覆われている。はんだ表面の酸化膜が除去できるように、絶縁性樹脂にフラックス成分等を付加させたりする方法が提案されている。

【0008】

また、特許文献3では、バンプを溶融させて電極間を接合させるためにフラックスを加

熱により硬化させ補強の効果を付加させる方法が提案されている。特許文献4では、上記方法を組み合わせた方法も提案されている。

【0009】

いずれの方法においても、バンプ(はんだ)自体を溶融させて電極間を電気的に接合するため、接合後のバンプの高さが低くなると共に低くなった分だけバンプが膨らむ。結果、接合後(図4(B))の半導体素子と回路基板間との間隔と共にバンプ間の間隔が小さくなり、半導体素子と回路基板間との間に形成される空間(隙間)が狭くなる。さらに、バンプを覆う絶縁性樹脂によって、この空間(隙間)はさらに狭められて、アンダーフィルを十分に注入できない。

【0010】

特に、近年の半導体の微細配線化に伴い、半導体素子の電極部の狭ピッチ、電極のエリア配置が一層進み、バンプの大きさも小さくなり、半導体素子と回路基板間の隙間がなお一層狭くなって、アンダーフィル注入をさらに困難なものにしている。そのために、半導体素子と回路基板間の隙間の狭隘化の防止が重要な課題となっている。

【0011】

この課題に対して、特許文献5における提案は、半導体素子側および回路基板側の両方のバンプが溶融する場合に対しては有効ではない。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2003−100811号公報

【特許文献2】特開2008−034775号公報

【特許文献3】特開2003−158153号公報

【特許文献4】特許第3417281号公報

【特許文献5】特開2007−12953号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、従来技術において、半導体素子と回路基板を接合する際のバンプ(はんだ)の融解により、半導体素子と回路基板との隙間が狭くなり、アンダーフィルの注入が阻害されるという課題がある。本発明は、フリップチップ実装後のアンダーフィルの注入を阻害しにくい、半導体素子と回路基板とのバンプを介して接合された半導体装置およびその接合方法を提供することを目的とする。

【課題を解決するための手段】

【0014】

上記の課題を解決する為に、本発明の半導体装置は、

第1の電極部と当該第1の電極部上に設けられた第1のバンプとを有する半導体素子と、

第2の電極部と当該第2の電極部上に設けられた第2のバンプとを有する回路基板と、

前記第1のバンプと前記第2のバンプの融点よりも低い融点を有して、当該第1のバンプと当該第2のバンプとを電気的に接合する接合部とを備える。

【発明の効果】

【0015】

本発明は、バンプを溶かさずに電気的に接合するので、半導体素子と回路基板との隙間を広いまま維持できる。

【図面の簡単な説明】

【0016】

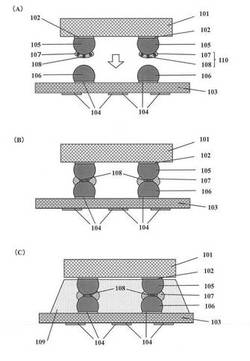

【図1】本発明の第1の実施例に係る半導体素子の回路基板への実装方法の説明図である。

【図2】本発明の第2の実施例に係る半導体素子の回路基板への実装方法の説明図である。

【図3】本発明の第3の実施例に係る半導体素子の回路基板への実装方法の説明図である。

【図4】従来例の技術に係る半導体素子の回路基板への実装方法の説明図である。

【発明を実施するための形態】

【0017】

以下に、本発明にかかる実施の形態を図面に基づいて詳細に説明する。

【0018】

(第1の実施形態)

図1を参照して、本発明の第1の実施形態に係る半導体素子の回路基板への実装方法について、3つの行程に分けて説明する。

【0019】

まず、図1(A)に示すように、電極部102に凸状のバンプ105が形成された半導体素子101と、電極部104に凸状のバンプ106が形成された回路基板103とが、バンプ105およびバンプ106が対向するように配される。バンプ105およびバンプ106のどちらか一方あるいは両方の先端に、熱硬化性樹脂107に導電性フィラー108が混合された導電性ペースト110が、例えば転写方式等の手段で塗布されている。

【0020】

半導体素子101および回路基板103は、バンプ105およびバンプ106が当接するように互いに近づけられる。具体的には、電子部品搭載装置において、部品保持部材の先端の接合ツールにより、上記前工程でバンプ105が電極部102上に形成された半導体素子101を吸着保持しつつ、該半導体素子101を、上記前工程で準備された回路基板103に対して、半導体素子101の電極部102が対応する回路基板103の電極部104上に位置するように位置合わせした後に、半導体素子101を回路基板103に実装する。この位置合わせは、公知の位置認識動作を使用する。そして、バンプ105およびバンプ106を構成する材料の融点より低温でかつ導電性ペースト110の導電性フィラー108の融点および熱硬化性樹脂107の硬化温度より高温で所定時間加熱される。

【0021】

熱硬化性樹脂107が硬化する前に、熱硬化性樹脂107は融解してバンプ105とバンプ106の当接部の周囲に集まる。そして、熱硬化性樹脂107は融解した導電性フィラー108の周囲にバンプ105とバンプ106の当接部の周囲で硬化する。この状態で加熱を停止することによって、導電性フィラー108をバンプ105とバンプ106との当接部の周囲或いは一部を覆うよう状態で固化させて電気的接合させ、熱硬化性樹脂107を固化した導電性フィラー108の周囲或いは一部を覆わせる。

【0022】

所定時間の加熱後に、図1(B)に示すように、バンプ105とバンプ106は、互いに当接する先端部の周囲で導電性フィラー108によって蝋付されて、電気的に接合される。この場合、バンプ105およびバンプ106は溶融されずに互いの先端部で接触しおり、その先端部の周囲の空間で溶融した導電性フィラー108が固化する。個化した導電性フィラー108によってバンプ105とバンプ106とが蝋付けされて、電気的に接合される。そして、固化した導電性フィラー108の周囲で硬化した熱硬化性樹脂107によって部分的或いは全体的に覆われて、バンプ105とバンプ106の接合部が保護される。

【0023】

結果、半導体素子101と回路基板103との間の距離は、実装(加熱)の前後で実質的に変化がなく、さらに隣り合うバンプ105あるいはバンプ106の距離も実装(加熱)の前後で実質的に変化がなく。半導体素子101と回路基板103との間の隙間も確保できる。このようにして、半導体素子401と回路基板403との間に確保された隙間に、絶縁性樹脂から成るアンダーフィル109が注入される。そして、アンダーフィル109の硬化温度まで加熱されて、図1(C)に示す半導体装置が出来上がる。

【0024】

なお、導電性ペースト110中の導電性フィラー108の量は、好ましくは導電性フィラー108が固化した場合に、バンプ105とバンプ106が互いに当接する先端部の周囲の空間内におさまり、バンプ105およびバンプ106の径方向にはみ出さないように決められる。さらに、導電性ペースト110中の熱硬化性樹脂107の量も、好ましくは熱硬化性樹脂107が固化した場合に、固化した導電性フィラー108の周囲の空間内におさまり、バンプ105およびバンプ106の径方向にはみ出さないように決められる。

【0025】

このように、バンプ105とバンプ106とを溶融接合させないので、従来技術におけるようなフラックスを用いないので、その洗浄除去も不要である。そのために、実装された半導体素子101と回路基板103とを、従来に較べてより大きな空間に注入された熱硬化性樹脂107によって確実に保持できる。

【0026】

なお、電極部102としては、Alパッドの電極、なお材質はAuやCu、下地としてNi等のメッキをした上に金属をメッキした電極でもよい。バンプ105は、電極部102に、はんだボールマウンタ装置等を用いて形成される。バンプ105のはんだ組成には、例えばスズ系合金単一またはそれら合金の混合物、具体的にはSn−Bi系、Sn−In系、Sn−Bi−In系、Sn−Ag系、Sn−Cu系、Sn−Ag−Cu系、Sn−Ag−Bi系、Sn−Cu−Bi系、Sn−Ag−Cu−Bi系、Sn−Ag−In系、Sn−Cu−In系、Sn−Ag−Cu−In系、およびSn−Ag−Cu−Bi−In系からなる群から選ばれる合金組成を用いることができる。特にSn−Ag系やSn−Ag−Cu系の群から選ばれる合金組成を用いることが好ましい。

【0027】

回路基板103の電極部104上に、バンプ106を形成する。バンプ106の形成方法や材質は、バンプ105と同じであってもよいし、異なっていてもよい。例えば、蒸着法やソルダーペーストによる形成方法でもよい。回路基板103には、セラミック多層基板、FPC、ガラス布積層エポキシ基板(ガラエポ基板)やガラス布積層ポリイミド樹脂基板、アラミド不織布エポキシ基板(例えば、パナソニック株式会社製の登録商標アリブ「ALIVH」として販売されている樹脂多層基板)などが用いられる。また、半導体素子と同じ材質、例えばSiなどをベースとしたものでもよい。

【0028】

回路基板103上の電極部104は、例としてCuの上にNiをメッキし表面をAuのフラッシュメッキしたものを使用するが、上記半導体素子101の電極部102と材質が同じであってもよいし、異なっていてもよい。熱硬化性樹脂107は絶縁性樹脂と硬化剤と、酸化膜除去効果を有する活性剤とを主成分とし、選択により、粘度調整/チクソ性付与添加剤を適宜加えることができる。

【0029】

絶縁性樹脂109は、エポキシ樹脂、ウレタン樹脂、アクリル樹脂、ポリイミド樹脂、ポリアミド樹脂、ビスマレイミド、フェノール樹脂、ポリエステル樹脂、シリコン樹脂、オキセタン樹脂など、様々な樹脂を含むことができる。これらは単独で用いてもよく、2種類以上を組み合わせて用いてもよい。これらのうちでは、特にエポキシ樹脂が好適である。

【0030】

エポキシ樹脂には、ビスフェノール型エポキシ樹脂、多官能エポキシ樹脂、可撓性エポキシ樹脂、臭素化エポキシ樹脂、グリシジルエステル型エポキシ樹脂、および高分子型エポキシ樹脂の群から選ばれるエポキシ樹脂も用いることができる。例えば、ビスフェノールA型エポキシ樹脂、ビスフェノールF型エポキシ樹脂、ビスフェノールS型エポキシ樹脂、ビフェニル型エポキシ樹脂、ナフタレン型エポキシ樹脂、フェノールノボラック型エポキシ樹脂、およびクレゾールノボラック型エポキシ樹脂などが好適に用いられる。これらを変性させたエポキシ樹脂も用いられる。これらは単独で用いてもよく、2種以上を組

み合わせて用いてもよい。

【0031】

上記のような熱硬化性樹脂と組み合わせて用いる硬化剤としては、チオール系化合物、変性アミン系化合物、多官能フェノール系化合物、イミダゾール系化合物、および酸無水物系化合物の群から選ばれる化合物を用いることができる。これらは単独で用いてもよく、2種以上を組み合わせて用いてもよい。硬化剤は、導電性ペーストの使用環境や用途に応じて、好適なものが選択される。

【0032】

酸化膜除去効果を有する活性剤としては、導電性ペーストを加熱硬化する温度域で、被着体である電極あるいは合金粒子表面の酸化膜を除去し、溶融接合させることができる還元力を有するものを用いる。JIS Z3283に記載されているようなロジンまたは変性ロジンを主剤とし、所望により活性化成分としてアミンのハロゲン塩、有機酸若しくはアミン有機酸塩を含むものなどを用いることができる。

【0033】

例えば飽和脂肪族モノカルボン酸であるラウリン酸、ミリスチン酸、パルミチン酸、ステアリン酸、不飽和脂肪族モノカルボン酸であるクロトン酸、飽和脂肪族ジカルボン酸であるシュウ酸、マロン酸、コハク酸、グルタル酸、アジピン酸、ピメリン酸、スベリン酸、アゼライン酸、セバシン酸、不飽和脂肪族ジカルボン酸であるマレイン酸、フマル酸、芳香族系カルボン酸であるフタルアルデヒド酸、フェニル酪酸、フェノキシ酢酸、フェニルプロピオン酸、エーテル系ジカルボン酸であるジグリコール酸、チオジグリコール酸、ジチオジグリコール酸、アミン塩酸塩であるエチルアミン塩酸塩、ジエチルアミン塩酸塩、ジメチルアミン塩酸塩、シクロヘキシルアミン塩酸塩、トリエタノールアミン塩酸塩、グルタミン酸塩酸塩、アミン臭化水素酸塩であるジエチルアミン臭化水素酸塩、シクロヘキシルアミン臭化水素酸塩、他にアビエチン酸、アスコルビン酸などが挙げられる。

【0034】

粘度調整/チクソ性付与添加剤としては、無機系あるいは有機系のものが使用できる。例えば、無機系であれば、シリカやアルミナなどが用いられ、有機系であれば固形のエポキシ樹脂や低分子量のアマイド、ポリエステル系、ヒマシ油の有機誘導体などが用いられる。これらは単独で用いてもよく、2種以上を組み合わせて用いてもよい。

【0035】

導電性(はんだ)フィラー108には、例えばスズ系合金単一またはそれら合金の混合物のはんだ材料を用いることができる。具体的には、Sn−Bi系、Sn−In系、Sn−Bi−In系、Sn−Ag系、Sn−Cu系、Sn−Ag−Cu系、Sn−Ag−Bi系、Sn−Cu−Bi系、Sn−Ag−Cu−Bi系、Sn−Ag−In系、Sn−Cu−In系、Sn−Ag−Cu−In系、およびSn−Ag−Cu−Bi−In系からなる群から選ばれる合金組成を用いることができる。特にSn42Bi58、Sn48In52、Sn16Bi56In28、SnAg3CuO.5、およびSnAg3.5Bi0.5In8の群から選ばれる合金組成を用いることが好ましい。

【0036】

しかし、バンプ105或いは、バンプ106の材料として選択された、はんだの融点以下の融点をもつ合金組成が選択されなければいけない。好ましくは、バンプ105或いは、バンプ106の材料として選択された、はんだの融点より約10℃以上低い融点を持つものがよい。また、導電性フィラー108の融点は、熱硬化性樹脂107が硬化開始する温度以上の融点を持つものから選択される。好ましくは、熱硬化性樹脂107が硬化開始する温度より約10〜20℃高い融点を持つ合金組成がよい。

【0037】

合金粒子は、微細な粒子状の形態、好ましくは球状粒子の形態で供給される。所定の組成の合金を調製した後に、アトマイズや転動造粒等の操作によって粒状化することにより、球状粒子の形態のものが得られる。球状粒子は、一般に、約1〜50μmの粒子径のものでよく、約10〜40μmの粒子径を有するものがさらに好ましい。

【0038】

熱硬化性樹脂107と導電性フィラー108の混合割合は、例えば熱硬化性樹脂107を約100重量部とするなら、導電性フィラー108は、約1〜50重量部としてよい。しかし、本発明はこれに限定されず、適宜選択され得る。

【0039】

絶縁性樹脂109としては、一般的にアンダーフィルや封止剤として市販されているものでよく、熱硬化性樹脂107と同じものでもよい。好ましくは、酸化膜除去効果を有する活性剤は添加されていない方がよい。

【0040】

(第2の実施形態)

図2を参照して、本発明の第2の実施形態にかかる半導体素子を回路基板に実装する方法について説明する。図2(A)に示すように、本実施形態においては、回路基板103が回路基板203に置き換えられている点を除いて、第1の実施の形態におけるのと同様に構成されている。なお、回路基板203は、回路基板103において、バンプ106がハンダメッキバンプ206に置き換えられている。

【0041】

ハンダメッキバンプ206は、その形成方法と形状がバンプ106と異なる。つまり、ハンダメッキバンプ206は、電解或いは無電解法を用いて、概ね平板状に形成される。ハンダメッキバンプ206の組成は、バンプ105と同じであってもよいし、異なっていてもよい。

【0042】

本実施の形態においても、図2(B)に示すように、凸状のバンプ105の先端と、平板状のハンダメッキバンプ206の直面との当接部の周囲に導電性フィラー108が固化して、その周囲に熱硬化性樹脂107が硬化して、バンプ105とハンダメッキバンプ206が電気的かつ物理的に接合される。なお、固化した導電性フィラー108と硬化した熱硬化性樹脂107は、概ねハンダメッキバンプ206およびバンプ105の輪郭程度に収まる。よって、半導体素子101と回路基板203との間には、図2(C)に示すように、アンダーフィルである絶縁性樹脂109を注入する十分な空間(隙間)が確保できる。

【0043】

(第3の実施形態)

図3を参照して、本発明の第3の実施形態にかかる半導体素子の回路基板への実装方法について説明する。図3(A)に示すように、本実施形態においては、回路基板101が回路基板301に置き換えられている点を除いて、第2の実施の形態におけるのと同様である。なお、回路基板301は、回路基板201において、バンプ105がハンダメッキバンプ305に置き換えられている。

【0044】

互いに接合されるハンダメッキバンプ305およびハンダメッキバンプ206が共に平板状であるので、図3(B)に示すように、導電性フィラー108はハンダメッキバンプ305およびハンダメッキバンプ206の主面の間に平板状に固化する。つまり、ハンダメッキバンプ305およびハンダメッキバンプ206はそれぞれの主面で固化した導電性フィラー108によって全面的に接合される。この固化した導電性フィラー108による接合部は、硬化した導電性フィラー108によって覆われる。

【0045】

この場合、導電性フィラー108は、概ね固化したハンダメッキバンプ305およびハンダメッキバンプ206の輪郭内におさまり、硬化した導電性フィラー108は、ハンダメッキバンプ305およびハンダメッキバンプ206の外形より若干はみ出す。よって、半導体素子101と回路基板203との間には、図2(C)に示すように、アンダーフィルである絶縁性樹脂109を注入する十分な空間(隙間)が確保できる。なお、ハンダメッキバンプ305とハンダメッキバンプ206が、導電性フィラー108によって全面的に接合されるので、より確実な電気的接合が得られる。

【0046】

以下に、実際の半導体素子の回路基板の接合に本発明を適用した実施例について述べる。

【0047】

[実施例]

半導体素子として、厚み100μm、8mm□Siの面内全域にAlパッドの電極(サイズは85×85μm)が計160個あるものを使用した。その半導体素子の電極は、各180μm以上の間隔で配列されている。

【0048】

回路基板は、ALIVH基板で厚み340μm、上記半導体素子の電極に対応する箇所に、100μm□サイズで、Cuの下地にNiとフラッシュAuメッキを設けた電極を使用した。なお、基板の電極の中心と半導体素子の電極の中心が一致するように設計されている。

【0049】

熱硬化性樹脂と導電性(はんだ)フィラーを混合した導電性ペーストは、ビスフェノールA型エポキシ樹脂に潜在性のイミダゾール系硬化剤を混合し一液にした熱硬化性樹脂に、球形状で平均粒子径21μmのSnAgBiIn合金粒子(融点約195℃)からなる導電性フィラーと、酸化膜除去効果を有するアビエチン酸を主とする活性剤を混合して用いた。

【0050】

比較例1〜3および実施例1〜3で作成した後に、半導体素子と回路基板との隙間に絶縁性樹脂(アンダーフィル)を注入し、加熱硬化後に半導体素子と回路基板との間隔を測定した結果を表1に示す。アンダーフィルの充填は、硬化させた後にSAT(超音波顕微鏡)にてボイド(気泡)を観察し、ボイドが10箇所以上確認された時は×、5箇所以下の時は○、それ以外では△と評価した。

【0051】

比較例1:

半導体素子の電極上に、はんだボールマウンタ装置を用いて、SnAgCu組成(融点218℃)で直径85μmのはんだボールバンプを作成した。一方、回路基板の電極上に、ソルダーペースト印刷法にてSnAgCu組成(融点218℃)で高さ80μmのバンプを作成した。半導体素子の電極上のバンプにフラックスを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、230℃まで加熱した。

【0052】

実施例1:

比較例1と同様に、バンプを作成し、半導体素子の電極上のバンプに導電性ペーストを転写した後に、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、200℃まで加熱した。

【0053】

比較例2:

半導体素子の電極上に、はんだボールマウンタ装置を用いて、SnAg組成(融点220℃)で直径85μmのはんだボールバンプを作成した。一方、回路基板の電極上に、電解メッキ法にてSnAg組成(融点220℃)で高さ50μmのハンダメッキバンプを作成した。半導体素子の電極上のバンプにフラックスを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、230℃まで加熱した。

【0054】

実施例2:

比較例2と同様に、バンプを作成し、半導体素子の電極上のバンプに導電性ペーストを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、200℃まで加熱した。

【0055】

比較例3:

半導体素子の電極上に、電解メッキ法で、SnAg組成(融点220℃)で高さ50μmのハンダメッキバンプを作成した。一方、回路基板の電極上に、電解メッキ法にてSnAg組成(融点220℃)で高さ50μmのハンダメッキバンプを作成した。半導体素子の電極上のバンプにフラックスを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、230℃まで加熱した。

【0056】

実施例3:

比較例3と同様に、ハンダメッキバンプを作成し、半導体素子の電極上のハンダメッキバンプに導電性ペーストを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、200℃まで加熱した。

【0057】

【表1】

【0058】

表1より、従来構造の比較例に対して、いずれの実施例においても半導体素子と回路基板の間隔は大きくなり、アンダーフィルの充填も良化の効果が見てとれる。

【産業上の利用可能性】

【0059】

本発明は、半導体素子と回路基板とがバンプを介して接合される半導体装置に広く適用できる。

【符号の説明】

【0060】

101、301、401 半導体素子

102 電極部

103、203、403 回路基板

104 電極部

105、106、405、405i、405c バンプ

206、305 ハンダメッキバンプ

107 熱硬化性樹脂

108 導電性フィラー

109 絶縁性樹脂

410 フラックス

【技術分野】

【0001】

本発明は、半導体素子と回路基板とがバンプを介して接合された半導体装置およびその接合方法に関する。

【背景技術】

【0002】

今日、電子回路基板は、あらゆる製品に使用され、日増しにその性能が向上し、回路基板上で用いられる周波数も高くなっており、インピーダンスが低くなるフリップチップ実装は高周波を使用する電子機器に適した実装方法となっている。また、携帯機器の増加から、回路基板に半導体素子をパッケージではなく裸のまま搭載するフリップチップ実装が求められている。また、上記フリップチップ以外にもCSP(Chip Size Package)およびBGA(Ball Grid Array)等のパッケージが用いられるようになってきている。また、半導体素子は高密度化に伴い、小チップ化且つ多ピン化の対応が求められている。

【0003】

従来、半導体素子を回路基板に実装する方法として、フリップチップなど半導体素子に突設されたバンプを基板の電極に接合する方法が知られている。バンプとしては、はんだが多用されている。半導体素子の実装時に、加熱されてはんだ(バンプ)が溶融して、基板の電極にはんだ付けされる。その際に、はんだ付けを阻害する、はんだ表面の酸化膜は物理的に、或いはフラックスを用いて化学的に除去される。また、半導体素子と回路基板との隙間はアンダーフィル樹脂で封止される。アンダーフィルは、はんだ接合部を包み込んで補強すると共に異物の侵入を防ぐ。アンダーフィル樹脂には、エポキシ樹脂などの熱硬化性樹脂が用いられる。

【0004】

図4を参照して、バンプを用いた半導体素子の回路基板への従来の実装方法について、3つの行程に分けて簡単に説明する。

【0005】

まず、図4(A)に示すように、電極部402にバンプ405iが形成された半導体素子401と、電極部404にバンプ405cが形成された回路基板403とが、バンプ405iおよび405cが対向するように配される。なお、バンプ405iおよびバンプ405cのどちらか一方あるいは両方にはフラックス410が塗布される。半導体素子401および回路基板403は、バンプ405iおよびバンプ405cが当接するように互いに近づけられる。この状態で、バンプ405iおよびバンプ405cのはんだの融点以上まで加熱される。

【0006】

結果、図4(B)に示すように、互いに当接するバンプ405iとバンプ405cとは、1つのバンプ405に成り電気的に接合する。そして、回路基板403の電極部404の周囲に残留するフラックス410が洗浄除去された後に、絶縁性樹脂から成るアンダーフィル409が半導体素子401と回路基板403との隙間に注入される。そして、アンダーフィル409の硬化温度まで加熱されて、図4(C)に示す半導体装置が出来上がる。

【0007】

はんだによる接合部を補強するために様々な対策が採られている。例えば、特許文献1の例では、接合部のはんだと基板とが絶縁性樹脂で接合されている。特許文献2では、はんだによる接合部全体が絶縁性樹脂で覆われている。はんだ表面の酸化膜が除去できるように、絶縁性樹脂にフラックス成分等を付加させたりする方法が提案されている。

【0008】

また、特許文献3では、バンプを溶融させて電極間を接合させるためにフラックスを加

熱により硬化させ補強の効果を付加させる方法が提案されている。特許文献4では、上記方法を組み合わせた方法も提案されている。

【0009】

いずれの方法においても、バンプ(はんだ)自体を溶融させて電極間を電気的に接合するため、接合後のバンプの高さが低くなると共に低くなった分だけバンプが膨らむ。結果、接合後(図4(B))の半導体素子と回路基板間との間隔と共にバンプ間の間隔が小さくなり、半導体素子と回路基板間との間に形成される空間(隙間)が狭くなる。さらに、バンプを覆う絶縁性樹脂によって、この空間(隙間)はさらに狭められて、アンダーフィルを十分に注入できない。

【0010】

特に、近年の半導体の微細配線化に伴い、半導体素子の電極部の狭ピッチ、電極のエリア配置が一層進み、バンプの大きさも小さくなり、半導体素子と回路基板間の隙間がなお一層狭くなって、アンダーフィル注入をさらに困難なものにしている。そのために、半導体素子と回路基板間の隙間の狭隘化の防止が重要な課題となっている。

【0011】

この課題に対して、特許文献5における提案は、半導体素子側および回路基板側の両方のバンプが溶融する場合に対しては有効ではない。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2003−100811号公報

【特許文献2】特開2008−034775号公報

【特許文献3】特開2003−158153号公報

【特許文献4】特許第3417281号公報

【特許文献5】特開2007−12953号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、従来技術において、半導体素子と回路基板を接合する際のバンプ(はんだ)の融解により、半導体素子と回路基板との隙間が狭くなり、アンダーフィルの注入が阻害されるという課題がある。本発明は、フリップチップ実装後のアンダーフィルの注入を阻害しにくい、半導体素子と回路基板とのバンプを介して接合された半導体装置およびその接合方法を提供することを目的とする。

【課題を解決するための手段】

【0014】

上記の課題を解決する為に、本発明の半導体装置は、

第1の電極部と当該第1の電極部上に設けられた第1のバンプとを有する半導体素子と、

第2の電極部と当該第2の電極部上に設けられた第2のバンプとを有する回路基板と、

前記第1のバンプと前記第2のバンプの融点よりも低い融点を有して、当該第1のバンプと当該第2のバンプとを電気的に接合する接合部とを備える。

【発明の効果】

【0015】

本発明は、バンプを溶かさずに電気的に接合するので、半導体素子と回路基板との隙間を広いまま維持できる。

【図面の簡単な説明】

【0016】

【図1】本発明の第1の実施例に係る半導体素子の回路基板への実装方法の説明図である。

【図2】本発明の第2の実施例に係る半導体素子の回路基板への実装方法の説明図である。

【図3】本発明の第3の実施例に係る半導体素子の回路基板への実装方法の説明図である。

【図4】従来例の技術に係る半導体素子の回路基板への実装方法の説明図である。

【発明を実施するための形態】

【0017】

以下に、本発明にかかる実施の形態を図面に基づいて詳細に説明する。

【0018】

(第1の実施形態)

図1を参照して、本発明の第1の実施形態に係る半導体素子の回路基板への実装方法について、3つの行程に分けて説明する。

【0019】

まず、図1(A)に示すように、電極部102に凸状のバンプ105が形成された半導体素子101と、電極部104に凸状のバンプ106が形成された回路基板103とが、バンプ105およびバンプ106が対向するように配される。バンプ105およびバンプ106のどちらか一方あるいは両方の先端に、熱硬化性樹脂107に導電性フィラー108が混合された導電性ペースト110が、例えば転写方式等の手段で塗布されている。

【0020】

半導体素子101および回路基板103は、バンプ105およびバンプ106が当接するように互いに近づけられる。具体的には、電子部品搭載装置において、部品保持部材の先端の接合ツールにより、上記前工程でバンプ105が電極部102上に形成された半導体素子101を吸着保持しつつ、該半導体素子101を、上記前工程で準備された回路基板103に対して、半導体素子101の電極部102が対応する回路基板103の電極部104上に位置するように位置合わせした後に、半導体素子101を回路基板103に実装する。この位置合わせは、公知の位置認識動作を使用する。そして、バンプ105およびバンプ106を構成する材料の融点より低温でかつ導電性ペースト110の導電性フィラー108の融点および熱硬化性樹脂107の硬化温度より高温で所定時間加熱される。

【0021】

熱硬化性樹脂107が硬化する前に、熱硬化性樹脂107は融解してバンプ105とバンプ106の当接部の周囲に集まる。そして、熱硬化性樹脂107は融解した導電性フィラー108の周囲にバンプ105とバンプ106の当接部の周囲で硬化する。この状態で加熱を停止することによって、導電性フィラー108をバンプ105とバンプ106との当接部の周囲或いは一部を覆うよう状態で固化させて電気的接合させ、熱硬化性樹脂107を固化した導電性フィラー108の周囲或いは一部を覆わせる。

【0022】

所定時間の加熱後に、図1(B)に示すように、バンプ105とバンプ106は、互いに当接する先端部の周囲で導電性フィラー108によって蝋付されて、電気的に接合される。この場合、バンプ105およびバンプ106は溶融されずに互いの先端部で接触しおり、その先端部の周囲の空間で溶融した導電性フィラー108が固化する。個化した導電性フィラー108によってバンプ105とバンプ106とが蝋付けされて、電気的に接合される。そして、固化した導電性フィラー108の周囲で硬化した熱硬化性樹脂107によって部分的或いは全体的に覆われて、バンプ105とバンプ106の接合部が保護される。

【0023】

結果、半導体素子101と回路基板103との間の距離は、実装(加熱)の前後で実質的に変化がなく、さらに隣り合うバンプ105あるいはバンプ106の距離も実装(加熱)の前後で実質的に変化がなく。半導体素子101と回路基板103との間の隙間も確保できる。このようにして、半導体素子401と回路基板403との間に確保された隙間に、絶縁性樹脂から成るアンダーフィル109が注入される。そして、アンダーフィル109の硬化温度まで加熱されて、図1(C)に示す半導体装置が出来上がる。

【0024】

なお、導電性ペースト110中の導電性フィラー108の量は、好ましくは導電性フィラー108が固化した場合に、バンプ105とバンプ106が互いに当接する先端部の周囲の空間内におさまり、バンプ105およびバンプ106の径方向にはみ出さないように決められる。さらに、導電性ペースト110中の熱硬化性樹脂107の量も、好ましくは熱硬化性樹脂107が固化した場合に、固化した導電性フィラー108の周囲の空間内におさまり、バンプ105およびバンプ106の径方向にはみ出さないように決められる。

【0025】

このように、バンプ105とバンプ106とを溶融接合させないので、従来技術におけるようなフラックスを用いないので、その洗浄除去も不要である。そのために、実装された半導体素子101と回路基板103とを、従来に較べてより大きな空間に注入された熱硬化性樹脂107によって確実に保持できる。

【0026】

なお、電極部102としては、Alパッドの電極、なお材質はAuやCu、下地としてNi等のメッキをした上に金属をメッキした電極でもよい。バンプ105は、電極部102に、はんだボールマウンタ装置等を用いて形成される。バンプ105のはんだ組成には、例えばスズ系合金単一またはそれら合金の混合物、具体的にはSn−Bi系、Sn−In系、Sn−Bi−In系、Sn−Ag系、Sn−Cu系、Sn−Ag−Cu系、Sn−Ag−Bi系、Sn−Cu−Bi系、Sn−Ag−Cu−Bi系、Sn−Ag−In系、Sn−Cu−In系、Sn−Ag−Cu−In系、およびSn−Ag−Cu−Bi−In系からなる群から選ばれる合金組成を用いることができる。特にSn−Ag系やSn−Ag−Cu系の群から選ばれる合金組成を用いることが好ましい。

【0027】

回路基板103の電極部104上に、バンプ106を形成する。バンプ106の形成方法や材質は、バンプ105と同じであってもよいし、異なっていてもよい。例えば、蒸着法やソルダーペーストによる形成方法でもよい。回路基板103には、セラミック多層基板、FPC、ガラス布積層エポキシ基板(ガラエポ基板)やガラス布積層ポリイミド樹脂基板、アラミド不織布エポキシ基板(例えば、パナソニック株式会社製の登録商標アリブ「ALIVH」として販売されている樹脂多層基板)などが用いられる。また、半導体素子と同じ材質、例えばSiなどをベースとしたものでもよい。

【0028】

回路基板103上の電極部104は、例としてCuの上にNiをメッキし表面をAuのフラッシュメッキしたものを使用するが、上記半導体素子101の電極部102と材質が同じであってもよいし、異なっていてもよい。熱硬化性樹脂107は絶縁性樹脂と硬化剤と、酸化膜除去効果を有する活性剤とを主成分とし、選択により、粘度調整/チクソ性付与添加剤を適宜加えることができる。

【0029】

絶縁性樹脂109は、エポキシ樹脂、ウレタン樹脂、アクリル樹脂、ポリイミド樹脂、ポリアミド樹脂、ビスマレイミド、フェノール樹脂、ポリエステル樹脂、シリコン樹脂、オキセタン樹脂など、様々な樹脂を含むことができる。これらは単独で用いてもよく、2種類以上を組み合わせて用いてもよい。これらのうちでは、特にエポキシ樹脂が好適である。

【0030】

エポキシ樹脂には、ビスフェノール型エポキシ樹脂、多官能エポキシ樹脂、可撓性エポキシ樹脂、臭素化エポキシ樹脂、グリシジルエステル型エポキシ樹脂、および高分子型エポキシ樹脂の群から選ばれるエポキシ樹脂も用いることができる。例えば、ビスフェノールA型エポキシ樹脂、ビスフェノールF型エポキシ樹脂、ビスフェノールS型エポキシ樹脂、ビフェニル型エポキシ樹脂、ナフタレン型エポキシ樹脂、フェノールノボラック型エポキシ樹脂、およびクレゾールノボラック型エポキシ樹脂などが好適に用いられる。これらを変性させたエポキシ樹脂も用いられる。これらは単独で用いてもよく、2種以上を組

み合わせて用いてもよい。

【0031】

上記のような熱硬化性樹脂と組み合わせて用いる硬化剤としては、チオール系化合物、変性アミン系化合物、多官能フェノール系化合物、イミダゾール系化合物、および酸無水物系化合物の群から選ばれる化合物を用いることができる。これらは単独で用いてもよく、2種以上を組み合わせて用いてもよい。硬化剤は、導電性ペーストの使用環境や用途に応じて、好適なものが選択される。

【0032】

酸化膜除去効果を有する活性剤としては、導電性ペーストを加熱硬化する温度域で、被着体である電極あるいは合金粒子表面の酸化膜を除去し、溶融接合させることができる還元力を有するものを用いる。JIS Z3283に記載されているようなロジンまたは変性ロジンを主剤とし、所望により活性化成分としてアミンのハロゲン塩、有機酸若しくはアミン有機酸塩を含むものなどを用いることができる。

【0033】

例えば飽和脂肪族モノカルボン酸であるラウリン酸、ミリスチン酸、パルミチン酸、ステアリン酸、不飽和脂肪族モノカルボン酸であるクロトン酸、飽和脂肪族ジカルボン酸であるシュウ酸、マロン酸、コハク酸、グルタル酸、アジピン酸、ピメリン酸、スベリン酸、アゼライン酸、セバシン酸、不飽和脂肪族ジカルボン酸であるマレイン酸、フマル酸、芳香族系カルボン酸であるフタルアルデヒド酸、フェニル酪酸、フェノキシ酢酸、フェニルプロピオン酸、エーテル系ジカルボン酸であるジグリコール酸、チオジグリコール酸、ジチオジグリコール酸、アミン塩酸塩であるエチルアミン塩酸塩、ジエチルアミン塩酸塩、ジメチルアミン塩酸塩、シクロヘキシルアミン塩酸塩、トリエタノールアミン塩酸塩、グルタミン酸塩酸塩、アミン臭化水素酸塩であるジエチルアミン臭化水素酸塩、シクロヘキシルアミン臭化水素酸塩、他にアビエチン酸、アスコルビン酸などが挙げられる。

【0034】

粘度調整/チクソ性付与添加剤としては、無機系あるいは有機系のものが使用できる。例えば、無機系であれば、シリカやアルミナなどが用いられ、有機系であれば固形のエポキシ樹脂や低分子量のアマイド、ポリエステル系、ヒマシ油の有機誘導体などが用いられる。これらは単独で用いてもよく、2種以上を組み合わせて用いてもよい。

【0035】

導電性(はんだ)フィラー108には、例えばスズ系合金単一またはそれら合金の混合物のはんだ材料を用いることができる。具体的には、Sn−Bi系、Sn−In系、Sn−Bi−In系、Sn−Ag系、Sn−Cu系、Sn−Ag−Cu系、Sn−Ag−Bi系、Sn−Cu−Bi系、Sn−Ag−Cu−Bi系、Sn−Ag−In系、Sn−Cu−In系、Sn−Ag−Cu−In系、およびSn−Ag−Cu−Bi−In系からなる群から選ばれる合金組成を用いることができる。特にSn42Bi58、Sn48In52、Sn16Bi56In28、SnAg3CuO.5、およびSnAg3.5Bi0.5In8の群から選ばれる合金組成を用いることが好ましい。

【0036】

しかし、バンプ105或いは、バンプ106の材料として選択された、はんだの融点以下の融点をもつ合金組成が選択されなければいけない。好ましくは、バンプ105或いは、バンプ106の材料として選択された、はんだの融点より約10℃以上低い融点を持つものがよい。また、導電性フィラー108の融点は、熱硬化性樹脂107が硬化開始する温度以上の融点を持つものから選択される。好ましくは、熱硬化性樹脂107が硬化開始する温度より約10〜20℃高い融点を持つ合金組成がよい。

【0037】

合金粒子は、微細な粒子状の形態、好ましくは球状粒子の形態で供給される。所定の組成の合金を調製した後に、アトマイズや転動造粒等の操作によって粒状化することにより、球状粒子の形態のものが得られる。球状粒子は、一般に、約1〜50μmの粒子径のものでよく、約10〜40μmの粒子径を有するものがさらに好ましい。

【0038】

熱硬化性樹脂107と導電性フィラー108の混合割合は、例えば熱硬化性樹脂107を約100重量部とするなら、導電性フィラー108は、約1〜50重量部としてよい。しかし、本発明はこれに限定されず、適宜選択され得る。

【0039】

絶縁性樹脂109としては、一般的にアンダーフィルや封止剤として市販されているものでよく、熱硬化性樹脂107と同じものでもよい。好ましくは、酸化膜除去効果を有する活性剤は添加されていない方がよい。

【0040】

(第2の実施形態)

図2を参照して、本発明の第2の実施形態にかかる半導体素子を回路基板に実装する方法について説明する。図2(A)に示すように、本実施形態においては、回路基板103が回路基板203に置き換えられている点を除いて、第1の実施の形態におけるのと同様に構成されている。なお、回路基板203は、回路基板103において、バンプ106がハンダメッキバンプ206に置き換えられている。

【0041】

ハンダメッキバンプ206は、その形成方法と形状がバンプ106と異なる。つまり、ハンダメッキバンプ206は、電解或いは無電解法を用いて、概ね平板状に形成される。ハンダメッキバンプ206の組成は、バンプ105と同じであってもよいし、異なっていてもよい。

【0042】

本実施の形態においても、図2(B)に示すように、凸状のバンプ105の先端と、平板状のハンダメッキバンプ206の直面との当接部の周囲に導電性フィラー108が固化して、その周囲に熱硬化性樹脂107が硬化して、バンプ105とハンダメッキバンプ206が電気的かつ物理的に接合される。なお、固化した導電性フィラー108と硬化した熱硬化性樹脂107は、概ねハンダメッキバンプ206およびバンプ105の輪郭程度に収まる。よって、半導体素子101と回路基板203との間には、図2(C)に示すように、アンダーフィルである絶縁性樹脂109を注入する十分な空間(隙間)が確保できる。

【0043】

(第3の実施形態)

図3を参照して、本発明の第3の実施形態にかかる半導体素子の回路基板への実装方法について説明する。図3(A)に示すように、本実施形態においては、回路基板101が回路基板301に置き換えられている点を除いて、第2の実施の形態におけるのと同様である。なお、回路基板301は、回路基板201において、バンプ105がハンダメッキバンプ305に置き換えられている。

【0044】

互いに接合されるハンダメッキバンプ305およびハンダメッキバンプ206が共に平板状であるので、図3(B)に示すように、導電性フィラー108はハンダメッキバンプ305およびハンダメッキバンプ206の主面の間に平板状に固化する。つまり、ハンダメッキバンプ305およびハンダメッキバンプ206はそれぞれの主面で固化した導電性フィラー108によって全面的に接合される。この固化した導電性フィラー108による接合部は、硬化した導電性フィラー108によって覆われる。

【0045】

この場合、導電性フィラー108は、概ね固化したハンダメッキバンプ305およびハンダメッキバンプ206の輪郭内におさまり、硬化した導電性フィラー108は、ハンダメッキバンプ305およびハンダメッキバンプ206の外形より若干はみ出す。よって、半導体素子101と回路基板203との間には、図2(C)に示すように、アンダーフィルである絶縁性樹脂109を注入する十分な空間(隙間)が確保できる。なお、ハンダメッキバンプ305とハンダメッキバンプ206が、導電性フィラー108によって全面的に接合されるので、より確実な電気的接合が得られる。

【0046】

以下に、実際の半導体素子の回路基板の接合に本発明を適用した実施例について述べる。

【0047】

[実施例]

半導体素子として、厚み100μm、8mm□Siの面内全域にAlパッドの電極(サイズは85×85μm)が計160個あるものを使用した。その半導体素子の電極は、各180μm以上の間隔で配列されている。

【0048】

回路基板は、ALIVH基板で厚み340μm、上記半導体素子の電極に対応する箇所に、100μm□サイズで、Cuの下地にNiとフラッシュAuメッキを設けた電極を使用した。なお、基板の電極の中心と半導体素子の電極の中心が一致するように設計されている。

【0049】

熱硬化性樹脂と導電性(はんだ)フィラーを混合した導電性ペーストは、ビスフェノールA型エポキシ樹脂に潜在性のイミダゾール系硬化剤を混合し一液にした熱硬化性樹脂に、球形状で平均粒子径21μmのSnAgBiIn合金粒子(融点約195℃)からなる導電性フィラーと、酸化膜除去効果を有するアビエチン酸を主とする活性剤を混合して用いた。

【0050】

比較例1〜3および実施例1〜3で作成した後に、半導体素子と回路基板との隙間に絶縁性樹脂(アンダーフィル)を注入し、加熱硬化後に半導体素子と回路基板との間隔を測定した結果を表1に示す。アンダーフィルの充填は、硬化させた後にSAT(超音波顕微鏡)にてボイド(気泡)を観察し、ボイドが10箇所以上確認された時は×、5箇所以下の時は○、それ以外では△と評価した。

【0051】

比較例1:

半導体素子の電極上に、はんだボールマウンタ装置を用いて、SnAgCu組成(融点218℃)で直径85μmのはんだボールバンプを作成した。一方、回路基板の電極上に、ソルダーペースト印刷法にてSnAgCu組成(融点218℃)で高さ80μmのバンプを作成した。半導体素子の電極上のバンプにフラックスを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、230℃まで加熱した。

【0052】

実施例1:

比較例1と同様に、バンプを作成し、半導体素子の電極上のバンプに導電性ペーストを転写した後に、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、200℃まで加熱した。

【0053】

比較例2:

半導体素子の電極上に、はんだボールマウンタ装置を用いて、SnAg組成(融点220℃)で直径85μmのはんだボールバンプを作成した。一方、回路基板の電極上に、電解メッキ法にてSnAg組成(融点220℃)で高さ50μmのハンダメッキバンプを作成した。半導体素子の電極上のバンプにフラックスを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、230℃まで加熱した。

【0054】

実施例2:

比較例2と同様に、バンプを作成し、半導体素子の電極上のバンプに導電性ペーストを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、200℃まで加熱した。

【0055】

比較例3:

半導体素子の電極上に、電解メッキ法で、SnAg組成(融点220℃)で高さ50μmのハンダメッキバンプを作成した。一方、回路基板の電極上に、電解メッキ法にてSnAg組成(融点220℃)で高さ50μmのハンダメッキバンプを作成した。半導体素子の電極上のバンプにフラックスを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、230℃まで加熱した。

【0056】

実施例3:

比較例3と同様に、ハンダメッキバンプを作成し、半導体素子の電極上のハンダメッキバンプに導電性ペーストを転写した後、実装機にて回路基板の電極上のバンプと位置合わせを行い実装し、200℃まで加熱した。

【0057】

【表1】

【0058】

表1より、従来構造の比較例に対して、いずれの実施例においても半導体素子と回路基板の間隔は大きくなり、アンダーフィルの充填も良化の効果が見てとれる。

【産業上の利用可能性】

【0059】

本発明は、半導体素子と回路基板とがバンプを介して接合される半導体装置に広く適用できる。

【符号の説明】

【0060】

101、301、401 半導体素子

102 電極部

103、203、403 回路基板

104 電極部

105、106、405、405i、405c バンプ

206、305 ハンダメッキバンプ

107 熱硬化性樹脂

108 導電性フィラー

109 絶縁性樹脂

410 フラックス

【特許請求の範囲】

【請求項1】

第1の電極部と当該第1の電極部上に設けられた第1のバンプとを有する半導体素子と、

第2の電極部と当該第2の電極部上に設けられた第2のバンプとを有する回路基板と、

前記第1のバンプと前記第2のバンプの融点よりも低い融点を有して、当該第1のバンプと当該第2のバンプとを電気的に接合する接合部とを備える半導体装置。

【請求項2】

前記接合部の周囲或いは一部を覆う熱硬化性絶縁樹脂部をさらに備える、請求項1に記載の半導体装置。

【請求項3】

前記第1のバンプと前記第2のバンプは共に凸状に形成されて互いに先端部近傍で当接し、

前記接合部は当該当接部の周囲或いは一部を覆うように形成されていることを特徴とする、請求項1に記載の半導体装置。

【請求項4】

前記第1のバンプと前記第2のバンプの一方は凸状に形成され他方は平板状に形成されて、先端部近傍が平板面に当接し、

前記接合部は当該当接部の周囲或いは一部を覆うように形成されていることを特徴とする、請求項1に記載の半導体装置。

【請求項5】

前記第1のバンプと前記第2のバンプは共に平板状に形成されて、互いに平板面で前記接合部を介して当接していることを特徴とする、請求項1に記載の半導体装置。

【請求項6】

第1のバンプを有する半導体素子と第2のバンプとを、当該第1のバンプと当該第2のバンプの融点より低い融点を有する導電性材で電気的に接合させて半導体装置を製造する方法であって、

前記第1のバンプおよび前記第2のバンプの少なくとも一方に、前記導電性材と熱硬化性絶縁樹脂とが皇后されたペーストを塗布するステップと、

前記第1のバンプおよび前記第2のバンプを前記ペーストを介して互いに当接させるステップと、

前記1のバンプおよび前記第2のバンプを前記ペーストを介して互いに当接下状態で、当該導電性材の融点および前記熱硬化性絶縁樹脂の硬化温度以上かつ当該1のバンプおよび当該第2のバンプの融点より低い温度で加熱するステップとを備える方法。

【請求項7】

前記導電性材の溶融後かつ前記熱硬化性樹脂の硬化後に加熱を停止して、当該導電性材を前記第1のバンプと前記第2のバンプとの当接部の周囲或いは一部を覆うように固化させ、前記熱硬化性絶縁樹脂を当該固化した導電性材の周囲或いは一部を覆うように硬化させるステップをさらに備える請求項6に記載の方法。

【請求項1】

第1の電極部と当該第1の電極部上に設けられた第1のバンプとを有する半導体素子と、

第2の電極部と当該第2の電極部上に設けられた第2のバンプとを有する回路基板と、

前記第1のバンプと前記第2のバンプの融点よりも低い融点を有して、当該第1のバンプと当該第2のバンプとを電気的に接合する接合部とを備える半導体装置。

【請求項2】

前記接合部の周囲或いは一部を覆う熱硬化性絶縁樹脂部をさらに備える、請求項1に記載の半導体装置。

【請求項3】

前記第1のバンプと前記第2のバンプは共に凸状に形成されて互いに先端部近傍で当接し、

前記接合部は当該当接部の周囲或いは一部を覆うように形成されていることを特徴とする、請求項1に記載の半導体装置。

【請求項4】

前記第1のバンプと前記第2のバンプの一方は凸状に形成され他方は平板状に形成されて、先端部近傍が平板面に当接し、

前記接合部は当該当接部の周囲或いは一部を覆うように形成されていることを特徴とする、請求項1に記載の半導体装置。

【請求項5】

前記第1のバンプと前記第2のバンプは共に平板状に形成されて、互いに平板面で前記接合部を介して当接していることを特徴とする、請求項1に記載の半導体装置。

【請求項6】

第1のバンプを有する半導体素子と第2のバンプとを、当該第1のバンプと当該第2のバンプの融点より低い融点を有する導電性材で電気的に接合させて半導体装置を製造する方法であって、

前記第1のバンプおよび前記第2のバンプの少なくとも一方に、前記導電性材と熱硬化性絶縁樹脂とが皇后されたペーストを塗布するステップと、

前記第1のバンプおよび前記第2のバンプを前記ペーストを介して互いに当接させるステップと、

前記1のバンプおよび前記第2のバンプを前記ペーストを介して互いに当接下状態で、当該導電性材の融点および前記熱硬化性絶縁樹脂の硬化温度以上かつ当該1のバンプおよび当該第2のバンプの融点より低い温度で加熱するステップとを備える方法。

【請求項7】

前記導電性材の溶融後かつ前記熱硬化性樹脂の硬化後に加熱を停止して、当該導電性材を前記第1のバンプと前記第2のバンプとの当接部の周囲或いは一部を覆うように固化させ、前記熱硬化性絶縁樹脂を当該固化した導電性材の周囲或いは一部を覆うように硬化させるステップをさらに備える請求項6に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2010−263014(P2010−263014A)

【公開日】平成22年11月18日(2010.11.18)

【国際特許分類】

【出願番号】特願2009−111358(P2009−111358)

【出願日】平成21年4月30日(2009.4.30)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成22年11月18日(2010.11.18)

【国際特許分類】

【出願日】平成21年4月30日(2009.4.30)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]