半導体装置

【課題】半導体チップ上に積層された半導体チップの放熱を改善することが可能な半導体装置を提供する。

【解決手段】周辺部に接続パッド22を有するパッケージ基板21、上面の周辺部に形成された接続パッド12、及び上面の接続パッド12より内側に形成され、接続パッド12に接続された接続パッド13を有し、下面をパッケージ基板21に固定された半導体チップ11、下面の最も外側の周辺部を取り巻く1列が、電源または接地に接続された接続パッド16を有し、下面の接続パッド16の列より内側に、信号線に接続された接続パッド17を有し、接続パッド16及び接続パッド17が半田バンプ25を介して対応する位置の接続パッド13に電気的に接続且つ固定された半導体チップ15、並びに、接続パッド16が半田バンプ25及び接続パッド13を経由して接続された接続パッド12と、接続パッド22とを電気的に接続する金属細線27を備える。

【解決手段】周辺部に接続パッド22を有するパッケージ基板21、上面の周辺部に形成された接続パッド12、及び上面の接続パッド12より内側に形成され、接続パッド12に接続された接続パッド13を有し、下面をパッケージ基板21に固定された半導体チップ11、下面の最も外側の周辺部を取り巻く1列が、電源または接地に接続された接続パッド16を有し、下面の接続パッド16の列より内側に、信号線に接続された接続パッド17を有し、接続パッド16及び接続パッド17が半田バンプ25を介して対応する位置の接続パッド13に電気的に接続且つ固定された半導体チップ15、並びに、接続パッド16が半田バンプ25及び接続パッド13を経由して接続された接続パッド12と、接続パッド22とを電気的に接続する金属細線27を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スタック型MCPの半導体装置に関する。

【背景技術】

【0002】

デジタルネットワーク情報社会の急速な進展に対応し、携帯電話に代表されるモバイル情報端末等は高性能化、高・多機能化、及び小型化等が求められている。そして、これらを支えるLSI等の半導体装置は、例えば、1チップの中に全ての回路を詰め込む構成のSoC(System on a Chip)の開発が行われている。しかしながら、小型化、特に実装面積の低減、適する製造プロセスの採用等からは、全てを1チップ化することが必ずしも最適であるわけではない。

【0003】

半導体チップを三次元に積層するCoC(Chip on Chip)、または、スタック型MCP(St-MCP:Stacked Multi Chip Package)等と称される半導体装置の開発・製品化が進められている。例えば、ダイパッドまたはフィルム状基板に固定された第1の半導体チップの上に、平面視において第1の半導体チップより小さい第2の半導体チップが、互いに対向配置した状態で電気的に接続され、第2の半導体チップと半導体装置の外部との間で信号の送受を行うための信号用の端子部を、第2の半導体チップの側方位置の第1の半導体チップ上に形成し、対向して接続した各端子部を介して導通する構造のスタック型MCPの半導体装置が開示されている(例えば、特許文献1参照。)。

【0004】

この、開示されたスタック型MCPの半導体装置は、上側の第2の半導体チップと半導体装置の外部との間で信号の送受を行うことができる構成となっている。より大きな下側の第1の半導体チップは内部リードまたはパッケージ基板(インタポーザ)等に固定され、更にボンディングワイヤ等を介して、半導体装置の外部に接続されるので、下側の半導体チップは、上側の半導体チップと比較して、熱の放出が比較的容易である。

【0005】

しかしながら、半導体装置は、高速化等が進み、発熱量が増してくると、発熱量が放熱量を超えて、より高い温度に曝される機会が増えてくる結果、半導体装置の誤動作が懸念されるという問題が発生する。特に、半導体装置の外部に直接接続されない2層構造の上側の半導体チップの誤動作が懸念されるという問題を有している。

【特許文献1】特開2000−22074号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、半導体チップ上に積層された半導体チップの放熱を改善することが可能な半導体装置を提供する。

【課題を解決するための手段】

【0007】

本発明の一態様の半導体装置は、周辺部に第1の接続パッドを有するパッケージ基板と、上面の周辺部に形成された第2の接続パッド、及び上面の前記第2の接続パッドより内側に形成され、前記第2の接続パッドに接続された第3の接続パッドを有し、下面を前記パッケージ基板に固定された第1の半導体チップと、下面の最も外側の周辺部を取り巻く少なくとも1列が、電源または接地に接続された外側接続パッドを有し、下面の前記外側接続パッドの列より内側に、信号線に接続された内側接続パッドを有し、前記外側接続パッド及び前記内側接続パッドが第1の導電材を介して対応する位置の前記第3の接続パッドに電気的に接続且つ固定された第2の半導体チップと、前記外側接続パッドが前記第1の導電材及び前記第3の接続パッドを経由して接続された前記第2の接続パッドと、前記第1の接続パッドとを電気的に接続する第2の導電材とを備えていることを特徴とする。

【発明の効果】

【0008】

本発明によれば、半導体チップ上に積層された半導体チップの放熱を改善することが可能な半導体装置を提供することが可能である。

【発明を実施するための最良の形態】

【0009】

以下、本発明の実施例について、図面を参照しながら説明する。各図では、同一の構成要素には同一の符号を付す。

【実施例1】

【0010】

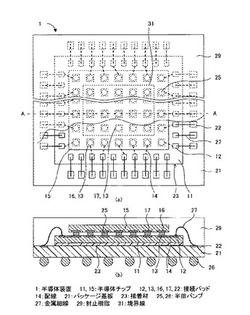

本発明の実施例1に係る半導体装置について、図1及び図2を参照しながら説明する。図1は半導体装置の構成を模式的に示す図で、図1(a)は半導体装置の一部を切り欠いて平面的に示す図、図1(b)は図1(a)のA−A線に沿った全体の断面図である。図2は半導体装置の上側に積層される半導体チップの下側を模式的に示す平面図である。なお、半導体装置のパッケージ基板に対して、半導体チップが積層されている側を上、対向するバンプ電極の側を下という。

【0011】

図1に示すように、半導体装置1は、インターポーザ等とも呼ばれるパッケージ基板21の上に、回路形成面が互いに対面するように積層された半導体チップ11、15が固定されている。

【0012】

半導体装置1は、周辺部に第1の接続パッドである接続パッド22を有するパッケージ基板21、並びに、上面の周辺部に形成された第2の接続パッドである接続パッド12、及び上面の接続パッド12より内側に形成され、接続パッド12に接続された第3の接続パッドである接続パッド13を有し、下面をパッケージ基板21に固定された第1の半導体チップである半導体チップ11を有している。半導体装置1は、下面の最も外側の周辺部を取り巻く1列が、電源または接地に接続された外側接続パッドである接続パッド16を有し、下面の接続パッド16の列より内側に、信号線に接続された内側接続パッドである接続パッド17を有し、接続パッド16及び接続パッド17が第1の導電材である半田バンプ25を介して対応する位置の接続パッド13に電気的に接続且つ固定された第2の半導体チップである半導体チップ15、並びに、接続パッド16が半田バンプ25及び接続パッド13を経由して接続された接続パッド12と、接続パッド22とを電気的に接続する第2の導電材である金属細線27を備えている。

【0013】

また、半導体装置1は、外部接続端子となる半田バンプ26をパッケージ基板21の下面に有している。図示を省略するが、パッケージ基板21は、上面の接続パッド22と接続された配線の一部をなすランドを下面に設けて、ランドに半田バンプ26が接続され、半田バンプ26との接続部を除いたランド及び下面がソルダレジストで被われている。パッケージ基板21の上面は、周辺部に配設された接続パッド22を除いて、ソルダレジストで被われている。パッケージ基板21の上面の中央部に、例えば、エポキシ樹脂を主成分とする接着材23を介して、半導体チップ11の下面が接着、固定されている。

【0014】

更に、半導体装置1は、パッケージ基板21の上面、半導体チップ11、15、金属細線27、半田バンプ25を被って、例えば、エポキシ樹脂を主成分とする封止樹脂29が形成されている。互いに対面する半導体チップ11、15の間には、封止樹脂29が充填されるが、封止樹脂29の代わりにアンダーフィル材(図示略)を充填することは可能である。半導体装置1は、半田バンプ26を除くと、ほぼ、直方体の外形を有している。

【0015】

半導体チップ11の上面の最も外側は、周知のように、層間絶縁膜の中に配線層が形成され、周辺部に、ワイヤボンディングのための接続パッド12が層間絶縁膜及び表面保護膜から露出し、中央部に、半導体チップ15と接続するための接続パッド13が露出している。半導体チップ15は、半導体チップ11の接続パッド12のなす列の内側、すなわち半導体チップ11の中央部に収められる大きさである。

【0016】

図2に示すように、半導体チップ15の下面にほぼ等間隔の行列状に、つまり格子状に配列された接続パッド16及び接続パッド17が、図示を省略するが、半導体チップ15の最も外側の層をなす配線層で形成されている。接続パッド16と接続パッド17は、破線で示した矩形の境界線31で区分けされ、境界線31の外側に接続パッド16、内側に接続パッド17が配置されている。接続パッド16は、境界線31の外側にある矩形(図示略)の辺の上に、ほぼ等間隔で配列されている。接続パッド16及び接続パッド17のそれぞれの中央部に、半田バンプ25が位置する関係にある。なお、製造プロセス上、半田バンプ25は、半導体チップ15の接続パッド16、17に配設されるとは限らない。

【0017】

接続パッド16は、半導体チップ15が電気的に必要とする接続パッド数より多く配設されている。接続パッド16は、一部が電源に接続され、残りが接地に接続されている。電源供給のための接続パッド16は、必ずしも同電位とは限らず、必要とする電位に近い電位が供給される。なお、接続パッド16は、接続パッド17と同等の大きさに形成されているが、接続パッド17より大きく形成され、大きな接続パッド17に対応した、より大きな半田バンプ、より大きな接続パッド13とすることは可能である。

【0018】

接続パッド16は、電源と接地とに振り分けずに、例えば、全てを電源に接続することは可能であり、逆に、全てを接地に接続することは可能である。接続パッド16が、電源または接地の一方にのみ接続される場合、接続パッド17の一部が電源または接地の他方に接続される。また、接続パッド16の一部を半導体チップ15の電源及び接地のどちらにも接続せず、独立に存在するパッド、つまり放熱のためのパッドとすることは可能である。

【0019】

接続パッド17は、少なくとも一部が信号の配線に接続される。接続パッド17は、境界線31の内側の半導体チップ15の下面全面に分布しているが、必要とする信号の数に応じて、例えば、境界線31の内側に接続パッド17のない領域が形成されることは差し支えない。

【0020】

図1に示すように、接続パッド12及び接続パッド13は、図示を省略するが、半導体チップ11の最上層(最も外側の層)をなす配線層で形成されている。接続パッド16に対向する全ての接続パッド13は、半導体チップ11上面で、配線14により、接続パッド12と接続されている。配線14は、例えば、半導体チップ11の最上層または最上層に近い配線層で形成され、接続パッド12と接続パッド13とは、可能な限り断面積が大きく、距離が短くなるように接続されることが好ましい。なお、接続パッド12の一部は、信号用に使用される。

【0021】

半田バンプ25は、例えば、接続方向に垂直な断面の径が30〜40μm、接続距離が20〜30μm程度である。金属細線37は、例えば、20〜30μm径のAuまたはAl等を主成分とするワイヤであり、半導体チップ11の接続パッド12から上方に引き出してループを形成して、パッケージ基板21の接続パッド22と接続されている。

【0022】

半導体チップ11は、例えば、ロジックLSI(Large Scale Integrated Circuit)であり、半導体チップ15は、例えば、メモリLSIである。

【0023】

次に、発熱及び放熱の経路等を説明する。半導体装置1は、半田バンプ26を介して、外部と接続される。従って、電源は、半田バンプ26、接続パッド22、金属細線27、及び接続パッド12を経由して、半導体チップ11に供給される。更に、電源は、接続パッド12から、配線14、接続パッド13、半田バンプ25、及び接続パッド16を経由して、半導体チップ15に供給される。接地は、電源と同様な、しかし、電源とは独立な配線を経由して、半導体チップ11及び半導体チップ15に接続される。

【0024】

半導体チップ11、15は、電源及び接地とは別の配線を経由して送られる駆動信号によって、トランジスタ等の能動素子が駆動され、その結果、電流が、能動素子、受動素子、配線等を流れ、更にリーク電流の発生等があり、ジュール熱を発生する。高集積化、高速化に伴って半導体チップは、必要な電流が増加し、発熱量も大きくなる。

【0025】

半導体チップ15で発生した熱は、一部が、封止樹脂29を伝導し、封止樹脂29の表面から放熱される。また、一部が、電源及び接地の配線を経由して半田バンプ26を伝導、また、半導体チップ15の半田バンプ26へ通ずる封止樹脂29、半導体チップ11、接着材23、及びパッケージ基板21を伝導して、半導体装置1が実装されたプリント基板(図示略)等へ放熱される。電気の良導体は、熱の良導体でもあり、半導体チップ15で発生した熱は、電源及び接地の配線を電気と同様な経路で、または、電源及び接地の配線の一部を経由して、パッケージ基板21の下面側に通ずる経路で放熱される。

【0026】

上述したように、半導体装置1は、半導体チップ15、半導体チップ11、及びパッケージ基板21のそれぞれの周辺部、すなわち半導体装置1の側面部に、電源または接地に接続された強化された放熱経路を有しているので、半導体チップ15で発生した熱を、半導体チップ15の周辺部に導き、半導体装置1の外部へ放熱することが可能である。スタック形MCPにおいては、それぞれの半導体チップ15、11の中心部でより高温になる傾向がある。半導体チップ11の中心部で発生する熱量が大きいので、半導体チップ15の中心部で発生する熱は、半導体チップ11の中心部を経路として半田バンプ26の側に流すことが難しい。中心部により大きな放熱経路を持たないパッケージ基板21を使用しているので、半導体チップ15の中心部と周辺部との温度差を利用して発生する熱を周辺部へ導き、更に、温度差を利用して半導体チップ11の周辺部へ導き、更に、温度差を利用してパッケージ基板21の周辺部から半田バンプ26の側に放熱することは可能である。

【0027】

半導体チップ15、半導体チップ11、及びパッケージ基板21に配設された電源または接地のための接続パッド16、13、12、22は、それぞれの周辺部を取り巻いて、しかも、数がより多く配置されているので、半導体装置1は、より大きな放熱経路が周辺部に確保された構成をなしている。半導体装置1の中心部は、放熱経路が増強されているわけではないので放熱を促進することはないが、周辺部は、放熱経路が増強されているので、半導体チップ15の放熱を促進することが可能となる。

【0028】

半導体装置1は、結果的に、2層構造の上側の半導体チップ15の温度の上昇が、特に、抑えられるので、誤動作の発生は抑制される。また、半導体装置1は、動作昇温時と保管時との温度差が小さくなるので、温度サイクルによる故障の頻度を低減することが可能である。

【0029】

半導体装置1は、電源または接地のための接続パッド16が、半導体チップ15の周囲を一周する位置にあって、より適する位置で半導体チップ15内の配線に接続が可能なので、すなわち、電源系が強化されているので、電源と接地との電位差が小さくなることを避けることが可能である。

【実施例2】

【0030】

本発明の実施例2に係る半導体装置について、図3を参照しながら説明する。図3は半導体装置の上側に積層される半導体チップの下側を模式的に示す平面図である。実施例1の半導体装置とは、上側の半導体チップが周辺部の2列からなる電源または接地のための接続パッドを有することが異なる。なお、実施例1と同一構成部分には同一の符号を付して、その説明は省略する。

【0031】

図3に示すように、上側の半導体チップ35は、下面にほぼ等間隔の行列状に、接続パッド36及び接続パッド37が配列されている。接続パッド36と接続パッド37は、矩形の境界線41で区分けされ、境界線41の外側に2列並列の接続パッド36、内側に2列並列の接続パッド37が配置されている。半導体チップ35の中央部は、接続パッド37が配置されていない。接続パッド36及び接続パッド37のそれぞれの中央部に、半田バンプ25が位置する関係にある。

【0032】

接続パッド36は、電源または接地のための接続パッドであり、接続パッド37は、少なくとも一部が信号用の接続パッドである。接続パッド37は、必要とする信号の数に応じて形成され、半導体チップ35の中央部に配設する必要がない。接続パッド36は、実施例1の接続パッド16、接続パッド37は、実施例1の接続パッド17に、それぞれ対応している。

【0033】

半導体チップ35は、電源または接地のための接続パッドの数が、実施例1の場合より、相対的に増加されている。半導体チップ35は、実施例1の半導体チップ15より、発熱量が多い場合、または、放熱の強化が必要な場合に相当する。一方、信号のための接続パッドの数は、相対的に少なくて済む場合である。

【0034】

図示を省略(図1参照)するが、半導体チップ35に対向する下層の半導体チップは、半導体チップ35が有する接続パッド36に対応する接続パッドを、上面の周辺部に有し、接続パッド37に対応する接続パッドを、上面の中央部に有している。下層の半導体チップは、実施例1の半導体チップ11の接続パッド12と同様に、接続パッド36に対応する接続パッドの外側に、金属細線用の接続パッドを有している。なお、この金属細線用の接続パッドは、1列に収まらない場合は、2列に並列して形成することが可能である。そして、金属細線用の接続パッドに対応した接続パッドが、実施例1のパッケージ基板21の接続パッド22と同様に、パッケージ基板上に形成されている。

【0035】

本実施例の半導体装置は、実施例1の半導体装置1と同様な放熱経路が、半導体装置の周辺部に確保可能である。従って、本実施例の半導体装置は、実施例1の半導体装置1が有する効果を同様に有している。しかも、接続パッド36が、相対的に数が多く配設されているので、より大きな放熱が可能となる。

【0036】

また、上側に積層される半導体チップの2列の接続パッド36が、電源または接地のために使用される例を上述したが、上記実施例2の半導体装置の変形例として、外側の矩形の辺の上に配列された接続パッド36を電源用として、内側の矩形の辺の上に配列された接続パッド36を接地用として、区分けすることは可能であり、逆に、外側の接続パッド36を接地用、内側の接続パッド36を電源用とすることは可能である。

【0037】

また、上側に積層される半導体チップの電源または接地のための接続パッド36は、2列配設される例を上述したが、上記実施例2の半導体装置の変形例として、電源または接地のための接続パッドが、3列以上配設されることは可能である。

【0038】

本発明は、上述した実施例に限定されるものではなく、本発明の要旨を逸脱しない範囲内で、種々、変形して実施することができる。

【0039】

例えば、実施例では、第1の半導体チップは、ロジックLSIであり、第2の半導体チップは、メモリLSIである半導体装置の例を示したが、第1の半導体チップが大きいとした上で、第1の半導体チップがメモリLSI、第2の半導体チップがロジックLSIとすることは可能である。その他、第1及び第2の半導体チップは、2つのロジックLSIの組合せ、または、2つのメモリLSIの組合せとすることは可能である。

【0040】

また、第1または第2の半導体チップは、アナログ回路を有するIC(Integrated Circuit)、内部にアナログ回路ブロックと制御論理回路ブロックを組み合わせた、いわゆるアナログ・デジタル混載LSI等であっても差し支えない。

【0041】

また、実施例では、BGA(Ball Grid Array)型のパッケージの例を示したが、リードフレームを使用したパッケージを使用することは可能である。

【0042】

その他、以下の付記に記載されるような構成が考えられる。

(付記1) 周辺部に第1の接続パッドを有するパッケージ基板と、上面の周辺部に形成された第2の接続パッド、及び上面の前記第2の接続パッドより内側に形成され、前記第2の接続パッドに接続された第3の接続パッドを有し、下面を前記パッケージ基板に固定された第1の半導体チップと、下面の最も外側の周辺部を取り巻く少なくとも1列が、電源または接地に接続された外側接続パッドを有し、下面の前記外側接続パッドの列より内側に、信号線に接続された内側接続パッドを有し、前記外側接続パッド及び前記内側接続パッドが第1の導電材を介して対応する位置の前記第3の接続パッドに電気的に接続且つ固定された第2の半導体チップと、前記外側接続パッドが前記第1の導電材及び前記第3の接続パッドを経由して接続された前記第2の接続パッドと、前記第1の接続パッドとを電気的に接続する第2の導電材とを備えている半導体装置。

【0043】

(付記2) 前記第1の半導体チップは、ロジックLSIであり、前記第2の半導体チップは、メモリLSIである付記1に記載の半導体装置。

【図面の簡単な説明】

【0044】

【図1】本発明の実施例1に係る半導体装置の構成を模式的に示す図で、図1(a)は半導体装置の一部を切り欠いて平面的に示す図、図1(b)は図1(a)のA−A線に沿った全体の断面図。

【図2】本発明の実施例1に係る半導体装置の上側に積層される半導体チップの下側を模式的に示す平面図。

【図3】本発明の実施例2に係る半導体装置の上側に積層される半導体チップの下側を模式的に示す平面図。

【符号の説明】

【0045】

1 半導体装置

11、15、35 半導体チップ

12、13、16、17、22、36、37 接続パッド

14 配線

21 パッケージ基板

23 接着材

25、26 半田バンプ

27 金属細線

29 封止樹脂

31、41 境界線

【技術分野】

【0001】

本発明は、スタック型MCPの半導体装置に関する。

【背景技術】

【0002】

デジタルネットワーク情報社会の急速な進展に対応し、携帯電話に代表されるモバイル情報端末等は高性能化、高・多機能化、及び小型化等が求められている。そして、これらを支えるLSI等の半導体装置は、例えば、1チップの中に全ての回路を詰め込む構成のSoC(System on a Chip)の開発が行われている。しかしながら、小型化、特に実装面積の低減、適する製造プロセスの採用等からは、全てを1チップ化することが必ずしも最適であるわけではない。

【0003】

半導体チップを三次元に積層するCoC(Chip on Chip)、または、スタック型MCP(St-MCP:Stacked Multi Chip Package)等と称される半導体装置の開発・製品化が進められている。例えば、ダイパッドまたはフィルム状基板に固定された第1の半導体チップの上に、平面視において第1の半導体チップより小さい第2の半導体チップが、互いに対向配置した状態で電気的に接続され、第2の半導体チップと半導体装置の外部との間で信号の送受を行うための信号用の端子部を、第2の半導体チップの側方位置の第1の半導体チップ上に形成し、対向して接続した各端子部を介して導通する構造のスタック型MCPの半導体装置が開示されている(例えば、特許文献1参照。)。

【0004】

この、開示されたスタック型MCPの半導体装置は、上側の第2の半導体チップと半導体装置の外部との間で信号の送受を行うことができる構成となっている。より大きな下側の第1の半導体チップは内部リードまたはパッケージ基板(インタポーザ)等に固定され、更にボンディングワイヤ等を介して、半導体装置の外部に接続されるので、下側の半導体チップは、上側の半導体チップと比較して、熱の放出が比較的容易である。

【0005】

しかしながら、半導体装置は、高速化等が進み、発熱量が増してくると、発熱量が放熱量を超えて、より高い温度に曝される機会が増えてくる結果、半導体装置の誤動作が懸念されるという問題が発生する。特に、半導体装置の外部に直接接続されない2層構造の上側の半導体チップの誤動作が懸念されるという問題を有している。

【特許文献1】特開2000−22074号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、半導体チップ上に積層された半導体チップの放熱を改善することが可能な半導体装置を提供する。

【課題を解決するための手段】

【0007】

本発明の一態様の半導体装置は、周辺部に第1の接続パッドを有するパッケージ基板と、上面の周辺部に形成された第2の接続パッド、及び上面の前記第2の接続パッドより内側に形成され、前記第2の接続パッドに接続された第3の接続パッドを有し、下面を前記パッケージ基板に固定された第1の半導体チップと、下面の最も外側の周辺部を取り巻く少なくとも1列が、電源または接地に接続された外側接続パッドを有し、下面の前記外側接続パッドの列より内側に、信号線に接続された内側接続パッドを有し、前記外側接続パッド及び前記内側接続パッドが第1の導電材を介して対応する位置の前記第3の接続パッドに電気的に接続且つ固定された第2の半導体チップと、前記外側接続パッドが前記第1の導電材及び前記第3の接続パッドを経由して接続された前記第2の接続パッドと、前記第1の接続パッドとを電気的に接続する第2の導電材とを備えていることを特徴とする。

【発明の効果】

【0008】

本発明によれば、半導体チップ上に積層された半導体チップの放熱を改善することが可能な半導体装置を提供することが可能である。

【発明を実施するための最良の形態】

【0009】

以下、本発明の実施例について、図面を参照しながら説明する。各図では、同一の構成要素には同一の符号を付す。

【実施例1】

【0010】

本発明の実施例1に係る半導体装置について、図1及び図2を参照しながら説明する。図1は半導体装置の構成を模式的に示す図で、図1(a)は半導体装置の一部を切り欠いて平面的に示す図、図1(b)は図1(a)のA−A線に沿った全体の断面図である。図2は半導体装置の上側に積層される半導体チップの下側を模式的に示す平面図である。なお、半導体装置のパッケージ基板に対して、半導体チップが積層されている側を上、対向するバンプ電極の側を下という。

【0011】

図1に示すように、半導体装置1は、インターポーザ等とも呼ばれるパッケージ基板21の上に、回路形成面が互いに対面するように積層された半導体チップ11、15が固定されている。

【0012】

半導体装置1は、周辺部に第1の接続パッドである接続パッド22を有するパッケージ基板21、並びに、上面の周辺部に形成された第2の接続パッドである接続パッド12、及び上面の接続パッド12より内側に形成され、接続パッド12に接続された第3の接続パッドである接続パッド13を有し、下面をパッケージ基板21に固定された第1の半導体チップである半導体チップ11を有している。半導体装置1は、下面の最も外側の周辺部を取り巻く1列が、電源または接地に接続された外側接続パッドである接続パッド16を有し、下面の接続パッド16の列より内側に、信号線に接続された内側接続パッドである接続パッド17を有し、接続パッド16及び接続パッド17が第1の導電材である半田バンプ25を介して対応する位置の接続パッド13に電気的に接続且つ固定された第2の半導体チップである半導体チップ15、並びに、接続パッド16が半田バンプ25及び接続パッド13を経由して接続された接続パッド12と、接続パッド22とを電気的に接続する第2の導電材である金属細線27を備えている。

【0013】

また、半導体装置1は、外部接続端子となる半田バンプ26をパッケージ基板21の下面に有している。図示を省略するが、パッケージ基板21は、上面の接続パッド22と接続された配線の一部をなすランドを下面に設けて、ランドに半田バンプ26が接続され、半田バンプ26との接続部を除いたランド及び下面がソルダレジストで被われている。パッケージ基板21の上面は、周辺部に配設された接続パッド22を除いて、ソルダレジストで被われている。パッケージ基板21の上面の中央部に、例えば、エポキシ樹脂を主成分とする接着材23を介して、半導体チップ11の下面が接着、固定されている。

【0014】

更に、半導体装置1は、パッケージ基板21の上面、半導体チップ11、15、金属細線27、半田バンプ25を被って、例えば、エポキシ樹脂を主成分とする封止樹脂29が形成されている。互いに対面する半導体チップ11、15の間には、封止樹脂29が充填されるが、封止樹脂29の代わりにアンダーフィル材(図示略)を充填することは可能である。半導体装置1は、半田バンプ26を除くと、ほぼ、直方体の外形を有している。

【0015】

半導体チップ11の上面の最も外側は、周知のように、層間絶縁膜の中に配線層が形成され、周辺部に、ワイヤボンディングのための接続パッド12が層間絶縁膜及び表面保護膜から露出し、中央部に、半導体チップ15と接続するための接続パッド13が露出している。半導体チップ15は、半導体チップ11の接続パッド12のなす列の内側、すなわち半導体チップ11の中央部に収められる大きさである。

【0016】

図2に示すように、半導体チップ15の下面にほぼ等間隔の行列状に、つまり格子状に配列された接続パッド16及び接続パッド17が、図示を省略するが、半導体チップ15の最も外側の層をなす配線層で形成されている。接続パッド16と接続パッド17は、破線で示した矩形の境界線31で区分けされ、境界線31の外側に接続パッド16、内側に接続パッド17が配置されている。接続パッド16は、境界線31の外側にある矩形(図示略)の辺の上に、ほぼ等間隔で配列されている。接続パッド16及び接続パッド17のそれぞれの中央部に、半田バンプ25が位置する関係にある。なお、製造プロセス上、半田バンプ25は、半導体チップ15の接続パッド16、17に配設されるとは限らない。

【0017】

接続パッド16は、半導体チップ15が電気的に必要とする接続パッド数より多く配設されている。接続パッド16は、一部が電源に接続され、残りが接地に接続されている。電源供給のための接続パッド16は、必ずしも同電位とは限らず、必要とする電位に近い電位が供給される。なお、接続パッド16は、接続パッド17と同等の大きさに形成されているが、接続パッド17より大きく形成され、大きな接続パッド17に対応した、より大きな半田バンプ、より大きな接続パッド13とすることは可能である。

【0018】

接続パッド16は、電源と接地とに振り分けずに、例えば、全てを電源に接続することは可能であり、逆に、全てを接地に接続することは可能である。接続パッド16が、電源または接地の一方にのみ接続される場合、接続パッド17の一部が電源または接地の他方に接続される。また、接続パッド16の一部を半導体チップ15の電源及び接地のどちらにも接続せず、独立に存在するパッド、つまり放熱のためのパッドとすることは可能である。

【0019】

接続パッド17は、少なくとも一部が信号の配線に接続される。接続パッド17は、境界線31の内側の半導体チップ15の下面全面に分布しているが、必要とする信号の数に応じて、例えば、境界線31の内側に接続パッド17のない領域が形成されることは差し支えない。

【0020】

図1に示すように、接続パッド12及び接続パッド13は、図示を省略するが、半導体チップ11の最上層(最も外側の層)をなす配線層で形成されている。接続パッド16に対向する全ての接続パッド13は、半導体チップ11上面で、配線14により、接続パッド12と接続されている。配線14は、例えば、半導体チップ11の最上層または最上層に近い配線層で形成され、接続パッド12と接続パッド13とは、可能な限り断面積が大きく、距離が短くなるように接続されることが好ましい。なお、接続パッド12の一部は、信号用に使用される。

【0021】

半田バンプ25は、例えば、接続方向に垂直な断面の径が30〜40μm、接続距離が20〜30μm程度である。金属細線37は、例えば、20〜30μm径のAuまたはAl等を主成分とするワイヤであり、半導体チップ11の接続パッド12から上方に引き出してループを形成して、パッケージ基板21の接続パッド22と接続されている。

【0022】

半導体チップ11は、例えば、ロジックLSI(Large Scale Integrated Circuit)であり、半導体チップ15は、例えば、メモリLSIである。

【0023】

次に、発熱及び放熱の経路等を説明する。半導体装置1は、半田バンプ26を介して、外部と接続される。従って、電源は、半田バンプ26、接続パッド22、金属細線27、及び接続パッド12を経由して、半導体チップ11に供給される。更に、電源は、接続パッド12から、配線14、接続パッド13、半田バンプ25、及び接続パッド16を経由して、半導体チップ15に供給される。接地は、電源と同様な、しかし、電源とは独立な配線を経由して、半導体チップ11及び半導体チップ15に接続される。

【0024】

半導体チップ11、15は、電源及び接地とは別の配線を経由して送られる駆動信号によって、トランジスタ等の能動素子が駆動され、その結果、電流が、能動素子、受動素子、配線等を流れ、更にリーク電流の発生等があり、ジュール熱を発生する。高集積化、高速化に伴って半導体チップは、必要な電流が増加し、発熱量も大きくなる。

【0025】

半導体チップ15で発生した熱は、一部が、封止樹脂29を伝導し、封止樹脂29の表面から放熱される。また、一部が、電源及び接地の配線を経由して半田バンプ26を伝導、また、半導体チップ15の半田バンプ26へ通ずる封止樹脂29、半導体チップ11、接着材23、及びパッケージ基板21を伝導して、半導体装置1が実装されたプリント基板(図示略)等へ放熱される。電気の良導体は、熱の良導体でもあり、半導体チップ15で発生した熱は、電源及び接地の配線を電気と同様な経路で、または、電源及び接地の配線の一部を経由して、パッケージ基板21の下面側に通ずる経路で放熱される。

【0026】

上述したように、半導体装置1は、半導体チップ15、半導体チップ11、及びパッケージ基板21のそれぞれの周辺部、すなわち半導体装置1の側面部に、電源または接地に接続された強化された放熱経路を有しているので、半導体チップ15で発生した熱を、半導体チップ15の周辺部に導き、半導体装置1の外部へ放熱することが可能である。スタック形MCPにおいては、それぞれの半導体チップ15、11の中心部でより高温になる傾向がある。半導体チップ11の中心部で発生する熱量が大きいので、半導体チップ15の中心部で発生する熱は、半導体チップ11の中心部を経路として半田バンプ26の側に流すことが難しい。中心部により大きな放熱経路を持たないパッケージ基板21を使用しているので、半導体チップ15の中心部と周辺部との温度差を利用して発生する熱を周辺部へ導き、更に、温度差を利用して半導体チップ11の周辺部へ導き、更に、温度差を利用してパッケージ基板21の周辺部から半田バンプ26の側に放熱することは可能である。

【0027】

半導体チップ15、半導体チップ11、及びパッケージ基板21に配設された電源または接地のための接続パッド16、13、12、22は、それぞれの周辺部を取り巻いて、しかも、数がより多く配置されているので、半導体装置1は、より大きな放熱経路が周辺部に確保された構成をなしている。半導体装置1の中心部は、放熱経路が増強されているわけではないので放熱を促進することはないが、周辺部は、放熱経路が増強されているので、半導体チップ15の放熱を促進することが可能となる。

【0028】

半導体装置1は、結果的に、2層構造の上側の半導体チップ15の温度の上昇が、特に、抑えられるので、誤動作の発生は抑制される。また、半導体装置1は、動作昇温時と保管時との温度差が小さくなるので、温度サイクルによる故障の頻度を低減することが可能である。

【0029】

半導体装置1は、電源または接地のための接続パッド16が、半導体チップ15の周囲を一周する位置にあって、より適する位置で半導体チップ15内の配線に接続が可能なので、すなわち、電源系が強化されているので、電源と接地との電位差が小さくなることを避けることが可能である。

【実施例2】

【0030】

本発明の実施例2に係る半導体装置について、図3を参照しながら説明する。図3は半導体装置の上側に積層される半導体チップの下側を模式的に示す平面図である。実施例1の半導体装置とは、上側の半導体チップが周辺部の2列からなる電源または接地のための接続パッドを有することが異なる。なお、実施例1と同一構成部分には同一の符号を付して、その説明は省略する。

【0031】

図3に示すように、上側の半導体チップ35は、下面にほぼ等間隔の行列状に、接続パッド36及び接続パッド37が配列されている。接続パッド36と接続パッド37は、矩形の境界線41で区分けされ、境界線41の外側に2列並列の接続パッド36、内側に2列並列の接続パッド37が配置されている。半導体チップ35の中央部は、接続パッド37が配置されていない。接続パッド36及び接続パッド37のそれぞれの中央部に、半田バンプ25が位置する関係にある。

【0032】

接続パッド36は、電源または接地のための接続パッドであり、接続パッド37は、少なくとも一部が信号用の接続パッドである。接続パッド37は、必要とする信号の数に応じて形成され、半導体チップ35の中央部に配設する必要がない。接続パッド36は、実施例1の接続パッド16、接続パッド37は、実施例1の接続パッド17に、それぞれ対応している。

【0033】

半導体チップ35は、電源または接地のための接続パッドの数が、実施例1の場合より、相対的に増加されている。半導体チップ35は、実施例1の半導体チップ15より、発熱量が多い場合、または、放熱の強化が必要な場合に相当する。一方、信号のための接続パッドの数は、相対的に少なくて済む場合である。

【0034】

図示を省略(図1参照)するが、半導体チップ35に対向する下層の半導体チップは、半導体チップ35が有する接続パッド36に対応する接続パッドを、上面の周辺部に有し、接続パッド37に対応する接続パッドを、上面の中央部に有している。下層の半導体チップは、実施例1の半導体チップ11の接続パッド12と同様に、接続パッド36に対応する接続パッドの外側に、金属細線用の接続パッドを有している。なお、この金属細線用の接続パッドは、1列に収まらない場合は、2列に並列して形成することが可能である。そして、金属細線用の接続パッドに対応した接続パッドが、実施例1のパッケージ基板21の接続パッド22と同様に、パッケージ基板上に形成されている。

【0035】

本実施例の半導体装置は、実施例1の半導体装置1と同様な放熱経路が、半導体装置の周辺部に確保可能である。従って、本実施例の半導体装置は、実施例1の半導体装置1が有する効果を同様に有している。しかも、接続パッド36が、相対的に数が多く配設されているので、より大きな放熱が可能となる。

【0036】

また、上側に積層される半導体チップの2列の接続パッド36が、電源または接地のために使用される例を上述したが、上記実施例2の半導体装置の変形例として、外側の矩形の辺の上に配列された接続パッド36を電源用として、内側の矩形の辺の上に配列された接続パッド36を接地用として、区分けすることは可能であり、逆に、外側の接続パッド36を接地用、内側の接続パッド36を電源用とすることは可能である。

【0037】

また、上側に積層される半導体チップの電源または接地のための接続パッド36は、2列配設される例を上述したが、上記実施例2の半導体装置の変形例として、電源または接地のための接続パッドが、3列以上配設されることは可能である。

【0038】

本発明は、上述した実施例に限定されるものではなく、本発明の要旨を逸脱しない範囲内で、種々、変形して実施することができる。

【0039】

例えば、実施例では、第1の半導体チップは、ロジックLSIであり、第2の半導体チップは、メモリLSIである半導体装置の例を示したが、第1の半導体チップが大きいとした上で、第1の半導体チップがメモリLSI、第2の半導体チップがロジックLSIとすることは可能である。その他、第1及び第2の半導体チップは、2つのロジックLSIの組合せ、または、2つのメモリLSIの組合せとすることは可能である。

【0040】

また、第1または第2の半導体チップは、アナログ回路を有するIC(Integrated Circuit)、内部にアナログ回路ブロックと制御論理回路ブロックを組み合わせた、いわゆるアナログ・デジタル混載LSI等であっても差し支えない。

【0041】

また、実施例では、BGA(Ball Grid Array)型のパッケージの例を示したが、リードフレームを使用したパッケージを使用することは可能である。

【0042】

その他、以下の付記に記載されるような構成が考えられる。

(付記1) 周辺部に第1の接続パッドを有するパッケージ基板と、上面の周辺部に形成された第2の接続パッド、及び上面の前記第2の接続パッドより内側に形成され、前記第2の接続パッドに接続された第3の接続パッドを有し、下面を前記パッケージ基板に固定された第1の半導体チップと、下面の最も外側の周辺部を取り巻く少なくとも1列が、電源または接地に接続された外側接続パッドを有し、下面の前記外側接続パッドの列より内側に、信号線に接続された内側接続パッドを有し、前記外側接続パッド及び前記内側接続パッドが第1の導電材を介して対応する位置の前記第3の接続パッドに電気的に接続且つ固定された第2の半導体チップと、前記外側接続パッドが前記第1の導電材及び前記第3の接続パッドを経由して接続された前記第2の接続パッドと、前記第1の接続パッドとを電気的に接続する第2の導電材とを備えている半導体装置。

【0043】

(付記2) 前記第1の半導体チップは、ロジックLSIであり、前記第2の半導体チップは、メモリLSIである付記1に記載の半導体装置。

【図面の簡単な説明】

【0044】

【図1】本発明の実施例1に係る半導体装置の構成を模式的に示す図で、図1(a)は半導体装置の一部を切り欠いて平面的に示す図、図1(b)は図1(a)のA−A線に沿った全体の断面図。

【図2】本発明の実施例1に係る半導体装置の上側に積層される半導体チップの下側を模式的に示す平面図。

【図3】本発明の実施例2に係る半導体装置の上側に積層される半導体チップの下側を模式的に示す平面図。

【符号の説明】

【0045】

1 半導体装置

11、15、35 半導体チップ

12、13、16、17、22、36、37 接続パッド

14 配線

21 パッケージ基板

23 接着材

25、26 半田バンプ

27 金属細線

29 封止樹脂

31、41 境界線

【特許請求の範囲】

【請求項1】

周辺部に第1の接続パッドを有するパッケージ基板と、

上面の周辺部に形成された第2の接続パッド、及び上面の前記第2の接続パッドより内側に形成され、前記第2の接続パッドに接続された第3の接続パッドを有し、下面を前記パッケージ基板に固定された第1の半導体チップと、

下面の最も外側の周辺部を取り巻く少なくとも1列が、電源または接地に接続された外側接続パッドを有し、下面の前記外側接続パッドの列より内側に、信号線に接続された内側接続パッドを有し、前記外側接続パッド及び前記内側接続パッドが第1の導電材を介して対応する位置の前記第3の接続パッドに電気的に接続且つ固定された第2の半導体チップと、

前記外側接続パッドが前記第1の導電材及び前記第3の接続パッドを経由して接続された前記第2の接続パッドと、前記第1の接続パッドとを電気的に接続する第2の導電材と、

を備えていることを特徴とする半導体装置。

【請求項2】

前記外側接続パッドは、一部が電源に接続され、一部が接地に接続されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記外側接続パッドは、矩形の辺の上に載るように配置され、ほぼ等間隔で配列されていることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記内側接続パッドは、前記矩形の内側に、前記外側接続パッドに対応した行列をなして配列されていることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記第1の導電材は、半田バンプであり、前記第2の導電材は、金属細線であることを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項1】

周辺部に第1の接続パッドを有するパッケージ基板と、

上面の周辺部に形成された第2の接続パッド、及び上面の前記第2の接続パッドより内側に形成され、前記第2の接続パッドに接続された第3の接続パッドを有し、下面を前記パッケージ基板に固定された第1の半導体チップと、

下面の最も外側の周辺部を取り巻く少なくとも1列が、電源または接地に接続された外側接続パッドを有し、下面の前記外側接続パッドの列より内側に、信号線に接続された内側接続パッドを有し、前記外側接続パッド及び前記内側接続パッドが第1の導電材を介して対応する位置の前記第3の接続パッドに電気的に接続且つ固定された第2の半導体チップと、

前記外側接続パッドが前記第1の導電材及び前記第3の接続パッドを経由して接続された前記第2の接続パッドと、前記第1の接続パッドとを電気的に接続する第2の導電材と、

を備えていることを特徴とする半導体装置。

【請求項2】

前記外側接続パッドは、一部が電源に接続され、一部が接地に接続されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記外側接続パッドは、矩形の辺の上に載るように配置され、ほぼ等間隔で配列されていることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記内側接続パッドは、前記矩形の内側に、前記外側接続パッドに対応した行列をなして配列されていることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記第1の導電材は、半田バンプであり、前記第2の導電材は、金属細線であることを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2010−62328(P2010−62328A)

【公開日】平成22年3月18日(2010.3.18)

【国際特許分類】

【出願番号】特願2008−226413(P2008−226413)

【出願日】平成20年9月3日(2008.9.3)

【出願人】(000221199)東芝マイクロエレクトロニクス株式会社 (376)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成22年3月18日(2010.3.18)

【国際特許分類】

【出願日】平成20年9月3日(2008.9.3)

【出願人】(000221199)東芝マイクロエレクトロニクス株式会社 (376)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]