半導体装置

【課題】素子の高耐圧化に伴い反転領域を介して流れるリーク電流を低減する方法の提供。

【解決手段】所望の不純物濃度を有する半導体層を備えた半導体基板と、半導体層内に形成された複数のストライプ状のトレンチ内にゲート酸化膜を介して導電体層を埋め込み形成したトレンチゲートと、半導体層表面を覆う絶縁膜と、絶縁膜を貫通し、ソースコンタクト開口部に形成されたソース電極と、半導体層内に形成され、ソース電極に電気的に接続されたボディ領域及びソース領域と、トレンチゲート周縁部でトレンチゲートに接続されたゲート周辺配線と、ソース電極と同一表面上で、ソース電極から離間して形成され、ゲート周辺配線に接続されるゲート電極と、ドレイン電極とを具備し、周縁部のスクライブ領域の拡散領域と、デバイス周縁部の拡散領域との間の半導体基板表面に、チャネルストッパ1csを形成し、反転領域形成を抑制する。

【解決手段】所望の不純物濃度を有する半導体層を備えた半導体基板と、半導体層内に形成された複数のストライプ状のトレンチ内にゲート酸化膜を介して導電体層を埋め込み形成したトレンチゲートと、半導体層表面を覆う絶縁膜と、絶縁膜を貫通し、ソースコンタクト開口部に形成されたソース電極と、半導体層内に形成され、ソース電極に電気的に接続されたボディ領域及びソース領域と、トレンチゲート周縁部でトレンチゲートに接続されたゲート周辺配線と、ソース電極と同一表面上で、ソース電極から離間して形成され、ゲート周辺配線に接続されるゲート電極と、ドレイン電極とを具備し、周縁部のスクライブ領域の拡散領域と、デバイス周縁部の拡散領域との間の半導体基板表面に、チャネルストッパ1csを形成し、反転領域形成を抑制する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に係り、特にトレンチ構造を有する絶縁ゲートトランジスタなどの半導体装置におけるチップ周縁部からのリーク防止に関するものである。

【背景技術】

【0002】

近年、携帯電話をはじめとした電子機器における低消費電力化、高機能化及び高速化に伴って、それに搭載される半導体装置も低消費電力化、高速化が要求されてきている。一般的に電子機器のロードスイッチ及びDC−DCコンバータ等に用いられているトランジスタも、それらに対応するためにオン抵抗の小さなものが要求されている。トランジスタのオン抵抗の低減をはかるためには、個々のデバイスを微細化して、単位面積あたりに配置するトランジスタの密度を大きくすることが、一つの方法としてあげられる。具体的には、トレンチにゲート電極を形成した縦型MOSFETにおいて、トランジスタを形成しているトレンチをストライプ状に配置して、トレンチの幅を微細化すると共に、隣接するトレンチ間のピッチを小さくすることでトランジスタ密度を大きくすることが出来る。

【0003】

一例として、半導体チップ内に多数のトレンチを配設し、このトレンチ内にMOSFETを配設したものがある。この構造では、半導体チップの表面の一部にゲートパッドが形成され、トレンチに多結晶シリコンを充填して形成されるゲート電極は、半導体チップの周縁に沿って形成されるゲート配線によって、このゲートパッドに接続される(特許文献1)。

【0004】

このようなMOSFETにおいては図11および図12に一例を示すように、スクライブ領域に埋め込み拡散領域11dとして、P-領域が形成されている。

【0005】

【特許文献1】特開2007-48769号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

上述したように、従来のストライプ状トレンチゲートを有する半導体装置では、周縁部のスクライブ領域に形成される拡散領域11dと、ソース領域を構成する埋め込み拡散領域11sとの間に形成される反転領域を介してリーク電流が流れるという問題がある。

この課題は、素子の高耐圧化が進むにつれて特に深刻になってきている。

【0007】

本発明は、前記実情に鑑みてなされたもので、周縁部のスクライブ領域に埋め込み拡散領域11dが形成されるMOSFETなどの半導体装置において、リーク電流を低減し、信頼性の高い半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明の半導体装置は、スクライブ領域の埋め込み拡散領域と、デバイス周縁部の埋め込み拡散領域との間において、基板表面に、例えば配線層からなるチャネルストッパを形成し、チャネルとなる反転領域の形成を抑制するようにしたものである。

例えば、高温逆バイアス試験後において、スクライブ領域の埋め込み拡散領域と、デバイス周縁部の埋め込み拡散領域との間において、チャネルとなる反転領域が形成されるが、この構成によれば、基板表面に、配線層からなるチャネルストッパを形成することで、反転領域の形成を抑制することができる。高温逆バイアス試験後において、リークは、温度印加とバイアス印加によって、スクライブ領域の埋め込み拡散領域と、デバイス周縁部の埋め込み拡散領域との間において、チャネルとなる反転領域が形成されることが原因と考えられている。直接の原因は、チャネル領域となる不純物領域(N-層)の上に形成された熱酸化膜中の可動イオンが同試験時に誘起されて負電位になり、反転層を形成し易い状況にあったことと考えられるが、本発明ではこの原因を抑止することで、このリークの発生を抑制することができる。

【0009】

すなわち本発明は、所望のデバイスが形成されると共に、デバイス周縁部に第1の導電型を有する第1の不純物領域を備えた半導体基板で構成され、前記半導体基板のスクライブ領域に第1の導電型を有する第2の不純物領域が形成された半導体装置であって、前記スクライブ領域の第1の不純物領域と前記第2の不純物領域との間にチャネルストッパを形成したことを特徴とする。

【0010】

望ましくは、このチャネルストッパとなる配線層は、アルミニウム配線などの周辺配線と同一層で形成する。

【0011】

またこのチャネルストッパはさらにこのアルミニウム配線などの周辺配線と同一層で形成される配線層に接続される多結晶シリコンリングを具備している。

【0012】

なおこのチャネルストッパは、スクライブ領域の埋め込み拡散領域から、わずかでも突出していれば有効である。

【0013】

また、望ましくは、このチャネルストッパとなる配線層は、半導体チップのコーナー部分で、裏面電極と電気的に接続する。

【0014】

また、スクライブ領域の埋め込み拡散領域上に逆導電型の半導体領域を形成し、これをチャネルストッパとしてもよい。

【0015】

すなわち、本発明の半導体装置は、所望の不純物濃度を有する半導体層を備えた半導体基板と、前記半導体層内に形成された複数のストライプ状のトレンチ内にゲート酸化膜を介して導電体層を埋め込み形成したトレンチゲートと、前記半導体層表面を覆う絶縁膜と、前記絶縁膜を貫通し、ソースコンタクト開口部を通して形成されたソース電極と、前記半導体層内に形成され、前記ソース電極に電気的に接続されたボディ領域及びソース領域と、前記トレンチゲートの周縁部で前記トレンチゲートに接続されたゲート周辺配線と、前記ソース電極と同一表面上であって、前記ソース電極から離間した位置に形成され、前記ゲート周辺配線に接続されるゲート電極と、ドレイン電極とを具備し、周縁部のスクライブ領域の埋め込み拡散領域と、デバイス周縁部の埋め込み拡散領域との間において、前記半導体基板表面に、配線層からなるチャネルストッパを形成し、チャネルとなる反転領域の形成を抑制するようにしたものである。

なお、チャネルストッパは、ソース電極と同一層で構成してもよい。また2層で構成し、下層側をトレンチゲートと同一層で構成してもよい。

【発明の効果】

【0016】

以上詳述したように、本発明の構造によれば、スクライブ領域周縁部の埋め込み拡散領域とデバイス周縁部の拡散領域との間に、チャネルストッパを形成しているため、反転領域の形成を抑制しリークの発生を抑制することができる。また、配線を用いたチャネルストッパを用いることで、配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制し、リーク電流の発生・耐圧の劣化を防止することができる。

また、アルミニウム配線などの配線層よりもより下層に位置する多結晶シリコン層を、チャネルを形成し易い領域に配することで、チャネルストッパ効果をより高めることが可能となる。

【発明を実施するための最良の形態】

【0017】

(実施の形態1)

以下本発明の実施の形態について、図面を参照しつつ詳細に説明する。

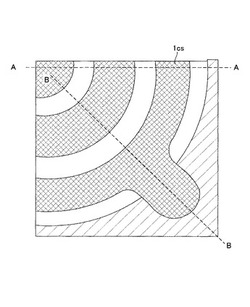

図1は本発明の実施の形態に係るトレンチMOSFETの要部平面概念図、図2は図1のA-A‘断面図、図3は図1のB-B’断面図、図4および図5はトレンチMOSFETの全体平面概念図、図5は図4のA-A‘断面図を示している。

本実施の形態のトレンチMOSFETは、図1乃至3に示すように、スクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域と、トレンチMOSFET周縁部の拡散領域11sとしてのP−領域との間に、アルミニウム配線を用いたチャネルストッパ電極1csを形成したことを特徴とする。ここでチャネルストッパ電極1csはスクライブ領域周縁部の埋め込み拡散領域11tに対し5μm以上の重なり領域を具備しており、ドレイン電極1dと同電位となるように構成されている。この構成により配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制し、リーク電流の発生・耐圧の劣化を防止することができるという特徴を有する。なおチャネルストッパ電極1csはドレイン電極1dと同電位となるように構成されている。なおこのトレンチMOSFET周縁部の拡散領域11sは第1の不純物領域、埋め込み拡散領域は第2の不純物領域に相当する。

【0018】

他の部分については通例の構成をとっており、図4および図5に示すように、ソース領域13は、半導体層内にトレンチ4を形成するとともに、このトレンチ4内に酸化シリコンからなるゲート酸化膜10を介して多結晶シリコンを充填して形成したトレンチゲート7に接し、その両端に一定の深さを持つように形成され、ソースコンタクト開口部3においてソース電極1s(ソースパッド)に電気的に接続されている。

ドレイン領域はN型エピタキシャル層6及びN型基板5で構成され、半導体チップの裏面全体がドレイン電極1dとなっている。

【0019】

すなわち、N型のシリコン基板5の表面に形成されたN型エピタキシャル層6内に形成された複数のストライプ状のトレンチ4内にゲート酸化膜10を介して多結晶シリコン層(導電体層)を埋め込み形成したトレンチゲート7と、前記半導体層表面を覆う酸化シリコン膜からなる絶縁膜15と、この絶縁膜15に形成された、ソースコンタクト開口部3を介して前記ソース領域13にコンタクトするように形成されたソース電極1sと、トレンチゲート7の周縁部でトレンチゲート7に接続されたゲート周辺配線2と、前記ソース電極1sと同一表面上であって、前記ソース電極1sから離間した位置に形成され、前記ゲート周辺配線2に接続されるゲート電極1gと、裏面部に形成されたドレイン電極1dとを具備している。

【0020】

なお、図4に示すように、ゲート周辺配線2はチップ周縁部に加え、ゲート電極1gの形成領域を囲むように、ゲート電極1gの形成領域とソース電極1sの間にも配設されているため、トレンチゲートへの給電のための給電ラインをより短くし、配線抵抗の低減をはかることができる。

【0021】

次に本発明の半導体装置の製造方法を、図6を参照して説明する。製造方法については、トレンチ形成のための製造工程については何ら従来と変わるものではない。

ストライプ状のトレンチゲート構造を有するN型MOSFETの製造方法は、図6(a)に示すように、半導体基板5としてN+型のシリコンウェハを使用し、その表面にN-型エピタキシャル層6を形成する。このN-型エピタキシャル層内にP型ウェル層11を形成する。

【0022】

次に、図6(b)に示すようにフォトリソグラフィー及びドライエッチングにより、P型ウェル層11の形成されたN-型エピタキシャル層6表面にトレンチ4を形成する。

【0023】

この後、図6(c)に示すようにトレンチ側壁に熱酸化により厚膜30nm程度のゲート酸化膜10を形成したのち、トレンチ4内にCVD法によって多結晶シリコン膜(トレンチゲート)7を堆積し、多結晶シリコン(7)に不純物ドーピングを行う。引き続き、化学機械研磨(CMP)あるいはエッチバックにより不要部を除去したのち、熱酸化により、この多結晶シリコン(7)上に酸化シリコン膜9を形成する。

【0024】

ソース領域13となるN型拡散層及びボディ領域12となるP型拡散層を形成するため、図6(d)に示すように、P型ウェル層11中にイオン注入法を用いて、リン及びボロン不純物を注入する。

その後、半導体チップ表面に絶縁膜及び保護膜を堆積しソース電極1sとソース領域13を電気的に導通させるため、ソースコンタクト開口部3を設けて、アルミニウム薄膜を形成し、ソース電極1s、チャネルストッパ電極1csなどを構成する金属配線を形成する。このようにして、アルミニウム薄膜のパターニングに際し、マスクパターンを変更するのみで、図1乃至図5に示す半導体装置が形成される。

【0025】

この構成によれば、スクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域と、トレンチMOSFET周縁部の拡散領域11sとしてのP−領域との間に、アルミニウム配線を用いたチャネルストッパ電極1csを形成しており、配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制することができる。従ってアルミニウム配線パターンの変更のみで、耐圧、リーク特性の劣化を防止することができる。

【0026】

ここでアルミニウム配線で構成されるチャネルストッパ電極のスクライブ領域周縁部の埋め込み拡散領域11tへのはみ出し量と耐圧との関係を測定した結果を図7に示す。曲線aはチャネルストッパ電極がない場合、曲線bはチャネルストッパ電極がある場合の耐圧特性を示す。高温逆バイアス試験後、デバイスのリーク電流(IDSS)がVDSS18V近傍から増加し、段付きの特性を示した。そして電流増加後は飽和傾向にあり、耐圧変動はなかった。この結果からもチャネルストッパ電極の存在によりリークが抑制できることがわかる。

【0027】

(実施の形態2)

次に本発明の実施の形態2について説明する。

実施の形態2では、図8および図9に示すように、前記実施の形態1におけるチャネルストッパ電極1csに加え、トレンチゲート7に接続され、多結晶シリコンで形成されるゲート周辺配線2と同一工程で形成された多結晶シリコンからなるチャネルストッパ層2cdをこのチャネルストッパ電極(アルミニウム配線)よりも下層に設け、トレンチMOSFET周縁部の拡散領域11sとしてのP−領域(ソース領域11s)とスクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域との間のチャネル領域に絶縁膜14を介して、対向するように配置し、よりチャネルストッパ効果を高めるようにしたことを特徴とするものである。

なおここで8はコンタクト性を高めるための高濃度コンタクト領域である。

【0028】

(実施の形態3)

次に本発明の実施の形態3について説明する。

前記実施の形態2では、図8および図9に示すように、前記実施の形態1におけるチャネルストッパ電極1csに加え、トレンチゲート7に接続され、多結晶シリコンで形成されるゲート周辺配線2と同一工程で形成された多結晶シリコンからなるチャネルストッパ層2cdをこのチャネルストッパ電極よりも下層に設けたが、本実施の形態では、図10に示すように、スクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域に、逆導電型の半導体領域であるnウェルからなるチャンネルストッパ内層20を形成したことを特徴とするものである。なお図10は図1のA-A断面に相当する断面である。

【0029】

この構成においても、トレンチMOSFET周縁部の拡散領域11sとしてのP−領域(ソース領域11s)とスクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域との間のチャネル領域にと反転層が形成されリークが発生するのを抑制することができる。

また、前記第1乃至第3の実施の形態におけるチャネルストッパは2つ以上を併設することも可能である。

【0030】

また前記実施の形態では、トレンチMOSFETについて説明したが、MOSFETに限定されることなく、トレンチキャパシタ、DRAMなど、トレンチ構造を有する他の素子にも適用可能である。特にスクライブ周縁部にテスト用のコンタクトを形成するために埋め込み拡散領域をもつデバイスに適用可能であり、スクライブ周縁部の埋め込み拡散領域とデバイス周縁部の拡散領域との間に、配線を用いたチャネルストッパを形成しているため、配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制し、リーク電流の発生・耐圧の劣化を防止することができる。

【0031】

この構成により配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制し、リーク電流の発生・耐圧の劣化を防止することができるという特徴を有する。なおチャネルストッパ電極1csおよびチャネルストッパ層2csはドレイン電極1dと同電位となるように構成されている。

【産業上の利用可能性】

【0032】

以上説明してきたように、本発明によれば高耐圧化に際しても、リーク電流の発生を抑制することができることから、車載用など信頼性の高い電子デバイスへの適用が有効である。

【図面の簡単な説明】

【0033】

【図1】本発明の実施の形態1に係るトレンチMOSFETの要部平面概念図

【図2】図1のA−A断面図

【図3】図1のB−B断面図

【図4】本発明の実施の形態1に係るトレンチMOSFETの全体概要平面図

【図5】図4のA-A‘断面図

【図6】本発明の実施の形態1に係るトレンチMOSFETの製造工程図

【図7】チャネルストッパ電極の突出長とリーク電流との関係を測定した結果を示す図

【図8】本発明の実施の形態2に係るトレンチMOSFETのA−A断面図

【図9】同トレンチMOSFETのB−B断面図

【図10】本発明の実施の形態3に係るトレンチMOSFETのA−A断面図

【図11】従来例のトレンチMOSFETのA−A断面図

【図12】従来例のトレンチゲート構造のB−B断面図

【符号の説明】

【0034】

1g ゲート電極

1s ソース電極

1d ドレイン電極

1cs チャネルストッパ電極

2 ゲート周辺配線

2cs チャネルストッパ配線(層)

3 ソースコンタクト開口部

T トレンチ

5 N+型基板

6 N-エピタキシャル層

4,7 トレンチゲート(多結晶シリコン)

9,14 絶縁膜

10 ゲート酸化膜

11 Pウェル

11t スクライブ領域周縁部の埋め込み拡散領域

11s トレンチMOSFET周縁部の拡散領域

12 ボディ領域

13 ソース領域

20 チャネルストッパ層

【技術分野】

【0001】

本発明は、半導体装置に係り、特にトレンチ構造を有する絶縁ゲートトランジスタなどの半導体装置におけるチップ周縁部からのリーク防止に関するものである。

【背景技術】

【0002】

近年、携帯電話をはじめとした電子機器における低消費電力化、高機能化及び高速化に伴って、それに搭載される半導体装置も低消費電力化、高速化が要求されてきている。一般的に電子機器のロードスイッチ及びDC−DCコンバータ等に用いられているトランジスタも、それらに対応するためにオン抵抗の小さなものが要求されている。トランジスタのオン抵抗の低減をはかるためには、個々のデバイスを微細化して、単位面積あたりに配置するトランジスタの密度を大きくすることが、一つの方法としてあげられる。具体的には、トレンチにゲート電極を形成した縦型MOSFETにおいて、トランジスタを形成しているトレンチをストライプ状に配置して、トレンチの幅を微細化すると共に、隣接するトレンチ間のピッチを小さくすることでトランジスタ密度を大きくすることが出来る。

【0003】

一例として、半導体チップ内に多数のトレンチを配設し、このトレンチ内にMOSFETを配設したものがある。この構造では、半導体チップの表面の一部にゲートパッドが形成され、トレンチに多結晶シリコンを充填して形成されるゲート電極は、半導体チップの周縁に沿って形成されるゲート配線によって、このゲートパッドに接続される(特許文献1)。

【0004】

このようなMOSFETにおいては図11および図12に一例を示すように、スクライブ領域に埋め込み拡散領域11dとして、P-領域が形成されている。

【0005】

【特許文献1】特開2007-48769号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

上述したように、従来のストライプ状トレンチゲートを有する半導体装置では、周縁部のスクライブ領域に形成される拡散領域11dと、ソース領域を構成する埋め込み拡散領域11sとの間に形成される反転領域を介してリーク電流が流れるという問題がある。

この課題は、素子の高耐圧化が進むにつれて特に深刻になってきている。

【0007】

本発明は、前記実情に鑑みてなされたもので、周縁部のスクライブ領域に埋め込み拡散領域11dが形成されるMOSFETなどの半導体装置において、リーク電流を低減し、信頼性の高い半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明の半導体装置は、スクライブ領域の埋め込み拡散領域と、デバイス周縁部の埋め込み拡散領域との間において、基板表面に、例えば配線層からなるチャネルストッパを形成し、チャネルとなる反転領域の形成を抑制するようにしたものである。

例えば、高温逆バイアス試験後において、スクライブ領域の埋め込み拡散領域と、デバイス周縁部の埋め込み拡散領域との間において、チャネルとなる反転領域が形成されるが、この構成によれば、基板表面に、配線層からなるチャネルストッパを形成することで、反転領域の形成を抑制することができる。高温逆バイアス試験後において、リークは、温度印加とバイアス印加によって、スクライブ領域の埋め込み拡散領域と、デバイス周縁部の埋め込み拡散領域との間において、チャネルとなる反転領域が形成されることが原因と考えられている。直接の原因は、チャネル領域となる不純物領域(N-層)の上に形成された熱酸化膜中の可動イオンが同試験時に誘起されて負電位になり、反転層を形成し易い状況にあったことと考えられるが、本発明ではこの原因を抑止することで、このリークの発生を抑制することができる。

【0009】

すなわち本発明は、所望のデバイスが形成されると共に、デバイス周縁部に第1の導電型を有する第1の不純物領域を備えた半導体基板で構成され、前記半導体基板のスクライブ領域に第1の導電型を有する第2の不純物領域が形成された半導体装置であって、前記スクライブ領域の第1の不純物領域と前記第2の不純物領域との間にチャネルストッパを形成したことを特徴とする。

【0010】

望ましくは、このチャネルストッパとなる配線層は、アルミニウム配線などの周辺配線と同一層で形成する。

【0011】

またこのチャネルストッパはさらにこのアルミニウム配線などの周辺配線と同一層で形成される配線層に接続される多結晶シリコンリングを具備している。

【0012】

なおこのチャネルストッパは、スクライブ領域の埋め込み拡散領域から、わずかでも突出していれば有効である。

【0013】

また、望ましくは、このチャネルストッパとなる配線層は、半導体チップのコーナー部分で、裏面電極と電気的に接続する。

【0014】

また、スクライブ領域の埋め込み拡散領域上に逆導電型の半導体領域を形成し、これをチャネルストッパとしてもよい。

【0015】

すなわち、本発明の半導体装置は、所望の不純物濃度を有する半導体層を備えた半導体基板と、前記半導体層内に形成された複数のストライプ状のトレンチ内にゲート酸化膜を介して導電体層を埋め込み形成したトレンチゲートと、前記半導体層表面を覆う絶縁膜と、前記絶縁膜を貫通し、ソースコンタクト開口部を通して形成されたソース電極と、前記半導体層内に形成され、前記ソース電極に電気的に接続されたボディ領域及びソース領域と、前記トレンチゲートの周縁部で前記トレンチゲートに接続されたゲート周辺配線と、前記ソース電極と同一表面上であって、前記ソース電極から離間した位置に形成され、前記ゲート周辺配線に接続されるゲート電極と、ドレイン電極とを具備し、周縁部のスクライブ領域の埋め込み拡散領域と、デバイス周縁部の埋め込み拡散領域との間において、前記半導体基板表面に、配線層からなるチャネルストッパを形成し、チャネルとなる反転領域の形成を抑制するようにしたものである。

なお、チャネルストッパは、ソース電極と同一層で構成してもよい。また2層で構成し、下層側をトレンチゲートと同一層で構成してもよい。

【発明の効果】

【0016】

以上詳述したように、本発明の構造によれば、スクライブ領域周縁部の埋め込み拡散領域とデバイス周縁部の拡散領域との間に、チャネルストッパを形成しているため、反転領域の形成を抑制しリークの発生を抑制することができる。また、配線を用いたチャネルストッパを用いることで、配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制し、リーク電流の発生・耐圧の劣化を防止することができる。

また、アルミニウム配線などの配線層よりもより下層に位置する多結晶シリコン層を、チャネルを形成し易い領域に配することで、チャネルストッパ効果をより高めることが可能となる。

【発明を実施するための最良の形態】

【0017】

(実施の形態1)

以下本発明の実施の形態について、図面を参照しつつ詳細に説明する。

図1は本発明の実施の形態に係るトレンチMOSFETの要部平面概念図、図2は図1のA-A‘断面図、図3は図1のB-B’断面図、図4および図5はトレンチMOSFETの全体平面概念図、図5は図4のA-A‘断面図を示している。

本実施の形態のトレンチMOSFETは、図1乃至3に示すように、スクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域と、トレンチMOSFET周縁部の拡散領域11sとしてのP−領域との間に、アルミニウム配線を用いたチャネルストッパ電極1csを形成したことを特徴とする。ここでチャネルストッパ電極1csはスクライブ領域周縁部の埋め込み拡散領域11tに対し5μm以上の重なり領域を具備しており、ドレイン電極1dと同電位となるように構成されている。この構成により配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制し、リーク電流の発生・耐圧の劣化を防止することができるという特徴を有する。なおチャネルストッパ電極1csはドレイン電極1dと同電位となるように構成されている。なおこのトレンチMOSFET周縁部の拡散領域11sは第1の不純物領域、埋め込み拡散領域は第2の不純物領域に相当する。

【0018】

他の部分については通例の構成をとっており、図4および図5に示すように、ソース領域13は、半導体層内にトレンチ4を形成するとともに、このトレンチ4内に酸化シリコンからなるゲート酸化膜10を介して多結晶シリコンを充填して形成したトレンチゲート7に接し、その両端に一定の深さを持つように形成され、ソースコンタクト開口部3においてソース電極1s(ソースパッド)に電気的に接続されている。

ドレイン領域はN型エピタキシャル層6及びN型基板5で構成され、半導体チップの裏面全体がドレイン電極1dとなっている。

【0019】

すなわち、N型のシリコン基板5の表面に形成されたN型エピタキシャル層6内に形成された複数のストライプ状のトレンチ4内にゲート酸化膜10を介して多結晶シリコン層(導電体層)を埋め込み形成したトレンチゲート7と、前記半導体層表面を覆う酸化シリコン膜からなる絶縁膜15と、この絶縁膜15に形成された、ソースコンタクト開口部3を介して前記ソース領域13にコンタクトするように形成されたソース電極1sと、トレンチゲート7の周縁部でトレンチゲート7に接続されたゲート周辺配線2と、前記ソース電極1sと同一表面上であって、前記ソース電極1sから離間した位置に形成され、前記ゲート周辺配線2に接続されるゲート電極1gと、裏面部に形成されたドレイン電極1dとを具備している。

【0020】

なお、図4に示すように、ゲート周辺配線2はチップ周縁部に加え、ゲート電極1gの形成領域を囲むように、ゲート電極1gの形成領域とソース電極1sの間にも配設されているため、トレンチゲートへの給電のための給電ラインをより短くし、配線抵抗の低減をはかることができる。

【0021】

次に本発明の半導体装置の製造方法を、図6を参照して説明する。製造方法については、トレンチ形成のための製造工程については何ら従来と変わるものではない。

ストライプ状のトレンチゲート構造を有するN型MOSFETの製造方法は、図6(a)に示すように、半導体基板5としてN+型のシリコンウェハを使用し、その表面にN-型エピタキシャル層6を形成する。このN-型エピタキシャル層内にP型ウェル層11を形成する。

【0022】

次に、図6(b)に示すようにフォトリソグラフィー及びドライエッチングにより、P型ウェル層11の形成されたN-型エピタキシャル層6表面にトレンチ4を形成する。

【0023】

この後、図6(c)に示すようにトレンチ側壁に熱酸化により厚膜30nm程度のゲート酸化膜10を形成したのち、トレンチ4内にCVD法によって多結晶シリコン膜(トレンチゲート)7を堆積し、多結晶シリコン(7)に不純物ドーピングを行う。引き続き、化学機械研磨(CMP)あるいはエッチバックにより不要部を除去したのち、熱酸化により、この多結晶シリコン(7)上に酸化シリコン膜9を形成する。

【0024】

ソース領域13となるN型拡散層及びボディ領域12となるP型拡散層を形成するため、図6(d)に示すように、P型ウェル層11中にイオン注入法を用いて、リン及びボロン不純物を注入する。

その後、半導体チップ表面に絶縁膜及び保護膜を堆積しソース電極1sとソース領域13を電気的に導通させるため、ソースコンタクト開口部3を設けて、アルミニウム薄膜を形成し、ソース電極1s、チャネルストッパ電極1csなどを構成する金属配線を形成する。このようにして、アルミニウム薄膜のパターニングに際し、マスクパターンを変更するのみで、図1乃至図5に示す半導体装置が形成される。

【0025】

この構成によれば、スクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域と、トレンチMOSFET周縁部の拡散領域11sとしてのP−領域との間に、アルミニウム配線を用いたチャネルストッパ電極1csを形成しており、配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制することができる。従ってアルミニウム配線パターンの変更のみで、耐圧、リーク特性の劣化を防止することができる。

【0026】

ここでアルミニウム配線で構成されるチャネルストッパ電極のスクライブ領域周縁部の埋め込み拡散領域11tへのはみ出し量と耐圧との関係を測定した結果を図7に示す。曲線aはチャネルストッパ電極がない場合、曲線bはチャネルストッパ電極がある場合の耐圧特性を示す。高温逆バイアス試験後、デバイスのリーク電流(IDSS)がVDSS18V近傍から増加し、段付きの特性を示した。そして電流増加後は飽和傾向にあり、耐圧変動はなかった。この結果からもチャネルストッパ電極の存在によりリークが抑制できることがわかる。

【0027】

(実施の形態2)

次に本発明の実施の形態2について説明する。

実施の形態2では、図8および図9に示すように、前記実施の形態1におけるチャネルストッパ電極1csに加え、トレンチゲート7に接続され、多結晶シリコンで形成されるゲート周辺配線2と同一工程で形成された多結晶シリコンからなるチャネルストッパ層2cdをこのチャネルストッパ電極(アルミニウム配線)よりも下層に設け、トレンチMOSFET周縁部の拡散領域11sとしてのP−領域(ソース領域11s)とスクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域との間のチャネル領域に絶縁膜14を介して、対向するように配置し、よりチャネルストッパ効果を高めるようにしたことを特徴とするものである。

なおここで8はコンタクト性を高めるための高濃度コンタクト領域である。

【0028】

(実施の形態3)

次に本発明の実施の形態3について説明する。

前記実施の形態2では、図8および図9に示すように、前記実施の形態1におけるチャネルストッパ電極1csに加え、トレンチゲート7に接続され、多結晶シリコンで形成されるゲート周辺配線2と同一工程で形成された多結晶シリコンからなるチャネルストッパ層2cdをこのチャネルストッパ電極よりも下層に設けたが、本実施の形態では、図10に示すように、スクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域に、逆導電型の半導体領域であるnウェルからなるチャンネルストッパ内層20を形成したことを特徴とするものである。なお図10は図1のA-A断面に相当する断面である。

【0029】

この構成においても、トレンチMOSFET周縁部の拡散領域11sとしてのP−領域(ソース領域11s)とスクライブ領域周縁部の埋め込み拡散領域11tとしてのP−領域との間のチャネル領域にと反転層が形成されリークが発生するのを抑制することができる。

また、前記第1乃至第3の実施の形態におけるチャネルストッパは2つ以上を併設することも可能である。

【0030】

また前記実施の形態では、トレンチMOSFETについて説明したが、MOSFETに限定されることなく、トレンチキャパシタ、DRAMなど、トレンチ構造を有する他の素子にも適用可能である。特にスクライブ周縁部にテスト用のコンタクトを形成するために埋め込み拡散領域をもつデバイスに適用可能であり、スクライブ周縁部の埋め込み拡散領域とデバイス周縁部の拡散領域との間に、配線を用いたチャネルストッパを形成しているため、配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制し、リーク電流の発生・耐圧の劣化を防止することができる。

【0031】

この構成により配線層のパターニングに際し、パターンの変更のみで、反転層の形成を抑制し、リーク電流の発生・耐圧の劣化を防止することができるという特徴を有する。なおチャネルストッパ電極1csおよびチャネルストッパ層2csはドレイン電極1dと同電位となるように構成されている。

【産業上の利用可能性】

【0032】

以上説明してきたように、本発明によれば高耐圧化に際しても、リーク電流の発生を抑制することができることから、車載用など信頼性の高い電子デバイスへの適用が有効である。

【図面の簡単な説明】

【0033】

【図1】本発明の実施の形態1に係るトレンチMOSFETの要部平面概念図

【図2】図1のA−A断面図

【図3】図1のB−B断面図

【図4】本発明の実施の形態1に係るトレンチMOSFETの全体概要平面図

【図5】図4のA-A‘断面図

【図6】本発明の実施の形態1に係るトレンチMOSFETの製造工程図

【図7】チャネルストッパ電極の突出長とリーク電流との関係を測定した結果を示す図

【図8】本発明の実施の形態2に係るトレンチMOSFETのA−A断面図

【図9】同トレンチMOSFETのB−B断面図

【図10】本発明の実施の形態3に係るトレンチMOSFETのA−A断面図

【図11】従来例のトレンチMOSFETのA−A断面図

【図12】従来例のトレンチゲート構造のB−B断面図

【符号の説明】

【0034】

1g ゲート電極

1s ソース電極

1d ドレイン電極

1cs チャネルストッパ電極

2 ゲート周辺配線

2cs チャネルストッパ配線(層)

3 ソースコンタクト開口部

T トレンチ

5 N+型基板

6 N-エピタキシャル層

4,7 トレンチゲート(多結晶シリコン)

9,14 絶縁膜

10 ゲート酸化膜

11 Pウェル

11t スクライブ領域周縁部の埋め込み拡散領域

11s トレンチMOSFET周縁部の拡散領域

12 ボディ領域

13 ソース領域

20 チャネルストッパ層

【特許請求の範囲】

【請求項1】

所望のデバイスが形成されると共に、デバイス周縁部に第1の導電型を有する第1の不純物領域を備えた半導体基板で構成され、前記半導体基板のスクライブ領域に第1の導電型を有する第2の不純物領域が形成された半導体装置であって、

前記スクライブ領域の第1の不純物領域と前記第2の不純物領域との間にチャネルストッパを形成した半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記チャネルストッパは、前記スクライブ領域の第1の不純物領域と前記第2の不純物領域との間において、前記半導体基板上に形成されたチャネルストッパ配線層である半導体装置。

【請求項3】

請求項1または2に記載の半導体装置であって、

前記チャネルストッパは、前記スクライブ領域の第1の不純物領域と前記第2の不純物領域との間において、前記半導体基板表面に絶縁膜を介して形成されたチャネルストッパ層である半導体装置。

【請求項4】

請求項3に記載の半導体装置であって、

前記チャネルストッパ層は、アルミニウム配線である半導体装置。

【請求項5】

請求項3に記載の半導体装置であって、

前記チャネルストッパ層は、アルミニウム配線と前記アルミニウム配線の下層に形成された多結晶シリコン層とで構成された半導体装置。

【請求項6】

請求項1乃至5のいずれかに記載の半導体装置であって、

前記チャネルストッパ層は、前記スクライブ領域の前記第2の不純物領域の少なくとも前記第1の不純物領域に対向する領域に形成された第2の導電型を有する第3の不純物領域を具備した半導体装置。

【請求項7】

請求項1乃至6のいずれかに記載の半導体装置であって、

前記半導体基板は、所望の不純物濃度を有する半導体層を備え、

前記半導体層内に形成された複数のストライプ状のトレンチ内にゲート酸化膜を介して導電体層を埋め込み形成したトレンチゲートと、

前記半導体層表面を覆う絶縁膜と、

前記絶縁膜を貫通し、ソースコンタクト開口部を通して形成されたソース電極と、

前記半導体層内に形成され、前記ソース電極に電気的に接続されたボディ領域及び前記第1の不純物領域としてのソース領域と、

前記トレンチゲートの周縁部で前記トレンチゲートに接続されたゲート周辺配線と、

前記ソース電極と同一表面上であって、前記ソース電極から離間した位置に形成され、前記ゲート周辺配線に接続されるゲート電極と、

ドレイン電極とを具備し、

前記第2の不純物領域は、前記ソース領域の外縁近傍に所定の間隔を隔てて形成され、スクライブ領域を構成する半導体装置。

【請求項8】

請求項7に記載の半導体装置であって、

前記チャネルストッパは前記ソース電極と同一層で構成された半導体装置。

【請求項9】

請求項7に記載の半導体装置であって、

前記チャネルストッパは2層で構成され下層側が前記トレンチゲートと同一層で構成された半導体装置。

【請求項10】

請求項7に記載の半導体装置であって、

前記チャネルストッパは前記第2の不純物領域内で、前記ソース領域と対向する領域を含む要に形成された第2の導電型を有する第3の不純物領域である半導体装置。

【請求項11】

請求項7乃至10のいずれかに記載の半導体装置であって、

前記チャネルストッパは、前記半導体基板のコーナー部分で、前記ドレイン電極と電気的に接続された半導体装置。

【請求項1】

所望のデバイスが形成されると共に、デバイス周縁部に第1の導電型を有する第1の不純物領域を備えた半導体基板で構成され、前記半導体基板のスクライブ領域に第1の導電型を有する第2の不純物領域が形成された半導体装置であって、

前記スクライブ領域の第1の不純物領域と前記第2の不純物領域との間にチャネルストッパを形成した半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記チャネルストッパは、前記スクライブ領域の第1の不純物領域と前記第2の不純物領域との間において、前記半導体基板上に形成されたチャネルストッパ配線層である半導体装置。

【請求項3】

請求項1または2に記載の半導体装置であって、

前記チャネルストッパは、前記スクライブ領域の第1の不純物領域と前記第2の不純物領域との間において、前記半導体基板表面に絶縁膜を介して形成されたチャネルストッパ層である半導体装置。

【請求項4】

請求項3に記載の半導体装置であって、

前記チャネルストッパ層は、アルミニウム配線である半導体装置。

【請求項5】

請求項3に記載の半導体装置であって、

前記チャネルストッパ層は、アルミニウム配線と前記アルミニウム配線の下層に形成された多結晶シリコン層とで構成された半導体装置。

【請求項6】

請求項1乃至5のいずれかに記載の半導体装置であって、

前記チャネルストッパ層は、前記スクライブ領域の前記第2の不純物領域の少なくとも前記第1の不純物領域に対向する領域に形成された第2の導電型を有する第3の不純物領域を具備した半導体装置。

【請求項7】

請求項1乃至6のいずれかに記載の半導体装置であって、

前記半導体基板は、所望の不純物濃度を有する半導体層を備え、

前記半導体層内に形成された複数のストライプ状のトレンチ内にゲート酸化膜を介して導電体層を埋め込み形成したトレンチゲートと、

前記半導体層表面を覆う絶縁膜と、

前記絶縁膜を貫通し、ソースコンタクト開口部を通して形成されたソース電極と、

前記半導体層内に形成され、前記ソース電極に電気的に接続されたボディ領域及び前記第1の不純物領域としてのソース領域と、

前記トレンチゲートの周縁部で前記トレンチゲートに接続されたゲート周辺配線と、

前記ソース電極と同一表面上であって、前記ソース電極から離間した位置に形成され、前記ゲート周辺配線に接続されるゲート電極と、

ドレイン電極とを具備し、

前記第2の不純物領域は、前記ソース領域の外縁近傍に所定の間隔を隔てて形成され、スクライブ領域を構成する半導体装置。

【請求項8】

請求項7に記載の半導体装置であって、

前記チャネルストッパは前記ソース電極と同一層で構成された半導体装置。

【請求項9】

請求項7に記載の半導体装置であって、

前記チャネルストッパは2層で構成され下層側が前記トレンチゲートと同一層で構成された半導体装置。

【請求項10】

請求項7に記載の半導体装置であって、

前記チャネルストッパは前記第2の不純物領域内で、前記ソース領域と対向する領域を含む要に形成された第2の導電型を有する第3の不純物領域である半導体装置。

【請求項11】

請求項7乃至10のいずれかに記載の半導体装置であって、

前記チャネルストッパは、前記半導体基板のコーナー部分で、前記ドレイン電極と電気的に接続された半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2010−87196(P2010−87196A)

【公開日】平成22年4月15日(2010.4.15)

【国際特許分類】

【出願番号】特願2008−254051(P2008−254051)

【出願日】平成20年9月30日(2008.9.30)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成22年4月15日(2010.4.15)

【国際特許分類】

【出願日】平成20年9月30日(2008.9.30)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]