半導体装置

【課題】配線基板上に実装された半導体チップと配線基板上のワイヤボンドパッドとを接続するボンディングワイヤが半導体チップに干渉することを回避しつつ、半導体チップとワイヤボンドパッドまでの距離が小さい半導体装置を提供する。

【解決手段】配線基板2上に半導体チップ1が実装され、配線基板2上のワイヤボンドパッド5と半導体チップ1上の電極パッド4とがボンディングワイヤを介して接続された半導体装置8であって、電極パッド4よりも半導体チップ1の端部に近接した位置にワイヤボンドパッドを有する中継基板10が設けられ、半導体チップ1上の電極パッド4と中継基板10上のワイヤボンドパッドとが第1のボンディングワイヤ3Aを介して接続され、中継基板10上のワイヤボンドパッドと配線基板2上のワイヤボンドパッド5とが第2のボンディングワイヤ3Bを介して接続されている。

【解決手段】配線基板2上に半導体チップ1が実装され、配線基板2上のワイヤボンドパッド5と半導体チップ1上の電極パッド4とがボンディングワイヤを介して接続された半導体装置8であって、電極パッド4よりも半導体チップ1の端部に近接した位置にワイヤボンドパッドを有する中継基板10が設けられ、半導体チップ1上の電極パッド4と中継基板10上のワイヤボンドパッドとが第1のボンディングワイヤ3Aを介して接続され、中継基板10上のワイヤボンドパッドと配線基板2上のワイヤボンドパッド5とが第2のボンディングワイヤ3Bを介して接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板上に半導体チップが実装された半導体装置に関するものである。

【背景技術】

【0002】

半導体チップの集積度は年々向上している。半導体チップの集積度の向上に伴って、半導体チップは高密度化、高性能化され、動作速度も高速化されている。また、半導体チップを含む半導体装置(「半導体パッケージ」と呼ばれる場合もある。)に対しても、小型化、薄型化の要求が高まってきている。小型化を目的とした半導体装置の構造としては、例えばBGA(Ball Grid Array)構造やCSP(Chip Size Package)構造などが知られている。これらの構造では、配線基板に実装された半導体チップの電極パッドと配線基板のワイヤボンドパッドとがボンディングワイヤなどにより接続される。また、配線基板に実装された半導体チップは、封止樹脂により封止される。さらに、配線基板の半導体チップが実装されている面(以下「実装面」という。)とは反対側の面(以下「裏面」という。)には、外部端子電極となる半田ボールが設けられる。

【0003】

ここで、汎用のDRAM(Dynamic Random Access Memory)のような電極パッドが半導体チップの中央に配列されている半導体チップを含む半導体装置の概略構造を図11、図12に示す。図11は、半導体装置8の断面図であり、図12はボンディングワイヤ形成後(樹脂封止前)の実装面側の平面図である。図示されている半導体チップ1は、配線基板2の実装面上にフェイスアップ(半導体チップの回路面が配線基板の実装面と逆側に位置)で実装されている。また、半導体チップ1上の電極パッド4と配線基板2上のワイヤボンドパッド5とを接続するボンディングワイヤ3が図11、図12に示すように設けられている。

【特許文献1】特開2003−68782号公報

【特許文献2】特開2008−66389号公報

【特許文献3】特開平11−307483号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

上記のような半導体装置においては、半導体チップの回路面に設けられている電極パッドと配線基板の実装面に設けられているワイヤボンドパッドとを接続するボンディングワイヤが半導体チップのエッジ部(端部)に干渉することを避けなければならない。そのため、ボンディングワイヤ3の形状を図11に示すような形状とする必要がある。結果、ワイヤボンドパッド5を半導体チップ1の端部から離れた位置に設けることとなり、半導体チップ1の端部と配線基板2上のワイヤボンドパッド5との間の距離D1が大きく(長く)なる。さらには、半導体チップ1の端部と半導体装置8の端部との間の距離D2も大きく(長く)なってしまい、半導体装置8が大型化してしまう。

【0005】

本発明の目的は、上記課題を解決し、半導体装置の小型化を実現することである。

【課題を解決するための手段】

【0006】

本発明の半導体装置は、配線基板上に半導体チップが実装され、前記配線基板上のワイヤボンドパッドと前記半導体チップ上の電極パッドとがボンディングワイヤを介して接続された半導体装置であって、前記半導体チップの高さよりも、前記半導体チップの端部から前記配線基板上の前記ワイヤボンドパッドまでの距離の方が小さいことを特徴とする。

【発明の効果】

【0007】

配線基板上に実装された半導体チップと配線基板上のワイヤボンドパッドとを接続するボンディングワイヤが半導体チップに干渉することを回避しつつ、半導体チップとワイヤボンドパッドとを可及的に近づけることができる。

【発明を実施するための最良の形態】

【0008】

(実施形態1)

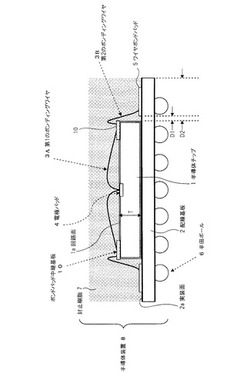

図1、図2を参照しながら本発明の半導体装置の実施形態の一例について説明する。図1は、本実施形態に係る半導体装置8の断面図、図2は平面図である。

【0009】

本実施形態に係る半導体装置8は、配線基板2と、配線基板2の実装面2aにフェイスアップで実装された半導体チップ1とを少なくとも有する。

【0010】

半導体チップ1の回路面1aの中央には、複数の電極パッド4が第1の方向に沿って配列されている。ここで、半導体チップ1の回路面1aとは、配線基板2に実装される面とは反対の上面を意味している。さらに、半導体チップ1の回路面1aの端部には、中継基板(ボンドパッド中継基板10)が設けられている。換言すれば、半導体チップ1の上面端部には、中継基板10が設けられている。具体的には、第1の方向に沿って形成された電極パッド4の列(電極パッド列)の両外側に、帯状のボンドパッド中継基板10が電極パッド列と平行に配置されている。換言すれば、複数の電極パッド4に対向して、半導体チップ1の2辺に沿って複数のボンドパッド中継基板10が設けられている。

【0011】

図2に示すように、ボンドパッド中継基板10は、帯状の絶縁部10aと、該絶縁部10aの長手方向に沿って設けられた複数のワイヤボンドパッド10bとを有する。

【0012】

各電極パッド4は、対応するボンドパッド中継基板10の対応するワイヤボンドパッド10bに第1のボンディングワイヤ3Aを介して接続されている。さらに、各ボンドパッド中継基板10の各ワイヤボンドパッド10bは、配線基板2上の対応するワイヤボンドパッド5に、第2のボンディングワイヤ3Bを介して接続されている。

【0013】

図1に示されているように、第2のボンディングワイヤ3Bは、ボンドパッド中継基板10から上方に向けて略垂直に立ち上がった後に、配線基板2上のワイヤボンドパッド5に向けて急角度で降下している。換言すれば、第2のボンディングワイヤ3Bは、配線基板2上のワイヤボンドパッド5からボンドパッド中継基板10よりも高い位置まで急角度で立ち上がった後に、ボンドパッド中継基板10に向けて略垂直に降下している。

【0014】

上記構造により、半導体チップ1上の電極パッド4と、配線基板2上のワイヤボンドパッド5とを接続するボンディングワイヤが半導体チップ1に干渉することを回避しつつ、半導体チップ1の端部(側面)とワイヤボンドパッド5との間の距離D1を小さく(短く)することができる。さらには、半導体チップ1の端部と半導体装置8の端部(配線基板2の側面)との間の距離D2も小さく(短く)することができ、半導体装置8が小型化される。本実施形態では、上記距離D1は、半導体チップ1の高さ(厚み)Tよりも小さい(短い)。

【0015】

次に、図3〜図6を参照しながら本実施形態に係る半導体装置8の製造方法の一例について説明する。図3〜図6は、各製造工程における断面図である。

【0016】

まず、図3に示すように、半導体チップ1を配線基板2の実装面2a上の実装領域にフェイスアップで実装する。なお、配線基板2の上記実装領域の周囲には、予めワイヤボンドパッド5が形成されている。さらに、ワイヤボンドパッド5の位置は、該ワイヤボンドパッド5から上記実装領域に実装された半導体チップ1の端部までの距離D1が半導体チップ1の高さTよりも小さい所定距離D1となるように設定されている。

【0017】

次に、図4に示すように、半導体チップ1の回路面1aの端部にボンドパッド中継基板10を実装する。

【0018】

その後、図5に示すように、半導体チップ1の電極パッド4とボンドパッド中継基板10とを第1のボンディングワイヤ3Aによって接続(ボンディング)する。次に、図6に示すように、ボンドパッド中継基板10と配線基板2のワイヤボンドパッド5とを第2のボンディングワイヤ3Bによって接続(ボンディング)する。

【0019】

次いで、半導体チップ1、ボンディングワイヤ3A、3Bおよびワイヤボンドパッド5を封止樹脂7(図1)で封止し、配線基板2の裏面に、外部端子電極となる半田ボール6(図1)を形成する。

【0020】

ここで、ボンドパッド中継基板10には、FR4などの絶縁体基板(絶縁部)の上に、銅箔などの導電体によって配線パターン(ワイヤボンドパッド)が形成されたリジッド基板を用いることができる。また、ポリイミドテープ(絶縁部)などの上に、銅箔などの導電体によって配線パターン(ワイヤボンドパッド)が形成されたテープ基板を用いることもできる。リジッド基板には、コストが低いというメリットがあり、テープ基板にはパッケージの薄型化が可能であるというメリットがある。よって、半導体装置の用途に応じてリジッド基板とテープ基板とを使い分けることが好ましい。

【0021】

また、上記製造方法の説明から明らかなように、ボンドパッド中継基板10は、半導体チップ1の回路面1aに直接形成されるものではなく、回路面1aに事後的に実装される。よって、ボンドパッド中継基板10の実装位置を容易かつ低コストで変更することができる。換言すれば、ボンドパッド中継基板10の実装位置の変更に伴って半導体チップ1の製造工程に変更が生ずることはない。

【0022】

図7に示すように、図1に示す半導体チップ1の上に、同様の半導体チップ1を積層し、それら複数の半導体チップ1を一括して封止樹脂7で封止することもできる。図7には、2つの半導体チップ1が積層された小型積層パッケージを示したが、積層される半導体チップ1の数は3つ以上であってもよい。なお、複数の半導体チップを積層する際には、上段の半導体チップによって下段の半導体チップのボンディングワイヤなどが押し潰されて変形するなどの不具合を回避するために、上下の半導体チップの間にスペーサを介在させたり、下段の半導体チップを樹脂封止した後に上段の半導体チップを積層するなどすることが好ましい。

(実施形態2)

図8を参照しながら本発明の半導体装置の実施形態の他例について説明する。図8は、本実施形態に係る半導体装置8の断面図である。なお、実施形態1に係る半導体装置8と同一の構成については、図8中に同一の符号を付して説明を省略する。

【0023】

本実施形態に係る半導体装置8では、半導体チップ1上の電極パッド4と配線基板2上のワイヤボンドパッド5とを接続するボンディングワイヤ30が図8に示すようにうねっている。具体的には、ボンディングワイヤ30は、電極パッド4から略垂直に立ち上がって回路面1aから離間した後、半導体チップ1の端部に向けて緩やかな下り傾斜で降下して回路面1aに近接し、その後再び立ち上がって回路面1aから離間した後にワイヤボンドパッド5に向けて急角度で降下している。

【0024】

上記のようなボンディングワイヤ30の形状は、ボンディング時のキャピラリ(ボンディングワイヤ用のノズル)を図8に点線で示す軌跡を描くように移動させることで実現することができる。具体的には、一端を電極パッド4にボンディングさせたワイヤを半導体チップ1の端部に干渉しない位置まで近づけ、その後、再度半導体チップ1から離し、次いで急角度でワイヤボンドパッド5へボンディングさせる。

【0025】

上記構造により、半導体チップ1上の電極パッド4と、配線基板2上のワイヤボンドパッド5とを接続するボンディングワイヤ30が半導体チップ1に干渉することを回避しつつ、半導体チップ1の端部とワイヤボンドパッド5との間の距離D1を小さく(短く)することができる。さらには、半導体チップ1の端部と半導体装置8の端部(配線基板2の端部)との間の距離D2も小さく(短く)することができ、半導体装置8が小型化される。本実施形態においても、上記距離D1は、半導体チップ1の高さ(厚み)Tよりも小さい(短い)。本実施形態における距離D1の数値やその他の数値について図9を参照して説明する。本実施形態では、距離D1は50[um]、ワイヤボンドパッド5の長さLは200[um]、半導体チップ1の高さ(厚み)Tは190[um]である。すなわち、半導体チップ1の高さ(厚み)Tと距離D1との間には、T>(19/20)×D1の関係が成立している。また、半導体チップ1の端部(コーナー)からボンディングワイヤ30までの最短距離Aは20[um]である。この場合、ワイヤボンドパッド5の表面に対するボンディングワイヤ30の傾斜角度θは60度である。傾斜角度θは次の数式によって求めることができる。

【0026】

【数1】

【0027】

なお、図11に示す従来の半導体装置8における距離D1は200[um]である。よって、ワイヤボンドパッド5の表面に対するボンディングワイヤ3の傾斜角度θは40度である。また、本実施形態における、半導体チップ1の端部と半導体装置8の端部(配線基板2の端部)との間の距離D2は350[um]である。一方、図11に示す従来の半導体装置8における距離D2は500[um]である。すなわち、本実施形態の半導体装置8は、片側で150[um]、全体で300[um]の小型化が図られている。

【0028】

図10に示すように、図8に示す半導体チップ1の上に、同様の半導体チップ1を積層し、それら複数の半導体チップ1を一括して封止樹脂7で封止することもできる。図10には、2つの半導体チップ1が積層された小型積層パッケージを示したが、積層される半導体チップ1の数は3つ以上であってもよい。複数の半導体チップを積層する際には、上段の半導体チップによって下段の半導体チップのボンディングワイヤなどが押し潰されて変形するなどの不具合を回避するために、上下の半導体チップの間にスペーサを介在させたり、下段の半導体チップを樹脂封止した後に上段の半導体チップを積層するなどすることが好ましい。

【図面の簡単な説明】

【0029】

【図1】実施形態1に係る半導体装置の断面図である。

【図2】実施形態1に係る半導体装置の平面図である。

【図3】実施形態1に係る半導体装置の製造工程の一部を示す断面図である。

【図4】実施形態1に係る半導体装置の製造工程の他の一部を示す断面図である。

【図5】実施形態1に係る半導体装置の製造工程の他の一部を示す断面図である。

【図6】実施形態1に係る半導体装置の製造工程の他の一部を示す断面図である。

【図7】実施形態1に係る半導体装置の変形例を示す断面図である。

【図8】実施形態2に係る半導体装置の断面図である。

【図9】実施形態2に係る半導体装置の各部の寸法を説明するための図である。

【図10】実施形態2に係る半導体装置の変形例を示す断面図である。

【図11】従来の半導体装置の断面図である。

【図12】図11に示す半導体装置の平面図である。

【符号の説明】

【0030】

1 半導体チップ

2 配線基板

2a 実装面

3A 第1のボンディングワイヤ

3B 第2のボンディングワイヤ

30 ボンディングワイヤ

4 電極パッド

5 ワイヤボンドパッド

6 半田ボール

7 封止樹脂

8 半導体装置

10 ボンドパッド中継基板

【技術分野】

【0001】

本発明は、配線基板上に半導体チップが実装された半導体装置に関するものである。

【背景技術】

【0002】

半導体チップの集積度は年々向上している。半導体チップの集積度の向上に伴って、半導体チップは高密度化、高性能化され、動作速度も高速化されている。また、半導体チップを含む半導体装置(「半導体パッケージ」と呼ばれる場合もある。)に対しても、小型化、薄型化の要求が高まってきている。小型化を目的とした半導体装置の構造としては、例えばBGA(Ball Grid Array)構造やCSP(Chip Size Package)構造などが知られている。これらの構造では、配線基板に実装された半導体チップの電極パッドと配線基板のワイヤボンドパッドとがボンディングワイヤなどにより接続される。また、配線基板に実装された半導体チップは、封止樹脂により封止される。さらに、配線基板の半導体チップが実装されている面(以下「実装面」という。)とは反対側の面(以下「裏面」という。)には、外部端子電極となる半田ボールが設けられる。

【0003】

ここで、汎用のDRAM(Dynamic Random Access Memory)のような電極パッドが半導体チップの中央に配列されている半導体チップを含む半導体装置の概略構造を図11、図12に示す。図11は、半導体装置8の断面図であり、図12はボンディングワイヤ形成後(樹脂封止前)の実装面側の平面図である。図示されている半導体チップ1は、配線基板2の実装面上にフェイスアップ(半導体チップの回路面が配線基板の実装面と逆側に位置)で実装されている。また、半導体チップ1上の電極パッド4と配線基板2上のワイヤボンドパッド5とを接続するボンディングワイヤ3が図11、図12に示すように設けられている。

【特許文献1】特開2003−68782号公報

【特許文献2】特開2008−66389号公報

【特許文献3】特開平11−307483号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

上記のような半導体装置においては、半導体チップの回路面に設けられている電極パッドと配線基板の実装面に設けられているワイヤボンドパッドとを接続するボンディングワイヤが半導体チップのエッジ部(端部)に干渉することを避けなければならない。そのため、ボンディングワイヤ3の形状を図11に示すような形状とする必要がある。結果、ワイヤボンドパッド5を半導体チップ1の端部から離れた位置に設けることとなり、半導体チップ1の端部と配線基板2上のワイヤボンドパッド5との間の距離D1が大きく(長く)なる。さらには、半導体チップ1の端部と半導体装置8の端部との間の距離D2も大きく(長く)なってしまい、半導体装置8が大型化してしまう。

【0005】

本発明の目的は、上記課題を解決し、半導体装置の小型化を実現することである。

【課題を解決するための手段】

【0006】

本発明の半導体装置は、配線基板上に半導体チップが実装され、前記配線基板上のワイヤボンドパッドと前記半導体チップ上の電極パッドとがボンディングワイヤを介して接続された半導体装置であって、前記半導体チップの高さよりも、前記半導体チップの端部から前記配線基板上の前記ワイヤボンドパッドまでの距離の方が小さいことを特徴とする。

【発明の効果】

【0007】

配線基板上に実装された半導体チップと配線基板上のワイヤボンドパッドとを接続するボンディングワイヤが半導体チップに干渉することを回避しつつ、半導体チップとワイヤボンドパッドとを可及的に近づけることができる。

【発明を実施するための最良の形態】

【0008】

(実施形態1)

図1、図2を参照しながら本発明の半導体装置の実施形態の一例について説明する。図1は、本実施形態に係る半導体装置8の断面図、図2は平面図である。

【0009】

本実施形態に係る半導体装置8は、配線基板2と、配線基板2の実装面2aにフェイスアップで実装された半導体チップ1とを少なくとも有する。

【0010】

半導体チップ1の回路面1aの中央には、複数の電極パッド4が第1の方向に沿って配列されている。ここで、半導体チップ1の回路面1aとは、配線基板2に実装される面とは反対の上面を意味している。さらに、半導体チップ1の回路面1aの端部には、中継基板(ボンドパッド中継基板10)が設けられている。換言すれば、半導体チップ1の上面端部には、中継基板10が設けられている。具体的には、第1の方向に沿って形成された電極パッド4の列(電極パッド列)の両外側に、帯状のボンドパッド中継基板10が電極パッド列と平行に配置されている。換言すれば、複数の電極パッド4に対向して、半導体チップ1の2辺に沿って複数のボンドパッド中継基板10が設けられている。

【0011】

図2に示すように、ボンドパッド中継基板10は、帯状の絶縁部10aと、該絶縁部10aの長手方向に沿って設けられた複数のワイヤボンドパッド10bとを有する。

【0012】

各電極パッド4は、対応するボンドパッド中継基板10の対応するワイヤボンドパッド10bに第1のボンディングワイヤ3Aを介して接続されている。さらに、各ボンドパッド中継基板10の各ワイヤボンドパッド10bは、配線基板2上の対応するワイヤボンドパッド5に、第2のボンディングワイヤ3Bを介して接続されている。

【0013】

図1に示されているように、第2のボンディングワイヤ3Bは、ボンドパッド中継基板10から上方に向けて略垂直に立ち上がった後に、配線基板2上のワイヤボンドパッド5に向けて急角度で降下している。換言すれば、第2のボンディングワイヤ3Bは、配線基板2上のワイヤボンドパッド5からボンドパッド中継基板10よりも高い位置まで急角度で立ち上がった後に、ボンドパッド中継基板10に向けて略垂直に降下している。

【0014】

上記構造により、半導体チップ1上の電極パッド4と、配線基板2上のワイヤボンドパッド5とを接続するボンディングワイヤが半導体チップ1に干渉することを回避しつつ、半導体チップ1の端部(側面)とワイヤボンドパッド5との間の距離D1を小さく(短く)することができる。さらには、半導体チップ1の端部と半導体装置8の端部(配線基板2の側面)との間の距離D2も小さく(短く)することができ、半導体装置8が小型化される。本実施形態では、上記距離D1は、半導体チップ1の高さ(厚み)Tよりも小さい(短い)。

【0015】

次に、図3〜図6を参照しながら本実施形態に係る半導体装置8の製造方法の一例について説明する。図3〜図6は、各製造工程における断面図である。

【0016】

まず、図3に示すように、半導体チップ1を配線基板2の実装面2a上の実装領域にフェイスアップで実装する。なお、配線基板2の上記実装領域の周囲には、予めワイヤボンドパッド5が形成されている。さらに、ワイヤボンドパッド5の位置は、該ワイヤボンドパッド5から上記実装領域に実装された半導体チップ1の端部までの距離D1が半導体チップ1の高さTよりも小さい所定距離D1となるように設定されている。

【0017】

次に、図4に示すように、半導体チップ1の回路面1aの端部にボンドパッド中継基板10を実装する。

【0018】

その後、図5に示すように、半導体チップ1の電極パッド4とボンドパッド中継基板10とを第1のボンディングワイヤ3Aによって接続(ボンディング)する。次に、図6に示すように、ボンドパッド中継基板10と配線基板2のワイヤボンドパッド5とを第2のボンディングワイヤ3Bによって接続(ボンディング)する。

【0019】

次いで、半導体チップ1、ボンディングワイヤ3A、3Bおよびワイヤボンドパッド5を封止樹脂7(図1)で封止し、配線基板2の裏面に、外部端子電極となる半田ボール6(図1)を形成する。

【0020】

ここで、ボンドパッド中継基板10には、FR4などの絶縁体基板(絶縁部)の上に、銅箔などの導電体によって配線パターン(ワイヤボンドパッド)が形成されたリジッド基板を用いることができる。また、ポリイミドテープ(絶縁部)などの上に、銅箔などの導電体によって配線パターン(ワイヤボンドパッド)が形成されたテープ基板を用いることもできる。リジッド基板には、コストが低いというメリットがあり、テープ基板にはパッケージの薄型化が可能であるというメリットがある。よって、半導体装置の用途に応じてリジッド基板とテープ基板とを使い分けることが好ましい。

【0021】

また、上記製造方法の説明から明らかなように、ボンドパッド中継基板10は、半導体チップ1の回路面1aに直接形成されるものではなく、回路面1aに事後的に実装される。よって、ボンドパッド中継基板10の実装位置を容易かつ低コストで変更することができる。換言すれば、ボンドパッド中継基板10の実装位置の変更に伴って半導体チップ1の製造工程に変更が生ずることはない。

【0022】

図7に示すように、図1に示す半導体チップ1の上に、同様の半導体チップ1を積層し、それら複数の半導体チップ1を一括して封止樹脂7で封止することもできる。図7には、2つの半導体チップ1が積層された小型積層パッケージを示したが、積層される半導体チップ1の数は3つ以上であってもよい。なお、複数の半導体チップを積層する際には、上段の半導体チップによって下段の半導体チップのボンディングワイヤなどが押し潰されて変形するなどの不具合を回避するために、上下の半導体チップの間にスペーサを介在させたり、下段の半導体チップを樹脂封止した後に上段の半導体チップを積層するなどすることが好ましい。

(実施形態2)

図8を参照しながら本発明の半導体装置の実施形態の他例について説明する。図8は、本実施形態に係る半導体装置8の断面図である。なお、実施形態1に係る半導体装置8と同一の構成については、図8中に同一の符号を付して説明を省略する。

【0023】

本実施形態に係る半導体装置8では、半導体チップ1上の電極パッド4と配線基板2上のワイヤボンドパッド5とを接続するボンディングワイヤ30が図8に示すようにうねっている。具体的には、ボンディングワイヤ30は、電極パッド4から略垂直に立ち上がって回路面1aから離間した後、半導体チップ1の端部に向けて緩やかな下り傾斜で降下して回路面1aに近接し、その後再び立ち上がって回路面1aから離間した後にワイヤボンドパッド5に向けて急角度で降下している。

【0024】

上記のようなボンディングワイヤ30の形状は、ボンディング時のキャピラリ(ボンディングワイヤ用のノズル)を図8に点線で示す軌跡を描くように移動させることで実現することができる。具体的には、一端を電極パッド4にボンディングさせたワイヤを半導体チップ1の端部に干渉しない位置まで近づけ、その後、再度半導体チップ1から離し、次いで急角度でワイヤボンドパッド5へボンディングさせる。

【0025】

上記構造により、半導体チップ1上の電極パッド4と、配線基板2上のワイヤボンドパッド5とを接続するボンディングワイヤ30が半導体チップ1に干渉することを回避しつつ、半導体チップ1の端部とワイヤボンドパッド5との間の距離D1を小さく(短く)することができる。さらには、半導体チップ1の端部と半導体装置8の端部(配線基板2の端部)との間の距離D2も小さく(短く)することができ、半導体装置8が小型化される。本実施形態においても、上記距離D1は、半導体チップ1の高さ(厚み)Tよりも小さい(短い)。本実施形態における距離D1の数値やその他の数値について図9を参照して説明する。本実施形態では、距離D1は50[um]、ワイヤボンドパッド5の長さLは200[um]、半導体チップ1の高さ(厚み)Tは190[um]である。すなわち、半導体チップ1の高さ(厚み)Tと距離D1との間には、T>(19/20)×D1の関係が成立している。また、半導体チップ1の端部(コーナー)からボンディングワイヤ30までの最短距離Aは20[um]である。この場合、ワイヤボンドパッド5の表面に対するボンディングワイヤ30の傾斜角度θは60度である。傾斜角度θは次の数式によって求めることができる。

【0026】

【数1】

【0027】

なお、図11に示す従来の半導体装置8における距離D1は200[um]である。よって、ワイヤボンドパッド5の表面に対するボンディングワイヤ3の傾斜角度θは40度である。また、本実施形態における、半導体チップ1の端部と半導体装置8の端部(配線基板2の端部)との間の距離D2は350[um]である。一方、図11に示す従来の半導体装置8における距離D2は500[um]である。すなわち、本実施形態の半導体装置8は、片側で150[um]、全体で300[um]の小型化が図られている。

【0028】

図10に示すように、図8に示す半導体チップ1の上に、同様の半導体チップ1を積層し、それら複数の半導体チップ1を一括して封止樹脂7で封止することもできる。図10には、2つの半導体チップ1が積層された小型積層パッケージを示したが、積層される半導体チップ1の数は3つ以上であってもよい。複数の半導体チップを積層する際には、上段の半導体チップによって下段の半導体チップのボンディングワイヤなどが押し潰されて変形するなどの不具合を回避するために、上下の半導体チップの間にスペーサを介在させたり、下段の半導体チップを樹脂封止した後に上段の半導体チップを積層するなどすることが好ましい。

【図面の簡単な説明】

【0029】

【図1】実施形態1に係る半導体装置の断面図である。

【図2】実施形態1に係る半導体装置の平面図である。

【図3】実施形態1に係る半導体装置の製造工程の一部を示す断面図である。

【図4】実施形態1に係る半導体装置の製造工程の他の一部を示す断面図である。

【図5】実施形態1に係る半導体装置の製造工程の他の一部を示す断面図である。

【図6】実施形態1に係る半導体装置の製造工程の他の一部を示す断面図である。

【図7】実施形態1に係る半導体装置の変形例を示す断面図である。

【図8】実施形態2に係る半導体装置の断面図である。

【図9】実施形態2に係る半導体装置の各部の寸法を説明するための図である。

【図10】実施形態2に係る半導体装置の変形例を示す断面図である。

【図11】従来の半導体装置の断面図である。

【図12】図11に示す半導体装置の平面図である。

【符号の説明】

【0030】

1 半導体チップ

2 配線基板

2a 実装面

3A 第1のボンディングワイヤ

3B 第2のボンディングワイヤ

30 ボンディングワイヤ

4 電極パッド

5 ワイヤボンドパッド

6 半田ボール

7 封止樹脂

8 半導体装置

10 ボンドパッド中継基板

【特許請求の範囲】

【請求項1】

配線基板上に半導体チップが実装され、前記配線基板上のワイヤボンドパッドと前記半導体チップ上の電極パッドとがボンディングワイヤを介して接続された半導体装置であって、

前記半導体チップの高さよりも、前記半導体チップの端部から前記配線基板上の前記ワイヤボンドパッドまでの距離の方が短いことを特徴とする半導体装置。

【請求項2】

前記半導体チップ上であって、前記電極パッドよりも前記半導体チップの端部に近接した位置に、ワイヤボンドパッドを有する中継基板が設けられ、

前記半導体チップ上の前記電極パッドと前記中継基板上の前記ワイヤボンドパッドとが第1のボンディングワイヤを介して接続され、

前記中継基板上の前記ワイヤボンドパッドと前記配線基板上の前記ワイヤボンドパッドとが第2のボンディングワイヤを介して接続されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記ボンディングワイヤは、前記電極パッドから略垂直に立ち上がって前記半導体チップから離間した後、前記半導体チップの端部に向けて斜めに降下して前記半導体チップに接近し、その後再び立ち上がって前記半導体チップから離間した後に前記ワイヤボンドパッドに向けて降下していることを特徴とする請求項1に記載の半導体装置。

【請求項4】

複数の前記電極パッドが前記半導体チップの中央に並べられて列を成し、

前記中継基板が、前記電極パッドの列の両側に、該電極パッドの列と平行に設けられていることを特徴とする請求項2に記載の半導体装置。

【請求項5】

配線基板と、

前記配線基板上に形成されたワイヤボンドパッドと、

前記配線基板上に実装されると共に前記配線基板に実装される面とは反対の上面中央に形成された電極パッドを備える半導体チップと、

前記半導体チップの前記上面端部に設けられた、ワイヤボンドパッドを有する中継基板と、

前記電極パッドと前記中継基板上の前記ワイヤボンドパッドとの間を接続する第1のボンディングワイヤと、

前記中継基板上の前記ワイヤボンドパッドと前記配線基板上の前記ワイヤボンドパッドとの間を接続する第2のボンディングワイヤと、を備えることを特徴とする半導体装置。

【請求項6】

前記電極パッドは、前記半導体チップの中央部に第1の方向に沿って形成された複数の電極パッドから構成されていることを特徴とする請求項5記載の半導体装置。

【請求項7】

前記中継基板は、前記第1の方向に沿って形成された複数の電極パッドに対向して前記半導体チップの2辺に沿って形成された複数の中継基板によって構成されていることを特徴とする請求項6記載の半導体装置。

【請求項8】

前記中継基板には、前記複数の電極パッドに対応して設けられた複数のワイヤボンドパッドが形成されていることを特徴とする請求項6記載の半導体装置。

【請求項9】

前記半導体チップの側面から前記配線基板上の前記ワイヤボンドパッドまでの距離は前記半導体チップの高さよりも短く形成されていることを特徴とする請求項5乃至8のいずれか記載の半導体装置。

【請求項1】

配線基板上に半導体チップが実装され、前記配線基板上のワイヤボンドパッドと前記半導体チップ上の電極パッドとがボンディングワイヤを介して接続された半導体装置であって、

前記半導体チップの高さよりも、前記半導体チップの端部から前記配線基板上の前記ワイヤボンドパッドまでの距離の方が短いことを特徴とする半導体装置。

【請求項2】

前記半導体チップ上であって、前記電極パッドよりも前記半導体チップの端部に近接した位置に、ワイヤボンドパッドを有する中継基板が設けられ、

前記半導体チップ上の前記電極パッドと前記中継基板上の前記ワイヤボンドパッドとが第1のボンディングワイヤを介して接続され、

前記中継基板上の前記ワイヤボンドパッドと前記配線基板上の前記ワイヤボンドパッドとが第2のボンディングワイヤを介して接続されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記ボンディングワイヤは、前記電極パッドから略垂直に立ち上がって前記半導体チップから離間した後、前記半導体チップの端部に向けて斜めに降下して前記半導体チップに接近し、その後再び立ち上がって前記半導体チップから離間した後に前記ワイヤボンドパッドに向けて降下していることを特徴とする請求項1に記載の半導体装置。

【請求項4】

複数の前記電極パッドが前記半導体チップの中央に並べられて列を成し、

前記中継基板が、前記電極パッドの列の両側に、該電極パッドの列と平行に設けられていることを特徴とする請求項2に記載の半導体装置。

【請求項5】

配線基板と、

前記配線基板上に形成されたワイヤボンドパッドと、

前記配線基板上に実装されると共に前記配線基板に実装される面とは反対の上面中央に形成された電極パッドを備える半導体チップと、

前記半導体チップの前記上面端部に設けられた、ワイヤボンドパッドを有する中継基板と、

前記電極パッドと前記中継基板上の前記ワイヤボンドパッドとの間を接続する第1のボンディングワイヤと、

前記中継基板上の前記ワイヤボンドパッドと前記配線基板上の前記ワイヤボンドパッドとの間を接続する第2のボンディングワイヤと、を備えることを特徴とする半導体装置。

【請求項6】

前記電極パッドは、前記半導体チップの中央部に第1の方向に沿って形成された複数の電極パッドから構成されていることを特徴とする請求項5記載の半導体装置。

【請求項7】

前記中継基板は、前記第1の方向に沿って形成された複数の電極パッドに対向して前記半導体チップの2辺に沿って形成された複数の中継基板によって構成されていることを特徴とする請求項6記載の半導体装置。

【請求項8】

前記中継基板には、前記複数の電極パッドに対応して設けられた複数のワイヤボンドパッドが形成されていることを特徴とする請求項6記載の半導体装置。

【請求項9】

前記半導体チップの側面から前記配線基板上の前記ワイヤボンドパッドまでの距離は前記半導体チップの高さよりも短く形成されていることを特徴とする請求項5乃至8のいずれか記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2010−87403(P2010−87403A)

【公開日】平成22年4月15日(2010.4.15)

【国際特許分類】

【出願番号】特願2008−257367(P2008−257367)

【出願日】平成20年10月2日(2008.10.2)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成22年4月15日(2010.4.15)

【国際特許分類】

【出願日】平成20年10月2日(2008.10.2)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]