半導体装置

【課題】ミリ波帯等の高周波伝送線路に介在されるワイヤボンディング長を短くし、その部分の寄生インダクタンスの影響による信号品質の劣化を抑制するとともに、放熱性を高めること。

【解決手段】半導体装置10は、半導体素子(チップ)30が配線基板20に形成されたキャビティ27内にその底面との間に接着材料33を介在させて搭載され、チップの電極端子31がキャビティ周囲の基板上に形成された配線部分22a,22bにワイヤ32を介して接続された構造を有する。チップ30は、配線部分のうち他の配線に比べて高周波用の配線22aが形成されている領域に近い側のキャビティの側壁27aに密着して搭載され、チップ30を密着させた側のキャビティの底面27eに凹部28が設けられ、さらにこの凹部の底面から基板外部に繋がるサーマルビア29が設けられている。

【解決手段】半導体装置10は、半導体素子(チップ)30が配線基板20に形成されたキャビティ27内にその底面との間に接着材料33を介在させて搭載され、チップの電極端子31がキャビティ周囲の基板上に形成された配線部分22a,22bにワイヤ32を介して接続された構造を有する。チップ30は、配線部分のうち他の配線に比べて高周波用の配線22aが形成されている領域に近い側のキャビティの側壁27aに密着して搭載され、チップ30を密着させた側のキャビティの底面27eに凹部28が設けられ、さらにこの凹部の底面から基板外部に繋がるサーマルビア29が設けられている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板に半導体素子を搭載した半導体装置に関し、より詳細には、ミリ波帯等の高周波回路を備えた半導体素子(チップ)が配線基板に設けられたキャビティ内にその底面との間に接着材料を介在させて搭載されるとともに、半導体素子の電極端子(パッド)がキャビティの周囲の基板上に形成された配線部分にワイヤを介して接続された構造を有する半導体装置に関する。

【0002】

かかる半導体装置において配線基板は、半導体チップを搭載するという点で、以下の記述では便宜上、「半導体パッケージ」もしくは単に「パッケージ」ともいう。

【背景技術】

【0003】

ミリ波帯(波長:10mm〜1mm、周波数:30GHz〜300GHz)の回路を備えたIC向けのミリ波アンテナを内蔵したパッケージの場合、所要の特性(高周波伝送特性、アンテナの指向性等)を確保するために、パッケージの設計に際して構造上考慮すべき幾つかの点がある。

【0004】

その一つとして、IC(半導体チップ)のパッケージ上への実装は、ワイヤを用いたボンディングにより行う。その際、チップの電極パッドと基板上のパッド(配線の一部に画定される部分)とを繋ぐワイヤの長さ(ワイヤ長)が長くなると、寄生インダクタンスが増大して信号品質の劣化をひき起こすため、そのワイヤ長は出来るだけ短くなるようにチップを配置する必要がある。このため、パッケージに凹部(キャビティ)を形成し、このキャビティ内にチップを搭載している。

【0005】

その際、チップは、キャビティの底面に塗布された接着剤(導電性ペースト等)を介してチップの裏面(電極パッドが形成されている側と反対側の面)が接着されるよう搭載される。また、ワイヤ長を極力短くするために、キャビティの深さは、チップの厚さとほぼ同じ程度となるように形成される。

【0006】

また、ミリ波帯の回路を備えたIC(チップ)は、その高周波動作によりチップ温度が高温となるため、チップの熱暴走や破壊等を防止するために、チップの動作時に放出された熱をパッケージ外部に放熱させるための手段を講じる必要がある。その典型的な手段として、サーマルビア(放熱用のビアホール)がある。このサーマルビアは、パッケージに設けられたキャビティの底面(接着剤を介してチップに熱結合されている)と基板外部とを繋ぐように基板の厚み方向に貫通して形成されている。

【0007】

かかる従来技術に関連する技術の一例は、下記の特許文献1に記載されている。この文献には、多段増幅器の最終段トランジスタの出力端子側の寄生インダクタンスのばらつきを低減するようにした半導体装置が開示されている。これを実現するため、配線基板に設けた四角形の窪み(キャビティ)の内側壁に当該トランジスタが形成された半導体チップの一辺を当接させてチップをキャビティ底に固定し、このキャビティ底にチップと同じ大きさのメタライズ層を形成した後、このメタライズ層上に所定量の溶融接合材を供給し、この溶融接合材をリフローして溶けた当該接合材の表面張力と自己整合作用によってチップの一辺をキャビティの内側壁の一辺に接触させている(図5)。

【0008】

また、これに関連する技術として、下記の特許文献2に記載されるように、半導体チップを接着剤にて設置する凹部(キャビティ)と外部端子を有するパッケージを備え、この外部端子にワイヤを介して半導体チップが電気的に接続された構造を有する半導体装置において、キャビティ表面の、キャビティと半導体チップの接する面に溝を形成するようにしたものがある。半導体チップとパッケージ基板を接着する際に、この溝に接着剤が入り込むことで、半導体チップの電極部分への接着剤の這い上がりを防止している。

【0009】

また、パッケージの放熱に関連する技術としては、下記の特許文献3に記載されるように、絶縁基板の内部にその厚み方向に貫くサーマルビアホールを複数配置した回路基板において、そのサーマルビアホールを形成するために、平均粒径が5μm以上であるAg粉末と平均粒径が1μm以下であるAg粉末を含有したペーストを使用したものがある。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】WO2003/023843号公報

【特許文献2】特開平9−283544号公報

【特許文献3】特開2002−198660号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上述したように半導体素子(チップ)とともにミリ波帯等の高周波伝送線路を備えたパッケージ(配線基板)の場合、所要の特性を確保する必要性から、基板上にキャビティを設け、このキャビティ内にチップを搭載するとともに、このチップと基板上に形成された配線部分との電気的な接続をワイヤボンディングにより行っている。つまり、ワイヤ長が極力短くなるようにチップを配置することで、寄生インダクタンスが増大するのを防ぐようにしている。

【0012】

このような設計上の配慮は、ミリ波帯(周波数:30GHz〜300GHz)よりも波長の長い高周波(20GHzや2GHz等)の信号伝送に対してはそれなりの効果が期待されるが、ミリ波帯の信号伝送に対してはあまり効果がないというのが現状である。つまり、ミリ波帯の信号伝送は、配線経路の特性インピーダンスの違いによる反射や、従来では無視できたような配線によって生じる微小な寄生インダクタンスも信号品質の劣化の要因となってくるからである。従って、高周波伝送線路の中でも特にミリ波帯用の伝送線路に介在されるワイヤの長さは、可能な限り短くするような工夫が必要である。

【0013】

また、現状の技術では、ミリ波の中でも60GHz以上の周波数を使用した製品は未だ開発されておらず、基板構成や実装方法など、様々な点を考慮した設計が必要となっている。

【0014】

なお、上記の特許文献1に記載された発明では、キャビティ内でチップの一辺をキャビティの内側壁の一辺に当接させることで、寄生インダクタンスのばらつきを低減するようにした技術が開示されている。この構成によれば、キャビティ内でチップと内側壁とを密着させているので、この部分近傍にはチップから放出された熱が溜まりやすく、他の部分と比べて放熱性が低下するものと推測される。しかし、この特許文献1では、その放熱を行うための手段や方法については一切言及されていない。

【0015】

本発明は、かかる従来技術における課題に鑑み創作されたもので、ミリ波帯等の高周波伝送線路に介在されるワイヤボンディング長を短くし、その部分の寄生インダクタンスの影響による信号品質の劣化を抑制するとともに、放熱性を高めた半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0016】

上記の従来技術の課題を解決するため、本発明の一形態によれば、半導体素子が配線基板に形成されたキャビティ内にその底面との間に接着材料を介在させて搭載されるとともに、前記半導体素子の電極端子が前記キャビティの周囲の基板上に形成された配線部分にワイヤを介して接続された構造を有する半導体装置において、前記半導体素子が、前記配線部分のうち他の配線に比べて高周波用の配線が形成されている領域に近い側の前記キャビティの側壁に密着して搭載され、前記半導体素子を密着させた側の前記キャビティの底面に、該底面から基板外部に繋がる放熱構造が形成されていることを特徴とする半導体装置が提供される。

【発明の効果】

【0017】

本発明の一形態に係る半導体装置の構成によれば、配線部分のうち他の配線に比べて高周波用の配線(例えば、ミリ波帯用の配線)が形成されている領域に近い側のキャビティの側壁に、半導体素子を密着させて搭載しているので、半導体素子と当該高周波用の配線とを接続するボンディングワイヤの長さを最小限に短くすることができる。これにより、そのワイヤ部分で発生する寄生インダクタンスを最小限とし、その寄生インダクタンスの影響による信号品質の劣化を抑制することが可能となる。

【0018】

また、キャビティ内で、高周波用の配線(ミリ波帯等)が形成されている領域に近い側の側壁に半導体素子を密着させているので、この密着させた側のキャビティ底面の近傍部分には熱が溜まりやすく、キャビティ内の他の部分と比べて放熱性が低下することが懸念される。これに対し、本発明では、半導体素子を密着させた側のキャビティの底面に、基板外部に繋がる放熱構造が設けられているので、放熱性を高めることができる。

【図面の簡単な説明】

【0019】

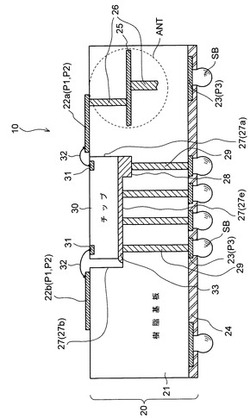

【図1】本発明の第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】図1の半導体装置をチップが実装される側の面から見たときの概略平面図である。

【図3】第1の実施形態の変形例に係る半導体装置(要部)の構成を示す断面図である。

【図4】本発明の第2の実施形態に係る半導体装置の構成を示す断面図である。

【発明を実施するための形態】

【0020】

以下、本発明の好適な実施の形態について、添付の図面を参照しながら説明する。

【0021】

(第1の実施形態…図1、図2参照)

図1は本発明の第1の実施形態に係る半導体装置の構成を断面図の形態で示したものであり、図2はこの半導体装置をチップが実装される側の面から平面的に見たときの概略構成を示している。

【0022】

本実施形態に係る半導体装置10は、例えば、画像伝送などのデータ容量の大きい通信を行うのに適応されたPDA等の携帯端末機器に組み込まれて使用される。この半導体装置10は、配線基板(パッケージ)20と、この配線基板20の一方の面側に実装された半導体素子(チップ)30とを備えている。さらに、図1には特に示していないが、チップ30及びこれに繋がる導体部分(ボンディングワイヤ32、配線22a等)を封止するためのキャップが適宜設けられている。

【0023】

配線基板(パッケージ)20は、基板本体を構成する樹脂基板21を有している。この樹脂基板21の形態としては、少なくとも両面に最外層の配線層22(22a,22b,22c,22d)及び23が形成された基板であって、各配線層22,23が基板内部を通して電気的に接続されている形態のものであれば十分である。

【0024】

樹脂基板21の内部には、図示のように配線層25が形成されていてもよいし、形成されていなくてもよい。本発明を特徴付ける部分ではないので詳細な図示は省略するが、樹脂基板21の内部に配線層が形成されている形態の場合、基板内部で樹脂層(絶縁層)を介在させて形成された各配線層(図1の例では、図示の簡略化のため1層の配線層25のみを示している)及び各配線層間を相互に接続するビアホール(に充填された導体:ビア26)を介して最外層の各配線層22,23が電気的に接続されている。この形態の基板は、例えば、ビルドアップ法を用いて形成することができる。一方、樹脂基板の内部に配線層が形成されていない形態の場合には、この樹脂基板の所要の箇所に適宜形成されたスルーホール(に充填された導体)を介して最外層の各配線層が相互に接続されている。

【0025】

配線層22,23,25及びビア26の材料としては、代表的に銅(Cu)が用いられる。また、樹脂層(絶縁層)の材料としては、熱硬化性のエポキシ系樹脂やポリイミド系樹脂等が好適に用いられる。

【0026】

さらに、パッケージ20の一方の面(チップ30が実装される側の面)には、最外層の配線層22の所要の箇所に画定されたパッドP1,P2の部分を露出させて表面を覆うように保護膜としてのソルダレジスト層(図示せず)が形成されている。ただし、後述するように配線層22(a,b,c,d)のうち、配線層22a,22bについては、パッドP1,P2と共に配線部分についても露出しており、配線層22c,22dについては、パッドP1のみが露出している。

【0027】

パッケージ20の他方の面にも、最外層の配線層23の所要の箇所に画定されたパッドP3の部分を露出させて表面を覆うように保護膜としてのソルダレジスト層24が形成されている。このソルダレジスト層24から露出するパッドP3には、本装置10をマザーボード等に実装する際に使用される外部接続端子(図示の例では、はんだボールSB)が接合されるので、そのコンタクト性を良くするために適当な表面処理を施している。典型的には、パッドP3(Cu)上にニッケル(Ni)めっき及び金(Au)めっきをこの順に施している。この場合、Niめっき層はバリヤメタル膜として機能する。

【0028】

なお、図1の例ではパッドP3にはんだボールSB(外部接続端子)を設けているが、これは必ずしも設ける必要はない。要は、必要なときに外部接続端子(はんだボールや金属ピン等)を接合できるように当該パッドP3が露出していれば十分である。

【0029】

配線基板(パッケージ)20は、図2に示すように平面視したときの形状が正方形であり、その大きさは15mm×15mm程度、厚さは1mm程度に選定されている。このパッケージ20には、一方の面のほぼ中央部に、半導体素子(チップ)30を搭載すると共に基板内に収容するためのキャビティ27が形成されている。

【0030】

このキャビティ27は、図2に示すように矩形(長方形)の形状に形成され、その4箇所の隅部は丸められている。キャビティ27の大きさは、長辺方向の長さが6mm程度、短辺方向の長さが4mm程度に選定され、その深さは300μm程度に選定されている。なお、図示の例ではキャビティ27の形状を矩形(長方形)としているが、必ずしもこれに限定されず、正方形や他の形状であってもよいことはもちろんである。

【0031】

このキャビティ27内に搭載されるチップ30は、例えば、シリコンウエハに所要のデバイスプロセスを施して作り込まれた複数のデバイスを各デバイス単位にダイシングして得られたシリコンチップ(「ダイ」ともいう。)である。このチップ30は、その電極パッド(端子)31が形成されている側の面を上にしたフェイスアップの態様で、キャビティ27内にその底面27eとの間に接着剤33を介在させて搭載されている。例えば、導電性ペースト(エポキシ系樹脂等の熱硬化性樹脂にAgやCu等の金属微粒子を分散させてペースト状にしたもの)をキャビティ27の底面に塗布し、この導電性ペースト(接着剤33)上にチップ30を載せ、接着剤33を加熱し硬化させて、チップ30をパッケージ20(キャビティ27内)に接着し固定する(ダイ・アタッチ)。

【0032】

配線基板(パッケージ)20上でキャビティ27の周囲は、配線形成領域WR(図2)である。この配線形成領域WRのうち、キャビティ27の長辺方向に沿った周縁部(各側壁27a,27b)の外側の領域(図2の例では左右方向の2箇所の領域)には、ミリ波帯等の高周波用の伝送線路(配線22a,22b)が設けられている。本実施形態では、右側の配線形成領域には60GHz(ミリ波帯)用の配線22aが形成されており、これと対向する左側の配線形成領域には、ミリ波帯よりも波長の長い高周波(20GHzや2GHz等)用の配線22bが形成されている。

【0033】

一方、キャビティ27の短辺方向に沿った周縁部(各側壁27c,27d)の外側の領域(図2の例では上下方向の2箇所の領域)には、チップ30に対する入出力(I/O)信号伝送用の配線、電源用及びグランド用の各配線22c,22dが形成されている。

【0034】

配線形成領域WRにおいて左右方向の2箇所の領域に高周波用の配線22a,22bを形成している理由は、当該配線のボンディング用パッドP1とチップ30側の対応する電極パッド31との距離(高周波伝送線路の一部をなすワイヤ32の長さ)を短くできるからである。つまり、ワイヤ長を短くすることで、そのワイヤ部分で発生する寄生インダクタンスを小さくし、当該配線上を伝送されるミリ波帯等の高周波信号の品質劣化を抑制できるからである。

【0035】

さらに本実施形態では、キャビティ27内にチップ30を搭載する際に、図示のようにキャビティ27内の、ミリ波帯用の配線22aが形成されている側の側壁27aに、チップ30の対応する側面が接触するように密着させている。これにより、ミリ波帯用の配線22aのパッドP1とチップ30側の対応する電極パッド31とを接続するワイヤ32の長さを更に短くすることができ、ミリ波帯信号の品質劣化の更なる抑制を図ることができる。

【0036】

この場合、キャビティ27内でチップ30を密着させた側と反対側に位置する高周波用の配線22bについては、そのボンディング用パッドP1とチップ30側の対応する電極パッド31とを接続するワイヤ32の長さは相対的に長くなる。しかしながら、そのワイヤ長は、他の配線22c,22dの各パッドP1とチップ30側の対応する各電極パッド31とを接続するワイヤ長に比べると十分に短いため、寄生インダクタンスの低減及びそれに基づく高周波信号の品質劣化の抑制には十分である。

【0037】

パッケージ20の表面に形成されたミリ波帯用の配線22aには、その層間接続用パッドP2を介して、樹脂基板21内に形成されたアンテナANT(図1参照)が接続されている。本実施形態では、図示のように基板内部の配線層25の一部分とこれに繋がるビア26によりアンテナANTが構成されている。アンテナANTの形態が図示の例に限定されないことはもちろんである。

【0038】

I/O信号伝送用、電源用、グランド用の各配線22c,22dは、それぞれボンディング用パッドP1の部分のみを露出させて、ソルダレジスト層で被覆されている。このソルダレジスト層については、図2の例では図示を省略している。

【0039】

一方、ミリ波帯等の高周波用の各配線22a,22bについては、所要の特性を確保するため、それぞれボンディング用パッドP1及び層間接続用パッドP2の部分と共に配線部分についても、当該ソルダレジスト層で被覆せずに、パッケージ20の面上に露出させている(図1参照)。このため、この露出部分を外部から保護する(つまり、ミリ波等の高周波伝送特性に及ぼされる影響を除去する)ために、中空構造の凹状のキャップ(図示せず)で封止する必要がある。

【0040】

このようなキャップは、耐熱性を有したエポキシ系樹脂等の熱硬化性樹脂(接着剤)によりパッケージ20上に接着される。その場合の接着剤が有する耐熱性は、最終的にパッケージ20の実装面側に外部接続端子(図示の例では、はんだボールSB)を接合する際のリフロー温度(例えば、240〜260℃前後)に耐え得るものである。

【0041】

パッケージ20に設けられるキャビティ27は、例えば、ビルドアップ法等により形成した多層配線樹脂基板(所要のパッケージ20)に対し、ルータ加工等の切削加工により形成することができる。さらに、このキャビティ27の底面27eの一部に、本発明を特徴付ける溝28(凹部)が形成されている。この溝28は、キャビティ27と同様に、ルータ加工等により形成することができる。

【0042】

この溝28は、図示のようにキャビティ27の底面27eのエッジ部分に設けられており、より具体的には、キャビティ27の底面27eとキャビティ27内でチップ30の側面が接触(密着)している側壁27aとが交差するエッジ部分に沿って直線状に形成されている。ただし、この溝28は必ずしも連続している必要はなく、チップ30の搭載時に溶融する接着剤33(導電性ペースト等)の流出量に合わせて適宜断続的に形成されていてもよい。

【0043】

この溝28(凹部)は、キャビティ27内でミリ波帯用の配線22aが形成されている側の側壁27aにチップ30の対応する側面を接触させた状態で搭載したときに、溶融した接着剤33の一部(搭載部分からはみ出した接着剤33の余分な部分)を溜めておくための「接着剤溜め部分」として機能する。特に、接着剤33を溝28に積極的に溜めておくようにする(充填する)のが望ましい。この「接着剤溜め部分」としての機能により、溝28は2つの役割を果たしている。

【0044】

第1の役割は、溝28に充填された接着剤33(硬化された導電性ペースト等)を介して、後述するサーマルビア29の一部(溝28の直下の領域に形成されるサーマルビア)にチップ30の裏面(フェイス面と反対側の面)を熱的に結合させることである。特に、図示のように接着剤33が溝28に充填された状態にあると、溝28内に溜められてはいるが充填されていない状態(つまり、空気が介在している状態)に比べて、チップ30から放出された熱の当該サーマルビア29の一部への伝達効果(熱伝導性)を高めることができる。

【0045】

第2の役割は、キャビティ27内へのチップ30の搭載時に溶融した接着剤33(硬化する前の導電性ペースト等)が、チップ30を密着させたキャビティ27の側壁27aに沿って這い上がるのを防ぐことである。接着剤33(導電性ペースト等)がキャビティ27の上端まで這い上がった場合、その上端近傍に位置するミリ波帯用の配線22a(パッドP1)に付着してショートするおそれがあるからである。また、接着剤33が導電性ペーストではなく、アクリル系樹脂やエポキシ系樹脂等の熱硬化性の絶縁樹脂からなる場合であっても、かかる絶縁樹脂は相応の誘電率を有しているため、ミリ波帯用の配線22aに付着するとその高周波伝送特性に影響を及ぼすからである。

【0046】

さらに、配線基板20(樹脂基板21)においてキャビティ27の底面27e(溝28を含む)の直下の領域には、基板の厚み方向に貫通する所要の数のサーマルビア29(少なくとも内壁部分にCuめっき等が施された放熱用のビアホール)が一定の配設間隔で形成されている。これらサーマルビア29のうち、一部のサーマルビア29は溝28の底面に露出し、残りのサーマルビア29はキャビティ27の底面27e(溝28が形成されている領域を除く)に露出している。各サーマルビア29は、それぞれキャビティ27の底面27e及び溝28の底面上を被覆する接着剤33(硬化された導電性ペースト等)を介してチップ30の裏面(フェイス面と反対側の面)に熱的に結合されている。

【0047】

これによって、チップ30の動作時に放出された熱は、接着剤33を介して各サーマルビア29に確実に伝達され、さらに、各サーマルビア29に熱的に結合された外部接続端子(はんだボールSB)を介してパッケージ外部に放熱される。この場合の各サーマルビア29への熱伝達経路は2つあり、一方は、溝28に充填された接着剤33を介して当該サーマルビア29の一部に伝達される経路(第1の放熱構造)であり、他方は、チップ30の裏面とキャビティ27の底面27e(溝28が形成されている領域を除く)との間に介在する接着剤33を介して他のサーマルビア29に伝達される経路(第2の放熱構造)である。

【0048】

特に、キャビティ27内でチップ30の側面とキャビティ27の側壁27aとを密着させているので、何の手段も講じなければこのキャビティ27のエッジ部分(側壁27aと底面27eが交差するエッジ部分)近傍に熱が溜まりやすく、他の部分と比べて放熱性が悪くなる。本実施形態では、このエッジ部分近傍に溝28(凹部)を設けているので、キャビティ27のエッジ部分近傍に溜まった熱を、第1の放熱構造(溝28に充填された接着剤33及びこれに熱結合されたサーマルビア29)を介してパッケージ20の外部に有効に逃がすことができる(放熱性の向上)。

【0049】

以上説明したように、第1の実施形態に係る半導体装置10の構成によれば、パッケージ20に設けたキャビティ27内で、ミリ波帯用の配線22aが形成されている側の側壁27aにチップ30の側面を密着させてチップ搭載を行うとともに、チップ30を密着させた側のキャビティ底面27eに溝28(凹部)を設け、さらに、溝28の底面とキャビティ27の底面27e(溝28が形成されている領域を除く)にそれぞれ露出するサーマルビア29(上述した第1、第2の放熱構造)を形成している。

【0050】

先ず、キャビティ27内にチップ30を搭載する際に、ミリ波帯用の配線22aが形成されている側の側壁27aにチップ30を密着させているので、チップ30の電極パッド31と配線22aのパッドP1とを接続するボンディングワイヤ32の長さを短く(最小限に)することができる。これにより、そのワイヤ部分で発生する寄生インダクタンスを最小限とし、その寄生インダクタンスの影響によるミリ波帯信号の品質劣化を抑制することができる。

【0051】

また、チップ30を、キャビティ27内で側壁27aに接触させた状態で底面27eとの間に接着剤33(導電性ペースト等)を介在させて搭載したときに、溶融した接着剤33の一部(搭載部分からはみ出した接着剤33の余分な部分)は、溝28内に溜められて充填される。これにより、チップ30の裏面とキャビティ底面27eの間に介在する接着剤33及び溝28に充填された接着剤33を介してチップ30の裏面をそれぞれ対応するサーマルビア29に確実に熱結合させることができる。

【0052】

特に、キャビティ27内でチップ30を密着させた側のキャビティ底面27eの近傍部分には熱が溜まりやすいため、この部分に設けた溝28(充填された接着剤33)を放熱手段(第1の放熱構造)として積極的に利用しているので、放熱性の点で大いに有効である。

【0053】

また、キャビティ27内でチップ30を側壁27aに密着させたことにより、チップ搭載時に溶融した接着剤33の一部が側壁27aに沿って這い上がる可能性があるが、上述したように搭載部分からはみ出した接着剤33の余分な部分は溝28内に溜められているので、接着剤33の「這い上がり」を防止することができる。これにより、接着剤33がキャビティ27の上端まで這い上がった場合に起こり得る不都合(ミリ波帯用の配線22aに付着してショートしたり、あるいは特性上の影響を及ぼすこと)を解消することができる。

【0054】

上述した第1の実施形態の構成(図1)では、キャビティ27内でチップ30の側面が密着している側壁27aとキャビティ27の底面27eとが交差するエッジ部分に沿ってキャビティ27の直下の領域にのみ凹部(溝28)を形成した場合を例にとって説明したが、当該凹部の形状や配置形態がこれに限定されないことはもちろんである。要は、キャビティ27内へのチップ30の搭載時にその搭載部分から流出する接着剤33(導電性ペースト等)を溜めておくことで、その溜めた部分(接着剤33)を介してチップ30がパッケージ外部と熱的に結合されるような形状(第1の放熱構造)に形成されていれば十分である。図3はその場合の変形例を示したものである。

【0055】

図3は、図1に示す実施形態の変形例に係る半導体装置の要部(チップ30が搭載されているキャビティ27及びその周辺部分)の構成を断面図の形態で示したものであり、本来の放熱経路であるサーマルビア29とは異なる放熱経路を新たに設けた場合の実施形態を示している。

【0056】

図3(a)は一変形例に係る半導体装置10aの構成(要部)を示している。この半導体装置10aの構成では、キャビティ27内でチップ30の側面を密着させた側壁27aに、溝28と一体的に繋がる凹部28aを形成し、この凹部28aに接着剤33(導電性ペースト等)を溜めて放熱手段(第1の放熱構造)として利用することにより、放熱経路(面積)を増やしている。つまり、凹部28aは、溝28と同様に「接着剤溜め部分」として機能する。

【0057】

凹部28aは、ルータ加工等により、溝28と一体的に形成することができる。その形成の際、凹部28aの上端が基板21の上端面よりも下側に止まるようにするのが望ましい。このように凹部28aの上端を基板21内に止めておくことにより、キャビティ27内へのチップ30の搭載時に溶融した接着剤33が側壁27aに沿ってキャビティ27の上端まで這い上がる(この場合、ミリ波帯用の配線22a(パッドP1)に付着するおそれがある)のを確実に防止できるからである。

【0058】

この半導体装置10aの構成によれば、チップ30の動作時に放出された熱は、図中矢印で示すように、本来の放熱経路(チップ30の裏面とキャビティ27の底面27e及び溝28の底面との間に介在する接着剤33を介してサーマルビア29に伝達され、最終的にパッケージ外部に放熱される経路)とは別に、チップ30の側面上の凹部28aに溜められた接着剤33を介して基板21中にも放熱させることができる。これにより、第1の実施形態に係る半導体装置10と比べて、放熱効果を更に高めることができる。

【0059】

特に、キャビティ27内でチップ30とキャビティ27の側壁27aとを密着させているため、このキャビティ27のエッジ部分近傍に熱が溜まりやすく、キャビティ27内の他の部分と比べて放熱性は低下する。本実施形態では、当該エッジ部分近傍に設けた追加の凹部28aを放熱手段(第1の放熱構造)として利用しているので、放熱性の点で大いに有効である。

【0060】

図3(b)は他の変形例に係る半導体装置10bの構成(要部)を示している。この半導体装置10bの構成では、図3(a)の半導体装置10aと同様に、キャビティ27内でチップ30の側面を密着させた側壁27aに、溝28と一体的に繋がるテーパ状の凹部28bを形成し、このテーパ状の凹部28bに溜めた接着剤33(導電性ペースト等)を放熱手段(第1の放熱構造)として利用している。

【0061】

テーパ状の凹部28bは、図示のようにキャビティ27の下側から上側に向かって凹部28bの深さが徐々に浅くなるように形成されている。この凹部28bについても、上記の凹部28aと同様に、ルータ加工等により形成することができ、その際、凹部28bの上端が基板21の上端面よりも下側に止まるようにするのが望ましい。

【0062】

この半導体装置10bの構成によれば、図3(a)の半導体装置10aと同様に、チップ30の動作時に放出された熱は、本来の放熱経路(サーマルビア29を介してパッケージ外部に放熱される経路)とは別に、チップ30の側面上の凹部28bに溜められた接着剤33を介して基板21中にも放熱させることができ、放熱性の更なる向上に寄与することができる。

【0063】

(第2の実施形態…図4参照)

図4は本発明の第2の実施形態に係る半導体装置の構成を断面図の形態で示したものである。

【0064】

この第2の実施形態に係る半導体装置40(図4)は、上述した第1の実施形態に係る半導体装置10(図1)の構成と比べて、キャビティ27の底面27eに溝28(図1)を設けていない点、配線基板(パッケージ)50に設けたキャビティ27の直下の領域に形成されるサーマルビア29を、第1の実施形態のように一定の配設間隔で形成するのではなく、キャビティ27内でチップ30を密着させた側(ミリ波帯用の配線22aが形成されている領域に近い側)のキャビティ底面27eの近傍部分に「密に」形成した点で相違している。つまり、この部分に形成するサーマルビア29の単位面積あたりの数を、他の部分に形成するサーマルビア29の単位面積あたりの数よりも多くしている。ここに、キャビティ27の底面27eに「密に」形成されているサーマルビア29は「第1の放熱構造」を構成し、それ以外の部分に形成されるサーマルビア29は「第2の放熱構造」を構成する。他の構成については、第1の実施形態の場合と同じであるのでその説明は省略する。

【0065】

上述した第1の実施形態では、キャビティ27内でチップ30を密着させた側のキャビティ底面27eに設けた溝28(に充填された接着剤33)と、この溝28の底面から基板外部に繋がるサーマルビア29とにより第1の放熱構造を構成しているが、この第2の実施形態に係る半導体装置40の構成では、キャビティ27内でチップ30を密着させた側のキャビティ底面27eにサーマルビア29を「密に」形成することにより、所要の第1の放熱構造を構成している。

【0066】

従って、この第2の実施形態に係る半導体装置40の構成においても、上述した第1の実施形態の場合と同様に、キャビティ27内で熱が溜まりやすい部分(チップ30を密着させた側のキャビティ底面27eの近傍部分)に設けられた第1の放熱構造(密に配置されたサーマルビア29)により、放熱性を有効に高めることができる。

【0067】

この第2の実施形態の構成(図4)では、キャビティ27内でチップ30を密着させた側(ミリ波帯用の配線22aが形成されている領域に近い側)のキャビティ底面27eに直接熱結合される形でサーマルビア29を「密に」形成しているが(第1の放熱構造)、形成されるべきサーマルビア29(第1の放熱構造)は、必ずしもキャビティ27の底面27eに直接熱結合されている必要はない。例えば、第1の実施形態(図1)のような凹部(溝28)を介在させてもよい。

【0068】

すなわち、キャビティ27内でチップ30を密着させた側(ミリ波帯用の配線22aが形成されている領域に近い側)のキャビティ底面27eに溝28を形成し、この溝28の底面にサーマルビア29を「密に」形成してもよい。この場合、溝28に充填された接着剤33と、この溝28の底面から基板外部に繋がる「密に」配置されたサーマルビア29とにより、第1の放熱構造が構成される。この構成によれば、上述した第1の実施形態の場合と比べて、溝28の底面に熱結合された放熱経路としてのサーマルビア29の数が相対的に多いので、放熱性の更なる向上を図ることができる。

【0069】

また、この第2の実施形態の構成(図4)は、上述した第1の実施形態の変形例に係る半導体装置10a,10bの構成にも同様に適用することができる。この場合、凹部28a,28bが一体的に形成された溝28において、当該溝の底面が広がることでサーマルビア29(第1の放熱構造の一部)を「密に」形成することができ、放熱性を更に高めることができる。

【0070】

上述した各実施形態では、サーマルビア29はキャビティ27内で半導体素子(チップ30)の直下の領域にのみ形成されている場合を例にとって説明したが、サーマルビア29の形成領域がこれに限定されないことはもちろんである。チップ30の直下の領域に限らず、例えば、キャビティ27内でチップ30の搭載領域から露出されるように形成されている溝28の全面に亘って形成するようにしてもよい。この場合、キャビティ27内で熱的に結合されていないチップ30の直下以外の領域におけるサーマルビアに対しても、このサーマルビア上に形成された接着剤(溝28に充填された接着剤33)を介して放熱を行うことができ、放熱性の更なる向上に寄与する。

【0071】

また、上述した各実施形態では、キャビティ27内にチップ30を搭載する際に所定の1辺の側壁(ミリ波帯用の配線22aが形成されている側の側壁27a)にのみチップ30を密着させる場合を例にとって説明したが、本発明の要旨からも明らかなように、必ずしもその1辺にのみ密着させる必要はない。例えば、キャビティ27内の最大2辺(隣り合っている2辺)の側壁にチップ30の対応する2辺を接触(密着)させるようにしてもよい。この場合、形成される溝28や凹部28a,28b、サーマルビア29の配置形態については、上述した第1、第2の実施形態と同様の構成を適用することができる。この実施形態(キャビティ27内の最大2辺の側壁にチップ30を密着させる構成)では、信号用配線22c,22dや第2の高周波用配線22bが、チップ30とキャビティ側壁とが接する辺と隣り合う辺にも形成されている場合に、上記と同様の効果が得られる、

また、上述した各実施形態では、配線基板(パッケージ)の形態として樹脂基板を使用した場合を例にとって説明したが、本発明の要旨からも明らかなように、樹脂基板に限定されないことはもちろんであり、例えば、セラミック基板を使用した場合にも同様に適用することが可能である。

【符号の説明】

【0072】

10,10a,10b,40…半導体装置、

20,50…配線基板(パッケージ)、

22a,22b,22c,22d,23…配線(層)、

24…ソルダレジスト層(保護膜)、

27(27a〜27d,27e)…キャビティ(キャビティの側壁、底面)、

28…溝(接着剤溜め部分/凹部)、

28a,28b…凹部(接着剤溜め部分)、

29…サーマルビア(放熱用ビアホール)、

30…半導体素子(チップ)、

31…電極パッド(端子)、

32…ボンディングワイヤ、

33…チップ搭載用の接着剤(接着材料)、

ANT…アンテナ、

P1,P2,P3…パッド(ボンディング用、層間接続用、外部接続用)、

SB…はんだボール(外部接続端子)、

WR…配線形成領域。

【技術分野】

【0001】

本発明は、配線基板に半導体素子を搭載した半導体装置に関し、より詳細には、ミリ波帯等の高周波回路を備えた半導体素子(チップ)が配線基板に設けられたキャビティ内にその底面との間に接着材料を介在させて搭載されるとともに、半導体素子の電極端子(パッド)がキャビティの周囲の基板上に形成された配線部分にワイヤを介して接続された構造を有する半導体装置に関する。

【0002】

かかる半導体装置において配線基板は、半導体チップを搭載するという点で、以下の記述では便宜上、「半導体パッケージ」もしくは単に「パッケージ」ともいう。

【背景技術】

【0003】

ミリ波帯(波長:10mm〜1mm、周波数:30GHz〜300GHz)の回路を備えたIC向けのミリ波アンテナを内蔵したパッケージの場合、所要の特性(高周波伝送特性、アンテナの指向性等)を確保するために、パッケージの設計に際して構造上考慮すべき幾つかの点がある。

【0004】

その一つとして、IC(半導体チップ)のパッケージ上への実装は、ワイヤを用いたボンディングにより行う。その際、チップの電極パッドと基板上のパッド(配線の一部に画定される部分)とを繋ぐワイヤの長さ(ワイヤ長)が長くなると、寄生インダクタンスが増大して信号品質の劣化をひき起こすため、そのワイヤ長は出来るだけ短くなるようにチップを配置する必要がある。このため、パッケージに凹部(キャビティ)を形成し、このキャビティ内にチップを搭載している。

【0005】

その際、チップは、キャビティの底面に塗布された接着剤(導電性ペースト等)を介してチップの裏面(電極パッドが形成されている側と反対側の面)が接着されるよう搭載される。また、ワイヤ長を極力短くするために、キャビティの深さは、チップの厚さとほぼ同じ程度となるように形成される。

【0006】

また、ミリ波帯の回路を備えたIC(チップ)は、その高周波動作によりチップ温度が高温となるため、チップの熱暴走や破壊等を防止するために、チップの動作時に放出された熱をパッケージ外部に放熱させるための手段を講じる必要がある。その典型的な手段として、サーマルビア(放熱用のビアホール)がある。このサーマルビアは、パッケージに設けられたキャビティの底面(接着剤を介してチップに熱結合されている)と基板外部とを繋ぐように基板の厚み方向に貫通して形成されている。

【0007】

かかる従来技術に関連する技術の一例は、下記の特許文献1に記載されている。この文献には、多段増幅器の最終段トランジスタの出力端子側の寄生インダクタンスのばらつきを低減するようにした半導体装置が開示されている。これを実現するため、配線基板に設けた四角形の窪み(キャビティ)の内側壁に当該トランジスタが形成された半導体チップの一辺を当接させてチップをキャビティ底に固定し、このキャビティ底にチップと同じ大きさのメタライズ層を形成した後、このメタライズ層上に所定量の溶融接合材を供給し、この溶融接合材をリフローして溶けた当該接合材の表面張力と自己整合作用によってチップの一辺をキャビティの内側壁の一辺に接触させている(図5)。

【0008】

また、これに関連する技術として、下記の特許文献2に記載されるように、半導体チップを接着剤にて設置する凹部(キャビティ)と外部端子を有するパッケージを備え、この外部端子にワイヤを介して半導体チップが電気的に接続された構造を有する半導体装置において、キャビティ表面の、キャビティと半導体チップの接する面に溝を形成するようにしたものがある。半導体チップとパッケージ基板を接着する際に、この溝に接着剤が入り込むことで、半導体チップの電極部分への接着剤の這い上がりを防止している。

【0009】

また、パッケージの放熱に関連する技術としては、下記の特許文献3に記載されるように、絶縁基板の内部にその厚み方向に貫くサーマルビアホールを複数配置した回路基板において、そのサーマルビアホールを形成するために、平均粒径が5μm以上であるAg粉末と平均粒径が1μm以下であるAg粉末を含有したペーストを使用したものがある。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】WO2003/023843号公報

【特許文献2】特開平9−283544号公報

【特許文献3】特開2002−198660号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上述したように半導体素子(チップ)とともにミリ波帯等の高周波伝送線路を備えたパッケージ(配線基板)の場合、所要の特性を確保する必要性から、基板上にキャビティを設け、このキャビティ内にチップを搭載するとともに、このチップと基板上に形成された配線部分との電気的な接続をワイヤボンディングにより行っている。つまり、ワイヤ長が極力短くなるようにチップを配置することで、寄生インダクタンスが増大するのを防ぐようにしている。

【0012】

このような設計上の配慮は、ミリ波帯(周波数:30GHz〜300GHz)よりも波長の長い高周波(20GHzや2GHz等)の信号伝送に対してはそれなりの効果が期待されるが、ミリ波帯の信号伝送に対してはあまり効果がないというのが現状である。つまり、ミリ波帯の信号伝送は、配線経路の特性インピーダンスの違いによる反射や、従来では無視できたような配線によって生じる微小な寄生インダクタンスも信号品質の劣化の要因となってくるからである。従って、高周波伝送線路の中でも特にミリ波帯用の伝送線路に介在されるワイヤの長さは、可能な限り短くするような工夫が必要である。

【0013】

また、現状の技術では、ミリ波の中でも60GHz以上の周波数を使用した製品は未だ開発されておらず、基板構成や実装方法など、様々な点を考慮した設計が必要となっている。

【0014】

なお、上記の特許文献1に記載された発明では、キャビティ内でチップの一辺をキャビティの内側壁の一辺に当接させることで、寄生インダクタンスのばらつきを低減するようにした技術が開示されている。この構成によれば、キャビティ内でチップと内側壁とを密着させているので、この部分近傍にはチップから放出された熱が溜まりやすく、他の部分と比べて放熱性が低下するものと推測される。しかし、この特許文献1では、その放熱を行うための手段や方法については一切言及されていない。

【0015】

本発明は、かかる従来技術における課題に鑑み創作されたもので、ミリ波帯等の高周波伝送線路に介在されるワイヤボンディング長を短くし、その部分の寄生インダクタンスの影響による信号品質の劣化を抑制するとともに、放熱性を高めた半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0016】

上記の従来技術の課題を解決するため、本発明の一形態によれば、半導体素子が配線基板に形成されたキャビティ内にその底面との間に接着材料を介在させて搭載されるとともに、前記半導体素子の電極端子が前記キャビティの周囲の基板上に形成された配線部分にワイヤを介して接続された構造を有する半導体装置において、前記半導体素子が、前記配線部分のうち他の配線に比べて高周波用の配線が形成されている領域に近い側の前記キャビティの側壁に密着して搭載され、前記半導体素子を密着させた側の前記キャビティの底面に、該底面から基板外部に繋がる放熱構造が形成されていることを特徴とする半導体装置が提供される。

【発明の効果】

【0017】

本発明の一形態に係る半導体装置の構成によれば、配線部分のうち他の配線に比べて高周波用の配線(例えば、ミリ波帯用の配線)が形成されている領域に近い側のキャビティの側壁に、半導体素子を密着させて搭載しているので、半導体素子と当該高周波用の配線とを接続するボンディングワイヤの長さを最小限に短くすることができる。これにより、そのワイヤ部分で発生する寄生インダクタンスを最小限とし、その寄生インダクタンスの影響による信号品質の劣化を抑制することが可能となる。

【0018】

また、キャビティ内で、高周波用の配線(ミリ波帯等)が形成されている領域に近い側の側壁に半導体素子を密着させているので、この密着させた側のキャビティ底面の近傍部分には熱が溜まりやすく、キャビティ内の他の部分と比べて放熱性が低下することが懸念される。これに対し、本発明では、半導体素子を密着させた側のキャビティの底面に、基板外部に繋がる放熱構造が設けられているので、放熱性を高めることができる。

【図面の簡単な説明】

【0019】

【図1】本発明の第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】図1の半導体装置をチップが実装される側の面から見たときの概略平面図である。

【図3】第1の実施形態の変形例に係る半導体装置(要部)の構成を示す断面図である。

【図4】本発明の第2の実施形態に係る半導体装置の構成を示す断面図である。

【発明を実施するための形態】

【0020】

以下、本発明の好適な実施の形態について、添付の図面を参照しながら説明する。

【0021】

(第1の実施形態…図1、図2参照)

図1は本発明の第1の実施形態に係る半導体装置の構成を断面図の形態で示したものであり、図2はこの半導体装置をチップが実装される側の面から平面的に見たときの概略構成を示している。

【0022】

本実施形態に係る半導体装置10は、例えば、画像伝送などのデータ容量の大きい通信を行うのに適応されたPDA等の携帯端末機器に組み込まれて使用される。この半導体装置10は、配線基板(パッケージ)20と、この配線基板20の一方の面側に実装された半導体素子(チップ)30とを備えている。さらに、図1には特に示していないが、チップ30及びこれに繋がる導体部分(ボンディングワイヤ32、配線22a等)を封止するためのキャップが適宜設けられている。

【0023】

配線基板(パッケージ)20は、基板本体を構成する樹脂基板21を有している。この樹脂基板21の形態としては、少なくとも両面に最外層の配線層22(22a,22b,22c,22d)及び23が形成された基板であって、各配線層22,23が基板内部を通して電気的に接続されている形態のものであれば十分である。

【0024】

樹脂基板21の内部には、図示のように配線層25が形成されていてもよいし、形成されていなくてもよい。本発明を特徴付ける部分ではないので詳細な図示は省略するが、樹脂基板21の内部に配線層が形成されている形態の場合、基板内部で樹脂層(絶縁層)を介在させて形成された各配線層(図1の例では、図示の簡略化のため1層の配線層25のみを示している)及び各配線層間を相互に接続するビアホール(に充填された導体:ビア26)を介して最外層の各配線層22,23が電気的に接続されている。この形態の基板は、例えば、ビルドアップ法を用いて形成することができる。一方、樹脂基板の内部に配線層が形成されていない形態の場合には、この樹脂基板の所要の箇所に適宜形成されたスルーホール(に充填された導体)を介して最外層の各配線層が相互に接続されている。

【0025】

配線層22,23,25及びビア26の材料としては、代表的に銅(Cu)が用いられる。また、樹脂層(絶縁層)の材料としては、熱硬化性のエポキシ系樹脂やポリイミド系樹脂等が好適に用いられる。

【0026】

さらに、パッケージ20の一方の面(チップ30が実装される側の面)には、最外層の配線層22の所要の箇所に画定されたパッドP1,P2の部分を露出させて表面を覆うように保護膜としてのソルダレジスト層(図示せず)が形成されている。ただし、後述するように配線層22(a,b,c,d)のうち、配線層22a,22bについては、パッドP1,P2と共に配線部分についても露出しており、配線層22c,22dについては、パッドP1のみが露出している。

【0027】

パッケージ20の他方の面にも、最外層の配線層23の所要の箇所に画定されたパッドP3の部分を露出させて表面を覆うように保護膜としてのソルダレジスト層24が形成されている。このソルダレジスト層24から露出するパッドP3には、本装置10をマザーボード等に実装する際に使用される外部接続端子(図示の例では、はんだボールSB)が接合されるので、そのコンタクト性を良くするために適当な表面処理を施している。典型的には、パッドP3(Cu)上にニッケル(Ni)めっき及び金(Au)めっきをこの順に施している。この場合、Niめっき層はバリヤメタル膜として機能する。

【0028】

なお、図1の例ではパッドP3にはんだボールSB(外部接続端子)を設けているが、これは必ずしも設ける必要はない。要は、必要なときに外部接続端子(はんだボールや金属ピン等)を接合できるように当該パッドP3が露出していれば十分である。

【0029】

配線基板(パッケージ)20は、図2に示すように平面視したときの形状が正方形であり、その大きさは15mm×15mm程度、厚さは1mm程度に選定されている。このパッケージ20には、一方の面のほぼ中央部に、半導体素子(チップ)30を搭載すると共に基板内に収容するためのキャビティ27が形成されている。

【0030】

このキャビティ27は、図2に示すように矩形(長方形)の形状に形成され、その4箇所の隅部は丸められている。キャビティ27の大きさは、長辺方向の長さが6mm程度、短辺方向の長さが4mm程度に選定され、その深さは300μm程度に選定されている。なお、図示の例ではキャビティ27の形状を矩形(長方形)としているが、必ずしもこれに限定されず、正方形や他の形状であってもよいことはもちろんである。

【0031】

このキャビティ27内に搭載されるチップ30は、例えば、シリコンウエハに所要のデバイスプロセスを施して作り込まれた複数のデバイスを各デバイス単位にダイシングして得られたシリコンチップ(「ダイ」ともいう。)である。このチップ30は、その電極パッド(端子)31が形成されている側の面を上にしたフェイスアップの態様で、キャビティ27内にその底面27eとの間に接着剤33を介在させて搭載されている。例えば、導電性ペースト(エポキシ系樹脂等の熱硬化性樹脂にAgやCu等の金属微粒子を分散させてペースト状にしたもの)をキャビティ27の底面に塗布し、この導電性ペースト(接着剤33)上にチップ30を載せ、接着剤33を加熱し硬化させて、チップ30をパッケージ20(キャビティ27内)に接着し固定する(ダイ・アタッチ)。

【0032】

配線基板(パッケージ)20上でキャビティ27の周囲は、配線形成領域WR(図2)である。この配線形成領域WRのうち、キャビティ27の長辺方向に沿った周縁部(各側壁27a,27b)の外側の領域(図2の例では左右方向の2箇所の領域)には、ミリ波帯等の高周波用の伝送線路(配線22a,22b)が設けられている。本実施形態では、右側の配線形成領域には60GHz(ミリ波帯)用の配線22aが形成されており、これと対向する左側の配線形成領域には、ミリ波帯よりも波長の長い高周波(20GHzや2GHz等)用の配線22bが形成されている。

【0033】

一方、キャビティ27の短辺方向に沿った周縁部(各側壁27c,27d)の外側の領域(図2の例では上下方向の2箇所の領域)には、チップ30に対する入出力(I/O)信号伝送用の配線、電源用及びグランド用の各配線22c,22dが形成されている。

【0034】

配線形成領域WRにおいて左右方向の2箇所の領域に高周波用の配線22a,22bを形成している理由は、当該配線のボンディング用パッドP1とチップ30側の対応する電極パッド31との距離(高周波伝送線路の一部をなすワイヤ32の長さ)を短くできるからである。つまり、ワイヤ長を短くすることで、そのワイヤ部分で発生する寄生インダクタンスを小さくし、当該配線上を伝送されるミリ波帯等の高周波信号の品質劣化を抑制できるからである。

【0035】

さらに本実施形態では、キャビティ27内にチップ30を搭載する際に、図示のようにキャビティ27内の、ミリ波帯用の配線22aが形成されている側の側壁27aに、チップ30の対応する側面が接触するように密着させている。これにより、ミリ波帯用の配線22aのパッドP1とチップ30側の対応する電極パッド31とを接続するワイヤ32の長さを更に短くすることができ、ミリ波帯信号の品質劣化の更なる抑制を図ることができる。

【0036】

この場合、キャビティ27内でチップ30を密着させた側と反対側に位置する高周波用の配線22bについては、そのボンディング用パッドP1とチップ30側の対応する電極パッド31とを接続するワイヤ32の長さは相対的に長くなる。しかしながら、そのワイヤ長は、他の配線22c,22dの各パッドP1とチップ30側の対応する各電極パッド31とを接続するワイヤ長に比べると十分に短いため、寄生インダクタンスの低減及びそれに基づく高周波信号の品質劣化の抑制には十分である。

【0037】

パッケージ20の表面に形成されたミリ波帯用の配線22aには、その層間接続用パッドP2を介して、樹脂基板21内に形成されたアンテナANT(図1参照)が接続されている。本実施形態では、図示のように基板内部の配線層25の一部分とこれに繋がるビア26によりアンテナANTが構成されている。アンテナANTの形態が図示の例に限定されないことはもちろんである。

【0038】

I/O信号伝送用、電源用、グランド用の各配線22c,22dは、それぞれボンディング用パッドP1の部分のみを露出させて、ソルダレジスト層で被覆されている。このソルダレジスト層については、図2の例では図示を省略している。

【0039】

一方、ミリ波帯等の高周波用の各配線22a,22bについては、所要の特性を確保するため、それぞれボンディング用パッドP1及び層間接続用パッドP2の部分と共に配線部分についても、当該ソルダレジスト層で被覆せずに、パッケージ20の面上に露出させている(図1参照)。このため、この露出部分を外部から保護する(つまり、ミリ波等の高周波伝送特性に及ぼされる影響を除去する)ために、中空構造の凹状のキャップ(図示せず)で封止する必要がある。

【0040】

このようなキャップは、耐熱性を有したエポキシ系樹脂等の熱硬化性樹脂(接着剤)によりパッケージ20上に接着される。その場合の接着剤が有する耐熱性は、最終的にパッケージ20の実装面側に外部接続端子(図示の例では、はんだボールSB)を接合する際のリフロー温度(例えば、240〜260℃前後)に耐え得るものである。

【0041】

パッケージ20に設けられるキャビティ27は、例えば、ビルドアップ法等により形成した多層配線樹脂基板(所要のパッケージ20)に対し、ルータ加工等の切削加工により形成することができる。さらに、このキャビティ27の底面27eの一部に、本発明を特徴付ける溝28(凹部)が形成されている。この溝28は、キャビティ27と同様に、ルータ加工等により形成することができる。

【0042】

この溝28は、図示のようにキャビティ27の底面27eのエッジ部分に設けられており、より具体的には、キャビティ27の底面27eとキャビティ27内でチップ30の側面が接触(密着)している側壁27aとが交差するエッジ部分に沿って直線状に形成されている。ただし、この溝28は必ずしも連続している必要はなく、チップ30の搭載時に溶融する接着剤33(導電性ペースト等)の流出量に合わせて適宜断続的に形成されていてもよい。

【0043】

この溝28(凹部)は、キャビティ27内でミリ波帯用の配線22aが形成されている側の側壁27aにチップ30の対応する側面を接触させた状態で搭載したときに、溶融した接着剤33の一部(搭載部分からはみ出した接着剤33の余分な部分)を溜めておくための「接着剤溜め部分」として機能する。特に、接着剤33を溝28に積極的に溜めておくようにする(充填する)のが望ましい。この「接着剤溜め部分」としての機能により、溝28は2つの役割を果たしている。

【0044】

第1の役割は、溝28に充填された接着剤33(硬化された導電性ペースト等)を介して、後述するサーマルビア29の一部(溝28の直下の領域に形成されるサーマルビア)にチップ30の裏面(フェイス面と反対側の面)を熱的に結合させることである。特に、図示のように接着剤33が溝28に充填された状態にあると、溝28内に溜められてはいるが充填されていない状態(つまり、空気が介在している状態)に比べて、チップ30から放出された熱の当該サーマルビア29の一部への伝達効果(熱伝導性)を高めることができる。

【0045】

第2の役割は、キャビティ27内へのチップ30の搭載時に溶融した接着剤33(硬化する前の導電性ペースト等)が、チップ30を密着させたキャビティ27の側壁27aに沿って這い上がるのを防ぐことである。接着剤33(導電性ペースト等)がキャビティ27の上端まで這い上がった場合、その上端近傍に位置するミリ波帯用の配線22a(パッドP1)に付着してショートするおそれがあるからである。また、接着剤33が導電性ペーストではなく、アクリル系樹脂やエポキシ系樹脂等の熱硬化性の絶縁樹脂からなる場合であっても、かかる絶縁樹脂は相応の誘電率を有しているため、ミリ波帯用の配線22aに付着するとその高周波伝送特性に影響を及ぼすからである。

【0046】

さらに、配線基板20(樹脂基板21)においてキャビティ27の底面27e(溝28を含む)の直下の領域には、基板の厚み方向に貫通する所要の数のサーマルビア29(少なくとも内壁部分にCuめっき等が施された放熱用のビアホール)が一定の配設間隔で形成されている。これらサーマルビア29のうち、一部のサーマルビア29は溝28の底面に露出し、残りのサーマルビア29はキャビティ27の底面27e(溝28が形成されている領域を除く)に露出している。各サーマルビア29は、それぞれキャビティ27の底面27e及び溝28の底面上を被覆する接着剤33(硬化された導電性ペースト等)を介してチップ30の裏面(フェイス面と反対側の面)に熱的に結合されている。

【0047】

これによって、チップ30の動作時に放出された熱は、接着剤33を介して各サーマルビア29に確実に伝達され、さらに、各サーマルビア29に熱的に結合された外部接続端子(はんだボールSB)を介してパッケージ外部に放熱される。この場合の各サーマルビア29への熱伝達経路は2つあり、一方は、溝28に充填された接着剤33を介して当該サーマルビア29の一部に伝達される経路(第1の放熱構造)であり、他方は、チップ30の裏面とキャビティ27の底面27e(溝28が形成されている領域を除く)との間に介在する接着剤33を介して他のサーマルビア29に伝達される経路(第2の放熱構造)である。

【0048】

特に、キャビティ27内でチップ30の側面とキャビティ27の側壁27aとを密着させているので、何の手段も講じなければこのキャビティ27のエッジ部分(側壁27aと底面27eが交差するエッジ部分)近傍に熱が溜まりやすく、他の部分と比べて放熱性が悪くなる。本実施形態では、このエッジ部分近傍に溝28(凹部)を設けているので、キャビティ27のエッジ部分近傍に溜まった熱を、第1の放熱構造(溝28に充填された接着剤33及びこれに熱結合されたサーマルビア29)を介してパッケージ20の外部に有効に逃がすことができる(放熱性の向上)。

【0049】

以上説明したように、第1の実施形態に係る半導体装置10の構成によれば、パッケージ20に設けたキャビティ27内で、ミリ波帯用の配線22aが形成されている側の側壁27aにチップ30の側面を密着させてチップ搭載を行うとともに、チップ30を密着させた側のキャビティ底面27eに溝28(凹部)を設け、さらに、溝28の底面とキャビティ27の底面27e(溝28が形成されている領域を除く)にそれぞれ露出するサーマルビア29(上述した第1、第2の放熱構造)を形成している。

【0050】

先ず、キャビティ27内にチップ30を搭載する際に、ミリ波帯用の配線22aが形成されている側の側壁27aにチップ30を密着させているので、チップ30の電極パッド31と配線22aのパッドP1とを接続するボンディングワイヤ32の長さを短く(最小限に)することができる。これにより、そのワイヤ部分で発生する寄生インダクタンスを最小限とし、その寄生インダクタンスの影響によるミリ波帯信号の品質劣化を抑制することができる。

【0051】

また、チップ30を、キャビティ27内で側壁27aに接触させた状態で底面27eとの間に接着剤33(導電性ペースト等)を介在させて搭載したときに、溶融した接着剤33の一部(搭載部分からはみ出した接着剤33の余分な部分)は、溝28内に溜められて充填される。これにより、チップ30の裏面とキャビティ底面27eの間に介在する接着剤33及び溝28に充填された接着剤33を介してチップ30の裏面をそれぞれ対応するサーマルビア29に確実に熱結合させることができる。

【0052】

特に、キャビティ27内でチップ30を密着させた側のキャビティ底面27eの近傍部分には熱が溜まりやすいため、この部分に設けた溝28(充填された接着剤33)を放熱手段(第1の放熱構造)として積極的に利用しているので、放熱性の点で大いに有効である。

【0053】

また、キャビティ27内でチップ30を側壁27aに密着させたことにより、チップ搭載時に溶融した接着剤33の一部が側壁27aに沿って這い上がる可能性があるが、上述したように搭載部分からはみ出した接着剤33の余分な部分は溝28内に溜められているので、接着剤33の「這い上がり」を防止することができる。これにより、接着剤33がキャビティ27の上端まで這い上がった場合に起こり得る不都合(ミリ波帯用の配線22aに付着してショートしたり、あるいは特性上の影響を及ぼすこと)を解消することができる。

【0054】

上述した第1の実施形態の構成(図1)では、キャビティ27内でチップ30の側面が密着している側壁27aとキャビティ27の底面27eとが交差するエッジ部分に沿ってキャビティ27の直下の領域にのみ凹部(溝28)を形成した場合を例にとって説明したが、当該凹部の形状や配置形態がこれに限定されないことはもちろんである。要は、キャビティ27内へのチップ30の搭載時にその搭載部分から流出する接着剤33(導電性ペースト等)を溜めておくことで、その溜めた部分(接着剤33)を介してチップ30がパッケージ外部と熱的に結合されるような形状(第1の放熱構造)に形成されていれば十分である。図3はその場合の変形例を示したものである。

【0055】

図3は、図1に示す実施形態の変形例に係る半導体装置の要部(チップ30が搭載されているキャビティ27及びその周辺部分)の構成を断面図の形態で示したものであり、本来の放熱経路であるサーマルビア29とは異なる放熱経路を新たに設けた場合の実施形態を示している。

【0056】

図3(a)は一変形例に係る半導体装置10aの構成(要部)を示している。この半導体装置10aの構成では、キャビティ27内でチップ30の側面を密着させた側壁27aに、溝28と一体的に繋がる凹部28aを形成し、この凹部28aに接着剤33(導電性ペースト等)を溜めて放熱手段(第1の放熱構造)として利用することにより、放熱経路(面積)を増やしている。つまり、凹部28aは、溝28と同様に「接着剤溜め部分」として機能する。

【0057】

凹部28aは、ルータ加工等により、溝28と一体的に形成することができる。その形成の際、凹部28aの上端が基板21の上端面よりも下側に止まるようにするのが望ましい。このように凹部28aの上端を基板21内に止めておくことにより、キャビティ27内へのチップ30の搭載時に溶融した接着剤33が側壁27aに沿ってキャビティ27の上端まで這い上がる(この場合、ミリ波帯用の配線22a(パッドP1)に付着するおそれがある)のを確実に防止できるからである。

【0058】

この半導体装置10aの構成によれば、チップ30の動作時に放出された熱は、図中矢印で示すように、本来の放熱経路(チップ30の裏面とキャビティ27の底面27e及び溝28の底面との間に介在する接着剤33を介してサーマルビア29に伝達され、最終的にパッケージ外部に放熱される経路)とは別に、チップ30の側面上の凹部28aに溜められた接着剤33を介して基板21中にも放熱させることができる。これにより、第1の実施形態に係る半導体装置10と比べて、放熱効果を更に高めることができる。

【0059】

特に、キャビティ27内でチップ30とキャビティ27の側壁27aとを密着させているため、このキャビティ27のエッジ部分近傍に熱が溜まりやすく、キャビティ27内の他の部分と比べて放熱性は低下する。本実施形態では、当該エッジ部分近傍に設けた追加の凹部28aを放熱手段(第1の放熱構造)として利用しているので、放熱性の点で大いに有効である。

【0060】

図3(b)は他の変形例に係る半導体装置10bの構成(要部)を示している。この半導体装置10bの構成では、図3(a)の半導体装置10aと同様に、キャビティ27内でチップ30の側面を密着させた側壁27aに、溝28と一体的に繋がるテーパ状の凹部28bを形成し、このテーパ状の凹部28bに溜めた接着剤33(導電性ペースト等)を放熱手段(第1の放熱構造)として利用している。

【0061】

テーパ状の凹部28bは、図示のようにキャビティ27の下側から上側に向かって凹部28bの深さが徐々に浅くなるように形成されている。この凹部28bについても、上記の凹部28aと同様に、ルータ加工等により形成することができ、その際、凹部28bの上端が基板21の上端面よりも下側に止まるようにするのが望ましい。

【0062】

この半導体装置10bの構成によれば、図3(a)の半導体装置10aと同様に、チップ30の動作時に放出された熱は、本来の放熱経路(サーマルビア29を介してパッケージ外部に放熱される経路)とは別に、チップ30の側面上の凹部28bに溜められた接着剤33を介して基板21中にも放熱させることができ、放熱性の更なる向上に寄与することができる。

【0063】

(第2の実施形態…図4参照)

図4は本発明の第2の実施形態に係る半導体装置の構成を断面図の形態で示したものである。

【0064】

この第2の実施形態に係る半導体装置40(図4)は、上述した第1の実施形態に係る半導体装置10(図1)の構成と比べて、キャビティ27の底面27eに溝28(図1)を設けていない点、配線基板(パッケージ)50に設けたキャビティ27の直下の領域に形成されるサーマルビア29を、第1の実施形態のように一定の配設間隔で形成するのではなく、キャビティ27内でチップ30を密着させた側(ミリ波帯用の配線22aが形成されている領域に近い側)のキャビティ底面27eの近傍部分に「密に」形成した点で相違している。つまり、この部分に形成するサーマルビア29の単位面積あたりの数を、他の部分に形成するサーマルビア29の単位面積あたりの数よりも多くしている。ここに、キャビティ27の底面27eに「密に」形成されているサーマルビア29は「第1の放熱構造」を構成し、それ以外の部分に形成されるサーマルビア29は「第2の放熱構造」を構成する。他の構成については、第1の実施形態の場合と同じであるのでその説明は省略する。

【0065】

上述した第1の実施形態では、キャビティ27内でチップ30を密着させた側のキャビティ底面27eに設けた溝28(に充填された接着剤33)と、この溝28の底面から基板外部に繋がるサーマルビア29とにより第1の放熱構造を構成しているが、この第2の実施形態に係る半導体装置40の構成では、キャビティ27内でチップ30を密着させた側のキャビティ底面27eにサーマルビア29を「密に」形成することにより、所要の第1の放熱構造を構成している。

【0066】

従って、この第2の実施形態に係る半導体装置40の構成においても、上述した第1の実施形態の場合と同様に、キャビティ27内で熱が溜まりやすい部分(チップ30を密着させた側のキャビティ底面27eの近傍部分)に設けられた第1の放熱構造(密に配置されたサーマルビア29)により、放熱性を有効に高めることができる。

【0067】

この第2の実施形態の構成(図4)では、キャビティ27内でチップ30を密着させた側(ミリ波帯用の配線22aが形成されている領域に近い側)のキャビティ底面27eに直接熱結合される形でサーマルビア29を「密に」形成しているが(第1の放熱構造)、形成されるべきサーマルビア29(第1の放熱構造)は、必ずしもキャビティ27の底面27eに直接熱結合されている必要はない。例えば、第1の実施形態(図1)のような凹部(溝28)を介在させてもよい。

【0068】

すなわち、キャビティ27内でチップ30を密着させた側(ミリ波帯用の配線22aが形成されている領域に近い側)のキャビティ底面27eに溝28を形成し、この溝28の底面にサーマルビア29を「密に」形成してもよい。この場合、溝28に充填された接着剤33と、この溝28の底面から基板外部に繋がる「密に」配置されたサーマルビア29とにより、第1の放熱構造が構成される。この構成によれば、上述した第1の実施形態の場合と比べて、溝28の底面に熱結合された放熱経路としてのサーマルビア29の数が相対的に多いので、放熱性の更なる向上を図ることができる。

【0069】

また、この第2の実施形態の構成(図4)は、上述した第1の実施形態の変形例に係る半導体装置10a,10bの構成にも同様に適用することができる。この場合、凹部28a,28bが一体的に形成された溝28において、当該溝の底面が広がることでサーマルビア29(第1の放熱構造の一部)を「密に」形成することができ、放熱性を更に高めることができる。

【0070】

上述した各実施形態では、サーマルビア29はキャビティ27内で半導体素子(チップ30)の直下の領域にのみ形成されている場合を例にとって説明したが、サーマルビア29の形成領域がこれに限定されないことはもちろんである。チップ30の直下の領域に限らず、例えば、キャビティ27内でチップ30の搭載領域から露出されるように形成されている溝28の全面に亘って形成するようにしてもよい。この場合、キャビティ27内で熱的に結合されていないチップ30の直下以外の領域におけるサーマルビアに対しても、このサーマルビア上に形成された接着剤(溝28に充填された接着剤33)を介して放熱を行うことができ、放熱性の更なる向上に寄与する。

【0071】

また、上述した各実施形態では、キャビティ27内にチップ30を搭載する際に所定の1辺の側壁(ミリ波帯用の配線22aが形成されている側の側壁27a)にのみチップ30を密着させる場合を例にとって説明したが、本発明の要旨からも明らかなように、必ずしもその1辺にのみ密着させる必要はない。例えば、キャビティ27内の最大2辺(隣り合っている2辺)の側壁にチップ30の対応する2辺を接触(密着)させるようにしてもよい。この場合、形成される溝28や凹部28a,28b、サーマルビア29の配置形態については、上述した第1、第2の実施形態と同様の構成を適用することができる。この実施形態(キャビティ27内の最大2辺の側壁にチップ30を密着させる構成)では、信号用配線22c,22dや第2の高周波用配線22bが、チップ30とキャビティ側壁とが接する辺と隣り合う辺にも形成されている場合に、上記と同様の効果が得られる、

また、上述した各実施形態では、配線基板(パッケージ)の形態として樹脂基板を使用した場合を例にとって説明したが、本発明の要旨からも明らかなように、樹脂基板に限定されないことはもちろんであり、例えば、セラミック基板を使用した場合にも同様に適用することが可能である。

【符号の説明】

【0072】

10,10a,10b,40…半導体装置、

20,50…配線基板(パッケージ)、

22a,22b,22c,22d,23…配線(層)、

24…ソルダレジスト層(保護膜)、

27(27a〜27d,27e)…キャビティ(キャビティの側壁、底面)、

28…溝(接着剤溜め部分/凹部)、

28a,28b…凹部(接着剤溜め部分)、

29…サーマルビア(放熱用ビアホール)、

30…半導体素子(チップ)、

31…電極パッド(端子)、

32…ボンディングワイヤ、

33…チップ搭載用の接着剤(接着材料)、

ANT…アンテナ、

P1,P2,P3…パッド(ボンディング用、層間接続用、外部接続用)、

SB…はんだボール(外部接続端子)、

WR…配線形成領域。

【特許請求の範囲】

【請求項1】

半導体素子が配線基板に形成されたキャビティ内にその底面との間に接着材料を介在させて搭載されるとともに、前記半導体素子の電極端子が前記キャビティの周囲の基板上に形成された配線部分にワイヤを介して接続された構造を有する半導体装置において、

前記半導体素子が、前記配線部分のうち他の配線に比べて高周波用の配線が形成されている領域に近い側の前記キャビティの側壁に密着して搭載され、

前記半導体素子を密着させた側の前記キャビティの底面に、該底面から基板外部に繋がる放熱構造が形成されていることを特徴とする半導体装置。

【請求項2】

前記放熱構造を第1の放熱構造とするとともに、前記キャビティの底面の、前記第1の放熱構造が形成されている部分以外の部分に、第2の放熱構造が形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1の放熱構造は、前記半導体素子を密着させた側の前記キャビティの底面に設けられた凹部と、該凹部の底面から基板外部に繋がるサーマルビアを有していることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記接着材料が前記凹部に充填された状態にあることを特徴とする請求項3に記載の半導体装置。

【請求項5】

さらに、前記半導体素子を密着させた前記キャビティの側壁に、前記凹部と一体的に繋がる別の凹部が設けられていることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記第1の放熱構造は、前記半導体素子を密着させた側の前記キャビティの底面から基板外部に繋がり、かつ、前記第2の放熱構造に比べて密に形成されたサーマルビアを有していることを特徴とする請求項2に記載の半導体装置。

【請求項7】

前記第1の放熱構造は、前記凹部の底面から基板外部に繋がり、かつ、前記第2の放熱構造に比べて密に形成されたサーマルビアを有していることを特徴とする請求項3に記載の半導体装置。

【請求項8】

前記高周波用の配線は、ミリ波帯用の配線であることを特徴とする請求項1から7のいずれか一項に記載の半導体装置。

【請求項9】

前記配線基板は、前記高周波用の配線に電気的に接続されたアンテナを有していることを特徴とする請求項1から8のいずれか一項に記載の半導体装置。

【請求項1】

半導体素子が配線基板に形成されたキャビティ内にその底面との間に接着材料を介在させて搭載されるとともに、前記半導体素子の電極端子が前記キャビティの周囲の基板上に形成された配線部分にワイヤを介して接続された構造を有する半導体装置において、

前記半導体素子が、前記配線部分のうち他の配線に比べて高周波用の配線が形成されている領域に近い側の前記キャビティの側壁に密着して搭載され、

前記半導体素子を密着させた側の前記キャビティの底面に、該底面から基板外部に繋がる放熱構造が形成されていることを特徴とする半導体装置。

【請求項2】

前記放熱構造を第1の放熱構造とするとともに、前記キャビティの底面の、前記第1の放熱構造が形成されている部分以外の部分に、第2の放熱構造が形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1の放熱構造は、前記半導体素子を密着させた側の前記キャビティの底面に設けられた凹部と、該凹部の底面から基板外部に繋がるサーマルビアを有していることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記接着材料が前記凹部に充填された状態にあることを特徴とする請求項3に記載の半導体装置。

【請求項5】

さらに、前記半導体素子を密着させた前記キャビティの側壁に、前記凹部と一体的に繋がる別の凹部が設けられていることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記第1の放熱構造は、前記半導体素子を密着させた側の前記キャビティの底面から基板外部に繋がり、かつ、前記第2の放熱構造に比べて密に形成されたサーマルビアを有していることを特徴とする請求項2に記載の半導体装置。

【請求項7】

前記第1の放熱構造は、前記凹部の底面から基板外部に繋がり、かつ、前記第2の放熱構造に比べて密に形成されたサーマルビアを有していることを特徴とする請求項3に記載の半導体装置。

【請求項8】

前記高周波用の配線は、ミリ波帯用の配線であることを特徴とする請求項1から7のいずれか一項に記載の半導体装置。

【請求項9】

前記配線基板は、前記高周波用の配線に電気的に接続されたアンテナを有していることを特徴とする請求項1から8のいずれか一項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−134956(P2011−134956A)

【公開日】平成23年7月7日(2011.7.7)

【国際特許分類】

【出願番号】特願2009−294434(P2009−294434)

【出願日】平成21年12月25日(2009.12.25)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【Fターム(参考)】

【公開日】平成23年7月7日(2011.7.7)

【国際特許分類】

【出願日】平成21年12月25日(2009.12.25)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【Fターム(参考)】

[ Back to top ]