半導体装置

【課題】従来と比較して低消費電力化を図ることが可能であると共に、外部制御装置の処理負荷の増大を回避可能な半導体装置を提供する。

【解決手段】複数の機能回路と、各機能回路による内部バスの使用を管理するバス管理回路とを備える半導体装置であって、前記バス管理回路は、各機能回路から通知されるデータ通信情報に基づいて各機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行する機能を有する。

【解決手段】複数の機能回路と、各機能回路による内部バスの使用を管理するバス管理回路とを備える半導体装置であって、前記バス管理回路は、各機能回路から通知されるデータ通信情報に基づいて各機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行する機能を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

周知のように、ASIC(Application Specific Integrated Circuit)とは、特定の用途向けに設計された複数のモジュールを備える半導体装置(半導体集積回路)である。このASICには、各モジュールによって共有される内部バスの使用権を調停したり、内部バスを介して入出力されるデータのデコード等を行うHub回路が内蔵されている。

【0003】

このHub回路は、自身に接続された全モジュールからのアクセスがなくなった場合、その旨を外部のCPUに割込み等で通知し、CPUによる制御の下、省電力モード(スリープ状態)に移行する機能を有している。なお、共有バスの未使用時における低消費電力化を図る技術としては、下記特許文献1に記載された技術が知られている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−49580号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記のように、ASIC内部のHub回路を省電力モードに移行させるためには、CPUのソフトウェア処理によるモード移行制御(例えば、Hub回路に対するクロック信号の供給停止等)が必要となる。そのため、Hub回路は、CPUのソフトウェア処理を待たなければ省電力モードに移行することができず、十分な省電力効果を得ることができなかった(つまり、低消費電力化の観点から改善の余地があった)。また、CPUは割込み処理としてモード移行制御を行うため、CPUの処理負荷の増大を招いていた。

【0006】

さらに、従来では、あるモジュールからHub回路へのアクセスがなくなった場合には、そのモジュールに関するHub回路内の処理部分だけでも停止可能な時間帯があるにも関わらず、全モジュールからのアクセスがなくなった場合にのみ省電力モードに移行するため、十分な省電力制御の効果を得ることができなかった。

【0007】

本発明は、上述した事情に鑑みてなされたものであり、従来と比較して低消費電力化を図ることが可能であると共に、外部制御装置の処理負荷の増大を回避可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するために、本発明に係る半導体装置は、複数の機能回路と、各機能回路による内部バスの使用を管理するバス管理回路とを備える半導体装置であって、前記バス管理回路は、各機能回路から通知されるデータ通信情報に基づいて各機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行することを特徴とする。

このような特徴を有する半導体装置によれば、バス管理回路(Hub回路)自身が各機能回路(モジュール)の通信状態を判断し、その判断結果に応じて省電力モードに移行するため、CPU等の外部制御装置のソフトウェア処理を待つことなく即座に省電力モードに移行することができ、従来と比較してより低消費電力化を図ることができる。また、外部制御装置は割込み処理としてモード移行制御を行う必要がなくなるため、外部制御装置の処理負荷の増大を回避することができる。

【0009】

また、本発明に係る半導体装置において、前記バス管理回路は、各機能回路に対応して1対1で通信を行う受信処理回路を備え、各受信処理回路は、自身に対応する機能回路から通知されるデータ通信情報に基づいて前記自身に対応する機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行することを特徴とする。

これにより、各機能回路のそれぞれの通信状態に応じて、それらに対応する受信処理回路を個別に省電力モードに移行させることができるため、従来のように全機能回路からのアクセスがなくなった時に省電力モードに移行する場合と比較して、より低消費電力化を図ることができる。

【発明の効果】

【0010】

本発明によれば、従来と比較して低消費電力化を図ることが可能であると共に、外部制御装置の処理負荷の増大を回避可能な半導体装置を提供することができる。

【図面の簡単な説明】

【0011】

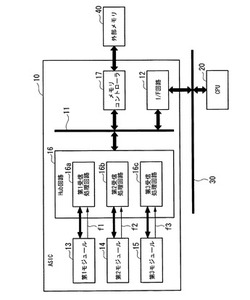

【図1】本実施形態におけるASIC(半導体装置)10の機能ブロック図である。

【発明を実施するための形態】

【0012】

以下、図面を参照しながら、本発明の一実施形態について説明する。なお、以下では、本発明に係る半導体装置として、外部制御装置であるCPUによって制御されるASICを例示して説明する。

【0013】

図1は、本実施形態におけるASIC10の機能ブロック図である。この図1に示すように、本実施形態におけるASIC10は、CPUバス30を介してCPU20と通信可能に接続された半導体装置(半導体集積回路)であり、内部バス11、I/F回路12、第1モジュール13、第2モジュール14、第3モジュール15、Hub回路16、及びメモリコントローラ17を備えている。

【0014】

内部バス11は、各モジュール13〜15によって共有される共有バスである。I/F回路12は、内部バス11とCPUバス30との間で信号の送受信を行う(言い換えれば、CPU20を含む外部装置とASIC10との双方向通信を実現する)通信インターフェイスである。各モジュール13〜15は、それぞれ異なる機能を有する機能回路であり、Hub回路16と通信可能に接続されている。

【0015】

具体的には、第1モジュール13は、Hub回路16内の第1受信処理回路16aとの双方向通信を行うと共に、第1受信処理回路16aに対してデータ通信情報f1を通知する。第2モジュール14は、Hub回路16内の第2受信処理回路16bとの双方向通信を行うと共に、第2受信処理回路16bに対してデータ通信情報f2を通知する。また、第3モジュール15は、Hub回路16内の第3受信処理回路16cとの双方向通信を行うと共に、第3受信処理回路16cに対してデータ通信情報f3を通知する。

【0016】

Hub回路16は、各モジュール13〜15による内部バス11の使用を管理するバス管理回路であり、内部バス11を介してI/F回路12及びメモリコントローラ17と通信可能に接続されている。具体的には、このHub回路16は、各モジュール13〜15から通知されるバス使用要求に応じて内部バス11の使用権を割り当てるバス調停処理や、内部バス11を介して入出力されるデータのデコード処理(行先制御)等を行う。

【0017】

また、このHub回路16は、各モジュール13〜15に対応して1対1で設けられた受信処理回路(第1受信処理回路16a、第2受信処理回路16b、第3受信処理回路16c)を備えている。第1受信処理回路16aは、第1モジュール13との双方向通信を行うと共に、第1モジュール13から通知されるデータ通信情報f1に基づいて第1モジュール13の通信状態を判断し、その判断結果に応じて自ら省電力モードに移行する。第2受信処理回路16bは、第2モジュール14との双方向通信を行うと共に、第2モジュール14から通知されるデータ通信情報f2に基づいて第2モジュール14の通信状態を判断し、その判断結果に応じて自ら省電力モードに移行する。また、第3受信処理回路16cは、第3モジュール15との双方向通信を行うと共に、第3モジュール15から通知されるデータ通信情報f3に基づいて第3モジュール15の通信状態を判断し、その判断結果に応じて自ら省電力モードに移行する。

【0018】

メモリコントローラ17は、内部バス11を介してI/F回路12及びHub回路16と接続されており、各モジュール13〜15の要求に応じて外部メモリ40に対するデータのRead/Writeを制御するメモリ制御回路である。

【0019】

続いて、上記のように構成されたASIC10におけるHub回路16の省電力モード移行動作について具体的に説明する。例えば、Hub回路16の第1受信処理回路16aに着目すると、第1受信処理回路16aは、第1モジュール13から通知されるデータ通信情報f1に基づいて第1モジュール13の通信状態を判断し、その判断結果に応じて自ら省電力モードに移行する。

【0020】

本実施形態では、第1モジュール13から第1受信処理回路16aへ通知するデータ通信情報f1として、データ転送回数(例えば、外部メモリ40に対するRead/Writeが、外部メモリ40上のアドレスとデータサイズとの関係を示すテーブルによって管理されている場合、今から行う処理に必要なテーブル数)を用いる場合を想定する。

【0021】

第1受信処理回路16aは、第1モジュール13からデータ通信情報f1としてデータ転送回数の通知を受けると、その通知情報に基づいて実際の第1モジュール13のデータ転送回数をカウントする。そして、第1受信処理回路16aは、通知されたデータ転送回数と実際のデータ転送回数とが一致した場合に、第1モジュール13の通信状態が通信終了状態に遷移したと判断して省電力モードに移行する。他の第2受信処理回路16b及び第3受信処理回路16cも同様である。なお、Hub回路16は、各受信処理回路16a〜16cの全てが省電力モードに移行した場合、全体的な動作状態を省電力モードに移行する。

【0022】

以上説明したように、本実施形態によれば、Hub回路16自身が各モジュール13〜15の通信状態を判断し、その判断結果に応じて省電力モードに移行するため、CPU20等の外部制御装置のソフトウェア処理を待つことなく即座に省電力モードに移行することができ、従来と比較してより低消費電力化を図ることができる。また、CPU20は割込み処理としてモード移行制御を行う必要がなくなるため、CPU20の処理負荷の増大を回避することができる。

【0023】

また、各モジュール13〜15のそれぞれの通信状態に応じて、それらに対応する受信処理回路16a〜16cを個別に省電力モードに移行させることができるため、従来のように全モジュール13〜15からのアクセスがなくなった時に省電力モードに移行する場合と比較して、より低消費電力化を図ることができる。

【0024】

なお、上記実施形態では、各受信処理回路16a〜16cを個別に省電力モードに移行させる場合を例示したが、これに限らず、全てのモジュール13〜15の通信状態が通信終了状態に遷移した場合に、一括的にHub回路16全体を省電力モードに移行させるようにしても良い。また、上記実施形態では、データ通信情報としてデータ転送回数を用いる場合を例示したが、これに限らず、例えばデータサイズやデータ転送時間など、各モジュール13〜15の通信状態が通信終了状態に遷移したことを判断可能な情報であればデータ通信情報として使用することができる。

【0025】

<適用例>

本発明に係る半導体装置(ASIC10)を適用可能なシステムとして、例えば、プリンタやコピー機、或いは複合機などの画像形成装置が挙げられる。具体的には、第1モジュール13に、スキャナによって読み取られた原稿の画像データを外部メモリ40に記憶させる機能を持たせ、第2モジュール14に、外部メモリ40から画像データを読み出して圧縮や拡大等の画像処理を行い、画像処理後の画像データを再度外部メモリ40に記憶させる機能を持たせ、さらに、第3モジュール15に、外部メモリ40から画像処理後の画像データを読み出して、レーザ露光器に送信する機能を持たせたシステムが考えられる。

【符号の説明】

【0026】

10…ASIC(半導体装置)、11…内部バス、12…I/F回路、13…第1モジュール(機能回路)、14…第2モジュール(機能回路)、15…第3モジュール(機能回路)、16…Hub回路(バス管理回路)、17…メモリコントローラ、20…CPU、30…CPUバス、40外部メモリ

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

周知のように、ASIC(Application Specific Integrated Circuit)とは、特定の用途向けに設計された複数のモジュールを備える半導体装置(半導体集積回路)である。このASICには、各モジュールによって共有される内部バスの使用権を調停したり、内部バスを介して入出力されるデータのデコード等を行うHub回路が内蔵されている。

【0003】

このHub回路は、自身に接続された全モジュールからのアクセスがなくなった場合、その旨を外部のCPUに割込み等で通知し、CPUによる制御の下、省電力モード(スリープ状態)に移行する機能を有している。なお、共有バスの未使用時における低消費電力化を図る技術としては、下記特許文献1に記載された技術が知られている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−49580号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記のように、ASIC内部のHub回路を省電力モードに移行させるためには、CPUのソフトウェア処理によるモード移行制御(例えば、Hub回路に対するクロック信号の供給停止等)が必要となる。そのため、Hub回路は、CPUのソフトウェア処理を待たなければ省電力モードに移行することができず、十分な省電力効果を得ることができなかった(つまり、低消費電力化の観点から改善の余地があった)。また、CPUは割込み処理としてモード移行制御を行うため、CPUの処理負荷の増大を招いていた。

【0006】

さらに、従来では、あるモジュールからHub回路へのアクセスがなくなった場合には、そのモジュールに関するHub回路内の処理部分だけでも停止可能な時間帯があるにも関わらず、全モジュールからのアクセスがなくなった場合にのみ省電力モードに移行するため、十分な省電力制御の効果を得ることができなかった。

【0007】

本発明は、上述した事情に鑑みてなされたものであり、従来と比較して低消費電力化を図ることが可能であると共に、外部制御装置の処理負荷の増大を回避可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するために、本発明に係る半導体装置は、複数の機能回路と、各機能回路による内部バスの使用を管理するバス管理回路とを備える半導体装置であって、前記バス管理回路は、各機能回路から通知されるデータ通信情報に基づいて各機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行することを特徴とする。

このような特徴を有する半導体装置によれば、バス管理回路(Hub回路)自身が各機能回路(モジュール)の通信状態を判断し、その判断結果に応じて省電力モードに移行するため、CPU等の外部制御装置のソフトウェア処理を待つことなく即座に省電力モードに移行することができ、従来と比較してより低消費電力化を図ることができる。また、外部制御装置は割込み処理としてモード移行制御を行う必要がなくなるため、外部制御装置の処理負荷の増大を回避することができる。

【0009】

また、本発明に係る半導体装置において、前記バス管理回路は、各機能回路に対応して1対1で通信を行う受信処理回路を備え、各受信処理回路は、自身に対応する機能回路から通知されるデータ通信情報に基づいて前記自身に対応する機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行することを特徴とする。

これにより、各機能回路のそれぞれの通信状態に応じて、それらに対応する受信処理回路を個別に省電力モードに移行させることができるため、従来のように全機能回路からのアクセスがなくなった時に省電力モードに移行する場合と比較して、より低消費電力化を図ることができる。

【発明の効果】

【0010】

本発明によれば、従来と比較して低消費電力化を図ることが可能であると共に、外部制御装置の処理負荷の増大を回避可能な半導体装置を提供することができる。

【図面の簡単な説明】

【0011】

【図1】本実施形態におけるASIC(半導体装置)10の機能ブロック図である。

【発明を実施するための形態】

【0012】

以下、図面を参照しながら、本発明の一実施形態について説明する。なお、以下では、本発明に係る半導体装置として、外部制御装置であるCPUによって制御されるASICを例示して説明する。

【0013】

図1は、本実施形態におけるASIC10の機能ブロック図である。この図1に示すように、本実施形態におけるASIC10は、CPUバス30を介してCPU20と通信可能に接続された半導体装置(半導体集積回路)であり、内部バス11、I/F回路12、第1モジュール13、第2モジュール14、第3モジュール15、Hub回路16、及びメモリコントローラ17を備えている。

【0014】

内部バス11は、各モジュール13〜15によって共有される共有バスである。I/F回路12は、内部バス11とCPUバス30との間で信号の送受信を行う(言い換えれば、CPU20を含む外部装置とASIC10との双方向通信を実現する)通信インターフェイスである。各モジュール13〜15は、それぞれ異なる機能を有する機能回路であり、Hub回路16と通信可能に接続されている。

【0015】

具体的には、第1モジュール13は、Hub回路16内の第1受信処理回路16aとの双方向通信を行うと共に、第1受信処理回路16aに対してデータ通信情報f1を通知する。第2モジュール14は、Hub回路16内の第2受信処理回路16bとの双方向通信を行うと共に、第2受信処理回路16bに対してデータ通信情報f2を通知する。また、第3モジュール15は、Hub回路16内の第3受信処理回路16cとの双方向通信を行うと共に、第3受信処理回路16cに対してデータ通信情報f3を通知する。

【0016】

Hub回路16は、各モジュール13〜15による内部バス11の使用を管理するバス管理回路であり、内部バス11を介してI/F回路12及びメモリコントローラ17と通信可能に接続されている。具体的には、このHub回路16は、各モジュール13〜15から通知されるバス使用要求に応じて内部バス11の使用権を割り当てるバス調停処理や、内部バス11を介して入出力されるデータのデコード処理(行先制御)等を行う。

【0017】

また、このHub回路16は、各モジュール13〜15に対応して1対1で設けられた受信処理回路(第1受信処理回路16a、第2受信処理回路16b、第3受信処理回路16c)を備えている。第1受信処理回路16aは、第1モジュール13との双方向通信を行うと共に、第1モジュール13から通知されるデータ通信情報f1に基づいて第1モジュール13の通信状態を判断し、その判断結果に応じて自ら省電力モードに移行する。第2受信処理回路16bは、第2モジュール14との双方向通信を行うと共に、第2モジュール14から通知されるデータ通信情報f2に基づいて第2モジュール14の通信状態を判断し、その判断結果に応じて自ら省電力モードに移行する。また、第3受信処理回路16cは、第3モジュール15との双方向通信を行うと共に、第3モジュール15から通知されるデータ通信情報f3に基づいて第3モジュール15の通信状態を判断し、その判断結果に応じて自ら省電力モードに移行する。

【0018】

メモリコントローラ17は、内部バス11を介してI/F回路12及びHub回路16と接続されており、各モジュール13〜15の要求に応じて外部メモリ40に対するデータのRead/Writeを制御するメモリ制御回路である。

【0019】

続いて、上記のように構成されたASIC10におけるHub回路16の省電力モード移行動作について具体的に説明する。例えば、Hub回路16の第1受信処理回路16aに着目すると、第1受信処理回路16aは、第1モジュール13から通知されるデータ通信情報f1に基づいて第1モジュール13の通信状態を判断し、その判断結果に応じて自ら省電力モードに移行する。

【0020】

本実施形態では、第1モジュール13から第1受信処理回路16aへ通知するデータ通信情報f1として、データ転送回数(例えば、外部メモリ40に対するRead/Writeが、外部メモリ40上のアドレスとデータサイズとの関係を示すテーブルによって管理されている場合、今から行う処理に必要なテーブル数)を用いる場合を想定する。

【0021】

第1受信処理回路16aは、第1モジュール13からデータ通信情報f1としてデータ転送回数の通知を受けると、その通知情報に基づいて実際の第1モジュール13のデータ転送回数をカウントする。そして、第1受信処理回路16aは、通知されたデータ転送回数と実際のデータ転送回数とが一致した場合に、第1モジュール13の通信状態が通信終了状態に遷移したと判断して省電力モードに移行する。他の第2受信処理回路16b及び第3受信処理回路16cも同様である。なお、Hub回路16は、各受信処理回路16a〜16cの全てが省電力モードに移行した場合、全体的な動作状態を省電力モードに移行する。

【0022】

以上説明したように、本実施形態によれば、Hub回路16自身が各モジュール13〜15の通信状態を判断し、その判断結果に応じて省電力モードに移行するため、CPU20等の外部制御装置のソフトウェア処理を待つことなく即座に省電力モードに移行することができ、従来と比較してより低消費電力化を図ることができる。また、CPU20は割込み処理としてモード移行制御を行う必要がなくなるため、CPU20の処理負荷の増大を回避することができる。

【0023】

また、各モジュール13〜15のそれぞれの通信状態に応じて、それらに対応する受信処理回路16a〜16cを個別に省電力モードに移行させることができるため、従来のように全モジュール13〜15からのアクセスがなくなった時に省電力モードに移行する場合と比較して、より低消費電力化を図ることができる。

【0024】

なお、上記実施形態では、各受信処理回路16a〜16cを個別に省電力モードに移行させる場合を例示したが、これに限らず、全てのモジュール13〜15の通信状態が通信終了状態に遷移した場合に、一括的にHub回路16全体を省電力モードに移行させるようにしても良い。また、上記実施形態では、データ通信情報としてデータ転送回数を用いる場合を例示したが、これに限らず、例えばデータサイズやデータ転送時間など、各モジュール13〜15の通信状態が通信終了状態に遷移したことを判断可能な情報であればデータ通信情報として使用することができる。

【0025】

<適用例>

本発明に係る半導体装置(ASIC10)を適用可能なシステムとして、例えば、プリンタやコピー機、或いは複合機などの画像形成装置が挙げられる。具体的には、第1モジュール13に、スキャナによって読み取られた原稿の画像データを外部メモリ40に記憶させる機能を持たせ、第2モジュール14に、外部メモリ40から画像データを読み出して圧縮や拡大等の画像処理を行い、画像処理後の画像データを再度外部メモリ40に記憶させる機能を持たせ、さらに、第3モジュール15に、外部メモリ40から画像処理後の画像データを読み出して、レーザ露光器に送信する機能を持たせたシステムが考えられる。

【符号の説明】

【0026】

10…ASIC(半導体装置)、11…内部バス、12…I/F回路、13…第1モジュール(機能回路)、14…第2モジュール(機能回路)、15…第3モジュール(機能回路)、16…Hub回路(バス管理回路)、17…メモリコントローラ、20…CPU、30…CPUバス、40外部メモリ

【特許請求の範囲】

【請求項1】

複数の機能回路と、各機能回路による内部バスの使用を管理するバス管理回路とを備える半導体装置であって、

前記バス管理回路は、各機能回路から通知されるデータ通信情報に基づいて各機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行することを特徴とする半導体装置。

【請求項2】

前記バス管理回路は、各機能回路に対応して1対1で通信を行う受信処理回路を備え、

各受信処理回路は、自身に対応する機能回路から通知されるデータ通信情報に基づいて

前記自身に対応する機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行することを特徴とする請求項1に記載の半導体装置。

【請求項1】

複数の機能回路と、各機能回路による内部バスの使用を管理するバス管理回路とを備える半導体装置であって、

前記バス管理回路は、各機能回路から通知されるデータ通信情報に基づいて各機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行することを特徴とする半導体装置。

【請求項2】

前記バス管理回路は、各機能回路に対応して1対1で通信を行う受信処理回路を備え、

各受信処理回路は、自身に対応する機能回路から通知されるデータ通信情報に基づいて

前記自身に対応する機能回路の通信状態を判断し、その判断結果に応じて省電力モードに移行することを特徴とする請求項1に記載の半導体装置。

【図1】

【公開番号】特開2011−180766(P2011−180766A)

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願番号】特願2010−43079(P2010−43079)

【出願日】平成22年2月26日(2010.2.26)

【出願人】(000006150)京セラミタ株式会社 (13,173)

【Fターム(参考)】

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願日】平成22年2月26日(2010.2.26)

【出願人】(000006150)京セラミタ株式会社 (13,173)

【Fターム(参考)】

[ Back to top ]