半導体装置

【課題】電流駆動型の半導体装置のゲートへの寄生インダクタンスによる外乱ノイズを低減し、ゲート駆動を高精度化及び安定化させる。

【解決手段】半導体装置100であって、電流駆動型の半導体素子3と、半導体素子3を制御するゲート駆動回路11と、接続端子部とを備え、半導体素子3は、窒化物半導体層の積層体の上に形成されたゲート電極パッド1と、オーミック電極パッド2及び5とを有し、接続端子部は、オーミック電極パッド2と接続されたオーミック電極端子6と、オーミック電極パッド5と接続されたオーミック電極端子10と、オーミック電極パッド2と接続されたゲート駆動用端子7と、ゲート電極パッド1と接続されたゲート端子8とを有し、ゲート駆動回路11の入力端子はゲート駆動用端子7に接続され、ゲート駆動回路11の出力端子はゲート端子8に接続され、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位とする。

【解決手段】半導体装置100であって、電流駆動型の半導体素子3と、半導体素子3を制御するゲート駆動回路11と、接続端子部とを備え、半導体素子3は、窒化物半導体層の積層体の上に形成されたゲート電極パッド1と、オーミック電極パッド2及び5とを有し、接続端子部は、オーミック電極パッド2と接続されたオーミック電極端子6と、オーミック電極パッド5と接続されたオーミック電極端子10と、オーミック電極パッド2と接続されたゲート駆動用端子7と、ゲート電極パッド1と接続されたゲート端子8とを有し、ゲート駆動回路11の入力端子はゲート駆動用端子7に接続され、ゲート駆動回路11の出力端子はゲート端子8に接続され、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力変換を行う半導体装置に関し、特に窒化物半導体を用いた電流駆動型の半導体装置に関する。

【背景技術】

【0002】

地球温暖化問題を背景として、電気機器のさらなる省エネルギー化が期待されており、多くの電力を扱う電源回路やインバータ回路等の電力変換装置の電力変換効率を向上することが求められている。電力変換装置の電力変換効率を決定する最も大きな要因は、電力変換の際に用いられるIGBT(Insulated Gate Bipolar Transistor)やMOSFET(Metal Oxide Semiconductor Field Effect Transistor)等のパワー半導体素子における損失である。パワー半導体素子における損失を低減すれば、電力変換装置の電力変換効率を大きく向上させることができる。パワー半導体素子において発生する損失には、素子に電流が通電することで発生する導通損失と、素子がスイッチングする際に発生するスイッチング損失がある。導通損失については、よりオン抵抗の小さい素子を用いれば低減でき、スイッチング損失については、より高速にスイッチングする素子を用いれば低減できる。そのため、パワー半導体素子の高速スイッチング化及び低オン抵抗化が進められている。

【0003】

しかし、現在のパワー半導体素子は、シリコン(Si)を材料として作られており、Siの材料限界に到達しつつあるため、さらなるオン抵抗の低減及びスイッチング速度の向上が困難になってきている。Siの材料限界を打破して導通損失及びスイッチング損失を低減するために、窒化ガリウム(GaN)に代表される窒化物系半導体又は炭化珪素(SiC)等のいわゆるワイドバンドギャップ半導体素子の利用が検討されている。ワイドバンドギャップ半導体素子は絶縁破壊電界がSiに比べて約1桁高く、特に、窒化アルミニウムガリウム(AlGaN)と窒化ガリウム(GaN)とのヘテロ接合界面には自発分極及びピエゾ分極により電荷が生じる。これにより、アンドープ時においても1×1013cm-2以上のシートキャリア濃度と1000cm2V/sec以上の高移動度の2次元電子ガス(2DEG)層が形成される。このため、AlGaN/GaNヘテロ接合電界効果トランジスタ(以下GaNトランジスタと記載する)は、低オン抵抗及び高耐圧を実現するパワースイッチングトランジスタとして期待されている。

【0004】

GaNトランジスタは、潜在的な特性は従来のSiデバイスを遙かに上回る。例えば、GaNトランジスタは数十ns程度と非常に早い立ち上り・立ち下り時間を有し、数十から数百Aと大電流をスイッチングすることが可能である。しかし、高速・大電流スイッチングすることでチップとの接続ワイヤ、パッケージのリード、配線パターンの寄生インダクタンスLの影響を受け、ゲートにはL×di/dtによって決まる電圧ノイズが発生しゲートの誤点呼等ゲート誤動作の原因となる。よって、GaNトランジスタの高速・大電流スイッチング特性を活かすためには、ゲート誤動作を抑制する方法が必要不可欠である。

【0005】

図12は、特許文献1に記載された、従来のIGBTのドライブ回路を説明する回路構成図である。同図におけるドライブ回路は、過電流や温度上昇に対する保護機能を有する保護回路を含んでいる。上記ドライブ回路のパワー素子であるIGBT516が上記保護回路を経由したゲート電圧によりゲート誤動作をすることを抑制するために、上記ドライブ回路には、IGBT516の出力端子より分岐するパワーGND端子551と、センスGND端子552とが配置されている。ここで、パワーGND端子551は、ドレイン−ソース間を流れるドライブ電流の径路であるパワーラインの基準電位となる端子であり、センスGND端子は保護回路の入力端子における電圧を計測するための基準電位となる端子である。

【0006】

パワーGND端子551は、IGBT516をドライブしたときに流れるドライブ電流の電流経路上に配置される。一方、センスGND端子552は、IGBT516の動作状態を監視する保護回路のGNDレベルを規定する電流経路上に配置される。

【0007】

具体的には、保護回路は、過電流をモニタするためのセンス端子553の電圧と、基準電圧源581で規定される閾値電圧とを比較器579にて比較することにより、過電流保護の要否を判定している。よって、保護回路は、比較器579への入力電圧である上記両電圧を規定するためのセンスGND線576が必要となる。このため、センスGND線576は、パワー線から分岐した配線であって、パワーGND線567からインピーダンス(抵抗584)を介して接続されている。つまり、このパワーGND線567上に保護回路用のセンスGNDが別途設けられている。

【0008】

すなわち、センスGND端子552は、パワー素子が接続される側から見て保護回路が接続される配線パターンの位置よりも遠い位置で、インピーダンスを介してパワーGND線567に接続されている。これにより、パワー線の寄生インダクタンス585によりパワーGND線567に過渡的に発生した電圧は、そのインピーダンス(抵抗584)により抑制されるので、適正な保護回路の保護動作が担保され、IGBT516を含むドライブ回路は、安定した動作が得られるとしている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特許第3008924号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、特許文献1に記載されたドライブ回路では、IGBT516からのセンス電圧を正確にモニタするためのセンスGND線576及びセンスGND端子552を別途設ける必要がある。

【0011】

また、センスGND線576は、その終端部にインピーダンス(抵抗584)が接続されているとはいえ、パワーラインから分岐させたものであるため、パワーGND線567から完全に独立したものではない。従って、IGBT516のオンオフ切り換え時である過渡状態において発生する電圧ノイズは、センスGND線576の内部インダクタンス583によっても発生する可能性があり、上記センス電圧は、依然として電圧ノイズを含む可能性がある。

【0012】

特に、GaN(窒化ガリウム)やSiC(炭化珪素)といったワイドバンドギャップ半導体を用いた電流駆動型のスイッチングパワーデバイスでは、寄生容量が非常に小さい為、高速・大電流動作が可能である反面、ゲートの動作閾値電圧が1V程度と非常に低い。よって、特許文献1に記載されたドライブ回路を、特に、上述した低閾値電圧を有する電流駆動型のGaNやSiCパワーデバイスに適用した場合、上記電圧ノイズを厳しく抑制することが必要である。さもなければ、過渡状態において寄生インダクタンスの影響によりゲートあるいはゲート駆動回路に発生した電圧ノイズにより、誤点呼等、ゲートの誤動作が発生し、上記誤動作防止の効果が抑制されてしまう。

【0013】

さらに、上記保護回路に代表されるゲート駆動回路を複数構成し、パワー素子の出力電流を高精度または複雑に制御する場合、特許文献1に記載されたドライブ回路のように、ゲート駆動回路である保護回路の基準電位がパワーラインのGNDで規定されると、複数のゲート駆動回路を独立に動作させることが制限されてしまう。

【0014】

本発明は上記の課題に鑑み、電流駆動型の半導体装置のゲートあるいはゲート駆動回路への寄生インダクタンスによる外乱ノイズを低減し、ゲート駆動を高精度化及び安定化させることが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0015】

上記の課題を解決するために、本発明の一態様に係る半導体装置は、電力変換を行う電流駆動型の第1半導体素子と、前記第1半導体素子の電力変換を制御する第1ゲート駆動回路と、接続端子部とを備え、前記第1半導体素子は、基板の上に積層された窒化物半導体層の積層体と、前記積層体の上に形成されたゲート電極と、前記基板上であって、前記ゲート電極の両側方に形成された第1オーミック電極及び第2オーミック電極と、前記第1半導体素子上にあって、前記ゲート電極から配線されたゲート電極パッドと、前記第1半導体素子上にあって、前記第1オーミック電極及び前記第2オーミック電極からそれぞれ配線された第1オーミック電極パッド及び第2オーミック電極パッドとを有し、前記接続端子部は、第1の接続材により前記第1オーミック電極パッドと接続された第1オーミック電極端子と、第2の接続材により前記第2オーミック電極パッドと接続された第2オーミック電極端子と、第3の接続材により前記第1オーミック電極パッドと接続されたゲート駆動用端子と、第4の接続材により前記ゲート電極パッドと接続されたゲート端子とを有し、前記第1ゲート駆動回路の入力端子は、前記ゲート駆動用端子に接続され、前記第1ゲート駆動回路の出力端子は、前記ゲート端子に接続され、前記第1ゲート駆動回路の基準電位を前記第1オーミック電極パッドの電位とすることを特徴とする。

【0016】

上記構成をとることにより、第1半導体素子、第1オーミック電極パッド、第1の接続材、第1オーミック電極端子、外部電源及び負荷、第2オーミック電極端子、第2の接続材及び第2オーミック電極パッド、を流れるパワーラインの電流径路と、第1半導体素子、第1オーミック電極パッド、第3の接続材、ゲート駆動用端子、ゲート駆動用回路、ゲート端子、第4の接続材、ゲート電極パッド、を流れるゲート駆動ラインの電流径路とは、別個の電流径路を形成している。また、ゲート駆動回路の入力端子は、第3の接続材を介して第1オーミック電極パッドに電気接続されているので、当該第1オーミック電極パッドの電位が、電流駆動型のゲート駆動回路の基準電位となっている。

【0017】

本態様によれば、本発明の半導体装置は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路の接地端子を設ける必要がない。よって、第1半導体素子の過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路は、高精度及び安定なゲート駆動を実行することが可能となる。

【0018】

また、前記接続端子部は、さらに、前記第1半導体素子が接合された第1基板端子とを有し、前記ゲート駆動用端子は、前記第1基板端子と同一端子としてもよい。

【0019】

本態様によれば、窒化物半導体素子の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効である。

【0020】

また、さらに、前記第1半導体素子と同一の構造を有する第2半導体素子と、前記第1ゲート駆動回路と同一の構造を有する第2ゲート駆動回路とを備え、前記第2半導体素子と前記第2ゲート駆動回路との接続関係は、前記第1半導体素子と前記第1ゲート駆動回路との接続関係と同一であり、前記第1半導体素子の第1オーミック電極端子と、前記第2半導体素子の第2オーミック電極端子とが接続されることにより、前記第1半導体素子、前記第2半導体素子、前記第1ゲート駆動回路及び前記第2ゲート駆動回路は、第1のハーフブリッジを構成してもよい。

【0021】

本発明の一態様に係る半導体装置は、上記半導体素子とゲート駆動回路とを1ユニットとした構成を2ユニット直列接続したハーフブリッジに適用することが可能である。この構成においても、ゲート駆動回路は、高精度及び安定なゲート駆動を実行することが可能となる。

【0022】

また、さらに、前記第1のハーフブリッジと並列に接続された、前記第1のハーフブリッジと同一構成を有する第2のハーフブリッジを備え、単相モータを駆動するモータ駆動インバータを構成してもよい。

【0023】

本発明の一態様に係る半導体装置は、2つの並列接続された上記ハーフブリッジからなる単相駆動のインバータ回路に適用することが可能である。これにより、誤動作が低減された、安定した単相モータの駆動が実現される。

【0024】

また、さらに、前記第1のハーフブリッジと並列に接続された、前記第1のハーフブリッジと同一構成を有する第2のハーフブリッジ及び第3のハーフブリッジを備え、三相モータを駆動するモータ駆動インバータを構成してもよい。

【0025】

本発明の一態様に係る半導体装置は、3つの並列接続された上記ハーフブリッジからなる三相駆動のインバータ回路に適用することが可能である。これにより、誤動作が低減された、安定した三相モータの駆動が実現される。

【0026】

また、上記の課題を解決するために、本発明の一態様に係る半導体装置は、電力変換を行う電流駆動型の第3半導体素子と、前記第3半導体素子の電力変換を制御する第3ゲート駆動回路及び第4ゲート駆動回路と、接続端子部とを備え、前記第3半導体素子は、基板の上に積層された窒化物半導体層の積層体と、前記積層体の上に隣接して形成された第1ゲート電極及び第2ゲート電極と、前記基板上であって、前記第1ゲート電極及び前記第2ゲート電極の両側方に形成された第3オーミック電極及び第4オーミック電極と、前記第1半導体素子上にあって、前記第1ゲート電極及び前記第2ゲート電極からそれぞれ配線された第1ゲート電極パッド及び第2ゲート電極パッドと、前記第1半導体素子上にあって、前記第3オーミック電極及び前記第4オーミック電極からそれぞれ配線された第3オーミック電極パッド及び第4オーミック電極パッドとを有し、前記接続端子部は、第1の接続材により前記第3オーミック電極パッドと接続された第3オーミック電極端子と、第2の接続材により前記第4オーミック電極パッドと接続された第4オーミック電極端子と、第3の接続材により前記第3オーミック電極パッドと接続された第1ゲート駆動用端子と、第4の接続材により前記第4オーミック電極パッドと接続された第2ゲート駆動用端子と、第5の接続材により前記第1ゲート電極パッドと接続された第1ゲート端子と、第6の接続材により前記第2ゲート電極パッドと接続された第2ゲート端子とを有し、前記第3ゲート駆動回路の入力端子は、前記第1ゲート駆動用端子に接続され、前記第3ゲート駆動回路の出力端子は、前記第1ゲート端子に接続され、前記第3ゲート駆動回路の基準電位を前記第3オーミック電極パッドの電位とし、前記第4ゲート駆動回路の入力端子は、前記第2ゲート駆動用端子に接続され、前記第4ゲート駆動回路の出力端子は、前記第2ゲート端子に接続され、前記第4ゲート駆動回路の基準電位を前記第4オーミック電極パッドの電位とすることを特徴とする。

【0027】

上記構成をとることにより、ダブルゲート型の第3半導体素子、第3オーミック電極パッド、第1の接続材、第3オーミック電極端子、外部電源及び負荷、第4オーミック電極端子、第2の接続材及び第4オーミック電極パッド、を流れるパワーラインの電流径路と、第3半導体素子、第3オーミック電極パッド、第3の接続材、第1ゲート駆動用端子、第3ゲート駆動用回路、第1ゲート端子、第5の接続材、第1ゲート電極パッド、を流れる第1ゲート駆動ラインの電流径路とは、別個の電流径路を形成している。また、上記パワーラインの電流径路と、第3半導体素子、第4オーミック電極パッド、第4の接続材、第2ゲート駆動用端子、第4ゲート駆動用回路、第2ゲート端子、第6の接続材、第2ゲート電極パッド、を流れる第2ゲート駆動ラインの電流径路とは、別個の電流径路を形成している。また、第3ゲート駆動回路の入力端子は、第3の接続材を介して第3オーミック電極パッドに電気接続されているので、当該第3オーミック電極パッドの電位が、電流駆動型の第3ゲート駆動回路の基準電位となっている。また、第4ゲート駆動回路の入力端子は、第4の接続材を介して第4オーミック電極パッドに電気接続されているので、当該第4オーミック電極パッドの電位が、電流駆動型の第4ゲート駆動回路の基準電位となっている。

【0028】

本態様によれば、本発明の半導体装置は、上記パワーライン及び上記第1及び第2ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、第3半導体素子の過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、第3及び第4ゲート駆動回路は、高精度及び安定なゲート駆動を実行することが可能となる。

【0029】

また、さらに、前記第3半導体素子と同一の構造を有する第4半導体素子と、前記第3ゲート駆動回路と同一の構造を有する第5ゲート駆動回路と、前記第4ゲート駆動回路と同一の構造を有する第6ゲート駆動回路とを備え、前記第4半導体素子と前記第5ゲート駆動回路との接続関係は、前記第3半導体素子と前記第3ゲート駆動回路との接続関係と同一であり、前記第4半導体素子と前記第6ゲート駆動回路との接続関係は、前記第3半導体素子と前記第4ゲート駆動回路との接続関係と同一であり、前記第3半導体素子の第3オーミック電極端子と、前記第4半導体素子の第4オーミック電極端子とが接続されることにより、前記第3半導体素子、前記第4半導体素子、前記第3ゲート駆動回路、前記第4ゲート駆動回路、前記第5ゲート駆動回路及び前記第6ゲート駆動回路は、第4のハーフブリッジを構成してもよい。

【0030】

本発明の一態様に係る半導体装置は、上記ダブルゲート型の半導体素子と2つのゲート駆動回路とを1ユニットとした構成を2ユニット直列接続したハーフブリッジに適用することが可能である。この構成においても、第3及び第4ゲート駆動回路は、高精度及び安定なゲート駆動を実行することが可能となる。

【0031】

また、さらに、前記第4のハーフブリッジと並列に接続された、前記第4のハーフブリッジと同一構成を有する第5のハーフブリッジを備え、単相モータを駆動するモータ駆動インバータを構成してもよい。

【0032】

本発明の一態様に係る半導体装置は、2つの並列接続された上記ハーフブリッジからなる単相駆動のインバータ回路に適用することが可能である。これにより、誤動作が低減された、安定した単相モータの駆動が実現される。

【0033】

また、さらに、前記第4のハーフブリッジと並列に接続された、前記第4のハーフブリッジと同一構成を有する第5のハーフブリッジ及び第6のハーフブリッジを備え、三相モータを駆動するモータ駆動インバータを構成してもよい。

【0034】

本発明の一態様に係る半導体装置は、3つの並列接続された上記ハーフブリッジからなる三相駆動のインバータ回路に適用することが可能である。これにより、誤動作が低減された、安定した三相モータの駆動が実現される。

【0035】

また、さらに、前記第3半導体素子と同一の構造を有する第4半導体素子〜第11半導体素子を備え、前記第4半導体素子〜第11半導体素子のそれぞれは、前記第3ゲート駆動回路と同一の構造を有するゲート駆動回路と接続され、かつ、前記第4ゲート駆動回路と同一の構造を有するゲート駆動回路と接続されており、前記第3半導体素子、前記第6半導体素子及び前記第9半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第1出力端子に接続され、前記第4半導体素子、前記第7半導体素子及び前記第10半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第2出力端子に接続され、前記第5半導体素子、前記第8半導体素子及び前記第11半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第3出力端子に接続され、前記第3半導体素子、前記第4半導体素子及び前記第5半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第1入力端子に接続され、前記第6半導体素子、前記第7半導体素子及び前記第8半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第2入力端子に接続され、前記第9半導体素子、前記第10半導体素子及び前記第11半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第3入力端子に接続されており、三相モータを駆動するモータ駆動マトリクスコンバータを構成してもよい。

【0036】

本発明の一態様に係る半導体装置は、上記ダブルゲート型の半導体素子と2つのゲート駆動回路とを1ユニットとした構成をマトリクス状に配置した三相駆動のマトリクスコンバータ回路に適用することが可能である。入力電源が交流の場合、駆動システムの基準電位が変動するので、各ユニットの基準電位は、駆動システムの基準電位とせずに、任意の基準電位とすることが好ましい。本構成によれば、各ユニットの基準電位は、電流駆動型のソースパッドである第3オーミック電極パッドまたは第4オーミック電極パッドとしているので、半導体装置の基準電位と合わせる必要がなく、複数のゲート駆動回路を独立に動作させることが可能となる。

【発明の効果】

【0037】

本発明の半導体装置によれば、パワーラインの電流径路とゲート駆動ラインの電流径路とを別個の電流径路とし、ゲート駆動回路の基準電位を電流駆動型の半導体素子のソースパッド電位とし、且つゲート駆動用端子電位とすることにより、寄生インダクタンスにより発生する外乱ノイズを低減することができる。

【図面の簡単な説明】

【0038】

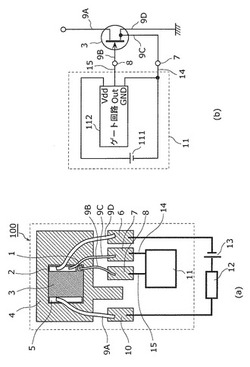

【図1】(a)は、本発明の実施の形態1に係る半導体装置の結線を説明する上面図である。(b)は、本発明の実施の形態1に係る半導体装置の要部における等価回路図である。

【図2】(a)は、本発明の実施の形態1に係る半導体素子の上面図である。(b)は、図2(a)に記載された半導体素子のX−X’における断面図である。(c)は、図2(a)に記載された半導体素子のY−Y’における断面図である。

【図3】本発明の実施の形態2に係る半導体装置を含む回路構成図である。

【図4】本発明の実施の形態2に係るハーフブリッジの要部における等価回路図である。

【図5】本発明の実施の形態2に係る変形例を示す半導体装置を含む回路構成図である。

【図6】(a)は、本発明の実施の形態3に係る半導体装置の結線を説明する上面図である。(b)は、本発明の実施の形態3に係る半導体装置の要部における等価回路図である。

【図7】(a)は、本発明の実施の形態3に係る半導体素子の上面図である。(b)は、図7(a)に記載された半導体素子のX−X’における断面図である。(c)は、図7(a)に記載された半導体素子のY−Y’における断面図である。

【図8】本発明の実施の形態4に係る半導体装置を含む回路構成図である。

【図9】本発明の実施の形態4に係るハーフブリッジの要部における等価回路図である。

【図10】本発明の実施の形態4に係る第1の変形例を示す半導体装置を含む回路構成図である。

【図11】本発明の実施の形態4に係る第2の変形例を示す半導体装置を含む回路構成図である。

【図12】特許文献1に記載された、従来のIGBTのドライブ回路を説明する回路構成図である。

【発明を実施するための形態】

【0039】

以下、本発明の半導体装置の実施の形態について、図面を参照しながら説明する。

【0040】

(実施の形態1)

図1(a)は、本発明の実施の形態1に係る半導体装置の結線を説明する上面図である。同図に記載された半導体装置100は、第1半導体素子である半導体素子3と、接続材である複数のボンディングワイヤ9A〜9Dと、ゲート駆動回路11とを備える。また、半導体装置100上には、第1基板端子である基板端子4と、第1オーミック電極端子であるオーミック電極端子6及び第2オーミック電極端子であるオーミック電極端子10と、ゲート駆動用端子7と、ゲート端子8とが、互いに分離されて配置されており、これらは接続端子部を構成している。また、半導体素子3は、基板端子4上に接合され、半導体素子3上には、ゲート電極パッド1と、第1オーミック電極パッドであるオーミック電極パッド2及び第2オーミック電極パッドであるオーミック電極パッド5とが、互いに分離されて配置されている。

【0041】

オーミック電極パッド5は、ボンディングワイヤ9Aを介して、オーミック電極端子10に電気接続されている。また、オーミック電極パッド2は、ボンディングワイヤ9Dを介して、オーミック電極端子6に電気接続されており、別途、ボンディングワイヤ9Cを介して、ゲート駆動用端子7にも電気接続されている。また、ゲート電極パッド1は、ボンディングワイヤ9Bを介して、ゲート端子8に電気接続されている。ボンディングワイヤ9A〜9Dは、例えば、Alからなる。

【0042】

オーミック電極端子10は、負荷12の一方の端子に電気接続され、オーミック電極端子6は直流電源13の負極に電気接続されている。また、負荷12の他方の端子は、直流電源13の正極に電気接続されている。上記接続により、半導体素子3、半導体素子3上に配置されたオーミック電極パッド2、ボンディングワイヤ9D、オーミック電極端子6、直流電源13、負荷12、オーミック電極端子10、ボンディングワイヤ9A、及びオーミック電極パッド5は、半導体素子3のドレイン電流が流れるパワーラインを構成している。

【0043】

ゲート駆動回路11は、出力端子15、入力端子である基準電位端子14、及びゲート駆動回路駆動用の直流電源(図示せず)を有する。出力端子15はゲート端子8へ電気接続され、基準電位端子14はゲート駆動用端子7へ電気接続されている。上記接続により、半導体素子3、オーミック電極パッド2、ボンディングワイヤ9C、ゲート駆動用端子7、ゲート駆動回路11、ゲート端子8、ボンディングワイヤ9B、及びゲート電極パッド1は、ゲート駆動ラインを構成している。つまり、ゲート駆動回路11は、半導体素子3のゲート−ソース間抵抗により決定されるゲート−ソース間電流をオーミック電極パッド2、ボンディングワイヤ9C及びゲート駆動用端子7を介して入力し、この入力電流により、半導体素子3の電力変換を制御するための、ゲートに供給する電気信号を決定する第1ゲート駆動回路である。

【0044】

図1(b)は、本発明の実施の形態1に係る半導体装置の要部における等価回路図である。ゲート駆動回路11は、直流電源111とゲート回路112とを備えた電流駆動型の回路である。ゲート回路112の電源端子Vddには直流電源111の正極が電気接続され、ゲート回路112の基準電位端子GNDには直流電源111の負極が電気接続されている。この場合、図1(a)により説明した上記パワーラインと、上記ゲート駆動ラインとは、別個の電流ラインを形成している。また、ゲート駆動回路11の基準電位端子14は、ボンディングワイヤ9Cを介してオーミック電極パッド2に電気接続されているので、このオーミック電極パッド2の電位が、電流駆動型のゲート駆動回路11の基準電位となっている。

【0045】

これにより、半導体装置100は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、半導体素子3の過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路11は、高精度及び安定なゲート駆動を実行することが可能となる。

【0046】

なお、上記構成では、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位としており、オーミック電極パッド2の電位を半導体装置100のGND電位とは独立に設定することが可能であるが、ゲート駆動回路11の用途及び構成により、オーミック電極パッド2の電位を半導体装置100のGND電位としてもよい。この場合においても、上記構成により得られた効果と同様の効果を奏することが可能となる。また、半導体装置100の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効である。

【0047】

図2(a)は、本発明の実施の形態1に係る半導体素子の上面図である。また、図2(b)は、図2(a)に記載された半導体素子のX−X’における断面図である。また、図2(c)は、図2(a)に記載された半導体素子のY−Y’における断面図である。図2(a)に記載された、半導体素子3は、例えば、AlGaN/GaNのヘテロ接合からなる二次元電子ガス(2DEG)をチャネルとして用いた窒化物半導体素子である。

【0048】

図2(a)、図2(b)及び図2(c)に記載されたように、半導体素子3には、基板23上にバッファ層22、窒化物半導体層21、窒化物半導体層20、p型窒化物半導体層26が順次積層され、ゲート電極1A、オーミック電極2A及び5Aが形成され、保護膜19が形成されている。バッファ層22、窒化物半導体層21、窒化物半導体層20、p型窒化物半導体層26は、窒化物半導体層の積層体を形成している。オーミック電極パッド5は、第2オーミック電極であるオーミック電極5Aに接続され、オーミック電極パッド2は第1オーミック電極であるオーミック電極2Aに接続され、ゲート電極パッド1は、ゲート配線1Bを介してゲート電極1Aに接続され、それぞれ、保護膜19の開口部に形成されている。また、オーミック電極5A、オーミック電極2A及びゲート電極1Aは、活性領域30にて、図2(a)に示されたようなフィンガー形状を構成している。つまり、オーミック電極5Aと2Aとの間に、ゲート電極1Aが配置されている。上記構成の半導体素子3は、例えば、図1(a)に記載された直流電源13の電圧値が300Vであって、10A程度のパワーラインを流れる電流をオンオフさせるスイッチング素子である。

【0049】

図2(a)、図2(b)及び図2(c)に記載されたような窒化物半導体素子は、各端子間の寄生容量が数十pF〜数百pFと非常に小さいため、MOSFETやIGBTに比べて、数十ns〜数百nsレベルの高速スイッチングが可能である。しかし、上記スイッチングが高速であればある程、ワイヤやリード、配線パターン等の寄生インダクタンスLとdi/dtとの積である電圧ノイズが発生する。前述したように、この電圧ノイズは、ゲート駆動において誤点呼といった誤動作を引き起こすため、低減する必要がある。

【0050】

上記電圧ノイズを低減するために、図1(a)に記載したように、具体的には、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位としている。そして、オーミック電極パッド2からボンディングワイヤ9Dを介したオーミック電極端子6への電流経路と、オーミック電極パッド2からボンディングワイヤ9Dを介したゲート駆動用端子7への電流径路とを分離することで、大電流用のパワーループとゲート駆動回路11用のゲート駆動ループとを分離することを可能としている。この構成により、ゲート駆動回路11への外乱ノイズとなる上記電圧ノイズを低減することが可能となる。

【0051】

なお、図2(a)、図2(b)及び図2(c)に記載された窒化物半導体素子は、ショットキーゲート電極を用いたMESFETでもよい。

【0052】

また、各電極パッドと電極とを接続する接続材としては、ボンディングワイヤ以外にもAlリボンやCu製のクリップ材料であってもよい。

【0053】

また、半導体装置100の回路構成によっては、オーミック電極パッド2を基板23へ接続することで、基板端子4をゲート駆動用端子7としてもよい。こうすることで窒化物半導体素子の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効な手段となる。

【0054】

(実施の形態2)

図3は、本発明の実施の形態2に係る半導体装置を含む回路構成図である。同図に記載された駆動システムは、単相インバータ回路によりモータを駆動するシステムであり、直流電源28と、半導体装置110とモータ29とを備える。

【0055】

半導体装置110は、第1のハーフブリッジであるハーフブリッジ101及び第2のハーフブリッジであるハーフブリッジ102を備える。ハーフブリッジ101とハーフブリッジ102とは同一構成であり、それぞれ、実施の形態1に記載された半導体装置100の構成を有している。つまり、図3に記載された半導体素子3A、3B、3C及び3Dは、それぞれ、図1に記載された半導体素子3と同じ構成である。また、図3に記載されたゲート駆動回路11A、11B、11C及び11Dは、それぞれ、図1に記載されたゲート駆動回路11と同じ構成である。また、ハーフブリッジ101とハーフブリッジ102とは、並列接続されている。ハーフブリッジ101の有する第1半導体素子である半導体素子3A及び第2半導体素子である3Bの中点とモータ29の一方の端子とが電気接続され、ハーフブリッジ102の有する半導体素子3C及び3Dの中点とモータ29の他方の端子とが電気接続されている。ここで、第1ゲート駆動回路であるゲート駆動回路11A及び11C、つまり、ハイサイドの基準電位端子14を、例えば、上述した各々の中点に接続し、第2ゲート駆動回路であるゲート駆動回路11B及び11D、つまり、ローサイドの基準電位端子14を、例えば、半導体装置110のGNDに接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0056】

図4は、本発明の実施の形態2に係るハーフブリッジの要部における等価回路図である。ゲート駆動回路11Aは、直流電源111Aとゲート回路112Aとを備えた電流駆動型の第1ゲート駆動回路である。ゲート回路112Aの電源端子Vddには直流電源111Aの正極が電気接続され、ゲート回路112Aの基準電位端子GNDには直流電源111Aの負極が電気接続されている。この場合、図3に記載された、直流電源28、オーミック電極端子10、半導体素子3A、オーミック電極端子6、及びモータ29とで構成されるパワーラインと、直流電源111A、ゲート回路112A、ゲート端子8、半導体素子3A、ゲート駆動用端子7とで構成されるゲート駆動ラインとは、別個の電流ラインを形成している。また、ゲート駆動回路11Aの基準電位端子14は、ボンディングワイヤ9Cを介してオーミック電極パッド2に電気接続されているので、このオーミック電極パッド2の電位が、電流駆動型のゲート駆動回路11の基準電位となっている。

【0057】

また、ゲート駆動回路11B、11C及び11Dにおいても、上述したゲート駆動回路11Aと同様の構成となっている。

【0058】

これにより、半導体装置110は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、半導体素子3A〜3Dの過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路11A〜11Dは、高精度及び安定なゲート駆動を実行することが可能となる。

【0059】

図5は、本発明の実施の形態2に係る変形例を示す半導体装置を含む回路構成図である。同図に記載された駆動システムは、三相インバータ回路によりモータを駆動するシステムであり、直流電源28と、半導体装置120とモータ31とを備える。

【0060】

半導体装置120は、ハーフブリッジ101、102及び第3のハーフブリッジであるハーフブリッジ103を備える。ハーフブリッジ101、102及び103は同一構成であり、それぞれ、実施の形態1に記載された半導体装置100の構成を有している。つまり、図5に記載された半導体素子3A、3B、3C、3D、3E及び3Fは、それぞれ、図1に記載された半導体素子3と同じ構成である。また、図5に記載されたゲート駆動回路11A、11B、11C、11D、11E及び11Fは、それぞれ、図1に記載されたゲート駆動回路11と同じ構成である。また、ハーフブリッジ101、102及び103は、互いに並列接続されている。ハーフブリッジ101の有する半導体素子3A及び3Bの中点とモータ31の第1の端子とが電気接続され、ハーフブリッジ102の有する半導体素子3C及び3Dの中点とモータ31の第2の端子とが電気接続され、ハーフブリッジ103の有する半導体素子3E及び3Fの中点とモータ31の第3の端子とが電気接続されている。ここで、ゲート駆動回路11A、11C、及び11E、つまり、ハイサイドの基準電位端子14を、例えば、上述した各々の中点に接続し、ゲート駆動回路11B、11D及び11F、つまり、ローサイドの基準電位端子14を、例えば、半導体装置110のGNDに接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0061】

(実施の形態3)

本実施の形態では、ダブルゲート型の半導体素子を有する半導体装置について、本発明を適用した場合の構成及び効果を、図面を用いて説明する。つまり、半導体素子のドレイン電流を、当該ドレイン−ソース間に配置された2つのゲート電極を独立に制御することにより、高精度または複雑に制御することが可能となる。

【0062】

図6(a)は本発明の実施の形態3に係る半導体装置の結線を説明する上面図である。同図に記載された半導体装置200は、第3半導体素子である半導体素子40と、接続材である複数のボンディングワイヤ9A〜9Fと、第4ゲート駆動回路であるゲート駆動回路47及び第3ゲート駆動回路であるゲート駆動回路48とを備える。また、半導体装置200上には、基板端子4と、第3オーミック電極端子であるオーミック電極端子6及び第4オーミック電極端子であるオーミック電極端子46と、第1ゲート駆動用端子であるゲート駆動用端子7及び第2ゲート駆動用端子であるゲート駆動用端子45と、第1ゲート端子であるゲート端子42及び第2ゲート端子であるゲート端子44とが、互いに分離されて配置されている。また、半導体素子40は、基板端子4上に接合され、半導体素子40上には、第1ゲート電極パッドであるゲート電極パッド41及び第2ゲート電極パッドであるゲート電極パッド43と、第3オーミック電極パッドであるオーミック電極パッド2及び第4オーミック電極パッドであるオーミック電極パッド5とが、互いに分離されて配置されている。

【0063】

オーミック電極パッド5は、ボンディングワイヤ9Aを介して、オーミック電極端子46に電気接続されており、別途、ボンディングワイヤ9Eを介して、ゲート駆動用端子45にも電気接続されている。また、オーミック電極パッド2は、ボンディングワイヤ9Dを介して、オーミック電極端子6に電気接続されており、別途、ボンディングワイヤ9Cを介して、ゲート駆動用端子7にも電気接続されている。また、ゲート電極パッド41は、ボンディングワイヤ9Bを介して、ゲート端子42に電気接続され、ゲート電極パッド43は、ボンディングワイヤ9Fを介して、ゲート端子44に電気接続されている。ボンディングワイヤ9A〜9Fは、例えば、Alからなる。

【0064】

オーミック電極端子46は、負荷12の一方の端子に電気接続され、オーミック電極端子6は直流電源13の負極に電気接続されている。また、負荷12の他方の端子は、直流電源13の正極に電気接続されている。上記接続により、半導体素子40、半導体素子40上に配置されたオーミック電極パッド2、ボンディングワイヤ9D、オーミック電極端子6、直流電源13、負荷12、オーミック電極端子46、ボンディングワイヤ9A、及びオーミック電極パッド5は、パワーラインを構成している。

【0065】

ゲート駆動回路48は、出力端子15、入力端子である基準電位端子14、及びゲート駆動回路駆動用の直流電源(図示せず)を有する。出力端子15はゲート端子42へ電気接続され、基準電位端子14はゲート駆動用端子7へ電気接続されている。上記接続により、半導体素子40、オーミック電極パッド2、ボンディングワイヤ9C、ゲート駆動用端子7、ゲート駆動回路48、ゲート端子42、ボンディングワイヤ9B、及びゲート電極パッド41は、ゲート駆動ラインを構成している。つまり、ゲート駆動回路48は、半導体素子40のゲート−ソース間抵抗により決定されるゲート−ソース間電流をオーミック電極パッド2、ボンディングワイヤ9C及びゲート駆動用端子7を介して入力し、この入力電流により、半導体素子40の電力変換を制御するための、ゲートに供給する電気信号を決定する。

【0066】

ゲート駆動回路47は、ゲート駆動回路48と同様の構成を有する。ゲート駆動回路47の接続により、半導体素子40、オーミック電極パッド5、ボンディングワイヤ9E、ゲート駆動用端子45、ゲート駆動回路47、ゲート端子44、ボンディングワイヤ9F、及びゲート電極パッド43は、ゲート駆動ラインを構成している。つまり、ゲート駆動回路47は、半導体素子40のゲート−ドレイン間抵抗により決定されるゲート−ドレイン間電流をオーミック電極パッド5、ボンディングワイヤ9E及びゲート駆動用端子45を介して入力し、この入力電流により、半導体素子40の電力変換を制御するための、ゲートに供給する電気信号を決定する。

【0067】

図6(b)は、本発明の実施の形態3に係る半導体装置の要部における等価回路図である。ゲート駆動回路47は、直流電源471とゲート回路472とを備えた電流駆動型の回路である。ゲート回路472の電源端子Vddには直流電源471の正極が電気接続され、ゲート回路472の基準電位端子GNDには直流電源471の負極が電気接続されている。この場合、図6(a)により説明したパワーラインと、ゲート駆動ラインとは、別個の電流ラインを形成している。また、ゲート駆動回路47の基準電位端子14は、ボンディングワイヤ9Eを介してオーミック電極パッド5に電気接続されているので、このオーミック電極パッド5の電位が、電流駆動型のゲート駆動回路47の基準電位となっている。

【0068】

また、ゲート駆動回路48は、直流電源481とゲート回路482とを備えた電流駆動型の回路である。ゲート回路482の電源端子Vddには直流電源481の正極が電気接続され、ゲート回路482の基準電位端子GNDには直流電源481の負極が電気接続されている。この場合、図6(a)により説明したパワーラインと、ゲート駆動ラインとは、別個の電流ラインを形成している。また、ゲート駆動回路48の基準電位端子14は、ボンディングワイヤ9Cを介してオーミック電極パッド2に電気接続されているので、このオーミック電極パッド2の電位が、電流駆動型のゲート駆動回路48の基準電位となっている。

【0069】

これにより、半導体装置200は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、半導体素子40の過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路47及び48は、それぞれ独立に、高精度及び安定なゲート駆動を実行することが可能となる。

【0070】

なお、上記構成では、ゲート駆動回路47の基準電位とゲート駆動回路48の基準電位とを、それぞれ、オーミック電極パッド5及び2の電位としており、オーミック電極パッド5及び2の電位を半導体装置200のGND電位とは独立に設定することが可能であるが、ゲート駆動回路47及び48の用途及び構成により、オーミック電極パッド2の電位を半導体装置200のGND電位としてもよい。この場合においても、上記構成により得られた効果と同様の効果を奏することが可能となる。また、半導体装置200の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効である。

【0071】

図7(a)は、本発明の実施の形態3に係る半導体素子の上面図である。また、図7(b)は、図7(a)に記載された半導体素子のX−X’における断面図である。また、図7(c)は、図7(a)に記載された半導体素子のY−Y’における断面図である。図7(a)に記載された、半導体素子40は、例えば、AlGaN/GaNのヘテロ接合からなる二次元電子ガス(2DEG)をチャネルとして用いた窒化物半導体素子である。

【0072】

図7(a)、図7(b)及び図7(c)に記載されたように、半導体素子40には、基板23上にバッファ層22、窒化物半導体層21、窒化物半導体層20、p型窒化物半導体層27及び32が順次積層され、ゲート電極41A及び43A、オーミック電極2A及び5Aが形成され、保護膜19が形成されている。バッファ層22、窒化物半導体層21、窒化物半導体層20、p型窒化物半導体層27及び32は、窒化物半導体層の積層体を形成している。オーミック電極パッド2及び5は、それぞれ、第3オーミック電極であるオーミック電極2A及び第4オーミック電極であるオーミック電極5Aに接続されている。また、ゲート電極パッド41及び43は、それぞれ、ゲート配線41B及び43Bを介して第1ゲート電極であるゲート電極41A及び第2ゲート電極であるゲート電極43Aに接続され、それぞれ、保護膜19の開口部に形成されている。また、オーミック電極2A、5A、ゲート電極41A及び43Aは、活性領域30にて、図7(a)に示されたようなフィンガー形状を構成している。つまり、オーミック電極5Aと2Aとの間に、ゲート電極41A及び43Aが、この順で配置されている。上記構成の半導体素子40は、例えば、図6(a)に記載された直流電源13の電圧値が300Vであって、10A程度のパワーラインを流れる電流をオンオフさせるスイッチング素子である。

【0073】

図7(a)、図7(b)及び図7(c)に記載されたような窒化物半導体素子は、各端子間の寄生容量が数十pF〜数百pFと非常に小さいため、MOSFETやIGBTに比べて数十ns〜数百nsと高速でスイッチングすることが可能である。しかし、上記スイッチングが、高速であればある程、ワイヤやリード、配線パターン等の寄生インダクタンスLとdi/dtとの積である電圧ノイズが発生する。前述したように、この電圧ノイズは、ゲート駆動において誤点呼といった誤動作を引き起こすため、低減する必要がある。

【0074】

上記電圧ノイズを低減するために、図6(a)に記載したように、具体的には、ゲート駆動回路47及び48の基準電位を、それぞれ、オーミック電極パッド5及び2の電位としている。そして、オーミック電極パッド5からボンディングワイヤ9Aを介したオーミック電極端子46への電流経路と、オーミック電極パッド5からボンディングワイヤ9Aを介したゲート駆動用端子45への電流径路とを分離することで、大電流用のパワーループとゲート駆動回路47用のゲート駆動ループとを分離することを可能としている。オーミック電極パッド2における同様の接続により、大電流用のパワーループとゲート駆動回路48用のゲート駆動ループとを分離することを可能としている。この構成により、ゲート駆動回路47及び48への外乱ノイズとなる上記電圧ノイズを低減することが可能となる。

【0075】

なお、図7(a)、図7(b)及び図7(c)に記載された窒化物半導体素子は、ショットキーゲート電極を用いたMESFETでもよい。

【0076】

また、各電極パッドと電極とを接続する接続材としては、ボンディングワイヤ以外にもAlリボンやCu製のクリップ材料であってもよい。

【0077】

また、半導体装置200の回路構成によっては、オーミック電極パッド2を基板23へ接続することで、基板端子4をゲート駆動用端子7としてもよい。こうすることで窒化物半導体素子の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効な手段となる。

【0078】

(実施の形態4)

図8は、本発明の実施の形態4に係る半導体装置を含む回路構成図である。同図に記載された駆動システムは、単相インバータ回路によりモータを駆動するシステムであり、直流電源28と、半導体装置210とモータ29とを備える。

【0079】

半導体装置210は、第4のハーフブリッジであるハーフブリッジ201及び第5のハーフブリッジであるハーフブリッジ202を備える。ハーフブリッジ201とハーフブリッジ202とは同一構成であり、それぞれ、実施の形態3に記載されたダブルゲート型の半導体装置200の構成を有している。つまり、図8に記載された半導体素子40A、40B、40C及び40Dは、それぞれ、図6に記載された半導体素子40と同じ構成である。また、図8に記載された、第4ゲート駆動回路であるゲート駆動回路47A、第6ゲート駆動回路である47B、第4ゲート駆動回路である47C及び第6ゲート駆動回路である47Dは、それぞれ、図6に記載されたゲート駆動回路47と同じ構成である。また、図8に記載された、第3ゲート駆動回路であるゲート駆動回路48A、第5ゲート駆動回路である48B、第3ゲート駆動回路である48C及び第5ゲート駆動回路である48Dは、それぞれ、図6に記載されたゲート駆動回路48と同じ構成である。また、ハーフブリッジ201とハーフブリッジ202とは、並列接続されている。ハーフブリッジ201の有する第3半導体素子である半導体素子40A及び第4半導体素子である40Bの中点とモータ29の一方の端子とが電気接続され、ハーフブリッジ202の有する第3半導体素子である半導体素子40C及び第4半導体素子である40Dの中点とモータ29の他方の端子とが電気接続されている。

【0080】

ここで、ゲート駆動回路48A及び48Cの基準電位端子14を、例えば、上述した各々の中点に接続し、ゲート駆動回路47A及び47Cの基準電位端子14を、例えば、直流電源28の正極に電気接続し、ゲート駆動回路48B及び48Dの基準電位端子14を、例えば、半導体装置210の接地端子に電気接続し、ゲート駆動回路47B及び47Dの基準電位端子14を例えば、上述した各々の中点に接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0081】

図9は、本発明の実施の形態4に係るハーフブリッジの要部における等価回路図である。ゲート駆動回路47Aは、直流電源471Aとゲート回路472Aとを備えた電流駆動型の回路である。ゲート回路472Aの電源端子Vddには直流電源471Aの正極が電気接続され、ゲート回路472Aの基準電位端子GNDには直流電源471Aの負極が電気接続されている。また、ゲート駆動回路48Aは、直流電源481Aとゲート回路482Aとを備えた電流駆動型の回路である。ゲート回路482Aの電源端子Vddには直流電源481Aの正極が電気接続され、ゲート回路482Aの基準電位端子GNDには直流電源481Aの負極が電気接続されている。

【0082】

この場合、図8に記載された、直流電源28、オーミック電極端子46、半導体素子40A、オーミック電極端子6、及びモータ29とで構成されるパワーラインと、直流電源471A、ゲート回路472A、ゲート端子44、半導体素子40A、ゲート駆動用端子45とで構成されるゲート駆動ラインとは、別個の電流ラインを形成している。同様に、上記パワーラインと、直流電源481A、ゲート回路482A、ゲート端子42、半導体素子40A、ゲート駆動用端子7とで構成されるゲート駆動ラインとは、別個の電流ラインを形成している。

【0083】

また、ゲート駆動回路47Aの基準電位端子14は、ボンディングワイヤ9Eを介してオーミック電極パッド5に電気接続されているので、このオーミック電極パッド5の電位が、電流駆動型のゲート駆動回路47Aの基準電位となっている。

【0084】

また、ゲート駆動回路48Aの基準電位端子14は、ボンディングワイヤ9Cを介してオーミック電極パッド2に電気接続されているので、このオーミック電極パッド2の電位が、電流駆動型のゲート駆動回路48Aの基準電位となっている。

【0085】

また、ゲート駆動回路47B、47C及び47Dにおいても、上述したゲート駆動回路47Aと同様の構成となっている。

【0086】

また、ゲート駆動回路48B、48C及び48Dにおいても、上述したゲート駆動回路48Aと同様の構成となっている。

【0087】

これにより、半導体装置210は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、半導体素子40A〜40Dの過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路47A〜47D及びゲート駆動回路48A〜48Dは、高精度及び安定なゲート駆動を実行することが可能となる。

【0088】

図10は、本発明の実施の形態4に係る第1の変形例を示す半導体装置を含む回路構成図である。同図に記載された駆動システムは、三相インバータ回路によりモータを駆動するシステムであり、直流電源28と、半導体装置220とモータ31とを備える。

【0089】

半導体装置220は、ハーフブリッジ201、202及び第6のハーフブリッジであるハーフブリッジ203を備える。ハーフブリッジ201、202及び203は同一構成であり、それぞれ、実施の形態3に記載されたダブルゲート型の半導体装置200の構成を有している。つまり、図10に記載された半導体素子40A、40B、40C、40D、40E及び40Fは、それぞれ、図6に記載された半導体素子40と同じ構成である。また、図10に記載されたゲート駆動回路47A、47B、47C、47D、47E及び47Fは、それぞれ、図6に記載されたゲート駆動回路47と同じ構成である。また、ハーフブリッジ201、202及び203は、互いに並列接続されている。ハーフブリッジ201の有する半導体素子40A及び40Bの中点とモータ31の第1の端子とが電気接続され、ハーフブリッジ202の有する半導体素子40C及び40Dの中点とモータ31の第2の端子とが電気接続され、ハーフブリッジ203の有する半導体素子40E及び40Fの中点とモータ31の第3の端子とが電気接続されている。

【0090】

ここで、ゲート駆動回路48A、48C及び48Eの基準電位端子14を、例えば、それぞれのハーフブリッジにおける上記中点に接続し、ゲート駆動回路47A、47C及び47Eの基準電位端子14を、例えば、直流電源28の正極に電気接続し、ゲート駆動回路48B、48D及び48Fの基準電位端子14を、例えば、半導体装置220の接地端子に接続し、ゲート駆動回路47B、47D及び47Fの基準電位端子14を、例えば、それぞれのハーフブリッジにおける上記中点に接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0091】

図11は、本発明の実施の形態4に係る第2の変形例を示す半導体装置を含む回路構成図である。同図に記載された駆動システムは、三相インバータ回路によりモータを駆動するシステムであり、交流電源60と、入力フィルタ61と、半導体装置230とモータ31とを備える。

【0092】

図11に記載された半導体素子50A〜50Iは、それぞれ、図6に記載されたダブルゲート型の半導体素子40と同じ構成である。また、図11に記載されたゲート駆動回路57A〜57Iは、それぞれ、図6に記載されたゲート駆動回路47と同じ構成である。また、図11に記載されたゲート駆動回路58A〜58Iは、それぞれ、図6に記載されたゲート駆動回路48と同じ構成である。

【0093】

交流電源60から三相の交流電力が入力され、三相入力の各相間に入力フィルタ61が接続されている。ゲート駆動回路58A、57A及びダブルゲート型の半導体素子50Aを1つの構成ユニットとし、同様の構成ユニットが9つ配置されている。つまり、1構成ユニットは、1つのダブルゲート型の半導体素子を、2つのゲート駆動回路で駆動している。上記9つの構成ユニットは、三相マトリクスコンバータ回路を形成することにより、モータ31へ三相の出力電流を供給している。

【0094】

具体的には、半導体装置230は、以下の構成を有する。

【0095】

第3半導体素子である半導体素子50A、第6半導体素子である半導体素子50D及び第9半導体素子である半導体素子50Gのオーミック電極端子46は、それぞれ、三相交流電源の第1出力端子に接続されている。

【0096】

第4半導体素子である半導体素子50B、第7半導体素子である半導体素子50E及び第10半導体素子である半導体素子50Hのオーミック電極端子46は、それぞれ、三相交流電源の第2出力端子に接続されている。

【0097】

第5半導体素子である半導体素子50C、第8半導体素子である半導体素子50F及び第11半導体素子である半導体素子50Iのオーミック電極端子46は、それぞれ、三相交流電源の第3出力端子に接続されている。

【0098】

半導体素子50A、半導体素子50B及び半導体素子50Cのオーミック電極端子6は、それぞれ、三相モータの第1入力端子に接続されている。

【0099】

半導体素子50D、半導体素子50E及び半導体素子50Fのオーミック電極端子6は、それぞれ、三相モータの第2入力端子に接続されている。

【0100】

半導体素子50G、半導体素子50H及び半導体素子50Iのオーミック電極端子6は、それぞれ、三相モータの第3入力端子に接続されている。

【0101】

ここで、ゲート駆動回路57A〜57Iの有する基準電位端子14を、例えば、入力側の端子へ接続し、ゲート駆動回路58A〜58Iの有する基準電位端子14を、例えば、出力側の端子へ接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0102】

また入力電源が交流の場合、駆動システムの基準電位が変動するので、各ユニットの基準電位は、駆動システムの基準電位とせずに、任意の基準電位とすることが好ましい。本構成によれば、各ユニットの基準電位は、電流駆動型のソースパッドであるオーミック電極パッド2またはオーミック電極パッド5としているので、半導体装置の基準電位と合わせる必要がなく、複数のゲート駆動回路を独立に動作させることが可能となる。

【0103】

以上、本発明の半導体装置について、実施の形態に基づいて説明してきたが、本発明に係る半導体装置は、上記実施の形態に限定されるものではない。実施の形態1〜4及びその変形例における任意の構成要素を組み合わせて実現される別の実施の形態や、実施の形態1〜4及びその変形例に対して本発明の主旨を逸脱しない範囲で当業者が思いつく各種変形を施して得られる変形例や、本発明に係る半導体装置を内蔵した各種機器も本発明に含まれる。

【産業上の利用可能性】

【0104】

本発明は、高精度かつ安定な電力制御を要するハイパワーデバイスのゲート駆動制御に利用可能であり、電流駆動型の半導体装置への応用に適している。

【符号の説明】

【0105】

1、41、43 ゲート電極パッド

1A、41A、43A ゲート電極

1B ゲート配線

2、5 オーミック電極パッド

2A、5A オーミック電極

3、3A、3B、3C、3D、3E、3F、40、40A、40B、40C、40D、40E、40F、50A、50B、50C、50D、50E、50F、50G、50H、50I 半導体素子

4 基板端子

6、10、46 オーミック電極端子

7、45 ゲート駆動用端子

8、42、44 ゲート端子

9A、9B、9C、9D、9E、9F ボンディングワイヤ

11、11A、11B、11C、11D、11E、11F、47、47A、47B、47C、47D、47E、47F、48、48A、48B、48C、48D、48E、48F、57A、57B、57C、57D、57E、57F、57G、57H、57I、58A、58B、58C、58D、58E、58F、58G、58H、58I ゲート駆動回路

12 負荷

13、28、111、111A、111B、471、471A、471B、481、481A、481B 直流電源

14 基準電位端子

15 出力端子

19 保護膜

20、21 窒化物半導体層

22 バッファ層

23 基板

26、27、32 p型窒化物半導体層

29、31 モータ

30 活性領域

60 交流電源

61 入力フィルタ

100、110、120、200、210、220、230 半導体装置

101、102、103、201、202、203 ハーフブリッジ

112、112A、112B、472、472A、472B、482、482A、482B ゲート回路

500 ドライブ回路

516 IGBT

551 パワーGND端子

552 センスGND端子

553 センス端子

567 パワーGND線

576 センスGND線

579 比較器

580 抵抗

581 基準電圧源

583 内部インダクタンス

584 抵抗

585 寄生インダクタンス

【技術分野】

【0001】

本発明は、電力変換を行う半導体装置に関し、特に窒化物半導体を用いた電流駆動型の半導体装置に関する。

【背景技術】

【0002】

地球温暖化問題を背景として、電気機器のさらなる省エネルギー化が期待されており、多くの電力を扱う電源回路やインバータ回路等の電力変換装置の電力変換効率を向上することが求められている。電力変換装置の電力変換効率を決定する最も大きな要因は、電力変換の際に用いられるIGBT(Insulated Gate Bipolar Transistor)やMOSFET(Metal Oxide Semiconductor Field Effect Transistor)等のパワー半導体素子における損失である。パワー半導体素子における損失を低減すれば、電力変換装置の電力変換効率を大きく向上させることができる。パワー半導体素子において発生する損失には、素子に電流が通電することで発生する導通損失と、素子がスイッチングする際に発生するスイッチング損失がある。導通損失については、よりオン抵抗の小さい素子を用いれば低減でき、スイッチング損失については、より高速にスイッチングする素子を用いれば低減できる。そのため、パワー半導体素子の高速スイッチング化及び低オン抵抗化が進められている。

【0003】

しかし、現在のパワー半導体素子は、シリコン(Si)を材料として作られており、Siの材料限界に到達しつつあるため、さらなるオン抵抗の低減及びスイッチング速度の向上が困難になってきている。Siの材料限界を打破して導通損失及びスイッチング損失を低減するために、窒化ガリウム(GaN)に代表される窒化物系半導体又は炭化珪素(SiC)等のいわゆるワイドバンドギャップ半導体素子の利用が検討されている。ワイドバンドギャップ半導体素子は絶縁破壊電界がSiに比べて約1桁高く、特に、窒化アルミニウムガリウム(AlGaN)と窒化ガリウム(GaN)とのヘテロ接合界面には自発分極及びピエゾ分極により電荷が生じる。これにより、アンドープ時においても1×1013cm-2以上のシートキャリア濃度と1000cm2V/sec以上の高移動度の2次元電子ガス(2DEG)層が形成される。このため、AlGaN/GaNヘテロ接合電界効果トランジスタ(以下GaNトランジスタと記載する)は、低オン抵抗及び高耐圧を実現するパワースイッチングトランジスタとして期待されている。

【0004】

GaNトランジスタは、潜在的な特性は従来のSiデバイスを遙かに上回る。例えば、GaNトランジスタは数十ns程度と非常に早い立ち上り・立ち下り時間を有し、数十から数百Aと大電流をスイッチングすることが可能である。しかし、高速・大電流スイッチングすることでチップとの接続ワイヤ、パッケージのリード、配線パターンの寄生インダクタンスLの影響を受け、ゲートにはL×di/dtによって決まる電圧ノイズが発生しゲートの誤点呼等ゲート誤動作の原因となる。よって、GaNトランジスタの高速・大電流スイッチング特性を活かすためには、ゲート誤動作を抑制する方法が必要不可欠である。

【0005】

図12は、特許文献1に記載された、従来のIGBTのドライブ回路を説明する回路構成図である。同図におけるドライブ回路は、過電流や温度上昇に対する保護機能を有する保護回路を含んでいる。上記ドライブ回路のパワー素子であるIGBT516が上記保護回路を経由したゲート電圧によりゲート誤動作をすることを抑制するために、上記ドライブ回路には、IGBT516の出力端子より分岐するパワーGND端子551と、センスGND端子552とが配置されている。ここで、パワーGND端子551は、ドレイン−ソース間を流れるドライブ電流の径路であるパワーラインの基準電位となる端子であり、センスGND端子は保護回路の入力端子における電圧を計測するための基準電位となる端子である。

【0006】

パワーGND端子551は、IGBT516をドライブしたときに流れるドライブ電流の電流経路上に配置される。一方、センスGND端子552は、IGBT516の動作状態を監視する保護回路のGNDレベルを規定する電流経路上に配置される。

【0007】

具体的には、保護回路は、過電流をモニタするためのセンス端子553の電圧と、基準電圧源581で規定される閾値電圧とを比較器579にて比較することにより、過電流保護の要否を判定している。よって、保護回路は、比較器579への入力電圧である上記両電圧を規定するためのセンスGND線576が必要となる。このため、センスGND線576は、パワー線から分岐した配線であって、パワーGND線567からインピーダンス(抵抗584)を介して接続されている。つまり、このパワーGND線567上に保護回路用のセンスGNDが別途設けられている。

【0008】

すなわち、センスGND端子552は、パワー素子が接続される側から見て保護回路が接続される配線パターンの位置よりも遠い位置で、インピーダンスを介してパワーGND線567に接続されている。これにより、パワー線の寄生インダクタンス585によりパワーGND線567に過渡的に発生した電圧は、そのインピーダンス(抵抗584)により抑制されるので、適正な保護回路の保護動作が担保され、IGBT516を含むドライブ回路は、安定した動作が得られるとしている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特許第3008924号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、特許文献1に記載されたドライブ回路では、IGBT516からのセンス電圧を正確にモニタするためのセンスGND線576及びセンスGND端子552を別途設ける必要がある。

【0011】

また、センスGND線576は、その終端部にインピーダンス(抵抗584)が接続されているとはいえ、パワーラインから分岐させたものであるため、パワーGND線567から完全に独立したものではない。従って、IGBT516のオンオフ切り換え時である過渡状態において発生する電圧ノイズは、センスGND線576の内部インダクタンス583によっても発生する可能性があり、上記センス電圧は、依然として電圧ノイズを含む可能性がある。

【0012】

特に、GaN(窒化ガリウム)やSiC(炭化珪素)といったワイドバンドギャップ半導体を用いた電流駆動型のスイッチングパワーデバイスでは、寄生容量が非常に小さい為、高速・大電流動作が可能である反面、ゲートの動作閾値電圧が1V程度と非常に低い。よって、特許文献1に記載されたドライブ回路を、特に、上述した低閾値電圧を有する電流駆動型のGaNやSiCパワーデバイスに適用した場合、上記電圧ノイズを厳しく抑制することが必要である。さもなければ、過渡状態において寄生インダクタンスの影響によりゲートあるいはゲート駆動回路に発生した電圧ノイズにより、誤点呼等、ゲートの誤動作が発生し、上記誤動作防止の効果が抑制されてしまう。

【0013】

さらに、上記保護回路に代表されるゲート駆動回路を複数構成し、パワー素子の出力電流を高精度または複雑に制御する場合、特許文献1に記載されたドライブ回路のように、ゲート駆動回路である保護回路の基準電位がパワーラインのGNDで規定されると、複数のゲート駆動回路を独立に動作させることが制限されてしまう。

【0014】

本発明は上記の課題に鑑み、電流駆動型の半導体装置のゲートあるいはゲート駆動回路への寄生インダクタンスによる外乱ノイズを低減し、ゲート駆動を高精度化及び安定化させることが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0015】

上記の課題を解決するために、本発明の一態様に係る半導体装置は、電力変換を行う電流駆動型の第1半導体素子と、前記第1半導体素子の電力変換を制御する第1ゲート駆動回路と、接続端子部とを備え、前記第1半導体素子は、基板の上に積層された窒化物半導体層の積層体と、前記積層体の上に形成されたゲート電極と、前記基板上であって、前記ゲート電極の両側方に形成された第1オーミック電極及び第2オーミック電極と、前記第1半導体素子上にあって、前記ゲート電極から配線されたゲート電極パッドと、前記第1半導体素子上にあって、前記第1オーミック電極及び前記第2オーミック電極からそれぞれ配線された第1オーミック電極パッド及び第2オーミック電極パッドとを有し、前記接続端子部は、第1の接続材により前記第1オーミック電極パッドと接続された第1オーミック電極端子と、第2の接続材により前記第2オーミック電極パッドと接続された第2オーミック電極端子と、第3の接続材により前記第1オーミック電極パッドと接続されたゲート駆動用端子と、第4の接続材により前記ゲート電極パッドと接続されたゲート端子とを有し、前記第1ゲート駆動回路の入力端子は、前記ゲート駆動用端子に接続され、前記第1ゲート駆動回路の出力端子は、前記ゲート端子に接続され、前記第1ゲート駆動回路の基準電位を前記第1オーミック電極パッドの電位とすることを特徴とする。

【0016】

上記構成をとることにより、第1半導体素子、第1オーミック電極パッド、第1の接続材、第1オーミック電極端子、外部電源及び負荷、第2オーミック電極端子、第2の接続材及び第2オーミック電極パッド、を流れるパワーラインの電流径路と、第1半導体素子、第1オーミック電極パッド、第3の接続材、ゲート駆動用端子、ゲート駆動用回路、ゲート端子、第4の接続材、ゲート電極パッド、を流れるゲート駆動ラインの電流径路とは、別個の電流径路を形成している。また、ゲート駆動回路の入力端子は、第3の接続材を介して第1オーミック電極パッドに電気接続されているので、当該第1オーミック電極パッドの電位が、電流駆動型のゲート駆動回路の基準電位となっている。

【0017】

本態様によれば、本発明の半導体装置は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路の接地端子を設ける必要がない。よって、第1半導体素子の過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路は、高精度及び安定なゲート駆動を実行することが可能となる。

【0018】

また、前記接続端子部は、さらに、前記第1半導体素子が接合された第1基板端子とを有し、前記ゲート駆動用端子は、前記第1基板端子と同一端子としてもよい。

【0019】

本態様によれば、窒化物半導体素子の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効である。

【0020】

また、さらに、前記第1半導体素子と同一の構造を有する第2半導体素子と、前記第1ゲート駆動回路と同一の構造を有する第2ゲート駆動回路とを備え、前記第2半導体素子と前記第2ゲート駆動回路との接続関係は、前記第1半導体素子と前記第1ゲート駆動回路との接続関係と同一であり、前記第1半導体素子の第1オーミック電極端子と、前記第2半導体素子の第2オーミック電極端子とが接続されることにより、前記第1半導体素子、前記第2半導体素子、前記第1ゲート駆動回路及び前記第2ゲート駆動回路は、第1のハーフブリッジを構成してもよい。

【0021】

本発明の一態様に係る半導体装置は、上記半導体素子とゲート駆動回路とを1ユニットとした構成を2ユニット直列接続したハーフブリッジに適用することが可能である。この構成においても、ゲート駆動回路は、高精度及び安定なゲート駆動を実行することが可能となる。

【0022】

また、さらに、前記第1のハーフブリッジと並列に接続された、前記第1のハーフブリッジと同一構成を有する第2のハーフブリッジを備え、単相モータを駆動するモータ駆動インバータを構成してもよい。

【0023】

本発明の一態様に係る半導体装置は、2つの並列接続された上記ハーフブリッジからなる単相駆動のインバータ回路に適用することが可能である。これにより、誤動作が低減された、安定した単相モータの駆動が実現される。

【0024】

また、さらに、前記第1のハーフブリッジと並列に接続された、前記第1のハーフブリッジと同一構成を有する第2のハーフブリッジ及び第3のハーフブリッジを備え、三相モータを駆動するモータ駆動インバータを構成してもよい。

【0025】

本発明の一態様に係る半導体装置は、3つの並列接続された上記ハーフブリッジからなる三相駆動のインバータ回路に適用することが可能である。これにより、誤動作が低減された、安定した三相モータの駆動が実現される。

【0026】

また、上記の課題を解決するために、本発明の一態様に係る半導体装置は、電力変換を行う電流駆動型の第3半導体素子と、前記第3半導体素子の電力変換を制御する第3ゲート駆動回路及び第4ゲート駆動回路と、接続端子部とを備え、前記第3半導体素子は、基板の上に積層された窒化物半導体層の積層体と、前記積層体の上に隣接して形成された第1ゲート電極及び第2ゲート電極と、前記基板上であって、前記第1ゲート電極及び前記第2ゲート電極の両側方に形成された第3オーミック電極及び第4オーミック電極と、前記第1半導体素子上にあって、前記第1ゲート電極及び前記第2ゲート電極からそれぞれ配線された第1ゲート電極パッド及び第2ゲート電極パッドと、前記第1半導体素子上にあって、前記第3オーミック電極及び前記第4オーミック電極からそれぞれ配線された第3オーミック電極パッド及び第4オーミック電極パッドとを有し、前記接続端子部は、第1の接続材により前記第3オーミック電極パッドと接続された第3オーミック電極端子と、第2の接続材により前記第4オーミック電極パッドと接続された第4オーミック電極端子と、第3の接続材により前記第3オーミック電極パッドと接続された第1ゲート駆動用端子と、第4の接続材により前記第4オーミック電極パッドと接続された第2ゲート駆動用端子と、第5の接続材により前記第1ゲート電極パッドと接続された第1ゲート端子と、第6の接続材により前記第2ゲート電極パッドと接続された第2ゲート端子とを有し、前記第3ゲート駆動回路の入力端子は、前記第1ゲート駆動用端子に接続され、前記第3ゲート駆動回路の出力端子は、前記第1ゲート端子に接続され、前記第3ゲート駆動回路の基準電位を前記第3オーミック電極パッドの電位とし、前記第4ゲート駆動回路の入力端子は、前記第2ゲート駆動用端子に接続され、前記第4ゲート駆動回路の出力端子は、前記第2ゲート端子に接続され、前記第4ゲート駆動回路の基準電位を前記第4オーミック電極パッドの電位とすることを特徴とする。

【0027】

上記構成をとることにより、ダブルゲート型の第3半導体素子、第3オーミック電極パッド、第1の接続材、第3オーミック電極端子、外部電源及び負荷、第4オーミック電極端子、第2の接続材及び第4オーミック電極パッド、を流れるパワーラインの電流径路と、第3半導体素子、第3オーミック電極パッド、第3の接続材、第1ゲート駆動用端子、第3ゲート駆動用回路、第1ゲート端子、第5の接続材、第1ゲート電極パッド、を流れる第1ゲート駆動ラインの電流径路とは、別個の電流径路を形成している。また、上記パワーラインの電流径路と、第3半導体素子、第4オーミック電極パッド、第4の接続材、第2ゲート駆動用端子、第4ゲート駆動用回路、第2ゲート端子、第6の接続材、第2ゲート電極パッド、を流れる第2ゲート駆動ラインの電流径路とは、別個の電流径路を形成している。また、第3ゲート駆動回路の入力端子は、第3の接続材を介して第3オーミック電極パッドに電気接続されているので、当該第3オーミック電極パッドの電位が、電流駆動型の第3ゲート駆動回路の基準電位となっている。また、第4ゲート駆動回路の入力端子は、第4の接続材を介して第4オーミック電極パッドに電気接続されているので、当該第4オーミック電極パッドの電位が、電流駆動型の第4ゲート駆動回路の基準電位となっている。

【0028】

本態様によれば、本発明の半導体装置は、上記パワーライン及び上記第1及び第2ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、第3半導体素子の過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、第3及び第4ゲート駆動回路は、高精度及び安定なゲート駆動を実行することが可能となる。

【0029】

また、さらに、前記第3半導体素子と同一の構造を有する第4半導体素子と、前記第3ゲート駆動回路と同一の構造を有する第5ゲート駆動回路と、前記第4ゲート駆動回路と同一の構造を有する第6ゲート駆動回路とを備え、前記第4半導体素子と前記第5ゲート駆動回路との接続関係は、前記第3半導体素子と前記第3ゲート駆動回路との接続関係と同一であり、前記第4半導体素子と前記第6ゲート駆動回路との接続関係は、前記第3半導体素子と前記第4ゲート駆動回路との接続関係と同一であり、前記第3半導体素子の第3オーミック電極端子と、前記第4半導体素子の第4オーミック電極端子とが接続されることにより、前記第3半導体素子、前記第4半導体素子、前記第3ゲート駆動回路、前記第4ゲート駆動回路、前記第5ゲート駆動回路及び前記第6ゲート駆動回路は、第4のハーフブリッジを構成してもよい。

【0030】

本発明の一態様に係る半導体装置は、上記ダブルゲート型の半導体素子と2つのゲート駆動回路とを1ユニットとした構成を2ユニット直列接続したハーフブリッジに適用することが可能である。この構成においても、第3及び第4ゲート駆動回路は、高精度及び安定なゲート駆動を実行することが可能となる。

【0031】

また、さらに、前記第4のハーフブリッジと並列に接続された、前記第4のハーフブリッジと同一構成を有する第5のハーフブリッジを備え、単相モータを駆動するモータ駆動インバータを構成してもよい。

【0032】

本発明の一態様に係る半導体装置は、2つの並列接続された上記ハーフブリッジからなる単相駆動のインバータ回路に適用することが可能である。これにより、誤動作が低減された、安定した単相モータの駆動が実現される。

【0033】

また、さらに、前記第4のハーフブリッジと並列に接続された、前記第4のハーフブリッジと同一構成を有する第5のハーフブリッジ及び第6のハーフブリッジを備え、三相モータを駆動するモータ駆動インバータを構成してもよい。

【0034】

本発明の一態様に係る半導体装置は、3つの並列接続された上記ハーフブリッジからなる三相駆動のインバータ回路に適用することが可能である。これにより、誤動作が低減された、安定した三相モータの駆動が実現される。

【0035】

また、さらに、前記第3半導体素子と同一の構造を有する第4半導体素子〜第11半導体素子を備え、前記第4半導体素子〜第11半導体素子のそれぞれは、前記第3ゲート駆動回路と同一の構造を有するゲート駆動回路と接続され、かつ、前記第4ゲート駆動回路と同一の構造を有するゲート駆動回路と接続されており、前記第3半導体素子、前記第6半導体素子及び前記第9半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第1出力端子に接続され、前記第4半導体素子、前記第7半導体素子及び前記第10半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第2出力端子に接続され、前記第5半導体素子、前記第8半導体素子及び前記第11半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第3出力端子に接続され、前記第3半導体素子、前記第4半導体素子及び前記第5半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第1入力端子に接続され、前記第6半導体素子、前記第7半導体素子及び前記第8半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第2入力端子に接続され、前記第9半導体素子、前記第10半導体素子及び前記第11半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第3入力端子に接続されており、三相モータを駆動するモータ駆動マトリクスコンバータを構成してもよい。

【0036】

本発明の一態様に係る半導体装置は、上記ダブルゲート型の半導体素子と2つのゲート駆動回路とを1ユニットとした構成をマトリクス状に配置した三相駆動のマトリクスコンバータ回路に適用することが可能である。入力電源が交流の場合、駆動システムの基準電位が変動するので、各ユニットの基準電位は、駆動システムの基準電位とせずに、任意の基準電位とすることが好ましい。本構成によれば、各ユニットの基準電位は、電流駆動型のソースパッドである第3オーミック電極パッドまたは第4オーミック電極パッドとしているので、半導体装置の基準電位と合わせる必要がなく、複数のゲート駆動回路を独立に動作させることが可能となる。

【発明の効果】

【0037】

本発明の半導体装置によれば、パワーラインの電流径路とゲート駆動ラインの電流径路とを別個の電流径路とし、ゲート駆動回路の基準電位を電流駆動型の半導体素子のソースパッド電位とし、且つゲート駆動用端子電位とすることにより、寄生インダクタンスにより発生する外乱ノイズを低減することができる。

【図面の簡単な説明】

【0038】

【図1】(a)は、本発明の実施の形態1に係る半導体装置の結線を説明する上面図である。(b)は、本発明の実施の形態1に係る半導体装置の要部における等価回路図である。

【図2】(a)は、本発明の実施の形態1に係る半導体素子の上面図である。(b)は、図2(a)に記載された半導体素子のX−X’における断面図である。(c)は、図2(a)に記載された半導体素子のY−Y’における断面図である。

【図3】本発明の実施の形態2に係る半導体装置を含む回路構成図である。

【図4】本発明の実施の形態2に係るハーフブリッジの要部における等価回路図である。

【図5】本発明の実施の形態2に係る変形例を示す半導体装置を含む回路構成図である。

【図6】(a)は、本発明の実施の形態3に係る半導体装置の結線を説明する上面図である。(b)は、本発明の実施の形態3に係る半導体装置の要部における等価回路図である。

【図7】(a)は、本発明の実施の形態3に係る半導体素子の上面図である。(b)は、図7(a)に記載された半導体素子のX−X’における断面図である。(c)は、図7(a)に記載された半導体素子のY−Y’における断面図である。

【図8】本発明の実施の形態4に係る半導体装置を含む回路構成図である。

【図9】本発明の実施の形態4に係るハーフブリッジの要部における等価回路図である。

【図10】本発明の実施の形態4に係る第1の変形例を示す半導体装置を含む回路構成図である。

【図11】本発明の実施の形態4に係る第2の変形例を示す半導体装置を含む回路構成図である。

【図12】特許文献1に記載された、従来のIGBTのドライブ回路を説明する回路構成図である。

【発明を実施するための形態】

【0039】

以下、本発明の半導体装置の実施の形態について、図面を参照しながら説明する。

【0040】

(実施の形態1)

図1(a)は、本発明の実施の形態1に係る半導体装置の結線を説明する上面図である。同図に記載された半導体装置100は、第1半導体素子である半導体素子3と、接続材である複数のボンディングワイヤ9A〜9Dと、ゲート駆動回路11とを備える。また、半導体装置100上には、第1基板端子である基板端子4と、第1オーミック電極端子であるオーミック電極端子6及び第2オーミック電極端子であるオーミック電極端子10と、ゲート駆動用端子7と、ゲート端子8とが、互いに分離されて配置されており、これらは接続端子部を構成している。また、半導体素子3は、基板端子4上に接合され、半導体素子3上には、ゲート電極パッド1と、第1オーミック電極パッドであるオーミック電極パッド2及び第2オーミック電極パッドであるオーミック電極パッド5とが、互いに分離されて配置されている。

【0041】

オーミック電極パッド5は、ボンディングワイヤ9Aを介して、オーミック電極端子10に電気接続されている。また、オーミック電極パッド2は、ボンディングワイヤ9Dを介して、オーミック電極端子6に電気接続されており、別途、ボンディングワイヤ9Cを介して、ゲート駆動用端子7にも電気接続されている。また、ゲート電極パッド1は、ボンディングワイヤ9Bを介して、ゲート端子8に電気接続されている。ボンディングワイヤ9A〜9Dは、例えば、Alからなる。

【0042】

オーミック電極端子10は、負荷12の一方の端子に電気接続され、オーミック電極端子6は直流電源13の負極に電気接続されている。また、負荷12の他方の端子は、直流電源13の正極に電気接続されている。上記接続により、半導体素子3、半導体素子3上に配置されたオーミック電極パッド2、ボンディングワイヤ9D、オーミック電極端子6、直流電源13、負荷12、オーミック電極端子10、ボンディングワイヤ9A、及びオーミック電極パッド5は、半導体素子3のドレイン電流が流れるパワーラインを構成している。

【0043】

ゲート駆動回路11は、出力端子15、入力端子である基準電位端子14、及びゲート駆動回路駆動用の直流電源(図示せず)を有する。出力端子15はゲート端子8へ電気接続され、基準電位端子14はゲート駆動用端子7へ電気接続されている。上記接続により、半導体素子3、オーミック電極パッド2、ボンディングワイヤ9C、ゲート駆動用端子7、ゲート駆動回路11、ゲート端子8、ボンディングワイヤ9B、及びゲート電極パッド1は、ゲート駆動ラインを構成している。つまり、ゲート駆動回路11は、半導体素子3のゲート−ソース間抵抗により決定されるゲート−ソース間電流をオーミック電極パッド2、ボンディングワイヤ9C及びゲート駆動用端子7を介して入力し、この入力電流により、半導体素子3の電力変換を制御するための、ゲートに供給する電気信号を決定する第1ゲート駆動回路である。

【0044】

図1(b)は、本発明の実施の形態1に係る半導体装置の要部における等価回路図である。ゲート駆動回路11は、直流電源111とゲート回路112とを備えた電流駆動型の回路である。ゲート回路112の電源端子Vddには直流電源111の正極が電気接続され、ゲート回路112の基準電位端子GNDには直流電源111の負極が電気接続されている。この場合、図1(a)により説明した上記パワーラインと、上記ゲート駆動ラインとは、別個の電流ラインを形成している。また、ゲート駆動回路11の基準電位端子14は、ボンディングワイヤ9Cを介してオーミック電極パッド2に電気接続されているので、このオーミック電極パッド2の電位が、電流駆動型のゲート駆動回路11の基準電位となっている。

【0045】

これにより、半導体装置100は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、半導体素子3の過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路11は、高精度及び安定なゲート駆動を実行することが可能となる。

【0046】

なお、上記構成では、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位としており、オーミック電極パッド2の電位を半導体装置100のGND電位とは独立に設定することが可能であるが、ゲート駆動回路11の用途及び構成により、オーミック電極パッド2の電位を半導体装置100のGND電位としてもよい。この場合においても、上記構成により得られた効果と同様の効果を奏することが可能となる。また、半導体装置100の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効である。

【0047】

図2(a)は、本発明の実施の形態1に係る半導体素子の上面図である。また、図2(b)は、図2(a)に記載された半導体素子のX−X’における断面図である。また、図2(c)は、図2(a)に記載された半導体素子のY−Y’における断面図である。図2(a)に記載された、半導体素子3は、例えば、AlGaN/GaNのヘテロ接合からなる二次元電子ガス(2DEG)をチャネルとして用いた窒化物半導体素子である。

【0048】

図2(a)、図2(b)及び図2(c)に記載されたように、半導体素子3には、基板23上にバッファ層22、窒化物半導体層21、窒化物半導体層20、p型窒化物半導体層26が順次積層され、ゲート電極1A、オーミック電極2A及び5Aが形成され、保護膜19が形成されている。バッファ層22、窒化物半導体層21、窒化物半導体層20、p型窒化物半導体層26は、窒化物半導体層の積層体を形成している。オーミック電極パッド5は、第2オーミック電極であるオーミック電極5Aに接続され、オーミック電極パッド2は第1オーミック電極であるオーミック電極2Aに接続され、ゲート電極パッド1は、ゲート配線1Bを介してゲート電極1Aに接続され、それぞれ、保護膜19の開口部に形成されている。また、オーミック電極5A、オーミック電極2A及びゲート電極1Aは、活性領域30にて、図2(a)に示されたようなフィンガー形状を構成している。つまり、オーミック電極5Aと2Aとの間に、ゲート電極1Aが配置されている。上記構成の半導体素子3は、例えば、図1(a)に記載された直流電源13の電圧値が300Vであって、10A程度のパワーラインを流れる電流をオンオフさせるスイッチング素子である。

【0049】

図2(a)、図2(b)及び図2(c)に記載されたような窒化物半導体素子は、各端子間の寄生容量が数十pF〜数百pFと非常に小さいため、MOSFETやIGBTに比べて、数十ns〜数百nsレベルの高速スイッチングが可能である。しかし、上記スイッチングが高速であればある程、ワイヤやリード、配線パターン等の寄生インダクタンスLとdi/dtとの積である電圧ノイズが発生する。前述したように、この電圧ノイズは、ゲート駆動において誤点呼といった誤動作を引き起こすため、低減する必要がある。

【0050】

上記電圧ノイズを低減するために、図1(a)に記載したように、具体的には、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位としている。そして、オーミック電極パッド2からボンディングワイヤ9Dを介したオーミック電極端子6への電流経路と、オーミック電極パッド2からボンディングワイヤ9Dを介したゲート駆動用端子7への電流径路とを分離することで、大電流用のパワーループとゲート駆動回路11用のゲート駆動ループとを分離することを可能としている。この構成により、ゲート駆動回路11への外乱ノイズとなる上記電圧ノイズを低減することが可能となる。

【0051】

なお、図2(a)、図2(b)及び図2(c)に記載された窒化物半導体素子は、ショットキーゲート電極を用いたMESFETでもよい。

【0052】

また、各電極パッドと電極とを接続する接続材としては、ボンディングワイヤ以外にもAlリボンやCu製のクリップ材料であってもよい。

【0053】

また、半導体装置100の回路構成によっては、オーミック電極パッド2を基板23へ接続することで、基板端子4をゲート駆動用端子7としてもよい。こうすることで窒化物半導体素子の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効な手段となる。

【0054】

(実施の形態2)

図3は、本発明の実施の形態2に係る半導体装置を含む回路構成図である。同図に記載された駆動システムは、単相インバータ回路によりモータを駆動するシステムであり、直流電源28と、半導体装置110とモータ29とを備える。

【0055】

半導体装置110は、第1のハーフブリッジであるハーフブリッジ101及び第2のハーフブリッジであるハーフブリッジ102を備える。ハーフブリッジ101とハーフブリッジ102とは同一構成であり、それぞれ、実施の形態1に記載された半導体装置100の構成を有している。つまり、図3に記載された半導体素子3A、3B、3C及び3Dは、それぞれ、図1に記載された半導体素子3と同じ構成である。また、図3に記載されたゲート駆動回路11A、11B、11C及び11Dは、それぞれ、図1に記載されたゲート駆動回路11と同じ構成である。また、ハーフブリッジ101とハーフブリッジ102とは、並列接続されている。ハーフブリッジ101の有する第1半導体素子である半導体素子3A及び第2半導体素子である3Bの中点とモータ29の一方の端子とが電気接続され、ハーフブリッジ102の有する半導体素子3C及び3Dの中点とモータ29の他方の端子とが電気接続されている。ここで、第1ゲート駆動回路であるゲート駆動回路11A及び11C、つまり、ハイサイドの基準電位端子14を、例えば、上述した各々の中点に接続し、第2ゲート駆動回路であるゲート駆動回路11B及び11D、つまり、ローサイドの基準電位端子14を、例えば、半導体装置110のGNDに接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0056】

図4は、本発明の実施の形態2に係るハーフブリッジの要部における等価回路図である。ゲート駆動回路11Aは、直流電源111Aとゲート回路112Aとを備えた電流駆動型の第1ゲート駆動回路である。ゲート回路112Aの電源端子Vddには直流電源111Aの正極が電気接続され、ゲート回路112Aの基準電位端子GNDには直流電源111Aの負極が電気接続されている。この場合、図3に記載された、直流電源28、オーミック電極端子10、半導体素子3A、オーミック電極端子6、及びモータ29とで構成されるパワーラインと、直流電源111A、ゲート回路112A、ゲート端子8、半導体素子3A、ゲート駆動用端子7とで構成されるゲート駆動ラインとは、別個の電流ラインを形成している。また、ゲート駆動回路11Aの基準電位端子14は、ボンディングワイヤ9Cを介してオーミック電極パッド2に電気接続されているので、このオーミック電極パッド2の電位が、電流駆動型のゲート駆動回路11の基準電位となっている。

【0057】

また、ゲート駆動回路11B、11C及び11Dにおいても、上述したゲート駆動回路11Aと同様の構成となっている。

【0058】

これにより、半導体装置110は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、半導体素子3A〜3Dの過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路11A〜11Dは、高精度及び安定なゲート駆動を実行することが可能となる。

【0059】

図5は、本発明の実施の形態2に係る変形例を示す半導体装置を含む回路構成図である。同図に記載された駆動システムは、三相インバータ回路によりモータを駆動するシステムであり、直流電源28と、半導体装置120とモータ31とを備える。

【0060】

半導体装置120は、ハーフブリッジ101、102及び第3のハーフブリッジであるハーフブリッジ103を備える。ハーフブリッジ101、102及び103は同一構成であり、それぞれ、実施の形態1に記載された半導体装置100の構成を有している。つまり、図5に記載された半導体素子3A、3B、3C、3D、3E及び3Fは、それぞれ、図1に記載された半導体素子3と同じ構成である。また、図5に記載されたゲート駆動回路11A、11B、11C、11D、11E及び11Fは、それぞれ、図1に記載されたゲート駆動回路11と同じ構成である。また、ハーフブリッジ101、102及び103は、互いに並列接続されている。ハーフブリッジ101の有する半導体素子3A及び3Bの中点とモータ31の第1の端子とが電気接続され、ハーフブリッジ102の有する半導体素子3C及び3Dの中点とモータ31の第2の端子とが電気接続され、ハーフブリッジ103の有する半導体素子3E及び3Fの中点とモータ31の第3の端子とが電気接続されている。ここで、ゲート駆動回路11A、11C、及び11E、つまり、ハイサイドの基準電位端子14を、例えば、上述した各々の中点に接続し、ゲート駆動回路11B、11D及び11F、つまり、ローサイドの基準電位端子14を、例えば、半導体装置110のGNDに接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0061】

(実施の形態3)

本実施の形態では、ダブルゲート型の半導体素子を有する半導体装置について、本発明を適用した場合の構成及び効果を、図面を用いて説明する。つまり、半導体素子のドレイン電流を、当該ドレイン−ソース間に配置された2つのゲート電極を独立に制御することにより、高精度または複雑に制御することが可能となる。

【0062】

図6(a)は本発明の実施の形態3に係る半導体装置の結線を説明する上面図である。同図に記載された半導体装置200は、第3半導体素子である半導体素子40と、接続材である複数のボンディングワイヤ9A〜9Fと、第4ゲート駆動回路であるゲート駆動回路47及び第3ゲート駆動回路であるゲート駆動回路48とを備える。また、半導体装置200上には、基板端子4と、第3オーミック電極端子であるオーミック電極端子6及び第4オーミック電極端子であるオーミック電極端子46と、第1ゲート駆動用端子であるゲート駆動用端子7及び第2ゲート駆動用端子であるゲート駆動用端子45と、第1ゲート端子であるゲート端子42及び第2ゲート端子であるゲート端子44とが、互いに分離されて配置されている。また、半導体素子40は、基板端子4上に接合され、半導体素子40上には、第1ゲート電極パッドであるゲート電極パッド41及び第2ゲート電極パッドであるゲート電極パッド43と、第3オーミック電極パッドであるオーミック電極パッド2及び第4オーミック電極パッドであるオーミック電極パッド5とが、互いに分離されて配置されている。

【0063】

オーミック電極パッド5は、ボンディングワイヤ9Aを介して、オーミック電極端子46に電気接続されており、別途、ボンディングワイヤ9Eを介して、ゲート駆動用端子45にも電気接続されている。また、オーミック電極パッド2は、ボンディングワイヤ9Dを介して、オーミック電極端子6に電気接続されており、別途、ボンディングワイヤ9Cを介して、ゲート駆動用端子7にも電気接続されている。また、ゲート電極パッド41は、ボンディングワイヤ9Bを介して、ゲート端子42に電気接続され、ゲート電極パッド43は、ボンディングワイヤ9Fを介して、ゲート端子44に電気接続されている。ボンディングワイヤ9A〜9Fは、例えば、Alからなる。

【0064】

オーミック電極端子46は、負荷12の一方の端子に電気接続され、オーミック電極端子6は直流電源13の負極に電気接続されている。また、負荷12の他方の端子は、直流電源13の正極に電気接続されている。上記接続により、半導体素子40、半導体素子40上に配置されたオーミック電極パッド2、ボンディングワイヤ9D、オーミック電極端子6、直流電源13、負荷12、オーミック電極端子46、ボンディングワイヤ9A、及びオーミック電極パッド5は、パワーラインを構成している。

【0065】

ゲート駆動回路48は、出力端子15、入力端子である基準電位端子14、及びゲート駆動回路駆動用の直流電源(図示せず)を有する。出力端子15はゲート端子42へ電気接続され、基準電位端子14はゲート駆動用端子7へ電気接続されている。上記接続により、半導体素子40、オーミック電極パッド2、ボンディングワイヤ9C、ゲート駆動用端子7、ゲート駆動回路48、ゲート端子42、ボンディングワイヤ9B、及びゲート電極パッド41は、ゲート駆動ラインを構成している。つまり、ゲート駆動回路48は、半導体素子40のゲート−ソース間抵抗により決定されるゲート−ソース間電流をオーミック電極パッド2、ボンディングワイヤ9C及びゲート駆動用端子7を介して入力し、この入力電流により、半導体素子40の電力変換を制御するための、ゲートに供給する電気信号を決定する。

【0066】

ゲート駆動回路47は、ゲート駆動回路48と同様の構成を有する。ゲート駆動回路47の接続により、半導体素子40、オーミック電極パッド5、ボンディングワイヤ9E、ゲート駆動用端子45、ゲート駆動回路47、ゲート端子44、ボンディングワイヤ9F、及びゲート電極パッド43は、ゲート駆動ラインを構成している。つまり、ゲート駆動回路47は、半導体素子40のゲート−ドレイン間抵抗により決定されるゲート−ドレイン間電流をオーミック電極パッド5、ボンディングワイヤ9E及びゲート駆動用端子45を介して入力し、この入力電流により、半導体素子40の電力変換を制御するための、ゲートに供給する電気信号を決定する。

【0067】

図6(b)は、本発明の実施の形態3に係る半導体装置の要部における等価回路図である。ゲート駆動回路47は、直流電源471とゲート回路472とを備えた電流駆動型の回路である。ゲート回路472の電源端子Vddには直流電源471の正極が電気接続され、ゲート回路472の基準電位端子GNDには直流電源471の負極が電気接続されている。この場合、図6(a)により説明したパワーラインと、ゲート駆動ラインとは、別個の電流ラインを形成している。また、ゲート駆動回路47の基準電位端子14は、ボンディングワイヤ9Eを介してオーミック電極パッド5に電気接続されているので、このオーミック電極パッド5の電位が、電流駆動型のゲート駆動回路47の基準電位となっている。

【0068】

また、ゲート駆動回路48は、直流電源481とゲート回路482とを備えた電流駆動型の回路である。ゲート回路482の電源端子Vddには直流電源481の正極が電気接続され、ゲート回路482の基準電位端子GNDには直流電源481の負極が電気接続されている。この場合、図6(a)により説明したパワーラインと、ゲート駆動ラインとは、別個の電流ラインを形成している。また、ゲート駆動回路48の基準電位端子14は、ボンディングワイヤ9Cを介してオーミック電極パッド2に電気接続されているので、このオーミック電極パッド2の電位が、電流駆動型のゲート駆動回路48の基準電位となっている。

【0069】

これにより、半導体装置200は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、半導体素子40の過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路47及び48は、それぞれ独立に、高精度及び安定なゲート駆動を実行することが可能となる。

【0070】

なお、上記構成では、ゲート駆動回路47の基準電位とゲート駆動回路48の基準電位とを、それぞれ、オーミック電極パッド5及び2の電位としており、オーミック電極パッド5及び2の電位を半導体装置200のGND電位とは独立に設定することが可能であるが、ゲート駆動回路47及び48の用途及び構成により、オーミック電極パッド2の電位を半導体装置200のGND電位としてもよい。この場合においても、上記構成により得られた効果と同様の効果を奏することが可能となる。また、半導体装置200の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効である。

【0071】

図7(a)は、本発明の実施の形態3に係る半導体素子の上面図である。また、図7(b)は、図7(a)に記載された半導体素子のX−X’における断面図である。また、図7(c)は、図7(a)に記載された半導体素子のY−Y’における断面図である。図7(a)に記載された、半導体素子40は、例えば、AlGaN/GaNのヘテロ接合からなる二次元電子ガス(2DEG)をチャネルとして用いた窒化物半導体素子である。

【0072】

図7(a)、図7(b)及び図7(c)に記載されたように、半導体素子40には、基板23上にバッファ層22、窒化物半導体層21、窒化物半導体層20、p型窒化物半導体層27及び32が順次積層され、ゲート電極41A及び43A、オーミック電極2A及び5Aが形成され、保護膜19が形成されている。バッファ層22、窒化物半導体層21、窒化物半導体層20、p型窒化物半導体層27及び32は、窒化物半導体層の積層体を形成している。オーミック電極パッド2及び5は、それぞれ、第3オーミック電極であるオーミック電極2A及び第4オーミック電極であるオーミック電極5Aに接続されている。また、ゲート電極パッド41及び43は、それぞれ、ゲート配線41B及び43Bを介して第1ゲート電極であるゲート電極41A及び第2ゲート電極であるゲート電極43Aに接続され、それぞれ、保護膜19の開口部に形成されている。また、オーミック電極2A、5A、ゲート電極41A及び43Aは、活性領域30にて、図7(a)に示されたようなフィンガー形状を構成している。つまり、オーミック電極5Aと2Aとの間に、ゲート電極41A及び43Aが、この順で配置されている。上記構成の半導体素子40は、例えば、図6(a)に記載された直流電源13の電圧値が300Vであって、10A程度のパワーラインを流れる電流をオンオフさせるスイッチング素子である。

【0073】

図7(a)、図7(b)及び図7(c)に記載されたような窒化物半導体素子は、各端子間の寄生容量が数十pF〜数百pFと非常に小さいため、MOSFETやIGBTに比べて数十ns〜数百nsと高速でスイッチングすることが可能である。しかし、上記スイッチングが、高速であればある程、ワイヤやリード、配線パターン等の寄生インダクタンスLとdi/dtとの積である電圧ノイズが発生する。前述したように、この電圧ノイズは、ゲート駆動において誤点呼といった誤動作を引き起こすため、低減する必要がある。

【0074】

上記電圧ノイズを低減するために、図6(a)に記載したように、具体的には、ゲート駆動回路47及び48の基準電位を、それぞれ、オーミック電極パッド5及び2の電位としている。そして、オーミック電極パッド5からボンディングワイヤ9Aを介したオーミック電極端子46への電流経路と、オーミック電極パッド5からボンディングワイヤ9Aを介したゲート駆動用端子45への電流径路とを分離することで、大電流用のパワーループとゲート駆動回路47用のゲート駆動ループとを分離することを可能としている。オーミック電極パッド2における同様の接続により、大電流用のパワーループとゲート駆動回路48用のゲート駆動ループとを分離することを可能としている。この構成により、ゲート駆動回路47及び48への外乱ノイズとなる上記電圧ノイズを低減することが可能となる。

【0075】

なお、図7(a)、図7(b)及び図7(c)に記載された窒化物半導体素子は、ショットキーゲート電極を用いたMESFETでもよい。

【0076】

また、各電極パッドと電極とを接続する接続材としては、ボンディングワイヤ以外にもAlリボンやCu製のクリップ材料であってもよい。

【0077】

また、半導体装置200の回路構成によっては、オーミック電極パッド2を基板23へ接続することで、基板端子4をゲート駆動用端子7としてもよい。こうすることで窒化物半導体素子の基板電位を安定化させることが可能となり、外乱ノイズ対策として極めて有効な手段となる。

【0078】

(実施の形態4)

図8は、本発明の実施の形態4に係る半導体装置を含む回路構成図である。同図に記載された駆動システムは、単相インバータ回路によりモータを駆動するシステムであり、直流電源28と、半導体装置210とモータ29とを備える。

【0079】

半導体装置210は、第4のハーフブリッジであるハーフブリッジ201及び第5のハーフブリッジであるハーフブリッジ202を備える。ハーフブリッジ201とハーフブリッジ202とは同一構成であり、それぞれ、実施の形態3に記載されたダブルゲート型の半導体装置200の構成を有している。つまり、図8に記載された半導体素子40A、40B、40C及び40Dは、それぞれ、図6に記載された半導体素子40と同じ構成である。また、図8に記載された、第4ゲート駆動回路であるゲート駆動回路47A、第6ゲート駆動回路である47B、第4ゲート駆動回路である47C及び第6ゲート駆動回路である47Dは、それぞれ、図6に記載されたゲート駆動回路47と同じ構成である。また、図8に記載された、第3ゲート駆動回路であるゲート駆動回路48A、第5ゲート駆動回路である48B、第3ゲート駆動回路である48C及び第5ゲート駆動回路である48Dは、それぞれ、図6に記載されたゲート駆動回路48と同じ構成である。また、ハーフブリッジ201とハーフブリッジ202とは、並列接続されている。ハーフブリッジ201の有する第3半導体素子である半導体素子40A及び第4半導体素子である40Bの中点とモータ29の一方の端子とが電気接続され、ハーフブリッジ202の有する第3半導体素子である半導体素子40C及び第4半導体素子である40Dの中点とモータ29の他方の端子とが電気接続されている。

【0080】

ここで、ゲート駆動回路48A及び48Cの基準電位端子14を、例えば、上述した各々の中点に接続し、ゲート駆動回路47A及び47Cの基準電位端子14を、例えば、直流電源28の正極に電気接続し、ゲート駆動回路48B及び48Dの基準電位端子14を、例えば、半導体装置210の接地端子に電気接続し、ゲート駆動回路47B及び47Dの基準電位端子14を例えば、上述した各々の中点に接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0081】

図9は、本発明の実施の形態4に係るハーフブリッジの要部における等価回路図である。ゲート駆動回路47Aは、直流電源471Aとゲート回路472Aとを備えた電流駆動型の回路である。ゲート回路472Aの電源端子Vddには直流電源471Aの正極が電気接続され、ゲート回路472Aの基準電位端子GNDには直流電源471Aの負極が電気接続されている。また、ゲート駆動回路48Aは、直流電源481Aとゲート回路482Aとを備えた電流駆動型の回路である。ゲート回路482Aの電源端子Vddには直流電源481Aの正極が電気接続され、ゲート回路482Aの基準電位端子GNDには直流電源481Aの負極が電気接続されている。

【0082】

この場合、図8に記載された、直流電源28、オーミック電極端子46、半導体素子40A、オーミック電極端子6、及びモータ29とで構成されるパワーラインと、直流電源471A、ゲート回路472A、ゲート端子44、半導体素子40A、ゲート駆動用端子45とで構成されるゲート駆動ラインとは、別個の電流ラインを形成している。同様に、上記パワーラインと、直流電源481A、ゲート回路482A、ゲート端子42、半導体素子40A、ゲート駆動用端子7とで構成されるゲート駆動ラインとは、別個の電流ラインを形成している。

【0083】

また、ゲート駆動回路47Aの基準電位端子14は、ボンディングワイヤ9Eを介してオーミック電極パッド5に電気接続されているので、このオーミック電極パッド5の電位が、電流駆動型のゲート駆動回路47Aの基準電位となっている。

【0084】

また、ゲート駆動回路48Aの基準電位端子14は、ボンディングワイヤ9Cを介してオーミック電極パッド2に電気接続されているので、このオーミック電極パッド2の電位が、電流駆動型のゲート駆動回路48Aの基準電位となっている。

【0085】

また、ゲート駆動回路47B、47C及び47Dにおいても、上述したゲート駆動回路47Aと同様の構成となっている。

【0086】

また、ゲート駆動回路48B、48C及び48Dにおいても、上述したゲート駆動回路48Aと同様の構成となっている。

【0087】

これにより、半導体装置210は、上記パワーライン及び上記ゲート駆動ラインの他経路に、別途ゲート駆動回路のGND端子を設ける必要がない。また、上記ゲート駆動ラインは、半導体素子40A〜40Dの過渡状態における、上記パワーラインの寄生インダクタンスにより発生する電圧ノイズの影響を受けることがないので、ゲート駆動回路47A〜47D及びゲート駆動回路48A〜48Dは、高精度及び安定なゲート駆動を実行することが可能となる。

【0088】

図10は、本発明の実施の形態4に係る第1の変形例を示す半導体装置を含む回路構成図である。同図に記載された駆動システムは、三相インバータ回路によりモータを駆動するシステムであり、直流電源28と、半導体装置220とモータ31とを備える。

【0089】

半導体装置220は、ハーフブリッジ201、202及び第6のハーフブリッジであるハーフブリッジ203を備える。ハーフブリッジ201、202及び203は同一構成であり、それぞれ、実施の形態3に記載されたダブルゲート型の半導体装置200の構成を有している。つまり、図10に記載された半導体素子40A、40B、40C、40D、40E及び40Fは、それぞれ、図6に記載された半導体素子40と同じ構成である。また、図10に記載されたゲート駆動回路47A、47B、47C、47D、47E及び47Fは、それぞれ、図6に記載されたゲート駆動回路47と同じ構成である。また、ハーフブリッジ201、202及び203は、互いに並列接続されている。ハーフブリッジ201の有する半導体素子40A及び40Bの中点とモータ31の第1の端子とが電気接続され、ハーフブリッジ202の有する半導体素子40C及び40Dの中点とモータ31の第2の端子とが電気接続され、ハーフブリッジ203の有する半導体素子40E及び40Fの中点とモータ31の第3の端子とが電気接続されている。

【0090】

ここで、ゲート駆動回路48A、48C及び48Eの基準電位端子14を、例えば、それぞれのハーフブリッジにおける上記中点に接続し、ゲート駆動回路47A、47C及び47Eの基準電位端子14を、例えば、直流電源28の正極に電気接続し、ゲート駆動回路48B、48D及び48Fの基準電位端子14を、例えば、半導体装置220の接地端子に接続し、ゲート駆動回路47B、47D及び47Fの基準電位端子14を、例えば、それぞれのハーフブリッジにおける上記中点に接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0091】

図11は、本発明の実施の形態4に係る第2の変形例を示す半導体装置を含む回路構成図である。同図に記載された駆動システムは、三相インバータ回路によりモータを駆動するシステムであり、交流電源60と、入力フィルタ61と、半導体装置230とモータ31とを備える。

【0092】

図11に記載された半導体素子50A〜50Iは、それぞれ、図6に記載されたダブルゲート型の半導体素子40と同じ構成である。また、図11に記載されたゲート駆動回路57A〜57Iは、それぞれ、図6に記載されたゲート駆動回路47と同じ構成である。また、図11に記載されたゲート駆動回路58A〜58Iは、それぞれ、図6に記載されたゲート駆動回路48と同じ構成である。

【0093】

交流電源60から三相の交流電力が入力され、三相入力の各相間に入力フィルタ61が接続されている。ゲート駆動回路58A、57A及びダブルゲート型の半導体素子50Aを1つの構成ユニットとし、同様の構成ユニットが9つ配置されている。つまり、1構成ユニットは、1つのダブルゲート型の半導体素子を、2つのゲート駆動回路で駆動している。上記9つの構成ユニットは、三相マトリクスコンバータ回路を形成することにより、モータ31へ三相の出力電流を供給している。

【0094】

具体的には、半導体装置230は、以下の構成を有する。

【0095】

第3半導体素子である半導体素子50A、第6半導体素子である半導体素子50D及び第9半導体素子である半導体素子50Gのオーミック電極端子46は、それぞれ、三相交流電源の第1出力端子に接続されている。

【0096】

第4半導体素子である半導体素子50B、第7半導体素子である半導体素子50E及び第10半導体素子である半導体素子50Hのオーミック電極端子46は、それぞれ、三相交流電源の第2出力端子に接続されている。

【0097】

第5半導体素子である半導体素子50C、第8半導体素子である半導体素子50F及び第11半導体素子である半導体素子50Iのオーミック電極端子46は、それぞれ、三相交流電源の第3出力端子に接続されている。

【0098】

半導体素子50A、半導体素子50B及び半導体素子50Cのオーミック電極端子6は、それぞれ、三相モータの第1入力端子に接続されている。

【0099】

半導体素子50D、半導体素子50E及び半導体素子50Fのオーミック電極端子6は、それぞれ、三相モータの第2入力端子に接続されている。

【0100】

半導体素子50G、半導体素子50H及び半導体素子50Iのオーミック電極端子6は、それぞれ、三相モータの第3入力端子に接続されている。

【0101】

ここで、ゲート駆動回路57A〜57Iの有する基準電位端子14を、例えば、入力側の端子へ接続し、ゲート駆動回路58A〜58Iの有する基準電位端子14を、例えば、出力側の端子へ接続することで、ゲート駆動回路への外乱ノイズを低減することが可能となる。

【0102】

また入力電源が交流の場合、駆動システムの基準電位が変動するので、各ユニットの基準電位は、駆動システムの基準電位とせずに、任意の基準電位とすることが好ましい。本構成によれば、各ユニットの基準電位は、電流駆動型のソースパッドであるオーミック電極パッド2またはオーミック電極パッド5としているので、半導体装置の基準電位と合わせる必要がなく、複数のゲート駆動回路を独立に動作させることが可能となる。

【0103】

以上、本発明の半導体装置について、実施の形態に基づいて説明してきたが、本発明に係る半導体装置は、上記実施の形態に限定されるものではない。実施の形態1〜4及びその変形例における任意の構成要素を組み合わせて実現される別の実施の形態や、実施の形態1〜4及びその変形例に対して本発明の主旨を逸脱しない範囲で当業者が思いつく各種変形を施して得られる変形例や、本発明に係る半導体装置を内蔵した各種機器も本発明に含まれる。

【産業上の利用可能性】

【0104】

本発明は、高精度かつ安定な電力制御を要するハイパワーデバイスのゲート駆動制御に利用可能であり、電流駆動型の半導体装置への応用に適している。

【符号の説明】

【0105】

1、41、43 ゲート電極パッド

1A、41A、43A ゲート電極

1B ゲート配線

2、5 オーミック電極パッド

2A、5A オーミック電極

3、3A、3B、3C、3D、3E、3F、40、40A、40B、40C、40D、40E、40F、50A、50B、50C、50D、50E、50F、50G、50H、50I 半導体素子

4 基板端子

6、10、46 オーミック電極端子

7、45 ゲート駆動用端子

8、42、44 ゲート端子

9A、9B、9C、9D、9E、9F ボンディングワイヤ

11、11A、11B、11C、11D、11E、11F、47、47A、47B、47C、47D、47E、47F、48、48A、48B、48C、48D、48E、48F、57A、57B、57C、57D、57E、57F、57G、57H、57I、58A、58B、58C、58D、58E、58F、58G、58H、58I ゲート駆動回路

12 負荷

13、28、111、111A、111B、471、471A、471B、481、481A、481B 直流電源

14 基準電位端子

15 出力端子

19 保護膜

20、21 窒化物半導体層

22 バッファ層

23 基板

26、27、32 p型窒化物半導体層

29、31 モータ

30 活性領域

60 交流電源

61 入力フィルタ

100、110、120、200、210、220、230 半導体装置

101、102、103、201、202、203 ハーフブリッジ

112、112A、112B、472、472A、472B、482、482A、482B ゲート回路

500 ドライブ回路

516 IGBT

551 パワーGND端子

552 センスGND端子

553 センス端子

567 パワーGND線

576 センスGND線

579 比較器

580 抵抗

581 基準電圧源

583 内部インダクタンス

584 抵抗

585 寄生インダクタンス

【特許請求の範囲】

【請求項1】

電力変換を行う電流駆動型の第1半導体素子と、

前記第1半導体素子の電力変換を制御する第1ゲート駆動回路と、

接続端子部とを備え、

前記第1半導体素子は、

基板の上に積層された窒化物半導体層の積層体と、

前記積層体の上に形成されたゲート電極と、

前記基板上であって、前記ゲート電極の両側方に形成された第1オーミック電極及び第2オーミック電極と、

前記第1半導体素子上にあって、前記ゲート電極から配線されたゲート電極パッドと、

前記第1半導体素子上にあって、前記第1オーミック電極及び前記第2オーミック電極からそれぞれ配線された第1オーミック電極パッド及び第2オーミック電極パッドとを有し、

前記接続端子部は、

第1の接続材により前記第1オーミック電極パッドと接続された第1オーミック電極端子と、

第2の接続材により前記第2オーミック電極パッドと接続された第2オーミック電極端子と、

第3の接続材により前記第1オーミック電極パッドと接続されたゲート駆動用端子と、

第4の接続材により前記ゲート電極パッドと接続されたゲート端子とを有し、

前記第1ゲート駆動回路の入力端子は、前記ゲート駆動用端子に接続され、前記第1ゲート駆動回路の出力端子は、前記ゲート端子に接続され、前記第1ゲート駆動回路の基準電位を前記第1オーミック電極パッドの電位とする

半導体装置。

【請求項2】

前記接続端子部は、さらに、

前記第1半導体素子が接合された第1基板端子とを有し、

前記ゲート駆動用端子は、前記第1基板端子と同一端子とする

請求項1に記載の半導体装置。

【請求項3】

さらに、

前記第1半導体素子と同一の構造を有する第2半導体素子と、

前記第1ゲート駆動回路と同一の構造を有する第2ゲート駆動回路とを備え、

前記第2半導体素子と前記第2ゲート駆動回路との接続関係は、前記第1半導体素子と前記第1ゲート駆動回路との接続関係と同一であり、

前記第1半導体素子の第1オーミック電極端子と、前記第2半導体素子の第2オーミック電極端子とが接続されることにより、前記第1半導体素子、前記第2半導体素子、前記第1ゲート駆動回路及び前記第2ゲート駆動回路は、第1のハーフブリッジを構成する

請求項1又は2に記載の半導体装置。

【請求項4】

さらに、

前記第1のハーフブリッジと並列に接続された、前記第1のハーフブリッジと同一構成を有する第2のハーフブリッジを備え、

単相モータを駆動するモータ駆動インバータを構成する

請求項3に記載の半導体装置。

【請求項5】

さらに、

前記第1のハーフブリッジと並列に接続された、前記第1のハーフブリッジと同一構成を有する第2のハーフブリッジ及び第3のハーフブリッジを備え、

三相モータを駆動するモータ駆動インバータを構成する

請求項3に記載の半導体装置。

【請求項6】

電力変換を行う電流駆動型の第3半導体素子と、

前記第3半導体素子の電力変換を制御する第3ゲート駆動回路及び第4ゲート駆動回路と、

接続端子部とを備え、

前記第3半導体素子は、

基板の上に積層された窒化物半導体層の積層体と、

前記積層体の上に隣接して形成された第1ゲート電極及び第2ゲート電極と、

前記基板上であって、前記第1ゲート電極及び前記第2ゲート電極の両側方に形成された第3オーミック電極及び第4オーミック電極と、

前記第1半導体素子上にあって、前記第1ゲート電極及び前記第2ゲート電極からそれぞれ配線された第1ゲート電極パッド及び第2ゲート電極パッドと、

前記第1半導体素子上にあって、前記第3オーミック電極及び前記第4オーミック電極からそれぞれ配線された第3オーミック電極パッド及び第4オーミック電極パッドとを有し、

前記接続端子部は、

第1の接続材により前記第3オーミック電極パッドと接続された第3オーミック電極端子と、

第2の接続材により前記第4オーミック電極パッドと接続された第4オーミック電極端子と、

第3の接続材により前記第3オーミック電極パッドと接続された第1ゲート駆動用端子と、

第4の接続材により前記第4オーミック電極パッドと接続された第2ゲート駆動用端子と、

第5の接続材により前記第1ゲート電極パッドと接続された第1ゲート端子と、

第6の接続材により前記第2ゲート電極パッドと接続された第2ゲート端子とを有し、

前記第3ゲート駆動回路の入力端子は、前記第1ゲート駆動用端子に接続され、前記第3ゲート駆動回路の出力端子は、前記第1ゲート端子に接続され、前記第3ゲート駆動回路の基準電位を前記第3オーミック電極パッドの電位とし、

前記第4ゲート駆動回路の入力端子は、前記第2ゲート駆動用端子に接続され、前記第4ゲート駆動回路の出力端子は、前記第2ゲート端子に接続され、前記第4ゲート駆動回路の基準電位を前記第4オーミック電極パッドの電位とする

半導体装置。

【請求項7】

さらに、

前記第3半導体素子と同一の構造を有する第4半導体素子と、

前記第3ゲート駆動回路と同一の構造を有する第5ゲート駆動回路と、

前記第4ゲート駆動回路と同一の構造を有する第6ゲート駆動回路とを備え、

前記第4半導体素子と前記第5ゲート駆動回路との接続関係は、前記第3半導体素子と前記第3ゲート駆動回路との接続関係と同一であり、

前記第4半導体素子と前記第6ゲート駆動回路との接続関係は、前記第3半導体素子と前記第4ゲート駆動回路との接続関係と同一であり、

前記第3半導体素子の第3オーミック電極端子と、前記第4半導体素子の第4オーミック電極端子とが接続されることにより、前記第3半導体素子、前記第4半導体素子、前記第3ゲート駆動回路、前記第4ゲート駆動回路、前記第5ゲート駆動回路及び前記第6ゲート駆動回路は、第4のハーフブリッジを構成する

請求項6に記載の半導体装置。

【請求項8】

さらに、

前記第4のハーフブリッジと並列に接続された、前記第4のハーフブリッジと同一構成を有する第5のハーフブリッジを備え、

単相モータを駆動するモータ駆動インバータを構成する

請求項7に記載の半導体装置。

【請求項9】

さらに、

前記第4のハーフブリッジと並列に接続された、前記第4のハーフブリッジと同一構成を有する第5のハーフブリッジ及び第6のハーフブリッジを備え、

三相モータを駆動するモータ駆動インバータを構成する

請求項7に記載の半導体装置。

【請求項10】

さらに、

前記第3半導体素子と同一の構造を有する第4半導体素子〜第11半導体素子を備え、

前記第4半導体素子〜第11半導体素子のそれぞれは、前記第3ゲート駆動回路と同一の構造を有するゲート駆動回路と接続され、かつ、前記第4ゲート駆動回路と同一の構造を有するゲート駆動回路と接続されており、

前記第3半導体素子、前記第6半導体素子及び前記第9半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第1出力端子に接続され、

前記第4半導体素子、前記第7半導体素子及び前記第10半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第2出力端子に接続され、

前記第5半導体素子、前記第8半導体素子及び前記第11半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第3出力端子に接続され、

前記第3半導体素子、前記第4半導体素子及び前記第5半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第1入力端子に接続され、

前記第6半導体素子、前記第7半導体素子及び前記第8半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第2入力端子に接続され、

前記第9半導体素子、前記第10半導体素子及び前記第11半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第3入力端子に接続されており、

三相モータを駆動するモータ駆動マトリクスコンバータを構成する

請求項6に記載の半導体装置。

【請求項1】

電力変換を行う電流駆動型の第1半導体素子と、

前記第1半導体素子の電力変換を制御する第1ゲート駆動回路と、

接続端子部とを備え、

前記第1半導体素子は、

基板の上に積層された窒化物半導体層の積層体と、

前記積層体の上に形成されたゲート電極と、

前記基板上であって、前記ゲート電極の両側方に形成された第1オーミック電極及び第2オーミック電極と、

前記第1半導体素子上にあって、前記ゲート電極から配線されたゲート電極パッドと、

前記第1半導体素子上にあって、前記第1オーミック電極及び前記第2オーミック電極からそれぞれ配線された第1オーミック電極パッド及び第2オーミック電極パッドとを有し、

前記接続端子部は、

第1の接続材により前記第1オーミック電極パッドと接続された第1オーミック電極端子と、

第2の接続材により前記第2オーミック電極パッドと接続された第2オーミック電極端子と、

第3の接続材により前記第1オーミック電極パッドと接続されたゲート駆動用端子と、

第4の接続材により前記ゲート電極パッドと接続されたゲート端子とを有し、

前記第1ゲート駆動回路の入力端子は、前記ゲート駆動用端子に接続され、前記第1ゲート駆動回路の出力端子は、前記ゲート端子に接続され、前記第1ゲート駆動回路の基準電位を前記第1オーミック電極パッドの電位とする

半導体装置。

【請求項2】

前記接続端子部は、さらに、

前記第1半導体素子が接合された第1基板端子とを有し、

前記ゲート駆動用端子は、前記第1基板端子と同一端子とする

請求項1に記載の半導体装置。

【請求項3】

さらに、

前記第1半導体素子と同一の構造を有する第2半導体素子と、

前記第1ゲート駆動回路と同一の構造を有する第2ゲート駆動回路とを備え、

前記第2半導体素子と前記第2ゲート駆動回路との接続関係は、前記第1半導体素子と前記第1ゲート駆動回路との接続関係と同一であり、

前記第1半導体素子の第1オーミック電極端子と、前記第2半導体素子の第2オーミック電極端子とが接続されることにより、前記第1半導体素子、前記第2半導体素子、前記第1ゲート駆動回路及び前記第2ゲート駆動回路は、第1のハーフブリッジを構成する

請求項1又は2に記載の半導体装置。

【請求項4】

さらに、

前記第1のハーフブリッジと並列に接続された、前記第1のハーフブリッジと同一構成を有する第2のハーフブリッジを備え、

単相モータを駆動するモータ駆動インバータを構成する

請求項3に記載の半導体装置。

【請求項5】

さらに、

前記第1のハーフブリッジと並列に接続された、前記第1のハーフブリッジと同一構成を有する第2のハーフブリッジ及び第3のハーフブリッジを備え、

三相モータを駆動するモータ駆動インバータを構成する

請求項3に記載の半導体装置。

【請求項6】

電力変換を行う電流駆動型の第3半導体素子と、

前記第3半導体素子の電力変換を制御する第3ゲート駆動回路及び第4ゲート駆動回路と、

接続端子部とを備え、

前記第3半導体素子は、

基板の上に積層された窒化物半導体層の積層体と、

前記積層体の上に隣接して形成された第1ゲート電極及び第2ゲート電極と、

前記基板上であって、前記第1ゲート電極及び前記第2ゲート電極の両側方に形成された第3オーミック電極及び第4オーミック電極と、

前記第1半導体素子上にあって、前記第1ゲート電極及び前記第2ゲート電極からそれぞれ配線された第1ゲート電極パッド及び第2ゲート電極パッドと、

前記第1半導体素子上にあって、前記第3オーミック電極及び前記第4オーミック電極からそれぞれ配線された第3オーミック電極パッド及び第4オーミック電極パッドとを有し、

前記接続端子部は、

第1の接続材により前記第3オーミック電極パッドと接続された第3オーミック電極端子と、

第2の接続材により前記第4オーミック電極パッドと接続された第4オーミック電極端子と、

第3の接続材により前記第3オーミック電極パッドと接続された第1ゲート駆動用端子と、

第4の接続材により前記第4オーミック電極パッドと接続された第2ゲート駆動用端子と、

第5の接続材により前記第1ゲート電極パッドと接続された第1ゲート端子と、

第6の接続材により前記第2ゲート電極パッドと接続された第2ゲート端子とを有し、

前記第3ゲート駆動回路の入力端子は、前記第1ゲート駆動用端子に接続され、前記第3ゲート駆動回路の出力端子は、前記第1ゲート端子に接続され、前記第3ゲート駆動回路の基準電位を前記第3オーミック電極パッドの電位とし、

前記第4ゲート駆動回路の入力端子は、前記第2ゲート駆動用端子に接続され、前記第4ゲート駆動回路の出力端子は、前記第2ゲート端子に接続され、前記第4ゲート駆動回路の基準電位を前記第4オーミック電極パッドの電位とする

半導体装置。

【請求項7】

さらに、

前記第3半導体素子と同一の構造を有する第4半導体素子と、

前記第3ゲート駆動回路と同一の構造を有する第5ゲート駆動回路と、

前記第4ゲート駆動回路と同一の構造を有する第6ゲート駆動回路とを備え、

前記第4半導体素子と前記第5ゲート駆動回路との接続関係は、前記第3半導体素子と前記第3ゲート駆動回路との接続関係と同一であり、

前記第4半導体素子と前記第6ゲート駆動回路との接続関係は、前記第3半導体素子と前記第4ゲート駆動回路との接続関係と同一であり、

前記第3半導体素子の第3オーミック電極端子と、前記第4半導体素子の第4オーミック電極端子とが接続されることにより、前記第3半導体素子、前記第4半導体素子、前記第3ゲート駆動回路、前記第4ゲート駆動回路、前記第5ゲート駆動回路及び前記第6ゲート駆動回路は、第4のハーフブリッジを構成する

請求項6に記載の半導体装置。

【請求項8】

さらに、

前記第4のハーフブリッジと並列に接続された、前記第4のハーフブリッジと同一構成を有する第5のハーフブリッジを備え、

単相モータを駆動するモータ駆動インバータを構成する

請求項7に記載の半導体装置。

【請求項9】

さらに、

前記第4のハーフブリッジと並列に接続された、前記第4のハーフブリッジと同一構成を有する第5のハーフブリッジ及び第6のハーフブリッジを備え、

三相モータを駆動するモータ駆動インバータを構成する

請求項7に記載の半導体装置。

【請求項10】

さらに、

前記第3半導体素子と同一の構造を有する第4半導体素子〜第11半導体素子を備え、

前記第4半導体素子〜第11半導体素子のそれぞれは、前記第3ゲート駆動回路と同一の構造を有するゲート駆動回路と接続され、かつ、前記第4ゲート駆動回路と同一の構造を有するゲート駆動回路と接続されており、

前記第3半導体素子、前記第6半導体素子及び前記第9半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第1出力端子に接続され、

前記第4半導体素子、前記第7半導体素子及び前記第10半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第2出力端子に接続され、

前記第5半導体素子、前記第8半導体素子及び前記第11半導体素子の第4オーミック電極端子は、それぞれ、三相交流電源の第3出力端子に接続され、

前記第3半導体素子、前記第4半導体素子及び前記第5半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第1入力端子に接続され、

前記第6半導体素子、前記第7半導体素子及び前記第8半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第2入力端子に接続され、

前記第9半導体素子、前記第10半導体素子及び前記第11半導体素子の第3オーミック電極端子は、それぞれ、三相モータの第3入力端子に接続されており、

三相モータを駆動するモータ駆動マトリクスコンバータを構成する

請求項6に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−182591(P2011−182591A)

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願番号】特願2010−45966(P2010−45966)

【出願日】平成22年3月2日(2010.3.2)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願日】平成22年3月2日(2010.3.2)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]