半導体装置

【課題】精度の高い負電圧をプログラマブルに生成することが可能な半導体装置を提供すること。

【解決手段】負電圧発生装置の出力電圧VPWを制御する負電圧検出回路に、負電圧の検出値を切り替える切り替えスイッチTGと、補正スイッチTBとを備える。補正スイッチは、切り替えスイッチと同一の構成を有するスイッチとし、オン状態に保つ。これにより、切り替えスイッチのオン抵抗の影響をキャンセルすることができる。そのため、精度の高い負電圧をプログラマブルに生成することが可能である。

【解決手段】負電圧発生装置の出力電圧VPWを制御する負電圧検出回路に、負電圧の検出値を切り替える切り替えスイッチTGと、補正スイッチTBとを備える。補正スイッチは、切り替えスイッチと同一の構成を有するスイッチとし、オン状態に保つ。これにより、切り替えスイッチのオン抵抗の影響をキャンセルすることができる。そのため、精度の高い負電圧をプログラマブルに生成することが可能である。

【発明の詳細な説明】

【技術分野】

【0001】

本願は、負電圧を使用する半導体装置に関する。

【背景技術】

【0002】

従来、半導体装置において、負電圧の生成が行われている。図4に一例を示す。定電圧回路1は正の定電圧Vrを出力し、負電圧発生装置3は負電圧VPWを出力する。抵抗R3、R4は、定電圧Vrと負電圧VPWとを分圧し、分圧電圧Vcomを出力する。コンパレータ2は、分圧電圧Vcomとグランド電位VSSとの電圧レベルを比較し、比較結果を負電圧発生装置3に出力する。

【0003】

上記の構成により、負電圧発生装置3が出力する負電圧VPWの電圧値を検出して、負電圧VPWを設定値に維持することができる。具体的には、負電圧VPWが設定値より高い場合、分圧電圧Vcomの電圧レベルがグランド電位VSSの電圧レベルより高くなるため、コンパレータ2はHレベルを出力する。コンパレータ2のHレベル出力を受けて、負電圧発生装置3は、負電圧VPWを下げるように動作する。そして、負電圧VPWが設定値となり、分圧電圧Vcomの電圧レベルがグランド電位VSSの電圧レベルと等しくなると、コンパレータ2はHレベル出力を止め、負電圧発生装置3の動作を停止する。

【0004】

これにより、負電圧VPWは、抵抗R3、R4の抵抗値の比によって決まる設定値に維持される。例えば、抵抗R3、R4の抵抗値が等しい場合、負電圧VPWは、図5に示されるように、定電圧回路1の出力電圧Vrの1倍の反転増幅となり、Vr=1.8Vの場合、VPW=−1.8Vとなる。

【0005】

このような負電圧の生成において、負電圧VPWの電圧値を選択可能にしたい場合がある。これに関し、例えば、定電圧Vrと負電圧VPWとの分圧比を、スイッチのオンオフ、あるいはヒューズの切断・非切断によって切り替えることで、負電圧VPWの電圧値を選択可能にする技術が知られている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平11−150230

【特許文献2】特開2001−332094

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、スイッチを用いる方法では、スイッチのオン抵抗によって負電圧の検出にばらつきが生じるという問題がある。また、ヒューズを用いる方法では、ヒューズは切断すると元には戻せないため、設定値の変更に制限があるという問題がある。

【0008】

本発明は、上記の課題に鑑み提案されたものであって、精度の高い負電圧をプログラマブルに生成することが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

本願に開示されている半導体装置は、負電圧を発生する負電圧発生装置と、前記負電圧発生装置の出力電圧を制御する負電圧検出回路と、を備える半導体装置であって、前記負電圧検出回路は、一定の電圧を出力する定電圧回路と、前記定電圧回路の出力とグランドとの間に直列に接続された複数の分圧抵抗と、一端が前記複数の分圧抵抗の各分圧点に接続され、他端が共通に接続された複数の切り替えスイッチと、前記複数の切り替えスイッチの他端と前記負電圧発生装置の出力との間に直列に接続され、前記複数の分圧抵抗により分圧された前記定電圧回路の出力電圧と前記負電圧発生装置の出力電圧とを分圧する第1及び第2の抵抗と、前記複数の切り替えスイッチと同一の構成を有するスイッチであって、前記第1及び第2の抵抗の分圧点と前記負電圧発生装置の出力との間で前記第1及び第2の抵抗と直列に接続され、オン状態に保たれる補正スイッチと、前記第1及び第2の抵抗による分圧電圧の電圧レベルとグランドの電圧レベルとを比較し、比較結果を前記負電圧発生装置に出力するコンパレータと、を備える。

【発明の効果】

【0010】

開示の半導体装置によれば、負電圧の検出値を切り替える切り替えスイッチと同一の構成を有する補正スイッチを備えることで、切り替えスイッチのオン抵抗の影響をキャンセルすることができる。そのため、精度の高い負電圧をプログラマブルに生成することが可能である。

【図面の簡単な説明】

【0011】

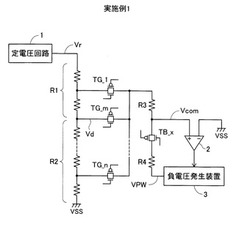

【図1】実施例1の回路ブロック図である。

【図2】実施例2の回路ブロック図である。

【図3】実施例3の回路ブロック図である。

【図4】従来例を示す回路ブロック図である。

【図5】負電圧の生成における入力電圧と出力電圧との関係の一例を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態について、図面を参照して説明する。

【実施例1】

【0013】

図1は、実施例1の回路ブロック図を示す。定電圧回路1の出力とグランド電位VSSとの間に複数の分圧抵抗が直列に接続され、各分圧点には、トランスミッションゲートTG_1〜TG_nが接続される。トランスミッションゲートTG_1〜TG_nの他端は、抵抗R3に共通に接続される。抵抗R3は抵抗R4とともに、複数の分圧抵抗により分圧された定電圧回路1の出力電圧Vrと、負電圧発生装置3が出力する負電圧VPWとを分圧する。また、抵抗R3、R4の分圧点と負電圧発生装置3の出力との間に、トランスミッションゲートTB_xが抵抗R3、R4と直列に接続される。ここで、トランスミッションゲートTG_1〜TG_nはいずれか1つが選択的にオン状態にされ、トランスミッションゲートTB_xはトランスミッションゲートTG_1〜TG_nと同一の構成を有し、常時オン状態に保たれる。コンパレータ2は、抵抗R3、R4による分圧電圧Vcomとグランド電位VSSとの電圧レベルを比較し、比較結果を負電圧発生装置3に出力する。

【0014】

上記の構成により、負電圧発生装置3が出力する負電圧VPWの電圧値を検出して、負電圧VPWを設定値に維持することができる。また、トランスミッションゲートTG_1〜TG_nのうち、いずれか1つを選択的にオン状態にすることにより、複数の分圧抵抗による定電圧回路1の出力電圧Vrの分圧比を切り替え、負電圧VPWの電圧値を選択することができる。

【0015】

上記の構成を有する実施例1の効果についてさらに説明する。図1において、トランスミッションゲートTG_1〜TG_nのうち、任意のトランスミッションゲートTG_mが選択され、オン状態になっているとする。このとき、複数の分圧抵抗は、R1:R2の比で定電圧回路1の出力電圧Vrを分圧し、電圧Vd={R2/(R1+R2)}×Vrを出力する。以下では、トランスミッションゲートTG_mのオン抵抗をRgm、トランスミッションゲートTB_xのオン抵抗をRbxとし、トランスミッションゲートTB_xがある場合とない場合とを比較する。

【0016】

(1)トランスミッションゲートTB_xがない場合

負電圧発生装置3が出力する負電圧VPWは、VPW=−{R4/(R3+Rgm)}×Vdとなる。ここで、RgmがR3、R4と比較して十分に小さければ、Rgmによる影響は問題とならず、例えば、R3=R4のときVPW≒−Vdとなる。しかし、例えば、R3=R4で、RgmがR3、R4の10%であるとすると、VPW≒−0.91×Vdとなり、約9%の誤差が生じる。

【0017】

(2)トランスミッションゲートTB_xがある場合

負電圧発生装置3が出力する負電圧VPWは、VPW=−{(R4+Rbx)/(R3+Rgm)}×Vdとなる。ここで、前述のように、トランスミッションゲートTB_xはトランスミッションゲートTG_1〜TG_nと同一の構成を有するため、Rgm=Rbxとなる。したがって、例えば、R3=R4のときVPW=−Vdとなり、トランスミッションゲートのオン抵抗による誤差は生じない。

【0018】

このように、実施例1では、トランスミッションゲートTG_1〜TG_nと同一の構成を有して常時オン状態に保たれるトランスミッションゲートTB_xを備えることで、トランスミッションゲートTG_mのオン抵抗Rgmによる影響をキャンセルすることができる。したがって、例えば、リーク電流の増大によりトランスミッションゲートTG_mのオン抵抗Rgmが無視できないほど大きくなる場合でも、負電圧VPWの電圧値の検出に生じるばらつきを抑制し、精度の高い負電圧VPWをプログラマブルに生成することが可能である。

【実施例2】

【0019】

図2は、実施例2の回路ブロック図を示す。まず、図2を参照して、負電圧発生装置3について具体的に説明する。負電圧発生装置3は、リングオシレータ31、コンデンサC1、ダイオードD1、D2、を備える。リングオシレータ31は、NANDゲートと偶数個のインバータとを含み、NANDゲートの一方の入力端子には、コンパレータ2の比較結果がイネーブル信号enとして入力される。これにより、リングオシレータ31は、コンパレータ2の出力がHレベルの場合に矩形波を出力する。ダイオードD1のカソードはグランドに、アノードはダイオードD2のカソードに、それぞれ接続される。また、コンデンサC1は、リングオシレータ31の出力ノードAとダイオードD1、D2の接続ノードBとの間に接続される。ダイオードD2のアノードは、負電圧発生装置3の出力となる。

【0020】

あるタイミングで、リングオシレータ31の出力がLレベルであり、ノードAがLレベルになっているとする。この場合、ノードBは、コンデンサC1によって引き下げられることにより電位が低くなる。したがって、ダイオードD2がオン状態となり、負電圧発生装置3の出力からノードBへ電流が流れる。次のタイミングでは、リングオシレータ31の出力がHレベルとなり、ノードAがHレベルになる。この場合、ノードBは、コンデンサC1によって押し上げられることにより電位が高くなる。したがって、今度はダイオードD1がオン状態となり、ノードBからグランドへ電流が流れる。

【0021】

コンパレータ2のHレベル出力を受けて、リングオシレータ31の出力がHレベルとLレベルとの間で変化するのに伴って、上記のように、負電圧発生装置3の出力からグランドへ電荷が順繰りに移動する。その結果、負電圧発生装置3の出力の電位が低くなる。このようにして、負電圧発生装置3は、負電圧VPWを出力する。

【0022】

続いて、実施例2の全体の構成及び作用、効果について説明する。実施例2では、トランスミッションゲートTG_1〜TG_nと同数のトランスミッションゲートTB_1〜TB_nが互いに並列に接続されるとともに、抵抗R3、R4の分圧点と負電圧発生装置3の出力との間で抵抗R3、R4と直列に接続される。ここで、トランスミッションゲートTB_1〜TB_nは、トランスミッションゲートTG_1〜TG_nと同一の構成を有する。また、トランスミッションゲートTB_1〜TB_nには、それぞれトランスミッションゲートTG_1〜TG_nと同一の制御信号g1x〜gnx、g1z〜gnzが入力される。したがって、トランスミッションゲートTB_1〜TB_nは、トランスミッションゲートTG_1〜TG_nと連動してオンオフ制御される。そのため、例えば、トランスミッションゲートTG_1が選択され、オン状態になる場合、トランスミッションゲートTB_1もオン状態になる。このように、トランスミッションゲートTG_1〜TG_nのうち、任意のトランスミッションゲートTG_mが選択的にオン状態にされると、それに伴ってトランスミッションゲートTB_1〜TB_nのうち、対応するトランスミッションゲートTB_mがオン状態にされる。

【0023】

その他の点は実施例1と同様であるため、図2において、図1と対応する各部に同一の符号を付して、説明を省略する。トランスミッションゲートTB_1〜TB_nのうち、対応するトランスミッションゲートTB_mがオン状態にされることで、実施例2においても実施例1と同様に、トランスミッションゲートTG_mのオン抵抗Rgmによる影響をキャンセルすることができる。したがって、精度の高い負電圧VPWをプログラマブルに生成することが可能である。

【0024】

また、実施例2では、トランスミッションゲートTG_1〜TG_nと同一の構成を有して、トランスミッションゲートTG_1〜TG_nと連動してオンオフ制御される同数のトランスミッションゲートTB_1〜TB_nを備える。これにより、トランスミッションゲートTG_1〜TG_nのうち、オフ状態になっているトランスミッションゲートのオフ抵抗による影響もキャンセルすることができる。また、トランスミッションゲートTB_1〜TB_nは、トランスミッションゲートTG_1〜TG_nと連動して同時にオンオフ制御されるため、各トランスミッションゲートを構成するMOSトランジスタの寄生容量の充放電時のノイズが緩和される。そのため、分圧電圧Vcomがより高速に安定して、負電圧VPWの安定が高速化されるという効果が得られる。

【0025】

ここで、トランスミッションゲートTG_1〜TG_nは、請求項に記載の切り替えスイッチの一例であり、トランスミッションゲートTB_x、TB_1〜TB_nは、請求項に記載の補正スイッチの一例である。抵抗R3、R4は、請求項に記載の第1及び第2の抵抗の一例である。また、定電圧回路1、複数の分圧抵抗、トランスミッションゲートTG_1〜TG_n、抵抗R3、R4、トランスミッションゲートTB_xあるいはTB_1〜TB_n、コンパレータ2、を含む構成が、請求項に記載の負電圧検出回路の一例として挙げられる。

【0026】

以上、詳細に説明したように、前記実施例1、2を含む実施形態によれば、負電圧VPWの検出値を切り替えるトランスミッションゲートTG_1〜TG_nと同一の構成を有するトランスミッションゲートTB_xあるいはTB_1〜TB_nを備える。これにより、トランスミッションゲートTG_1〜TG_nのオン抵抗による影響をキャンセルすることができる。そのため、精度の高い負電圧VPWをプログラマブルに生成することが可能である。

【0027】

尚、本発明は前記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内での種々の改良、変更が可能であることは言うまでもない。

【0028】

例えば、トランスミッションゲートTG_1〜TG_n、トランスミッションゲートTB_x、TB_1〜TB_nについて、図3に実施例3として示されるように、カスケード接続で構成したスイッチを採用してもよい。これにより、スイッチ特性を確保することができる。

【0029】

また、実施例2において、トランスミッションゲートTB_1〜TB_nは、トランスミッションゲートTG_1〜TG_nと連動してオンオフ制御されるとしたが、これに限定されない。トランスミッションゲートTB_1〜TB_nのうち、いずれか1つを常時オン状態にして、他はオフ状態に保つようにしてもよい。

【0030】

その他、実施例1では、抵抗R3、トランスミッションゲートTB_x、抵抗R4の順に接続され、実施例2では、抵抗R3、抵抗R4、トランスミッションゲートTB_1〜TB_nの順に接続されたが、トランスミッションゲートTB_x、TB_1〜TB_nと抵抗R4との接続順は入れ替えられてもよいことは言うまでもない。

【符号の説明】

【0031】

1 定電圧回路

2 コンパレータ

3 負電圧発生装置

31 リングオシレータ

C1 コンデンサ

D1、D2 ダイオード

R1、R2 分圧抵抗

R3、R4 抵抗(第1及び第2の抵抗)

TB_x、TB_1〜TB_n トランスミッションゲート(補正スイッチ)

TG_1〜TG_n トランスミッションゲート(切り替えスイッチ)

【技術分野】

【0001】

本願は、負電圧を使用する半導体装置に関する。

【背景技術】

【0002】

従来、半導体装置において、負電圧の生成が行われている。図4に一例を示す。定電圧回路1は正の定電圧Vrを出力し、負電圧発生装置3は負電圧VPWを出力する。抵抗R3、R4は、定電圧Vrと負電圧VPWとを分圧し、分圧電圧Vcomを出力する。コンパレータ2は、分圧電圧Vcomとグランド電位VSSとの電圧レベルを比較し、比較結果を負電圧発生装置3に出力する。

【0003】

上記の構成により、負電圧発生装置3が出力する負電圧VPWの電圧値を検出して、負電圧VPWを設定値に維持することができる。具体的には、負電圧VPWが設定値より高い場合、分圧電圧Vcomの電圧レベルがグランド電位VSSの電圧レベルより高くなるため、コンパレータ2はHレベルを出力する。コンパレータ2のHレベル出力を受けて、負電圧発生装置3は、負電圧VPWを下げるように動作する。そして、負電圧VPWが設定値となり、分圧電圧Vcomの電圧レベルがグランド電位VSSの電圧レベルと等しくなると、コンパレータ2はHレベル出力を止め、負電圧発生装置3の動作を停止する。

【0004】

これにより、負電圧VPWは、抵抗R3、R4の抵抗値の比によって決まる設定値に維持される。例えば、抵抗R3、R4の抵抗値が等しい場合、負電圧VPWは、図5に示されるように、定電圧回路1の出力電圧Vrの1倍の反転増幅となり、Vr=1.8Vの場合、VPW=−1.8Vとなる。

【0005】

このような負電圧の生成において、負電圧VPWの電圧値を選択可能にしたい場合がある。これに関し、例えば、定電圧Vrと負電圧VPWとの分圧比を、スイッチのオンオフ、あるいはヒューズの切断・非切断によって切り替えることで、負電圧VPWの電圧値を選択可能にする技術が知られている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平11−150230

【特許文献2】特開2001−332094

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、スイッチを用いる方法では、スイッチのオン抵抗によって負電圧の検出にばらつきが生じるという問題がある。また、ヒューズを用いる方法では、ヒューズは切断すると元には戻せないため、設定値の変更に制限があるという問題がある。

【0008】

本発明は、上記の課題に鑑み提案されたものであって、精度の高い負電圧をプログラマブルに生成することが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

本願に開示されている半導体装置は、負電圧を発生する負電圧発生装置と、前記負電圧発生装置の出力電圧を制御する負電圧検出回路と、を備える半導体装置であって、前記負電圧検出回路は、一定の電圧を出力する定電圧回路と、前記定電圧回路の出力とグランドとの間に直列に接続された複数の分圧抵抗と、一端が前記複数の分圧抵抗の各分圧点に接続され、他端が共通に接続された複数の切り替えスイッチと、前記複数の切り替えスイッチの他端と前記負電圧発生装置の出力との間に直列に接続され、前記複数の分圧抵抗により分圧された前記定電圧回路の出力電圧と前記負電圧発生装置の出力電圧とを分圧する第1及び第2の抵抗と、前記複数の切り替えスイッチと同一の構成を有するスイッチであって、前記第1及び第2の抵抗の分圧点と前記負電圧発生装置の出力との間で前記第1及び第2の抵抗と直列に接続され、オン状態に保たれる補正スイッチと、前記第1及び第2の抵抗による分圧電圧の電圧レベルとグランドの電圧レベルとを比較し、比較結果を前記負電圧発生装置に出力するコンパレータと、を備える。

【発明の効果】

【0010】

開示の半導体装置によれば、負電圧の検出値を切り替える切り替えスイッチと同一の構成を有する補正スイッチを備えることで、切り替えスイッチのオン抵抗の影響をキャンセルすることができる。そのため、精度の高い負電圧をプログラマブルに生成することが可能である。

【図面の簡単な説明】

【0011】

【図1】実施例1の回路ブロック図である。

【図2】実施例2の回路ブロック図である。

【図3】実施例3の回路ブロック図である。

【図4】従来例を示す回路ブロック図である。

【図5】負電圧の生成における入力電圧と出力電圧との関係の一例を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態について、図面を参照して説明する。

【実施例1】

【0013】

図1は、実施例1の回路ブロック図を示す。定電圧回路1の出力とグランド電位VSSとの間に複数の分圧抵抗が直列に接続され、各分圧点には、トランスミッションゲートTG_1〜TG_nが接続される。トランスミッションゲートTG_1〜TG_nの他端は、抵抗R3に共通に接続される。抵抗R3は抵抗R4とともに、複数の分圧抵抗により分圧された定電圧回路1の出力電圧Vrと、負電圧発生装置3が出力する負電圧VPWとを分圧する。また、抵抗R3、R4の分圧点と負電圧発生装置3の出力との間に、トランスミッションゲートTB_xが抵抗R3、R4と直列に接続される。ここで、トランスミッションゲートTG_1〜TG_nはいずれか1つが選択的にオン状態にされ、トランスミッションゲートTB_xはトランスミッションゲートTG_1〜TG_nと同一の構成を有し、常時オン状態に保たれる。コンパレータ2は、抵抗R3、R4による分圧電圧Vcomとグランド電位VSSとの電圧レベルを比較し、比較結果を負電圧発生装置3に出力する。

【0014】

上記の構成により、負電圧発生装置3が出力する負電圧VPWの電圧値を検出して、負電圧VPWを設定値に維持することができる。また、トランスミッションゲートTG_1〜TG_nのうち、いずれか1つを選択的にオン状態にすることにより、複数の分圧抵抗による定電圧回路1の出力電圧Vrの分圧比を切り替え、負電圧VPWの電圧値を選択することができる。

【0015】

上記の構成を有する実施例1の効果についてさらに説明する。図1において、トランスミッションゲートTG_1〜TG_nのうち、任意のトランスミッションゲートTG_mが選択され、オン状態になっているとする。このとき、複数の分圧抵抗は、R1:R2の比で定電圧回路1の出力電圧Vrを分圧し、電圧Vd={R2/(R1+R2)}×Vrを出力する。以下では、トランスミッションゲートTG_mのオン抵抗をRgm、トランスミッションゲートTB_xのオン抵抗をRbxとし、トランスミッションゲートTB_xがある場合とない場合とを比較する。

【0016】

(1)トランスミッションゲートTB_xがない場合

負電圧発生装置3が出力する負電圧VPWは、VPW=−{R4/(R3+Rgm)}×Vdとなる。ここで、RgmがR3、R4と比較して十分に小さければ、Rgmによる影響は問題とならず、例えば、R3=R4のときVPW≒−Vdとなる。しかし、例えば、R3=R4で、RgmがR3、R4の10%であるとすると、VPW≒−0.91×Vdとなり、約9%の誤差が生じる。

【0017】

(2)トランスミッションゲートTB_xがある場合

負電圧発生装置3が出力する負電圧VPWは、VPW=−{(R4+Rbx)/(R3+Rgm)}×Vdとなる。ここで、前述のように、トランスミッションゲートTB_xはトランスミッションゲートTG_1〜TG_nと同一の構成を有するため、Rgm=Rbxとなる。したがって、例えば、R3=R4のときVPW=−Vdとなり、トランスミッションゲートのオン抵抗による誤差は生じない。

【0018】

このように、実施例1では、トランスミッションゲートTG_1〜TG_nと同一の構成を有して常時オン状態に保たれるトランスミッションゲートTB_xを備えることで、トランスミッションゲートTG_mのオン抵抗Rgmによる影響をキャンセルすることができる。したがって、例えば、リーク電流の増大によりトランスミッションゲートTG_mのオン抵抗Rgmが無視できないほど大きくなる場合でも、負電圧VPWの電圧値の検出に生じるばらつきを抑制し、精度の高い負電圧VPWをプログラマブルに生成することが可能である。

【実施例2】

【0019】

図2は、実施例2の回路ブロック図を示す。まず、図2を参照して、負電圧発生装置3について具体的に説明する。負電圧発生装置3は、リングオシレータ31、コンデンサC1、ダイオードD1、D2、を備える。リングオシレータ31は、NANDゲートと偶数個のインバータとを含み、NANDゲートの一方の入力端子には、コンパレータ2の比較結果がイネーブル信号enとして入力される。これにより、リングオシレータ31は、コンパレータ2の出力がHレベルの場合に矩形波を出力する。ダイオードD1のカソードはグランドに、アノードはダイオードD2のカソードに、それぞれ接続される。また、コンデンサC1は、リングオシレータ31の出力ノードAとダイオードD1、D2の接続ノードBとの間に接続される。ダイオードD2のアノードは、負電圧発生装置3の出力となる。

【0020】

あるタイミングで、リングオシレータ31の出力がLレベルであり、ノードAがLレベルになっているとする。この場合、ノードBは、コンデンサC1によって引き下げられることにより電位が低くなる。したがって、ダイオードD2がオン状態となり、負電圧発生装置3の出力からノードBへ電流が流れる。次のタイミングでは、リングオシレータ31の出力がHレベルとなり、ノードAがHレベルになる。この場合、ノードBは、コンデンサC1によって押し上げられることにより電位が高くなる。したがって、今度はダイオードD1がオン状態となり、ノードBからグランドへ電流が流れる。

【0021】

コンパレータ2のHレベル出力を受けて、リングオシレータ31の出力がHレベルとLレベルとの間で変化するのに伴って、上記のように、負電圧発生装置3の出力からグランドへ電荷が順繰りに移動する。その結果、負電圧発生装置3の出力の電位が低くなる。このようにして、負電圧発生装置3は、負電圧VPWを出力する。

【0022】

続いて、実施例2の全体の構成及び作用、効果について説明する。実施例2では、トランスミッションゲートTG_1〜TG_nと同数のトランスミッションゲートTB_1〜TB_nが互いに並列に接続されるとともに、抵抗R3、R4の分圧点と負電圧発生装置3の出力との間で抵抗R3、R4と直列に接続される。ここで、トランスミッションゲートTB_1〜TB_nは、トランスミッションゲートTG_1〜TG_nと同一の構成を有する。また、トランスミッションゲートTB_1〜TB_nには、それぞれトランスミッションゲートTG_1〜TG_nと同一の制御信号g1x〜gnx、g1z〜gnzが入力される。したがって、トランスミッションゲートTB_1〜TB_nは、トランスミッションゲートTG_1〜TG_nと連動してオンオフ制御される。そのため、例えば、トランスミッションゲートTG_1が選択され、オン状態になる場合、トランスミッションゲートTB_1もオン状態になる。このように、トランスミッションゲートTG_1〜TG_nのうち、任意のトランスミッションゲートTG_mが選択的にオン状態にされると、それに伴ってトランスミッションゲートTB_1〜TB_nのうち、対応するトランスミッションゲートTB_mがオン状態にされる。

【0023】

その他の点は実施例1と同様であるため、図2において、図1と対応する各部に同一の符号を付して、説明を省略する。トランスミッションゲートTB_1〜TB_nのうち、対応するトランスミッションゲートTB_mがオン状態にされることで、実施例2においても実施例1と同様に、トランスミッションゲートTG_mのオン抵抗Rgmによる影響をキャンセルすることができる。したがって、精度の高い負電圧VPWをプログラマブルに生成することが可能である。

【0024】

また、実施例2では、トランスミッションゲートTG_1〜TG_nと同一の構成を有して、トランスミッションゲートTG_1〜TG_nと連動してオンオフ制御される同数のトランスミッションゲートTB_1〜TB_nを備える。これにより、トランスミッションゲートTG_1〜TG_nのうち、オフ状態になっているトランスミッションゲートのオフ抵抗による影響もキャンセルすることができる。また、トランスミッションゲートTB_1〜TB_nは、トランスミッションゲートTG_1〜TG_nと連動して同時にオンオフ制御されるため、各トランスミッションゲートを構成するMOSトランジスタの寄生容量の充放電時のノイズが緩和される。そのため、分圧電圧Vcomがより高速に安定して、負電圧VPWの安定が高速化されるという効果が得られる。

【0025】

ここで、トランスミッションゲートTG_1〜TG_nは、請求項に記載の切り替えスイッチの一例であり、トランスミッションゲートTB_x、TB_1〜TB_nは、請求項に記載の補正スイッチの一例である。抵抗R3、R4は、請求項に記載の第1及び第2の抵抗の一例である。また、定電圧回路1、複数の分圧抵抗、トランスミッションゲートTG_1〜TG_n、抵抗R3、R4、トランスミッションゲートTB_xあるいはTB_1〜TB_n、コンパレータ2、を含む構成が、請求項に記載の負電圧検出回路の一例として挙げられる。

【0026】

以上、詳細に説明したように、前記実施例1、2を含む実施形態によれば、負電圧VPWの検出値を切り替えるトランスミッションゲートTG_1〜TG_nと同一の構成を有するトランスミッションゲートTB_xあるいはTB_1〜TB_nを備える。これにより、トランスミッションゲートTG_1〜TG_nのオン抵抗による影響をキャンセルすることができる。そのため、精度の高い負電圧VPWをプログラマブルに生成することが可能である。

【0027】

尚、本発明は前記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内での種々の改良、変更が可能であることは言うまでもない。

【0028】

例えば、トランスミッションゲートTG_1〜TG_n、トランスミッションゲートTB_x、TB_1〜TB_nについて、図3に実施例3として示されるように、カスケード接続で構成したスイッチを採用してもよい。これにより、スイッチ特性を確保することができる。

【0029】

また、実施例2において、トランスミッションゲートTB_1〜TB_nは、トランスミッションゲートTG_1〜TG_nと連動してオンオフ制御されるとしたが、これに限定されない。トランスミッションゲートTB_1〜TB_nのうち、いずれか1つを常時オン状態にして、他はオフ状態に保つようにしてもよい。

【0030】

その他、実施例1では、抵抗R3、トランスミッションゲートTB_x、抵抗R4の順に接続され、実施例2では、抵抗R3、抵抗R4、トランスミッションゲートTB_1〜TB_nの順に接続されたが、トランスミッションゲートTB_x、TB_1〜TB_nと抵抗R4との接続順は入れ替えられてもよいことは言うまでもない。

【符号の説明】

【0031】

1 定電圧回路

2 コンパレータ

3 負電圧発生装置

31 リングオシレータ

C1 コンデンサ

D1、D2 ダイオード

R1、R2 分圧抵抗

R3、R4 抵抗(第1及び第2の抵抗)

TB_x、TB_1〜TB_n トランスミッションゲート(補正スイッチ)

TG_1〜TG_n トランスミッションゲート(切り替えスイッチ)

【特許請求の範囲】

【請求項1】

負電圧を発生する負電圧発生装置と、前記負電圧発生装置の出力電圧を制御する負電圧検出回路と、を備える半導体装置であって、

前記負電圧検出回路は、

一定の電圧を出力する定電圧回路と、

前記定電圧回路の出力とグランドとの間に直列に接続された複数の分圧抵抗と、

一端が前記複数の分圧抵抗の各分圧点に接続され、他端が共通に接続された複数の切り替えスイッチと、

前記複数の切り替えスイッチの他端と前記負電圧発生装置の出力との間に直列に接続され、前記複数の分圧抵抗により分圧された前記定電圧回路の出力電圧と前記負電圧発生装置の出力電圧とを分圧する第1及び第2の抵抗と、

前記複数の切り替えスイッチと同一の構成を有するスイッチであって、前記第1及び第2の抵抗の分圧点と前記負電圧発生装置の出力との間で前記第1及び第2の抵抗と直列に接続され、オン状態に保たれる補正スイッチと、

前記第1及び第2の抵抗による分圧電圧の電圧レベルとグランドの電圧レベルとを比較し、比較結果を前記負電圧発生装置に出力するコンパレータと、

を備えることを特徴とする半導体装置。

【請求項2】

負電圧を発生する負電圧発生装置と、前記負電圧発生装置の出力電圧を制御する負電圧検出回路と、を備える半導体装置であって、

前記負電圧検出回路は、

一定の電圧を出力する定電圧回路と、

前記定電圧回路の出力とグランドとの間に直列に接続された複数の分圧抵抗と、

一端が前記複数の分圧抵抗の各分圧点に接続され、他端が共通に接続された複数の切り替えスイッチと、

前記複数の切り替えスイッチの他端と前記負電圧発生装置の出力との間に直列に接続され、前記複数の分圧抵抗により分圧された前記定電圧回路の出力電圧と前記負電圧発生装置の出力電圧とを分圧する第1及び第2の抵抗と、

前記複数の切り替えスイッチと同一の構成を有する同数のスイッチであって、互いに並列に接続されるとともに前記第1及び第2の抵抗の分圧点と前記負電圧発生装置の出力との間で前記第1及び第2の抵抗と直列に接続される複数の補正スイッチと、

前記第1及び第2の抵抗による分圧電圧の電圧レベルとグランドの電圧レベルとを比較し、比較結果を前記負電圧発生装置に出力するコンパレータと、

を備えることを特徴とする半導体装置。

【請求項3】

前記複数の補正スイッチのうち、いずれか1つはオン状態に保たれ、他はオフ状態に保たれる

ことを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記複数の補正スイッチは、前記複数の切り替えスイッチと連動してオンオフ制御される

ことを特徴とする請求項2に記載の半導体装置。

【請求項5】

前記切り替えスイッチと前記補正スイッチとは、カスケード接続で構成したスイッチである

ことを特徴とする請求項1乃至4のいずれかに記載の半導体装置。

【請求項6】

前記切り替えスイッチと前記補正スイッチとは、トランスミッションゲートである

ことを特徴とする請求項1乃至5のいずれかに記載の半導体装置。

【請求項1】

負電圧を発生する負電圧発生装置と、前記負電圧発生装置の出力電圧を制御する負電圧検出回路と、を備える半導体装置であって、

前記負電圧検出回路は、

一定の電圧を出力する定電圧回路と、

前記定電圧回路の出力とグランドとの間に直列に接続された複数の分圧抵抗と、

一端が前記複数の分圧抵抗の各分圧点に接続され、他端が共通に接続された複数の切り替えスイッチと、

前記複数の切り替えスイッチの他端と前記負電圧発生装置の出力との間に直列に接続され、前記複数の分圧抵抗により分圧された前記定電圧回路の出力電圧と前記負電圧発生装置の出力電圧とを分圧する第1及び第2の抵抗と、

前記複数の切り替えスイッチと同一の構成を有するスイッチであって、前記第1及び第2の抵抗の分圧点と前記負電圧発生装置の出力との間で前記第1及び第2の抵抗と直列に接続され、オン状態に保たれる補正スイッチと、

前記第1及び第2の抵抗による分圧電圧の電圧レベルとグランドの電圧レベルとを比較し、比較結果を前記負電圧発生装置に出力するコンパレータと、

を備えることを特徴とする半導体装置。

【請求項2】

負電圧を発生する負電圧発生装置と、前記負電圧発生装置の出力電圧を制御する負電圧検出回路と、を備える半導体装置であって、

前記負電圧検出回路は、

一定の電圧を出力する定電圧回路と、

前記定電圧回路の出力とグランドとの間に直列に接続された複数の分圧抵抗と、

一端が前記複数の分圧抵抗の各分圧点に接続され、他端が共通に接続された複数の切り替えスイッチと、

前記複数の切り替えスイッチの他端と前記負電圧発生装置の出力との間に直列に接続され、前記複数の分圧抵抗により分圧された前記定電圧回路の出力電圧と前記負電圧発生装置の出力電圧とを分圧する第1及び第2の抵抗と、

前記複数の切り替えスイッチと同一の構成を有する同数のスイッチであって、互いに並列に接続されるとともに前記第1及び第2の抵抗の分圧点と前記負電圧発生装置の出力との間で前記第1及び第2の抵抗と直列に接続される複数の補正スイッチと、

前記第1及び第2の抵抗による分圧電圧の電圧レベルとグランドの電圧レベルとを比較し、比較結果を前記負電圧発生装置に出力するコンパレータと、

を備えることを特徴とする半導体装置。

【請求項3】

前記複数の補正スイッチのうち、いずれか1つはオン状態に保たれ、他はオフ状態に保たれる

ことを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記複数の補正スイッチは、前記複数の切り替えスイッチと連動してオンオフ制御される

ことを特徴とする請求項2に記載の半導体装置。

【請求項5】

前記切り替えスイッチと前記補正スイッチとは、カスケード接続で構成したスイッチである

ことを特徴とする請求項1乃至4のいずれかに記載の半導体装置。

【請求項6】

前記切り替えスイッチと前記補正スイッチとは、トランスミッションゲートである

ことを特徴とする請求項1乃至5のいずれかに記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2011−29417(P2011−29417A)

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願番号】特願2009−173814(P2009−173814)

【出願日】平成21年7月27日(2009.7.27)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願日】平成21年7月27日(2009.7.27)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]