半導体装置

【課題】

活性領域と素子分離領域を別個の対象として応力を制御し,半導体装置の性能を向上する。

【解決手段】

半導体装置は、p−MOS領域を有する半導体基板と、半導体基板表面部に形成され、p−MOS領域内にp−MOS活性領域を画定する素子分離領域と、p−MOS活性領域を横断して,半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、p−MOSゲート電極構造を覆って、p−MOS活性領域上方に選択的に形成された圧縮応力膜と、p−MOS領域の素子分離領域上方に選択的に形成され,圧縮応力膜の応力を解放している応力解放領域と、を有し、p−MOSチャネル領域にゲート長方向の圧縮応力とゲート幅方向の引張応力を印加する。

活性領域と素子分離領域を別個の対象として応力を制御し,半導体装置の性能を向上する。

【解決手段】

半導体装置は、p−MOS領域を有する半導体基板と、半導体基板表面部に形成され、p−MOS領域内にp−MOS活性領域を画定する素子分離領域と、p−MOS活性領域を横断して,半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、p−MOSゲート電極構造を覆って、p−MOS活性領域上方に選択的に形成された圧縮応力膜と、p−MOS領域の素子分離領域上方に選択的に形成され,圧縮応力膜の応力を解放している応力解放領域と、を有し、p−MOSチャネル領域にゲート長方向の圧縮応力とゲート幅方向の引張応力を印加する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に半導体基板上方に、応力を内蔵したコンタクトエッチストッパ膜を形成した半導体装置に関する。

【背景技術】

【0002】

半導体集積回路装置に対する、高集積化、高速化の要求が高い。従来は半導体集積回路装置の主構成要素であるMOS電界効果トランジスタ(FET)を微細化することにより高集積化、高速化が進められてきた。微細化することにより、当然集積度は向上でき、ゲート長が短縮化されることにより動作速度も高くなる。微細化は、設計パターンをレジスト膜に転写するリソグラフィ技術の進歩によって支えられてきた。近年、要求される最小加工寸法が、リソグラフィに用いる光の波長以下になっており、MOSFETのより一層の微細化が困難になりつつある。

【0003】

なお、半導体基板上のゲート絶縁膜として酸化シリコン膜を用いた電界効果トランジスタが(ゲート電極として、金属でなく、半導体であるシリコンを用いていても)MOSFETと呼ばれてきた。FETの微細化と共に、ゲート絶縁膜として酸化窒化シリコン膜や、酸化シリコン膜上にHfO2等の高誘電率絶縁膜を積層した構造等も採用されるようになった。本願においては、酸化シリコン以外のゲート絶縁膜を有するFETもMOSFETと呼ぶ。すなわち、MOSFETは、絶縁ゲート電極を有する半導体電界効果トランジスタの意味である。

【0004】

低消費電力を意図する半導体集積回路装置の多くにおいては,nチャネルMOSFET(n−MOSFET)とpチャネルMOSFET(p−MOSFET)とで構成される相補型(C)MOSFET(CMOSと略記する)が用いられる。CMOS集積回路の高速化を実現するためには、n−MOSFETとp−MOSFETの両者の性能を向上することが望まれる。

【0005】

非特許文献1は、プラズマ(PE)化学気相堆積(CVD)で形成した窒化シリコン膜である、圧縮応力膜であるコンタクトエッチストッパ膜の圧縮応力を大きくすると,ゲート長方向に圧縮歪みがかかり、p−MOSのオン電流が増加し、n−MOSのオン電流が減少することを報告している。

【0006】

非特許文献2は、熱CVDにより形成した窒化シリコン膜である、引張応力膜であるコンタクトエッチストッパ膜の引張応力を大きくすると,ゲート長方向に引張歪がかかり、n−MOSのオン電流が増加し、p−MOSのオン電流が減少することを報告している。

【0007】

なお、圧縮応力膜とは、下地シリコン基板上に圧縮された状態で形成された膜を指す。圧縮応力膜は圧縮応力を内臓する。引張応力膜とは下地上に引張られた状態で形成された膜を言う。引張応力膜は引張応力を内臓する。

【0008】

このように、コンタクトエッチストッパ膜の内臓応力を増加すると、n−MOSFETとp−MOSの一方はオン電流が増大するが、他方はオン電流が減少し、相殺されるためCMOS全体としての性能は向上しない傾向がある。

【0009】

非特許文献3は、強い応力を内臓する窒化シリコン膜でコンタクトエッチストッパ膜を形成し,オン電流が減少する導電型のMOSFET領域に対して、Geイオンを注入し,応力を解放することを報告している。PE−CVDで強い圧縮応力を有する窒化シリコン膜のコンタクトエッチストッパ膜を形成する場合は、n−MOS領域にGeイオンを注入する。熱CVDで強い引張応力を有する窒化シリコン膜のコンタクトエッチストッパを形成する場合は、p−MOS領域にGeイオンを注入する。p−MOSFETのオン電流低下が抑制され、CMOS全体としての性能を向上することが可能となる。

【0010】

非特許文献4および特許文献1は、Si(001)面上,〈110〉方向にゲート長方向を配置した場合,n−MOSはゲート長方向の引張歪みに対してオン電流が増大し、ゲート幅方向の引張歪みに対してオン電流が増大し、p−MOSはゲート長方向の引張歪みに対してオン電流は減少し(ゲート長方向の圧縮歪みに対してオン電流は増大し),ゲート幅方向の引張歪みに対してオン電流は増大することを開示している。

【0011】

特許文献1は、さらにn−MOS領域上方には引張応力膜でコンタクトエッチストッパ膜を形成し、p−MOS領域上方には圧縮応力膜でコンタクトエッチストッパ膜を形成し、CMOS全体の特性を向上させること、コンタクトエッチストッパ膜の面積によって応力を調整することを開示する。

【0012】

特許文献2は、ゲート電極と素子分離領域との間の半導体表面をコンタクトエッチストッパとして機能する絶縁膜で覆った状態で、n−MOS領域上方に引張応力膜を形成し、p−MOS領域上方に圧縮応力膜を形成することを開示する。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2003−86708号公報

【特許文献2】特開2003−273240号公報

【非特許文献1】Ito et al.:IEDM 2000 Tech. Dig.,p.247

【非特許文献2】Ootsuka et al.:IEDM 2000 Tech. Dig.,p.575

【非特許文献3】Shimizu et al.:IEDM 2001 Tech. Dig.,p.433

【非特許文献4】Kumagai et al.:SSDM 2002,p.14

【発明の概要】

【発明が解決しようとする課題】

【0014】

本発明の目的は,応力を利用して性能を向上した半導体装置を提供することである。

【0015】

本発明の他の目的は,ゲート長方向,ゲート幅方向の応力を制御して、性能を向上した半導体装置を提供することである。

【0016】

本発明のさらに他の目的は,活性領域と素子分離領域を別個の対象として応力を制御し,性能を向上した半導体装置を提供することである。

【課題を解決するための手段】

【0017】

本発明の1観点によれば,

半導体基板と、

前記半導体基板に形成された素子分離領域と、

前記素子分離領域によって画定されたn型の第1活性領域と、

前記n型の第1活性領域上に形成されたp型ゲート電極と、

前記p型ゲート電極を覆って、前記第1活性領域上方に選択的に形成された圧縮応力膜と、

前記圧縮応力膜上に形成された層間絶縁膜と、

前記層間絶縁膜と前記圧縮応力膜を貫通して前記第1活性領域に達する開口部と、

前記開口部内に形成された導電性プラグと、

を有し、前記圧縮応力膜の端部は、前記p型ゲート電極のゲート幅方向において、前記素子分離領域と前記第1活性領域との境界上に位置する半導体装置

が提供される。

【発明の効果】

【0018】

チャネル領域に印加されるゲート長方向の応力、ゲート幅方向の応力により、MOSFETの性能が向上する。

【図面の簡単な説明】

【0019】

【図1】CMOS回路のオン電流を増加させることのできる応力をまとめた表と、応力を内蔵する膜をパターニングした時に発生する応力を説明する概略断面図である。

【図2(A)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す断面図ある。

【図2(B)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す平面図である。

【図2(C)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す断面図である。

【図2(D)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す平面図である。

【図2(E)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す断面図である。

【図2(F)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す平面図である。

【図2(G)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す断面図である。

【図2(H)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す平面図である。

【図3(A)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する断面図である。

【図3(B)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する平面図である。

【図3(C)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する断面図である。

【図3(D)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する平面図である。

【図3(E)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する断面図である。

【図3(F)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する平面図である。

【図3(G)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する断面図である。

【図3(H)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する平面図である。

【図4】MOS領域を活性領域とSTI領域とに分けて圧縮応力膜、引張応力膜を選択的に形成した時に発生し得る応力の種類を示す表及びコンタクトプラグの配置例を示す平面図である。

【図5】第1の実施例による半導体装置を示す断面図及び平面図である。

【図6(A)】第1の実施例の変形例を示す平面図である。

【図6(B)】第1の実施例の変形例を示す断面図である。

【図6(C)】第1の実施例の変形例を示す平面図である。

【図6(D)】第1の実施例の変形例を示す断面図である。

【図6(E)】第1の実施例の変形例を示す平面図である。

【図6(F)】第1の実施例の変形例を示す断面図である。

【図7】第2の実施例を示す断面図及び平面図である。

【図8(A)】第2の実施例の変形例を示す平面図である。

【図8(B)】第2の実施例の変形例を示す断面図である。

【図8(C)】第2の実施例の変形例を示す平面図である。

【図8(D)】第2の実施例の変形例を示す断面図である。

【図8(E)】第2の実施例の変形例を示す平面図である。

【図8(F)】第2の実施例の変形例を示す断面図である。

【図9】第3の実施例を示す断面図及び平面図である。

【図10】第4の実施例を示す断面図及び平面図である。

【図11】第5の実施例を示す断面図及び平面図である。

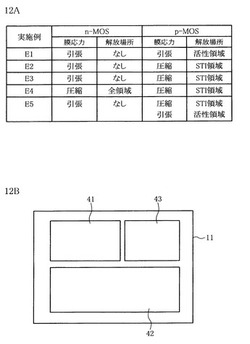

【図12】第1−第5の実施例の特徴をまとめた表及び半導体集積回路装置における実施例の応用例を示す平面図である。

【発明を実施するための形態】

【0020】

本発明者は、シリコン基板上に引張応力のコンタクトエッチストッパ膜を堆積し、このコンタクトエッチストッパ膜を部分的にエッチングした時の歪分布を計算した。平坦な面上に応力膜が堆積しても,シリコン基板に印加される応力は無視できる程度であり、応力膜が部分的に除去されたり、上方等に曲がったりした場合にシリコン基板に応力が印加されることが判った。

【0021】

引張応力のコンタクトエッチストッパ膜が残る領域のシリコン基板表面近傍にコンタクトエッチストッパ膜の縁に対して直角な横方向の圧縮歪が生じ、引張応力のコンタクトエッチストッパ膜をエッチング除去した領域のシリコン基板表面近傍にコンタクトエッチストッパ膜の縁に対して直角な横方向の引張歪が生じることを見出した。

【0022】

図1Aは、CMOSのn−MOSFETおよびp−MOSFET夫々のオン電流を増加させる歪の種類(引張歪,圧縮歪)をゲート長方向,深さ方向,ゲート幅方向それぞれについてまとめたものである。なお、深さ方向の歪はゲート長方向の歪と相補的な関係にある。非特許文献4および特許文献1が開示するように、n−MOSFETにおいてはゲート長方向、ゲート幅方向共に引張歪がオン電流を増加させるが、p−MOSFETにおいてはゲート長方向は圧縮歪、ゲート幅方向は引張歪がオン電流を増加させる。

【0023】

図1B−1Eは、上述の発明者の検討を概略的に示す断面図である。図1Bに示すように、平坦な表面を有するシリコン基板Sub上に引張応力膜TSを形成する。引張応力膜は例えば熱CVDで形成した窒化シリコン膜である。シリコン基板Subには歪は生じていない。

【0024】

図1Cに示すように、図1Bの引張応力膜TSを部分的に,選択的に除去し,応力解放部V1,V2,V3で画定された引張応力膜パターンTS1,TS2を残す。なお,応力解放部は応力を解放した領域であり,膜自体を除去するか,膜は残すがその応力を解放することで形成される。応力を解放するには例えばGeイオンを注入する。引張応力膜パターンTS1は,応力を解放した応力解放部V1,V2に挟まれ、引張応力膜パターンTS2は応力解放部V2,V3に挟まれている。

【0025】

応力解放部V1,V2、V3の引張応力が解放されると、残る引張応力膜パターンTS1、TS2を外側に引っ張る応力が消滅するので、引張応力膜パターンTS1、TS2は矢印で示すように縮もうとする。この力により引張応力膜パターンTS1、TS2下のシリコン基板Subには圧縮応力が印加される。応力解放部V2においては両側で外側に向かう応力が働くので、シリコン基板Subに引張応力が印加される。

【0026】

MOSFETにおいては、ゲート電極を覆って引張応力を内蔵するコンタクトエッチストッパ膜が形成される。コンタクトエッチストッパ膜は、チャネル領域上方でシリコン基板から離れる方向に曲がるので,応力解放部に相当する構造となる。チャネル領域には,ゲート電極両側の引張応力膜により、応力解放部同様、引張応力が働く。

【0027】

図1Dに示すように、平坦な表面を有するシリコン基板Sub上に圧縮応力膜CSを形成する。圧縮応力膜は例えばプラズマ(PE)CVDで形成した窒化シリコン膜で形成できる。全面に圧縮応力膜CSが形成されたシリコン基板Subには歪は生じていない。

【0028】

図1Eに示すように、図1Dの圧縮応力膜CSを部分的に,選択的に除去し、応力解放部V1,V2,V3で画定された圧縮応力膜パターンCS1,CS2を残す。圧縮応力膜パターンCS1は,圧縮応力を解放した応力解放部V1、V2に挟まれ、圧縮応力膜パターンCS2は応力解放部V2、V3に挟まれている。

【0029】

応力解放部V1,V2、V3の圧縮応力が解放されると,残る圧縮応力膜パターンCS1、CS2を圧縮する応力が消滅するので,圧縮応力膜パターンCS1,CS2は矢印で示すように拡がろうとする。この力により圧縮応力膜パターンCS1,CS2下のシリコン基板Subには引張応力が印加される。応力解放部V2においては両側で内側に向かう応力が働くので,シリコン基板Subに圧縮応力が印加される。

【0030】

MOSFETにおいて,ゲート電極を覆って圧縮応力を内臓するコンタクトエッチストッパ膜が形成されると、コンタクトエッチストッパ膜は、チャネル領域上方でシリコン基板から離れる方向に曲がる。応力解放部同様、チャネル領域には圧縮応力が働く。

【0031】

なお,応力を解放するため、イオン注入を行う場合、イオン注入する原子ないし原子群は,シリコン中に入っても電気的に影響を及ぼさないことが好ましい。シリコン基板の場合、Ge,Cなどの同族元素、またはAr等の不活性元素を用いることができよう。

【0032】

図2A−2Hは、MOSFETの上に引張応力膜を形成した時,どのような応力が生じるかを示す概略的断面図および平面図である。

【0033】

図2A、2Bは、引張応力膜がMOSFET領域全体に形成された状態を示す断面図,平面図である。シリコン基板表面部にシャロートレンチアイソレーション(STI)で形成された素子分離領域STIが形成され、活性領域ARを画定する。活性領域AR表面上に絶縁ゲート電極G,その側面上にサイドウォールSWが形成される。絶縁ゲート電極構造を覆って,引張応力膜TSが形成される。なお,平面図ではサイドウォールSWは図示を省略している。以下同様である。

【0034】

絶縁ゲート電極構造両側においては,引張応力膜TS1,TS2が基板表面に接しているが、絶縁ゲート電極構造上においては引張応力膜は基板表面から離れ、応力解放部V2を構成している。従って,縮まろうとする引張応力膜パターンTS1,TS2が矢印で示すような応力を印加し、絶縁ゲート電極下のシリコン基板(チャネル領域)表面は外側に向かう力を受け,引張応力が印加される。

【0035】

図2C、2Dは、引張応力膜がMOSFET領域中の活性領域上のみに配置され,素子分離領域STI上からは除去されている状態を示す断面図,平面図である。素子分離領域STI、活性領域AR,絶縁ゲート電極G,サイドウォールSWは、図2A、2Bと同様である。引張応力膜TSが形成され、素子分離領域STI上からは除去されている。引張応力膜を除去した応力解放部V1,V3を図2Dでは、点々を付して示している。

【0036】

絶縁ゲート電極構造両側の活性領域においては,引張応力膜パターンTS1、TS2が基板表面に接しているが、絶縁ゲート電極構造,素子分離領域STIにおいては引張応力膜は基板表面から離れるか,除去されて、応力解放部V1、V2、V3を構成している。従って,縮まろうとする引張応力膜パターンTS1、TS2が、絶縁ゲート電極G両側で矢印で示すような外側に向かう応力を印加し、絶縁ゲート電極G下のチャネル領域はゲート長方向に引張応力が印加される。

【0037】

さらに絶縁ゲート電極Gに沿う方向で、活性領域内側に向かう力が働き,ゲート幅方向には圧縮応力が働く。

【0038】

図2E、2Fは、引張応力膜がMOSFET領域中の素子分離領域STI上のみに残され、活性領域AR上からは除去されている状態を示す断面図、平面図である。シリコン表面上の絶縁ゲート電極G,その側面上のサイドウォールSWが構成する絶縁ゲート電極構造を覆って,引張応力膜TSが形成され、活性領域AR上からは除去されている。引張応力膜を除去した領域に点々を付して示している。その他の点は,図2A−2Dと同様である。

【0039】

素子分離領域STI上にのみ残された引張応力膜が,縮まろうとして、矢印で示すように,活性領域AR周辺で外側に向かう応力を印加する。絶縁ゲート電極Gに沿う方向で、活性領域外側に向かう力が働き,ゲート幅方向には引張応力が働く。

【0040】

図2G、2Hは、MOSFET領域上に形成された引張応力膜が全て除去された状態を示す。引張応力膜がすべて除去されるので、応力は働かない。実際に膜を除去するとすれば,膜を形成した意味がないが,上述のようにイオン注入などにより,応力を解放することにより応力的には除去したのと同等の効果が生じる。

【0041】

応力膜が,コンタクトエッチストッパ膜で形成される場合,素子分離領域上では応力解放のため,応力膜を除去してもよく,イオン注入などにより応力のみを解放し膜は残してもよい。活性領域上には,コンタクトエッチストッパ膜が必要であるので,応力解放はイオン注入などで行い,膜は残す。

【0042】

図3A−3Hは、MOSFETの上に圧縮応力膜を形成した時,どのような応力が生じるかを示す概略的断面図および平面図である。

【0043】

図3A、3Bは、圧縮応力膜がMOSFET領域全域に形成された状態を示す断面図,平面図である。シリコン表面上に絶縁ゲート電極G,その側面上にサイドウォールSWが形成され,この絶縁ゲート電極構造を覆って,圧縮応力膜CSが形成される。絶縁ゲート電極構造両側においては,圧縮応力膜CS1,CS2が基板表面に接しているが、絶縁ゲート電極構造においては圧縮応力膜は基板表面から離れ,応力解放部V2を構成している。従って,拡がろうとする圧縮応力膜パターンCS1,CS2が矢印で示すような応力を印加し、絶縁ゲート電極下のチャネル領域は内側に向かう力を受け,圧縮応力が印加される。

【0044】

図3C、3Dは、圧縮応力膜がMOSFET領域中の活性領域上のみに配置され,素子分離領域STI上からは応力が解放されている状態を示す断面図,平面図である。シリコン表面上の絶縁ゲート電極G,その側面上のサイドウォールSWが構成する絶縁ゲート電極構造を覆って、圧縮応力膜CSが形成され、素子分離領域STI上からは応力が解放されている。圧縮応力膜を除去した領域に点々を付して示している。

【0045】

絶縁ゲート電極構造両側の活性領域においては、圧縮応力膜CS1,CS2が基板表面に接しているが、絶縁ゲート電極構造,素子分離領域STIにおいては圧縮応力膜は基板表面から離れるか,除去されて、応力解放部V1,V2、V3を構成している。従って,拡がろうとする圧縮応力膜パターンCS1,CS2が、絶縁ゲート電極G両側で矢印で示すような内側に向かう応力を印加し、絶縁ゲート電極G下のチャネル領域にはゲート長方向に圧縮応力が印加される。さらに絶縁ゲート電極Gに沿うゲート幅方向で、活性領域外側に向かう力が働き、ゲート幅方向には引張応力が働く。

【0046】

図3E、3Fは、圧縮応力膜が、MOSFET領域中の素子分離領域STI上のみに配置され,活性領域AR上からは応力が解放されている状態を示す断面図,平面図である。シリコン表面上の絶縁ゲート電極G,その側面上のサイドウォールSWが構成する絶縁ゲート電極構造を覆って、圧縮応力膜CSが形成され,活性領域AR上からは応力が解放されている。圧縮応力膜を除去した領域に点々を付して示している。

【0047】

素子分離領域STI上にのみ残された圧縮応力膜が,拡がろうとして、矢印で示すように,活性領域AR周辺で内側に向かう応力を印加する。絶縁ゲート電極Gに沿う方向で、活性領域内側に向かう力が働き,ゲート幅方向には圧縮応力が働く。

【0048】

図3G、3Hは、MOSFET領域上に形成された圧縮応力膜が応力的には全て除去された状態を示す。圧縮応力膜がすべて除去されるので,応力は働かない。

【0049】

図4Aは,上述の検討結果をまとめて示す表である。MOSFET領域上に応力膜を形成し,応力を選択的に解放した時,ゲート長方向,深さ方向,ゲート幅方向に生じる歪を示す。なお,深さ方向の歪は,ゲート長方向の歪と相補的である。半導体装置において,所望の歪を得ようとするときは,この表に従って応力膜を選べばよい。(001)面シリコン基板の上に形成したMOSFETで、ゲート長方向が〈110〉方向の場合、nーMOSはゲート長方向,ゲート幅方向で引張歪がオン電流を増加し、p−MOSはゲート長方向の圧縮歪,ゲート幅方向の引張歪がオン電流を増加させる。

【0050】

ゲート長方向に所定(例えば引張)応力を働かせるには、所定(例えば引張)応力の応力膜を形成し,活性領域上の応力は保持する必要がある。ゲート幅方向に引張応力を働かせるには,引張応力膜を形成して,活性領域上の応力は解放するか,圧縮応力膜を形成してSTI領域では応力を解放する必要がある。

【0051】

図4Bは、コンタクトプラグの配置例を示す。活性領域AR上方のゲート電極Gの側壁上にサイドウォールSWが形成され、その両側にソースドレイン拡散層19が形成されている。絶縁ゲート電極構造を覆って、例えば圧縮応力膜が形成され、素子分離領域STI上で応力が解放されている。コンタクトホールCHおよびそれを埋め込む導電性プラグは、ゲート幅方向で部分的に、図示の例ではソース/ドレイン拡散層の各々の選択された2か所に形成され、その両側および中間にスペースSPを残す。サイドウォールSWとコンタクトホールCHとが接する領域では、シリコン表面と接する圧縮応力膜が除去されるが、スペースSPには圧縮応力膜が残る。STI上の圧縮応力膜を除去することにより、圧縮応力膜が拡張しようとして矢印で示すような応力を印加し、シリコン基板に所望の歪みを与えることができる。

【0052】

図5A−5Dは、第1の実施例によるCMOS構造を示す断面図,平面図である。図5Aに示すように、(001)面p型シリコン基板11の表面部にトレンチを形成し、絶縁層を埋め込んで、不要部を除去して、活性領域を画定するシャロートレンチアイソレーション(STI)による素子分離領域12を形成する。p型不純物、n型不純物を選択的に注入し,所望のpウェル13、nウェル14を形成する。活性領域表面を熱酸化し,必要に応じてさらに窒化し,ゲート絶縁膜15を形成する。

【0053】

ゲート絶縁膜上に多結晶シリコン層を、例えば厚さ約100nm堆積し,ゲート電極層を形成する。レジストパターンを用いてゲート電極層,ゲート絶縁膜をパターニングし,例えば〈110〉方向のゲート長50nmの絶縁ゲート電極G(Gn、Gpをまとめて指す)を形成する。絶縁ゲート電極G両側の活性領域に選択的にn型不純物,p型不純物をイオン注入し、n型エクステンションExn,p型エクステンションExpを形成する。

【0054】

絶縁ゲート電極Gを覆って酸化膜等の絶縁膜を堆積し,異方性エッチングを行なって絶縁ゲート電極G側壁上にのみサイドウォールSWを残す。サイドウォールSWをマスクとし、n型不純物,p型不純物を選択的にイオン注入し、n型ソース/ドレイン拡散層18、p型ソース/ドレイン拡散層19を形成する。ゲート電極にも不純物が注入され、n−MOS領域にn型ゲート電極Gn、p−MOS領域にp型ゲート電極Gpが形成される。必要に応じCo等のシリサイド反応可能な金属層を堆積し,シリサイド反応を行なってゲート電極G,ソース/ドレイン拡散層上にシリサイド層を形成する。

【0055】

このようにして形成されたCMOS構造を覆って,熱CVDにより,引張応力を有する窒化シリコン膜のコンタクトエッチストッパ膜21を堆積する。例えば,シリコンソースガスとしてジクロルシラン(DCS)+モノシラン(SiH4)+ジシラン(Si2H6)+Si2H4を5〜50sccm,窒素ソースガスとしてNH3を500〜10000sccm、その他のガスとしてN2+Arを500〜10000sccm流し,圧力0.1〜400torr,温度500〜700℃で熱CVDを行ない、引張応力1.4GPaを内臓する厚さ約80nmの窒化シリコン膜21を堆積する。

【0056】

図5Bは、図5Aに対応する平面図である。素子分離領域12が活性領域AR1、AR2を画定し、活性領域の中間部を横断して絶縁ゲート電極Gn、Gpが形成されている。サイドウォールSW、窒化シリコン膜21は図示を省略している。引張応力が形成され、その上にp−MOS活性領域AR2上に開口を有するレジストパターンPR1が形成される。

【0057】

図5Cは、図5BのVC−VC線に沿う断面図である。図5Cに示すようにシリコン基板上にレジスト膜を塗布し、p−MOS領域の活性領域AR2を露出する開口を有するレジストパターンPR1を露光現像する。レジストパターンPR1をマスクとしてGeイオンを加速エネルギ100keV、ドーズ量5×1014atoms/cm2で注入し,シリコン窒化膜21のp−MOS活性領域AR2上を選択的に応力解放する。

【0058】

図5Dに示すように,公知の工程により窒化シリコン膜21の上に酸化シリコン等の層間絶縁膜23を形成し,窒化シリコン膜21をコンタクトエッチストッパ膜として利用して、コンタクト孔をエッチングし,導電性プラグ25を埋め込む。導電性プラグ25を覆って層間絶縁膜27を堆積し、トレンチを形成して銅配線28を埋め込む。銅配線28を覆って層間絶縁膜30を形成し,トレンチとビア孔を形成し,銅配線31を埋め込む。層間絶縁膜形成,配線形成,の工程を必要回数繰り返し、CMOS構造を完成する。これらの配線形成工程は公知の技術によって行なう。

【0059】

このようなCMOS構造によれば,n−MOS領域は引っ張り応力を有するシリコン窒化膜で覆われるので,ゲート長方向に引張歪が生じ、オン電流が増加する。p−MOS領域においては,活性領域で引張応力が解放されているので,ゲート幅方向に引張歪が生じ、オン電流が増加する。n−MOSFETもp−MOSFETも性能が向上し、CMOS全体として性能が向上する。

【0060】

第1の実施例において、p−MOS領域は引張応力を有するコンタクトエッチストッパ膜で覆われるが、活性領域上の応力を解放することにより、チャネル領域にはゲート幅方向の引張歪が生じ、p−MOSFETのオン電流が増加する。この効果は、ゲート幅方向に関する応力解放が重要であり、ゲート長方向に関しては厳密ではない。

【0061】

図6A、6Bは、NOR型CMOS回路に対する応用例を示す。図6Aに示すように横に長いp−MOS活性領域ARpを横断して複数の絶縁ゲート電極Gp1、Gp2が形成される。隣接する絶縁ゲート間の活性領域は2つのp−MOSトランジスタの共通のソース/ドレイン領域として機能する。Geイオン注入用のレジストパターンPR2は、活性領域ARpに合わせた開口を有する。図6Bに示すように、連結された複数のp−MOSトランジスタを開口するレジストパターンPR2をマスクとして活性領域ARpにGeイオンを注入する。

【0062】

図6C、6Dは,第1の実施例の第1の変形例を示す。2つのp−MOS活性領域ARp1、ARp2がゲート長方向に並んで配置されている場合,その間の素子分離領域は、レジストで覆ってもよいが、図示の様に開口してしまってもよい。並んで配置された2つのp−MOS活性領域ARp1、ARp2を開口し、ゲート幅方向に関しては素子分離領域12の上を覆うレジストパターンPR2を形成する。図6Dに示すように,レジストパターンPR2をマスクとしてGeイオンを注入する。活性領域ARp1、ARp2上の引張応力が解放されるので、チャネル領域のゲート長方向の引張歪は解放され,ゲート幅方向で素子分離領域12上に残る引張応力により,チャネル領域にはゲート幅方向の引張歪が生じ、オン電流が増加する。

【0063】

図6E、6Fは、第1の実施例の第2の変形例を示す。p−MOS活性領域AR2を開口するレジストパターンPR3は,ゲート長方向で素子分離領域12も一部開口している。このようなレジストパターであっても、Geイオンの注入により活性領域上の引張応力は解放され、チャネル領域にはゲート幅方向で素子分離領域12上に残る引張応力膜により,引張歪が生じる。

【0064】

図7A−7Dは、第2の実施例による半導体装置の構造および主要製造工程を概略的に示す断面図,平面図である。図7Aに示すように,第1の実施例同様の工程により,(001)面p型シリコン基板11の表面部に活性領域AR1、AR2を画定するシャロートレンチアイソレーション(STI)による素子分離領域12、pウェル13、nウェル14、ゲート絶縁膜15、多結晶シリコン層16で構成された絶縁ゲート電極Gを形成する。絶縁ゲート電極G両側の活性領域に選択的にn型不純物,p型不純物をイオン注入し、n型エクステンションExn、p型エクステンションExpを形成し、絶縁ゲート電極G側壁上にサイドウォールSWを形成する。

【0065】

サイドウォールSWをマスクとし、n型不純物,p型不純物を選択的にイオン注入し、n−MOSにn型ゲート電極Gn、n型ソース/ドレイン拡散層18、p−MOSにp型ゲート電極Gp、p型ソース/ドレイン拡散層19を形成する。必要に応じCo等のシリサイド反応可能な金属層を堆積し,シリサイド反応を行なってゲート電極G,ソース/ドレイン拡散層上にシリサイド層を形成する。ここまでは第1の実施例と同様である。

【0066】

本実施例においては、n−MOS領域上には引張応力を有する窒化シリコン膜21、p−MOS領域上には圧縮応力を有する窒化シリコン膜32を形成する。

【0067】

絶縁ゲート電極Gn、Gpを覆って,シリコン基板上に圧縮応力を有する窒化シリコン膜32を堆積する。例えば,シリコンソースガスとしてSiH4を100〜1000sccm、窒素ソースガスとしてNH3を500〜10000sccm、その他のガスとしてAr+N2を500〜10000sccm流し,圧力0.1〜400toorで、RF電力100〜1000Wのプラズマを生じさせ、PECVDで圧縮応力約1.4GPa,厚さ約80nmの窒化シリコン膜32を堆積する。

【0068】

レジストパターンでp−MOS領域を覆い、n−MOS領域上の圧縮応力窒化シリコン膜32を除去する。次に,露出したn−MOS領域を覆って,実施例1同様の熱CVDにより、1.4GPaの引張応力を有する厚さ約80nmの窒化シリコン膜21を形成する。n−MOS領域をレジストパターンで覆い,露出したp−MOS領域上の引張応力窒化シリコン膜21をエッチングして除去する。このようにして,図示の構造を得る。なお、最初に引張応力を有する窒化シリコン膜21を形成し、p−MOS領域上の引張応力窒化シリコン膜21を除去し、圧縮応力を有する窒化シリコン膜32を堆積し、n−MOS領域上の圧縮応力窒化シリコン膜32を除去してもよい。

【0069】

図7Bに示すように,n−MOS領域全体と,p−MOS領域の活性領域とを覆うレジストパターンPR4を形成する。p−MOS領域の素子分離領域12上が露出される。

【0070】

図7C、7Dに示すように、Geイオンを加速エネルギ100keV,ドーズ量5×1014atoms/cm2で注入し、p−MOS領域の素子分離領域12上の圧縮応力窒化シリコン膜32中の圧縮応力を解放する。図7Cはゲート長方向の断面図,図7Dはゲート幅方向の断面図である。

【0071】

p−MOS領域の活性領域AR2上に残る圧縮応力窒化シリコン膜32により,絶縁ゲート電極Gp下方のチャネル領域にはゲート長方向の圧縮応力が印加される。ゲート幅方向の素子分離領域上の圧縮応力が解放されるので、活性領域AR2上に選択的に残る圧縮応力窒化シリコン膜32の拡がろうとする力により、ゲート幅方向に引張歪が生じ、p−MOSトランジスタのオン電流が増大する。

【0072】

第2の実施例によれば、n−MOSトランジスタは第1の実施例同様であり、p−MOS領域は圧縮応力を有するコンタクトエッチストッパ膜で覆われ、素子分離領域上の応力を解放することにより、p−MOS領域のチャネル領域にゲート長方向の圧縮歪,ゲート幅方向の引張歪が生じる。p−MOSトランジスタの性能がさらに向上すると期待される。

【0073】

図8A、8Bは、NOR型CMOS回路に対する応用例を示す。図8Aに示すように横に長いp−MOS活性領域ARpを横断して複数の絶縁ゲート電極Gp1、Gp2が形成される。Geイオン注入用のレジストパターンPR5は、p−MOS領域の素子分離領域を露出する。図8Bに示すように、連結された複数のp−MOSトランジスタをマスクするレジストパターンPR5を用いて、素子分離領域12上にGeイオンを注入する。

【0074】

図8C、8Dは,第2の実施例の第1の変形例を示す。2つのp−MOS活性領域ARp1、ARp2がゲート長方向に並んで配置されている場合,その間の素子分離領域は、レジストを開口してもよいが,図示の様に覆ってしまってもよい。並んで配置された2つのp−MOS活性領域ARp1、ARp2を覆い,ゲート幅方向に関しては活性領域ARp1、ARp2の上を覆うレジストパターンPR6を形成する。図8Dに示すように、レジストパターンPR6をマスクとしてGeイオンを注入する。活性領域ARp1、ARp2外側の素子分離領域12上の圧縮応力が解放されるので、チャネル領域のゲート幅方向で引張歪が生じ、オン電流が増加する。

【0075】

図8E、8Fは、第2の実施例の第2の変形例を示す。p−MOS活性領域AR2を覆うレジストパターンPR7は,ゲート幅方向では素子分離領域12上からは除去されている。しかし、ゲート長方向では、素子分離領域12上に延在している。このようなレジストパターンであっても、Geイオンの注入により素子分離領域上の圧縮応力は解放され、チャネル領域にはゲート長方向の圧縮歪みとゲート幅方向の引張歪が生じる。

【0076】

図9A−9Dは,第3の実施例による半導体装置の構造および主要製造工程を概略的に示す断面図,平面図である。図9Aに示すように,第1の実施例同様の工程により,(001)面p型シリコン基板11の表面部に活性領域AR1、AR2を画定するシャロートレンチアイソレーション(STI)による素子分離領域12、pウェル13、nウェル14、ゲート絶縁膜15と多結晶シリコン層16で構成された絶縁ゲート電極Gを形成する。絶縁ゲート電極G両側の活性領域に選択的にn型不純物,p型不純物をイオン注入し、n型エクステンションExn,p型エクステンションExpを形成し、絶縁ゲート電極G側壁上にサイドウォールSWを形成する。

【0077】

サイドウォールSWをマスクとし、n型不純物,p型不純物を選択的にイオン注入し、n−MOSFETにn型ゲート電極Gn、n型ソース/ドレイン拡散層18、p−MOSFETにp型ゲート電極Gp、p型ソース/ドレイン拡散層19を形成する。必要に応じCo等のシリサイド反応可能な金属層を堆積し,シリサイド反応を行なってゲート電極G,ソース/ドレイン拡散層18、19上にシリサイド層を形成する。n−MOS領域上には引張応力を有する窒化シリコン膜21、p−MOS領域上には圧縮応力を有する窒化シリコン膜32を形成する。ここまでは第2の実施例と同様である。

【0078】

図9Bに示すように,n−MOS領域全体と,p−MOS領域の活性領域とを覆うレジストパターンPR8を形成する。p−MOS領域の素子分離領域12上が露出される。

【0079】

図9C、9Dに示すように、圧縮応力窒化シリコン膜32をエッチングして、p−MOS領域の素子分離領域12上の圧縮応力窒化シリコン膜32中の圧縮応力を解放する。図9Cはゲート長方向の断面図、図9Dはゲート幅方向の断面図である。p−MOS領域の活性領域AR2上に残る圧縮応力窒化シリコン膜32により,絶縁ゲート電極Gp下方のチャネル領域にはゲート長方向の圧縮応力が印加される。

【0080】

ゲート幅方向の素子分離領域上の圧縮応力が解放されるので、活性領域AR2上に選択的に残る圧縮応力窒化シリコン膜32が拡がろうとし、外側に向う力を発揮する。ゲート幅方向に引張歪が生じ、p−MOSトランジスタのオン電流が増大する。

【0081】

第3の実施例によれば、n−MOSトランジスタは第1の実施例同様であり、p−MOS領域のチャネル領域にゲート長方向の圧縮歪,ゲート幅方向の引張歪が生じる。p−MOSトランジスタの性能がさらに向上すると期待される。

【0082】

図10A−10Dは、第4の実施例による半導体装置の構成を概略的に示す断面図及び平面図である。

【0083】

図10Aに示すように、半導体基板11に前述の実施例同様の工程により、n−MOSFET、p−MOSFETを作成する。ゲート電極構造を覆って、半導体基板上に圧縮応力を有する窒化シリコン膜のコンタクトエッチストッパ膜32を堆積する。

【0084】

図10Bは、半導体基板を上方より観察した平面図である。STIによる素子分離領域12により、n−MOS活性領域AR1、p−MOS活性領域AR2が画定されている。活性領域AR1、AR2を横切って、ゲート電極構造Gn、Gpが形成されている。

【0085】

図10Cに示すように、ゲート電極構造を覆って半導体基板全面上に圧縮応力膜32が形成され、この圧縮応力膜32の上に、レジストパターンが形成される。レジストパターンPR9は、p−MOS活性領域AR2の上にのみ形成される。

【0086】

図10C、10Dで示すように、レジストパターンPR9をマスクとしてGeイオンを注入する。図10Cは、ゲート長方向に沿う断面図であり、図10Dはゲート幅方向の断面図である。

【0087】

n−MOS領域においては、全コンタクトエッチストッパ膜の応力が解放される。従って、圧縮応力に基づくオン電流の低下は低減される。p−MOS領域においては、素子分離領域12上の応力のみが解放される。活性領域上に残る圧縮応力膜は外側に広がろうとする。ゲート長方向においては、圧縮応力が働き、ゲート幅方向においては引張応力が働く。従って、p−MOSFETのオン電流は増加する。

【0088】

図11A−11Cは、第5の実施例による半導体装置の構成を概略的に示す断面図及び平面図である。図11A、11Bは、ゲート長方向及びゲート幅方向の断面図であり、図11Cは平面図である。本実施例においては、p‐MOS活性領域上にのみ圧縮応力膜のコンタクトエッチストッパ膜32が形成される。圧縮応力膜32の範囲は図9A−9Dに示す第3の実施例と同様である。n−MOS領域全域及びp−MOS領域の素子分離領域上には引張応力膜のコンタクトエッチストッパ膜21が形成される。引張応力膜21の範囲は、図5A−5Dに示す第1の実施例と同様である。

【0089】

n−MOSFETにおいては、第1の実施例同様、ゲート長方向に引張応力が働き、オン電流が増加する。p−MOSFETにおいては、第2、第3の実施例同様、圧縮応力膜32は、素子分離領域上で応力解放されており、引張応力膜21は、活性領域で応力解放されていると考えることができる。すなわち、図11Bに示すように、コンタクトエッチストッパ膜21,32は、ゲート幅方向で、活性領域を外側に拡げようとする力を発揮する。従って、p−MOSFETは、ゲート長方向に圧縮応力、ゲート幅方向に引張応力を受け、オン電流を増加させる。

【0090】

図12Aは、以上5つの実施例の特徴をまとめた表である。n‐MOSFETのゲート長方向に引張応力を生じさせるためには、活性領域上に引張応力膜を形成する必要がある。もし,素子分離領域の応力を解放するとゲート幅方向に圧縮応力が生じることになる。これは好ましくないので、この場合応力解放場所は「なし」となる。従って,ゲート幅方向には応力は発生しない。実施例E1、E2、E3、E5がこの構成を有する。

【0091】

実施例E4においては、圧縮応力膜の圧縮応力を全領域で解放しているため、n−MOS領域に応力は発生しない。圧縮応力によってオン電流が減少するところを、防止している。

【0092】

n−MOSFTのゲート幅方向に引張応力を働かせるには、引張応力膜であれば活性領域の応力を解放すればよいが、そうすると、ゲート長方向の応力が「なし」となってしまい効果が相殺される。圧縮応力膜であれば素子分離領域の応力を解放すればよいが、活性領域上に圧縮応力膜が残るとゲート長方向に圧縮応力が発生し、効果が相殺される。実施例においてはそのような構成は採用されていない。

【0093】

p−MOSFETのゲート長方向に圧縮応力を働かせるには、少なくとも活性領域上に圧縮応力膜を作成する必要がある。実施例E2、E3、E4、E5がこの構成を採用する。

【0094】

ゲート幅方向に引張応力を生じさせるためには、引張応力膜であれば活性領域上の応力を開放させればよい。実施例E1、E5がこの構成を採用する。又、圧縮応力膜であれば素子分離領域上の応力を解放すればよい。実施例E2、E3、E4、E5がこの構成を採用する。

【0095】

実施例E1は、引張応力膜のみを用い、n‐MOSFETにおいてはゲート長方向に引張応力を生じさせ、p−MOSFETにおいては、ゲート幅方向に引張応力を生じさせている。

【0096】

実施例E4は、圧縮応力膜のみを用い、p−MOSFETにおいてはゲート長方向に圧縮応力、ゲート幅方向に引張応力を生じさせている。但し、n−MOSFETにおいては応力は生じていない。他の実施例E2、E3、E5は、引張応力膜と圧縮応力膜を用い、n−MOSFETにはゲート長方向の引張応力、p−MOSFETにはゲート長方向の圧縮応力のゲート幅方向の引張応力を生じさせている。

【0097】

このような構成により、CMOSFETのオン電流を向上させられるが、露光工程が追加となる。このため、レイアウトに対する制約が発生することがある。例えば、スタティック(S)RAMに上述の実施例の構成を適用しようとすると、SRAMの面積が増加することがあり得る。又、入出力回路の特性は既存の品種と同じ性能が要求されることがある。

【0098】

図12Bは、半導体集積回路装置の構成を概略的に示す平面図である。半導体集積回路装置は、チップ11内に論理回路41、SRAM回路42、入出力(I/O)回路43を含む。上述の実施例による応力膜構造は、論理回路41のみに適応され、入出力回路43、SRAM回路42には採用されない。

【0099】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、応力膜として窒化シリコン膜を用いる場合を説明したが、適当な応力を生じる誘電体膜であれば窒化シリコンに制限されない。CMOSFETの構成としては、公知の種々の構成を採用することができる。その他、種々の変更、改良、組み合わせが可能_ことは当業者に自明であろう。

【0100】

以下,本発明の特徴を付記する。

【0101】

(付記1)

pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記pチャネル型トランジスタ領域内にpチャネル型活性領域を画定する素子分離領域と、

前記pチャネル型活性領域を横断して,前記半導体基板上方に形成され、下方にpチャネル領域を画定するpチャネル型ゲート電極構造と、

前記pチャネル型ゲート電極構造を覆って、前記pチャネル型活性領域上方に選択的に形成された圧縮応力膜と、

前記pチャネル型トランジスタ領域の素子分離領域上方に選択的に形成され,前記圧縮応力膜の応力を解放している応力解放領域と、

を有し、前記pチャネル型活性領域上方の前記圧縮応力膜が前記pチャネル領域にゲート長方向の圧縮応力を印加し、前記圧縮応力膜と前記応力解放領域が前記pチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0102】

(付記2)

前記圧縮応力膜が、窒化シリコン膜である付記1記載の半導体装置。

【0103】

(付記3)

前記応力解放領域が、イオン注入領域または前記圧縮応力膜を除去した領域で形成される付記1記載の半導体装置。

【0104】

(付記4)

前記イオン注入領域が、電気的に不活性な不純物イオンを注入された領域である付記3記載の半導体装置。

【0105】

(付記5)

前記応力解放領域が、前記圧縮応力膜を除去した領域で形成され、さらに前記pチャネル型トランジスタ領域の素子分離領域上に選択的に形成された引張応力膜を有し,前記引張応力膜も前記pチャネル領域にゲート幅方向の引張応力を印加する付記1記載の半導体装置。

【0106】

(付記6)

前記圧縮応力膜がプラズマCVDで形成された窒化シリコン膜であり,前記引張応力膜が熱CVDで形成された窒化シリコン膜である付記5記載の半導体装置。

【0107】

(付記7)

前記半導体基板がnチャネル型トランジスタ領域も有し、

前記素子分離領域が、前記nチャネル型トランジスタ領域内にnチャネル型活性領域を画定し、

さらに、

前記nチャネル型活性領域を横断して,前記半導体基板上方に形成され、下方にnチャネル領域を画定するnチャネル型ゲート電極構造と、

前記nチャネル型ゲート電極構造を覆って,前記nチャネル型トランジスタ領域上方に形成された絶縁膜と、

を有する付記1〜4のいずれか1項記載の半導体装置。

【0108】

(付記8)

前記絶縁膜が窒化シリコン膜である付記7記載の半導体装置。

【0109】

(付記9)

前記絶縁膜が,引張応力を有する膜であり、前記nチャネル領域にゲート長方向の引っ張り応力を印加する付記8記載の半導体装置。

【0110】

(付記10)

前記絶縁膜が,前記圧縮応力膜と同一の膜であり,全域で応力が解放されている付記7記載の半導体装置。

【0111】

(付記11)

pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記pチャネル型トランジスタ領域内にpチャネル型活性領域を画定する素子分離領域と、

前記pチャネル型活性領域を横断して,前記半導体基板上方に形成され、下方にpチャネル領域を画定するpチャネル型ゲート電極構造と、

前記pチャネル型トランジスタ領域の素子分離領域上方に選択的に形成された引張応力膜と、

前記pチャネル型ゲート電極構造を覆って、前記pチャネル型活性領域上方に選択的に形成され,前記引張応力膜と同一膜で形成され、応力が解放されている絶縁膜と、

を有し、前記pチャネル型トランジスタ領域の素子分離領域上方の前記引張応力膜が前記pチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0112】

(付記12)

前記引張応力膜と,前記絶縁膜とが窒化シリコン膜である付記11記載の半導体装置。

【0113】

(付記13)

前記半導体基板がnチャネル型トランジスタ領域も有し、

前記素子分離領域が、前記nチャネル型トランジスタ領域内にnチャネル型活性領域を画定し、

さらに、

前記nチャネル型活性領域を横断して,前記半導体基板上方に形成され、下方にnチャネル領域を画定するnチャネル型ゲート電極構造と、

前記nチャネル型ゲート電極構造を覆って,前記nチャネル型トランジスタ領域上方に形成され,前記引張応力膜と同一膜で形成された引張応力膜と、

を有する付記11記載の半導体装置。

【0114】

(付記14)

前記半導体基板が、(001)面を有するシリコン基板であり、前記ゲート長方向が〈110〉方向である付記1〜13のいずれか1項記載の半導体装置。

【0115】

(付記15)

nチャネル型トランジスタ領域、pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記nチャネル型トランジスタ領域内にn−MOS活性領域を画定し、前記pチャネル型トランジスタ領域内にp−MOS活性領域を画定する素子分離領域と、

前記n−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され,下方にn−MOSチャネル領域を画定するn−MOSゲート電極構造と、

前記p−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、

前記n−MOSゲート電極構造、p−MOSゲート電極構造を覆って、前記半導体基板上方に形成され,引張応力を有するコンタクトエッチストッパ膜と、

前記pチャネル型トランジスタ領域のp−MOS活性領域上方で選択的に前記コンタクトエッチストッパ膜中に形成され,前記コンタクトエッチストッパ膜の応力を解放する応力解放領域と、

を有し、前記nチャネル型トランジスタ領域上方のコンタクトエッチストッパ膜が前記n−MOSチャネル領域のゲート長方向に引張応力を印加し,前記pチャネル型トランジスタ領域の前記応力解放領域が前記p−MOSチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0116】

(付記16)

前記応力解放領域が、イオン注入領域で形成される付記15記載の半導体装置。

【0117】

(付記17)

nチャネル型トランジスタ領域、pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記nチャネル型トランジスタ領域内にn−MOS活性領域を画定し、前記pチャネル型トランジスタ領域内にp−MOS活性領域を画定する素子分離領域と、

前記n−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にn−MOSチャネル領域を画定するn−MOSゲート電極構造と、

前記p−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、

前記n−MOSゲート電極構造を覆って,前記nチャネル型トランジスタ領域上方に形成され、引張応力を有する第1コンタクトエッチストッパ膜と、

前記pチャネル型トランジスタ領域を覆って,前記pチャネル型トランジスタ領域上方に形成され,圧縮応力を有する第2コンタクトエッチストッパ膜と、

前記pチャネル型トランジスタ領域の前記素子分離領域上方で選択的に前記第2コンタクトエッチストッパ膜中に形成され,前記第2コンタクトエッチストッパ膜の圧縮応力を解放する応力解放領域と、

を有し、前記第1コンタクトエッチストッパ膜が前記n−MOSチャネル領域のゲート長方向に引張応力を印加し、前記p−MOS活性領域上方の第2コンタクトエッチストッパ膜が前記p−MOSチャネル領域にゲート長方向の圧縮応力を印加し、前記応力解放領域と前記p−MOS活性領域上方の第2コンタクトエッチストッパ膜とが前記p−MOSチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0118】

(付記18)

前記応力解放領域が,前記第2コンタクトエッチストッパ膜が除去された領域またはイオン注入領域で形成されている付記17記載の半導体装置。

【0119】

(付記19)

nチャネル型トランジスタ領域、pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記nチャネル型トランジスタ領域内にn−MOS活性領域を画定し、前記pチャネル型トランジスタ領域内にp−MOS活性領域を画定する素子分離領域と、

前記n−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され,下方にn−MOSチャネル領域を画定するn−MOSゲート電極構造と、

前記p−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、

前記n−MOSゲート電極構造、p−MOS電極構造を覆って、前記半導体基板上方に形成され,圧縮応力を有するコンタクトエッチストッパ膜と、

前記nチャネル型トランジスタ領域の全域と、前記pチャネル型トランジスタ領域の素子分離領域上方で選択的に前記コンタクトエッチストッパ膜中に形成され,前記コンタクトエッチストッパ膜の応力を解放する応力解放領域と、

を有し、前記pチャネル型トランジスタ領域上方の前記コンタクトエッチストッパ膜が前記p−MOSチャネル領域のゲート長方向に圧縮応力を印加し、前記p−MOS活性領域上方のコンタクトエッチストッパ膜と前記応力解放領域が前記p−MOSチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0120】

(付記20)

前記応力解放領域が、イオン注入領域で形成されている付記19記載の半導体装置。

【0121】

(付記21)

nチャネル型トランジスタ領域、pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記nチャネル型トランジスタ領域内にn−MOS活性領域を画定し、前記pチャネル型トランジスタ領域内にp−MOS活性領域を画定する素子分離領域と、

前記n−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され,下方にn−MOSチャネル領域を画定するn−MOSゲート電極構造と、

前記p−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、

前記nチャネル型トランジスタ領域と前記pチャネル型トランジスタ領域の素子分離領域を覆って、前記半導体基板上方に形成され、引張応力を有する第1コンタクトエッチストッパ膜と、

前記p−MOS活性領域を覆って,前記半導体基板上方に形成され、圧縮応力を有する第2コンタクトエッチストッパ膜と、

を有し、前記第1コンタクトエッチストッパ膜が前記n−MOSチャネル領域のゲート長方向に引張応力を印加し、前記第2コンタクトエッチストッパ膜が前記p−MOSチャネル領域にゲート長方向の圧縮応力を印加し、前記pチャネル型トランジスタ領域の素子分離領域上の第1コンタクトエッチストッパ膜と前記p−MOS活性領域上の第2コンタクトエッチストッパ膜とが、前記p−MOSチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0122】

(付記22)

前記素子分離領域が、前記pチャネル型トランジスタ領域に前記p−MOS活性領域と、隣接する他のp−MOS活性領域とを画定し、前記応力解放領域が、前記p−MOS活性領域と前記他のp−MOS活性領域のゲート幅方向に関して前記素子分離領域上に形成されている付記17〜20のいずれか1項記載の半導体装置。

【0123】

(付記23)

前記イオン注入領域が、電気的に不活性な不純物イオンを注入された領域である付記16、18、20のいずれか1項記載の半導体装置。

【0124】

(付記24)

前記半導体基板が、(001)面を有するシリコン基板であり、前記ゲート長方向が〈110〉方向である付記15〜23のいずれか1項記載の半導体装置。

【符号の説明】

【0125】

TS 引張応力膜

CS 圧縮応力膜

V 応力解放箇所

Sub 半導体基板

AR 活性領域

G ゲート電極構造

SW サイドウォール

11 シリコン基板

13 pウエル

14 nウエル

15 ゲート絶縁膜

16 多結晶シリコン膜

18 n型ソース/ドレイン拡散層

19 p型ソース/ドレイン拡散層

21 引張応力内蔵窒化シリコン膜

Ex エクステンション領域

23 層間絶縁膜

25 導電性プラグ

27 層間絶縁膜

28 銅配線

30 層間絶縁膜

31 デュアルダマシン銅配線

32 圧縮応力内蔵窒化シリコン膜

PR レジストパターン

【技術分野】

【0001】

本発明は、半導体装置に関し、特に半導体基板上方に、応力を内蔵したコンタクトエッチストッパ膜を形成した半導体装置に関する。

【背景技術】

【0002】

半導体集積回路装置に対する、高集積化、高速化の要求が高い。従来は半導体集積回路装置の主構成要素であるMOS電界効果トランジスタ(FET)を微細化することにより高集積化、高速化が進められてきた。微細化することにより、当然集積度は向上でき、ゲート長が短縮化されることにより動作速度も高くなる。微細化は、設計パターンをレジスト膜に転写するリソグラフィ技術の進歩によって支えられてきた。近年、要求される最小加工寸法が、リソグラフィに用いる光の波長以下になっており、MOSFETのより一層の微細化が困難になりつつある。

【0003】

なお、半導体基板上のゲート絶縁膜として酸化シリコン膜を用いた電界効果トランジスタが(ゲート電極として、金属でなく、半導体であるシリコンを用いていても)MOSFETと呼ばれてきた。FETの微細化と共に、ゲート絶縁膜として酸化窒化シリコン膜や、酸化シリコン膜上にHfO2等の高誘電率絶縁膜を積層した構造等も採用されるようになった。本願においては、酸化シリコン以外のゲート絶縁膜を有するFETもMOSFETと呼ぶ。すなわち、MOSFETは、絶縁ゲート電極を有する半導体電界効果トランジスタの意味である。

【0004】

低消費電力を意図する半導体集積回路装置の多くにおいては,nチャネルMOSFET(n−MOSFET)とpチャネルMOSFET(p−MOSFET)とで構成される相補型(C)MOSFET(CMOSと略記する)が用いられる。CMOS集積回路の高速化を実現するためには、n−MOSFETとp−MOSFETの両者の性能を向上することが望まれる。

【0005】

非特許文献1は、プラズマ(PE)化学気相堆積(CVD)で形成した窒化シリコン膜である、圧縮応力膜であるコンタクトエッチストッパ膜の圧縮応力を大きくすると,ゲート長方向に圧縮歪みがかかり、p−MOSのオン電流が増加し、n−MOSのオン電流が減少することを報告している。

【0006】

非特許文献2は、熱CVDにより形成した窒化シリコン膜である、引張応力膜であるコンタクトエッチストッパ膜の引張応力を大きくすると,ゲート長方向に引張歪がかかり、n−MOSのオン電流が増加し、p−MOSのオン電流が減少することを報告している。

【0007】

なお、圧縮応力膜とは、下地シリコン基板上に圧縮された状態で形成された膜を指す。圧縮応力膜は圧縮応力を内臓する。引張応力膜とは下地上に引張られた状態で形成された膜を言う。引張応力膜は引張応力を内臓する。

【0008】

このように、コンタクトエッチストッパ膜の内臓応力を増加すると、n−MOSFETとp−MOSの一方はオン電流が増大するが、他方はオン電流が減少し、相殺されるためCMOS全体としての性能は向上しない傾向がある。

【0009】

非特許文献3は、強い応力を内臓する窒化シリコン膜でコンタクトエッチストッパ膜を形成し,オン電流が減少する導電型のMOSFET領域に対して、Geイオンを注入し,応力を解放することを報告している。PE−CVDで強い圧縮応力を有する窒化シリコン膜のコンタクトエッチストッパ膜を形成する場合は、n−MOS領域にGeイオンを注入する。熱CVDで強い引張応力を有する窒化シリコン膜のコンタクトエッチストッパを形成する場合は、p−MOS領域にGeイオンを注入する。p−MOSFETのオン電流低下が抑制され、CMOS全体としての性能を向上することが可能となる。

【0010】

非特許文献4および特許文献1は、Si(001)面上,〈110〉方向にゲート長方向を配置した場合,n−MOSはゲート長方向の引張歪みに対してオン電流が増大し、ゲート幅方向の引張歪みに対してオン電流が増大し、p−MOSはゲート長方向の引張歪みに対してオン電流は減少し(ゲート長方向の圧縮歪みに対してオン電流は増大し),ゲート幅方向の引張歪みに対してオン電流は増大することを開示している。

【0011】

特許文献1は、さらにn−MOS領域上方には引張応力膜でコンタクトエッチストッパ膜を形成し、p−MOS領域上方には圧縮応力膜でコンタクトエッチストッパ膜を形成し、CMOS全体の特性を向上させること、コンタクトエッチストッパ膜の面積によって応力を調整することを開示する。

【0012】

特許文献2は、ゲート電極と素子分離領域との間の半導体表面をコンタクトエッチストッパとして機能する絶縁膜で覆った状態で、n−MOS領域上方に引張応力膜を形成し、p−MOS領域上方に圧縮応力膜を形成することを開示する。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2003−86708号公報

【特許文献2】特開2003−273240号公報

【非特許文献1】Ito et al.:IEDM 2000 Tech. Dig.,p.247

【非特許文献2】Ootsuka et al.:IEDM 2000 Tech. Dig.,p.575

【非特許文献3】Shimizu et al.:IEDM 2001 Tech. Dig.,p.433

【非特許文献4】Kumagai et al.:SSDM 2002,p.14

【発明の概要】

【発明が解決しようとする課題】

【0014】

本発明の目的は,応力を利用して性能を向上した半導体装置を提供することである。

【0015】

本発明の他の目的は,ゲート長方向,ゲート幅方向の応力を制御して、性能を向上した半導体装置を提供することである。

【0016】

本発明のさらに他の目的は,活性領域と素子分離領域を別個の対象として応力を制御し,性能を向上した半導体装置を提供することである。

【課題を解決するための手段】

【0017】

本発明の1観点によれば,

半導体基板と、

前記半導体基板に形成された素子分離領域と、

前記素子分離領域によって画定されたn型の第1活性領域と、

前記n型の第1活性領域上に形成されたp型ゲート電極と、

前記p型ゲート電極を覆って、前記第1活性領域上方に選択的に形成された圧縮応力膜と、

前記圧縮応力膜上に形成された層間絶縁膜と、

前記層間絶縁膜と前記圧縮応力膜を貫通して前記第1活性領域に達する開口部と、

前記開口部内に形成された導電性プラグと、

を有し、前記圧縮応力膜の端部は、前記p型ゲート電極のゲート幅方向において、前記素子分離領域と前記第1活性領域との境界上に位置する半導体装置

が提供される。

【発明の効果】

【0018】

チャネル領域に印加されるゲート長方向の応力、ゲート幅方向の応力により、MOSFETの性能が向上する。

【図面の簡単な説明】

【0019】

【図1】CMOS回路のオン電流を増加させることのできる応力をまとめた表と、応力を内蔵する膜をパターニングした時に発生する応力を説明する概略断面図である。

【図2(A)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す断面図ある。

【図2(B)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す平面図である。

【図2(C)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す断面図である。

【図2(D)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す平面図である。

【図2(E)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す断面図である。

【図2(F)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す平面図である。

【図2(G)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す断面図である。

【図2(H)】MOSFET上に引張応力膜を形成した時発生し得る応力を示す平面図である。

【図3(A)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する断面図である。

【図3(B)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する平面図である。

【図3(C)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する断面図である。

【図3(D)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する平面図である。

【図3(E)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する断面図である。

【図3(F)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する平面図である。

【図3(G)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する断面図である。

【図3(H)】MOSFET構造の上に圧縮応力膜を形成した時に、発生させることのできる応力を説明する平面図である。

【図4】MOS領域を活性領域とSTI領域とに分けて圧縮応力膜、引張応力膜を選択的に形成した時に発生し得る応力の種類を示す表及びコンタクトプラグの配置例を示す平面図である。

【図5】第1の実施例による半導体装置を示す断面図及び平面図である。

【図6(A)】第1の実施例の変形例を示す平面図である。

【図6(B)】第1の実施例の変形例を示す断面図である。

【図6(C)】第1の実施例の変形例を示す平面図である。

【図6(D)】第1の実施例の変形例を示す断面図である。

【図6(E)】第1の実施例の変形例を示す平面図である。

【図6(F)】第1の実施例の変形例を示す断面図である。

【図7】第2の実施例を示す断面図及び平面図である。

【図8(A)】第2の実施例の変形例を示す平面図である。

【図8(B)】第2の実施例の変形例を示す断面図である。

【図8(C)】第2の実施例の変形例を示す平面図である。

【図8(D)】第2の実施例の変形例を示す断面図である。

【図8(E)】第2の実施例の変形例を示す平面図である。

【図8(F)】第2の実施例の変形例を示す断面図である。

【図9】第3の実施例を示す断面図及び平面図である。

【図10】第4の実施例を示す断面図及び平面図である。

【図11】第5の実施例を示す断面図及び平面図である。

【図12】第1−第5の実施例の特徴をまとめた表及び半導体集積回路装置における実施例の応用例を示す平面図である。

【発明を実施するための形態】

【0020】

本発明者は、シリコン基板上に引張応力のコンタクトエッチストッパ膜を堆積し、このコンタクトエッチストッパ膜を部分的にエッチングした時の歪分布を計算した。平坦な面上に応力膜が堆積しても,シリコン基板に印加される応力は無視できる程度であり、応力膜が部分的に除去されたり、上方等に曲がったりした場合にシリコン基板に応力が印加されることが判った。

【0021】

引張応力のコンタクトエッチストッパ膜が残る領域のシリコン基板表面近傍にコンタクトエッチストッパ膜の縁に対して直角な横方向の圧縮歪が生じ、引張応力のコンタクトエッチストッパ膜をエッチング除去した領域のシリコン基板表面近傍にコンタクトエッチストッパ膜の縁に対して直角な横方向の引張歪が生じることを見出した。

【0022】

図1Aは、CMOSのn−MOSFETおよびp−MOSFET夫々のオン電流を増加させる歪の種類(引張歪,圧縮歪)をゲート長方向,深さ方向,ゲート幅方向それぞれについてまとめたものである。なお、深さ方向の歪はゲート長方向の歪と相補的な関係にある。非特許文献4および特許文献1が開示するように、n−MOSFETにおいてはゲート長方向、ゲート幅方向共に引張歪がオン電流を増加させるが、p−MOSFETにおいてはゲート長方向は圧縮歪、ゲート幅方向は引張歪がオン電流を増加させる。

【0023】

図1B−1Eは、上述の発明者の検討を概略的に示す断面図である。図1Bに示すように、平坦な表面を有するシリコン基板Sub上に引張応力膜TSを形成する。引張応力膜は例えば熱CVDで形成した窒化シリコン膜である。シリコン基板Subには歪は生じていない。

【0024】

図1Cに示すように、図1Bの引張応力膜TSを部分的に,選択的に除去し,応力解放部V1,V2,V3で画定された引張応力膜パターンTS1,TS2を残す。なお,応力解放部は応力を解放した領域であり,膜自体を除去するか,膜は残すがその応力を解放することで形成される。応力を解放するには例えばGeイオンを注入する。引張応力膜パターンTS1は,応力を解放した応力解放部V1,V2に挟まれ、引張応力膜パターンTS2は応力解放部V2,V3に挟まれている。

【0025】

応力解放部V1,V2、V3の引張応力が解放されると、残る引張応力膜パターンTS1、TS2を外側に引っ張る応力が消滅するので、引張応力膜パターンTS1、TS2は矢印で示すように縮もうとする。この力により引張応力膜パターンTS1、TS2下のシリコン基板Subには圧縮応力が印加される。応力解放部V2においては両側で外側に向かう応力が働くので、シリコン基板Subに引張応力が印加される。

【0026】

MOSFETにおいては、ゲート電極を覆って引張応力を内蔵するコンタクトエッチストッパ膜が形成される。コンタクトエッチストッパ膜は、チャネル領域上方でシリコン基板から離れる方向に曲がるので,応力解放部に相当する構造となる。チャネル領域には,ゲート電極両側の引張応力膜により、応力解放部同様、引張応力が働く。

【0027】

図1Dに示すように、平坦な表面を有するシリコン基板Sub上に圧縮応力膜CSを形成する。圧縮応力膜は例えばプラズマ(PE)CVDで形成した窒化シリコン膜で形成できる。全面に圧縮応力膜CSが形成されたシリコン基板Subには歪は生じていない。

【0028】

図1Eに示すように、図1Dの圧縮応力膜CSを部分的に,選択的に除去し、応力解放部V1,V2,V3で画定された圧縮応力膜パターンCS1,CS2を残す。圧縮応力膜パターンCS1は,圧縮応力を解放した応力解放部V1、V2に挟まれ、圧縮応力膜パターンCS2は応力解放部V2、V3に挟まれている。

【0029】

応力解放部V1,V2、V3の圧縮応力が解放されると,残る圧縮応力膜パターンCS1、CS2を圧縮する応力が消滅するので,圧縮応力膜パターンCS1,CS2は矢印で示すように拡がろうとする。この力により圧縮応力膜パターンCS1,CS2下のシリコン基板Subには引張応力が印加される。応力解放部V2においては両側で内側に向かう応力が働くので,シリコン基板Subに圧縮応力が印加される。

【0030】

MOSFETにおいて,ゲート電極を覆って圧縮応力を内臓するコンタクトエッチストッパ膜が形成されると、コンタクトエッチストッパ膜は、チャネル領域上方でシリコン基板から離れる方向に曲がる。応力解放部同様、チャネル領域には圧縮応力が働く。

【0031】

なお,応力を解放するため、イオン注入を行う場合、イオン注入する原子ないし原子群は,シリコン中に入っても電気的に影響を及ぼさないことが好ましい。シリコン基板の場合、Ge,Cなどの同族元素、またはAr等の不活性元素を用いることができよう。

【0032】

図2A−2Hは、MOSFETの上に引張応力膜を形成した時,どのような応力が生じるかを示す概略的断面図および平面図である。

【0033】

図2A、2Bは、引張応力膜がMOSFET領域全体に形成された状態を示す断面図,平面図である。シリコン基板表面部にシャロートレンチアイソレーション(STI)で形成された素子分離領域STIが形成され、活性領域ARを画定する。活性領域AR表面上に絶縁ゲート電極G,その側面上にサイドウォールSWが形成される。絶縁ゲート電極構造を覆って,引張応力膜TSが形成される。なお,平面図ではサイドウォールSWは図示を省略している。以下同様である。

【0034】

絶縁ゲート電極構造両側においては,引張応力膜TS1,TS2が基板表面に接しているが、絶縁ゲート電極構造上においては引張応力膜は基板表面から離れ、応力解放部V2を構成している。従って,縮まろうとする引張応力膜パターンTS1,TS2が矢印で示すような応力を印加し、絶縁ゲート電極下のシリコン基板(チャネル領域)表面は外側に向かう力を受け,引張応力が印加される。

【0035】

図2C、2Dは、引張応力膜がMOSFET領域中の活性領域上のみに配置され,素子分離領域STI上からは除去されている状態を示す断面図,平面図である。素子分離領域STI、活性領域AR,絶縁ゲート電極G,サイドウォールSWは、図2A、2Bと同様である。引張応力膜TSが形成され、素子分離領域STI上からは除去されている。引張応力膜を除去した応力解放部V1,V3を図2Dでは、点々を付して示している。

【0036】

絶縁ゲート電極構造両側の活性領域においては,引張応力膜パターンTS1、TS2が基板表面に接しているが、絶縁ゲート電極構造,素子分離領域STIにおいては引張応力膜は基板表面から離れるか,除去されて、応力解放部V1、V2、V3を構成している。従って,縮まろうとする引張応力膜パターンTS1、TS2が、絶縁ゲート電極G両側で矢印で示すような外側に向かう応力を印加し、絶縁ゲート電極G下のチャネル領域はゲート長方向に引張応力が印加される。

【0037】

さらに絶縁ゲート電極Gに沿う方向で、活性領域内側に向かう力が働き,ゲート幅方向には圧縮応力が働く。

【0038】

図2E、2Fは、引張応力膜がMOSFET領域中の素子分離領域STI上のみに残され、活性領域AR上からは除去されている状態を示す断面図、平面図である。シリコン表面上の絶縁ゲート電極G,その側面上のサイドウォールSWが構成する絶縁ゲート電極構造を覆って,引張応力膜TSが形成され、活性領域AR上からは除去されている。引張応力膜を除去した領域に点々を付して示している。その他の点は,図2A−2Dと同様である。

【0039】

素子分離領域STI上にのみ残された引張応力膜が,縮まろうとして、矢印で示すように,活性領域AR周辺で外側に向かう応力を印加する。絶縁ゲート電極Gに沿う方向で、活性領域外側に向かう力が働き,ゲート幅方向には引張応力が働く。

【0040】

図2G、2Hは、MOSFET領域上に形成された引張応力膜が全て除去された状態を示す。引張応力膜がすべて除去されるので、応力は働かない。実際に膜を除去するとすれば,膜を形成した意味がないが,上述のようにイオン注入などにより,応力を解放することにより応力的には除去したのと同等の効果が生じる。

【0041】

応力膜が,コンタクトエッチストッパ膜で形成される場合,素子分離領域上では応力解放のため,応力膜を除去してもよく,イオン注入などにより応力のみを解放し膜は残してもよい。活性領域上には,コンタクトエッチストッパ膜が必要であるので,応力解放はイオン注入などで行い,膜は残す。

【0042】

図3A−3Hは、MOSFETの上に圧縮応力膜を形成した時,どのような応力が生じるかを示す概略的断面図および平面図である。

【0043】

図3A、3Bは、圧縮応力膜がMOSFET領域全域に形成された状態を示す断面図,平面図である。シリコン表面上に絶縁ゲート電極G,その側面上にサイドウォールSWが形成され,この絶縁ゲート電極構造を覆って,圧縮応力膜CSが形成される。絶縁ゲート電極構造両側においては,圧縮応力膜CS1,CS2が基板表面に接しているが、絶縁ゲート電極構造においては圧縮応力膜は基板表面から離れ,応力解放部V2を構成している。従って,拡がろうとする圧縮応力膜パターンCS1,CS2が矢印で示すような応力を印加し、絶縁ゲート電極下のチャネル領域は内側に向かう力を受け,圧縮応力が印加される。

【0044】

図3C、3Dは、圧縮応力膜がMOSFET領域中の活性領域上のみに配置され,素子分離領域STI上からは応力が解放されている状態を示す断面図,平面図である。シリコン表面上の絶縁ゲート電極G,その側面上のサイドウォールSWが構成する絶縁ゲート電極構造を覆って、圧縮応力膜CSが形成され、素子分離領域STI上からは応力が解放されている。圧縮応力膜を除去した領域に点々を付して示している。

【0045】

絶縁ゲート電極構造両側の活性領域においては、圧縮応力膜CS1,CS2が基板表面に接しているが、絶縁ゲート電極構造,素子分離領域STIにおいては圧縮応力膜は基板表面から離れるか,除去されて、応力解放部V1,V2、V3を構成している。従って,拡がろうとする圧縮応力膜パターンCS1,CS2が、絶縁ゲート電極G両側で矢印で示すような内側に向かう応力を印加し、絶縁ゲート電極G下のチャネル領域にはゲート長方向に圧縮応力が印加される。さらに絶縁ゲート電極Gに沿うゲート幅方向で、活性領域外側に向かう力が働き、ゲート幅方向には引張応力が働く。

【0046】

図3E、3Fは、圧縮応力膜が、MOSFET領域中の素子分離領域STI上のみに配置され,活性領域AR上からは応力が解放されている状態を示す断面図,平面図である。シリコン表面上の絶縁ゲート電極G,その側面上のサイドウォールSWが構成する絶縁ゲート電極構造を覆って、圧縮応力膜CSが形成され,活性領域AR上からは応力が解放されている。圧縮応力膜を除去した領域に点々を付して示している。

【0047】

素子分離領域STI上にのみ残された圧縮応力膜が,拡がろうとして、矢印で示すように,活性領域AR周辺で内側に向かう応力を印加する。絶縁ゲート電極Gに沿う方向で、活性領域内側に向かう力が働き,ゲート幅方向には圧縮応力が働く。

【0048】

図3G、3Hは、MOSFET領域上に形成された圧縮応力膜が応力的には全て除去された状態を示す。圧縮応力膜がすべて除去されるので,応力は働かない。

【0049】

図4Aは,上述の検討結果をまとめて示す表である。MOSFET領域上に応力膜を形成し,応力を選択的に解放した時,ゲート長方向,深さ方向,ゲート幅方向に生じる歪を示す。なお,深さ方向の歪は,ゲート長方向の歪と相補的である。半導体装置において,所望の歪を得ようとするときは,この表に従って応力膜を選べばよい。(001)面シリコン基板の上に形成したMOSFETで、ゲート長方向が〈110〉方向の場合、nーMOSはゲート長方向,ゲート幅方向で引張歪がオン電流を増加し、p−MOSはゲート長方向の圧縮歪,ゲート幅方向の引張歪がオン電流を増加させる。

【0050】

ゲート長方向に所定(例えば引張)応力を働かせるには、所定(例えば引張)応力の応力膜を形成し,活性領域上の応力は保持する必要がある。ゲート幅方向に引張応力を働かせるには,引張応力膜を形成して,活性領域上の応力は解放するか,圧縮応力膜を形成してSTI領域では応力を解放する必要がある。

【0051】

図4Bは、コンタクトプラグの配置例を示す。活性領域AR上方のゲート電極Gの側壁上にサイドウォールSWが形成され、その両側にソースドレイン拡散層19が形成されている。絶縁ゲート電極構造を覆って、例えば圧縮応力膜が形成され、素子分離領域STI上で応力が解放されている。コンタクトホールCHおよびそれを埋め込む導電性プラグは、ゲート幅方向で部分的に、図示の例ではソース/ドレイン拡散層の各々の選択された2か所に形成され、その両側および中間にスペースSPを残す。サイドウォールSWとコンタクトホールCHとが接する領域では、シリコン表面と接する圧縮応力膜が除去されるが、スペースSPには圧縮応力膜が残る。STI上の圧縮応力膜を除去することにより、圧縮応力膜が拡張しようとして矢印で示すような応力を印加し、シリコン基板に所望の歪みを与えることができる。

【0052】

図5A−5Dは、第1の実施例によるCMOS構造を示す断面図,平面図である。図5Aに示すように、(001)面p型シリコン基板11の表面部にトレンチを形成し、絶縁層を埋め込んで、不要部を除去して、活性領域を画定するシャロートレンチアイソレーション(STI)による素子分離領域12を形成する。p型不純物、n型不純物を選択的に注入し,所望のpウェル13、nウェル14を形成する。活性領域表面を熱酸化し,必要に応じてさらに窒化し,ゲート絶縁膜15を形成する。

【0053】

ゲート絶縁膜上に多結晶シリコン層を、例えば厚さ約100nm堆積し,ゲート電極層を形成する。レジストパターンを用いてゲート電極層,ゲート絶縁膜をパターニングし,例えば〈110〉方向のゲート長50nmの絶縁ゲート電極G(Gn、Gpをまとめて指す)を形成する。絶縁ゲート電極G両側の活性領域に選択的にn型不純物,p型不純物をイオン注入し、n型エクステンションExn,p型エクステンションExpを形成する。

【0054】

絶縁ゲート電極Gを覆って酸化膜等の絶縁膜を堆積し,異方性エッチングを行なって絶縁ゲート電極G側壁上にのみサイドウォールSWを残す。サイドウォールSWをマスクとし、n型不純物,p型不純物を選択的にイオン注入し、n型ソース/ドレイン拡散層18、p型ソース/ドレイン拡散層19を形成する。ゲート電極にも不純物が注入され、n−MOS領域にn型ゲート電極Gn、p−MOS領域にp型ゲート電極Gpが形成される。必要に応じCo等のシリサイド反応可能な金属層を堆積し,シリサイド反応を行なってゲート電極G,ソース/ドレイン拡散層上にシリサイド層を形成する。

【0055】

このようにして形成されたCMOS構造を覆って,熱CVDにより,引張応力を有する窒化シリコン膜のコンタクトエッチストッパ膜21を堆積する。例えば,シリコンソースガスとしてジクロルシラン(DCS)+モノシラン(SiH4)+ジシラン(Si2H6)+Si2H4を5〜50sccm,窒素ソースガスとしてNH3を500〜10000sccm、その他のガスとしてN2+Arを500〜10000sccm流し,圧力0.1〜400torr,温度500〜700℃で熱CVDを行ない、引張応力1.4GPaを内臓する厚さ約80nmの窒化シリコン膜21を堆積する。

【0056】

図5Bは、図5Aに対応する平面図である。素子分離領域12が活性領域AR1、AR2を画定し、活性領域の中間部を横断して絶縁ゲート電極Gn、Gpが形成されている。サイドウォールSW、窒化シリコン膜21は図示を省略している。引張応力が形成され、その上にp−MOS活性領域AR2上に開口を有するレジストパターンPR1が形成される。

【0057】

図5Cは、図5BのVC−VC線に沿う断面図である。図5Cに示すようにシリコン基板上にレジスト膜を塗布し、p−MOS領域の活性領域AR2を露出する開口を有するレジストパターンPR1を露光現像する。レジストパターンPR1をマスクとしてGeイオンを加速エネルギ100keV、ドーズ量5×1014atoms/cm2で注入し,シリコン窒化膜21のp−MOS活性領域AR2上を選択的に応力解放する。

【0058】

図5Dに示すように,公知の工程により窒化シリコン膜21の上に酸化シリコン等の層間絶縁膜23を形成し,窒化シリコン膜21をコンタクトエッチストッパ膜として利用して、コンタクト孔をエッチングし,導電性プラグ25を埋め込む。導電性プラグ25を覆って層間絶縁膜27を堆積し、トレンチを形成して銅配線28を埋め込む。銅配線28を覆って層間絶縁膜30を形成し,トレンチとビア孔を形成し,銅配線31を埋め込む。層間絶縁膜形成,配線形成,の工程を必要回数繰り返し、CMOS構造を完成する。これらの配線形成工程は公知の技術によって行なう。

【0059】

このようなCMOS構造によれば,n−MOS領域は引っ張り応力を有するシリコン窒化膜で覆われるので,ゲート長方向に引張歪が生じ、オン電流が増加する。p−MOS領域においては,活性領域で引張応力が解放されているので,ゲート幅方向に引張歪が生じ、オン電流が増加する。n−MOSFETもp−MOSFETも性能が向上し、CMOS全体として性能が向上する。

【0060】

第1の実施例において、p−MOS領域は引張応力を有するコンタクトエッチストッパ膜で覆われるが、活性領域上の応力を解放することにより、チャネル領域にはゲート幅方向の引張歪が生じ、p−MOSFETのオン電流が増加する。この効果は、ゲート幅方向に関する応力解放が重要であり、ゲート長方向に関しては厳密ではない。

【0061】

図6A、6Bは、NOR型CMOS回路に対する応用例を示す。図6Aに示すように横に長いp−MOS活性領域ARpを横断して複数の絶縁ゲート電極Gp1、Gp2が形成される。隣接する絶縁ゲート間の活性領域は2つのp−MOSトランジスタの共通のソース/ドレイン領域として機能する。Geイオン注入用のレジストパターンPR2は、活性領域ARpに合わせた開口を有する。図6Bに示すように、連結された複数のp−MOSトランジスタを開口するレジストパターンPR2をマスクとして活性領域ARpにGeイオンを注入する。

【0062】

図6C、6Dは,第1の実施例の第1の変形例を示す。2つのp−MOS活性領域ARp1、ARp2がゲート長方向に並んで配置されている場合,その間の素子分離領域は、レジストで覆ってもよいが、図示の様に開口してしまってもよい。並んで配置された2つのp−MOS活性領域ARp1、ARp2を開口し、ゲート幅方向に関しては素子分離領域12の上を覆うレジストパターンPR2を形成する。図6Dに示すように,レジストパターンPR2をマスクとしてGeイオンを注入する。活性領域ARp1、ARp2上の引張応力が解放されるので、チャネル領域のゲート長方向の引張歪は解放され,ゲート幅方向で素子分離領域12上に残る引張応力により,チャネル領域にはゲート幅方向の引張歪が生じ、オン電流が増加する。

【0063】

図6E、6Fは、第1の実施例の第2の変形例を示す。p−MOS活性領域AR2を開口するレジストパターンPR3は,ゲート長方向で素子分離領域12も一部開口している。このようなレジストパターであっても、Geイオンの注入により活性領域上の引張応力は解放され、チャネル領域にはゲート幅方向で素子分離領域12上に残る引張応力膜により,引張歪が生じる。

【0064】

図7A−7Dは、第2の実施例による半導体装置の構造および主要製造工程を概略的に示す断面図,平面図である。図7Aに示すように,第1の実施例同様の工程により,(001)面p型シリコン基板11の表面部に活性領域AR1、AR2を画定するシャロートレンチアイソレーション(STI)による素子分離領域12、pウェル13、nウェル14、ゲート絶縁膜15、多結晶シリコン層16で構成された絶縁ゲート電極Gを形成する。絶縁ゲート電極G両側の活性領域に選択的にn型不純物,p型不純物をイオン注入し、n型エクステンションExn、p型エクステンションExpを形成し、絶縁ゲート電極G側壁上にサイドウォールSWを形成する。

【0065】

サイドウォールSWをマスクとし、n型不純物,p型不純物を選択的にイオン注入し、n−MOSにn型ゲート電極Gn、n型ソース/ドレイン拡散層18、p−MOSにp型ゲート電極Gp、p型ソース/ドレイン拡散層19を形成する。必要に応じCo等のシリサイド反応可能な金属層を堆積し,シリサイド反応を行なってゲート電極G,ソース/ドレイン拡散層上にシリサイド層を形成する。ここまでは第1の実施例と同様である。

【0066】

本実施例においては、n−MOS領域上には引張応力を有する窒化シリコン膜21、p−MOS領域上には圧縮応力を有する窒化シリコン膜32を形成する。

【0067】

絶縁ゲート電極Gn、Gpを覆って,シリコン基板上に圧縮応力を有する窒化シリコン膜32を堆積する。例えば,シリコンソースガスとしてSiH4を100〜1000sccm、窒素ソースガスとしてNH3を500〜10000sccm、その他のガスとしてAr+N2を500〜10000sccm流し,圧力0.1〜400toorで、RF電力100〜1000Wのプラズマを生じさせ、PECVDで圧縮応力約1.4GPa,厚さ約80nmの窒化シリコン膜32を堆積する。

【0068】

レジストパターンでp−MOS領域を覆い、n−MOS領域上の圧縮応力窒化シリコン膜32を除去する。次に,露出したn−MOS領域を覆って,実施例1同様の熱CVDにより、1.4GPaの引張応力を有する厚さ約80nmの窒化シリコン膜21を形成する。n−MOS領域をレジストパターンで覆い,露出したp−MOS領域上の引張応力窒化シリコン膜21をエッチングして除去する。このようにして,図示の構造を得る。なお、最初に引張応力を有する窒化シリコン膜21を形成し、p−MOS領域上の引張応力窒化シリコン膜21を除去し、圧縮応力を有する窒化シリコン膜32を堆積し、n−MOS領域上の圧縮応力窒化シリコン膜32を除去してもよい。

【0069】

図7Bに示すように,n−MOS領域全体と,p−MOS領域の活性領域とを覆うレジストパターンPR4を形成する。p−MOS領域の素子分離領域12上が露出される。

【0070】

図7C、7Dに示すように、Geイオンを加速エネルギ100keV,ドーズ量5×1014atoms/cm2で注入し、p−MOS領域の素子分離領域12上の圧縮応力窒化シリコン膜32中の圧縮応力を解放する。図7Cはゲート長方向の断面図,図7Dはゲート幅方向の断面図である。

【0071】

p−MOS領域の活性領域AR2上に残る圧縮応力窒化シリコン膜32により,絶縁ゲート電極Gp下方のチャネル領域にはゲート長方向の圧縮応力が印加される。ゲート幅方向の素子分離領域上の圧縮応力が解放されるので、活性領域AR2上に選択的に残る圧縮応力窒化シリコン膜32の拡がろうとする力により、ゲート幅方向に引張歪が生じ、p−MOSトランジスタのオン電流が増大する。

【0072】

第2の実施例によれば、n−MOSトランジスタは第1の実施例同様であり、p−MOS領域は圧縮応力を有するコンタクトエッチストッパ膜で覆われ、素子分離領域上の応力を解放することにより、p−MOS領域のチャネル領域にゲート長方向の圧縮歪,ゲート幅方向の引張歪が生じる。p−MOSトランジスタの性能がさらに向上すると期待される。

【0073】

図8A、8Bは、NOR型CMOS回路に対する応用例を示す。図8Aに示すように横に長いp−MOS活性領域ARpを横断して複数の絶縁ゲート電極Gp1、Gp2が形成される。Geイオン注入用のレジストパターンPR5は、p−MOS領域の素子分離領域を露出する。図8Bに示すように、連結された複数のp−MOSトランジスタをマスクするレジストパターンPR5を用いて、素子分離領域12上にGeイオンを注入する。

【0074】

図8C、8Dは,第2の実施例の第1の変形例を示す。2つのp−MOS活性領域ARp1、ARp2がゲート長方向に並んで配置されている場合,その間の素子分離領域は、レジストを開口してもよいが,図示の様に覆ってしまってもよい。並んで配置された2つのp−MOS活性領域ARp1、ARp2を覆い,ゲート幅方向に関しては活性領域ARp1、ARp2の上を覆うレジストパターンPR6を形成する。図8Dに示すように、レジストパターンPR6をマスクとしてGeイオンを注入する。活性領域ARp1、ARp2外側の素子分離領域12上の圧縮応力が解放されるので、チャネル領域のゲート幅方向で引張歪が生じ、オン電流が増加する。

【0075】

図8E、8Fは、第2の実施例の第2の変形例を示す。p−MOS活性領域AR2を覆うレジストパターンPR7は,ゲート幅方向では素子分離領域12上からは除去されている。しかし、ゲート長方向では、素子分離領域12上に延在している。このようなレジストパターンであっても、Geイオンの注入により素子分離領域上の圧縮応力は解放され、チャネル領域にはゲート長方向の圧縮歪みとゲート幅方向の引張歪が生じる。

【0076】

図9A−9Dは,第3の実施例による半導体装置の構造および主要製造工程を概略的に示す断面図,平面図である。図9Aに示すように,第1の実施例同様の工程により,(001)面p型シリコン基板11の表面部に活性領域AR1、AR2を画定するシャロートレンチアイソレーション(STI)による素子分離領域12、pウェル13、nウェル14、ゲート絶縁膜15と多結晶シリコン層16で構成された絶縁ゲート電極Gを形成する。絶縁ゲート電極G両側の活性領域に選択的にn型不純物,p型不純物をイオン注入し、n型エクステンションExn,p型エクステンションExpを形成し、絶縁ゲート電極G側壁上にサイドウォールSWを形成する。

【0077】

サイドウォールSWをマスクとし、n型不純物,p型不純物を選択的にイオン注入し、n−MOSFETにn型ゲート電極Gn、n型ソース/ドレイン拡散層18、p−MOSFETにp型ゲート電極Gp、p型ソース/ドレイン拡散層19を形成する。必要に応じCo等のシリサイド反応可能な金属層を堆積し,シリサイド反応を行なってゲート電極G,ソース/ドレイン拡散層18、19上にシリサイド層を形成する。n−MOS領域上には引張応力を有する窒化シリコン膜21、p−MOS領域上には圧縮応力を有する窒化シリコン膜32を形成する。ここまでは第2の実施例と同様である。

【0078】

図9Bに示すように,n−MOS領域全体と,p−MOS領域の活性領域とを覆うレジストパターンPR8を形成する。p−MOS領域の素子分離領域12上が露出される。

【0079】

図9C、9Dに示すように、圧縮応力窒化シリコン膜32をエッチングして、p−MOS領域の素子分離領域12上の圧縮応力窒化シリコン膜32中の圧縮応力を解放する。図9Cはゲート長方向の断面図、図9Dはゲート幅方向の断面図である。p−MOS領域の活性領域AR2上に残る圧縮応力窒化シリコン膜32により,絶縁ゲート電極Gp下方のチャネル領域にはゲート長方向の圧縮応力が印加される。

【0080】

ゲート幅方向の素子分離領域上の圧縮応力が解放されるので、活性領域AR2上に選択的に残る圧縮応力窒化シリコン膜32が拡がろうとし、外側に向う力を発揮する。ゲート幅方向に引張歪が生じ、p−MOSトランジスタのオン電流が増大する。

【0081】

第3の実施例によれば、n−MOSトランジスタは第1の実施例同様であり、p−MOS領域のチャネル領域にゲート長方向の圧縮歪,ゲート幅方向の引張歪が生じる。p−MOSトランジスタの性能がさらに向上すると期待される。

【0082】

図10A−10Dは、第4の実施例による半導体装置の構成を概略的に示す断面図及び平面図である。

【0083】

図10Aに示すように、半導体基板11に前述の実施例同様の工程により、n−MOSFET、p−MOSFETを作成する。ゲート電極構造を覆って、半導体基板上に圧縮応力を有する窒化シリコン膜のコンタクトエッチストッパ膜32を堆積する。

【0084】

図10Bは、半導体基板を上方より観察した平面図である。STIによる素子分離領域12により、n−MOS活性領域AR1、p−MOS活性領域AR2が画定されている。活性領域AR1、AR2を横切って、ゲート電極構造Gn、Gpが形成されている。

【0085】

図10Cに示すように、ゲート電極構造を覆って半導体基板全面上に圧縮応力膜32が形成され、この圧縮応力膜32の上に、レジストパターンが形成される。レジストパターンPR9は、p−MOS活性領域AR2の上にのみ形成される。

【0086】

図10C、10Dで示すように、レジストパターンPR9をマスクとしてGeイオンを注入する。図10Cは、ゲート長方向に沿う断面図であり、図10Dはゲート幅方向の断面図である。

【0087】

n−MOS領域においては、全コンタクトエッチストッパ膜の応力が解放される。従って、圧縮応力に基づくオン電流の低下は低減される。p−MOS領域においては、素子分離領域12上の応力のみが解放される。活性領域上に残る圧縮応力膜は外側に広がろうとする。ゲート長方向においては、圧縮応力が働き、ゲート幅方向においては引張応力が働く。従って、p−MOSFETのオン電流は増加する。

【0088】

図11A−11Cは、第5の実施例による半導体装置の構成を概略的に示す断面図及び平面図である。図11A、11Bは、ゲート長方向及びゲート幅方向の断面図であり、図11Cは平面図である。本実施例においては、p‐MOS活性領域上にのみ圧縮応力膜のコンタクトエッチストッパ膜32が形成される。圧縮応力膜32の範囲は図9A−9Dに示す第3の実施例と同様である。n−MOS領域全域及びp−MOS領域の素子分離領域上には引張応力膜のコンタクトエッチストッパ膜21が形成される。引張応力膜21の範囲は、図5A−5Dに示す第1の実施例と同様である。

【0089】

n−MOSFETにおいては、第1の実施例同様、ゲート長方向に引張応力が働き、オン電流が増加する。p−MOSFETにおいては、第2、第3の実施例同様、圧縮応力膜32は、素子分離領域上で応力解放されており、引張応力膜21は、活性領域で応力解放されていると考えることができる。すなわち、図11Bに示すように、コンタクトエッチストッパ膜21,32は、ゲート幅方向で、活性領域を外側に拡げようとする力を発揮する。従って、p−MOSFETは、ゲート長方向に圧縮応力、ゲート幅方向に引張応力を受け、オン電流を増加させる。

【0090】

図12Aは、以上5つの実施例の特徴をまとめた表である。n‐MOSFETのゲート長方向に引張応力を生じさせるためには、活性領域上に引張応力膜を形成する必要がある。もし,素子分離領域の応力を解放するとゲート幅方向に圧縮応力が生じることになる。これは好ましくないので、この場合応力解放場所は「なし」となる。従って,ゲート幅方向には応力は発生しない。実施例E1、E2、E3、E5がこの構成を有する。

【0091】

実施例E4においては、圧縮応力膜の圧縮応力を全領域で解放しているため、n−MOS領域に応力は発生しない。圧縮応力によってオン電流が減少するところを、防止している。

【0092】

n−MOSFTのゲート幅方向に引張応力を働かせるには、引張応力膜であれば活性領域の応力を解放すればよいが、そうすると、ゲート長方向の応力が「なし」となってしまい効果が相殺される。圧縮応力膜であれば素子分離領域の応力を解放すればよいが、活性領域上に圧縮応力膜が残るとゲート長方向に圧縮応力が発生し、効果が相殺される。実施例においてはそのような構成は採用されていない。

【0093】

p−MOSFETのゲート長方向に圧縮応力を働かせるには、少なくとも活性領域上に圧縮応力膜を作成する必要がある。実施例E2、E3、E4、E5がこの構成を採用する。

【0094】

ゲート幅方向に引張応力を生じさせるためには、引張応力膜であれば活性領域上の応力を開放させればよい。実施例E1、E5がこの構成を採用する。又、圧縮応力膜であれば素子分離領域上の応力を解放すればよい。実施例E2、E3、E4、E5がこの構成を採用する。

【0095】

実施例E1は、引張応力膜のみを用い、n‐MOSFETにおいてはゲート長方向に引張応力を生じさせ、p−MOSFETにおいては、ゲート幅方向に引張応力を生じさせている。

【0096】

実施例E4は、圧縮応力膜のみを用い、p−MOSFETにおいてはゲート長方向に圧縮応力、ゲート幅方向に引張応力を生じさせている。但し、n−MOSFETにおいては応力は生じていない。他の実施例E2、E3、E5は、引張応力膜と圧縮応力膜を用い、n−MOSFETにはゲート長方向の引張応力、p−MOSFETにはゲート長方向の圧縮応力のゲート幅方向の引張応力を生じさせている。

【0097】

このような構成により、CMOSFETのオン電流を向上させられるが、露光工程が追加となる。このため、レイアウトに対する制約が発生することがある。例えば、スタティック(S)RAMに上述の実施例の構成を適用しようとすると、SRAMの面積が増加することがあり得る。又、入出力回路の特性は既存の品種と同じ性能が要求されることがある。

【0098】

図12Bは、半導体集積回路装置の構成を概略的に示す平面図である。半導体集積回路装置は、チップ11内に論理回路41、SRAM回路42、入出力(I/O)回路43を含む。上述の実施例による応力膜構造は、論理回路41のみに適応され、入出力回路43、SRAM回路42には採用されない。

【0099】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、応力膜として窒化シリコン膜を用いる場合を説明したが、適当な応力を生じる誘電体膜であれば窒化シリコンに制限されない。CMOSFETの構成としては、公知の種々の構成を採用することができる。その他、種々の変更、改良、組み合わせが可能_ことは当業者に自明であろう。

【0100】

以下,本発明の特徴を付記する。

【0101】

(付記1)

pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記pチャネル型トランジスタ領域内にpチャネル型活性領域を画定する素子分離領域と、

前記pチャネル型活性領域を横断して,前記半導体基板上方に形成され、下方にpチャネル領域を画定するpチャネル型ゲート電極構造と、

前記pチャネル型ゲート電極構造を覆って、前記pチャネル型活性領域上方に選択的に形成された圧縮応力膜と、

前記pチャネル型トランジスタ領域の素子分離領域上方に選択的に形成され,前記圧縮応力膜の応力を解放している応力解放領域と、

を有し、前記pチャネル型活性領域上方の前記圧縮応力膜が前記pチャネル領域にゲート長方向の圧縮応力を印加し、前記圧縮応力膜と前記応力解放領域が前記pチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0102】

(付記2)

前記圧縮応力膜が、窒化シリコン膜である付記1記載の半導体装置。

【0103】

(付記3)

前記応力解放領域が、イオン注入領域または前記圧縮応力膜を除去した領域で形成される付記1記載の半導体装置。

【0104】

(付記4)

前記イオン注入領域が、電気的に不活性な不純物イオンを注入された領域である付記3記載の半導体装置。

【0105】

(付記5)

前記応力解放領域が、前記圧縮応力膜を除去した領域で形成され、さらに前記pチャネル型トランジスタ領域の素子分離領域上に選択的に形成された引張応力膜を有し,前記引張応力膜も前記pチャネル領域にゲート幅方向の引張応力を印加する付記1記載の半導体装置。

【0106】

(付記6)

前記圧縮応力膜がプラズマCVDで形成された窒化シリコン膜であり,前記引張応力膜が熱CVDで形成された窒化シリコン膜である付記5記載の半導体装置。

【0107】

(付記7)

前記半導体基板がnチャネル型トランジスタ領域も有し、

前記素子分離領域が、前記nチャネル型トランジスタ領域内にnチャネル型活性領域を画定し、

さらに、

前記nチャネル型活性領域を横断して,前記半導体基板上方に形成され、下方にnチャネル領域を画定するnチャネル型ゲート電極構造と、

前記nチャネル型ゲート電極構造を覆って,前記nチャネル型トランジスタ領域上方に形成された絶縁膜と、

を有する付記1〜4のいずれか1項記載の半導体装置。

【0108】

(付記8)

前記絶縁膜が窒化シリコン膜である付記7記載の半導体装置。

【0109】

(付記9)

前記絶縁膜が,引張応力を有する膜であり、前記nチャネル領域にゲート長方向の引っ張り応力を印加する付記8記載の半導体装置。

【0110】

(付記10)

前記絶縁膜が,前記圧縮応力膜と同一の膜であり,全域で応力が解放されている付記7記載の半導体装置。

【0111】

(付記11)

pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記pチャネル型トランジスタ領域内にpチャネル型活性領域を画定する素子分離領域と、

前記pチャネル型活性領域を横断して,前記半導体基板上方に形成され、下方にpチャネル領域を画定するpチャネル型ゲート電極構造と、

前記pチャネル型トランジスタ領域の素子分離領域上方に選択的に形成された引張応力膜と、

前記pチャネル型ゲート電極構造を覆って、前記pチャネル型活性領域上方に選択的に形成され,前記引張応力膜と同一膜で形成され、応力が解放されている絶縁膜と、

を有し、前記pチャネル型トランジスタ領域の素子分離領域上方の前記引張応力膜が前記pチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0112】

(付記12)

前記引張応力膜と,前記絶縁膜とが窒化シリコン膜である付記11記載の半導体装置。

【0113】

(付記13)

前記半導体基板がnチャネル型トランジスタ領域も有し、

前記素子分離領域が、前記nチャネル型トランジスタ領域内にnチャネル型活性領域を画定し、

さらに、

前記nチャネル型活性領域を横断して,前記半導体基板上方に形成され、下方にnチャネル領域を画定するnチャネル型ゲート電極構造と、

前記nチャネル型ゲート電極構造を覆って,前記nチャネル型トランジスタ領域上方に形成され,前記引張応力膜と同一膜で形成された引張応力膜と、

を有する付記11記載の半導体装置。

【0114】

(付記14)

前記半導体基板が、(001)面を有するシリコン基板であり、前記ゲート長方向が〈110〉方向である付記1〜13のいずれか1項記載の半導体装置。

【0115】

(付記15)

nチャネル型トランジスタ領域、pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記nチャネル型トランジスタ領域内にn−MOS活性領域を画定し、前記pチャネル型トランジスタ領域内にp−MOS活性領域を画定する素子分離領域と、

前記n−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され,下方にn−MOSチャネル領域を画定するn−MOSゲート電極構造と、

前記p−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、

前記n−MOSゲート電極構造、p−MOSゲート電極構造を覆って、前記半導体基板上方に形成され,引張応力を有するコンタクトエッチストッパ膜と、

前記pチャネル型トランジスタ領域のp−MOS活性領域上方で選択的に前記コンタクトエッチストッパ膜中に形成され,前記コンタクトエッチストッパ膜の応力を解放する応力解放領域と、

を有し、前記nチャネル型トランジスタ領域上方のコンタクトエッチストッパ膜が前記n−MOSチャネル領域のゲート長方向に引張応力を印加し,前記pチャネル型トランジスタ領域の前記応力解放領域が前記p−MOSチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0116】

(付記16)

前記応力解放領域が、イオン注入領域で形成される付記15記載の半導体装置。

【0117】

(付記17)

nチャネル型トランジスタ領域、pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記nチャネル型トランジスタ領域内にn−MOS活性領域を画定し、前記pチャネル型トランジスタ領域内にp−MOS活性領域を画定する素子分離領域と、

前記n−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にn−MOSチャネル領域を画定するn−MOSゲート電極構造と、

前記p−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、

前記n−MOSゲート電極構造を覆って,前記nチャネル型トランジスタ領域上方に形成され、引張応力を有する第1コンタクトエッチストッパ膜と、

前記pチャネル型トランジスタ領域を覆って,前記pチャネル型トランジスタ領域上方に形成され,圧縮応力を有する第2コンタクトエッチストッパ膜と、

前記pチャネル型トランジスタ領域の前記素子分離領域上方で選択的に前記第2コンタクトエッチストッパ膜中に形成され,前記第2コンタクトエッチストッパ膜の圧縮応力を解放する応力解放領域と、

を有し、前記第1コンタクトエッチストッパ膜が前記n−MOSチャネル領域のゲート長方向に引張応力を印加し、前記p−MOS活性領域上方の第2コンタクトエッチストッパ膜が前記p−MOSチャネル領域にゲート長方向の圧縮応力を印加し、前記応力解放領域と前記p−MOS活性領域上方の第2コンタクトエッチストッパ膜とが前記p−MOSチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0118】

(付記18)

前記応力解放領域が,前記第2コンタクトエッチストッパ膜が除去された領域またはイオン注入領域で形成されている付記17記載の半導体装置。

【0119】

(付記19)

nチャネル型トランジスタ領域、pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記nチャネル型トランジスタ領域内にn−MOS活性領域を画定し、前記pチャネル型トランジスタ領域内にp−MOS活性領域を画定する素子分離領域と、

前記n−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され,下方にn−MOSチャネル領域を画定するn−MOSゲート電極構造と、

前記p−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、

前記n−MOSゲート電極構造、p−MOS電極構造を覆って、前記半導体基板上方に形成され,圧縮応力を有するコンタクトエッチストッパ膜と、

前記nチャネル型トランジスタ領域の全域と、前記pチャネル型トランジスタ領域の素子分離領域上方で選択的に前記コンタクトエッチストッパ膜中に形成され,前記コンタクトエッチストッパ膜の応力を解放する応力解放領域と、

を有し、前記pチャネル型トランジスタ領域上方の前記コンタクトエッチストッパ膜が前記p−MOSチャネル領域のゲート長方向に圧縮応力を印加し、前記p−MOS活性領域上方のコンタクトエッチストッパ膜と前記応力解放領域が前記p−MOSチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0120】

(付記20)

前記応力解放領域が、イオン注入領域で形成されている付記19記載の半導体装置。

【0121】

(付記21)

nチャネル型トランジスタ領域、pチャネル型トランジスタ領域を有する半導体基板と、

前記半導体基板表面部に形成され、前記nチャネル型トランジスタ領域内にn−MOS活性領域を画定し、前記pチャネル型トランジスタ領域内にp−MOS活性領域を画定する素子分離領域と、

前記n−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され,下方にn−MOSチャネル領域を画定するn−MOSゲート電極構造と、

前記p−MOS活性領域の中間部を横断して,前記半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、

前記nチャネル型トランジスタ領域と前記pチャネル型トランジスタ領域の素子分離領域を覆って、前記半導体基板上方に形成され、引張応力を有する第1コンタクトエッチストッパ膜と、

前記p−MOS活性領域を覆って,前記半導体基板上方に形成され、圧縮応力を有する第2コンタクトエッチストッパ膜と、

を有し、前記第1コンタクトエッチストッパ膜が前記n−MOSチャネル領域のゲート長方向に引張応力を印加し、前記第2コンタクトエッチストッパ膜が前記p−MOSチャネル領域にゲート長方向の圧縮応力を印加し、前記pチャネル型トランジスタ領域の素子分離領域上の第1コンタクトエッチストッパ膜と前記p−MOS活性領域上の第2コンタクトエッチストッパ膜とが、前記p−MOSチャネル領域にゲート幅方向の引張応力を印加する半導体装置。

【0122】

(付記22)

前記素子分離領域が、前記pチャネル型トランジスタ領域に前記p−MOS活性領域と、隣接する他のp−MOS活性領域とを画定し、前記応力解放領域が、前記p−MOS活性領域と前記他のp−MOS活性領域のゲート幅方向に関して前記素子分離領域上に形成されている付記17〜20のいずれか1項記載の半導体装置。

【0123】

(付記23)

前記イオン注入領域が、電気的に不活性な不純物イオンを注入された領域である付記16、18、20のいずれか1項記載の半導体装置。

【0124】

(付記24)

前記半導体基板が、(001)面を有するシリコン基板であり、前記ゲート長方向が〈110〉方向である付記15〜23のいずれか1項記載の半導体装置。

【符号の説明】

【0125】

TS 引張応力膜

CS 圧縮応力膜

V 応力解放箇所

Sub 半導体基板

AR 活性領域

G ゲート電極構造

SW サイドウォール

11 シリコン基板

13 pウエル

14 nウエル

15 ゲート絶縁膜

16 多結晶シリコン膜

18 n型ソース/ドレイン拡散層

19 p型ソース/ドレイン拡散層

21 引張応力内蔵窒化シリコン膜

Ex エクステンション領域

23 層間絶縁膜

25 導電性プラグ

27 層間絶縁膜

28 銅配線

30 層間絶縁膜

31 デュアルダマシン銅配線

32 圧縮応力内蔵窒化シリコン膜

PR レジストパターン

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板に形成された素子分離領域と、

前記素子分離領域によって画定されたn型の第1活性領域と、

前記n型の第1活性領域上に形成されたp型ゲート電極と、

前記p型ゲート電極を覆って、前記第1活性領域上方に選択的に形成された圧縮応力膜と、

前記圧縮応力膜上に形成された層間絶縁膜と、

前記層間絶縁膜と前記圧縮応力膜を貫通して前記第1活性領域に達する開口部と、

前記開口部内に形成された導電性プラグと、

を有し、前記圧縮応力膜の端部は、前記p型ゲート電極のゲート幅方向において、前記素子分離領域と前記第1活性領域との境界上に位置する半導体装置。

【請求項2】

さらに、前記p型ゲート電極のゲート幅方向において、前記素子分離領域上に選択的に形成された引張応力膜を有する請求項1記載の半導体装置。

【請求項3】

前記素子分離領域が、前記半導体基板内にp型の第2活性領域を画定し、

さらに、

前記p型の第2活性領域上に形成されたn型ゲート電極と、

前記n型ゲート電極を覆って,前記第2活性領域上方から素子分離領域上方に延在する絶縁膜と、

を有する請求項1または2記載の半導体装置。

【請求項4】

前記絶縁膜が,引張応力を有する膜である請求項3記載の半導体装置。

【請求項1】

半導体基板と、

前記半導体基板に形成された素子分離領域と、

前記素子分離領域によって画定されたn型の第1活性領域と、

前記n型の第1活性領域上に形成されたp型ゲート電極と、

前記p型ゲート電極を覆って、前記第1活性領域上方に選択的に形成された圧縮応力膜と、

前記圧縮応力膜上に形成された層間絶縁膜と、

前記層間絶縁膜と前記圧縮応力膜を貫通して前記第1活性領域に達する開口部と、

前記開口部内に形成された導電性プラグと、

を有し、前記圧縮応力膜の端部は、前記p型ゲート電極のゲート幅方向において、前記素子分離領域と前記第1活性領域との境界上に位置する半導体装置。

【請求項2】

さらに、前記p型ゲート電極のゲート幅方向において、前記素子分離領域上に選択的に形成された引張応力膜を有する請求項1記載の半導体装置。

【請求項3】

前記素子分離領域が、前記半導体基板内にp型の第2活性領域を画定し、

さらに、

前記p型の第2活性領域上に形成されたn型ゲート電極と、

前記n型ゲート電極を覆って,前記第2活性領域上方から素子分離領域上方に延在する絶縁膜と、

を有する請求項1または2記載の半導体装置。

【請求項4】

前記絶縁膜が,引張応力を有する膜である請求項3記載の半導体装置。

【図1】

【図2(A)】

【図2(B)】

【図2(C)】

【図2(D)】

【図2(E)】

【図2(F)】

【図2(G)】

【図2(H)】

【図3(A)】

【図3(B)】

【図3(C)】

【図3(D)】

【図3(E)】

【図3(F)】

【図3(G)】

【図3(H)】

【図4】

【図5】

【図6(A)】

【図6(B)】

【図6(C)】

【図6(D)】

【図6(E)】

【図6(F)】

【図7】

【図8(A)】

【図8(B)】

【図8(C)】

【図8(D)】

【図8(E)】

【図8(F)】

【図9】

【図10】

【図11】

【図12】

【図2(A)】

【図2(B)】

【図2(C)】

【図2(D)】

【図2(E)】

【図2(F)】

【図2(G)】

【図2(H)】

【図3(A)】

【図3(B)】

【図3(C)】

【図3(D)】

【図3(E)】

【図3(F)】

【図3(G)】

【図3(H)】

【図4】

【図5】

【図6(A)】

【図6(B)】

【図6(C)】

【図6(D)】

【図6(E)】

【図6(F)】

【図7】

【図8(A)】

【図8(B)】

【図8(C)】

【図8(D)】

【図8(E)】

【図8(F)】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−29654(P2011−29654A)

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願番号】特願2010−216640(P2010−216640)

【出願日】平成22年9月28日(2010.9.28)

【分割の表示】特願2004−191405(P2004−191405)の分割

【原出願日】平成16年6月29日(2004.6.29)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願日】平成22年9月28日(2010.9.28)

【分割の表示】特願2004−191405(P2004−191405)の分割

【原出願日】平成16年6月29日(2004.6.29)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]