半導体装置

【課題】駆動安定性を高め、積層工程での歩留まりを向上させ、実装形態での長期信頼性を向上させた薄型半導体チップの積層パッケージを実現する。

【解決手段】チップ表面に半導体素子110と、半導体素子110に信号を供給する配線と信号用電極と電源用電極とグランド用電極を有し、チップ裏面に信号用電極と電源用電極とグランド用電極を有し、チップ表面の電極とチップ裏面の電極とを電気的に接続する貫通配線を有し、チップの裏面を覆い、グランド用電極と接続した導体層120が形成されている複数の半導体チップ500、501とインターポーザ502とが積層されている半導体パッケージ。

【解決手段】チップ表面に半導体素子110と、半導体素子110に信号を供給する配線と信号用電極と電源用電極とグランド用電極を有し、チップ裏面に信号用電極と電源用電極とグランド用電極を有し、チップ表面の電極とチップ裏面の電極とを電気的に接続する貫通配線を有し、チップの裏面を覆い、グランド用電極と接続した導体層120が形成されている複数の半導体チップ500、501とインターポーザ502とが積層されている半導体パッケージ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリ素子をはじめとする複数の半導体チップを基板上に実装したメモリパッケージなどの半導体装置に関し、とくに薄型の半導体パッケージを積層実装して小型化したメモリパッケージの動作の信頼性を高めるための構造に関するものである。

【背景技術】

【0002】

近年の半導体パッケージは、従来にも増して高集積化の要求が強まっている。こうした要求に対して、従来は、半導体チップの電界効果トランジスタ(FET)をはじめとする半導体素子の面密度を高めることで応えてきた。しかし、高集積化の進んだ今日においては、半導体素子の面密度を更に高めることへの技術的課題は多く、要求される高集積化の時間軸に追従することが困難になってきた。そこで、半導体素子を搭載した半導体ウェハもしくはチップを薄く研磨し、これを複数枚積層し、電気的に接続してパッケージ化する3次元実装技術の開発が注目されている。この一例として、「特許文献1」および「特許文献2」が挙げられる。

【0003】

「特許文献1」では、チップを三次元積層した場合においても、反りが生じたり、フリップチップ接続した半導体チップが剥離したり、半導体チップが薄型のものであってもクラックが生じたりするおそれのない半導体積層パッケージについて記載されている。また、「特許文献2」では、実装状態での落下や実装基板の変形にも耐えうる薄型の半導体装置について記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003-7962

【特許文献2】特開2009-26833

【発明の概要】

【発明が解決しようとする課題】

【0005】

半導体積層パッケージの薄型半導体チップに関しては、以下のような課題がある。半導体チップを薄く研磨することにより半導体素子を支持するウェハ厚が薄くなってきている。2008年現在で、25マイクロメートル厚にまで薄くした半導体チップを積層した半導体パッケージが製品化されており、20マイクロメートルを下回るほど薄く研磨する技術も開発されている。

【0006】

図1はn型チャネルMOSFETの断面図を示したものである。半導体チップの薄型化に伴い、表面に設けた半導体素子の電界が半導体チップの裏面に大きくしみ出すこととなり、半導体素子そのものの動作の信頼性が損なわれることが懸念される。また、このような薄型半導体チップを複数積層した半導体積層パッケージでは数マイクロメートル〜数十マイクロメートルの距離を隔てて薄型半導体チップが積層される。そのため、第1の半導体チップの裏面にしみ出した電界が直下に置かれた第2の半導体チップにおける半導体素子の駆動に作用した場合、誤動作の原因となる。

【0007】

また、図2に示すように、表面に設けた半導体素子により半導体チップは面内および表裏での対称性を保つことが不可能である。そのため構成部材による応力や熱膨張係数の差異が生じ、また薄く研磨する際のウェハ厚のわずかなバラツキ(面内での不均一性)により、半導体チップには反りが生じる。これにより、積層時の実装歩留まりを著しく低下させるとともに、実装形態での長期信頼性をも低下させる。

【0008】

さらに、半導体素子は高周波信号を制御するが、素子回路自身がアンテナとして機能することで不要電磁輻射が生じた場合、半導体素子の誤動作となり得る。ドライバICをはじめとする高速演算素子を搭載したチップを積層する場合、こうした誤動作は顕著となる。

【0009】

不要電磁輻射が生じにくいよう、また生じた不要電磁輻射の影響を受けにくくなるよう、半導体チップの内部回路は設計されているが、数マイクロメートル〜数十マイクロメートルの間隔を隔てて積層された第2の薄型半導体チップに対しては、第1の半導体チップからの不要電磁輻射を考慮した設計を行うことは困難である。異なるメーカの半導体チップを積層する場合、特に困難となる。

【0010】

本発明は、上記の課題を解決する半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明は、半導体素子と、前記半導体素子と接続され、半導体素子に信号を供給する配線と電極を表面に具備し、ウェハを貫通する貫通配線を具備し、裏面に電極と導体層を具備した半導体チップを搭載したインターポーザ付き半導体パッケージにおいて、前記半導体チップの前記裏面導体層がインターポーザもしくは半導体パッケージを搭載するマザーボードに設けたグランド層と電気的に接続されていることを特徴とする半導体パッケージである。これによって半導体チップの駆動安定性を高めるとともに接続時の歩留まり向上と接続の長期信頼性向上に寄与するものである。これについて、以下に説明する。

【0012】

先に説明したとおり、半導体チップの薄型化により半導体素子の裏面の電界は大きくなるが、ここにグランド層と接続した導体層を形成したことで、導体層面での電界は安定する。これにより、半導体チップ内部の電界に対する外部電磁界からの影響は極めて小さくなる。また、数マイクロメートル〜数十マイクロメートルの距離を隔てて薄型半導体チップを積層した場合、第1の半導体チップの裏面における電界が安定することにより、直下に置かれた第2の半導体チップでの半導体素子の駆動安定性も高くなる。

【0013】

また、高速演算素子を搭載したチップの駆動では特に顕著に生じる不要電磁輻射についても、導体層によるシールド効果により積層した別チップへの影響を大幅に低減させることができる。これにより、チップの誤動作を大幅に低減できる。

【0014】

導体層に求められる特性は、主として導電性、ウェハ密着性、パターニング性である。半導体チップの裏面に設ける電極と同時に同一プロセスで導体層を形成することで、導体層形成のための追加コストがほとんど掛からないため有利である。上記特性に加え、導体層形成のためのコスト増加を抑制できるのであれば、裏面電極形成に導体層形成工程を付加することは有効である。

【0015】

例えば、裏面電極とは異なる種類の導体層としてもよいし、裏面電極形成と同時に導体層を形成した後にこの導体層に異なる種類の導体層あるいは樹脂材料をはじめとする絶縁層を選択的に付加してもよいし、裏面電極と同じ種類であっても膜の成長速度や成膜環境・条件の変更や異なる膜厚としてもよいし、成膜時や成膜後に加熱あるいは冷却工程を加えてもよい。これら形成工程を選択することで、導体層の内部応力を制御し、薄型半導体チップの反りを低減させることができる。

【発明の効果】

【0016】

本発明に係る半導体装置は、表面に半導体素子を設けた薄型半導体チップの裏面に導体層を設け、これをインターポーザあるいはマザーボードのグランド層と電気的に接続したことにより、薄型半導体素子の裏面にしみ出す電界を半導体チップに閉じ込めることができる。

【0017】

また、このような半導体チップを積層した場合、安定したシールド効果により不要電磁輻射を半導体チップの中に留めることができるとともに、外部からの不要電磁輻射を抑制することができる。こうした効果は導体層の部材や膜質によらず得られるので、導体層の選択肢は広く、薄型半導体チップの反りを抑制することもできる。

【図面の簡単な説明】

【0018】

【図1】一般的なn型チャネルMOSFETの構成例を示す図である。

【図2】従来の薄型半導体チップの反り状態を示す図である。

【図3】実施例1の薄型半導体チップを示す斜視図である。

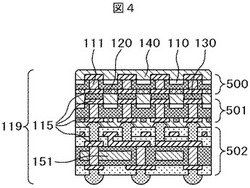

【図4】実施例1の薄型半導体チップを積層した半導体パッケージを示す図である。

【図5】実施例1の半導体パッケージの製作工程を示す図である。

【図6】実施例1のシリコンウェハの製造工程を示す図である。

【図7】実施例1の薄型半導体チップとして薄型メモリチップを複数積層し、樹脂基板多層配線インターポーザに積層した半導体パッケージを示す図である。

【図8】実施例1の薄型半導体チップを積層した半導体パッケージをマザーボードに実装した様子を示す図である。

【図9】実施例2の薄型半導体チップを示す斜視図である。

【図10】実施例2の薄型半導体チップを積層した半導体パッケージを示す図である。

【図11】実施例3の薄型半導体チップを積層した半導体パッケージを示す図である。

【図12】実施例3の薄型半導体チップを積層した半導体パッケージを示す図である。

【図13】実施例3の薄型半導体チップを積層した半導体パッケージを示す図である。

【図14】実施例3の薄型半導体チップを積層した半導体パッケージを示す図である。

【図15】シリコンウェハに形成される金属スパッタリング膜以外の導体層の例である。

【図16】シリコンウェハに形成される導体層の他の例である。

【図17】シリコンウェハに形成される導体層のさらに他の例である。

【発明を実施するための形態】

【0019】

以下、図面を参照して本発明の実施の形態を説明する。

【実施例1】

【0020】

図3に示す半導体チップは、本発明の半導体装置の内部で積層されるフリップチップタイプの薄型半導体チップを裏面側から見た斜視図である。薄型半導体チップ118は、表面に半導体素子110を形成するとともに第2の半導体チップあるいはインターポーザと接続するための表面電極112を備えており、また、半導体チップを貫通する穴を介して裏面に設けた電極群113を経て第3の半導体チップと接続するための電極をもつ。

【0021】

表裏面に設けた電極群は、これに接続された半導体素子によって信号用電極群114、グランド用電極群115、電源用電極群116に分類でき、それぞれ分離されて設けられている。また、電極群を除く半導体素子の裏面は導体層120に覆われており、上記電極群のうちグランド用電極群115の一部あるいは全部と電気的に接続され、信号用電極群114や電源用電極群116とは電気的に分離されている。

【0022】

例えば導体層にニッケルを用いた場合、成膜後に200℃程度に加熱すると収縮応力が作用する。薄型半導体チップが半導体素子を有する表面が凹面となるような反りを示していた場合、ニッケルの収縮応力は反りを低減することができる。また、樹脂材料からなる膜を導体層に貼り付けることでも反りの低減に効果的であり、加えて接着性を有する場合、これと積層される半導体チップとの接着性を向上させることもできる。

【0023】

図4に示す半導体装置は、図3に示した薄型半導体チップを積層した半導体パッケージ119の断面図の一例を示したものであり、メモリチップ500、ドライバIC501、インターポーザ502から構成される。

【0024】

半導体素子110の裏面に設けた導体層120はグランド用電極群115や第2、第3の半導体チップのグランド用電極群115とフリップチップ接続され、インターポーザに設けたグランド層に接続されている。また、信号用電極群や電源用電極群も、機能に応じておのおの適切に第2、第3の半導体チップの信号用電極群あるいは電源用電極群とはんだボール130を介してフリップチップ接続されている。

【0025】

図3の薄型半導体チップおよび図4の積層半導体パッケージの作製方法を、図5および図6を用いて説明する。図5において、まず、シリコンウェハ503の表面に、FETをはじめとする回路からなる半導体素子110を形成する(図5A)。この回路には、チップを駆動させるための表面回路電極群も含まれており、これらは用途に応じて信号用、グランド用、電源用としてそれぞれ機能する。

【0026】

このようなシリコンウェハの表面に絶縁層とアルミニウム膜を逐次積層し、非貫通穴を形成する領域のアルミニウム膜を除去する。アルミニウム膜をマスクとして、Boschプロセスに代表される反応性イオンエッチング(Reactive Ion Etching、RIE)により、アルミニウム膜の開口部のシリコンに非貫通穴を形成する。その後、マスクとして用いたアルミニウム膜を除去する。

【0027】

図6Aは、アルミニウム膜を除去した後のシリコンウェハ503の断面図である。図6Aには、回路素子110と非貫通穴5031が示されている。次に、シリコンウェハ503の表面全面にTEOS膜(Tetra Etoxi Silanによって形成されたSiO2膜)を形成する。SiO2膜の上に、例えば、Ni膜あるいはCr−Cuの積層膜等の金属膜5033をスパッタリングによって形成する。図6Bはこの状態を示す断面図である。

【0028】

次に、図6Cに示すように、金属膜5033の上にレジスト5034を形成する。レジストは、金属膜5033の上に選択的に銅めっき5035を形成するためである。次にシリコンウェハ503に対して銅めっきをおこなうと、図6Dに示すように、銅めっきはレジストの付いていない金属膜5033上に形成される。

【0029】

図6Dに示すように、非貫通穴5031は銅めっき5035によって充填され、シリコン貫通配線111が形成される。銅めっき5035は非貫通穴5031以外の箇所で、表面電極112が形成される部分、および、半導体素子110と表面電極112を結ぶ配線部分にも形成される。その後、図6Eに示すように、銅めっき5035の上にNiめっき5036を形成する。したがって、電極の表面にはNiめっき5036が形成されていることになる。

【0030】

次に図6Fに示すように、レジスト5034を除去する。さらに、電極を形成するCuめっき5035およびNiめっき5036をレジストにして、金属膜5033をエッチングによって除去する。この状態が図6Gである。

【0031】

図5Bは、図6Gの状態を金属膜等を省略し、簡略化して表したシリコンウェハ503の断面図である。図5Bは、シリコンウェハ503の表面に、表面回路電極群、シリコン貫通配線111が形成された非貫通穴、およびこれらを結ぶ配線が形成された状態である。

【0032】

次に、シリコンウェハ503の裏面を研磨して非貫通穴に充填した銅5035を露出させた後、裏面にニッケル膜を成膜する。ニッケル膜のパターニングによりチップ積層電極群(裏面)を形成するとともに、チップ積層電極群(裏面)の隙間を埋めるよう電気的に繋がったシールド用ニッケル膜を形成する。ただし、グランド用の表面回路電極群と電気的に接続されたグランド用チップ積層電極群(裏面)のうち少なくとも一つをシールド用ニッケル膜と接続させておく。チップ積層電極群(裏面)に選択的にはんだを形成し、ダイシングを経て薄型半導体チップを得る(図5C)。

【0033】

ここでは、半導体素子を形成した後で半導体チップの貫通穴を形成する、いわゆるvia lastと呼ばれる製造法での半導体チップの作製法を示したが、これに限定されるものではない。先に貫通穴を形成した後に半導体素子を形成するVia Firstと呼ばれる製造法で作製してもよい。

【0034】

このような方法で作成した薄型半導体チップは、回路構成に応じてメモリやドライバICとしての機能を付加させることができ、以降、それぞれ薄型メモリチップ、薄型ドライバICチップと称する。

【0035】

薄型半導体チップと接続するための電極を表面に備え、内層にグランド層をもち、裏面にマザーボードと接続するための電極を備え、層間を電気的に接続するビア配線を備えた多層配線樹脂基板に薄型メモリチップ、薄型ドライバICチップを重ね、はんだによって積層チップの電極を接合させる。このとき、多層配線樹脂基板のグランド層は薄型半導体チップのシールド用ニッケル層と電気的に接続させる(図5D)。

【0036】

ここで、グランド層や電源層で統一できる配線同士を接続することで、層間を電気的に接続するビア配線を少なくすることも可能であり、薄型半導体チップの貫通配線よりも大きなピッチとなる多層配線樹脂基板に有利である。これを樹脂材料で封止させて、図4に示すような半導体パッケージを得る。

【0037】

このようにして得た半導体パッケージは、それぞれの薄型半導体チップの裏面にインターポーザのグランド層と接続されたシールド用ニッケル層を有する。これにより、薄型半導体チップの裏面の電位が安定することから、表面に設けたFETをはじめとする回路からの電場のしみ出しをシールド用ニッケル層で抑えることができた。

【0038】

また、回路での高速信号により生じた不要電磁輻射はシールド用ニッケル層で吸収されるため、積層された他の薄型半導体チップの回路までは到達せず、誤動作を抑制することができる。

【0039】

FET形成に用いたヒ素やリン、ホウ素をはじめとするドーパント、回路の配線材料に用いるAl膜やCu膜、絶縁層に用いられるTEOS膜や窒化シリコン膜によって、半導体チップの構造は表面の面内や表裏面での対称性が崩れており、これら構成部材の内部応力によって半導体チップに反りが発生する。例えば、半導体チップの表面に収縮応力が作用することにより、表面が凹面となるような馬蹄形になる。このような現象は、裏面に設けたニッケル層が加熱により収縮することによって生じる収縮応力によって緩和され、半導体チップの平滑性は改善した。

【0040】

以上では薄型メモリチップ500、薄型ドライバICチップ501、インターポーザ502を積層した半導体パッケージの例を示したが、図7に示すような複数の薄型メモリチップとインターポーザを積層したメモリパッケージでもよく、積層するチップの機能を制限するものではない。また、インターポーザはその機能から積層されるチップの最上層もしくは最下層に位置するが、その他のチップはその積層する順番を制限されるものではない。

【0041】

以上ではインターポーザとして多層配線樹脂基板を用いた例を説明したが、シリコンウェハを基材としたインターポーザとした例を図8に示す。表面に薄型半導体チップと接続するための電極および配線の形成工程、シリコンの穴あけ加工および配線形成工程、ウェハの薄化工程、裏面の電極形成工程、ダイシング工程を適宜組合せて実施することで、薄型半導体チップと接続するシリコンインターポーザ504を得る。このようなインターポーザを薄型メモリチップ500と重ねてはんだ融点まで昇温させることで積層チップの電極を接合し、樹脂材料でチップを封止して半導体パッケージを得る。

【0042】

これら半導体パッケージの各電極群をマザーボード505の各電極群と接続して搭載する際、薄型メモリチップの裏面に形成した導体層は、それぞれのグランド電極を介して接続され、インターポーザのグランド電極を経由してマザーボードに設けたグランド層150と接続する構造とする。シリコンインターポーザの場合、その表面の多層配線に薄型半導体チップの裏面に形成した導体層と接続したグランド層を設けることも可能であるが、マザーボードのグランド層と接続した方が電気的安定性は高くなる。

【0043】

また、導体層120の部材を選択することで薄型半導体素子の反りを低減でき、積層時の実装歩留まりを著しく向上させるとともに、実装形態での長期信頼性をも向上させることができた。

【実施例2】

【0044】

図9は本発明の半導体装置の内部で積層されるフリップチップタイプの薄型半導体チップを示したものであり、薄型半導体チップの表裏面に導体層を有するものであり、図9Aは半導体素子側(表面)、図9Bはシリコン研磨面側(裏面)からの斜視図を示したものである。

【0045】

薄型半導体チップは、表面に半導体素子110を形成するとともに第2の半導体チップと接続するための電極112を備えており、また、半導体チップを貫通する配線111を経て第3の半導体チップあるいはインターポーザと接続するための電極113をもつ。表裏面に設けた電極群112、113は、これに接続された半導体素子110によって信号用電極群114、グランド用電極群115、電源用電極群116としての機能をそれぞれ有する。なお、半導体素子110の上には、図6Aに示す非貫通穴5031を形成するときのレジストとなるAl膜を形成する前に被着した絶縁膜および、非貫通穴5031形成後に被着した図6Bに示すTEOS膜5032が被着されている。

【0046】

半導体素子110の表面は導体層122に覆われており、表面の上記電極群のうちグランド用電極群の一部あるいは全部と電気的に接続されている。また、裏面は導体層120に覆われており、裏面の上記電極群のうちグランド用電極群の一部あるいは全部と電気的に接続されている。

【0047】

図10は、図9に示した同様の薄型半導体チップを複数積層した半導体パッケージを示したものであり、薄型半導体チップの表裏に設けた導体層120、122はこれを接続したグランド用電極115を介して、インターポーザのグランド層151と接続されている。

【0048】

このような半導体パッケージの薄型半導体チップは表裏両面の電極を除く領域をグランド用電極と接続された導体層で挟まれており、半導体素子の駆動を更に安定化させ、薄型半導体チップの外に不要電磁輻射を漏らすことを更に低減できると同時に周囲からの電磁輻射を受ける可能性を更に大幅に低減できた。また、導体層の部材を選択することで薄型半導体素子の反りを低減でき、積層時の実装歩留まりを著しく向上させるとともに、実装形態での長期信頼性をも向上させることができた。

【0049】

また、導体層120、122の部材を選択することで薄型半導体素子の反りを低減でき、積層時の実装歩留まりを著しく向上させるとともに、実装形態での長期信頼性をも向上させることができた。

【実施例3】

【0050】

本実施例は、本発明の半導体装置の内部で積層されるワイヤボンディングタイプの薄型半導体チップを示したものである。図11は、薄型メモリチップと樹脂基板多層配線インターポーザを積層して両者の電極をワイヤボンディングで接続し、薄型メモリチップの裏面に設けた導体層とインターポーザのグランド層とを接続した例を示したものである。

【0051】

薄型メモリチップ500は、表面に設けた半導体素子110とインターポーザ502と接続するための電極群112を備えている。電極群は、これに接続された半導体素子によって信号用電極群、グランド用電極群、電源用電極群に分類でき、それぞれ設けられている。また裏面には、導体層120が設けられている。

【0052】

インターポーザ502は薄型メモリチップの電極群112と接続するための電極群212と、グランド層151に接続された表面グランド電極215を備えている。薄型メモリチップの電極112とインターポーザの電極212はワイヤボンディング141で接続されている。また、薄型メモリチップの裏面の導体層120とインターポーザのグランド電極215は電気的に接続されている。

【0053】

図12は、薄型メモリチップの表面に導体層を設け、ワイヤボンディングを介してインターポーザのグランド層と接続した例を示したものである。すなわち、薄型半導体チップ500は表面に半導体素子110を形成するとともに第2の半導体チップ500あるいはインターポーザ502と接続するための電極群112を備えている。

【0054】

電極群112は、これに接続された半導体素子110によって信号用電極群、グランド用電極群、電源用電極群に分類でき、それぞれ設けられている。また、薄型半導体チップの表面は導体層122に覆われており、この表面導体層122は表面の上記電極群112のうちグランド用電極群115の一部あるいは全部と電気的に接続されている。

【0055】

インターポーザ502は薄型メモリチップ500の電極群112と接続するための電極群212を備えており、グランド層151に接続されたグランド電極群215も備えている。ワイヤボンディング141により、第1の薄型メモリチップ500の電極112と第2の薄型メモリチップ500の電極112、第2の薄型メモリチップ500の電極112とインターポーザの電極212、第1の半導体チップ表面のグランド用電極群115と第2の半導体チップ表面のグランド用電極群115、第2の半導体チップ表面のグランド用電極群115とインターポーザの表面グランド電極215が電気的に接続されている。

【0056】

図11あるいは図12のような半導体パッケージは、薄型半導体チップの貫通配線を必要とせず、薄型半導体チップの裏面導体層とインターポーザのグランド層を簡便に接続できることから、低コストで両者を積層することができた。また、高い接続信頼性を確保することができた。

【0057】

図13は、薄型メモリチップの裏面に設けた導体層と表面に設けたグランド電極を、貫通配線を介して接続し、その他の電極群とともにインターポーザの各電極群を接続した例を示したものである。グランド電極を貫通配線によって接続することによって、グランド配線の経路を短くすることが出来、シールド効果をより安定させることが出来る。

【0058】

すなわち、薄型半導体チップ500は表面に半導体素子110を形成するとともに第2の半導体チップ500あるいはインターポーザ502と接続するための電極群112を備えている。電極群112は、これに接続された半導体素子110によって信号用電極群、グランド用電極群、電源用電極群に分類でき、それぞれ設けられている。また、半導体チップの裏面には導体層120が設けられ、半導体チップを貫通する配線111を介して表面の上記電極群のうちグランド用電極群115の一部あるいは全部と電気的に接続されている。

【0059】

インターポーザ502は薄型メモリチップ500の電極群112と接続するための電極群212を備えており、グランド層151に接続されたグランド電極群215も備えている。

【0060】

ワイヤボンディング141により、第1の薄型メモリチップ500の電極112と第2の薄型メモリチップ500の電極112、第2の薄型メモリチップ500の電極112とインターポーザの電極212、第1の半導体チップ表面のグランド用電極群115と第2の半導体チップ表面のグランド用電極群115、第2の半導体チップ表面のグランド用電極群115とインターポーザの表面グランド電極215が電気的に接続されている。

【0061】

図14は、薄型メモリチップの表裏両面に導体層を設け、貫通配線を介して両導体層を接続した例を示したものである。すなわち、薄型半導体チップ500は表面に半導体素子110を形成するとともに第2の半導体チップあるいはインターポーザと接続するための電極群112を備えている。

【0062】

電極群112は、これに接続された半導体素子によって信号用電極群、グランド用電極群、電源用電極群に分類でき、それぞれ設けられている。また、半導体チップの表面は導体層122に覆われており、この表面導体層122は表面の上記電極群のうちグランド用電極群115の一部あるいは全部と電気的に接続されている。また、半導体チップ500の裏面にも導体層120が設けられており、この裏面導体層120と表面導体層122は半導体チップを貫通する配線111を介して電気的に接続されている。

【0063】

インターポーザ502は薄型メモリチップ500の電極群112と接続するための電極212と、グランド層151に接続された表面グランド電極215を備えている。インターポーザ502の電極群212や表面グランド電極215と重ならないように第1の薄型半導体チップ500をずらして積層するとともに、インターポーザの表面グランド層215と第1の薄型半導体チップ500の裏面導体層120を対向させて積層し接続する。

【0064】

また、第1の薄型半導体チップの電極群112やグランド電極群115と重ならないように第2の薄型半導体チップをずらして積層するとともに、第1の薄型半導体チップの表面導体層122と第2の薄型半導体チップの裏面導体層120とを接続する。

【0065】

ワイヤボンディング141により、第1の薄型メモリチップ500の電極112と第2の薄型メモリチップ500の電極112、第2の薄型メモリチップ500の電極112とインターポーザの電極212が電気的に接続されている。

【0066】

このような半導体パッケージの薄型半導体チップ500は表裏両面の電極群112を除く領域をグランド用電極と接続された導体層120、122で挟まれており、半導体素子110の駆動を更に安定化させ、薄型半導体チップの外に不要電磁輻射を漏らすことを更に低減できると同時に周囲からの電磁輻射を受ける可能性を更に大幅に低減できた。

また、導体層120、122の部材を選択することで薄型半導体素子の反りを低減でき、積層時の実装歩留まりを著しく向上させるとともに、実装形態での長期信頼性をも向上させることができた。

【0067】

以下に裏面導体層120の形成方法について説明する。裏面導体層120の形成方法は種々の方法が存在する。以上の実施例では、裏面導体層120としてNi膜を形成するとして説明した。Ni膜は、スパッタリングによって形成することが出来、膜厚は数十nmあればよい。また、Ni膜のパターニングはフォトリソグラフィを用い、エッチングによって行うことが出来る。

【0068】

裏面導体層120はNi膜に限らず、Cr−Cuの積層膜、あるいは、Al膜等によっても形成することが出来る。Cr−Cuの積層膜はスパッタリングによって形成することが出来、膜厚はCrが数十nm程度、Cuが数十nm程度〜数百nm程度である。Al膜もスパッタリングによって形成することが出来、Al膜の厚さは数十nm程度〜1μm程度である。Cr−Cuの積層膜の場合もAl膜の場合も、パターニングはフォトリソグラフィを用い、エッチングによって行うことが出来る。

【0069】

裏面導体層120をより厚く形成したい場合は、Ni膜あるいはCr−Cuの積層膜をパターニングした後、CuめっきあるいはNiめっきを行うことが出来る。このようなCuめっきあるいはNiめっきは数μmの厚さに裏面導体層120を形成することが出来る。

【0070】

以上の例は、裏面導体層120は金属膜を直接スパッタリングによってシリコンウェハ503に形成した場合である。以下の例は、裏面導体層120としてスパッタリングあるいはめっきによらずに、導体層を形成する場合である。

【0071】

図15は、シリコンウェハ503の裏面に金属箔620を接着剤によって貼り付ける例である。金属箔620としては、Al、Cu、ステンレス等を用いることが出来る。接着材610は例えば熱硬化性のエポキシ系の接着材を用いることが出来る。金属箔620の厚さは数μm、接着材610の厚さは数μm〜10μmである。

【0072】

このような導体層のパターニングは、樹脂を用いているので、エッチングは困難である。したがって、このタイプの裏面導体層120は、実施例3のような、ワイヤボンディングを用いる構成に特に適している。ワイヤボンディングを用いる構成では、シリコンウェハ503の裏面には、電極を形成しなくとも良い構成をとることが出来るからである。しかし、図15のような裏面導体層120を用いた場合でも、裏面に電極を形成する必要がある場合がある。この場合は、レーザ照射によって必要部分を除去すればよい。

【0073】

図16は、シリコンウェハ503の裏面に金属箔620を接着材630によって貼り付ける例であるが、接着材630には、黒点によって模式的に示すように、金属微粒子が分散されており、接着材630自身が導電性を有している場合である。図16における金属箔620の種類、金属箔620の厚さ、接着材630の厚さ等は図15で説明したのと同様である。接着材に分散されている金属微粒子には、Ag、Cu、Ni等の微粒子を用いることが出来る。接着材630は例えば、エポキシ樹脂を用いることが出来る。エポキシは熱膨張係数が大きいが、問題となる場合には、熱硬化性のポリイミド系樹脂を使用することも出来る。この場合、接着力を上げるために、ポリイミド樹脂にエポキシ樹脂を分散させたものを使用することが出来る。

【0074】

図17は、シリコンウェハ503の裏面に金属箔を用いず、導電性微粒子を分散させた導電性接着材630のみを用いた例である。導電性接着材630は図16において説明したのと同様なものを用いることが出来る。この場合、例えば、第1のシリコンウェハと第2のシリコンウェハを導電性接着材によって電気的、機械的に接続することが出来る。具体的には、保護シートでサンドイッチした熱硬化性の導電接着材のシートを取り出し、第1のシリコンウェハと第2のシリコンウェハとでサンドイッチして、加熱することによって第1のシリコンウェハと第2のシリコンウェハを接続する。

【0075】

以上では、シリコンウェハ503の裏面導体層120の形成方法について説明した。しかし、このような裏面導体層120の形成方法は、実施例2で説明したようなシリコンウェハ503の表面導体層122の形成に対しても適用することが出来る。

【0076】

また、以上の実施例では、シリコンウェハの裏面あるいは表面に形成された導体層は全てマザーボードあるいはインターポーザのグランドと接続された構成で説明した。しかし、この導体層は、必ずしもグランドと接続して使用されるとは限らない。導体層はシリコンウェハの反りを是正する効果があるので、この目的で使用する場合は、導体層をグランドに接続しないで使用する場合もある。

【符号の説明】

【0077】

100…シリコン基板、101…n型チャネル、102…n型チャネル、103…p型チャネル、104…酸化膜、105…ソース、106…ドレイン、107…ゲート、108…等電位面、110…半導体素子、111…シリコン貫通配線、112…表面電極、113…裏面電極、114…信号用電極群、115…グランド用電極群、116…電源用電極群、118…薄型半導体チップ、119…積層半導体パッケージ、120…裏面導体層、121…シリコン貫通配線、122…表面導体層、130…はんだボール、140…モールド樹脂、141…ワイヤボンディング150…マザーボードグランド層、151…インターポーザグランド層、212…インターポーザ電極群、215…インターポーザグランド用電極、500…メモリチップ、501…ドライバIC、502…樹脂基板多層配線インターポーザ、503…シリコンウェハ、504…シリコンインターポーザ、505…マザーボード、610…熱硬化性接着材、620…金属箔、630…導電性接着材、5031…非貫通穴、5032…TEOS膜、5033…金属膜、5034…レジスト、5035…Cuめっき、5036…Niメッキ。

【技術分野】

【0001】

本発明は、メモリ素子をはじめとする複数の半導体チップを基板上に実装したメモリパッケージなどの半導体装置に関し、とくに薄型の半導体パッケージを積層実装して小型化したメモリパッケージの動作の信頼性を高めるための構造に関するものである。

【背景技術】

【0002】

近年の半導体パッケージは、従来にも増して高集積化の要求が強まっている。こうした要求に対して、従来は、半導体チップの電界効果トランジスタ(FET)をはじめとする半導体素子の面密度を高めることで応えてきた。しかし、高集積化の進んだ今日においては、半導体素子の面密度を更に高めることへの技術的課題は多く、要求される高集積化の時間軸に追従することが困難になってきた。そこで、半導体素子を搭載した半導体ウェハもしくはチップを薄く研磨し、これを複数枚積層し、電気的に接続してパッケージ化する3次元実装技術の開発が注目されている。この一例として、「特許文献1」および「特許文献2」が挙げられる。

【0003】

「特許文献1」では、チップを三次元積層した場合においても、反りが生じたり、フリップチップ接続した半導体チップが剥離したり、半導体チップが薄型のものであってもクラックが生じたりするおそれのない半導体積層パッケージについて記載されている。また、「特許文献2」では、実装状態での落下や実装基板の変形にも耐えうる薄型の半導体装置について記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003-7962

【特許文献2】特開2009-26833

【発明の概要】

【発明が解決しようとする課題】

【0005】

半導体積層パッケージの薄型半導体チップに関しては、以下のような課題がある。半導体チップを薄く研磨することにより半導体素子を支持するウェハ厚が薄くなってきている。2008年現在で、25マイクロメートル厚にまで薄くした半導体チップを積層した半導体パッケージが製品化されており、20マイクロメートルを下回るほど薄く研磨する技術も開発されている。

【0006】

図1はn型チャネルMOSFETの断面図を示したものである。半導体チップの薄型化に伴い、表面に設けた半導体素子の電界が半導体チップの裏面に大きくしみ出すこととなり、半導体素子そのものの動作の信頼性が損なわれることが懸念される。また、このような薄型半導体チップを複数積層した半導体積層パッケージでは数マイクロメートル〜数十マイクロメートルの距離を隔てて薄型半導体チップが積層される。そのため、第1の半導体チップの裏面にしみ出した電界が直下に置かれた第2の半導体チップにおける半導体素子の駆動に作用した場合、誤動作の原因となる。

【0007】

また、図2に示すように、表面に設けた半導体素子により半導体チップは面内および表裏での対称性を保つことが不可能である。そのため構成部材による応力や熱膨張係数の差異が生じ、また薄く研磨する際のウェハ厚のわずかなバラツキ(面内での不均一性)により、半導体チップには反りが生じる。これにより、積層時の実装歩留まりを著しく低下させるとともに、実装形態での長期信頼性をも低下させる。

【0008】

さらに、半導体素子は高周波信号を制御するが、素子回路自身がアンテナとして機能することで不要電磁輻射が生じた場合、半導体素子の誤動作となり得る。ドライバICをはじめとする高速演算素子を搭載したチップを積層する場合、こうした誤動作は顕著となる。

【0009】

不要電磁輻射が生じにくいよう、また生じた不要電磁輻射の影響を受けにくくなるよう、半導体チップの内部回路は設計されているが、数マイクロメートル〜数十マイクロメートルの間隔を隔てて積層された第2の薄型半導体チップに対しては、第1の半導体チップからの不要電磁輻射を考慮した設計を行うことは困難である。異なるメーカの半導体チップを積層する場合、特に困難となる。

【0010】

本発明は、上記の課題を解決する半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明は、半導体素子と、前記半導体素子と接続され、半導体素子に信号を供給する配線と電極を表面に具備し、ウェハを貫通する貫通配線を具備し、裏面に電極と導体層を具備した半導体チップを搭載したインターポーザ付き半導体パッケージにおいて、前記半導体チップの前記裏面導体層がインターポーザもしくは半導体パッケージを搭載するマザーボードに設けたグランド層と電気的に接続されていることを特徴とする半導体パッケージである。これによって半導体チップの駆動安定性を高めるとともに接続時の歩留まり向上と接続の長期信頼性向上に寄与するものである。これについて、以下に説明する。

【0012】

先に説明したとおり、半導体チップの薄型化により半導体素子の裏面の電界は大きくなるが、ここにグランド層と接続した導体層を形成したことで、導体層面での電界は安定する。これにより、半導体チップ内部の電界に対する外部電磁界からの影響は極めて小さくなる。また、数マイクロメートル〜数十マイクロメートルの距離を隔てて薄型半導体チップを積層した場合、第1の半導体チップの裏面における電界が安定することにより、直下に置かれた第2の半導体チップでの半導体素子の駆動安定性も高くなる。

【0013】

また、高速演算素子を搭載したチップの駆動では特に顕著に生じる不要電磁輻射についても、導体層によるシールド効果により積層した別チップへの影響を大幅に低減させることができる。これにより、チップの誤動作を大幅に低減できる。

【0014】

導体層に求められる特性は、主として導電性、ウェハ密着性、パターニング性である。半導体チップの裏面に設ける電極と同時に同一プロセスで導体層を形成することで、導体層形成のための追加コストがほとんど掛からないため有利である。上記特性に加え、導体層形成のためのコスト増加を抑制できるのであれば、裏面電極形成に導体層形成工程を付加することは有効である。

【0015】

例えば、裏面電極とは異なる種類の導体層としてもよいし、裏面電極形成と同時に導体層を形成した後にこの導体層に異なる種類の導体層あるいは樹脂材料をはじめとする絶縁層を選択的に付加してもよいし、裏面電極と同じ種類であっても膜の成長速度や成膜環境・条件の変更や異なる膜厚としてもよいし、成膜時や成膜後に加熱あるいは冷却工程を加えてもよい。これら形成工程を選択することで、導体層の内部応力を制御し、薄型半導体チップの反りを低減させることができる。

【発明の効果】

【0016】

本発明に係る半導体装置は、表面に半導体素子を設けた薄型半導体チップの裏面に導体層を設け、これをインターポーザあるいはマザーボードのグランド層と電気的に接続したことにより、薄型半導体素子の裏面にしみ出す電界を半導体チップに閉じ込めることができる。

【0017】

また、このような半導体チップを積層した場合、安定したシールド効果により不要電磁輻射を半導体チップの中に留めることができるとともに、外部からの不要電磁輻射を抑制することができる。こうした効果は導体層の部材や膜質によらず得られるので、導体層の選択肢は広く、薄型半導体チップの反りを抑制することもできる。

【図面の簡単な説明】

【0018】

【図1】一般的なn型チャネルMOSFETの構成例を示す図である。

【図2】従来の薄型半導体チップの反り状態を示す図である。

【図3】実施例1の薄型半導体チップを示す斜視図である。

【図4】実施例1の薄型半導体チップを積層した半導体パッケージを示す図である。

【図5】実施例1の半導体パッケージの製作工程を示す図である。

【図6】実施例1のシリコンウェハの製造工程を示す図である。

【図7】実施例1の薄型半導体チップとして薄型メモリチップを複数積層し、樹脂基板多層配線インターポーザに積層した半導体パッケージを示す図である。

【図8】実施例1の薄型半導体チップを積層した半導体パッケージをマザーボードに実装した様子を示す図である。

【図9】実施例2の薄型半導体チップを示す斜視図である。

【図10】実施例2の薄型半導体チップを積層した半導体パッケージを示す図である。

【図11】実施例3の薄型半導体チップを積層した半導体パッケージを示す図である。

【図12】実施例3の薄型半導体チップを積層した半導体パッケージを示す図である。

【図13】実施例3の薄型半導体チップを積層した半導体パッケージを示す図である。

【図14】実施例3の薄型半導体チップを積層した半導体パッケージを示す図である。

【図15】シリコンウェハに形成される金属スパッタリング膜以外の導体層の例である。

【図16】シリコンウェハに形成される導体層の他の例である。

【図17】シリコンウェハに形成される導体層のさらに他の例である。

【発明を実施するための形態】

【0019】

以下、図面を参照して本発明の実施の形態を説明する。

【実施例1】

【0020】

図3に示す半導体チップは、本発明の半導体装置の内部で積層されるフリップチップタイプの薄型半導体チップを裏面側から見た斜視図である。薄型半導体チップ118は、表面に半導体素子110を形成するとともに第2の半導体チップあるいはインターポーザと接続するための表面電極112を備えており、また、半導体チップを貫通する穴を介して裏面に設けた電極群113を経て第3の半導体チップと接続するための電極をもつ。

【0021】

表裏面に設けた電極群は、これに接続された半導体素子によって信号用電極群114、グランド用電極群115、電源用電極群116に分類でき、それぞれ分離されて設けられている。また、電極群を除く半導体素子の裏面は導体層120に覆われており、上記電極群のうちグランド用電極群115の一部あるいは全部と電気的に接続され、信号用電極群114や電源用電極群116とは電気的に分離されている。

【0022】

例えば導体層にニッケルを用いた場合、成膜後に200℃程度に加熱すると収縮応力が作用する。薄型半導体チップが半導体素子を有する表面が凹面となるような反りを示していた場合、ニッケルの収縮応力は反りを低減することができる。また、樹脂材料からなる膜を導体層に貼り付けることでも反りの低減に効果的であり、加えて接着性を有する場合、これと積層される半導体チップとの接着性を向上させることもできる。

【0023】

図4に示す半導体装置は、図3に示した薄型半導体チップを積層した半導体パッケージ119の断面図の一例を示したものであり、メモリチップ500、ドライバIC501、インターポーザ502から構成される。

【0024】

半導体素子110の裏面に設けた導体層120はグランド用電極群115や第2、第3の半導体チップのグランド用電極群115とフリップチップ接続され、インターポーザに設けたグランド層に接続されている。また、信号用電極群や電源用電極群も、機能に応じておのおの適切に第2、第3の半導体チップの信号用電極群あるいは電源用電極群とはんだボール130を介してフリップチップ接続されている。

【0025】

図3の薄型半導体チップおよび図4の積層半導体パッケージの作製方法を、図5および図6を用いて説明する。図5において、まず、シリコンウェハ503の表面に、FETをはじめとする回路からなる半導体素子110を形成する(図5A)。この回路には、チップを駆動させるための表面回路電極群も含まれており、これらは用途に応じて信号用、グランド用、電源用としてそれぞれ機能する。

【0026】

このようなシリコンウェハの表面に絶縁層とアルミニウム膜を逐次積層し、非貫通穴を形成する領域のアルミニウム膜を除去する。アルミニウム膜をマスクとして、Boschプロセスに代表される反応性イオンエッチング(Reactive Ion Etching、RIE)により、アルミニウム膜の開口部のシリコンに非貫通穴を形成する。その後、マスクとして用いたアルミニウム膜を除去する。

【0027】

図6Aは、アルミニウム膜を除去した後のシリコンウェハ503の断面図である。図6Aには、回路素子110と非貫通穴5031が示されている。次に、シリコンウェハ503の表面全面にTEOS膜(Tetra Etoxi Silanによって形成されたSiO2膜)を形成する。SiO2膜の上に、例えば、Ni膜あるいはCr−Cuの積層膜等の金属膜5033をスパッタリングによって形成する。図6Bはこの状態を示す断面図である。

【0028】

次に、図6Cに示すように、金属膜5033の上にレジスト5034を形成する。レジストは、金属膜5033の上に選択的に銅めっき5035を形成するためである。次にシリコンウェハ503に対して銅めっきをおこなうと、図6Dに示すように、銅めっきはレジストの付いていない金属膜5033上に形成される。

【0029】

図6Dに示すように、非貫通穴5031は銅めっき5035によって充填され、シリコン貫通配線111が形成される。銅めっき5035は非貫通穴5031以外の箇所で、表面電極112が形成される部分、および、半導体素子110と表面電極112を結ぶ配線部分にも形成される。その後、図6Eに示すように、銅めっき5035の上にNiめっき5036を形成する。したがって、電極の表面にはNiめっき5036が形成されていることになる。

【0030】

次に図6Fに示すように、レジスト5034を除去する。さらに、電極を形成するCuめっき5035およびNiめっき5036をレジストにして、金属膜5033をエッチングによって除去する。この状態が図6Gである。

【0031】

図5Bは、図6Gの状態を金属膜等を省略し、簡略化して表したシリコンウェハ503の断面図である。図5Bは、シリコンウェハ503の表面に、表面回路電極群、シリコン貫通配線111が形成された非貫通穴、およびこれらを結ぶ配線が形成された状態である。

【0032】

次に、シリコンウェハ503の裏面を研磨して非貫通穴に充填した銅5035を露出させた後、裏面にニッケル膜を成膜する。ニッケル膜のパターニングによりチップ積層電極群(裏面)を形成するとともに、チップ積層電極群(裏面)の隙間を埋めるよう電気的に繋がったシールド用ニッケル膜を形成する。ただし、グランド用の表面回路電極群と電気的に接続されたグランド用チップ積層電極群(裏面)のうち少なくとも一つをシールド用ニッケル膜と接続させておく。チップ積層電極群(裏面)に選択的にはんだを形成し、ダイシングを経て薄型半導体チップを得る(図5C)。

【0033】

ここでは、半導体素子を形成した後で半導体チップの貫通穴を形成する、いわゆるvia lastと呼ばれる製造法での半導体チップの作製法を示したが、これに限定されるものではない。先に貫通穴を形成した後に半導体素子を形成するVia Firstと呼ばれる製造法で作製してもよい。

【0034】

このような方法で作成した薄型半導体チップは、回路構成に応じてメモリやドライバICとしての機能を付加させることができ、以降、それぞれ薄型メモリチップ、薄型ドライバICチップと称する。

【0035】

薄型半導体チップと接続するための電極を表面に備え、内層にグランド層をもち、裏面にマザーボードと接続するための電極を備え、層間を電気的に接続するビア配線を備えた多層配線樹脂基板に薄型メモリチップ、薄型ドライバICチップを重ね、はんだによって積層チップの電極を接合させる。このとき、多層配線樹脂基板のグランド層は薄型半導体チップのシールド用ニッケル層と電気的に接続させる(図5D)。

【0036】

ここで、グランド層や電源層で統一できる配線同士を接続することで、層間を電気的に接続するビア配線を少なくすることも可能であり、薄型半導体チップの貫通配線よりも大きなピッチとなる多層配線樹脂基板に有利である。これを樹脂材料で封止させて、図4に示すような半導体パッケージを得る。

【0037】

このようにして得た半導体パッケージは、それぞれの薄型半導体チップの裏面にインターポーザのグランド層と接続されたシールド用ニッケル層を有する。これにより、薄型半導体チップの裏面の電位が安定することから、表面に設けたFETをはじめとする回路からの電場のしみ出しをシールド用ニッケル層で抑えることができた。

【0038】

また、回路での高速信号により生じた不要電磁輻射はシールド用ニッケル層で吸収されるため、積層された他の薄型半導体チップの回路までは到達せず、誤動作を抑制することができる。

【0039】

FET形成に用いたヒ素やリン、ホウ素をはじめとするドーパント、回路の配線材料に用いるAl膜やCu膜、絶縁層に用いられるTEOS膜や窒化シリコン膜によって、半導体チップの構造は表面の面内や表裏面での対称性が崩れており、これら構成部材の内部応力によって半導体チップに反りが発生する。例えば、半導体チップの表面に収縮応力が作用することにより、表面が凹面となるような馬蹄形になる。このような現象は、裏面に設けたニッケル層が加熱により収縮することによって生じる収縮応力によって緩和され、半導体チップの平滑性は改善した。

【0040】

以上では薄型メモリチップ500、薄型ドライバICチップ501、インターポーザ502を積層した半導体パッケージの例を示したが、図7に示すような複数の薄型メモリチップとインターポーザを積層したメモリパッケージでもよく、積層するチップの機能を制限するものではない。また、インターポーザはその機能から積層されるチップの最上層もしくは最下層に位置するが、その他のチップはその積層する順番を制限されるものではない。

【0041】

以上ではインターポーザとして多層配線樹脂基板を用いた例を説明したが、シリコンウェハを基材としたインターポーザとした例を図8に示す。表面に薄型半導体チップと接続するための電極および配線の形成工程、シリコンの穴あけ加工および配線形成工程、ウェハの薄化工程、裏面の電極形成工程、ダイシング工程を適宜組合せて実施することで、薄型半導体チップと接続するシリコンインターポーザ504を得る。このようなインターポーザを薄型メモリチップ500と重ねてはんだ融点まで昇温させることで積層チップの電極を接合し、樹脂材料でチップを封止して半導体パッケージを得る。

【0042】

これら半導体パッケージの各電極群をマザーボード505の各電極群と接続して搭載する際、薄型メモリチップの裏面に形成した導体層は、それぞれのグランド電極を介して接続され、インターポーザのグランド電極を経由してマザーボードに設けたグランド層150と接続する構造とする。シリコンインターポーザの場合、その表面の多層配線に薄型半導体チップの裏面に形成した導体層と接続したグランド層を設けることも可能であるが、マザーボードのグランド層と接続した方が電気的安定性は高くなる。

【0043】

また、導体層120の部材を選択することで薄型半導体素子の反りを低減でき、積層時の実装歩留まりを著しく向上させるとともに、実装形態での長期信頼性をも向上させることができた。

【実施例2】

【0044】

図9は本発明の半導体装置の内部で積層されるフリップチップタイプの薄型半導体チップを示したものであり、薄型半導体チップの表裏面に導体層を有するものであり、図9Aは半導体素子側(表面)、図9Bはシリコン研磨面側(裏面)からの斜視図を示したものである。

【0045】

薄型半導体チップは、表面に半導体素子110を形成するとともに第2の半導体チップと接続するための電極112を備えており、また、半導体チップを貫通する配線111を経て第3の半導体チップあるいはインターポーザと接続するための電極113をもつ。表裏面に設けた電極群112、113は、これに接続された半導体素子110によって信号用電極群114、グランド用電極群115、電源用電極群116としての機能をそれぞれ有する。なお、半導体素子110の上には、図6Aに示す非貫通穴5031を形成するときのレジストとなるAl膜を形成する前に被着した絶縁膜および、非貫通穴5031形成後に被着した図6Bに示すTEOS膜5032が被着されている。

【0046】

半導体素子110の表面は導体層122に覆われており、表面の上記電極群のうちグランド用電極群の一部あるいは全部と電気的に接続されている。また、裏面は導体層120に覆われており、裏面の上記電極群のうちグランド用電極群の一部あるいは全部と電気的に接続されている。

【0047】

図10は、図9に示した同様の薄型半導体チップを複数積層した半導体パッケージを示したものであり、薄型半導体チップの表裏に設けた導体層120、122はこれを接続したグランド用電極115を介して、インターポーザのグランド層151と接続されている。

【0048】

このような半導体パッケージの薄型半導体チップは表裏両面の電極を除く領域をグランド用電極と接続された導体層で挟まれており、半導体素子の駆動を更に安定化させ、薄型半導体チップの外に不要電磁輻射を漏らすことを更に低減できると同時に周囲からの電磁輻射を受ける可能性を更に大幅に低減できた。また、導体層の部材を選択することで薄型半導体素子の反りを低減でき、積層時の実装歩留まりを著しく向上させるとともに、実装形態での長期信頼性をも向上させることができた。

【0049】

また、導体層120、122の部材を選択することで薄型半導体素子の反りを低減でき、積層時の実装歩留まりを著しく向上させるとともに、実装形態での長期信頼性をも向上させることができた。

【実施例3】

【0050】

本実施例は、本発明の半導体装置の内部で積層されるワイヤボンディングタイプの薄型半導体チップを示したものである。図11は、薄型メモリチップと樹脂基板多層配線インターポーザを積層して両者の電極をワイヤボンディングで接続し、薄型メモリチップの裏面に設けた導体層とインターポーザのグランド層とを接続した例を示したものである。

【0051】

薄型メモリチップ500は、表面に設けた半導体素子110とインターポーザ502と接続するための電極群112を備えている。電極群は、これに接続された半導体素子によって信号用電極群、グランド用電極群、電源用電極群に分類でき、それぞれ設けられている。また裏面には、導体層120が設けられている。

【0052】

インターポーザ502は薄型メモリチップの電極群112と接続するための電極群212と、グランド層151に接続された表面グランド電極215を備えている。薄型メモリチップの電極112とインターポーザの電極212はワイヤボンディング141で接続されている。また、薄型メモリチップの裏面の導体層120とインターポーザのグランド電極215は電気的に接続されている。

【0053】

図12は、薄型メモリチップの表面に導体層を設け、ワイヤボンディングを介してインターポーザのグランド層と接続した例を示したものである。すなわち、薄型半導体チップ500は表面に半導体素子110を形成するとともに第2の半導体チップ500あるいはインターポーザ502と接続するための電極群112を備えている。

【0054】

電極群112は、これに接続された半導体素子110によって信号用電極群、グランド用電極群、電源用電極群に分類でき、それぞれ設けられている。また、薄型半導体チップの表面は導体層122に覆われており、この表面導体層122は表面の上記電極群112のうちグランド用電極群115の一部あるいは全部と電気的に接続されている。

【0055】

インターポーザ502は薄型メモリチップ500の電極群112と接続するための電極群212を備えており、グランド層151に接続されたグランド電極群215も備えている。ワイヤボンディング141により、第1の薄型メモリチップ500の電極112と第2の薄型メモリチップ500の電極112、第2の薄型メモリチップ500の電極112とインターポーザの電極212、第1の半導体チップ表面のグランド用電極群115と第2の半導体チップ表面のグランド用電極群115、第2の半導体チップ表面のグランド用電極群115とインターポーザの表面グランド電極215が電気的に接続されている。

【0056】

図11あるいは図12のような半導体パッケージは、薄型半導体チップの貫通配線を必要とせず、薄型半導体チップの裏面導体層とインターポーザのグランド層を簡便に接続できることから、低コストで両者を積層することができた。また、高い接続信頼性を確保することができた。

【0057】

図13は、薄型メモリチップの裏面に設けた導体層と表面に設けたグランド電極を、貫通配線を介して接続し、その他の電極群とともにインターポーザの各電極群を接続した例を示したものである。グランド電極を貫通配線によって接続することによって、グランド配線の経路を短くすることが出来、シールド効果をより安定させることが出来る。

【0058】

すなわち、薄型半導体チップ500は表面に半導体素子110を形成するとともに第2の半導体チップ500あるいはインターポーザ502と接続するための電極群112を備えている。電極群112は、これに接続された半導体素子110によって信号用電極群、グランド用電極群、電源用電極群に分類でき、それぞれ設けられている。また、半導体チップの裏面には導体層120が設けられ、半導体チップを貫通する配線111を介して表面の上記電極群のうちグランド用電極群115の一部あるいは全部と電気的に接続されている。

【0059】

インターポーザ502は薄型メモリチップ500の電極群112と接続するための電極群212を備えており、グランド層151に接続されたグランド電極群215も備えている。

【0060】

ワイヤボンディング141により、第1の薄型メモリチップ500の電極112と第2の薄型メモリチップ500の電極112、第2の薄型メモリチップ500の電極112とインターポーザの電極212、第1の半導体チップ表面のグランド用電極群115と第2の半導体チップ表面のグランド用電極群115、第2の半導体チップ表面のグランド用電極群115とインターポーザの表面グランド電極215が電気的に接続されている。

【0061】

図14は、薄型メモリチップの表裏両面に導体層を設け、貫通配線を介して両導体層を接続した例を示したものである。すなわち、薄型半導体チップ500は表面に半導体素子110を形成するとともに第2の半導体チップあるいはインターポーザと接続するための電極群112を備えている。

【0062】

電極群112は、これに接続された半導体素子によって信号用電極群、グランド用電極群、電源用電極群に分類でき、それぞれ設けられている。また、半導体チップの表面は導体層122に覆われており、この表面導体層122は表面の上記電極群のうちグランド用電極群115の一部あるいは全部と電気的に接続されている。また、半導体チップ500の裏面にも導体層120が設けられており、この裏面導体層120と表面導体層122は半導体チップを貫通する配線111を介して電気的に接続されている。

【0063】

インターポーザ502は薄型メモリチップ500の電極群112と接続するための電極212と、グランド層151に接続された表面グランド電極215を備えている。インターポーザ502の電極群212や表面グランド電極215と重ならないように第1の薄型半導体チップ500をずらして積層するとともに、インターポーザの表面グランド層215と第1の薄型半導体チップ500の裏面導体層120を対向させて積層し接続する。

【0064】

また、第1の薄型半導体チップの電極群112やグランド電極群115と重ならないように第2の薄型半導体チップをずらして積層するとともに、第1の薄型半導体チップの表面導体層122と第2の薄型半導体チップの裏面導体層120とを接続する。

【0065】

ワイヤボンディング141により、第1の薄型メモリチップ500の電極112と第2の薄型メモリチップ500の電極112、第2の薄型メモリチップ500の電極112とインターポーザの電極212が電気的に接続されている。

【0066】

このような半導体パッケージの薄型半導体チップ500は表裏両面の電極群112を除く領域をグランド用電極と接続された導体層120、122で挟まれており、半導体素子110の駆動を更に安定化させ、薄型半導体チップの外に不要電磁輻射を漏らすことを更に低減できると同時に周囲からの電磁輻射を受ける可能性を更に大幅に低減できた。

また、導体層120、122の部材を選択することで薄型半導体素子の反りを低減でき、積層時の実装歩留まりを著しく向上させるとともに、実装形態での長期信頼性をも向上させることができた。

【0067】

以下に裏面導体層120の形成方法について説明する。裏面導体層120の形成方法は種々の方法が存在する。以上の実施例では、裏面導体層120としてNi膜を形成するとして説明した。Ni膜は、スパッタリングによって形成することが出来、膜厚は数十nmあればよい。また、Ni膜のパターニングはフォトリソグラフィを用い、エッチングによって行うことが出来る。

【0068】

裏面導体層120はNi膜に限らず、Cr−Cuの積層膜、あるいは、Al膜等によっても形成することが出来る。Cr−Cuの積層膜はスパッタリングによって形成することが出来、膜厚はCrが数十nm程度、Cuが数十nm程度〜数百nm程度である。Al膜もスパッタリングによって形成することが出来、Al膜の厚さは数十nm程度〜1μm程度である。Cr−Cuの積層膜の場合もAl膜の場合も、パターニングはフォトリソグラフィを用い、エッチングによって行うことが出来る。

【0069】

裏面導体層120をより厚く形成したい場合は、Ni膜あるいはCr−Cuの積層膜をパターニングした後、CuめっきあるいはNiめっきを行うことが出来る。このようなCuめっきあるいはNiめっきは数μmの厚さに裏面導体層120を形成することが出来る。

【0070】

以上の例は、裏面導体層120は金属膜を直接スパッタリングによってシリコンウェハ503に形成した場合である。以下の例は、裏面導体層120としてスパッタリングあるいはめっきによらずに、導体層を形成する場合である。

【0071】

図15は、シリコンウェハ503の裏面に金属箔620を接着剤によって貼り付ける例である。金属箔620としては、Al、Cu、ステンレス等を用いることが出来る。接着材610は例えば熱硬化性のエポキシ系の接着材を用いることが出来る。金属箔620の厚さは数μm、接着材610の厚さは数μm〜10μmである。

【0072】

このような導体層のパターニングは、樹脂を用いているので、エッチングは困難である。したがって、このタイプの裏面導体層120は、実施例3のような、ワイヤボンディングを用いる構成に特に適している。ワイヤボンディングを用いる構成では、シリコンウェハ503の裏面には、電極を形成しなくとも良い構成をとることが出来るからである。しかし、図15のような裏面導体層120を用いた場合でも、裏面に電極を形成する必要がある場合がある。この場合は、レーザ照射によって必要部分を除去すればよい。

【0073】

図16は、シリコンウェハ503の裏面に金属箔620を接着材630によって貼り付ける例であるが、接着材630には、黒点によって模式的に示すように、金属微粒子が分散されており、接着材630自身が導電性を有している場合である。図16における金属箔620の種類、金属箔620の厚さ、接着材630の厚さ等は図15で説明したのと同様である。接着材に分散されている金属微粒子には、Ag、Cu、Ni等の微粒子を用いることが出来る。接着材630は例えば、エポキシ樹脂を用いることが出来る。エポキシは熱膨張係数が大きいが、問題となる場合には、熱硬化性のポリイミド系樹脂を使用することも出来る。この場合、接着力を上げるために、ポリイミド樹脂にエポキシ樹脂を分散させたものを使用することが出来る。

【0074】

図17は、シリコンウェハ503の裏面に金属箔を用いず、導電性微粒子を分散させた導電性接着材630のみを用いた例である。導電性接着材630は図16において説明したのと同様なものを用いることが出来る。この場合、例えば、第1のシリコンウェハと第2のシリコンウェハを導電性接着材によって電気的、機械的に接続することが出来る。具体的には、保護シートでサンドイッチした熱硬化性の導電接着材のシートを取り出し、第1のシリコンウェハと第2のシリコンウェハとでサンドイッチして、加熱することによって第1のシリコンウェハと第2のシリコンウェハを接続する。

【0075】

以上では、シリコンウェハ503の裏面導体層120の形成方法について説明した。しかし、このような裏面導体層120の形成方法は、実施例2で説明したようなシリコンウェハ503の表面導体層122の形成に対しても適用することが出来る。

【0076】

また、以上の実施例では、シリコンウェハの裏面あるいは表面に形成された導体層は全てマザーボードあるいはインターポーザのグランドと接続された構成で説明した。しかし、この導体層は、必ずしもグランドと接続して使用されるとは限らない。導体層はシリコンウェハの反りを是正する効果があるので、この目的で使用する場合は、導体層をグランドに接続しないで使用する場合もある。

【符号の説明】

【0077】

100…シリコン基板、101…n型チャネル、102…n型チャネル、103…p型チャネル、104…酸化膜、105…ソース、106…ドレイン、107…ゲート、108…等電位面、110…半導体素子、111…シリコン貫通配線、112…表面電極、113…裏面電極、114…信号用電極群、115…グランド用電極群、116…電源用電極群、118…薄型半導体チップ、119…積層半導体パッケージ、120…裏面導体層、121…シリコン貫通配線、122…表面導体層、130…はんだボール、140…モールド樹脂、141…ワイヤボンディング150…マザーボードグランド層、151…インターポーザグランド層、212…インターポーザ電極群、215…インターポーザグランド用電極、500…メモリチップ、501…ドライバIC、502…樹脂基板多層配線インターポーザ、503…シリコンウェハ、504…シリコンインターポーザ、505…マザーボード、610…熱硬化性接着材、620…金属箔、630…導電性接着材、5031…非貫通穴、5032…TEOS膜、5033…金属膜、5034…レジスト、5035…Cuめっき、5036…Niメッキ。

【特許請求の範囲】

【請求項1】

チップの表面に半導体素子と、前記半導体素子と接続され半導体素子に信号を供給する配線と、信号用電極群、電源用電極群、グランド用電極群を有する半導体チップであって、

前記チップの裏面には、前記信号用電極群、前記電源用電極群とは絶縁された導体層が前記裏面を覆って形成されていることを特徴とする半導体チップ。

【請求項2】

前記チップには貫通配線が形成され、前記貫通配線は前記チップの表面に形成されたグランド電極と前記裏面に形成された前記導体層とを電気的に接続していることを特徴とする請求項1に記載の半導体チップ。

【請求項3】

前記チップの表面には、前記信号用電極群および前記電源用電極群と絶縁して、前記半導体素子の表面を含む前記チップの表面を覆う導体層が形成されていることを特徴とする請求項1または請求項2に記載の半導体チップ。

【請求項4】

チップの表面に半導体素子と、前記半導体素子と接続され半導体素子に信号を供給する配線と、信号用電極群、電源用電極群、グランド用電極群を有する半導体チップであって、

前記チップの裏面には、前記信号用電極群、前記電源用電極群とは絶縁された導体層が前記裏面を覆って形成されており、

前記チップを貫通する貫通配線が前記チップ表面のグランド用電極群と、前記チップの裏面に形成された前記導体層を接続していることを特徴とする半導体チップ。

【請求項5】

チップの表面に半導体素子と、前記半導体素子と接続され半導体素子に信号を供給する配線と、信号用電極群、電源用電極群、グランド用電極群を有し、チップの裏面に信号用電極群、電源用電極群、グランド用電極群を有し、チップを貫通する貫通配線が前記チップの表面と前記チップの裏面に形成された、前記信号用電極群どうし、前記電源用電極群どうし、前記グランド用電極群どうしを接続している半導体チップであって、

前記チップの裏面には、前記信号用電極群、電源用電極群とは絶縁し、前記裏面を覆う導体層が形成され、前記グランド用電極群と前記導体層は電気的に接続していることを特徴とする半導体チップ。

【請求項6】

前記チップの表面には、前記信号用電極群、前記電源用電極群と絶縁して、前記半導体素子の表面を含む前記チップの表面を覆う導体層が形成されていることを特徴とする請求項5に記載の半導体チップ。

【請求項7】

前記裏面または前記表面に形成された前記導体層は、スパッタリングによって形成された金属膜であることを特徴とする請求項1乃至請求項6のいずれか1項に記載の半導体チップ。

【請求項8】

前記裏面または前記表面に形成された前記導体層の表面には、金属メッキが形成されていることを特徴とする請求項1乃至請求項6のいずれか1項に記載の半導体チップ。

【請求項9】

前記裏面または前記表面に形成された前記導体層の表面には、金属微粒子が分散された導電性樹脂膜が形成されていることを特徴とする請求項1乃至請求項6のいずれか1項に記載の半導体チップ。

【請求項10】

複数の半導体チップとインターポーザを積層して形成された半導体パッケージであって、

前記インターポーザは、前記半導体チップと接続するための電極を表面に備え、内層にグランド層を持ち、裏面にマザーボードと接続するための電極を備え、

前記半導体チップは請求項1乃至請求項9のいずれか1項に記載の半導体チップであることを特徴とする半導体パッケージ。

【請求項11】

複数の半導体チップとインターポーザを積層して形成された半導体パッケージを有し、グランド配線をマザー基板であって、

前記インターポーザは、前記半導体チップと接続するための電極を表面に備え、内層にグランド層を持ち、裏面にマザーボードと接続するための電極を備え、

前記半導体チップは請求項1乃至請求項9のいずれか1項に記載の半導体チップであり、

前記半導体チップの前記グランド配線と前記導体層と前記インターポーザのグランド層と前記マザー基板のグランド配線とは接続していることを特徴とするマザー基板。

【請求項1】

チップの表面に半導体素子と、前記半導体素子と接続され半導体素子に信号を供給する配線と、信号用電極群、電源用電極群、グランド用電極群を有する半導体チップであって、

前記チップの裏面には、前記信号用電極群、前記電源用電極群とは絶縁された導体層が前記裏面を覆って形成されていることを特徴とする半導体チップ。

【請求項2】

前記チップには貫通配線が形成され、前記貫通配線は前記チップの表面に形成されたグランド電極と前記裏面に形成された前記導体層とを電気的に接続していることを特徴とする請求項1に記載の半導体チップ。

【請求項3】

前記チップの表面には、前記信号用電極群および前記電源用電極群と絶縁して、前記半導体素子の表面を含む前記チップの表面を覆う導体層が形成されていることを特徴とする請求項1または請求項2に記載の半導体チップ。

【請求項4】

チップの表面に半導体素子と、前記半導体素子と接続され半導体素子に信号を供給する配線と、信号用電極群、電源用電極群、グランド用電極群を有する半導体チップであって、

前記チップの裏面には、前記信号用電極群、前記電源用電極群とは絶縁された導体層が前記裏面を覆って形成されており、

前記チップを貫通する貫通配線が前記チップ表面のグランド用電極群と、前記チップの裏面に形成された前記導体層を接続していることを特徴とする半導体チップ。

【請求項5】

チップの表面に半導体素子と、前記半導体素子と接続され半導体素子に信号を供給する配線と、信号用電極群、電源用電極群、グランド用電極群を有し、チップの裏面に信号用電極群、電源用電極群、グランド用電極群を有し、チップを貫通する貫通配線が前記チップの表面と前記チップの裏面に形成された、前記信号用電極群どうし、前記電源用電極群どうし、前記グランド用電極群どうしを接続している半導体チップであって、

前記チップの裏面には、前記信号用電極群、電源用電極群とは絶縁し、前記裏面を覆う導体層が形成され、前記グランド用電極群と前記導体層は電気的に接続していることを特徴とする半導体チップ。

【請求項6】

前記チップの表面には、前記信号用電極群、前記電源用電極群と絶縁して、前記半導体素子の表面を含む前記チップの表面を覆う導体層が形成されていることを特徴とする請求項5に記載の半導体チップ。

【請求項7】

前記裏面または前記表面に形成された前記導体層は、スパッタリングによって形成された金属膜であることを特徴とする請求項1乃至請求項6のいずれか1項に記載の半導体チップ。

【請求項8】

前記裏面または前記表面に形成された前記導体層の表面には、金属メッキが形成されていることを特徴とする請求項1乃至請求項6のいずれか1項に記載の半導体チップ。

【請求項9】

前記裏面または前記表面に形成された前記導体層の表面には、金属微粒子が分散された導電性樹脂膜が形成されていることを特徴とする請求項1乃至請求項6のいずれか1項に記載の半導体チップ。

【請求項10】

複数の半導体チップとインターポーザを積層して形成された半導体パッケージであって、

前記インターポーザは、前記半導体チップと接続するための電極を表面に備え、内層にグランド層を持ち、裏面にマザーボードと接続するための電極を備え、

前記半導体チップは請求項1乃至請求項9のいずれか1項に記載の半導体チップであることを特徴とする半導体パッケージ。

【請求項11】

複数の半導体チップとインターポーザを積層して形成された半導体パッケージを有し、グランド配線をマザー基板であって、

前記インターポーザは、前記半導体チップと接続するための電極を表面に備え、内層にグランド層を持ち、裏面にマザーボードと接続するための電極を備え、

前記半導体チップは請求項1乃至請求項9のいずれか1項に記載の半導体チップであり、

前記半導体チップの前記グランド配線と前記導体層と前記インターポーザのグランド層と前記マザー基板のグランド配線とは接続していることを特徴とするマザー基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2011−54820(P2011−54820A)

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願番号】特願2009−203425(P2009−203425)

【出願日】平成21年9月3日(2009.9.3)

【出願人】(000005108)株式会社日立製作所 (27,607)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願日】平成21年9月3日(2009.9.3)

【出願人】(000005108)株式会社日立製作所 (27,607)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]