半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

電子産業の集積回路分野の製造技術において、さらなる高集積化かつ高速化の要求が高まっている。また集積化の進展により、回路の規模が大きくなり、設計の難易度が増大している。

【0003】

同一半導体基板上に論理回路とメモリ回路を搭載する集積回路、いわゆる混載回路では、同一の基板上に論理回路とメモリ回路が存在することで、単に近距離にレイアウトが可能となることで集積化が向上するだけでなく、回路間の配線が短くなることで動作速度の向上も可能となるなどの特徴を持つ。

【0004】

しかしながら、同一の半導体基板上に容量素子を備えたメモリ回路と論理回路を搭載する際には、メモリ回路が有するデータの記憶に用いられる容量素子の形成のために、通常論理回路を形成する場合には用いられない構造を用いる必要がある。例えば、トレンチ型容量素子の場合では、半導体基板に数ミクロン以上の深い溝を形成し、そこに容量素子を形成する手法が報告されているが、素子の微細化に伴ってトレンチ開口径が小さくなるだけでなく、容量の確保のためにその深さは増す一方であり、その製造工程は非常に難易度が上昇している。

【0005】

一方、スタック型容量素子の場合でも、所望の容量を実現するためにスタック構造をフィン型や円筒(シリンダ)型を採用するなどしている。容量素子をビット線上に形成する、いわゆるCOB構造(Capacitor Over Bit line構造)では容量素子の容量を稼ぐために容量の高さを高くする必要がある。

【0006】

現在、容量素子の下部容量配線と上部容量配線との間に設けられている配線層が1層である半導体装置として各種の提案がある(例えば、特許文献3、特許文献4参照)。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007―201101号公報

【特許文献2】特開2004−342787号公報

【特許文献3】特開2000−003960号公報

【特許文献4】特開2005−101647号公報

【非特許文献】

【0008】

【非特許文献1】M.Ueki et .al、IEEE IEDM、 pp973−976(2007)

【発明の概要】

【発明が解決しようとする課題】

【0009】

スタック型構造で容量素子の高さを稼ぐことは、容量下部の配線と容量上部の配線の距離が遠くなることになる。これによって論理回路部では第1の配線層から拡散層に至るまでのコンタクトも高くなり、製造工程においてはその難易度が高くなるとともに、容量素子が形成されている層の電気抵抗、すなわち寄生抵抗も増大することから性能面でも動作速度の低下を招くことになる。

【0010】

さらに、上述の通り、メモリ回路と論理回路を同一の半導体基板上に形成する場合において論理回路を設計する際には、容量素子の形成を考慮して、寄生抵抗などを考慮した設計を行う必要がある。これは同じ論理回路を設計する場合でも、容量素子が同一の半導体基板上に存在するか否かによって、特に配線抵抗やその寄生容量の違いにより設計パラメーターを変更する必要があるということである。全く同じ回路であるにも関わらず、容量素子と同時形成するばかりに設計をやり直さなければならないだけでなく、場合によっては容量素子と混載したことによって回路の動作速度が低下したり、動作マージンが低下して動作しなくなったりする可能性がある。

【0011】

論理回路部のコンタクト高さを低減する提案の例としては、まず、特許文献1を挙げることができる。特許文献1では、容量素子の上部電極を、論理回路部に存在する配線と同一の高さに形成された上部容量配線で接続することによって、上部電極間を接続するためのプレート線とよばれる配線を形成するための専用の工程や専用の設備を必要とせず、同時に容量素子の上下膜厚の確保と論理回路部のコンタクト(ロジックコンタクト)のアスペクトが低減可能であることが示されている。

【0012】

特許文献1の提案ではコンタクト高さの低減は可能であるが、論理回路部のコンタクト高さの低減は配線高さ1層分と限定的である。この構造において容量素子の容量を向上させるためには、容量素子高さを高くすることが必要となるが、この場合、容量高さの増加に伴ってロジックコンタクト高さも増大する。したがって、コンタクト製造の難易度が上昇する上に、ロジックコンタクトの抵抗は増大する。また、論理回路部の多層配線材は銅を主成分とした銅配線であることが望ましいのに対して、銅配線材以外の配線、すなわち高抵抗のタングステン(W)配線が使用される。さらに、また、容量素子の存在によって容量素子の存在するその配線層の構造は通常の論理回路の配線構造とは異なっており、容量素子の存在する層ではロジックコンタクト高さが高く、抵抗も高くなっている。その結果、すべての配線層が低抵抗銅材で形成される通常の論理回路設計用パラメーターとは互換性のない、専用の設計パラメーターが必要となってしまう。

【0013】

特許文献2の提案では、コンタクト高さを低減するために第1層配線を容量素子の中間部に形成している。これにより特許文献1同様に論理回路部のコンタクト高さを低減可能である。しかし特許文献2の手法を用いたとしても論理回路部の構造は容量素子の構造に依存し、容量素子を備えない構造とは異なる構造になる。

【0014】

したがって、特許文献2の構造を用いても、論理回路の設計パラメーターについてはメモリ回路と混載時には専用の値を用いる必要がある。また、特許文献2の手法でも特許文献1と同様に、容量素子の容量を稼ぐためには層間絶縁膜を厚くして背丈の高い容量を形成する必要がある。また、メモリ回路側の配線をすべて銅配線としていないことから、論理回路側の多層配線をすべて銅配線とすることができていない。やはり特許文献1同様にコンタクト形成時の難易度の上昇や、コンタクト抵抗の増大が生じることになる。さらに、最先端の論理回路の多層配線では少なくとも下層に位置する狭ピッチのローカル配線にはSiOCH膜などの低誘電率層間絶縁膜が導入されている。低誘電率層間絶縁膜(Low−k膜)は耐熱性に限界があり、例えば成長温度の高いCVD−Wなどを用いたW配線などを適用することはできない。このため、論理回路側多層配線の全層をLow−k/Cu配線化することができない。その結果、すべての配線層がLow−k/Cu構造で構成される通常の論理回路設計用パラメーターとは互換性のない、専用の設計パラメーターが必要となってしまう。

【0015】

また、特許文献2で示されている実施の形態1あるいは実施の形態3においては、上部電極や上層配線の銅膜の直上にシリコン酸化膜からなる絶縁膜を形成した構造となっている。シリコン酸化膜は銅膜に対する拡散耐性が無いために、特許文献2の構造では銅(Cu)が絶縁膜中に拡散し、絶縁膜の信頼性が劣化する。

【0016】

また、シリコン酸化膜の成膜においては主に原料ガスの酸化によって成膜が行われることから、配線表面のCuが露出している状態で、シリコン酸化膜の成膜を行うと、Cuが酸化して配線抵抗の増大や、成膜されるシリコン酸化膜のとの密着性の低下や、それに伴う信頼性の劣化などが懸念される。以上のように、特許文献2ではエッチングストッパ膜を設ける必要がない利点が謳われているが、特許文献2の構造ではむしろ信頼性が劣化する欠点を抱えていると考えられる。

【0017】

以上の内容を図に示すと図33((a)、(b))のようになる。特許文献2に代表されるように、従来の技術ではメモリ回路部101は容量素子90の上に多層配線部103を付与したような構造(アドオン型)を有していた。そのため、論理回路部102では、容量を確保するために容量素子90の高さに応じて多層配線部103をリフトアップする配線部(リフトアップ配線部104)が必要となり、多層配線構造が厚くなることが問題であった。

【課題を解決するための手段】

【0018】

本発明によれば、半導体基板と、

前記半導体基板上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線構造と、

前記多層配線構造内に埋め込まれた、下部電極、容量絶縁膜、および上部電極により構成された容量素子と、を備え、

前記下部電極に接続した下部容量配線と、前記上部電極に接続した上部容量配線との間に、少なくとも2層以上の前記配線層が設けられたことを特徴とする半導体装置が提供される。

【発明の効果】

【0019】

容量素子が多層配線構造内に埋め込まれるとともに、この容量素子の下部容量配線と上部容量配線との間に少なくとも2層以上の配線層が設けられた構造により、容量素子の容量を確保しつつも、多層配線構造が厚くなることを抑えることができる。

【図面の簡単な説明】

【0020】

【図1】この発明の第一の実施形態の半導体装置を示す断面図である。

【図2】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図3】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図4】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図5】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図6】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図7】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図8】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図9】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図10】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図11】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図12】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図13】この発明の第一の実施形態の一例における半導体装置を示す断面図である。

【図14】この発明の第一の実施形態の一例における半導体装置を示す断面図である。

【図15】この発明の第二の実施形態の一例における半導体装置を示す断面図である。

【図16】この発明の第三の実施形態の一例における半導体装置を示す断面図である。

【図17】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図18】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図19】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図20】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図21】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図22】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図23】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図24】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図25】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図26】この発明の第三の実施形態の一例における半導体装置を示す断面図である。

【図27】この発明の第四の実施形態の一例における半導体装置を示す断面図である。

【図28】この発明の第五の実施形態の一例における半導体装置を示す断面図である。

【図29】この発明の第六の実施形態の一例における半導体装置を示す断面図である。

【図30】この発明の第七の実施形態の一例における半導体装置を示す断面図である。

【図31】この発明の第七の実施形態の一例における半導体装置を示す断面図である。

【図32】この発明の第七の実施形態の一例における半導体装置を示す断面図である。

【図33】従来技術とこの発明の一例における半導体装置を比較する断面図である。

【図34】この発明の第八の実施形態の一例における半導体装置を示す断面図である。

【図35】この発明の第八の実施形態の一例における半導体装置を示す断面図である。

【図36】この発明の第九の実施形態の一例における半導体装置を示す断面図である。

【図37】図2に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図38】図3に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図39】図5に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図40】図6に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図41】図9に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図42】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図43】図42に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図44】この発明の第十の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【図45】この発明の第十の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【図46】この発明の第十の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【図47】この発明の第十の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【図48】この発明の第十一の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【発明を実施するための形態】

【0021】

本発明の実施の一形態を詳細に説明する前に、本実施形態における用語の意味を説明する。

絶縁膜とは、例えば配線材を絶縁分離する膜(層間絶縁膜)であり、低誘電率絶縁膜とは、半導体素子を接続する多層配線間の容量を低減するため、シリコン酸化膜(比誘電率4.5)よりも比誘電率の低い材料を指す。特に、多孔質絶縁膜としては、例えば、シリコン酸化膜を多孔化して、比誘電率を小さくしたポーラスシリカ材料や、HSQ(ハイドロゲンシルセスキオキサン(Hydrogen Silsesquioxane))膜、もしくはSiOCH、SiOC(例えば、Black DiamondTM、AuroraTM)などを多孔化して、比誘電率を小さくした材料などがある。この絶縁膜として、これらの膜をさらに低誘電率化した膜を用いても良い。

【0022】

本実施の形態において、金属配線材およびコンタクトプラグ材とは、主にCuを主成分とする。金属配線材の信頼性を向上させるため、Cu以外の金属元素がCuからなる部材に含まれていても良く、Cu以外の金属元素がCuの上面や側面などに形成されていても良い。また一部の実施の形態においては、第1層目配線とシリコン基板上に形成されたMOSFETとを接続するコンタクトプラグ材は主にタングステン(W)を主成分としている。この場合、第1層目の配線とシリコン基板上に形成されたMOSFETとを絶縁分離するプレメタル絶縁膜(PMD)は耐熱性に優れるシリコン酸化膜となる。

【0023】

バリアメタル膜とは、配線あるいはコンタクトプラグを構成する金属元素が層間絶縁膜や下層へ拡散することを防止するために、配線の側面および底面を被覆する、銅の拡散に対してバリアとなる性質を有する導電性膜を示す。例えば、配線がCuを主成分とする金属元素からなる場合には、タンタル(Ta)、窒化タンタル(TaN)、チタン(Ti)、窒化チタン(TiN)、炭窒化タングステン(WCN)、ルテニウム(Ru)のような高融点金属やその窒化物等、またはそれらの積層膜が使用される。またタングステンを主成分に用いるコンタクトプラグのバリアメタルにも前記の金属膜が用いられる。

【0024】

ダマシン配線とは、あらかじめ形成された層間絶縁膜の溝に、金属配線材を埋め込み、溝内以外の余剰な金属を、例えばCMPなどにより除去することで形成される埋め込み配線をさす。Cuによりダマシン配線を形成する場合には、Cu配線の側面および外周をバリアメタルで覆い、Cu配線の上面を、銅拡散耐性(Cuバリア性)を持つ絶縁性バリア膜(キャップ膜とも呼ぶ)で覆う配線構造が一般に用いられる。

【0025】

CMP(Chemical Mechanical Polishing)法とは、多層配線形成プロセス中に生じるウェハ表面の凹凸を、研磨液をウェハ表面に流しながら回転させた研磨パッドに接触させて研磨することによって平坦化する方法である。ダマシン法による配線形成においては、特に、配線溝あるいはビアホールに対し金属を埋設した後に、余剰の金属部分を除去し、平坦な配線表面を得るために用いる。

【0026】

半導体基板とは、半導体装置が構成された基板であり、特に単結晶シリコン基板上に作られたものだけでなく、SOI(Silicon on Insulator)基板やTFT(Thin film transistor)、液晶製造用基板などの基板も含む。

【0027】

ハードマスクとは、層間絶縁膜の低誘電率化による機械的強度低下やプロセス耐性の低下により、直接プラズマエッチングやCMPを行うことが困難な場合に、層間絶縁膜上に積層し、保護する役割を果たす絶縁膜をさす。

【0028】

プラズマCVD法とは、例えば、気体状の原料を減圧下の反応室に連続的に供給し、プラズマエネルギーによって、分子を励起状態にし、気相反応、あるいは基板表面反応などによって基板上に連続膜を形成する手法である。

【0029】

PVD法とは、通常のスパッタリング法のほか、埋め込み特性の向上や、膜質の向上や、膜厚のウェハ面内均一性を図った、例えばロングスロースパッタリング法やコリメートスパッタリング法、イオナイズドスパッタリング法、などの指向性の高いスパッタリング法を含む手法である。合金をスパッタする場合には、あらかじめ金属ターゲット内に主成分以外の金属を固溶限以下で含有させることで、成膜された金属膜を合金膜とすることができる。本発明中では、主にダマシンCu配線を形成する際のCuシード層や、バリアメタル層を形成する際に使用することができる。

【0030】

(第一の実施形態)

本発明の実施の一形態について図面を参照して以下に説明する。ただし、本実施の形態に関して前述した一従来例と同一の部分は、同一の名称を使用して詳細な説明は省略する。

本実施形態の半導体装置は、半導体基板(シリコン基板5)と、シリコン基板5に形成され、配線(第3層配線35、第4層配線45、第5層配線55、第6層配線65)および絶縁膜(第3層の層間絶縁膜31、第4層の層間絶縁膜41、第5層の層間絶縁膜51、第6層の層間絶縁膜61)により構成された配線層(第3層配線35と第3層の層間絶縁膜31、第4層配線45と第4層の層間絶縁膜41、第5層配線55と第5層の層間絶縁膜51、第6層配線65と第6層の層間絶縁膜61)が複数積層された多層配線構造と、この多層配線構造内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜(容量絶縁膜92)、および上部電極(上部電極膜93)により構成された容量素子90と、を備えるものである。さらに、本実施形態の半導体装置は、下部電極膜91に接続した下部容量配線(第2層配線25)と、上部電極膜93に接続した上部容量配線(プレート線配線として第5層配線55)との間に、少なくとも2層以上の前記配線層(第3層配線35と第3層の層間絶縁膜31、第4層配線45と第4層の層間絶縁膜41、第5層配線55と第5層の層間絶縁膜51)が設けられたことを特徴とするものである。

【0031】

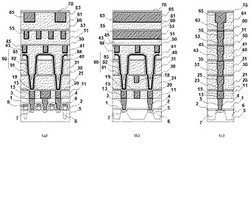

図1は、本発明のひとつの実施の形態の半導体装置を示す断面図であり、図2〜図12、図42は、図1の半導体装置の製造方法を工程順に示す断面図の例である。図1の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面である。また右側(c)は論理回路領域の代表的な断面図を示す。図2〜12、図42のいずれも図の左側(a)はメモリ回路領域、右側(b)は論理回路領域の代表的な断面図を示す。また図37〜図41、図43は、それぞれ図2、図3、図5、図6、図9および図42中(a)の上面図(平面レイアウト図)である。また図13および図14についても左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

【0032】

多層配線構造は、例えば第3層配線35および第3層の層間絶縁膜31により構成された配線層、第4層配線45および第4層の層間絶縁膜41により構成された配線層、第5層配線55および第5層の層間絶縁膜51により構成された配線層、第6層配線65および第6層の層間絶縁膜61により構成された配線層が積層された構造を有する。多層配線構造は、さらに異なる配線層が積層されてもよい。本実施形態では、この多層配線構造は、一般的な論理回路領域の多層配線構造を表すものである。この論理回路領域の多層配線構造では、上層に位置する多層配線層を構成する各配線層や配線の厚さは、下層に位置する多層配線層よりも厚いことが一般的であるが、本実施形態では、多層配線層を構成する各配線層や配線の厚さは特に限定されない。従来のように、一部または全部の配線層の各配線層や配線の厚さが同じでもよく、下層から上層に向かって配線層の各配線層や配線の厚さが厚くなってもよい。

または、少なくとも容量素子が設けられた領域の、配線層の高さ(厚み)が全て同じであり配線の高さ(厚み)が全て同じであってもよい。つまり、容量素子90が埋め込まれた領域においては、例えば第3層配線35、第4層配線45および第5層配線55の配線の厚みが同じであり、これらの配線が設けられた第3の配線層、第4の配線層、および第5の配線層の厚みが同じであればよい。さらに、容量素子90が埋め込まれていない領域の配線層や配線の厚さは、容量素子90が埋め込まれた領域の配線層や配線の厚さが同じでもよく、または異なっていてもよい。本実施形態では、図1に示すように、第2層配線25、第3層配線35、・・・第6層配線65の配線の厚さが同じかつ、これらが設けられた配線層の厚さも同じである。本実施形態では、配線および配線層の厚さ(厚み)は、シリコン基板5の法線方向の厚さを表すものとする。

【0033】

この多層配線構造おいて、メモリ回路領域と論理回路領域との配線層は同層に設けられているものである。つまり、メモリ回路領域の第3層配線層、・・・第5層配線層と論理回路領域の第3層配線層、・・・第5層配線層とは同層になる。本実施形態では、このメモリ回路領域の多層配線構造内に容量素子90が埋め込まれているものである。さらに、容量素子90は少なくとも2層以上の配線層にわたって設けられているため、この多層配線構造の配線層数を変えずに、容量素子90が貫く配線層数を変化させて所望の容量を得ることができる。また、上述のとおり、容量素子90が埋め込まれたメモリ回路領域の多層配線と論理回路領域の多層配線は同層に形成される。このため、新たに論理回路領域の多層配線を設ける必要がない。これにより、多層配線構造をコンパクトに設けることができる。

【0034】

図1に示すとおり、多層配線構造内に容量素子90が埋め込まれたことにより、下部電極膜91が、上から第5層の層間絶縁膜51、第4層の層間絶縁膜41、第3層の層間絶縁膜31を貫通するように設けられており、この多層配線構造内に凹部が形成されている。この凹部の底面および側面上に接するように容量絶縁膜92が形成されている。さらに、この容量絶縁膜92上に接するように上部電極膜93が形成されている。下部電極膜91、容量絶縁膜92および上部電極膜93をこのように設けることで、これらにより構成した容量素子90を多層配線構造内に設けることができる。また、容量素子90が多層配線構造内に埋め込まれたため、図1に示すとおり、容量素子90の上部電極膜93が設けられた第5層の層間絶縁膜51には、この上部電極膜93上に、上部電極膜93に接続した上部容量配線として第5層配線55が設けられている。

容量素子90が多層配線構造内に埋め込まれる位置には、下部容量配線(第2層配線25)と、上部容量配線(プレート線配線として第5層配線55)との間に、少なくとも2層以上の配線層が設けられている限り、特に限定されない。容量素子90は、最も微細化が進んでいる下層に位置する多層配線層に形成してもよい。

【0035】

さらに、図1に示す通り、容量素子90が設けられたメモリ回路領域の容量素子90が多層配線構造内に埋め込まれており、この多層配線構造において、本実施の形態では、列デコード配線18が下部容量配線の上層に形成されている。行デコード配線17もしくは列デコード配線18のいずれかもしくは両方が、容量素子90と同層に設けられているか、もしくは、下部容量配線と同層に設けることにより、上層配線を利用する必要がなくなり、メモリ回路領域の配線層数を減ずることができる。これによってメモリ回路領域の上層は論理回路領域の配線のために用いたり、各回路領域間を接続するために用いたりすることが可能となり、チップ面積を縮小することが可能になる。

なお、この多層配線構造において、例えば第3配線層と第4配線層などの異なる配線層の厚みを同一にしてもよい。また、容量素子90が設けられたメモリ回路領域の配線層の厚みと、容量素子90が設けられていない論理回路領域と配線層の厚みとを同一にすることができる。また、多層配線構造の配線層の厚みを変えずに、容量素子90を多層配線構造内に埋め込むことができる。これにより、多層配線構造の配線層を厚くせずに、容量素子90が貫く配線層により、容量素子90の所望の容量を得ることができる。

【0036】

つぎに本実施形態の半導体装置の製造方法について説明する。

図2では、標準的な集積回路の形成方法を用いて作成した、MOSトランジスタ9および第2層配線25形成後の構造を有する基板を示す。

本実施形態の半導体装置は、さらに、シリコン基板5の表面近傍に形成された第一の拡散層(拡散層7)と、シリコン基板5の表面近傍に形成された第二の拡散層(拡散層7)と、第一の拡散層(拡散層7)と第二の拡散層(拡散層7)との間のシリコン基板5に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極8と、を備える。そして、本実施形態の半導体装置は、これらのシリコン基板5、第一の拡散層(拡散層7)、第二の拡散層(拡散層7)、ゲート絶縁膜、およびゲート電極8により電界効果トランジスタ(MOSトランジスタ9)を構成するものである。

シリコン基板5上に形成されるMOSトランジスタ9のゲート絶縁膜は、高誘電率ゲート絶縁膜であればよい。例えば高誘電率ゲート絶縁膜として、SiONなどシリコン酸窒化物あるいはHf酸窒化物などのHfを含む高誘電率ゲート絶縁膜などを用いることができる。具体的には、Hf酸化物、Hfシリケート、およびHf酸化物またはHfシリケートに窒素が導入された高誘電率絶縁膜を用いることができる。ゲート絶縁膜は、単層またはこの種類で構成された多層でもよい。

またゲート電極材としてはポリシリコンあるいはその上面層がNi、Co、Ti、Ptなど金属シリサイドで覆われされたものである。さらには、ゲート電極の一部にTi、Ta、Alあるいはそれらの導電性窒化物を含むメタルゲート電極であってもよい。特に、メタルゲート電極の場合、ロジック部のトランジスタの駆動電流を向上させるといった効果のみならず、メタルゲート電極はDRAM部のワード線を構成しているので、このワード線の抵抗を低減する効果もあり、多層配線層に容量素子部を埋め込んだeDRAM構造と組み合わせることで、より高速動作が可能となる。

【0037】

MOSトランジスタ9は、N型またはP型いずれでもよい。また、N型トランジスタとP型トランジスタとは同一のシリコン基板5上に形成されてもよい。図2に示す拡散層7は、第一の拡散層および第二の拡散層を表し、第一の拡散層および第二の拡散層の一方はソース拡散層であり、他方はドレイン拡散層である。

なお図2において、1はコンタクト層間絶縁膜、2はエッチストップ膜、3はコンタクトバリアメタル膜、4はコンタクトプラグ、5はシリコン(Si)基板,6は素子分離STI(shallow trench isolation)、7は拡散層、8はゲート電極である。また、11は第1層の層間絶縁膜であり、13は第1層配線バリアメタル膜、15は第1層配線、20は第1層配線のキャップ膜、23は第2層配線バリアメタル膜、25は第2層配線、30は第2層配線のキャップ膜、である。また、ビット線19は第1層配線15と同時に形成されるが、メモリ回路部におけるビット線である。

【0038】

さらに、ここでビット線19は第1層配線15と同一層に形成されており、特許文献2などに見られるような、ビット線だけの配線層は存在しない。本実施形態に示す構造により、多層配線構造は層数を有効に活用可能である。

【0039】

図2ではコンタクト層間絶縁膜1はシリコン酸化膜からなり、コンタクトプラグ4はタングステンからなり、コンタクトバリアメタル膜3は窒化チタン/チタンの積層膜からなる。また、第1層の層間絶縁膜11および第2層の層間絶縁膜21は低誘電率絶縁膜でありSiOCH膜、より具体的にはMPS(Molecular Pore Stack)膜からなる。MPS膜の詳細については非特許文献1に記載されている。第1層配線バリアメタル膜13はタンタル/窒化タンタル積層膜からなり、第1層配線は銅からなる。また、第1層配線のキャップ膜20および第2層配線のキャップ膜30はSCC(Silica amorphous Carbon Composite)膜からなる。このSCC膜についても、MPS膜と同様に非特許文献1に詳細が記載されている。

【0040】

MPS膜とSCC膜について以下に簡単に記載する。MPS膜は、6員環の環状シロキサンを主骨格とし、有機基を官能基に持った有機シロキサンを原料として成膜する。シリコン原子に結合する有機官能基は不飽和炭化水素基とアルキル基である。SCC膜は、不飽和炭化水素基、アルコキシ基、アルキル基がそれぞれ、シリコン原子に直接結合した有機シラン原料を用いて成膜される。膜の構造としてはアモルファスカーボン構造と不飽和炭化水素結合が膜中に含まれることが特徴である。MPS膜とSCC膜のいずれの原料においても前記不飽和炭化水素基としては、ビニル基、プロペニル基、イソプロペニル基、1−メチル−プロペニル基、2−メチル−プロペニル基、1,2−ジメチル−プロペニル基などが挙げられる。特に好ましい不飽和炭化水素基は、ビニル基である。またMPS膜とSCC膜のいずれの原料においても前記アルコキシ基はアルキル基が酸素原子に結合した構造である。前記シリコン原子に直接結合するアルキル基、および前記アルコキシ基を構成するアルキル基としては、メチル基、エチル基、プロピル基、イソプロピル基、ブチル基、イソブチル基、sec−ブチル基、tert−ブチル基などが挙げられる。またMPS膜原料のシリコンに結合するアルキル基としては、イソプロピル基、イソブチル基、tert−ブチル基など、空間的に嵩高く、立体障害基として機能する官能基が好ましい。特に、より好ましい官能基の一つはイソプロピル基である。すなわち、トリイソプロピルトリビニルトリシクロシロキサンである。さらにSCC膜原料のシリコンに結合するアルコキシ基、アルキル基として、より好ましいのはメトキシ基とイソプロピル基である。すなわちイソプロピルジメトキシビニルシロキサンとなる。これらの原料を用いることでMPS膜では膜中に非常に微細な(主に0.5nm以下の)空孔構造が導入されることが特徴となる。またSCC膜は、SiOCH膜の一種でありながら、銅拡散耐性を持つことが特徴である。さらに比誘電率が3.1程度でありながら、機械強度が20GPa程度と高いことも特徴である。また、表面反応が強い成膜モードで成膜されるために、段差被覆性も良好である。これらの膜は一般的に知られているSiOCH膜に比べて炭素組成が高いことが特徴である。シリコン/酸素/炭素の元素比は、Siを基準とすると、SiOCH膜に対し、SCC膜で炭素が約2倍程度、MPS膜では4倍程度の炭素が含まれている。相対的に酸素の元素比が一般的なSiOCH膜に比較して少なく、SCC膜で3/4程度、MPS膜では1/2程度である。これはこれらの膜が、原料をプラズマ中で解離・活性化させるプラズマCVDではなく、プラズマ重合反応により成膜することでシリカ骨格を保持したまま不飽和炭化水素を優先的に活性化させ、絶縁膜の化学構造を制御することが容易となることから実現される。このMPSとSCC膜の組成の差が、容量開口部の加工形成においては重要なポイントとなる。

【0041】

第2層配線25を形成する手法について簡単に記載する。第1層配線15を形成し、SCC膜からなる第1層配線のキャップ膜20を成膜した後に、第2層の層間絶縁膜21として前記MPS膜を成膜する。引き続き加工時のマスクとしてシリコン酸化膜(図示せず)を成膜する。さらにリソグラフィとドライエッチングを用いたいわゆるデュアルダマシンプロセスによって第2層配線の開口部を形成する。このとき開口部の一部は第1層配線15に電気的に接続するためのビアホールを含んでいる。これらの開口部にスパッタリング法によって第2層配線バリアメタル膜23を堆積し、引き続いて銅めっきのシード層となる銅を堆積する。さらにめっき法によって銅を埋め込む。ここで用いる銅にはアルミニウムや銀などの金属の添加物を含んでいてもよい。この第2層配線の開口部にバリアメタル膜23と銅が残るように余分なバリアメタル膜と銅をCMPなどの手法を用いて除去し、第2層配線25を形成する。この工程中に前記シリコン酸化膜は除去され、第2層の層間絶縁膜21上には残らない。その後、第1層と同様にSCC膜からなる第2層配線のキャップ膜30を成膜する。ここで、容量素子の開口部以外の容量絶縁膜の下部に部分的にシリコン酸化膜が設けられていてもよい。以後の工程で、この第2層配線の開口部と同等にして、第3層配線の開口部、・・・第6層配線の開口部を形成することができる。図1に示す第3層配線バリアメタル膜33、第4層配線バリアメタル膜43、第5層配線バリアメタル膜53および第6層配線バリアメタル膜63は、第1層配線バリアメタル膜13または第2層配線バリアメタル膜23と同様にして形成できる。図1に示す第5層配線のキャップ膜60および第6層配線のキャップ膜70は、第2層配線のキャップ膜30と同様にして形成できる。

【0042】

本実施の形態では層間絶縁膜およびキャップ膜は単層の絶縁膜を用いているが、それぞれ、複数種の絶縁膜の積層構造でもよい。たとえば、層間絶縁膜はMPS膜と他のSiOCH膜、キャップ膜はSiC膜とSiCN膜の積層構造などでもよい。なお、図37は、第2層配線のキャップ膜30を成膜する前の平面レイアウトを示す。図37に示すように、デコード線18、第2層の層間絶縁膜21、第2層配線25が同層に設けられている。

【0043】

さらに図3には、第3層配線35および第4層配線45を形成する。形成方法は第2層配線25と同様である。ここでは後にメモリ回路領域には容量素子を形成するため、論理回路領域のみに配線層を形成する。本実施の形態では容量素子の高さを論理回路部の3層分よりは低い場合を示しているが、4層分より低い場合とする場合にはさらに論理回路部を1層多く形成する。なお、図38は、第4層配線のキャップ膜50を成膜する前の平面レイアウトを示す。図38に示すように、第4層の層間絶縁膜41、第4層配線45が同層に設けられている。

【0044】

次に図4のように第4層配線のキャップ膜50を堆積した後に、ハードマスク絶縁膜94を成膜する。さらにシリンダ加工レジスト膜95をリソグラフィによって形成する。

【0045】

ここでハードマスク絶縁膜94はシリコン酸化膜を用いたが、他の絶縁膜との積層構造でもよい。またレジスト膜との間に反射防止膜を備えるなどの多層構造としてもよい。いずれの場合も容量素子形成過程で第4層配線のキャップ膜50を保護する効果をもつ絶縁膜であることが好ましい。具体的には、シリコン酸化膜のほか、シリコン窒化膜、シリコン酸窒化膜などが挙げられる。

【0046】

引き続いて図5に示すようにドライエッチングによって容量素子開口部98を形成する。このとき、第2層配線の酸化を防止するため、第2層配線のキャップ膜30はエッチングしない。なお、図39は図5(a)における平面レイアウト図を示す。図39では、全面がシリンダ加工レジスト膜95となっており、容量素子となる容量素子開口部98の中に、第2層配線のキャップ膜30が設けられている。本実施の形態のように、シリンダ形状の容量素子90を矩形に形成することによって、光近接効果補正を含めた露光や、ドライエッチング加工などの形成プロセスが容易となる。特に32nmや28nm技術世代以降において、光近接効果補正は複雑になっており、各要素パターンを単純な矩形あるいは直線形状で形成することは、面積あたりのビット密度を向上させるため、あるいは設計通りの形状を得るためには非常に効果的である。

【0047】

容量素子開口部98の形成時には、ドライエッチングによって層間絶縁膜とキャップ膜を交互にエッチングを行うが、本実施の形態では、層間絶縁膜にMPS膜をキャップ膜にSCCを用いており、SiOCH膜が積層された構造となっている。先に述べた通り、この2つの膜は炭素の組成が大きく異なっており、ドライエッチングによる加工条件を工夫することにより、MPS/SCC膜のエッチングレートの比、いわゆるエッチング選択比を制御することが容易である。したがって、層間絶縁膜であるMPSをエッチングしながら、キャップ膜であるSCC膜のエッチング選択比を小さくして、容量素子開口部98を深く開口したり、反対にMPS/SCCの選択比を大きくして、シリンダ開口部底でエッチングを止めたりすることが出来る。層間絶縁膜はエッチングするが、キャップ膜のエッチング速度を相対的に著しく小さくしたりすることが可能である。つまりは炭素の存在によってエッチング速度が変化する条件と変化しない条件を選ぶことができる。こうした加工の自由度が高い構造を用いることにより、良好な容量素子開口部98の形状を得ることができる。ここで、キャップ絶縁膜と低誘電率SiOCH膜とのそれぞれの炭素/シリコン比を、キャップ絶縁膜(C/Si)、低誘電率SiOCH膜(C/Si)としたとき、例えばキャップ絶縁膜(C/Si)/低誘電率SiOCH膜(C/Si)<2とする。

【0048】

さらにシリンダ加工レジスト膜をアッシングにより除去し、容量素子の下部電極を下層の配線となる第2層配線25に接続するため、第2層配線のキャップ膜30をドライエッチングによってエッチバックする(図6)。なお、図40は図6(a)における平面レイアウト図であり、全面がハードマスク絶縁膜94となっており、容量素子となる容量素子開口部98の中に、第2層の層間絶縁膜21、第2層配線25が設けられている。

【0049】

引き続いて容量素子の下部電極となる下部電極膜91を成膜し、さらにリソグラフィによって下部電極加工レジスト膜(図示せず)を形成する。この下部電極加工レジスト膜をマスクにして下部電極膜91をエッチバック、さらにアッシングによって下部電極加工レジスト膜を除去した(図7)。さらに、下部容量配線と下部容量配線が設けられた配線層の配線との上面が同一の平面となるようにこの下部容量配線を設けても良い。

【0050】

さらに引き続いて、容量絶縁膜92と上部電極膜93を成膜し、この加工のマスクとなる上部電極加工レジスト膜97をリソグラフィによって形成する。上部電極加工レジスト膜97をマスクにドライエッチングによって容量絶縁膜92と上部電極膜93をエッチングする。このとき、均一性確保のためオーバーエッチングを行うが、これによって、ハードマスク絶縁膜94の一部がエッチングされる(図8)。さらに、上部容量配線と上部容量配線が設けられた配線層の配線との上面が同一の平面となるようにこの上部容量配線を設けても良い。

ここで容量素子90に用いる材料としては、上部電極膜93及び下部電極膜91には、Ti、TiN、Ta、TaN、Ruまたはこれらの積層構造等が挙げられる。また、容量絶縁膜92としては二酸化ジルコニウム(ZrO2)やジルコニウムアルミネート(ZrAlOx)、二酸化ジルコニウムにTb、Er、Ybなどのランタノイドを添加した膜などが挙げられる。

【0051】

このハードマスク絶縁膜94は上述のアッシングおよびエッチングの工程において、特に論理回路部のハードマスク膜の下層に存在するキャップ膜、ひいてはさらにその下層にある銅配線を保護する役目を担っている。特に層間絶縁膜やキャップ膜が酸素プラズマや容量膜のエッチングプロセス耐性が無い場合には、ハードマスク膜の存在がないと、論理回路部の銅配線が酸化するなどにより、抵抗の上昇や信頼性の劣化が起こり、論理回路部の性能劣化や動作不良を引き起こすことになる。

【0052】

次に、下部電極加工の際と同様にアッシングによって上部電極加工レジスト膜97を除去する。さらに上部電極をマスクとして、ハードマスク絶縁膜94をエッチバックし、第4層配線のキャップ膜50を露出させる(図9)。これにより、ハードマスク絶縁膜94は容量膜と上部電極が存在する領域のみに残存するのみとなる。なお、図41は図9(a)における平面レイアウト図であり、メモリ回路領域のほぼ全面が上部電極膜93となっており、容量素子となる容量素子開口部98と、容量素子が存在しない領域では第4層配線のキャップ膜50が設けられている。

【0053】

前記ハードマスク絶縁膜94の一部が容量膜と上部電極が存在する領域に一部残存する構造は、本実施の形態のように容量素子90を多層配線中に埋め込み、かつ、多層配線の層間絶縁膜を低誘電率膜とした場合には非常に好ましい構造であり、本実施の形態のプロセスによって多層配線中に容量素子90を形成する場合には、必ず前記領域にハードマスク絶縁膜94が残存することになる。

【0054】

その後、第5層の層間絶縁膜51を成膜する(図10)。この際、メモリ回路部では容量素子90の存在によって、論理回路部との間に段差が生じるため、これをCMPなどの手法によって平坦化を行う。また、シリンダ開口部への絶縁膜の埋設が困難な場合には埋設性に優れる層間絶縁膜を用いて容量素子開口部98を埋設した後に、エッチバックを行い、開口部のみに層間絶縁膜を形成したのちに、第5層の層間絶縁膜51を成膜してもよい。その後、第5層配線の開口部を形成するためのマスクに用いるハードマスク絶縁膜54を成膜する(図11)。

以後の形成プロセスは、第2層配線25を形成するときの手法と同様に行うことにより、第5層配線55を形成する(図12)。さらに第5層配線55の形成後、第5層配線のキャップ膜60を形成する(図12)。このとき、メモリ回路部においては、上部電極が配線溝加工時のストッパとして機能し、溝深さが制限されるとともに、上部電極に直接接続される上部容量配線(メモリ回路領域に形成された第5層配線55)が同時に形成される。プレート線配線として上部容量配線が上部電極に直接接続された構造が得られる。これはプレート線配線として容量素子間を接続するだけでなく、その素子間の電気抵抗低減を実現する。またプレート線配線(メモリ回路領域に形成された第5層配線55)は図42(a)では奥行き方向に配線が延びているようにのみ記載しているが、実際にはメモリ回路領域内の平面において、メッシュ上の配線形状となっていてもよい(図43)。このように、本実施形態では、上部電極上に直接プレート線配線が形成されるような構造が得られる。さらに第6層配線65を同様に形成し、引き続いて上層配線を形成し、半導体集積回路を完成させる(図1)。

【0055】

本実施形態の効果について説明する。以上のように、メモリ回路部の容量素子を多層配線構造に埋め込み、かつ容量素子の構造に多層配線の複数層以上の高さを確保することで、微細化されても多層配線の構造を変更することなく、容量素子の容量を確保することが容易となる。具体的には、本実施の形態では、容量素子の高さを論理回路部の2層分より高い場合を示しているが、微細化に伴って容量値が不足する場合は、さらに1層増やし、3層分よりは高い構造とすることができ、このとき論理回路部の多層配線構造は変更する必要がない。

【0056】

さらに本実施の形態では、論理回路部の性能を重視し、配線抵抗低減のため、少なくとも容量素子が形成された領域の配線層のすべての配線が、銅を主成分とする配線材料で構成されることが望ましく、より好ましくは、配線層のすべての配線が、銅を主成分とする配線材料で構成されることである。上述のとおり、銅にはアルミニウムや銀などの金属の添加物を含んでいてもよい。

配線抵抗低減のためには、少なくとも容量素子が埋め込まれている多層配線(第2層配線25、第3層配線35、第4層配線45)に用いられている配線材料は銅であればよい。より好ましくは配線層(第1の層配層から第6の層配層)全てに銅配線を用いることが望ましい(ただし、いわゆるパッドAl層は除く)。本実施の形態では、図1に示すように、第1層配線15から第6層配線65まで全ての配線層を銅配線としている。本実施の形態の様な、メモリ回路部と論理回路部が同一の半導体基板上に集積されたいわゆるメモリ混載型のLSIの論理回路部の設計において、メモリ回路部が混載されていない一般の論理LSIの設計と同一のパラメーターを用いることができる。これにより、メモリ回路部を混載するLSIの論理回路部専用の設計が不要となる。

【0057】

このように、本実施形態によれば、容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することができる。それにより、メモリ回路と論理回路を同一の半導体基板上に形成した場合においても、設計時の論理回路の設計パラメーターを容量素子の有無に関わらず互換性のある値を使用可能とすることで、容量素子が同一基板上に存在する集積回路においても、設計が容易となる。

また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保するとともに、論理回路部のトランジスタの拡散層から第1配線層までの距離を従来に比べて大幅に低減し、その形成を容易にし、同時に抵抗を低減することで、トランジスタの寄生抵抗が小さく、高速動作が可能となる。

さらに、メモリ回路部および論理回路部に共通して低抵抗かつ低寄生容量のLow−k/Cu配線を適用することが可能となることで、容量素子を有するメモリ回路部を混載したとしても論理回路部の性能劣化は一切なくなる。

【0058】

さらに、容量素子の上部電極を、論理回路部に存在する配線と同一の高さに形成された上部容量配線で接続することによって、上部電極間を接続するためのプレート線とよばれる配線を形成するための専用の工程や専用の設備を必要とせず、同時に容量素子の上下膜厚の確保と論理回路部のコンタクト(ロジックコンタクト)のアスペクトが低減可能である。また、下部容量配線と下部容量配線が設けられた配線層の配線との上面が同一の平面となるようにこの下部容量配線を設けても同様の効果が得られる。さらに、容量素子の開口部以外の容量絶縁膜の下部に部分的にシリコン酸化膜を設けることにより、容量素子形成中に論理回路部のシリコン酸化膜の下層に存在するキャップ膜、ひいてはさらにその下層にある銅配線および層間絶縁膜を保護する役目を担わせることができる。シリコン酸化膜の存在により、論理回路部の銅配線が酸化するなどによる抵抗の上昇や信頼性の劣化を防止し、論理回路部の性能劣化や動作不良を抑制することができる。

容量素子は、本実施形態に記載したように、最も微細化が進んでいる下層に位置する多層配線層に形成することが有効である。下層に位置する多層配線層を構成する配線層および配線の厚さは同一であることが一般的である。これは、配線の特性が各層で同等となり、混載されるロジック側の回路設計を容易ならしめるといった効果があるためである。但し、本実施形態の趣旨は、少なくとも2層以上にわたる多層配線層に容量素子が埋め込まれていることであり、その配線層や配線の厚さが同一であることを必要不可欠としているわけではない。第一の実施形態の変形例として、例えば後述する図32に示すように下層に位置する多層配線の上に位置する上層多層配線層(グローバル配線)に容量素子の上部の一部が形成されていてもよい。一般に該上層多層配線層を構成する各配線層や配線の厚さは、前記下層に位置する多層配線層よりも厚いことが一般である。

【0059】

ところで、特許文献2記載の内容を図に示すと図33((a)、(b))のようになる。図33に示す、111はリフトアップ絶縁膜A、112はリフトアップ配線プラグA、113は容量加工ストップ膜、114は、リフトアップ絶縁膜B、115はリフトアップ配線プラグB、116は、配線加工ストップ膜、117はプレート線を表す。特許文献2ではメモリ回路部101には容量素子90の上に多層配線部103を付与したような構造(アドオン型)になっており、論理回路部102では、容量素子90の高さに応じて多層配線部103をリフトアップする配線部(リフトアップ配線部104)が必要となっていた。このリフトアップ配線部104は、そのアスペクト比の高さから形成が困難なだけでなく、抵抗が高い。これはアドオン型論理回路部102の設計パラメーターがリフトアップ配線部104の存在によって、その存在が無い場合の設計パラメーターと大きく解離することとなるだけでなく、アドオン型論理回路部102の性能が劣化する。これらは微細化の進展によりさらに難易度が増すことになる。

【0060】

これに対して、本実施形態では、これらのメモリ回路部および論理回路部の構造を、図33((c)、(d))に示すような、容量素子90を多層配線構造に埋め込んだ、ビルトイン型構造のメモリ回路部105および論理回路部106とすることで、容量素子の高さは多層配線を貫く層数を変化させることで容量の確保が可能となり、かつ、ビルトイン型の論理回路部106は容量素子90の存在によって設計パラメーターが変化することが無い。すなわち、同一半導体基板上にビルトイン型のメモリ回路部105が存在していても、論理回路部の多層配線の構造・材料にはまったく変化を及ぼさないことから、論理回路部のみの場合と完全に互換性のある設計パラメーターを用いることが可能となる。別な言い方をすれば、容量素子を有するメモリ回路部と論理回路部からなる混載回路チップにおいて、通常の論理回路部のみの論理回路チップとまったく同等の論理演算能力を維持しつつ高速メモリ機能を発現させることができる。

【0061】

また、前記のように、本形態では、層間絶縁膜にMPS膜をキャップ膜にSCCを用いているが、図13に示すように、層間絶縁膜にBlack DiamondTM、のようなSiOCH膜を、キャップ膜にSiCN膜を採用してもよい。この場合、これらの膜組成は窒素の存在の有無が異なることから、容量素子90の開口部の形成においては、その点を考慮した加工条件を採用する必要がある。

あるいは、図14に示すようにプレート線配線(メモリ回路領域に形成された第5層配線55)をメモリ回路領域において、配線形状ではなくパッド上の形状、つまり超幅広配線のようになっていてもよい。また、ところどころにスリットを介在させたスリット入り幅広配線形状となっていてもよい。

【0062】

(第二の実施形態)

図15は、本発明のひとつの実施の形態の半導体装置を示す断面図である。図15の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

第一の実施形態の構造からさらに、コンタクトプラグ4に銅を採用し、さらに第1層配線15とデュアルダマシン形状(デュアルダマシンコンタクト形状)を形成する事により、さらに拡散層から第1層配線15までの抵抗を低減した構造とすることが可能である。この際、コンタクト層間絶縁膜1は図2のようにシリコン酸化膜とすることも可能であるが、ここでは第1層配線15と同一の層間絶縁膜としている。あるいはコンタクト層間絶縁膜1には第1層とは異なる別の種類の低誘電率SiOCH膜を用いても良い。また異種の低誘電率SiOCH膜の積層構造としてもよい。コンタクト層間絶縁膜1には、Cu拡散バリア耐性を持つ膜、例えば、前記SCC膜を用いることが望ましい。積層構造を用いる場合には、最下層、つまりはエッチストップ膜直上に用いることが望ましい。

【0063】

特にSCC膜はプラズマ重合法で成膜されることから、通常のプラズマCVD法による層間絶縁膜よりも段差被覆性に優れており、エッチストップ膜成膜後の半導体基板のようにゲートの存在による凹凸上に成膜する際にも、良好な埋設性が得られる。

【0064】

また、本実施の形態では、コンタクトプラグ4の材料にも銅を採用しており、コンタクトプラグ4を含めたプラグおよびビアを含めた配線金属全て(ただし、いわゆるパッドAl層は除く)に銅を用いることで、低抵抗化を実現しており、非常に好ましい形態の一つである。

【0065】

さらに、本実施の形態の構造におけるコンタクトプラグ4のコンタクトバリアメタル膜3は、第1層配線15のバリアメタル膜13を兼ねており、上述の通りデュアルダマシンプロセスで形成することから、その銅拡散耐性が高く、かつ低抵抗のバリア膜であることが望ましい。前記バリアメタルに使われる金属膜のなかでも、好ましくは窒化タンタル、タンタル/窒化タンタルの積層構造、より好ましくは、ルテニウム/チタンの積層構造が望ましい。

【0066】

(第三の実施形態)

図16は、本発明のひとつの実施の形態の半導体装置を示す断面図である。

図17〜図25は、図16の半導体装置の製造方法を工程順に示す断面図の例である。図16の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面である。また右側(c)は論理回路領域の代表的な断面図を示す。図17〜図25のいずれも図の左側(a)はメモリ回路領域、右側(b)は論理回路領域の代表的な断面図を示す。

第一の実施形態と同様に、標準的な集積回路の形成方法を用いて作成した、MOSトランジスタ9および第3層配線形成後の構造を有する基板を図17に示す。ここでは後にメモリ回路領域には容量素子を形成するため、論理回路領域のみに第2層配線25と第3層配線35を形成する。本実施の形態では容量素子の高さを論理回路部の3層分よりは低い場合を示しているが、4層分より低い場合とする場合にはさらに論理回路部を1層多く形成する。

【0067】

図17において、1はコンタクト層間絶縁膜、2はエッチストップ膜、3はコンタクトバリアメタル膜、4はコンタクトプラグ、5はシリコン(Si)基板,6は素子分離STI(shallow trench isolation)、7は拡散層、8はゲート電極である。

【0068】

また、11は第1層の層間絶縁膜であり、13は第1層配線バリアメタル膜、15は第1層配線、20は第1層配線のキャップ膜、23は第2層配線バリアメタル膜、25は第2層配線、30は第2層配線のキャップ膜、である。また、ビット線19は第1層配線15と同時に形成されるが、メモリ回路部におけるビット線である。

【0069】

さらに、ここでビット線19は第1層配線15と同一層に形成されており、特許文献2などに見られるような、ビット線だけの配線層は存在しない。さらに本実施の形態では、容量素子の下部電極との電気的接続を行う、いわゆる下部電極コンタクトを取る下部電極配線が、ビット線19と同層の第1層配線15中に形成されている。本実施の形態に示す構造により、多層配線構造は層数を有効に活用することが可能である。

【0070】

図17ではコンタクト層間絶縁膜1はシリコン酸化膜からなり、コンタクトプラグ4はタングステンからなり、コンタクトバリアメタル膜3は窒化チタン/チタンの積層膜からなる。また、第1層の層間絶縁膜11および第2層の層間絶縁膜21は低誘電率絶縁膜でありSiOCH膜、より具体的にはMPS膜からなる。第1層配線バリアメタル膜13はタンタル/窒化タンタル積層膜からなり、第1層配線15は銅からなる。また、第1層配線のキャップ膜20および第2層配線のキャップ膜30はSCC膜からなる。またSCC膜についても、MPS膜と同様に非特許文献1に詳細が記載されている。SCC膜はSiOCH膜の一種でありながら、銅拡散耐性を持つことが特徴である。第2層配線25および第3層配線35を形成する手法は第一の実施形態に示した通りである。

【0071】

本実施の形態においても層間絶縁膜およびキャップ膜は単層の絶縁膜を用いているが、第一の実施形態同様、それぞれ、複数種の絶縁膜の積層構造でもよい。たとえば、層間絶縁膜はMPS膜と他のSiOCH膜、キャップ膜はSiC膜とSiCN膜の積層構造などでもよい。

【0072】

ここでは後にメモリ回路領域には容量素子を形成するため、論理回路領域のみに配線層を形成する。本実施の形態では容量素子の高さを論理回路部の3層分よりは低い場合を示しているが、4層分より低い場合とする場合にはさらに論理回路部を1層多く形成する。

【0073】

次に図18のように第3層配線のキャップ膜40を堆積した後に、ハードマスク絶縁膜94を成膜する。さらにシリンダ加工レジスト膜A81をリソグラフィによって形成する。

【0074】

ここでハードマスク絶縁膜94はシリコン酸化膜を用いたが、他の絶縁膜との積層構造でもよい。またレジスト膜との間に反射防止膜を備えるなどの多層構造をとってもよい。いずれの場合も容量素子形成過程で第4層配線のキャップ膜50を保護する効果をもつ絶縁膜であることが好ましい。具体的には、シリコン酸化膜のほか、シリコン窒化膜、シリコン酸窒化膜などが挙げられる。

【0075】

引き続いて図19に示すようにドライエッチングによって容量素子開口部A88を形成する。このとき、第1層配線15の酸化を防止するため、第1層配線のキャップ膜20はエッチングしない。

【0076】

容量素子開口部A88の形成時には、ドライエッチングによって層間絶縁膜とキャップ膜を交互にエッチングを行うが、本実施の形態では、第一の実施形態同様に層間絶縁膜にMPS膜をキャップ膜にSCCを用いており、SiOCH膜が積層された構造を用いており、加工上の工夫によって、良好な容量素子開口部A88の形状を得ることができる。

【0077】

さらにシリンダ加工レジスト膜A81をアッシングにより除去した後に、シリンダ加工レジスト膜B82、シリンダ加工マスク絶縁膜84を形成し、リソグラフィによってシリンダ加工レジスト膜C83を形成する(図20)。再びドライエッチングによって、容量素子開口部B89を形成する(図21)。さらにアッシングを行い、シリンダ加工レジスト膜B82を除去し、引き続き、容量素子の下部電極を下層の配線となる第1層配線15に接続するため、第1層配線のキャップ膜20をエッチバックする(図22)。

【0078】

以後、第一の実施形態と同様に、容量素子の下部電極となる下部電極膜91を成膜し、リソグラフィによって下部電極膜91を容量素子内部のみに形成し、さらに引き続いて、容量絶縁膜92と上部電極膜93を成膜する(図23)。やはり第一の実施形態同様に、容量絶縁膜92と上部電極膜93を加工する(図24)。

【0079】

さらに上部電極をマスクとして、ハードマスク絶縁膜94をエッチバックし、第3層配線のキャップ膜40を露出させる(図示せず)。これにより、ハードマスク絶縁膜94は容量膜と上部電極が存在する領域のみに残存するのみとなる。

【0080】

その後、第4層の層間絶縁膜41を成膜する(図25)。以後の工程は第一の実施形態と同様に行い、第4層の層間絶縁膜41を平坦化後、第4層配線45を形成する。引き続き上層配線となる第5層配線55を形成し(図16)、さらに上層配線を形成し、半導体集積回路を完成させる。

【0081】

本実施の形態では、実施の形態1あるいは2と同様に、ビット線19は第1層配線15と同一層に形成されており、特許文献2などに見られるような、ビット線だけの配線層は存在しない。さらに本実施の形態では、容量素子の下部電極との電気的接続を行う、いわゆる下部電極コンタクトを取る配線が、ビット線19と同層の第1層配線15中に形成されている。本実施の形態に示す構造により、多層配線構造は層数を有効に活用することが可能である。また、容量素子を第2層配線25の層と第3層配線35の層を貫くように形成し、また、下部電極への接続については、第1層配線15に直接行うため、径の異なるシリンダを上下に接続した形状となっている。本形状は、前記容量素子の下部電極へ接続を第1層配線15に直接行うために好適な構造である。これにより、本実施形態の容量素子の構造は、径の異なるシリンダを接続した形状となる。

【0082】

前記のように、本実施の形態では、層間絶縁膜にMPS膜をキャップ膜にSCCを用いているが、図26に示すように、層間絶縁膜にBlack DiamondTM、のようなSiOCH膜を、キャップ膜にSiCN膜を採用してもよい。この場合、これらの膜組成は窒素の存在の有無が異なることから、容量素子の開口部の形成においては、その点を考慮した加工条件を採用する必要がある。

【0083】

(第四の実施形態)

図27は、本発明のひとつの実施の形態の半導体装置を示す断面図である。図27の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

第三の実施形態の構造からさらに、コンタクトプラグ4に銅を採用し、さらに第1層配線とデュアルダマシン形状(デュアルダマシンコンタクト形状)を形成する事により、さらに拡散層から第1層配線15までの抵抗を低減した構造とすることも可能である。この際、コンタクト層間絶縁膜1は図2のようにシリコン酸化膜とすることも可能であるが、ここでは第1層配線15と同一の層間絶縁膜としている。あるいはコンタクト層間絶縁膜1には第1層とは異なる別の種類の低誘電率SiOCH膜を用いても良い。また異種の低誘電率SiOCH膜の積層構造としてもよい。コンタクト層間絶縁膜には、Cu拡散バリア耐性を持つ膜、例えば、前記SCC膜を用いることが望ましい。積層構造を用いる場合には、最下層、つまりはエッチストップ膜直上に用いることが望ましい。

また、本実施の形態の半導体装置においては、下部電極(下部電極膜91)に接続する下部容量配線(第1層配線15)が、半導体基板(シリコン基板5)の表面近傍に形成された拡散層7に接続するコンタクトプラグ4に接続され、かつ下部容量配線(第1層配線15)と同層に半導体素子(MOSトランジスタ9)間を接続する信号配線(ビット線19)が形成されている。

【0084】

特にSCC膜はプラズマ重合法で成膜されることから、通常のプラズマCVD法による層間絶縁膜よりも段差被覆性に優れており、エッチストップ膜成膜後の半導体基板のようにゲートの存在による凹凸上に成膜する際にも、良好な埋設性が得られる。

【0085】

またさらに、本実施の形態の構造におけるコンタクトプラグ4のコンタクトバリアメタル膜3は、第1層配線15のバリアメタル膜13を兼ねており、上述の通りデュアルダマシンプロセスで形成することから、その銅拡散耐性が高く、かつ低抵抗のバリア膜であることが望ましい。前記バリアメタルに使われる金属膜のなかでも、好ましくは窒化タンタル、タンタル/窒化タンタルの積層構造、より好ましくは、ルテニウム/チタンの積層構造が望ましい。

【0086】

(第五の実施形態)

図28は、本発明のひとつの実施の形態にかかる半導体装置を示す断面図である。図28の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

図19において、シリンダ加工レジスト膜A81を形成後、容量素子開口部A88を形成する際に、ドライエッチング条件の異方性を制御し、等方成分を増加させることで、容量素子開口部A88をテーパー形状に形成することが可能である。テーパー形状の容量素子開口部A88が形成された後に、図23以降と同様の工程を実施することにより、図28に示すような構造が形成される。本実施の形態の手法により、容量素子開口部B89を形成するためのリソグラフィ工程およびレチクルが不要となり、製造コストの低減が可能となる。

【0087】

本実施の形態でも、容量素子は第2層配線25の層と第3層配線35の層を貫くように形成され、また、下部電極への接続については、第1層配線15に直接行うため、径の異なるテーパー付きのシリンダを上下に接続した形状となっている。本形状は、上述の第三の実施形態あるいは第四の実施形態同様、容量素子の下部電極へ接続を第1層配線15に直接行うために好適な構造である。

【0088】

(第六の実施形態)

図29は、本発明のひとつの実施の形態の半導体装置を示す断面図である。29の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

図18において、第3層配線のキャップ膜40を堆積した後に、ハードマスク絶縁膜94を成膜する。

この際、ハードマスク絶縁膜94を20nm以上、30nm以下程度の薄膜とする。さらにシリンダ加工レジスト膜A81をリソグラフィによる形成以降は第三の実施形態と同様に行う。シリンダ開口部Aの底にある第1層配線のキャップ膜20をエッチバックする際には、同時にハードマスク絶縁膜94もエッチングされるため、その膜厚は10nm以上、20nm以下程度に減少する。その後、第三の実施形態と同様に下部電極膜の成膜を行い、リソグラフィ後、下部電極のエッチバックを行う。その際、オーバーエッチングによって、ハードマスク絶縁膜94はさらに膜厚が減少し、10nm程度もしくは10nm未満となる。その後、容量絶縁膜92と上部電極膜93の成膜に続き、それらの加工を行う際には、ジョブ電極の無い領域のハードマスク絶縁膜94はほぼ除去される。したがって、第三の実施形態で記載したエッチバック工程は不要となる。以降の上層配線工程は第三の実施形態と同様に実施する。

【0089】

ただし、本実施の形態の構造では、第4層配線のキャップ膜50の下面(第4層配線45の表面)から、上部電極膜93の表面までの距離は、第4層配線45のビア高さより短いため、メモリ回路領域においても第4層配線45下のビアの形成が必要となり、ビアパターンを露光することが必要である。ただし、この際の露光は第4層配線45のビアパターン露光と同時に行うことから、レチクル数の増加や工程数の増加はない。

【0090】

以上の手法によって図29に示すような構造が形成される。

本実施形態は、第一の実施形態から第五の実施形態の構造に、さらに上部電極と上部容量配線との間に接続ビアが設けられたものである。これらの実施形態の構造においては、容量素子の上部電極上に直接形成する配線溝深さは、表面を同じくする同層の論理回路部の配線溝よりも浅くなければならない制限があった。これに対して、本実施の形態のような、容量素子の上部電極にビアを介して接続する構造とすることで、前記制限がなくなる。これによって、配線構造設計の自由度が向上する。言い換えると、容量素子の上部電極上に直接形成する配線構造に限定することは、容量素子の構造によっては、論理回路部の配線溝深さに制限が生じることになる。

【0091】

本実施の形態では容量素子を第2層と第3層を貫く形で形成したが、これを例えばローカル配線層とセミグローバル配線層の両方を貫く形で形成する場合には、セミグローバル配線層のビア高さが高くなることから、第一の実施形態のような上部電極上に直接プレート線配線が形成されるような構造を形成するより、本実施の形態のほうがハードマスク絶縁膜94の膜厚を低減でき、特にセミグローバル層の層間絶縁膜も低誘電率SiOCH膜を用いる場合には層間絶縁膜の実効誘電率を低減することが可能である。

【0092】

(第七の実施形態)

図30及び図31は、本発明のひとつの実施の形態の半導体装置を示す断面図である。図30の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

本実施の形態の図30では、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の3配線層にまたがる領域に該容量素子を埋め込んだ構造である。また図31は同様に4配線層にまたがる領域に該容量素子を埋め込んだ構造である。図31では、第6の配線層にさらに、第7の配線層として、第7層配線75と第7層の層間絶縁膜71が設けられている。第2層配線の開口部と同等にして、第7層配線の開口部を形成することができる。図31に示す、第7層配線バリアメタル膜73も、第1層配線バリアメタル膜13または第2層配線バリアメタル膜23と同様にして形成できる。図31に示す、第7層配線のキャップ膜70は、第2層配線のキャップ膜30と同様にして形成できる。

【0093】

図17の構造からさらに論理回路部に多層配線を1層、あるいは2層を形成した後に、実施の形態5同様、シリンダ加工レジスト膜(図示せず)を形成し、容量素子開口部Aを形成する際に、ドライエッチング条件の異方性を制御し、等方成分を増加させることで、容量素子開口部Aをテーパー形状に形成する(図示せず)。テーパー形状の容量素子開口部が形成された後に、図23以降と同様の工程を実施することにより、図30に、あるいは図31に示すような構造が形成される。本実施の形態の手法により、容量素子開口部Bを形成するためのリソグラフィ工程およびレチクルが不要となり、製造コストの低減が可能となる。

【0094】

図30では、容量素子は第2層配線25の層からと第4層配線45の層を貫くように形成され、また、図31では、容量素子は第2層配線25の層からと第5層配線55の層を貫くように形成され、下部電極への接続については、第1層配線15に直接行うため、径の異なるテーパーのついたシリンダを上下に接続した形状となっている。この形状は、上述の第三の実施形態あるいは第四の実施形態と同様、容量素子の下部電極へ接続を第1層配線に直接行うために好適な構造である。

さらに、図32に示すように、第一の実施形態の変形例として、下層に位置する多層配線の上に位置する上層多層配線層(グローバル配線)に容量素子90の上部の一部が形成されていてもよい。また、上層に位置する多層配線層を構成する各配線層や配線の厚さは、下層に位置する多層配線層よりも厚くてもよい。図32では、容量素子90が設けられた領域のうち、第2の配線層から第4の配線層が同じ厚みであり、第2層配線25から第4配線の厚みが同じであるとともに、これらの配線層の厚みと第5の配線層の厚みが異なり、これらの配線の厚みと第5の配線の厚みが異なる。このように、本実施形態は、容量素子90が設けられた領域の多層配線構造において、各配線層の厚みと各配線の厚みが異なる構造を有してもよい。

【0095】

容量素子90の開口部の形成時には、ドライエッチングによって層間絶縁膜とキャップ膜を交互にエッチングを行うが、本実施の形態では、層間絶縁膜にMPS膜をキャップ膜にSCCを用いており、SiOCH膜が積層された構造となっている。先に述べた通り、この2つの膜は炭素の組成が大きく異なっており、ドライエッチングによる加工条件を工夫することにより、MPS/SCC膜のエッチングレートの比、いわゆるエッチング選択比を制御することが容易である。したがって、層間絶縁膜であるMPSをエッチングしながら、キャップ膜であるSCC膜のエッチング選択比を小さくして、容量素子90の開口部を深く開口したり、反対にMP/SCCの選択比を大きくして、シリンダ開口部底でエッチングを止めたりすることか出来る。本実施の形態では特に深いシリンダ開口部を形成する必要があるが、本実施の形態の構造においては、積層構造での深い開口部を形成が容易である。これは一般的に用いられるSiOCH層間絶縁膜とSiCNキャップ膜の組み合わせでは実現困難な手法である。こうした加工の自由度が高い構造を用いることにより、良好な容量素子90の開口部の形状を得ることができる。

【0096】

さらに、本実施の形態では、3層以上の配線層を貫くように容量素子を形成していることから、メモリ回路部のセル容量を大きくすることができる。また、このとき、論理回路部の構造は、メモリ回路部の存在しない場合と同様の多層配線構造をとっており、設計パラメーターは変化せず、互換性がある。

さらに、図30に示す通り、容量素子90が3層以上の配線層を貫くように設けられているため、メモリ回路領域の容量素子90が埋め込まれている、この多層配線構造中に、行デコード配線17と列デコード配線18が設けられている。容量素子90が埋め込まれている多層配線構造中に、行デコード配線17および列デコード配線18を設けることにより、上層配線を利用する必要がなくなり、メモリ回路領域の配線層数を減ずることができる。これによってメモリ回路領域の上層は論理回路領域の配線のために用いたり、各回路領域間を接続するために用いたりすることが可能となり、チップ面積を縮小することが可能になる。

【0097】

(第八の実施の形態)

図34は、本発明のひとつの実施の形態にかかる半導体装置を示す断面図である。図34の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

本実施の形態の半導体装置においては、下部電極(下部電極膜91)に接続する下部容量配線がコンタクトプラグ4であり、下部電極(下部電極膜91)がコンタクトプラグ4に直接接続している。つまり、コンタクトプラグ4を構成するタングステン上に、下部電極(下部電極膜91)が設けられている。

【0098】

図34において、1はコンタクト層間絶縁膜、2はエッチストップ膜、3はコンタクトバリアメタル膜、4はコンタクトプラグ、5はシリコン(Si)基板、6は素子分離STI(shallow trench isolation)、7は拡散層、8はゲート電極である。

【0099】

また、11は第1層の層間絶縁膜であり、13は第1層配線バリアメタル膜、15は第1層配線、20は第1層配線のキャップ膜、23は第2層配線バリアメタル膜、25は第2層配線、30は第2層配線のキャップ膜、である。また、メモリ回路部において、ビット線19は、第1層配線15と同時に形成される。ここで、ビット線19は、第三の実施の形態と同様に、第1層配線15と同一の層に形成されている。また、本実施の形態においては、特許文献2などに見られるような、ビット線だけの配線層は存在しない。

【0100】

さらに、メモリ回路部において、列デコード配線18は、第2層配線25と同時に形成される。本実施の形態においては、列デコード配線18は第2層配線25と同時に形成されているが、これに限定されず、たとえば列デコード配線18の代わりに、行デコード配線17を形成してもよい。このとき、第2層配線25と同時に形成されなかった列デコード配線18は、たとえば第6層等に形成してもよい。

【0101】

図34ではコンタクト層間絶縁膜1はシリコン酸化膜からなり、コンタクトプラグ4はタングステンからなり、コンタクトバリアメタル膜3は窒化チタン/チタンの積層膜からなる。また、第1層の層間絶縁膜11および第2層の層間絶縁膜21は低誘電率絶縁膜でありSiOCH膜、より具体的にはMPS膜からなる。第1層配線バリアメタル膜13はタンタル/窒化タンタル積層膜からなり、第1層配線15は銅からなる。また、第1層配線のキャップ膜20および第2層配線のキャップ膜30は、SCC膜からなる。またSCC膜についても、MPS膜と同様に非特許文献1に詳細が記載されているものを用いることができる。SCC膜は、SiOCH膜の一種でありながら、銅拡散耐性を持つことが特徴である。第2層配線25および第3層配線35を形成する手法は、第一の実施の形態に示した通りである。

【0102】

本実施の形態においても層間絶縁膜およびキャップ膜は単層の絶縁膜を用いているが、第一の実施の形態と同様に、それぞれ、複数種の絶縁膜の積層構造でもよい。たとえば、層間絶縁膜はMPS膜と他のSiOCH膜、キャップ膜はSiC膜とSiCN膜の積層構造などでもよい。

【0103】

本実施の形態においても第三の実施の形態と同様に、容量素子90の構造を、径の異なるシリンダが接続された形状とする。第三の実施の形態と異なるのは、下部電極への接続を第1層配線15ではなく、より下層のコンタクトプラグ4に対して行うことである。したがって、本実施の形態においては、第三の実施の形態中の第1層配線15形成時には、下部電極が接続する予定領域に第1層配線の形成を行わない(図示せず)。

【0104】

容量素子90の形成手順は第三の実施の形態に準ずる。第三の実施の形態と異なる点としては、ドライエッチングによって容量素子開口部A88を形成する際には、第1層配線層のキャップ膜20と第1層の層間絶縁膜11までエッチングし、Wからなるコンタクトプラグ4を露出させる。容量素子開口部A88の形成時には、ドライエッチングによって層間絶縁膜とキャップ膜を交互にエッチングを行う。このとき、本実施の形態では、第三の実施の形態と同様に層間絶縁膜にMPS膜をキャップ膜にSCCを用いており、SiOCH膜が積層された構造を用いており、加工上の工夫によって、良好な容量素子開口部の形状を得ることができる。

【0105】

これ以後の工程は第三の実施の形態と同様である。ただし、すでに第1層配線層のキャップ膜20と第1層の層間絶縁膜11までエッチングされていることから、容量素子開口部B89を形成する際には、第1層配線キャップ膜20のエッチバック工程を行う必要はない。

以後、第一の実施の形態と同様に、容量素子90の形成と第4層配線45以降の上層配線の形成を行い、半導体集積回路を完成させる。

【0106】

本実施の形態では、容量素子90の下部電極(下部電極膜91)との電気的接続を行う、いわゆる下部電極コンタクトを取る配線(下部容量配線)が、トランジスタの拡散層7に接続するコンタクトプラグ4を兼ねている。これにより、下部電極が、上記集積回路の第1層配線15と同層にある。そのため、第1層配線15上に形成した場合よりも、容量素子90の容量を確保しやすくなる。また、下部容量配線が、トランジスタの拡散層に接続するコンタクトプラグを兼ねていることにより、コンタクトプラグ4までがトランジスタパラメータとして設計されている場合、容量素子90を混載した場合でも、パラメーターを変更する必要がない。同時に、従来技術と同様に、容量コンタクトはタングステン上に形成することになり、容量素子90形成過程において、異種材料の露出による性能への影響を考慮する必要がない。具体的には、下部電極形成時にはCuは露出することがないため、下部電極としてCuバリア性を考慮する必要がなくなる。したがって、TaNのようなCuバリア性を有するバリアメタル膜を下部電極に用いる必要がない。

【0107】

第八の実施の形態の変形例としては、図35に示すように、メモリ回路領域において、プレート線配線(メモリ回路領域に形成された第4層配線45)が、配線形状ではなく、シリンダ容量部上部を完全に覆っていて、超幅広配線のようになっている。さらには、このプレート線配線が、シリンダ内部まで配線材料で埋設されている。このプレート線配線の配線形状は、たとえば所定間隔でスリットを介在させた、スリット入り幅広配線形状になっていてもよい。

【0108】

図35の左側(a)はメモリ回路領域の断面図であり、右側(b)は論理回路領域の代表的な断面図を示す。図35において、ほとんどの構成は図34と同様である。90度回転させた構造は図示しないが図34とほぼ同様である。

【0109】

本実施の形態においても第三の実施の形態と同様に、容量素子90の構造を、径の異なるシリンダが接続された形状とする。また、容量素子90の構造は第八の実施の形態と同様であり、その形成方法も同様である。第八の実施の形態と異なるのは、第4層配線45の形成の前に、シリンダ内部の絶縁膜を除去する工程を追加することである(図示せず)。論理回路部の第4層配線の形成以降の工程については第三の実施の形態と同様である。

【0110】

(第九の実施形態)

図36は、本発明のひとつの実施の形態の半導体装置を示す断面図である。図36の左側(a)はメモリ回路領域の断面図であり、右側(b)は論理回路領域の代表的な断面図を示す。図36においては、第一の実施の形態と同様に、標準的な集積回路の形成方法を用いて作成した、MOSトランジスタ9を備えている。さらに、本実施の形態においては、従来の技術として示される図33(a)および33(b)のように、コンタクト相関絶縁膜1の上には、リフトアップ絶縁膜A111が形成されている。リフトアップ絶縁膜A111中には、ビット線19およびリフトアップ配線プラグA112が形成されている。これらのビット線19およびリフトアップ配線プラグA112の形成方法は一般的に知られた手法で形成可能である。このビット線19は第一層配線15の下層に形成されることから、第0層配線と呼ばれる。

【0111】

例えば、ビット線となる窒化チタン膜とタングステン膜の積層膜をリソグラフフィ技術とエッチング技術によってビット線パターンに加工する。その後、リフトアップ絶縁膜A111を成膜し、ビット線19に起因する段差をCMP技術によって平坦化する。再びリソグラフフィ技術とエッチング技術によって、リフトアップ配線プラグA112を形成するための接続孔を形成する。引き続いて窒化チタン膜とタングステン膜の積層膜を接続孔に埋め込むように成膜し、余剰部分をCMP技術によって除去する。

【0112】

以上が形成例の一つである。このとき、リフトアップ絶縁膜A111には通常シリコン酸化膜が用いられる。これは、リフトアップ配線プラグA112を形成する際のプロセス温度に耐えうる絶縁膜であればよい。また、ビット線19の形成方法として、リフトアップ絶縁膜A111をまず薄く成膜した後に、ビット線19と接続すべきコンタクトプラグ4との接続孔を開孔した後に、上記に示したような形成方法でビット線19を形成しても良い。

【0113】

ビット線19およびリフトアップ配線プラグA112を形成したのち、第一の実施の形態で示した、第3層と第4層の配線を形成した手法により、図36における第1層配線15および第2層配線25を形成する。ただし図36においては、第1層配線15はビア層がないため、ビア層形成に関わる工程は不要である。

【0114】

第2層配線25形成後、やはり第一の実施の形態で示した手法により、容量素子90を形成する。本実施の形態においては第一の実施の形態と異なり、第2層配線25のキャップ膜30を形成したのちに、第3層の層間絶縁膜31をビア層に相当する膜厚程度と同じか薄く成膜する。その後に、ハードマスク絶縁膜94を成膜し、以降は第一の実施の形態と同様に容量素子90の形成を行うため、下部電極膜91の形成を行い、さらに容量絶縁膜92と上部電極膜93の形成を行う。

【0115】

上部電極膜93を形成した後、第一の実施の形態と異なり、本実施の形態では、プレート線117となる金属材料を成膜する。例えば、タングステン膜である。金属材料成膜の膜厚は、表面高さが第3層の配線層の表面の高さより低くなっているようにする。

【0116】

ここで、ビット線19を形成する際に用いた手法と同様な手法により、プレート線として、プレート線117、上部電極膜93、容量絶縁膜92、ハードマスク絶縁膜94を加工した。引き続いて、第3層の層間絶縁膜B131を成膜する。第一の実施の形態と同様に、メモリ回路部では容量素子90の存在によって、論理回路部との間に段差が生じるため、CMPなどの手法によって平坦化を行う。この平坦化後の第3層の層間絶縁膜B131の膜厚は第3層配線35の上面の高さとなるようにする。

【0117】

この後、第一の実施の形態と同様にハードマスク絶縁膜(図示せず)を形成し、第3層配線35を形成する。

【0118】

本実施の形態の例では、プレート線としてタングステン膜を用いることを想定しているが、第一の実施の形態で示した図14あるいは、第八の実施の形態の変形例図35のようなプレート線配線形状となっていてもよい。

【0119】

本実施の形態の例では、第八までの実施の形態に比べて、論理回路部の配線構造が従来構造に近く特殊となっていることで、メモリ回路部が混載されない一般の論理LSIの設計パラメータと完全に一致させることは困難であるが、従来の技術に対しては近づけることは可能となる。同様に、従来の技術に比較して、多層配線構造の層数を有効に活用可能である。本実施の形態では、構造が比較的従来の技術に近いため、作成が容易であるという利点がある。もちろん、多層配線の複数層に渡るように該容量素子を配置することにより得られる効果は他の実施の形態と同様に得られる。

【0120】

(第十の実施形態)

図44〜図46は、本発明のひとつの実施の形態にかかる半導体装置を示す平面レイアウト図である。

各図は、第一の実施の形態におけるメモリ回路領域の構造について、代表的な素子構造を示している。特にプレート線や、その他の配線等、下記の説明のために一部の配線等については記載を省略している。

【0121】

ワード線となるゲート電極8とビット線19が直交している。ビット線19は列(Y)デコード線18と平行かつ、直線形状に形成されている。また、シリンダ形状の容量素子90の形状は矩形である。本実施の形態では、ビット線3本に対して列デコード線1本の割合で配置している。このビット線19と列デコード線18の配置比は16:1や64:1など、さらに大きくなっていてもよい。本実施の形態では、ビット線19を直線形状(矩形)にすることによって、さらに、シリンダ形状の容量素子90も矩形に形成でき、光近接効果補正を含めた露光や、ドライエッチング加工などの形成プロセスが容易となる。特に32nmや28nm技術世代以降において、光近接効果補正は複雑になっており、各要素パターンを単純な矩形あるいは直線形状で形成することは、面積あたりのビット密度を向上させるため、あるいは設計通りの形状を得るためには非常に効果的である。

【0122】

図44では、容量素子90の平面レイアウトにおいて、容量コンタクト119および容量セルコンタクト120に対するマージンを確保したレイアウトである。これに対して、図45では、容量素子90の外周側において上記のマージンを切り詰めたレイアウトになっている。図45に示すレイアウトでは、面積あたりのビット密度は図44のものより向上可能であるが、容量コンタクト119や容量セルコンタクト120に対するマージンがある一方向においてないため、形成時の目合わせずれの発生により、抵抗が上昇する可能性がある。

【0123】

さらに図46においては、拡散層7のレイアウトを図44のレイアウトから変更している。具体的には、図46に示すレイアウトでは、特に折り返しビット線方式を採用した場合に、単位面積あたりのビット密度を向上させることが可能となる。

【0124】

また、本実施の形態では、ワード線の抵抗を低減するための、いわゆるワード線裏打ち配線となる第5層配線55と、ワード線とのコンタクトをとるワード線コンタクト121をメモリ回路領域の外周に設けている。図44または図45が平面図であるため、図中のワード線コンタクト121は平面構造のみ示しているが、実施の形態における論理回路領域の様に第5層配線から第1層配線までのスタック形ビアを介して接続され、さらにその該第1層配線とゲート電極8上とをコンタクトプラグ4を介して接続されている。ワード線コンタクト121は一定のビット線毎に形成され、16本のビット線毎から、256本毎、512本毎等、メモリ回路領域の外周に形成されている。

【0125】

図47は、図44、45または46に例示する拡散層7をビット線19に対して傾け、平行四辺形に近い変形六角形に設けた平面レイアウト図の例である。本実施の形態では、拡散層7を変形六角形に形成することによって、図44、45または46の実施の形態より単位面積あたりのビット数を増加させることができる。ただし、レイアウトパターンに斜め形状を搭載することによって、拡散層7の露光プロセス等が複雑になる。

【0126】

(第十一の実施形態)

図48は、本発明のひとつの実施の形態にかかる半導体装置を示す平面レイアウト図である。

この図48は、第一の実施の形態におけるメモリ回路領域の構造について、代表的な素子構造を示している。特にプレート線117や、その他の配線等、下記の説明のために一部の配線等については記載を省略している。

【0127】

ワード線となるゲート電極8と列(Y)デコード線18が直交している。ビット線19は、列(Y)デコード線18と平行に形成されているが、容量コンタクト119とビット線コンタクト118を迂回するように一部斜めに形成されている。ただし、斜め部分は図48では第5層配線55の下になっているため図示されていない。また、本実施の形態では、ビット線3本に対して列デコード線1本の割合で配置しているが、このビット線19と列デコード線18の配置比は16:1や64:1など、さらに大きくなっていてもよい。

【0128】

拡散層7をビット線19に対して傾け、平行四辺形に近い変形六角形に形成するとともに、シリンダ形状の容量素子90の形状も変形六角形に形成することにより、本実施の形態においては、単位面積あたりのビット数を大きくすることが可能である。また、ワード線の抵抗を低減するための、いわゆるワード線裏打ち配線となる第5層配線55と、ワード線とのコンタクトをとるワード線コンタクト121をメモリ回路領域の外周に設けている。図48が平面図のため、図中のワード線コンタクト121は平面構造のみ示しているが、実施の形態における論理回路領域の様に第5層配線から第1層配線までのスタック形ビアを介して接続され、さらにその該第1層配線とゲート電極8上とをコンタクトプラグ4を介して接続されている。ワード線コンタクト121は一定のビット線毎に形成され、16本のビット線毎から、256本毎、512本毎等、メモリ回路領域の外周に形成されている。

【0129】

なお、当然ながら、上述した実施の形態および複数の変形例は、その内容が相反しない範囲で組み合わせることができる。また、上述した実施の形態および変形例では、各部の構造などを具体的に説明したが、その構造などは本願発明を満足する範囲で各種に変更することができる。

【符号の説明】

【0130】

1 コンタクト層間絶縁膜

2 エッチストップ膜

3 コンタクトバリアメタル膜

4 コンタクトプラグ

5 シリコン基板

6 素子分離STI

7 拡散層

8 ゲート電極

9 MOSトランジスタ

11 第1層の層間絶縁膜

13 第1層配線バリアメタル膜

15 第1層配線

17 行デコード配線

18 列デコード配線

19 ビット線

20 第1層配線のキャップ膜

21 第2層の層間絶縁膜

23 第2層配線バリアメタル膜

25 第2層配線

30 第2層配線のキャップ膜

31 第3層の層間絶縁膜

33 第3層配線バリアメタル膜

35 第3層配線

40 第3層配線のキャップ膜

41 第4層の層間絶縁膜

43 第4層配線バリアメタル膜

45 第4層配線

50 第4層配線のキャップ膜

51 第5層の層間絶縁膜

53 第5層配線バリアメタル膜

54 ハードマスク絶縁膜

55 第5層配線

60 第5層配線のキャップ膜

61 第6層の層間絶縁膜

63 第6層配線バリアメタル膜

65 第6層配線

70 第6層配線のキャップ膜

71 第7層の層間絶縁膜

73 第7層配線バリアメタル膜

75 第7層配線

80 第7層配線のキャップ膜

81 シリンダ加工レジスト膜A

82 シリンダ加工レジスト膜B

83 シリンダ加工レジスト膜C

84 シリンダ加工マスク絶縁膜

88 容量素子開口部A

89 容量素子開口部B

90 容量素子

91 下部電極膜

92 容量絶縁膜

93 上部電極膜

94 ハードマスク絶縁膜

95 シリンダ加工レジスト膜

97 上部電極加工レジスト膜

98 容量素子開口部

101 従来のアドオン型のメモリ回路部

102 従来のアドオン型の論理回路部

103 多層配線部

104 リフトアップ配線部

105 ビルトイン型のメモリ回路部

106 ビルトイン型の論理回路部

111 リフトアップ絶縁膜A

112 リフトアップ配線プラグA

113 容量加工ストップ膜

114 リフトアップ絶縁膜B

115 リフトアップ配線プラグB

116 配線加工ストップ膜

117 プレート線

118 ビット線コンタクト

119 容量コンタクト

120 容量セルコンタクト

121 ワード線コンタクト

131 第3層の層間絶縁膜B

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

電子産業の集積回路分野の製造技術において、さらなる高集積化かつ高速化の要求が高まっている。また集積化の進展により、回路の規模が大きくなり、設計の難易度が増大している。

【0003】

同一半導体基板上に論理回路とメモリ回路を搭載する集積回路、いわゆる混載回路では、同一の基板上に論理回路とメモリ回路が存在することで、単に近距離にレイアウトが可能となることで集積化が向上するだけでなく、回路間の配線が短くなることで動作速度の向上も可能となるなどの特徴を持つ。

【0004】

しかしながら、同一の半導体基板上に容量素子を備えたメモリ回路と論理回路を搭載する際には、メモリ回路が有するデータの記憶に用いられる容量素子の形成のために、通常論理回路を形成する場合には用いられない構造を用いる必要がある。例えば、トレンチ型容量素子の場合では、半導体基板に数ミクロン以上の深い溝を形成し、そこに容量素子を形成する手法が報告されているが、素子の微細化に伴ってトレンチ開口径が小さくなるだけでなく、容量の確保のためにその深さは増す一方であり、その製造工程は非常に難易度が上昇している。

【0005】

一方、スタック型容量素子の場合でも、所望の容量を実現するためにスタック構造をフィン型や円筒(シリンダ)型を採用するなどしている。容量素子をビット線上に形成する、いわゆるCOB構造(Capacitor Over Bit line構造)では容量素子の容量を稼ぐために容量の高さを高くする必要がある。

【0006】

現在、容量素子の下部容量配線と上部容量配線との間に設けられている配線層が1層である半導体装置として各種の提案がある(例えば、特許文献3、特許文献4参照)。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007―201101号公報

【特許文献2】特開2004−342787号公報

【特許文献3】特開2000−003960号公報

【特許文献4】特開2005−101647号公報

【非特許文献】

【0008】

【非特許文献1】M.Ueki et .al、IEEE IEDM、 pp973−976(2007)

【発明の概要】

【発明が解決しようとする課題】

【0009】

スタック型構造で容量素子の高さを稼ぐことは、容量下部の配線と容量上部の配線の距離が遠くなることになる。これによって論理回路部では第1の配線層から拡散層に至るまでのコンタクトも高くなり、製造工程においてはその難易度が高くなるとともに、容量素子が形成されている層の電気抵抗、すなわち寄生抵抗も増大することから性能面でも動作速度の低下を招くことになる。

【0010】

さらに、上述の通り、メモリ回路と論理回路を同一の半導体基板上に形成する場合において論理回路を設計する際には、容量素子の形成を考慮して、寄生抵抗などを考慮した設計を行う必要がある。これは同じ論理回路を設計する場合でも、容量素子が同一の半導体基板上に存在するか否かによって、特に配線抵抗やその寄生容量の違いにより設計パラメーターを変更する必要があるということである。全く同じ回路であるにも関わらず、容量素子と同時形成するばかりに設計をやり直さなければならないだけでなく、場合によっては容量素子と混載したことによって回路の動作速度が低下したり、動作マージンが低下して動作しなくなったりする可能性がある。

【0011】

論理回路部のコンタクト高さを低減する提案の例としては、まず、特許文献1を挙げることができる。特許文献1では、容量素子の上部電極を、論理回路部に存在する配線と同一の高さに形成された上部容量配線で接続することによって、上部電極間を接続するためのプレート線とよばれる配線を形成するための専用の工程や専用の設備を必要とせず、同時に容量素子の上下膜厚の確保と論理回路部のコンタクト(ロジックコンタクト)のアスペクトが低減可能であることが示されている。

【0012】

特許文献1の提案ではコンタクト高さの低減は可能であるが、論理回路部のコンタクト高さの低減は配線高さ1層分と限定的である。この構造において容量素子の容量を向上させるためには、容量素子高さを高くすることが必要となるが、この場合、容量高さの増加に伴ってロジックコンタクト高さも増大する。したがって、コンタクト製造の難易度が上昇する上に、ロジックコンタクトの抵抗は増大する。また、論理回路部の多層配線材は銅を主成分とした銅配線であることが望ましいのに対して、銅配線材以外の配線、すなわち高抵抗のタングステン(W)配線が使用される。さらに、また、容量素子の存在によって容量素子の存在するその配線層の構造は通常の論理回路の配線構造とは異なっており、容量素子の存在する層ではロジックコンタクト高さが高く、抵抗も高くなっている。その結果、すべての配線層が低抵抗銅材で形成される通常の論理回路設計用パラメーターとは互換性のない、専用の設計パラメーターが必要となってしまう。

【0013】

特許文献2の提案では、コンタクト高さを低減するために第1層配線を容量素子の中間部に形成している。これにより特許文献1同様に論理回路部のコンタクト高さを低減可能である。しかし特許文献2の手法を用いたとしても論理回路部の構造は容量素子の構造に依存し、容量素子を備えない構造とは異なる構造になる。

【0014】

したがって、特許文献2の構造を用いても、論理回路の設計パラメーターについてはメモリ回路と混載時には専用の値を用いる必要がある。また、特許文献2の手法でも特許文献1と同様に、容量素子の容量を稼ぐためには層間絶縁膜を厚くして背丈の高い容量を形成する必要がある。また、メモリ回路側の配線をすべて銅配線としていないことから、論理回路側の多層配線をすべて銅配線とすることができていない。やはり特許文献1同様にコンタクト形成時の難易度の上昇や、コンタクト抵抗の増大が生じることになる。さらに、最先端の論理回路の多層配線では少なくとも下層に位置する狭ピッチのローカル配線にはSiOCH膜などの低誘電率層間絶縁膜が導入されている。低誘電率層間絶縁膜(Low−k膜)は耐熱性に限界があり、例えば成長温度の高いCVD−Wなどを用いたW配線などを適用することはできない。このため、論理回路側多層配線の全層をLow−k/Cu配線化することができない。その結果、すべての配線層がLow−k/Cu構造で構成される通常の論理回路設計用パラメーターとは互換性のない、専用の設計パラメーターが必要となってしまう。

【0015】

また、特許文献2で示されている実施の形態1あるいは実施の形態3においては、上部電極や上層配線の銅膜の直上にシリコン酸化膜からなる絶縁膜を形成した構造となっている。シリコン酸化膜は銅膜に対する拡散耐性が無いために、特許文献2の構造では銅(Cu)が絶縁膜中に拡散し、絶縁膜の信頼性が劣化する。

【0016】

また、シリコン酸化膜の成膜においては主に原料ガスの酸化によって成膜が行われることから、配線表面のCuが露出している状態で、シリコン酸化膜の成膜を行うと、Cuが酸化して配線抵抗の増大や、成膜されるシリコン酸化膜のとの密着性の低下や、それに伴う信頼性の劣化などが懸念される。以上のように、特許文献2ではエッチングストッパ膜を設ける必要がない利点が謳われているが、特許文献2の構造ではむしろ信頼性が劣化する欠点を抱えていると考えられる。

【0017】

以上の内容を図に示すと図33((a)、(b))のようになる。特許文献2に代表されるように、従来の技術ではメモリ回路部101は容量素子90の上に多層配線部103を付与したような構造(アドオン型)を有していた。そのため、論理回路部102では、容量を確保するために容量素子90の高さに応じて多層配線部103をリフトアップする配線部(リフトアップ配線部104)が必要となり、多層配線構造が厚くなることが問題であった。

【課題を解決するための手段】

【0018】

本発明によれば、半導体基板と、

前記半導体基板上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線構造と、

前記多層配線構造内に埋め込まれた、下部電極、容量絶縁膜、および上部電極により構成された容量素子と、を備え、

前記下部電極に接続した下部容量配線と、前記上部電極に接続した上部容量配線との間に、少なくとも2層以上の前記配線層が設けられたことを特徴とする半導体装置が提供される。

【発明の効果】

【0019】

容量素子が多層配線構造内に埋め込まれるとともに、この容量素子の下部容量配線と上部容量配線との間に少なくとも2層以上の配線層が設けられた構造により、容量素子の容量を確保しつつも、多層配線構造が厚くなることを抑えることができる。

【図面の簡単な説明】

【0020】

【図1】この発明の第一の実施形態の半導体装置を示す断面図である。

【図2】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図3】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図4】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図5】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図6】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図7】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図8】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図9】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図10】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図11】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図12】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図13】この発明の第一の実施形態の一例における半導体装置を示す断面図である。

【図14】この発明の第一の実施形態の一例における半導体装置を示す断面図である。

【図15】この発明の第二の実施形態の一例における半導体装置を示す断面図である。

【図16】この発明の第三の実施形態の一例における半導体装置を示す断面図である。

【図17】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図18】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図19】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図20】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図21】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図22】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図23】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図24】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図25】この発明の第三の実施形態の一例における半導体装置の製造工程断面図である。

【図26】この発明の第三の実施形態の一例における半導体装置を示す断面図である。

【図27】この発明の第四の実施形態の一例における半導体装置を示す断面図である。

【図28】この発明の第五の実施形態の一例における半導体装置を示す断面図である。

【図29】この発明の第六の実施形態の一例における半導体装置を示す断面図である。

【図30】この発明の第七の実施形態の一例における半導体装置を示す断面図である。

【図31】この発明の第七の実施形態の一例における半導体装置を示す断面図である。

【図32】この発明の第七の実施形態の一例における半導体装置を示す断面図である。

【図33】従来技術とこの発明の一例における半導体装置を比較する断面図である。

【図34】この発明の第八の実施形態の一例における半導体装置を示す断面図である。

【図35】この発明の第八の実施形態の一例における半導体装置を示す断面図である。

【図36】この発明の第九の実施形態の一例における半導体装置を示す断面図である。

【図37】図2に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図38】図3に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図39】図5に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図40】図6に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図41】図9に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図42】この発明の第一の実施形態の一例における半導体装置の製造工程断面図である。

【図43】図42に示すこの発明の第一の実施形態の一例における半導体装置の製造工程の平面レイアウト図である。

【図44】この発明の第十の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【図45】この発明の第十の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【図46】この発明の第十の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【図47】この発明の第十の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【図48】この発明の第十一の実施の形態の一例における半導体装置のレイアウトを示す平面図である。

【発明を実施するための形態】

【0021】

本発明の実施の一形態を詳細に説明する前に、本実施形態における用語の意味を説明する。

絶縁膜とは、例えば配線材を絶縁分離する膜(層間絶縁膜)であり、低誘電率絶縁膜とは、半導体素子を接続する多層配線間の容量を低減するため、シリコン酸化膜(比誘電率4.5)よりも比誘電率の低い材料を指す。特に、多孔質絶縁膜としては、例えば、シリコン酸化膜を多孔化して、比誘電率を小さくしたポーラスシリカ材料や、HSQ(ハイドロゲンシルセスキオキサン(Hydrogen Silsesquioxane))膜、もしくはSiOCH、SiOC(例えば、Black DiamondTM、AuroraTM)などを多孔化して、比誘電率を小さくした材料などがある。この絶縁膜として、これらの膜をさらに低誘電率化した膜を用いても良い。

【0022】

本実施の形態において、金属配線材およびコンタクトプラグ材とは、主にCuを主成分とする。金属配線材の信頼性を向上させるため、Cu以外の金属元素がCuからなる部材に含まれていても良く、Cu以外の金属元素がCuの上面や側面などに形成されていても良い。また一部の実施の形態においては、第1層目配線とシリコン基板上に形成されたMOSFETとを接続するコンタクトプラグ材は主にタングステン(W)を主成分としている。この場合、第1層目の配線とシリコン基板上に形成されたMOSFETとを絶縁分離するプレメタル絶縁膜(PMD)は耐熱性に優れるシリコン酸化膜となる。

【0023】

バリアメタル膜とは、配線あるいはコンタクトプラグを構成する金属元素が層間絶縁膜や下層へ拡散することを防止するために、配線の側面および底面を被覆する、銅の拡散に対してバリアとなる性質を有する導電性膜を示す。例えば、配線がCuを主成分とする金属元素からなる場合には、タンタル(Ta)、窒化タンタル(TaN)、チタン(Ti)、窒化チタン(TiN)、炭窒化タングステン(WCN)、ルテニウム(Ru)のような高融点金属やその窒化物等、またはそれらの積層膜が使用される。またタングステンを主成分に用いるコンタクトプラグのバリアメタルにも前記の金属膜が用いられる。

【0024】

ダマシン配線とは、あらかじめ形成された層間絶縁膜の溝に、金属配線材を埋め込み、溝内以外の余剰な金属を、例えばCMPなどにより除去することで形成される埋め込み配線をさす。Cuによりダマシン配線を形成する場合には、Cu配線の側面および外周をバリアメタルで覆い、Cu配線の上面を、銅拡散耐性(Cuバリア性)を持つ絶縁性バリア膜(キャップ膜とも呼ぶ)で覆う配線構造が一般に用いられる。

【0025】

CMP(Chemical Mechanical Polishing)法とは、多層配線形成プロセス中に生じるウェハ表面の凹凸を、研磨液をウェハ表面に流しながら回転させた研磨パッドに接触させて研磨することによって平坦化する方法である。ダマシン法による配線形成においては、特に、配線溝あるいはビアホールに対し金属を埋設した後に、余剰の金属部分を除去し、平坦な配線表面を得るために用いる。

【0026】

半導体基板とは、半導体装置が構成された基板であり、特に単結晶シリコン基板上に作られたものだけでなく、SOI(Silicon on Insulator)基板やTFT(Thin film transistor)、液晶製造用基板などの基板も含む。

【0027】

ハードマスクとは、層間絶縁膜の低誘電率化による機械的強度低下やプロセス耐性の低下により、直接プラズマエッチングやCMPを行うことが困難な場合に、層間絶縁膜上に積層し、保護する役割を果たす絶縁膜をさす。

【0028】

プラズマCVD法とは、例えば、気体状の原料を減圧下の反応室に連続的に供給し、プラズマエネルギーによって、分子を励起状態にし、気相反応、あるいは基板表面反応などによって基板上に連続膜を形成する手法である。

【0029】

PVD法とは、通常のスパッタリング法のほか、埋め込み特性の向上や、膜質の向上や、膜厚のウェハ面内均一性を図った、例えばロングスロースパッタリング法やコリメートスパッタリング法、イオナイズドスパッタリング法、などの指向性の高いスパッタリング法を含む手法である。合金をスパッタする場合には、あらかじめ金属ターゲット内に主成分以外の金属を固溶限以下で含有させることで、成膜された金属膜を合金膜とすることができる。本発明中では、主にダマシンCu配線を形成する際のCuシード層や、バリアメタル層を形成する際に使用することができる。

【0030】

(第一の実施形態)

本発明の実施の一形態について図面を参照して以下に説明する。ただし、本実施の形態に関して前述した一従来例と同一の部分は、同一の名称を使用して詳細な説明は省略する。

本実施形態の半導体装置は、半導体基板(シリコン基板5)と、シリコン基板5に形成され、配線(第3層配線35、第4層配線45、第5層配線55、第6層配線65)および絶縁膜(第3層の層間絶縁膜31、第4層の層間絶縁膜41、第5層の層間絶縁膜51、第6層の層間絶縁膜61)により構成された配線層(第3層配線35と第3層の層間絶縁膜31、第4層配線45と第4層の層間絶縁膜41、第5層配線55と第5層の層間絶縁膜51、第6層配線65と第6層の層間絶縁膜61)が複数積層された多層配線構造と、この多層配線構造内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜(容量絶縁膜92)、および上部電極(上部電極膜93)により構成された容量素子90と、を備えるものである。さらに、本実施形態の半導体装置は、下部電極膜91に接続した下部容量配線(第2層配線25)と、上部電極膜93に接続した上部容量配線(プレート線配線として第5層配線55)との間に、少なくとも2層以上の前記配線層(第3層配線35と第3層の層間絶縁膜31、第4層配線45と第4層の層間絶縁膜41、第5層配線55と第5層の層間絶縁膜51)が設けられたことを特徴とするものである。

【0031】

図1は、本発明のひとつの実施の形態の半導体装置を示す断面図であり、図2〜図12、図42は、図1の半導体装置の製造方法を工程順に示す断面図の例である。図1の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面である。また右側(c)は論理回路領域の代表的な断面図を示す。図2〜12、図42のいずれも図の左側(a)はメモリ回路領域、右側(b)は論理回路領域の代表的な断面図を示す。また図37〜図41、図43は、それぞれ図2、図3、図5、図6、図9および図42中(a)の上面図(平面レイアウト図)である。また図13および図14についても左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

【0032】

多層配線構造は、例えば第3層配線35および第3層の層間絶縁膜31により構成された配線層、第4層配線45および第4層の層間絶縁膜41により構成された配線層、第5層配線55および第5層の層間絶縁膜51により構成された配線層、第6層配線65および第6層の層間絶縁膜61により構成された配線層が積層された構造を有する。多層配線構造は、さらに異なる配線層が積層されてもよい。本実施形態では、この多層配線構造は、一般的な論理回路領域の多層配線構造を表すものである。この論理回路領域の多層配線構造では、上層に位置する多層配線層を構成する各配線層や配線の厚さは、下層に位置する多層配線層よりも厚いことが一般的であるが、本実施形態では、多層配線層を構成する各配線層や配線の厚さは特に限定されない。従来のように、一部または全部の配線層の各配線層や配線の厚さが同じでもよく、下層から上層に向かって配線層の各配線層や配線の厚さが厚くなってもよい。

または、少なくとも容量素子が設けられた領域の、配線層の高さ(厚み)が全て同じであり配線の高さ(厚み)が全て同じであってもよい。つまり、容量素子90が埋め込まれた領域においては、例えば第3層配線35、第4層配線45および第5層配線55の配線の厚みが同じであり、これらの配線が設けられた第3の配線層、第4の配線層、および第5の配線層の厚みが同じであればよい。さらに、容量素子90が埋め込まれていない領域の配線層や配線の厚さは、容量素子90が埋め込まれた領域の配線層や配線の厚さが同じでもよく、または異なっていてもよい。本実施形態では、図1に示すように、第2層配線25、第3層配線35、・・・第6層配線65の配線の厚さが同じかつ、これらが設けられた配線層の厚さも同じである。本実施形態では、配線および配線層の厚さ(厚み)は、シリコン基板5の法線方向の厚さを表すものとする。

【0033】

この多層配線構造おいて、メモリ回路領域と論理回路領域との配線層は同層に設けられているものである。つまり、メモリ回路領域の第3層配線層、・・・第5層配線層と論理回路領域の第3層配線層、・・・第5層配線層とは同層になる。本実施形態では、このメモリ回路領域の多層配線構造内に容量素子90が埋め込まれているものである。さらに、容量素子90は少なくとも2層以上の配線層にわたって設けられているため、この多層配線構造の配線層数を変えずに、容量素子90が貫く配線層数を変化させて所望の容量を得ることができる。また、上述のとおり、容量素子90が埋め込まれたメモリ回路領域の多層配線と論理回路領域の多層配線は同層に形成される。このため、新たに論理回路領域の多層配線を設ける必要がない。これにより、多層配線構造をコンパクトに設けることができる。

【0034】

図1に示すとおり、多層配線構造内に容量素子90が埋め込まれたことにより、下部電極膜91が、上から第5層の層間絶縁膜51、第4層の層間絶縁膜41、第3層の層間絶縁膜31を貫通するように設けられており、この多層配線構造内に凹部が形成されている。この凹部の底面および側面上に接するように容量絶縁膜92が形成されている。さらに、この容量絶縁膜92上に接するように上部電極膜93が形成されている。下部電極膜91、容量絶縁膜92および上部電極膜93をこのように設けることで、これらにより構成した容量素子90を多層配線構造内に設けることができる。また、容量素子90が多層配線構造内に埋め込まれたため、図1に示すとおり、容量素子90の上部電極膜93が設けられた第5層の層間絶縁膜51には、この上部電極膜93上に、上部電極膜93に接続した上部容量配線として第5層配線55が設けられている。

容量素子90が多層配線構造内に埋め込まれる位置には、下部容量配線(第2層配線25)と、上部容量配線(プレート線配線として第5層配線55)との間に、少なくとも2層以上の配線層が設けられている限り、特に限定されない。容量素子90は、最も微細化が進んでいる下層に位置する多層配線層に形成してもよい。

【0035】

さらに、図1に示す通り、容量素子90が設けられたメモリ回路領域の容量素子90が多層配線構造内に埋め込まれており、この多層配線構造において、本実施の形態では、列デコード配線18が下部容量配線の上層に形成されている。行デコード配線17もしくは列デコード配線18のいずれかもしくは両方が、容量素子90と同層に設けられているか、もしくは、下部容量配線と同層に設けることにより、上層配線を利用する必要がなくなり、メモリ回路領域の配線層数を減ずることができる。これによってメモリ回路領域の上層は論理回路領域の配線のために用いたり、各回路領域間を接続するために用いたりすることが可能となり、チップ面積を縮小することが可能になる。

なお、この多層配線構造において、例えば第3配線層と第4配線層などの異なる配線層の厚みを同一にしてもよい。また、容量素子90が設けられたメモリ回路領域の配線層の厚みと、容量素子90が設けられていない論理回路領域と配線層の厚みとを同一にすることができる。また、多層配線構造の配線層の厚みを変えずに、容量素子90を多層配線構造内に埋め込むことができる。これにより、多層配線構造の配線層を厚くせずに、容量素子90が貫く配線層により、容量素子90の所望の容量を得ることができる。

【0036】

つぎに本実施形態の半導体装置の製造方法について説明する。

図2では、標準的な集積回路の形成方法を用いて作成した、MOSトランジスタ9および第2層配線25形成後の構造を有する基板を示す。

本実施形態の半導体装置は、さらに、シリコン基板5の表面近傍に形成された第一の拡散層(拡散層7)と、シリコン基板5の表面近傍に形成された第二の拡散層(拡散層7)と、第一の拡散層(拡散層7)と第二の拡散層(拡散層7)との間のシリコン基板5に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極8と、を備える。そして、本実施形態の半導体装置は、これらのシリコン基板5、第一の拡散層(拡散層7)、第二の拡散層(拡散層7)、ゲート絶縁膜、およびゲート電極8により電界効果トランジスタ(MOSトランジスタ9)を構成するものである。

シリコン基板5上に形成されるMOSトランジスタ9のゲート絶縁膜は、高誘電率ゲート絶縁膜であればよい。例えば高誘電率ゲート絶縁膜として、SiONなどシリコン酸窒化物あるいはHf酸窒化物などのHfを含む高誘電率ゲート絶縁膜などを用いることができる。具体的には、Hf酸化物、Hfシリケート、およびHf酸化物またはHfシリケートに窒素が導入された高誘電率絶縁膜を用いることができる。ゲート絶縁膜は、単層またはこの種類で構成された多層でもよい。

またゲート電極材としてはポリシリコンあるいはその上面層がNi、Co、Ti、Ptなど金属シリサイドで覆われされたものである。さらには、ゲート電極の一部にTi、Ta、Alあるいはそれらの導電性窒化物を含むメタルゲート電極であってもよい。特に、メタルゲート電極の場合、ロジック部のトランジスタの駆動電流を向上させるといった効果のみならず、メタルゲート電極はDRAM部のワード線を構成しているので、このワード線の抵抗を低減する効果もあり、多層配線層に容量素子部を埋め込んだeDRAM構造と組み合わせることで、より高速動作が可能となる。

【0037】

MOSトランジスタ9は、N型またはP型いずれでもよい。また、N型トランジスタとP型トランジスタとは同一のシリコン基板5上に形成されてもよい。図2に示す拡散層7は、第一の拡散層および第二の拡散層を表し、第一の拡散層および第二の拡散層の一方はソース拡散層であり、他方はドレイン拡散層である。

なお図2において、1はコンタクト層間絶縁膜、2はエッチストップ膜、3はコンタクトバリアメタル膜、4はコンタクトプラグ、5はシリコン(Si)基板,6は素子分離STI(shallow trench isolation)、7は拡散層、8はゲート電極である。また、11は第1層の層間絶縁膜であり、13は第1層配線バリアメタル膜、15は第1層配線、20は第1層配線のキャップ膜、23は第2層配線バリアメタル膜、25は第2層配線、30は第2層配線のキャップ膜、である。また、ビット線19は第1層配線15と同時に形成されるが、メモリ回路部におけるビット線である。

【0038】

さらに、ここでビット線19は第1層配線15と同一層に形成されており、特許文献2などに見られるような、ビット線だけの配線層は存在しない。本実施形態に示す構造により、多層配線構造は層数を有効に活用可能である。

【0039】

図2ではコンタクト層間絶縁膜1はシリコン酸化膜からなり、コンタクトプラグ4はタングステンからなり、コンタクトバリアメタル膜3は窒化チタン/チタンの積層膜からなる。また、第1層の層間絶縁膜11および第2層の層間絶縁膜21は低誘電率絶縁膜でありSiOCH膜、より具体的にはMPS(Molecular Pore Stack)膜からなる。MPS膜の詳細については非特許文献1に記載されている。第1層配線バリアメタル膜13はタンタル/窒化タンタル積層膜からなり、第1層配線は銅からなる。また、第1層配線のキャップ膜20および第2層配線のキャップ膜30はSCC(Silica amorphous Carbon Composite)膜からなる。このSCC膜についても、MPS膜と同様に非特許文献1に詳細が記載されている。

【0040】

MPS膜とSCC膜について以下に簡単に記載する。MPS膜は、6員環の環状シロキサンを主骨格とし、有機基を官能基に持った有機シロキサンを原料として成膜する。シリコン原子に結合する有機官能基は不飽和炭化水素基とアルキル基である。SCC膜は、不飽和炭化水素基、アルコキシ基、アルキル基がそれぞれ、シリコン原子に直接結合した有機シラン原料を用いて成膜される。膜の構造としてはアモルファスカーボン構造と不飽和炭化水素結合が膜中に含まれることが特徴である。MPS膜とSCC膜のいずれの原料においても前記不飽和炭化水素基としては、ビニル基、プロペニル基、イソプロペニル基、1−メチル−プロペニル基、2−メチル−プロペニル基、1,2−ジメチル−プロペニル基などが挙げられる。特に好ましい不飽和炭化水素基は、ビニル基である。またMPS膜とSCC膜のいずれの原料においても前記アルコキシ基はアルキル基が酸素原子に結合した構造である。前記シリコン原子に直接結合するアルキル基、および前記アルコキシ基を構成するアルキル基としては、メチル基、エチル基、プロピル基、イソプロピル基、ブチル基、イソブチル基、sec−ブチル基、tert−ブチル基などが挙げられる。またMPS膜原料のシリコンに結合するアルキル基としては、イソプロピル基、イソブチル基、tert−ブチル基など、空間的に嵩高く、立体障害基として機能する官能基が好ましい。特に、より好ましい官能基の一つはイソプロピル基である。すなわち、トリイソプロピルトリビニルトリシクロシロキサンである。さらにSCC膜原料のシリコンに結合するアルコキシ基、アルキル基として、より好ましいのはメトキシ基とイソプロピル基である。すなわちイソプロピルジメトキシビニルシロキサンとなる。これらの原料を用いることでMPS膜では膜中に非常に微細な(主に0.5nm以下の)空孔構造が導入されることが特徴となる。またSCC膜は、SiOCH膜の一種でありながら、銅拡散耐性を持つことが特徴である。さらに比誘電率が3.1程度でありながら、機械強度が20GPa程度と高いことも特徴である。また、表面反応が強い成膜モードで成膜されるために、段差被覆性も良好である。これらの膜は一般的に知られているSiOCH膜に比べて炭素組成が高いことが特徴である。シリコン/酸素/炭素の元素比は、Siを基準とすると、SiOCH膜に対し、SCC膜で炭素が約2倍程度、MPS膜では4倍程度の炭素が含まれている。相対的に酸素の元素比が一般的なSiOCH膜に比較して少なく、SCC膜で3/4程度、MPS膜では1/2程度である。これはこれらの膜が、原料をプラズマ中で解離・活性化させるプラズマCVDではなく、プラズマ重合反応により成膜することでシリカ骨格を保持したまま不飽和炭化水素を優先的に活性化させ、絶縁膜の化学構造を制御することが容易となることから実現される。このMPSとSCC膜の組成の差が、容量開口部の加工形成においては重要なポイントとなる。

【0041】

第2層配線25を形成する手法について簡単に記載する。第1層配線15を形成し、SCC膜からなる第1層配線のキャップ膜20を成膜した後に、第2層の層間絶縁膜21として前記MPS膜を成膜する。引き続き加工時のマスクとしてシリコン酸化膜(図示せず)を成膜する。さらにリソグラフィとドライエッチングを用いたいわゆるデュアルダマシンプロセスによって第2層配線の開口部を形成する。このとき開口部の一部は第1層配線15に電気的に接続するためのビアホールを含んでいる。これらの開口部にスパッタリング法によって第2層配線バリアメタル膜23を堆積し、引き続いて銅めっきのシード層となる銅を堆積する。さらにめっき法によって銅を埋め込む。ここで用いる銅にはアルミニウムや銀などの金属の添加物を含んでいてもよい。この第2層配線の開口部にバリアメタル膜23と銅が残るように余分なバリアメタル膜と銅をCMPなどの手法を用いて除去し、第2層配線25を形成する。この工程中に前記シリコン酸化膜は除去され、第2層の層間絶縁膜21上には残らない。その後、第1層と同様にSCC膜からなる第2層配線のキャップ膜30を成膜する。ここで、容量素子の開口部以外の容量絶縁膜の下部に部分的にシリコン酸化膜が設けられていてもよい。以後の工程で、この第2層配線の開口部と同等にして、第3層配線の開口部、・・・第6層配線の開口部を形成することができる。図1に示す第3層配線バリアメタル膜33、第4層配線バリアメタル膜43、第5層配線バリアメタル膜53および第6層配線バリアメタル膜63は、第1層配線バリアメタル膜13または第2層配線バリアメタル膜23と同様にして形成できる。図1に示す第5層配線のキャップ膜60および第6層配線のキャップ膜70は、第2層配線のキャップ膜30と同様にして形成できる。

【0042】

本実施の形態では層間絶縁膜およびキャップ膜は単層の絶縁膜を用いているが、それぞれ、複数種の絶縁膜の積層構造でもよい。たとえば、層間絶縁膜はMPS膜と他のSiOCH膜、キャップ膜はSiC膜とSiCN膜の積層構造などでもよい。なお、図37は、第2層配線のキャップ膜30を成膜する前の平面レイアウトを示す。図37に示すように、デコード線18、第2層の層間絶縁膜21、第2層配線25が同層に設けられている。

【0043】

さらに図3には、第3層配線35および第4層配線45を形成する。形成方法は第2層配線25と同様である。ここでは後にメモリ回路領域には容量素子を形成するため、論理回路領域のみに配線層を形成する。本実施の形態では容量素子の高さを論理回路部の3層分よりは低い場合を示しているが、4層分より低い場合とする場合にはさらに論理回路部を1層多く形成する。なお、図38は、第4層配線のキャップ膜50を成膜する前の平面レイアウトを示す。図38に示すように、第4層の層間絶縁膜41、第4層配線45が同層に設けられている。

【0044】

次に図4のように第4層配線のキャップ膜50を堆積した後に、ハードマスク絶縁膜94を成膜する。さらにシリンダ加工レジスト膜95をリソグラフィによって形成する。

【0045】

ここでハードマスク絶縁膜94はシリコン酸化膜を用いたが、他の絶縁膜との積層構造でもよい。またレジスト膜との間に反射防止膜を備えるなどの多層構造としてもよい。いずれの場合も容量素子形成過程で第4層配線のキャップ膜50を保護する効果をもつ絶縁膜であることが好ましい。具体的には、シリコン酸化膜のほか、シリコン窒化膜、シリコン酸窒化膜などが挙げられる。

【0046】

引き続いて図5に示すようにドライエッチングによって容量素子開口部98を形成する。このとき、第2層配線の酸化を防止するため、第2層配線のキャップ膜30はエッチングしない。なお、図39は図5(a)における平面レイアウト図を示す。図39では、全面がシリンダ加工レジスト膜95となっており、容量素子となる容量素子開口部98の中に、第2層配線のキャップ膜30が設けられている。本実施の形態のように、シリンダ形状の容量素子90を矩形に形成することによって、光近接効果補正を含めた露光や、ドライエッチング加工などの形成プロセスが容易となる。特に32nmや28nm技術世代以降において、光近接効果補正は複雑になっており、各要素パターンを単純な矩形あるいは直線形状で形成することは、面積あたりのビット密度を向上させるため、あるいは設計通りの形状を得るためには非常に効果的である。

【0047】

容量素子開口部98の形成時には、ドライエッチングによって層間絶縁膜とキャップ膜を交互にエッチングを行うが、本実施の形態では、層間絶縁膜にMPS膜をキャップ膜にSCCを用いており、SiOCH膜が積層された構造となっている。先に述べた通り、この2つの膜は炭素の組成が大きく異なっており、ドライエッチングによる加工条件を工夫することにより、MPS/SCC膜のエッチングレートの比、いわゆるエッチング選択比を制御することが容易である。したがって、層間絶縁膜であるMPSをエッチングしながら、キャップ膜であるSCC膜のエッチング選択比を小さくして、容量素子開口部98を深く開口したり、反対にMPS/SCCの選択比を大きくして、シリンダ開口部底でエッチングを止めたりすることが出来る。層間絶縁膜はエッチングするが、キャップ膜のエッチング速度を相対的に著しく小さくしたりすることが可能である。つまりは炭素の存在によってエッチング速度が変化する条件と変化しない条件を選ぶことができる。こうした加工の自由度が高い構造を用いることにより、良好な容量素子開口部98の形状を得ることができる。ここで、キャップ絶縁膜と低誘電率SiOCH膜とのそれぞれの炭素/シリコン比を、キャップ絶縁膜(C/Si)、低誘電率SiOCH膜(C/Si)としたとき、例えばキャップ絶縁膜(C/Si)/低誘電率SiOCH膜(C/Si)<2とする。

【0048】

さらにシリンダ加工レジスト膜をアッシングにより除去し、容量素子の下部電極を下層の配線となる第2層配線25に接続するため、第2層配線のキャップ膜30をドライエッチングによってエッチバックする(図6)。なお、図40は図6(a)における平面レイアウト図であり、全面がハードマスク絶縁膜94となっており、容量素子となる容量素子開口部98の中に、第2層の層間絶縁膜21、第2層配線25が設けられている。

【0049】

引き続いて容量素子の下部電極となる下部電極膜91を成膜し、さらにリソグラフィによって下部電極加工レジスト膜(図示せず)を形成する。この下部電極加工レジスト膜をマスクにして下部電極膜91をエッチバック、さらにアッシングによって下部電極加工レジスト膜を除去した(図7)。さらに、下部容量配線と下部容量配線が設けられた配線層の配線との上面が同一の平面となるようにこの下部容量配線を設けても良い。

【0050】

さらに引き続いて、容量絶縁膜92と上部電極膜93を成膜し、この加工のマスクとなる上部電極加工レジスト膜97をリソグラフィによって形成する。上部電極加工レジスト膜97をマスクにドライエッチングによって容量絶縁膜92と上部電極膜93をエッチングする。このとき、均一性確保のためオーバーエッチングを行うが、これによって、ハードマスク絶縁膜94の一部がエッチングされる(図8)。さらに、上部容量配線と上部容量配線が設けられた配線層の配線との上面が同一の平面となるようにこの上部容量配線を設けても良い。

ここで容量素子90に用いる材料としては、上部電極膜93及び下部電極膜91には、Ti、TiN、Ta、TaN、Ruまたはこれらの積層構造等が挙げられる。また、容量絶縁膜92としては二酸化ジルコニウム(ZrO2)やジルコニウムアルミネート(ZrAlOx)、二酸化ジルコニウムにTb、Er、Ybなどのランタノイドを添加した膜などが挙げられる。

【0051】

このハードマスク絶縁膜94は上述のアッシングおよびエッチングの工程において、特に論理回路部のハードマスク膜の下層に存在するキャップ膜、ひいてはさらにその下層にある銅配線を保護する役目を担っている。特に層間絶縁膜やキャップ膜が酸素プラズマや容量膜のエッチングプロセス耐性が無い場合には、ハードマスク膜の存在がないと、論理回路部の銅配線が酸化するなどにより、抵抗の上昇や信頼性の劣化が起こり、論理回路部の性能劣化や動作不良を引き起こすことになる。

【0052】

次に、下部電極加工の際と同様にアッシングによって上部電極加工レジスト膜97を除去する。さらに上部電極をマスクとして、ハードマスク絶縁膜94をエッチバックし、第4層配線のキャップ膜50を露出させる(図9)。これにより、ハードマスク絶縁膜94は容量膜と上部電極が存在する領域のみに残存するのみとなる。なお、図41は図9(a)における平面レイアウト図であり、メモリ回路領域のほぼ全面が上部電極膜93となっており、容量素子となる容量素子開口部98と、容量素子が存在しない領域では第4層配線のキャップ膜50が設けられている。

【0053】

前記ハードマスク絶縁膜94の一部が容量膜と上部電極が存在する領域に一部残存する構造は、本実施の形態のように容量素子90を多層配線中に埋め込み、かつ、多層配線の層間絶縁膜を低誘電率膜とした場合には非常に好ましい構造であり、本実施の形態のプロセスによって多層配線中に容量素子90を形成する場合には、必ず前記領域にハードマスク絶縁膜94が残存することになる。

【0054】

その後、第5層の層間絶縁膜51を成膜する(図10)。この際、メモリ回路部では容量素子90の存在によって、論理回路部との間に段差が生じるため、これをCMPなどの手法によって平坦化を行う。また、シリンダ開口部への絶縁膜の埋設が困難な場合には埋設性に優れる層間絶縁膜を用いて容量素子開口部98を埋設した後に、エッチバックを行い、開口部のみに層間絶縁膜を形成したのちに、第5層の層間絶縁膜51を成膜してもよい。その後、第5層配線の開口部を形成するためのマスクに用いるハードマスク絶縁膜54を成膜する(図11)。

以後の形成プロセスは、第2層配線25を形成するときの手法と同様に行うことにより、第5層配線55を形成する(図12)。さらに第5層配線55の形成後、第5層配線のキャップ膜60を形成する(図12)。このとき、メモリ回路部においては、上部電極が配線溝加工時のストッパとして機能し、溝深さが制限されるとともに、上部電極に直接接続される上部容量配線(メモリ回路領域に形成された第5層配線55)が同時に形成される。プレート線配線として上部容量配線が上部電極に直接接続された構造が得られる。これはプレート線配線として容量素子間を接続するだけでなく、その素子間の電気抵抗低減を実現する。またプレート線配線(メモリ回路領域に形成された第5層配線55)は図42(a)では奥行き方向に配線が延びているようにのみ記載しているが、実際にはメモリ回路領域内の平面において、メッシュ上の配線形状となっていてもよい(図43)。このように、本実施形態では、上部電極上に直接プレート線配線が形成されるような構造が得られる。さらに第6層配線65を同様に形成し、引き続いて上層配線を形成し、半導体集積回路を完成させる(図1)。

【0055】

本実施形態の効果について説明する。以上のように、メモリ回路部の容量素子を多層配線構造に埋め込み、かつ容量素子の構造に多層配線の複数層以上の高さを確保することで、微細化されても多層配線の構造を変更することなく、容量素子の容量を確保することが容易となる。具体的には、本実施の形態では、容量素子の高さを論理回路部の2層分より高い場合を示しているが、微細化に伴って容量値が不足する場合は、さらに1層増やし、3層分よりは高い構造とすることができ、このとき論理回路部の多層配線構造は変更する必要がない。

【0056】

さらに本実施の形態では、論理回路部の性能を重視し、配線抵抗低減のため、少なくとも容量素子が形成された領域の配線層のすべての配線が、銅を主成分とする配線材料で構成されることが望ましく、より好ましくは、配線層のすべての配線が、銅を主成分とする配線材料で構成されることである。上述のとおり、銅にはアルミニウムや銀などの金属の添加物を含んでいてもよい。

配線抵抗低減のためには、少なくとも容量素子が埋め込まれている多層配線(第2層配線25、第3層配線35、第4層配線45)に用いられている配線材料は銅であればよい。より好ましくは配線層(第1の層配層から第6の層配層)全てに銅配線を用いることが望ましい(ただし、いわゆるパッドAl層は除く)。本実施の形態では、図1に示すように、第1層配線15から第6層配線65まで全ての配線層を銅配線としている。本実施の形態の様な、メモリ回路部と論理回路部が同一の半導体基板上に集積されたいわゆるメモリ混載型のLSIの論理回路部の設計において、メモリ回路部が混載されていない一般の論理LSIの設計と同一のパラメーターを用いることができる。これにより、メモリ回路部を混載するLSIの論理回路部専用の設計が不要となる。

【0057】

このように、本実施形態によれば、容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することができる。それにより、メモリ回路と論理回路を同一の半導体基板上に形成した場合においても、設計時の論理回路の設計パラメーターを容量素子の有無に関わらず互換性のある値を使用可能とすることで、容量素子が同一基板上に存在する集積回路においても、設計が容易となる。

また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保するとともに、論理回路部のトランジスタの拡散層から第1配線層までの距離を従来に比べて大幅に低減し、その形成を容易にし、同時に抵抗を低減することで、トランジスタの寄生抵抗が小さく、高速動作が可能となる。

さらに、メモリ回路部および論理回路部に共通して低抵抗かつ低寄生容量のLow−k/Cu配線を適用することが可能となることで、容量素子を有するメモリ回路部を混載したとしても論理回路部の性能劣化は一切なくなる。

【0058】

さらに、容量素子の上部電極を、論理回路部に存在する配線と同一の高さに形成された上部容量配線で接続することによって、上部電極間を接続するためのプレート線とよばれる配線を形成するための専用の工程や専用の設備を必要とせず、同時に容量素子の上下膜厚の確保と論理回路部のコンタクト(ロジックコンタクト)のアスペクトが低減可能である。また、下部容量配線と下部容量配線が設けられた配線層の配線との上面が同一の平面となるようにこの下部容量配線を設けても同様の効果が得られる。さらに、容量素子の開口部以外の容量絶縁膜の下部に部分的にシリコン酸化膜を設けることにより、容量素子形成中に論理回路部のシリコン酸化膜の下層に存在するキャップ膜、ひいてはさらにその下層にある銅配線および層間絶縁膜を保護する役目を担わせることができる。シリコン酸化膜の存在により、論理回路部の銅配線が酸化するなどによる抵抗の上昇や信頼性の劣化を防止し、論理回路部の性能劣化や動作不良を抑制することができる。

容量素子は、本実施形態に記載したように、最も微細化が進んでいる下層に位置する多層配線層に形成することが有効である。下層に位置する多層配線層を構成する配線層および配線の厚さは同一であることが一般的である。これは、配線の特性が各層で同等となり、混載されるロジック側の回路設計を容易ならしめるといった効果があるためである。但し、本実施形態の趣旨は、少なくとも2層以上にわたる多層配線層に容量素子が埋め込まれていることであり、その配線層や配線の厚さが同一であることを必要不可欠としているわけではない。第一の実施形態の変形例として、例えば後述する図32に示すように下層に位置する多層配線の上に位置する上層多層配線層(グローバル配線)に容量素子の上部の一部が形成されていてもよい。一般に該上層多層配線層を構成する各配線層や配線の厚さは、前記下層に位置する多層配線層よりも厚いことが一般である。

【0059】

ところで、特許文献2記載の内容を図に示すと図33((a)、(b))のようになる。図33に示す、111はリフトアップ絶縁膜A、112はリフトアップ配線プラグA、113は容量加工ストップ膜、114は、リフトアップ絶縁膜B、115はリフトアップ配線プラグB、116は、配線加工ストップ膜、117はプレート線を表す。特許文献2ではメモリ回路部101には容量素子90の上に多層配線部103を付与したような構造(アドオン型)になっており、論理回路部102では、容量素子90の高さに応じて多層配線部103をリフトアップする配線部(リフトアップ配線部104)が必要となっていた。このリフトアップ配線部104は、そのアスペクト比の高さから形成が困難なだけでなく、抵抗が高い。これはアドオン型論理回路部102の設計パラメーターがリフトアップ配線部104の存在によって、その存在が無い場合の設計パラメーターと大きく解離することとなるだけでなく、アドオン型論理回路部102の性能が劣化する。これらは微細化の進展によりさらに難易度が増すことになる。

【0060】

これに対して、本実施形態では、これらのメモリ回路部および論理回路部の構造を、図33((c)、(d))に示すような、容量素子90を多層配線構造に埋め込んだ、ビルトイン型構造のメモリ回路部105および論理回路部106とすることで、容量素子の高さは多層配線を貫く層数を変化させることで容量の確保が可能となり、かつ、ビルトイン型の論理回路部106は容量素子90の存在によって設計パラメーターが変化することが無い。すなわち、同一半導体基板上にビルトイン型のメモリ回路部105が存在していても、論理回路部の多層配線の構造・材料にはまったく変化を及ぼさないことから、論理回路部のみの場合と完全に互換性のある設計パラメーターを用いることが可能となる。別な言い方をすれば、容量素子を有するメモリ回路部と論理回路部からなる混載回路チップにおいて、通常の論理回路部のみの論理回路チップとまったく同等の論理演算能力を維持しつつ高速メモリ機能を発現させることができる。

【0061】

また、前記のように、本形態では、層間絶縁膜にMPS膜をキャップ膜にSCCを用いているが、図13に示すように、層間絶縁膜にBlack DiamondTM、のようなSiOCH膜を、キャップ膜にSiCN膜を採用してもよい。この場合、これらの膜組成は窒素の存在の有無が異なることから、容量素子90の開口部の形成においては、その点を考慮した加工条件を採用する必要がある。

あるいは、図14に示すようにプレート線配線(メモリ回路領域に形成された第5層配線55)をメモリ回路領域において、配線形状ではなくパッド上の形状、つまり超幅広配線のようになっていてもよい。また、ところどころにスリットを介在させたスリット入り幅広配線形状となっていてもよい。

【0062】

(第二の実施形態)

図15は、本発明のひとつの実施の形態の半導体装置を示す断面図である。図15の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

第一の実施形態の構造からさらに、コンタクトプラグ4に銅を採用し、さらに第1層配線15とデュアルダマシン形状(デュアルダマシンコンタクト形状)を形成する事により、さらに拡散層から第1層配線15までの抵抗を低減した構造とすることが可能である。この際、コンタクト層間絶縁膜1は図2のようにシリコン酸化膜とすることも可能であるが、ここでは第1層配線15と同一の層間絶縁膜としている。あるいはコンタクト層間絶縁膜1には第1層とは異なる別の種類の低誘電率SiOCH膜を用いても良い。また異種の低誘電率SiOCH膜の積層構造としてもよい。コンタクト層間絶縁膜1には、Cu拡散バリア耐性を持つ膜、例えば、前記SCC膜を用いることが望ましい。積層構造を用いる場合には、最下層、つまりはエッチストップ膜直上に用いることが望ましい。

【0063】

特にSCC膜はプラズマ重合法で成膜されることから、通常のプラズマCVD法による層間絶縁膜よりも段差被覆性に優れており、エッチストップ膜成膜後の半導体基板のようにゲートの存在による凹凸上に成膜する際にも、良好な埋設性が得られる。

【0064】

また、本実施の形態では、コンタクトプラグ4の材料にも銅を採用しており、コンタクトプラグ4を含めたプラグおよびビアを含めた配線金属全て(ただし、いわゆるパッドAl層は除く)に銅を用いることで、低抵抗化を実現しており、非常に好ましい形態の一つである。

【0065】

さらに、本実施の形態の構造におけるコンタクトプラグ4のコンタクトバリアメタル膜3は、第1層配線15のバリアメタル膜13を兼ねており、上述の通りデュアルダマシンプロセスで形成することから、その銅拡散耐性が高く、かつ低抵抗のバリア膜であることが望ましい。前記バリアメタルに使われる金属膜のなかでも、好ましくは窒化タンタル、タンタル/窒化タンタルの積層構造、より好ましくは、ルテニウム/チタンの積層構造が望ましい。

【0066】

(第三の実施形態)

図16は、本発明のひとつの実施の形態の半導体装置を示す断面図である。

図17〜図25は、図16の半導体装置の製造方法を工程順に示す断面図の例である。図16の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面である。また右側(c)は論理回路領域の代表的な断面図を示す。図17〜図25のいずれも図の左側(a)はメモリ回路領域、右側(b)は論理回路領域の代表的な断面図を示す。

第一の実施形態と同様に、標準的な集積回路の形成方法を用いて作成した、MOSトランジスタ9および第3層配線形成後の構造を有する基板を図17に示す。ここでは後にメモリ回路領域には容量素子を形成するため、論理回路領域のみに第2層配線25と第3層配線35を形成する。本実施の形態では容量素子の高さを論理回路部の3層分よりは低い場合を示しているが、4層分より低い場合とする場合にはさらに論理回路部を1層多く形成する。

【0067】

図17において、1はコンタクト層間絶縁膜、2はエッチストップ膜、3はコンタクトバリアメタル膜、4はコンタクトプラグ、5はシリコン(Si)基板,6は素子分離STI(shallow trench isolation)、7は拡散層、8はゲート電極である。

【0068】

また、11は第1層の層間絶縁膜であり、13は第1層配線バリアメタル膜、15は第1層配線、20は第1層配線のキャップ膜、23は第2層配線バリアメタル膜、25は第2層配線、30は第2層配線のキャップ膜、である。また、ビット線19は第1層配線15と同時に形成されるが、メモリ回路部におけるビット線である。

【0069】

さらに、ここでビット線19は第1層配線15と同一層に形成されており、特許文献2などに見られるような、ビット線だけの配線層は存在しない。さらに本実施の形態では、容量素子の下部電極との電気的接続を行う、いわゆる下部電極コンタクトを取る下部電極配線が、ビット線19と同層の第1層配線15中に形成されている。本実施の形態に示す構造により、多層配線構造は層数を有効に活用することが可能である。

【0070】

図17ではコンタクト層間絶縁膜1はシリコン酸化膜からなり、コンタクトプラグ4はタングステンからなり、コンタクトバリアメタル膜3は窒化チタン/チタンの積層膜からなる。また、第1層の層間絶縁膜11および第2層の層間絶縁膜21は低誘電率絶縁膜でありSiOCH膜、より具体的にはMPS膜からなる。第1層配線バリアメタル膜13はタンタル/窒化タンタル積層膜からなり、第1層配線15は銅からなる。また、第1層配線のキャップ膜20および第2層配線のキャップ膜30はSCC膜からなる。またSCC膜についても、MPS膜と同様に非特許文献1に詳細が記載されている。SCC膜はSiOCH膜の一種でありながら、銅拡散耐性を持つことが特徴である。第2層配線25および第3層配線35を形成する手法は第一の実施形態に示した通りである。

【0071】

本実施の形態においても層間絶縁膜およびキャップ膜は単層の絶縁膜を用いているが、第一の実施形態同様、それぞれ、複数種の絶縁膜の積層構造でもよい。たとえば、層間絶縁膜はMPS膜と他のSiOCH膜、キャップ膜はSiC膜とSiCN膜の積層構造などでもよい。

【0072】

ここでは後にメモリ回路領域には容量素子を形成するため、論理回路領域のみに配線層を形成する。本実施の形態では容量素子の高さを論理回路部の3層分よりは低い場合を示しているが、4層分より低い場合とする場合にはさらに論理回路部を1層多く形成する。

【0073】

次に図18のように第3層配線のキャップ膜40を堆積した後に、ハードマスク絶縁膜94を成膜する。さらにシリンダ加工レジスト膜A81をリソグラフィによって形成する。

【0074】

ここでハードマスク絶縁膜94はシリコン酸化膜を用いたが、他の絶縁膜との積層構造でもよい。またレジスト膜との間に反射防止膜を備えるなどの多層構造をとってもよい。いずれの場合も容量素子形成過程で第4層配線のキャップ膜50を保護する効果をもつ絶縁膜であることが好ましい。具体的には、シリコン酸化膜のほか、シリコン窒化膜、シリコン酸窒化膜などが挙げられる。

【0075】

引き続いて図19に示すようにドライエッチングによって容量素子開口部A88を形成する。このとき、第1層配線15の酸化を防止するため、第1層配線のキャップ膜20はエッチングしない。

【0076】

容量素子開口部A88の形成時には、ドライエッチングによって層間絶縁膜とキャップ膜を交互にエッチングを行うが、本実施の形態では、第一の実施形態同様に層間絶縁膜にMPS膜をキャップ膜にSCCを用いており、SiOCH膜が積層された構造を用いており、加工上の工夫によって、良好な容量素子開口部A88の形状を得ることができる。

【0077】

さらにシリンダ加工レジスト膜A81をアッシングにより除去した後に、シリンダ加工レジスト膜B82、シリンダ加工マスク絶縁膜84を形成し、リソグラフィによってシリンダ加工レジスト膜C83を形成する(図20)。再びドライエッチングによって、容量素子開口部B89を形成する(図21)。さらにアッシングを行い、シリンダ加工レジスト膜B82を除去し、引き続き、容量素子の下部電極を下層の配線となる第1層配線15に接続するため、第1層配線のキャップ膜20をエッチバックする(図22)。

【0078】

以後、第一の実施形態と同様に、容量素子の下部電極となる下部電極膜91を成膜し、リソグラフィによって下部電極膜91を容量素子内部のみに形成し、さらに引き続いて、容量絶縁膜92と上部電極膜93を成膜する(図23)。やはり第一の実施形態同様に、容量絶縁膜92と上部電極膜93を加工する(図24)。

【0079】

さらに上部電極をマスクとして、ハードマスク絶縁膜94をエッチバックし、第3層配線のキャップ膜40を露出させる(図示せず)。これにより、ハードマスク絶縁膜94は容量膜と上部電極が存在する領域のみに残存するのみとなる。

【0080】

その後、第4層の層間絶縁膜41を成膜する(図25)。以後の工程は第一の実施形態と同様に行い、第4層の層間絶縁膜41を平坦化後、第4層配線45を形成する。引き続き上層配線となる第5層配線55を形成し(図16)、さらに上層配線を形成し、半導体集積回路を完成させる。

【0081】

本実施の形態では、実施の形態1あるいは2と同様に、ビット線19は第1層配線15と同一層に形成されており、特許文献2などに見られるような、ビット線だけの配線層は存在しない。さらに本実施の形態では、容量素子の下部電極との電気的接続を行う、いわゆる下部電極コンタクトを取る配線が、ビット線19と同層の第1層配線15中に形成されている。本実施の形態に示す構造により、多層配線構造は層数を有効に活用することが可能である。また、容量素子を第2層配線25の層と第3層配線35の層を貫くように形成し、また、下部電極への接続については、第1層配線15に直接行うため、径の異なるシリンダを上下に接続した形状となっている。本形状は、前記容量素子の下部電極へ接続を第1層配線15に直接行うために好適な構造である。これにより、本実施形態の容量素子の構造は、径の異なるシリンダを接続した形状となる。

【0082】

前記のように、本実施の形態では、層間絶縁膜にMPS膜をキャップ膜にSCCを用いているが、図26に示すように、層間絶縁膜にBlack DiamondTM、のようなSiOCH膜を、キャップ膜にSiCN膜を採用してもよい。この場合、これらの膜組成は窒素の存在の有無が異なることから、容量素子の開口部の形成においては、その点を考慮した加工条件を採用する必要がある。

【0083】

(第四の実施形態)

図27は、本発明のひとつの実施の形態の半導体装置を示す断面図である。図27の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

第三の実施形態の構造からさらに、コンタクトプラグ4に銅を採用し、さらに第1層配線とデュアルダマシン形状(デュアルダマシンコンタクト形状)を形成する事により、さらに拡散層から第1層配線15までの抵抗を低減した構造とすることも可能である。この際、コンタクト層間絶縁膜1は図2のようにシリコン酸化膜とすることも可能であるが、ここでは第1層配線15と同一の層間絶縁膜としている。あるいはコンタクト層間絶縁膜1には第1層とは異なる別の種類の低誘電率SiOCH膜を用いても良い。また異種の低誘電率SiOCH膜の積層構造としてもよい。コンタクト層間絶縁膜には、Cu拡散バリア耐性を持つ膜、例えば、前記SCC膜を用いることが望ましい。積層構造を用いる場合には、最下層、つまりはエッチストップ膜直上に用いることが望ましい。

また、本実施の形態の半導体装置においては、下部電極(下部電極膜91)に接続する下部容量配線(第1層配線15)が、半導体基板(シリコン基板5)の表面近傍に形成された拡散層7に接続するコンタクトプラグ4に接続され、かつ下部容量配線(第1層配線15)と同層に半導体素子(MOSトランジスタ9)間を接続する信号配線(ビット線19)が形成されている。

【0084】

特にSCC膜はプラズマ重合法で成膜されることから、通常のプラズマCVD法による層間絶縁膜よりも段差被覆性に優れており、エッチストップ膜成膜後の半導体基板のようにゲートの存在による凹凸上に成膜する際にも、良好な埋設性が得られる。

【0085】

またさらに、本実施の形態の構造におけるコンタクトプラグ4のコンタクトバリアメタル膜3は、第1層配線15のバリアメタル膜13を兼ねており、上述の通りデュアルダマシンプロセスで形成することから、その銅拡散耐性が高く、かつ低抵抗のバリア膜であることが望ましい。前記バリアメタルに使われる金属膜のなかでも、好ましくは窒化タンタル、タンタル/窒化タンタルの積層構造、より好ましくは、ルテニウム/チタンの積層構造が望ましい。

【0086】

(第五の実施形態)

図28は、本発明のひとつの実施の形態にかかる半導体装置を示す断面図である。図28の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

図19において、シリンダ加工レジスト膜A81を形成後、容量素子開口部A88を形成する際に、ドライエッチング条件の異方性を制御し、等方成分を増加させることで、容量素子開口部A88をテーパー形状に形成することが可能である。テーパー形状の容量素子開口部A88が形成された後に、図23以降と同様の工程を実施することにより、図28に示すような構造が形成される。本実施の形態の手法により、容量素子開口部B89を形成するためのリソグラフィ工程およびレチクルが不要となり、製造コストの低減が可能となる。

【0087】

本実施の形態でも、容量素子は第2層配線25の層と第3層配線35の層を貫くように形成され、また、下部電極への接続については、第1層配線15に直接行うため、径の異なるテーパー付きのシリンダを上下に接続した形状となっている。本形状は、上述の第三の実施形態あるいは第四の実施形態同様、容量素子の下部電極へ接続を第1層配線15に直接行うために好適な構造である。

【0088】

(第六の実施形態)

図29は、本発明のひとつの実施の形態の半導体装置を示す断面図である。29の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

図18において、第3層配線のキャップ膜40を堆積した後に、ハードマスク絶縁膜94を成膜する。

この際、ハードマスク絶縁膜94を20nm以上、30nm以下程度の薄膜とする。さらにシリンダ加工レジスト膜A81をリソグラフィによる形成以降は第三の実施形態と同様に行う。シリンダ開口部Aの底にある第1層配線のキャップ膜20をエッチバックする際には、同時にハードマスク絶縁膜94もエッチングされるため、その膜厚は10nm以上、20nm以下程度に減少する。その後、第三の実施形態と同様に下部電極膜の成膜を行い、リソグラフィ後、下部電極のエッチバックを行う。その際、オーバーエッチングによって、ハードマスク絶縁膜94はさらに膜厚が減少し、10nm程度もしくは10nm未満となる。その後、容量絶縁膜92と上部電極膜93の成膜に続き、それらの加工を行う際には、ジョブ電極の無い領域のハードマスク絶縁膜94はほぼ除去される。したがって、第三の実施形態で記載したエッチバック工程は不要となる。以降の上層配線工程は第三の実施形態と同様に実施する。

【0089】

ただし、本実施の形態の構造では、第4層配線のキャップ膜50の下面(第4層配線45の表面)から、上部電極膜93の表面までの距離は、第4層配線45のビア高さより短いため、メモリ回路領域においても第4層配線45下のビアの形成が必要となり、ビアパターンを露光することが必要である。ただし、この際の露光は第4層配線45のビアパターン露光と同時に行うことから、レチクル数の増加や工程数の増加はない。

【0090】

以上の手法によって図29に示すような構造が形成される。

本実施形態は、第一の実施形態から第五の実施形態の構造に、さらに上部電極と上部容量配線との間に接続ビアが設けられたものである。これらの実施形態の構造においては、容量素子の上部電極上に直接形成する配線溝深さは、表面を同じくする同層の論理回路部の配線溝よりも浅くなければならない制限があった。これに対して、本実施の形態のような、容量素子の上部電極にビアを介して接続する構造とすることで、前記制限がなくなる。これによって、配線構造設計の自由度が向上する。言い換えると、容量素子の上部電極上に直接形成する配線構造に限定することは、容量素子の構造によっては、論理回路部の配線溝深さに制限が生じることになる。

【0091】

本実施の形態では容量素子を第2層と第3層を貫く形で形成したが、これを例えばローカル配線層とセミグローバル配線層の両方を貫く形で形成する場合には、セミグローバル配線層のビア高さが高くなることから、第一の実施形態のような上部電極上に直接プレート線配線が形成されるような構造を形成するより、本実施の形態のほうがハードマスク絶縁膜94の膜厚を低減でき、特にセミグローバル層の層間絶縁膜も低誘電率SiOCH膜を用いる場合には層間絶縁膜の実効誘電率を低減することが可能である。

【0092】

(第七の実施形態)

図30及び図31は、本発明のひとつの実施の形態の半導体装置を示す断面図である。図30の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

本実施の形態の図30では、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の3配線層にまたがる領域に該容量素子を埋め込んだ構造である。また図31は同様に4配線層にまたがる領域に該容量素子を埋め込んだ構造である。図31では、第6の配線層にさらに、第7の配線層として、第7層配線75と第7層の層間絶縁膜71が設けられている。第2層配線の開口部と同等にして、第7層配線の開口部を形成することができる。図31に示す、第7層配線バリアメタル膜73も、第1層配線バリアメタル膜13または第2層配線バリアメタル膜23と同様にして形成できる。図31に示す、第7層配線のキャップ膜70は、第2層配線のキャップ膜30と同様にして形成できる。

【0093】

図17の構造からさらに論理回路部に多層配線を1層、あるいは2層を形成した後に、実施の形態5同様、シリンダ加工レジスト膜(図示せず)を形成し、容量素子開口部Aを形成する際に、ドライエッチング条件の異方性を制御し、等方成分を増加させることで、容量素子開口部Aをテーパー形状に形成する(図示せず)。テーパー形状の容量素子開口部が形成された後に、図23以降と同様の工程を実施することにより、図30に、あるいは図31に示すような構造が形成される。本実施の形態の手法により、容量素子開口部Bを形成するためのリソグラフィ工程およびレチクルが不要となり、製造コストの低減が可能となる。

【0094】

図30では、容量素子は第2層配線25の層からと第4層配線45の層を貫くように形成され、また、図31では、容量素子は第2層配線25の層からと第5層配線55の層を貫くように形成され、下部電極への接続については、第1層配線15に直接行うため、径の異なるテーパーのついたシリンダを上下に接続した形状となっている。この形状は、上述の第三の実施形態あるいは第四の実施形態と同様、容量素子の下部電極へ接続を第1層配線に直接行うために好適な構造である。

さらに、図32に示すように、第一の実施形態の変形例として、下層に位置する多層配線の上に位置する上層多層配線層(グローバル配線)に容量素子90の上部の一部が形成されていてもよい。また、上層に位置する多層配線層を構成する各配線層や配線の厚さは、下層に位置する多層配線層よりも厚くてもよい。図32では、容量素子90が設けられた領域のうち、第2の配線層から第4の配線層が同じ厚みであり、第2層配線25から第4配線の厚みが同じであるとともに、これらの配線層の厚みと第5の配線層の厚みが異なり、これらの配線の厚みと第5の配線の厚みが異なる。このように、本実施形態は、容量素子90が設けられた領域の多層配線構造において、各配線層の厚みと各配線の厚みが異なる構造を有してもよい。

【0095】

容量素子90の開口部の形成時には、ドライエッチングによって層間絶縁膜とキャップ膜を交互にエッチングを行うが、本実施の形態では、層間絶縁膜にMPS膜をキャップ膜にSCCを用いており、SiOCH膜が積層された構造となっている。先に述べた通り、この2つの膜は炭素の組成が大きく異なっており、ドライエッチングによる加工条件を工夫することにより、MPS/SCC膜のエッチングレートの比、いわゆるエッチング選択比を制御することが容易である。したがって、層間絶縁膜であるMPSをエッチングしながら、キャップ膜であるSCC膜のエッチング選択比を小さくして、容量素子90の開口部を深く開口したり、反対にMP/SCCの選択比を大きくして、シリンダ開口部底でエッチングを止めたりすることか出来る。本実施の形態では特に深いシリンダ開口部を形成する必要があるが、本実施の形態の構造においては、積層構造での深い開口部を形成が容易である。これは一般的に用いられるSiOCH層間絶縁膜とSiCNキャップ膜の組み合わせでは実現困難な手法である。こうした加工の自由度が高い構造を用いることにより、良好な容量素子90の開口部の形状を得ることができる。

【0096】

さらに、本実施の形態では、3層以上の配線層を貫くように容量素子を形成していることから、メモリ回路部のセル容量を大きくすることができる。また、このとき、論理回路部の構造は、メモリ回路部の存在しない場合と同様の多層配線構造をとっており、設計パラメーターは変化せず、互換性がある。

さらに、図30に示す通り、容量素子90が3層以上の配線層を貫くように設けられているため、メモリ回路領域の容量素子90が埋め込まれている、この多層配線構造中に、行デコード配線17と列デコード配線18が設けられている。容量素子90が埋め込まれている多層配線構造中に、行デコード配線17および列デコード配線18を設けることにより、上層配線を利用する必要がなくなり、メモリ回路領域の配線層数を減ずることができる。これによってメモリ回路領域の上層は論理回路領域の配線のために用いたり、各回路領域間を接続するために用いたりすることが可能となり、チップ面積を縮小することが可能になる。

【0097】

(第八の実施の形態)

図34は、本発明のひとつの実施の形態にかかる半導体装置を示す断面図である。図34の左側(a)と中央(b)の2つの図はメモリ回路領域の断面図であり、お互いに90度回転させた断面図である。また右側(c)は論理回路領域の代表的な断面図を示す。

本実施の形態の半導体装置においては、下部電極(下部電極膜91)に接続する下部容量配線がコンタクトプラグ4であり、下部電極(下部電極膜91)がコンタクトプラグ4に直接接続している。つまり、コンタクトプラグ4を構成するタングステン上に、下部電極(下部電極膜91)が設けられている。

【0098】

図34において、1はコンタクト層間絶縁膜、2はエッチストップ膜、3はコンタクトバリアメタル膜、4はコンタクトプラグ、5はシリコン(Si)基板、6は素子分離STI(shallow trench isolation)、7は拡散層、8はゲート電極である。

【0099】

また、11は第1層の層間絶縁膜であり、13は第1層配線バリアメタル膜、15は第1層配線、20は第1層配線のキャップ膜、23は第2層配線バリアメタル膜、25は第2層配線、30は第2層配線のキャップ膜、である。また、メモリ回路部において、ビット線19は、第1層配線15と同時に形成される。ここで、ビット線19は、第三の実施の形態と同様に、第1層配線15と同一の層に形成されている。また、本実施の形態においては、特許文献2などに見られるような、ビット線だけの配線層は存在しない。

【0100】

さらに、メモリ回路部において、列デコード配線18は、第2層配線25と同時に形成される。本実施の形態においては、列デコード配線18は第2層配線25と同時に形成されているが、これに限定されず、たとえば列デコード配線18の代わりに、行デコード配線17を形成してもよい。このとき、第2層配線25と同時に形成されなかった列デコード配線18は、たとえば第6層等に形成してもよい。

【0101】

図34ではコンタクト層間絶縁膜1はシリコン酸化膜からなり、コンタクトプラグ4はタングステンからなり、コンタクトバリアメタル膜3は窒化チタン/チタンの積層膜からなる。また、第1層の層間絶縁膜11および第2層の層間絶縁膜21は低誘電率絶縁膜でありSiOCH膜、より具体的にはMPS膜からなる。第1層配線バリアメタル膜13はタンタル/窒化タンタル積層膜からなり、第1層配線15は銅からなる。また、第1層配線のキャップ膜20および第2層配線のキャップ膜30は、SCC膜からなる。またSCC膜についても、MPS膜と同様に非特許文献1に詳細が記載されているものを用いることができる。SCC膜は、SiOCH膜の一種でありながら、銅拡散耐性を持つことが特徴である。第2層配線25および第3層配線35を形成する手法は、第一の実施の形態に示した通りである。

【0102】

本実施の形態においても層間絶縁膜およびキャップ膜は単層の絶縁膜を用いているが、第一の実施の形態と同様に、それぞれ、複数種の絶縁膜の積層構造でもよい。たとえば、層間絶縁膜はMPS膜と他のSiOCH膜、キャップ膜はSiC膜とSiCN膜の積層構造などでもよい。

【0103】

本実施の形態においても第三の実施の形態と同様に、容量素子90の構造を、径の異なるシリンダが接続された形状とする。第三の実施の形態と異なるのは、下部電極への接続を第1層配線15ではなく、より下層のコンタクトプラグ4に対して行うことである。したがって、本実施の形態においては、第三の実施の形態中の第1層配線15形成時には、下部電極が接続する予定領域に第1層配線の形成を行わない(図示せず)。

【0104】

容量素子90の形成手順は第三の実施の形態に準ずる。第三の実施の形態と異なる点としては、ドライエッチングによって容量素子開口部A88を形成する際には、第1層配線層のキャップ膜20と第1層の層間絶縁膜11までエッチングし、Wからなるコンタクトプラグ4を露出させる。容量素子開口部A88の形成時には、ドライエッチングによって層間絶縁膜とキャップ膜を交互にエッチングを行う。このとき、本実施の形態では、第三の実施の形態と同様に層間絶縁膜にMPS膜をキャップ膜にSCCを用いており、SiOCH膜が積層された構造を用いており、加工上の工夫によって、良好な容量素子開口部の形状を得ることができる。

【0105】

これ以後の工程は第三の実施の形態と同様である。ただし、すでに第1層配線層のキャップ膜20と第1層の層間絶縁膜11までエッチングされていることから、容量素子開口部B89を形成する際には、第1層配線キャップ膜20のエッチバック工程を行う必要はない。

以後、第一の実施の形態と同様に、容量素子90の形成と第4層配線45以降の上層配線の形成を行い、半導体集積回路を完成させる。

【0106】

本実施の形態では、容量素子90の下部電極(下部電極膜91)との電気的接続を行う、いわゆる下部電極コンタクトを取る配線(下部容量配線)が、トランジスタの拡散層7に接続するコンタクトプラグ4を兼ねている。これにより、下部電極が、上記集積回路の第1層配線15と同層にある。そのため、第1層配線15上に形成した場合よりも、容量素子90の容量を確保しやすくなる。また、下部容量配線が、トランジスタの拡散層に接続するコンタクトプラグを兼ねていることにより、コンタクトプラグ4までがトランジスタパラメータとして設計されている場合、容量素子90を混載した場合でも、パラメーターを変更する必要がない。同時に、従来技術と同様に、容量コンタクトはタングステン上に形成することになり、容量素子90形成過程において、異種材料の露出による性能への影響を考慮する必要がない。具体的には、下部電極形成時にはCuは露出することがないため、下部電極としてCuバリア性を考慮する必要がなくなる。したがって、TaNのようなCuバリア性を有するバリアメタル膜を下部電極に用いる必要がない。

【0107】

第八の実施の形態の変形例としては、図35に示すように、メモリ回路領域において、プレート線配線(メモリ回路領域に形成された第4層配線45)が、配線形状ではなく、シリンダ容量部上部を完全に覆っていて、超幅広配線のようになっている。さらには、このプレート線配線が、シリンダ内部まで配線材料で埋設されている。このプレート線配線の配線形状は、たとえば所定間隔でスリットを介在させた、スリット入り幅広配線形状になっていてもよい。

【0108】

図35の左側(a)はメモリ回路領域の断面図であり、右側(b)は論理回路領域の代表的な断面図を示す。図35において、ほとんどの構成は図34と同様である。90度回転させた構造は図示しないが図34とほぼ同様である。

【0109】

本実施の形態においても第三の実施の形態と同様に、容量素子90の構造を、径の異なるシリンダが接続された形状とする。また、容量素子90の構造は第八の実施の形態と同様であり、その形成方法も同様である。第八の実施の形態と異なるのは、第4層配線45の形成の前に、シリンダ内部の絶縁膜を除去する工程を追加することである(図示せず)。論理回路部の第4層配線の形成以降の工程については第三の実施の形態と同様である。

【0110】

(第九の実施形態)