半導体装置

【課題】スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体素子を有する半導体基板1と、半導体基板1の上方に形成され、配線10a、10b、10c、10d、配線10c、10dの周囲のエアギャップ101、およびエアギャップ101に連続するスルーホール102含む配線構造と、スルーホール102下に形成されたスルーホールストッパー103と、を有する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体素子を有する半導体基板1と、半導体基板1の上方に形成され、配線10a、10b、10c、10d、配線10c、10dの周囲のエアギャップ101、およびエアギャップ101に連続するスルーホール102含む配線構造と、スルーホール102下に形成されたスルーホールストッパー103と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

近年の微細化された半導体装置では、多層配線を流れる信号の遅延(RC遅延)が性能低下の大きな要因になっている。信号遅延を低減するためには、多層配線構造の静電容量を減少させることが重要である。そこで、多層配線構造の配線層の絶縁膜を除去することにより形成されるエアギャップ多層配線構造を有する半導体装置が提案されている(例えば、特許文献1参照)。

【0003】

しかし、この特許文献1等に記載の半導体装置によると、配線層の絶縁膜を除去するために配線構造中に形成するスルーホールの深さを制御することが難しく、スルーホールの下の部材にエッチングダメージが生じる等の問題がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−166726号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は、スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供することにある。

【課題を解決するための手段】

【0006】

本発明の一態様は、半導体素子を有する半導体基板と、前記半導体基板の上方に形成され、配線、前記配線の少なくとも一部の周囲に位置するエアギャップ、および前記エアギャップに連続するスルーホールを含む配線構造と、前記スルーホール下に形成されたスルーホールストッパーと、を有する半導体装置を提供する。

【0007】

本発明の他の態様は、半導体素子を有する半導体基板と、前記半導体基板の上方に形成された配線構造と、前記配線構造中において、第1の配線、前記第1の配線の少なくとも一部の周囲に位置する第1のエアギャップ、および前記第1のエアギャップに連続する第1のスルーホールを含む第1の領域と、第2の配線、前記第2の配線の少なくとも一部の周囲に位置する第2のエアギャップ、および前記第2のエアギャップに連続する第2のスルーホールを含む第2の領域とを区画するガードリングと、前記第1のスルーホール下に形成された第1のスルーホールストッパーと、前記第2のスルーホール下に形成され、前記第1のスルーホールストッパーよりも高い位置に形成された第2のスルーホールストッパーと、を有する半導体装置を提供する。

【発明の効果】

【0008】

本発明によれば、スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供することができる。

【図面の簡単な説明】

【0009】

【図1】本発明の第1の実施の形態に係る半導体装置の垂直断面図。

【図2】(a)、(b)は、それぞれ図1の破線IIa−IIa、IIb−IIbに沿った半導体装置の水平断面図。

【図3A】(a)〜(e)は、本発明の第1の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図3B】(f)〜(i)は、本発明の第1の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図3C】(j)〜(l)は、本発明の第1の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図3D】(m)〜(o)は、本発明の第1の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図4】本発明の第2の実施の形態に係る半導体装置の垂直断面図。

【図5】(a)、(b)は、それぞれ図4の破線Va−Va、Vb−Vbに沿った半導体装置の水平断面図。

【図6】本発明の第3の実施の形態に係る半導体装置の垂直断面図。

【図7A】(a)〜(d)は、本発明の第3の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図7B】(e)、(f)は、本発明の第3の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図8】本発明の第4の実施の形態に係る半導体装置の垂直断面図。

【図9】本発明の第5の実施の形態に係る半導体装置の垂直断面図。

【図10】(a)、(b)は、それぞれ図9の破線Xa−Xa、Xb−Xbに沿った半導体装置の水平断面図。

【図11】本発明の第6の実施の形態に係る半導体装置の垂直断面図。

【図12】(a)、(b)、(c)は、それぞれ図11の破線XIIa−XIIa、XIIb−XIIb、XIIc−XIIcに沿った半導体装置600の水平断面図。

【図13】本発明の第7の実施の形態に係る半導体装置の垂直断面図。

【図14】(a)、(b)は、それぞれ図13の破線XIVa−XIVa、XIVb−XIVbに沿った半導体装置の水平断面図。

【発明を実施するための形態】

【0010】

〔第1の実施の形態〕

(半導体装置の構成)

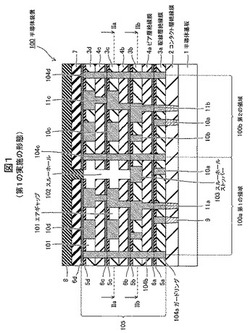

図1は、本発明の第1の実施の形態に係る半導体装置100の垂直断面図である。また、図2(a)、(b)は、それぞれ図1の破線IIa−IIa、IIb−IIbに沿った半導体装置100の水平断面図である。

【0011】

半導体装置100は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造105と、半導体基板1の半導体素子と多層配線構造105の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0012】

多層配線構造105は、コンタクト層絶縁膜2上の配線10aを含む配線層絶縁膜3aと、配線層絶縁膜3a上のビア11aを含むビア層絶縁膜4aと、ビア層絶縁膜4a上の配線10bを含む配線層絶縁膜3bと、配線層絶縁膜3b上のビア11bを含むビア層絶縁膜4bと、ビア層絶縁膜4b上の配線10cを含む配線層絶縁膜3cと、配線層絶縁膜3c上のビア11cを含むビア層絶縁膜4cと、ビア層絶縁膜4c上の配線10dを含む配線層絶縁膜3dと、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域100aおよび第2の領域100bを区画するガードリング104a、104b、104c、104dと、第1の領域100aの配線層絶縁膜3b中のスルーホールストッパー103と、配線層絶縁膜3c、3dおよびビア層絶縁膜4b、4cを貫通するように形成されたスルーホールストッパー103上のスルーホール102と、第1の領域100aの配線10c、10dが設けられた層のエアギャップ101と、を含む。なお、多層配線構造105の配線層の数は、4層に限られない。

【0013】

また、配線層絶縁膜3a上にはキャップ膜5aおよび拡散防止膜6aが形成され、配線層絶縁膜3b上にはキャップ膜5bおよび拡散防止膜6bが形成され、配線層絶縁膜3c上にはキャップ膜5cおよび拡散防止膜6cが形成され、配線層絶縁膜3d上にはキャップ膜5dおよび拡散防止膜6dが形成される。また、拡散防止膜6d上にはハードマスク7が形成される。また、スルーホール102の開口部は、スルーホールキャップ膜8により塞がれる。

【0014】

半導体基板1は、Si結晶等のSi系結晶からなる。

【0015】

コンタクト層絶縁膜2は、SiO2等の絶縁材料からなる。

【0016】

配線層絶縁膜3a、3b、3c、3dは、有機絶縁材料等の絶縁材料からなる。配線層絶縁膜3a、3b、3c、3dの誘電率を下げるために、微小空孔を含んだ有機絶縁材料を用いてもよい。

【0017】

ビア層絶縁膜4a、4b、4cは、SiOC等の絶縁材料からなる。ビア層絶縁膜4a、4b、4cの誘電率を下げるために、微小空孔を含んだ絶縁材料を用いてもよい。

【0018】

キャップ膜5a、5b、5c、5dは、SiO2、SiOC等の絶縁材料からなり、配線10a、10b、10c、10dをエッチングや平坦化処理によるダメージから守る機能、およびエアギャップ101上の部材の保持部材としての機能を有する。

【0019】

拡散防止膜6a、6b、6c、6dは、SiN、SiCN、SiON、SiC等の絶縁材料からなる絶縁膜、またはこれらの絶縁膜の積層体である。また、拡散防止膜6a、6b、6c、6dは、配線10a、10b、10c、10dにおける金属元素の表面拡散を抑える機能や、上層の部材を加工する際のストッパーとしての機能を有する。なお、拡散防止膜6a、6b、6c、6dは、配線10a、10b、10c、10dの上面にのみ形成されるものであってもよい。

【0020】

ハードマスク7は、TEOS(Tetraethoxysilane)を原料ガスに用いて形成されるSiO2、SiOC、SiN、TaN、TiN等の絶縁材料からなる絶縁膜、またはこれらの絶縁膜の積層体である。

【0021】

スルーホールキャップ膜8は、スルーホール102の開口部を塞いで、配線構造内への水分等の進入を防ぐ機能を有する。スルーホールキャップ膜8は、SiO2、TEOS、SiOC、SiCN、SiN等の絶縁材料からなる。

【0022】

コンタクトプラグ9は、半導体基板1上の半導体素子(図示しない)と配線10aとを接続する。また、コンタクトプラグ9は、W等の導電材料からなる。また、図示しないが、コンタクトプラグ9の表面に、バリアメタルが形成されてもよい。バリアメタルは、Ta、Ti、Ru、Co、Mn等の金属や、これらの金属の窒化物または酸化物等の導電材料からなる。

【0023】

配線10a、10b、10c、10dは、Cu、W、Al等の導電材料からなる。また、図示しないが、配線10a、10b、10c、10dの表面に、バリアメタルが形成されてもよい。バリアメタルは、Ta、Ti、Ru、Co、Mn等の金属や、これらの金属の窒化物または酸化物等の導電材料からなる。なお、10a、10b、10c、10dのレイアウトは図1、2に示したものに限られない。

【0024】

ビア11aは、配線10aと配線10bを接続し、ビア11bは、配線10bと配線10cを接続し、ビア11cは、配線10cと配線10dを接続する。また、ビア11a、11b、11cは、配線10a、10b、10c、10dと同じ材料からなる。また、図示しないが、ビア11a、11b、11cの表面に、配線10a、10b、10c、10dのものと同じバリアメタルが形成されてもよい。

【0025】

エアギャップ101は、スルーホール102を通して第1の領域100aの配線層絶縁膜3c、3dを除去することにより形成される。このため、第1の領域100aの配線10c、10dの周囲にエアギャップ101が形成される。

【0026】

スルーホール102は、スルーホールストッパー103をストッパーとして用いて、第1の領域100aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6bをエッチングすることにより形成される。

【0027】

スルーホールストッパー103は、例えば、配線10a、10b、10c、10dと同じ材料からなる。図2(b)のスルーホールストッパー103内の点線は、スルーホール102の直下に位置する領域を表す。

【0028】

図1、2においては、スルーホールストッパー103は配線10bが設けられた層に位置するが、他の配線層に形成されてもよい。スルーホールストッパー103がいずれの層に形成された場合も、スルーホールストッパー103よりも上にある配線層絶縁膜が除去され、エアギャップが形成される。例えば、配線10cが設けられた層にスルーホールストッパー103が形成される場合は、第1の領域100aの配線層絶縁膜3dが除去され、配線10dの周囲にエアギャップ101が形成される。

【0029】

また、第1の領域100aのビア層絶縁膜4b、4cを除去して、エアギャップ101をビア11b、11cの設けられた層にも形成することができる。ビア層絶縁膜も除去する場合、スルーホールストッパー103よりも上にある配線層絶縁膜およびビア層絶縁膜が除去され、エアギャップが形成される。

【0030】

スルーホール102を形成する際のエッチングはスルーホールストッパー103により止められるため、スルーホールストッパー103の形成される層よりも下の層にはスルーホール102が形成されない。このため、スルーホール102の直下の領域に配線等の導電部材を形成した場合であっても、スルーホール102を形成する際のエッチングによるダメージから導電部材を保護することができる。例えば、図1に示すように、スルーホール102直下の配線層絶縁膜3a中の領域に配線10aを形成することができる。

【0031】

ガードリング104a、104b、104c、104dは、例えば、配線10a、10b、10c、10dと同じ材料からなる。また、図示しないが、ガードリング104a、104b、104c、104dの表面に、配線10a、10b、10c、10dのものと同じバリアメタルが形成されてもよい。

【0032】

第1の領域100aおよび第2の領域100bは、それぞれガードリング104a、104b、104c、104dによって外部から分離されているため、それぞれの領域内の配線層絶縁膜を選択的に除去し、エアギャップを形成することができる。また、第1の領域100aおよび第2の領域100bは、それぞれガードリング104a、104b、104c、104dによって囲まれているため、外部との電磁的相互作用が低減され、信頼性が向上する。

【0033】

以下に、本実施の形態に係る半導体装置100の製造方法の一例を示す。

【0034】

(半導体装置の製造方法)

図3A(a)〜(e)、図3B(f)〜(i)、図3C(j)〜(l)、図3D(m)〜(o)は、本発明の第1の実施の形態に係る半導体装置100の製造方法を表す垂直断面図である。

【0035】

まず、図3A(a)に示すように、半導体素子(図示しない)が形成された半導体基板上にコンタクト層絶縁膜2をCVD(Chemical Vapor Deposition)法等により形成する。

【0036】

次に、図3A(b)に示すように、コンタクト層絶縁膜2中にコンタクトホール20をリソグラフィ法とRIE(Reactive Ion Etching)の組み合わせ等により形成する。

【0037】

次に、図3A(c)に示すように、コンタクトホール20中にコンタクトプラグ9を形成する。コンタクトプラグ9は、コンタクトホール20を埋めるように半導体基板1上に導電材料を堆積させた後、コンタクトホール20の外側の導電材料を平坦化処理等により除去することにより形成される。

【0038】

次に、図3A(d)に示すように、コンタクト層絶縁膜2およびコンタクトプラグ9上に配線層絶縁膜3aおよびキャップ膜5aを形成する。配線層絶縁膜3aは、塗布法等により形成される。また、キャップ膜5aは、CVD法等により形成される。

【0039】

次に、図3A(e)に示すように、キャップ膜5aおよび配線層絶縁膜3a中に配線溝21aおよびガードリング溝22aをリソグラフィ法とRIEの組み合わせ等により形成する。

【0040】

次に、図3B(f)に示すように、配線溝21aおよびガードリング溝22a中にそれぞれ配線10aおよびガードリング104aを形成し、キャップ膜5a、配線10aおよびガードリング104a上に拡散防止膜6aをCVD法等により形成する。

【0041】

具体的には、配線10aおよびガードリング104aは、例えば以下の工程により形成される。まず、配線溝21aおよびガードリング溝22aの内面を覆うように半導体基板1上にバリアメタルの材料をCVD法、PVD(Physical Vapor Deposition)法、原子層気相成長法等により堆積させ、厚さ5nm程度のバリアメタルの材料膜を形成する。次に、バリアメタルの材料膜上にCuシード膜をCVD法、PVD法、原子層気相成長法等により形成する。次に、Cuシード膜をカソード極として用いて、配線溝21aおよびガードリング溝22aを埋めるようにCuシード膜上にCu膜を電解めっき法等の電気化学成長法により形成する。なお、配線10aおよびガードリング104aの材料であるCuは、PVD法またはCVD法により形成されてもよい。この場合、Cuシード膜を形成しなくてもよい。次に、アニール処理によりCu膜の結晶組織を安定化させる。次に、配線溝21aおよびガードリング溝22aの外側のバリアメタルの材料膜、Cuシード膜およびCu膜をCMP(Chemical Mechanical Polishing)法等による平坦化処理により除去し、配線10a、ガードリング104aおよびそれらの表面のバリアメタルに加工する。

【0042】

次に、図3B(g)に示すように、拡散防止膜6a上にビア層絶縁膜4a、配線層絶縁膜3bおよびキャップ膜5bを形成する。ビア層絶縁膜4aは、CVD法、塗布法等により形成される。配線層絶縁膜3bおよびキャップ膜5bは、それぞれ配線層絶縁膜3aおよびキャップ膜5aと同様の方法により形成される。

【0043】

次に、図3B(h)に示すように、キャップ膜5bおよび配線層絶縁膜3b中に配線溝21bおよびスルーホールストッパー103用の溝105を形成し、ビア層絶縁膜4aおよび拡散防止膜6a中にビアホール23aを形成し、キャップ膜5b、配線層絶縁膜3b、ビア層絶縁膜4aおよび拡散防止膜6a中にガードリング溝22bを形成する。配線溝21b、ビアホール23a、およびガードリング溝22bは、リソグラフィ法とRIEの組み合わせ等により形成される。

【0044】

ここで、配線溝21b、およびガードリング溝22bの上部と同時に溝105を形成することができる。このため、溝105を形成するために工程数を増やす必要はない。

【0045】

なお、溝105は、底がビア層絶縁膜4aに達するように形成されてもよい。この場合、スルーホールストッパー103の一部はビア層絶縁膜4a中に形成される。

【0046】

次に、図3B(i)に示すように、配線溝21b、溝105、ビアホール23a、およびガードリング溝22b中にそれぞれ配線10b、スルーホールストッパー103、ビア11aおよびガードリング104bを形成し、キャップ膜5b、配線10b、スルーホールストッパー103およびガードリング104b上に拡散防止膜6bをCVD法等により形成する。

【0047】

ここで、配線溝21b、ビアホール23a、溝105およびガードリング溝22bには、配線10aおよびガードリング104aと同様の方法により同時に導電材料が埋め込まれ、それぞれ配線10b、ビア11a、スルーホールストッパー103およびガードリング104bが形成される。このため、スルーホールストッパー103を形成するために工程数を増やす必要はない。なお、配線10bおよびビア11aはデュアルダマシン構造を有する。

【0048】

続けて、図3B(g)〜(i)に示した工程と同様の工程を繰り返して配線層絶縁膜3c、3d、ビア層絶縁膜4b、4c、キャップ膜5c、5d、拡散防止膜6c、6d、配線10c、10d、ビア11b、11c、およびガードリング104c、104dを形成する。

【0049】

その後、拡散防止膜6d上にスルーホール102のパターンを有するハードマスク7を形成し、図3C(j)に示す構造を得る。ハードマスク7は、CVD法、スパッタ法等により絶縁膜を形成した後、これをリソグラフィ法とRIE法の組み合わせによりパターニングすることにより形成される。

【0050】

次に、図3C(k)に示すように、ハードマスク7をマスクとして用いて拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4bおよび拡散防止膜6bをRIE法等によりエッチングし、スルーホール102を形成する。

【0051】

このとき、スルーホールストッパー103がエッチングのストッパーとして働き、スルーホール102の底にスルーホールストッパー103の上面が露出する。スルーホール102は、スルーホールストッパー103よりも上に位置する配線層絶縁膜3c、3d内に形成され、スルーホールストッパー103よりも上に位置しない配線層絶縁膜3a、3b内には形成されない。

【0052】

次に、図3C(l)に示すように、第1の領域100aの配線層絶縁膜3c、3dにスルーホール102を通してO2ガスを用いたアッシング処理等を施して、これらを除去する。これにより、第1の領域100aの配線10c、10dの周囲にエアギャップ101が形成される。

【0053】

このとき、スルーホールストッパー103よりも上に位置する配線層絶縁膜3c、3dのみが除去され、スルーホールストッパー103よりも上に位置しない配線層絶縁膜3a、3bは除去されない。

【0054】

次に、図3D(m)に示すように、スルーホールキャップ膜8を塗布法等により形成してスルーホール102の開口部を塞ぐことにより、図1に示した半導体装置100を得る。

【0055】

塗布法によりスルーホールキャップ膜8を形成する場合は、材料として有機絶縁材料、SiO2またはSiOC等が用いられる。

【0056】

この場合、図3D(n)に示すように、スルーホール102の外側のスルーホールキャップ膜8を全面エッチバック等により除去してもよい。

【0057】

また、CVD法等の成膜法において、被覆性の低い成膜条件を用いてスルーホールキャップ膜8を形成してもよい。この場合、図3D(o)に示すように、スルーホールキャップ膜8のスルーホール102の直上の領域に空隙が形成される。

【0058】

CVD法によりスルーホールキャップ膜8を形成する場合は、材料として有機絶縁材料、SiO2、TEOS、SiOC、SiCNまたはSiN等が用いられる。

【0059】

さらに、スルーホールキャップ膜8の防湿性が不十分である場合は、スルーホール102およびエアギャップ101への水分等の進入を防ぐために、スルーホールキャップ膜8上に防湿性に優れた膜を形成してもよい。

【0060】

(第1の実施の形態の効果)

本発明の第1の実施の形態によれば、スルーホールストッパー103を形成することによりスルーホール102の深さを正確に制御し、特定の配線層に選択的にエアギャップを形成することができる。

【0061】

また、スルーホールストッパー103を形成することにより、スルーホール102の直下の領域に配線等の導電部材を形成することができる。

【0062】

〔第2の実施の形態〕

第2の実施の形態は、第1の領域と第2の領域内において、それぞれ異なる層にスルーホールストッパーを形成し、それぞれ異なる層にエアギャップを形成する。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0063】

(半導体装置の構成)

図4は、本発明の第2の実施の形態に係る半導体装置200の垂直断面図である。また、図5(a)、(b)は、それぞれ図4の破線Va−Va、Vb−Vbに沿った半導体装置200の水平断面図である。

【0064】

半導体装置200は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造205と、半導体基板1の半導体素子と多層配線構造205の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0065】

多層配線構造205は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域200aおよび第2の領域200bを区画するガードリング204a、204b、204c、204dと、第1の領域200aの配線層絶縁膜3b中のスルーホールストッパー203aと、第2の領域200bの配線層絶縁膜3c中のスルーホールストッパー203bと、配線層絶縁膜3c、3dおよびビア層絶縁膜4b、4cを貫通するように形成されたスルーホールストッパー203a上のスルーホール202aと、配線層絶縁膜3dおよびビア層絶縁膜4cを貫通するように形成されたスルーホールストッパー203b上のスルーホール202bと、第1の領域200aの配線10c、10dが設けられた層のエアギャップ201aと、第2の領域200bの配線10dが設けられた層のエアギャップ201bと、を含む。

【0066】

エアギャップ201aは、スルーホール202aを通して第1の領域200aの配線層絶縁膜3c、3dを除去することにより形成される。このため、第1の領域200aの配線10c、10dの周囲にエアギャップ201aが形成される。

【0067】

エアギャップ201bは、スルーホール202bを通して第2の領域200bの配線層絶縁膜3dを除去することにより形成される。このため、第2の領域200bの配線10dの周囲にエアギャップ201bが形成される。

【0068】

スルーホール202aは、スルーホールストッパー203aをストッパーとして用いて、第1の領域200aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6bをエッチングすることにより形成される。

【0069】

スルーホール202bは、スルーホールストッパー203bをストッパーとして用いて、第2の領域200bハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6cをエッチングすることにより形成される。

【0070】

スルーホールストッパー203a、203bは、例えば、配線10a、10b、10c、10dと同じ材料からなる。図5(b)のスルーホールストッパー203b内の点線は、スルーホール202bの直下に位置する領域を表す。

【0071】

スルーホールストッパー203a、203bは、異なる配線層に形成される。なお、スルーホールストッパー203a、203bは、それぞれ図4、5に示される層と異なる層に形成されてもよい。スルーホールストッパー203a、203bがいずれの層に形成された場合も、スルーホールストッパー203a、203bよりも上にある配線層絶縁膜が除去され、エアギャップが形成される。

【0072】

(第2の実施の形態の効果)

本発明の第2の実施の形態によれば、スルーホールストッパー203a、203bを異なる配線層に形成することにより、スルーホール202aとスルーホール202bの深さを異ならせ、第1の領域200aのエアギャップ201aが形成される配線層の層数と、第2の領域200bのエアギャップ201bが形成される配線層の層数を異ならせることができる。

【0073】

なお、本実施例を応用して、3つ以上の領域をガードリングにより区画し、それぞれの領域において異なる配線層にエアギャップを形成してもよい。また、ガードリングにより区画される領域に、エアギャップが形成されない領域が含まれていてもよい。

【0074】

〔第3の実施の形態〕

第3の実施の形態は、スルーホールストッパーがビア層絶縁膜中に形成される点において、第1の実施の形態と異なる。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0075】

(半導体装置の構成)

図6は、本発明の第3の実施の形態に係る半導体装置300の垂直断面図である。

【0076】

半導体装置300は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造305と、半導体基板1の半導体素子と多層配線構造305の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0077】

多層配線構造305は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域300aおよび第2の領域300bを区画するガードリング304a、304b、304c、304dと、第1の領域300aのビア層絶縁膜4a中のスルーホールストッパー303と、配線層絶縁膜3b、3c、3dおよびビア層絶縁膜4b、4cを貫通するように形成されたスルーホールストッパー303上のスルーホール302と、第1の領域300aの配線10b、10c、10dが設けられた層のエアギャップ301と、を含む。

【0078】

エアギャップ301は、スルーホール302を通して第1の領域300aの配線層絶縁膜3b、3c、3dを除去することにより形成される。このため、第1の領域300aの配線10b、10c、10dの周囲にエアギャップ301が形成される。

【0079】

スルーホール302は、スルーホールストッパー303をストッパーとして用いて、第1の領域300aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6b、キャップ膜5b、配線層絶縁膜3bをエッチングすることにより形成される。

【0080】

スルーホールストッパー303は、例えば、ビア11a、11b、11cと同じ材料からなる。また、図6においては、スルーホールストッパー303はビア11aが設けられた層に位置するが、他のビア層に形成されてもよい。スルーホールストッパー303がいずれの層に形成された場合も、スルーホールストッパー303よりも上にある配線層絶縁膜が除去され、エアギャップが形成される。

【0081】

本実施例においては、ビア11aと配線10b、ビア11bと配線10c、およびビア11cと配線10dは、シングルダマシン法により別々に形成される。また、ガードリング304a、304b、304c、304dは、シングルダマシン法により、ビア層絶縁膜中の部分と配線層絶縁膜中の部分が別々に形成される。

【0082】

以下に、本実施の形態に係る半導体装置300の製造方法の一例を示す。

【0083】

(半導体装置の製造方法)

図7A(a)〜(d)、図7B(e)、(f)は、本発明の第3の実施の形態に係る半導体装置300の製造方法を表す垂直断面図である。

【0084】

まず、図7A(a)に示すように、図3A(a)〜図3B(f)に示される拡散防止膜6aを形成するまでの工程を第1の実施の形態と同様に行う。

【0085】

次に、図7A(b)に示すように、拡散防止膜6a上にビア層絶縁膜4aを形成する。

【0086】

次に、図7A(c)に示すように、ビア層絶縁膜4aおよび拡散防止膜6a中にビアホール23a、ガードリング溝22bおよびスルーホールストッパー303用の溝305を形成する。

【0087】

次に、7A(d)に示すように、ビアホール23a、ガードリング溝22bおよび溝305中にそれぞれビア11a、ガードリング304bおよびスルーホールストッパー303を形成する。

【0088】

ここで、ビアホール23a、ガードリング溝22bおよび溝305には、同時に導電材料が埋め込まれ、それぞれビア11a、ガードリング304bおよびスルーホールストッパー303が形成される。このため、スルーホールストッパー303を形成するために工程数を増やす必要はない。

【0089】

続けて、図7A(b)〜図7B(f)に示した工程と同様の工程を繰り返して配線層絶縁膜3c、3d、ビア層絶縁膜4b、4c、キャップ膜5c、5d、拡散防止膜6c、6d、配線10c、10d、ビア11b、11c、およびガードリング304c、304dを形成する。

【0090】

その後、ハードマスク7、スルーホール302、エアギャップ301およびスルーホールキャップ膜8を、第1の実施の形態のハードマスク7、スルーホール102、エアギャップ101およびスルーホールキャップ膜8と同様の方法で形成し、図6に示した半導体装置300を得る。

【0091】

(第3の実施の形態の効果)

本発明の第3の実施の形態によれば、配線およびビアをシングルダマシン法を用いて形成することにより、スルーホールストッパーをビア層絶縁膜中に形成することができる。そして、第1の実施の形態と同様の効果を得ることができる。

【0092】

〔第4の実施の形態〕

第4の実施の形態は、スルーホールストッパーがコンタクト層絶縁膜中に形成される点において第1の実施の形態と異なる。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0093】

(半導体装置の構成)

図8は、本発明の第4の実施の形態に係る半導体装置400の垂直断面図である。

【0094】

半導体装置400は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造405と、半導体基板1の半導体素子と多層配線構造405の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0095】

多層配線構造405は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域400aおよび第2の領域400bを区画するガードリング404a、404b、404c、404dと、第1の領域400aのコンタクト層絶縁膜2中のスルーホールストッパー403と、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4cを貫通するように形成されたスルーホールストッパー403上のスルーホール402と、第1の領域400aの配線10a、10b、10c、10dが設けられた層のエアギャップ401と、を含む。

【0096】

エアギャップ401は、スルーホール402を通して第1の領域400aの配線層絶縁膜3a、3b、3c、3dを除去することにより形成される。このため、第1の領域400aの配線10a、10b、10c、10dの周囲にエアギャップ401が形成される。

【0097】

スルーホール402は、スルーホールストッパー403をストッパーとして用いて、第1の領域400aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6b、キャップ膜5b、配線層絶縁膜3b、ビア層絶縁膜4a、拡散防止膜6a、キャップ膜5a、配線層絶縁膜3aをエッチングすることにより形成される。

【0098】

スルーホールストッパー403は、例えば、コンタクトプラグ9と同じ材料からなる。この場合、コンタクトプラグ9を形成する工程において、スルーホールストッパー403をコンタクトプラグ9と同時に形成することができるため、コンタクトプラグ9を形成するために工程数を増やす必要はない。

【0099】

(第4の実施の形態の効果)

本発明の第4の実施の形態によれば、スルーホールストッパーをコンタクト層絶縁膜中に形成することにより、コンタクト層絶縁膜をエッチングダメージから保護しつつ、最下層の配線である配線10aの周囲にもエアギャップを形成することができる。

【0100】

〔第5の実施の形態〕

第5の実施の形態は、ガードリングの一部の直下に配線が形成される点において第1の実施の形態と異なる。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0101】

(半導体装置の構成)

図9は、本発明の第5の実施の形態に係る半導体装置500の垂直断面図である。また、図10(a)、(b)は、それぞれ図9の破線Xa−Xa、Xb−Xbに沿った半導体装置500の水平断面図である。

【0102】

半導体装置500は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造505と、半導体基板1の半導体素子と多層配線構造505の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0103】

多層配線構造505は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域500aおよび第2の領域500bを区画するガードリング504a、504b、504c、504dと、第1の領域500aの配線層絶縁膜3c中のスルーホールストッパー503と、配線層絶縁膜3dおよびビア層絶縁膜4cを貫通するように形成されたスルーホールストッパー503上のスルーホール502と、第1の領域500aの配線10dが設けられた層のエアギャップ501と、を含む。

【0104】

エアギャップ501は、スルーホール502を通して第1の領域500aの配線層絶縁膜3dを除去することにより形成される。このため、第1の領域500aの配線10dの周囲にエアギャップ501が形成される。

【0105】

スルーホール502は、スルーホールストッパー503をストッパーとして用いて、第1の領域500aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6cをエッチングすることにより形成される。

【0106】

本実施の形態は、ガードリングの一部を一部の層にのみ形成することにより、その直下に配線を形成することができることを示す。

【0107】

例えば、図9、10に示すように、第1の領域500aの配線10dの周囲にエアギャップを形成する場合、配線層絶縁膜3c中にスルーホールストッパー503を形成し、ガードリング504dが第1の領域500aと第2の領域500bとを分離するパターンを有していればよい。ガードリング504a、504b、504cは第1の領域500aと第2の領域500bとを分離するパターンを有する必要はないため、配線10a、10bを第1の領域500aと第2の領域500bをまたぐ位置に形成することができる。図10(b)の配線層絶縁膜3b内の点線は、ガードリング504dの直下に位置する領域を表す。

【0108】

なお、ガードリング504cの配線層絶縁膜3cおよびキャップ膜5c中の部分は、ガードリング504dと同じパターンを有してもよい。ガードリング504cと配線10bが短絡するおそれがないためである。

【0109】

(第5の実施の形態の効果)

本発明の第5の実施の形態によれば、第1の領域500aと第2の領域500bを分離するパターンをガードリング504dのみが有するため、ガードリング504dの直下の第1の領域500aと第2の領域500bをまたぐ位置に配線を形成することができる。

【0110】

〔第6の実施の形態〕

第6の実施の形態は、配線層ごとにガードリングのパターンを変えて、配線層毎にエアギャップの形成される水平方向の領域を制御する。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0111】

(半導体装置の構成)

図11は、本発明の第6の実施の形態に係る半導体装置600の垂直断面図である。図12(a)、(b)、(c)は、それぞれ図11の破線XIIa−XIIa、XIIb−XIIb、XIIc−XIIcに沿った半導体装置600の水平断面図である。

【0112】

半導体装置600は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造605と、半導体基板1の半導体素子と多層配線構造605の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0113】

多層配線構造605は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域600aおよび第2の領域600bを区画するガードリング604a、604b、604c、604dと、第1の領域600aの配線層絶縁膜3c中のスルーホールストッパー603と、配線層絶縁膜3b、3c、3dおよびビア層絶縁膜4a、4b、4cを貫通するように形成されたスルーホールストッパー603上のスルーホール602と、第1の領域600aおよび第2の領域600bの配線10cが設けられた層ならびに第1の領域600aの配線10bが設けられた層のエアギャップ601と、を含む。

【0114】

エアギャップ601は、スルーホール602を通して第1の領域600aおよび第2の領域600bの配線層絶縁膜3cならびに第1の領域600aの配線層絶縁膜3bを除去することにより形成される。このため、第1の領域600aおよび第2の領域600bの配線10cの周囲ならびに第1の領域600aの配線10bの周囲にエアギャップ601が形成される。

【0115】

スルーホール602は、スルーホールストッパー603をストッパーとして用いて、第1の領域600aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6b、キャップ膜5b、配線層絶縁膜3b、ビア層絶縁膜4a、拡散防止膜6aをエッチングすることにより形成される。

【0116】

図12(a)に示すように、ガードリング604dは、スルーホール602を配線が含まれない領域に区画するパターンを有する。このため、配線10dの周囲にはエアギャップ601が形成されない。

【0117】

図12(b)に示すように、ガードリング604cは、第1の領域600aと第2の領域600bを分離しないパターンを有する。このため、第1の領域600aおよび第2の領域600bにおいて、配線10cの周囲にエアギャップ601が形成される。

【0118】

図12(c)に示すように、ガードリング604bは、第1の領域600aと第2の領域600bを分離するパターンを有する。このため、第1の領域600aの配線10bの周囲にエアギャップ601が形成される。

【0119】

(第6の実施の形態の効果)

本発明の第6の実施の形態によれば、配線層ごとにガードリングのパターンを変えることにより、配線層毎にエアギャップの形成される水平方向の領域を制御することができる。

【0120】

〔第7の実施の形態〕

第7の実施の形態は、配線の周囲にエアギャップを形成しない層のガードリングの内側にスルーホールリングを形成し、スルーホールをスルーホールリング内に形成し、配線をガードリングとスルーホールリングの間に形成する。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0121】

(半導体装置の構成)

図13は、本発明の第7の実施の形態に係る半導体装置700の垂直断面図である。図14(a)、(b)は、それぞれ図13の破線XIVa−XIVa、XIVb−XIVbに沿った半導体装置700の水平断面図である。

【0122】

半導体装置700は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造705と、半導体基板1の半導体素子と多層配線構造705の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0123】

多層配線構造705は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に配線を形成する領域を区画するガードリング704a、704b、704c、704dと、配線層絶縁膜3b中のスルーホールストッパー703と、ガードリング704dの内側にスルーホール702を囲むように形成されたスルーホールリング706と、配線層絶縁膜3c、3dおよびビア層絶縁膜4b、4cを貫通するように形成されたスルーホールストッパー703上のスルーホール702と、ガードリング704cの内側の配線10cが設けられた層に形成されたエアギャップ701と、を含む。

【0124】

エアギャップ701は、スルーホール702を通してガードリング704cの内側の配線層絶縁膜3cを除去することにより形成される。このため、ガードリング704cの内側の配線10cの周囲にエアギャップ701が形成される。

【0125】

スルーホール702は、スルーホールストッパー703をストッパーとして用いて、ガードリング704cの内側のハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6bをエッチングすることにより形成される。

【0126】

図14(a)に示すように、スルーホール702は、スルーホールリング706のリングの内側に形成され、配線10dは、ガードリング704dとスルーホールリング706との間に形成される。

【0127】

このため、スルーホール702と配線10dは、スルーホールリング706により分離され、配線10dの周囲にはエアギャップ701が形成されない。

【0128】

また、ガードリング704dとスルーホールリング706は分離して形成されているため、ガードリング704dとスルーホールリング706との間に自由に配線10dをレイアウトすることができる。すなわち、エアギャップを形成しない配線層において、スルーホールの周囲に配線を自由にレイアウトすることができる。

【0129】

図14(b)に示すように、ガードリング604cは、スルーホール702と配線10cを分離しない。このため、配線10cの周囲にエアギャップ701が形成される。

【0130】

(第7の実施の形態の効果)

本発明の第7の実施の形態によれば、エアギャップを形成しない配線層においてスルーホールリングを形成することにより、スルーホールの周囲に配線を自由にレイアウトすることができる。

【0131】

〔他の実施の形態〕

本発明は、上記実施の形態に限定されず、発明の主旨を逸脱しない範囲内において種々変形実施が可能である。

【0132】

また、発明の主旨を逸脱しない範囲内において上記各実施の形態の構成要素を任意に組み合わせることができる。

【符号の説明】

【0133】

100、200、300、400、500、600、700 半導体装置、100a、200a、300a、400a、500a、600a 第1の領域、 100b、200b、300b、400b、500b、600b 第2の領域、 101、201a、201b、301、401、501、601、701 エアギャップ、 102、202a、202b、302、402、502、602、702 スルーホール、 103、203a、203b、303、403、503、603、703 スルーホールストッパー、 104、204a、204b、304、404、504、604、704 ガードリング、 105、205、305、405、505、605、705 多層配線構造、 9 コンタクトプラグ

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

近年の微細化された半導体装置では、多層配線を流れる信号の遅延(RC遅延)が性能低下の大きな要因になっている。信号遅延を低減するためには、多層配線構造の静電容量を減少させることが重要である。そこで、多層配線構造の配線層の絶縁膜を除去することにより形成されるエアギャップ多層配線構造を有する半導体装置が提案されている(例えば、特許文献1参照)。

【0003】

しかし、この特許文献1等に記載の半導体装置によると、配線層の絶縁膜を除去するために配線構造中に形成するスルーホールの深さを制御することが難しく、スルーホールの下の部材にエッチングダメージが生じる等の問題がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−166726号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は、スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供することにある。

【課題を解決するための手段】

【0006】

本発明の一態様は、半導体素子を有する半導体基板と、前記半導体基板の上方に形成され、配線、前記配線の少なくとも一部の周囲に位置するエアギャップ、および前記エアギャップに連続するスルーホールを含む配線構造と、前記スルーホール下に形成されたスルーホールストッパーと、を有する半導体装置を提供する。

【0007】

本発明の他の態様は、半導体素子を有する半導体基板と、前記半導体基板の上方に形成された配線構造と、前記配線構造中において、第1の配線、前記第1の配線の少なくとも一部の周囲に位置する第1のエアギャップ、および前記第1のエアギャップに連続する第1のスルーホールを含む第1の領域と、第2の配線、前記第2の配線の少なくとも一部の周囲に位置する第2のエアギャップ、および前記第2のエアギャップに連続する第2のスルーホールを含む第2の領域とを区画するガードリングと、前記第1のスルーホール下に形成された第1のスルーホールストッパーと、前記第2のスルーホール下に形成され、前記第1のスルーホールストッパーよりも高い位置に形成された第2のスルーホールストッパーと、を有する半導体装置を提供する。

【発明の効果】

【0008】

本発明によれば、スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供することができる。

【図面の簡単な説明】

【0009】

【図1】本発明の第1の実施の形態に係る半導体装置の垂直断面図。

【図2】(a)、(b)は、それぞれ図1の破線IIa−IIa、IIb−IIbに沿った半導体装置の水平断面図。

【図3A】(a)〜(e)は、本発明の第1の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図3B】(f)〜(i)は、本発明の第1の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図3C】(j)〜(l)は、本発明の第1の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図3D】(m)〜(o)は、本発明の第1の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図4】本発明の第2の実施の形態に係る半導体装置の垂直断面図。

【図5】(a)、(b)は、それぞれ図4の破線Va−Va、Vb−Vbに沿った半導体装置の水平断面図。

【図6】本発明の第3の実施の形態に係る半導体装置の垂直断面図。

【図7A】(a)〜(d)は、本発明の第3の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図7B】(e)、(f)は、本発明の第3の実施の形態に係る半導体装置の製造方法を表す垂直断面図。

【図8】本発明の第4の実施の形態に係る半導体装置の垂直断面図。

【図9】本発明の第5の実施の形態に係る半導体装置の垂直断面図。

【図10】(a)、(b)は、それぞれ図9の破線Xa−Xa、Xb−Xbに沿った半導体装置の水平断面図。

【図11】本発明の第6の実施の形態に係る半導体装置の垂直断面図。

【図12】(a)、(b)、(c)は、それぞれ図11の破線XIIa−XIIa、XIIb−XIIb、XIIc−XIIcに沿った半導体装置600の水平断面図。

【図13】本発明の第7の実施の形態に係る半導体装置の垂直断面図。

【図14】(a)、(b)は、それぞれ図13の破線XIVa−XIVa、XIVb−XIVbに沿った半導体装置の水平断面図。

【発明を実施するための形態】

【0010】

〔第1の実施の形態〕

(半導体装置の構成)

図1は、本発明の第1の実施の形態に係る半導体装置100の垂直断面図である。また、図2(a)、(b)は、それぞれ図1の破線IIa−IIa、IIb−IIbに沿った半導体装置100の水平断面図である。

【0011】

半導体装置100は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造105と、半導体基板1の半導体素子と多層配線構造105の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0012】

多層配線構造105は、コンタクト層絶縁膜2上の配線10aを含む配線層絶縁膜3aと、配線層絶縁膜3a上のビア11aを含むビア層絶縁膜4aと、ビア層絶縁膜4a上の配線10bを含む配線層絶縁膜3bと、配線層絶縁膜3b上のビア11bを含むビア層絶縁膜4bと、ビア層絶縁膜4b上の配線10cを含む配線層絶縁膜3cと、配線層絶縁膜3c上のビア11cを含むビア層絶縁膜4cと、ビア層絶縁膜4c上の配線10dを含む配線層絶縁膜3dと、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域100aおよび第2の領域100bを区画するガードリング104a、104b、104c、104dと、第1の領域100aの配線層絶縁膜3b中のスルーホールストッパー103と、配線層絶縁膜3c、3dおよびビア層絶縁膜4b、4cを貫通するように形成されたスルーホールストッパー103上のスルーホール102と、第1の領域100aの配線10c、10dが設けられた層のエアギャップ101と、を含む。なお、多層配線構造105の配線層の数は、4層に限られない。

【0013】

また、配線層絶縁膜3a上にはキャップ膜5aおよび拡散防止膜6aが形成され、配線層絶縁膜3b上にはキャップ膜5bおよび拡散防止膜6bが形成され、配線層絶縁膜3c上にはキャップ膜5cおよび拡散防止膜6cが形成され、配線層絶縁膜3d上にはキャップ膜5dおよび拡散防止膜6dが形成される。また、拡散防止膜6d上にはハードマスク7が形成される。また、スルーホール102の開口部は、スルーホールキャップ膜8により塞がれる。

【0014】

半導体基板1は、Si結晶等のSi系結晶からなる。

【0015】

コンタクト層絶縁膜2は、SiO2等の絶縁材料からなる。

【0016】

配線層絶縁膜3a、3b、3c、3dは、有機絶縁材料等の絶縁材料からなる。配線層絶縁膜3a、3b、3c、3dの誘電率を下げるために、微小空孔を含んだ有機絶縁材料を用いてもよい。

【0017】

ビア層絶縁膜4a、4b、4cは、SiOC等の絶縁材料からなる。ビア層絶縁膜4a、4b、4cの誘電率を下げるために、微小空孔を含んだ絶縁材料を用いてもよい。

【0018】

キャップ膜5a、5b、5c、5dは、SiO2、SiOC等の絶縁材料からなり、配線10a、10b、10c、10dをエッチングや平坦化処理によるダメージから守る機能、およびエアギャップ101上の部材の保持部材としての機能を有する。

【0019】

拡散防止膜6a、6b、6c、6dは、SiN、SiCN、SiON、SiC等の絶縁材料からなる絶縁膜、またはこれらの絶縁膜の積層体である。また、拡散防止膜6a、6b、6c、6dは、配線10a、10b、10c、10dにおける金属元素の表面拡散を抑える機能や、上層の部材を加工する際のストッパーとしての機能を有する。なお、拡散防止膜6a、6b、6c、6dは、配線10a、10b、10c、10dの上面にのみ形成されるものであってもよい。

【0020】

ハードマスク7は、TEOS(Tetraethoxysilane)を原料ガスに用いて形成されるSiO2、SiOC、SiN、TaN、TiN等の絶縁材料からなる絶縁膜、またはこれらの絶縁膜の積層体である。

【0021】

スルーホールキャップ膜8は、スルーホール102の開口部を塞いで、配線構造内への水分等の進入を防ぐ機能を有する。スルーホールキャップ膜8は、SiO2、TEOS、SiOC、SiCN、SiN等の絶縁材料からなる。

【0022】

コンタクトプラグ9は、半導体基板1上の半導体素子(図示しない)と配線10aとを接続する。また、コンタクトプラグ9は、W等の導電材料からなる。また、図示しないが、コンタクトプラグ9の表面に、バリアメタルが形成されてもよい。バリアメタルは、Ta、Ti、Ru、Co、Mn等の金属や、これらの金属の窒化物または酸化物等の導電材料からなる。

【0023】

配線10a、10b、10c、10dは、Cu、W、Al等の導電材料からなる。また、図示しないが、配線10a、10b、10c、10dの表面に、バリアメタルが形成されてもよい。バリアメタルは、Ta、Ti、Ru、Co、Mn等の金属や、これらの金属の窒化物または酸化物等の導電材料からなる。なお、10a、10b、10c、10dのレイアウトは図1、2に示したものに限られない。

【0024】

ビア11aは、配線10aと配線10bを接続し、ビア11bは、配線10bと配線10cを接続し、ビア11cは、配線10cと配線10dを接続する。また、ビア11a、11b、11cは、配線10a、10b、10c、10dと同じ材料からなる。また、図示しないが、ビア11a、11b、11cの表面に、配線10a、10b、10c、10dのものと同じバリアメタルが形成されてもよい。

【0025】

エアギャップ101は、スルーホール102を通して第1の領域100aの配線層絶縁膜3c、3dを除去することにより形成される。このため、第1の領域100aの配線10c、10dの周囲にエアギャップ101が形成される。

【0026】

スルーホール102は、スルーホールストッパー103をストッパーとして用いて、第1の領域100aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6bをエッチングすることにより形成される。

【0027】

スルーホールストッパー103は、例えば、配線10a、10b、10c、10dと同じ材料からなる。図2(b)のスルーホールストッパー103内の点線は、スルーホール102の直下に位置する領域を表す。

【0028】

図1、2においては、スルーホールストッパー103は配線10bが設けられた層に位置するが、他の配線層に形成されてもよい。スルーホールストッパー103がいずれの層に形成された場合も、スルーホールストッパー103よりも上にある配線層絶縁膜が除去され、エアギャップが形成される。例えば、配線10cが設けられた層にスルーホールストッパー103が形成される場合は、第1の領域100aの配線層絶縁膜3dが除去され、配線10dの周囲にエアギャップ101が形成される。

【0029】

また、第1の領域100aのビア層絶縁膜4b、4cを除去して、エアギャップ101をビア11b、11cの設けられた層にも形成することができる。ビア層絶縁膜も除去する場合、スルーホールストッパー103よりも上にある配線層絶縁膜およびビア層絶縁膜が除去され、エアギャップが形成される。

【0030】

スルーホール102を形成する際のエッチングはスルーホールストッパー103により止められるため、スルーホールストッパー103の形成される層よりも下の層にはスルーホール102が形成されない。このため、スルーホール102の直下の領域に配線等の導電部材を形成した場合であっても、スルーホール102を形成する際のエッチングによるダメージから導電部材を保護することができる。例えば、図1に示すように、スルーホール102直下の配線層絶縁膜3a中の領域に配線10aを形成することができる。

【0031】

ガードリング104a、104b、104c、104dは、例えば、配線10a、10b、10c、10dと同じ材料からなる。また、図示しないが、ガードリング104a、104b、104c、104dの表面に、配線10a、10b、10c、10dのものと同じバリアメタルが形成されてもよい。

【0032】

第1の領域100aおよび第2の領域100bは、それぞれガードリング104a、104b、104c、104dによって外部から分離されているため、それぞれの領域内の配線層絶縁膜を選択的に除去し、エアギャップを形成することができる。また、第1の領域100aおよび第2の領域100bは、それぞれガードリング104a、104b、104c、104dによって囲まれているため、外部との電磁的相互作用が低減され、信頼性が向上する。

【0033】

以下に、本実施の形態に係る半導体装置100の製造方法の一例を示す。

【0034】

(半導体装置の製造方法)

図3A(a)〜(e)、図3B(f)〜(i)、図3C(j)〜(l)、図3D(m)〜(o)は、本発明の第1の実施の形態に係る半導体装置100の製造方法を表す垂直断面図である。

【0035】

まず、図3A(a)に示すように、半導体素子(図示しない)が形成された半導体基板上にコンタクト層絶縁膜2をCVD(Chemical Vapor Deposition)法等により形成する。

【0036】

次に、図3A(b)に示すように、コンタクト層絶縁膜2中にコンタクトホール20をリソグラフィ法とRIE(Reactive Ion Etching)の組み合わせ等により形成する。

【0037】

次に、図3A(c)に示すように、コンタクトホール20中にコンタクトプラグ9を形成する。コンタクトプラグ9は、コンタクトホール20を埋めるように半導体基板1上に導電材料を堆積させた後、コンタクトホール20の外側の導電材料を平坦化処理等により除去することにより形成される。

【0038】

次に、図3A(d)に示すように、コンタクト層絶縁膜2およびコンタクトプラグ9上に配線層絶縁膜3aおよびキャップ膜5aを形成する。配線層絶縁膜3aは、塗布法等により形成される。また、キャップ膜5aは、CVD法等により形成される。

【0039】

次に、図3A(e)に示すように、キャップ膜5aおよび配線層絶縁膜3a中に配線溝21aおよびガードリング溝22aをリソグラフィ法とRIEの組み合わせ等により形成する。

【0040】

次に、図3B(f)に示すように、配線溝21aおよびガードリング溝22a中にそれぞれ配線10aおよびガードリング104aを形成し、キャップ膜5a、配線10aおよびガードリング104a上に拡散防止膜6aをCVD法等により形成する。

【0041】

具体的には、配線10aおよびガードリング104aは、例えば以下の工程により形成される。まず、配線溝21aおよびガードリング溝22aの内面を覆うように半導体基板1上にバリアメタルの材料をCVD法、PVD(Physical Vapor Deposition)法、原子層気相成長法等により堆積させ、厚さ5nm程度のバリアメタルの材料膜を形成する。次に、バリアメタルの材料膜上にCuシード膜をCVD法、PVD法、原子層気相成長法等により形成する。次に、Cuシード膜をカソード極として用いて、配線溝21aおよびガードリング溝22aを埋めるようにCuシード膜上にCu膜を電解めっき法等の電気化学成長法により形成する。なお、配線10aおよびガードリング104aの材料であるCuは、PVD法またはCVD法により形成されてもよい。この場合、Cuシード膜を形成しなくてもよい。次に、アニール処理によりCu膜の結晶組織を安定化させる。次に、配線溝21aおよびガードリング溝22aの外側のバリアメタルの材料膜、Cuシード膜およびCu膜をCMP(Chemical Mechanical Polishing)法等による平坦化処理により除去し、配線10a、ガードリング104aおよびそれらの表面のバリアメタルに加工する。

【0042】

次に、図3B(g)に示すように、拡散防止膜6a上にビア層絶縁膜4a、配線層絶縁膜3bおよびキャップ膜5bを形成する。ビア層絶縁膜4aは、CVD法、塗布法等により形成される。配線層絶縁膜3bおよびキャップ膜5bは、それぞれ配線層絶縁膜3aおよびキャップ膜5aと同様の方法により形成される。

【0043】

次に、図3B(h)に示すように、キャップ膜5bおよび配線層絶縁膜3b中に配線溝21bおよびスルーホールストッパー103用の溝105を形成し、ビア層絶縁膜4aおよび拡散防止膜6a中にビアホール23aを形成し、キャップ膜5b、配線層絶縁膜3b、ビア層絶縁膜4aおよび拡散防止膜6a中にガードリング溝22bを形成する。配線溝21b、ビアホール23a、およびガードリング溝22bは、リソグラフィ法とRIEの組み合わせ等により形成される。

【0044】

ここで、配線溝21b、およびガードリング溝22bの上部と同時に溝105を形成することができる。このため、溝105を形成するために工程数を増やす必要はない。

【0045】

なお、溝105は、底がビア層絶縁膜4aに達するように形成されてもよい。この場合、スルーホールストッパー103の一部はビア層絶縁膜4a中に形成される。

【0046】

次に、図3B(i)に示すように、配線溝21b、溝105、ビアホール23a、およびガードリング溝22b中にそれぞれ配線10b、スルーホールストッパー103、ビア11aおよびガードリング104bを形成し、キャップ膜5b、配線10b、スルーホールストッパー103およびガードリング104b上に拡散防止膜6bをCVD法等により形成する。

【0047】

ここで、配線溝21b、ビアホール23a、溝105およびガードリング溝22bには、配線10aおよびガードリング104aと同様の方法により同時に導電材料が埋め込まれ、それぞれ配線10b、ビア11a、スルーホールストッパー103およびガードリング104bが形成される。このため、スルーホールストッパー103を形成するために工程数を増やす必要はない。なお、配線10bおよびビア11aはデュアルダマシン構造を有する。

【0048】

続けて、図3B(g)〜(i)に示した工程と同様の工程を繰り返して配線層絶縁膜3c、3d、ビア層絶縁膜4b、4c、キャップ膜5c、5d、拡散防止膜6c、6d、配線10c、10d、ビア11b、11c、およびガードリング104c、104dを形成する。

【0049】

その後、拡散防止膜6d上にスルーホール102のパターンを有するハードマスク7を形成し、図3C(j)に示す構造を得る。ハードマスク7は、CVD法、スパッタ法等により絶縁膜を形成した後、これをリソグラフィ法とRIE法の組み合わせによりパターニングすることにより形成される。

【0050】

次に、図3C(k)に示すように、ハードマスク7をマスクとして用いて拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4bおよび拡散防止膜6bをRIE法等によりエッチングし、スルーホール102を形成する。

【0051】

このとき、スルーホールストッパー103がエッチングのストッパーとして働き、スルーホール102の底にスルーホールストッパー103の上面が露出する。スルーホール102は、スルーホールストッパー103よりも上に位置する配線層絶縁膜3c、3d内に形成され、スルーホールストッパー103よりも上に位置しない配線層絶縁膜3a、3b内には形成されない。

【0052】

次に、図3C(l)に示すように、第1の領域100aの配線層絶縁膜3c、3dにスルーホール102を通してO2ガスを用いたアッシング処理等を施して、これらを除去する。これにより、第1の領域100aの配線10c、10dの周囲にエアギャップ101が形成される。

【0053】

このとき、スルーホールストッパー103よりも上に位置する配線層絶縁膜3c、3dのみが除去され、スルーホールストッパー103よりも上に位置しない配線層絶縁膜3a、3bは除去されない。

【0054】

次に、図3D(m)に示すように、スルーホールキャップ膜8を塗布法等により形成してスルーホール102の開口部を塞ぐことにより、図1に示した半導体装置100を得る。

【0055】

塗布法によりスルーホールキャップ膜8を形成する場合は、材料として有機絶縁材料、SiO2またはSiOC等が用いられる。

【0056】

この場合、図3D(n)に示すように、スルーホール102の外側のスルーホールキャップ膜8を全面エッチバック等により除去してもよい。

【0057】

また、CVD法等の成膜法において、被覆性の低い成膜条件を用いてスルーホールキャップ膜8を形成してもよい。この場合、図3D(o)に示すように、スルーホールキャップ膜8のスルーホール102の直上の領域に空隙が形成される。

【0058】

CVD法によりスルーホールキャップ膜8を形成する場合は、材料として有機絶縁材料、SiO2、TEOS、SiOC、SiCNまたはSiN等が用いられる。

【0059】

さらに、スルーホールキャップ膜8の防湿性が不十分である場合は、スルーホール102およびエアギャップ101への水分等の進入を防ぐために、スルーホールキャップ膜8上に防湿性に優れた膜を形成してもよい。

【0060】

(第1の実施の形態の効果)

本発明の第1の実施の形態によれば、スルーホールストッパー103を形成することによりスルーホール102の深さを正確に制御し、特定の配線層に選択的にエアギャップを形成することができる。

【0061】

また、スルーホールストッパー103を形成することにより、スルーホール102の直下の領域に配線等の導電部材を形成することができる。

【0062】

〔第2の実施の形態〕

第2の実施の形態は、第1の領域と第2の領域内において、それぞれ異なる層にスルーホールストッパーを形成し、それぞれ異なる層にエアギャップを形成する。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0063】

(半導体装置の構成)

図4は、本発明の第2の実施の形態に係る半導体装置200の垂直断面図である。また、図5(a)、(b)は、それぞれ図4の破線Va−Va、Vb−Vbに沿った半導体装置200の水平断面図である。

【0064】

半導体装置200は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造205と、半導体基板1の半導体素子と多層配線構造205の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0065】

多層配線構造205は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域200aおよび第2の領域200bを区画するガードリング204a、204b、204c、204dと、第1の領域200aの配線層絶縁膜3b中のスルーホールストッパー203aと、第2の領域200bの配線層絶縁膜3c中のスルーホールストッパー203bと、配線層絶縁膜3c、3dおよびビア層絶縁膜4b、4cを貫通するように形成されたスルーホールストッパー203a上のスルーホール202aと、配線層絶縁膜3dおよびビア層絶縁膜4cを貫通するように形成されたスルーホールストッパー203b上のスルーホール202bと、第1の領域200aの配線10c、10dが設けられた層のエアギャップ201aと、第2の領域200bの配線10dが設けられた層のエアギャップ201bと、を含む。

【0066】

エアギャップ201aは、スルーホール202aを通して第1の領域200aの配線層絶縁膜3c、3dを除去することにより形成される。このため、第1の領域200aの配線10c、10dの周囲にエアギャップ201aが形成される。

【0067】

エアギャップ201bは、スルーホール202bを通して第2の領域200bの配線層絶縁膜3dを除去することにより形成される。このため、第2の領域200bの配線10dの周囲にエアギャップ201bが形成される。

【0068】

スルーホール202aは、スルーホールストッパー203aをストッパーとして用いて、第1の領域200aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6bをエッチングすることにより形成される。

【0069】

スルーホール202bは、スルーホールストッパー203bをストッパーとして用いて、第2の領域200bハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6cをエッチングすることにより形成される。

【0070】

スルーホールストッパー203a、203bは、例えば、配線10a、10b、10c、10dと同じ材料からなる。図5(b)のスルーホールストッパー203b内の点線は、スルーホール202bの直下に位置する領域を表す。

【0071】

スルーホールストッパー203a、203bは、異なる配線層に形成される。なお、スルーホールストッパー203a、203bは、それぞれ図4、5に示される層と異なる層に形成されてもよい。スルーホールストッパー203a、203bがいずれの層に形成された場合も、スルーホールストッパー203a、203bよりも上にある配線層絶縁膜が除去され、エアギャップが形成される。

【0072】

(第2の実施の形態の効果)

本発明の第2の実施の形態によれば、スルーホールストッパー203a、203bを異なる配線層に形成することにより、スルーホール202aとスルーホール202bの深さを異ならせ、第1の領域200aのエアギャップ201aが形成される配線層の層数と、第2の領域200bのエアギャップ201bが形成される配線層の層数を異ならせることができる。

【0073】

なお、本実施例を応用して、3つ以上の領域をガードリングにより区画し、それぞれの領域において異なる配線層にエアギャップを形成してもよい。また、ガードリングにより区画される領域に、エアギャップが形成されない領域が含まれていてもよい。

【0074】

〔第3の実施の形態〕

第3の実施の形態は、スルーホールストッパーがビア層絶縁膜中に形成される点において、第1の実施の形態と異なる。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0075】

(半導体装置の構成)

図6は、本発明の第3の実施の形態に係る半導体装置300の垂直断面図である。

【0076】

半導体装置300は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造305と、半導体基板1の半導体素子と多層配線構造305の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0077】

多層配線構造305は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域300aおよび第2の領域300bを区画するガードリング304a、304b、304c、304dと、第1の領域300aのビア層絶縁膜4a中のスルーホールストッパー303と、配線層絶縁膜3b、3c、3dおよびビア層絶縁膜4b、4cを貫通するように形成されたスルーホールストッパー303上のスルーホール302と、第1の領域300aの配線10b、10c、10dが設けられた層のエアギャップ301と、を含む。

【0078】

エアギャップ301は、スルーホール302を通して第1の領域300aの配線層絶縁膜3b、3c、3dを除去することにより形成される。このため、第1の領域300aの配線10b、10c、10dの周囲にエアギャップ301が形成される。

【0079】

スルーホール302は、スルーホールストッパー303をストッパーとして用いて、第1の領域300aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6b、キャップ膜5b、配線層絶縁膜3bをエッチングすることにより形成される。

【0080】

スルーホールストッパー303は、例えば、ビア11a、11b、11cと同じ材料からなる。また、図6においては、スルーホールストッパー303はビア11aが設けられた層に位置するが、他のビア層に形成されてもよい。スルーホールストッパー303がいずれの層に形成された場合も、スルーホールストッパー303よりも上にある配線層絶縁膜が除去され、エアギャップが形成される。

【0081】

本実施例においては、ビア11aと配線10b、ビア11bと配線10c、およびビア11cと配線10dは、シングルダマシン法により別々に形成される。また、ガードリング304a、304b、304c、304dは、シングルダマシン法により、ビア層絶縁膜中の部分と配線層絶縁膜中の部分が別々に形成される。

【0082】

以下に、本実施の形態に係る半導体装置300の製造方法の一例を示す。

【0083】

(半導体装置の製造方法)

図7A(a)〜(d)、図7B(e)、(f)は、本発明の第3の実施の形態に係る半導体装置300の製造方法を表す垂直断面図である。

【0084】

まず、図7A(a)に示すように、図3A(a)〜図3B(f)に示される拡散防止膜6aを形成するまでの工程を第1の実施の形態と同様に行う。

【0085】

次に、図7A(b)に示すように、拡散防止膜6a上にビア層絶縁膜4aを形成する。

【0086】

次に、図7A(c)に示すように、ビア層絶縁膜4aおよび拡散防止膜6a中にビアホール23a、ガードリング溝22bおよびスルーホールストッパー303用の溝305を形成する。

【0087】

次に、7A(d)に示すように、ビアホール23a、ガードリング溝22bおよび溝305中にそれぞれビア11a、ガードリング304bおよびスルーホールストッパー303を形成する。

【0088】

ここで、ビアホール23a、ガードリング溝22bおよび溝305には、同時に導電材料が埋め込まれ、それぞれビア11a、ガードリング304bおよびスルーホールストッパー303が形成される。このため、スルーホールストッパー303を形成するために工程数を増やす必要はない。

【0089】

続けて、図7A(b)〜図7B(f)に示した工程と同様の工程を繰り返して配線層絶縁膜3c、3d、ビア層絶縁膜4b、4c、キャップ膜5c、5d、拡散防止膜6c、6d、配線10c、10d、ビア11b、11c、およびガードリング304c、304dを形成する。

【0090】

その後、ハードマスク7、スルーホール302、エアギャップ301およびスルーホールキャップ膜8を、第1の実施の形態のハードマスク7、スルーホール102、エアギャップ101およびスルーホールキャップ膜8と同様の方法で形成し、図6に示した半導体装置300を得る。

【0091】

(第3の実施の形態の効果)

本発明の第3の実施の形態によれば、配線およびビアをシングルダマシン法を用いて形成することにより、スルーホールストッパーをビア層絶縁膜中に形成することができる。そして、第1の実施の形態と同様の効果を得ることができる。

【0092】

〔第4の実施の形態〕

第4の実施の形態は、スルーホールストッパーがコンタクト層絶縁膜中に形成される点において第1の実施の形態と異なる。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0093】

(半導体装置の構成)

図8は、本発明の第4の実施の形態に係る半導体装置400の垂直断面図である。

【0094】

半導体装置400は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造405と、半導体基板1の半導体素子と多層配線構造405の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0095】

多層配線構造405は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域400aおよび第2の領域400bを区画するガードリング404a、404b、404c、404dと、第1の領域400aのコンタクト層絶縁膜2中のスルーホールストッパー403と、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4cを貫通するように形成されたスルーホールストッパー403上のスルーホール402と、第1の領域400aの配線10a、10b、10c、10dが設けられた層のエアギャップ401と、を含む。

【0096】

エアギャップ401は、スルーホール402を通して第1の領域400aの配線層絶縁膜3a、3b、3c、3dを除去することにより形成される。このため、第1の領域400aの配線10a、10b、10c、10dの周囲にエアギャップ401が形成される。

【0097】

スルーホール402は、スルーホールストッパー403をストッパーとして用いて、第1の領域400aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6b、キャップ膜5b、配線層絶縁膜3b、ビア層絶縁膜4a、拡散防止膜6a、キャップ膜5a、配線層絶縁膜3aをエッチングすることにより形成される。

【0098】

スルーホールストッパー403は、例えば、コンタクトプラグ9と同じ材料からなる。この場合、コンタクトプラグ9を形成する工程において、スルーホールストッパー403をコンタクトプラグ9と同時に形成することができるため、コンタクトプラグ9を形成するために工程数を増やす必要はない。

【0099】

(第4の実施の形態の効果)

本発明の第4の実施の形態によれば、スルーホールストッパーをコンタクト層絶縁膜中に形成することにより、コンタクト層絶縁膜をエッチングダメージから保護しつつ、最下層の配線である配線10aの周囲にもエアギャップを形成することができる。

【0100】

〔第5の実施の形態〕

第5の実施の形態は、ガードリングの一部の直下に配線が形成される点において第1の実施の形態と異なる。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0101】

(半導体装置の構成)

図9は、本発明の第5の実施の形態に係る半導体装置500の垂直断面図である。また、図10(a)、(b)は、それぞれ図9の破線Xa−Xa、Xb−Xbに沿った半導体装置500の水平断面図である。

【0102】

半導体装置500は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造505と、半導体基板1の半導体素子と多層配線構造505の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0103】

多層配線構造505は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域500aおよび第2の領域500bを区画するガードリング504a、504b、504c、504dと、第1の領域500aの配線層絶縁膜3c中のスルーホールストッパー503と、配線層絶縁膜3dおよびビア層絶縁膜4cを貫通するように形成されたスルーホールストッパー503上のスルーホール502と、第1の領域500aの配線10dが設けられた層のエアギャップ501と、を含む。

【0104】

エアギャップ501は、スルーホール502を通して第1の領域500aの配線層絶縁膜3dを除去することにより形成される。このため、第1の領域500aの配線10dの周囲にエアギャップ501が形成される。

【0105】

スルーホール502は、スルーホールストッパー503をストッパーとして用いて、第1の領域500aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6cをエッチングすることにより形成される。

【0106】

本実施の形態は、ガードリングの一部を一部の層にのみ形成することにより、その直下に配線を形成することができることを示す。

【0107】

例えば、図9、10に示すように、第1の領域500aの配線10dの周囲にエアギャップを形成する場合、配線層絶縁膜3c中にスルーホールストッパー503を形成し、ガードリング504dが第1の領域500aと第2の領域500bとを分離するパターンを有していればよい。ガードリング504a、504b、504cは第1の領域500aと第2の領域500bとを分離するパターンを有する必要はないため、配線10a、10bを第1の領域500aと第2の領域500bをまたぐ位置に形成することができる。図10(b)の配線層絶縁膜3b内の点線は、ガードリング504dの直下に位置する領域を表す。

【0108】

なお、ガードリング504cの配線層絶縁膜3cおよびキャップ膜5c中の部分は、ガードリング504dと同じパターンを有してもよい。ガードリング504cと配線10bが短絡するおそれがないためである。

【0109】

(第5の実施の形態の効果)

本発明の第5の実施の形態によれば、第1の領域500aと第2の領域500bを分離するパターンをガードリング504dのみが有するため、ガードリング504dの直下の第1の領域500aと第2の領域500bをまたぐ位置に配線を形成することができる。

【0110】

〔第6の実施の形態〕

第6の実施の形態は、配線層ごとにガードリングのパターンを変えて、配線層毎にエアギャップの形成される水平方向の領域を制御する。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0111】

(半導体装置の構成)

図11は、本発明の第6の実施の形態に係る半導体装置600の垂直断面図である。図12(a)、(b)、(c)は、それぞれ図11の破線XIIa−XIIa、XIIb−XIIb、XIIc−XIIcに沿った半導体装置600の水平断面図である。

【0112】

半導体装置600は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造605と、半導体基板1の半導体素子と多層配線構造605の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0113】

多層配線構造605は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に第1の領域600aおよび第2の領域600bを区画するガードリング604a、604b、604c、604dと、第1の領域600aの配線層絶縁膜3c中のスルーホールストッパー603と、配線層絶縁膜3b、3c、3dおよびビア層絶縁膜4a、4b、4cを貫通するように形成されたスルーホールストッパー603上のスルーホール602と、第1の領域600aおよび第2の領域600bの配線10cが設けられた層ならびに第1の領域600aの配線10bが設けられた層のエアギャップ601と、を含む。

【0114】

エアギャップ601は、スルーホール602を通して第1の領域600aおよび第2の領域600bの配線層絶縁膜3cならびに第1の領域600aの配線層絶縁膜3bを除去することにより形成される。このため、第1の領域600aおよび第2の領域600bの配線10cの周囲ならびに第1の領域600aの配線10bの周囲にエアギャップ601が形成される。

【0115】

スルーホール602は、スルーホールストッパー603をストッパーとして用いて、第1の領域600aのハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6b、キャップ膜5b、配線層絶縁膜3b、ビア層絶縁膜4a、拡散防止膜6aをエッチングすることにより形成される。

【0116】

図12(a)に示すように、ガードリング604dは、スルーホール602を配線が含まれない領域に区画するパターンを有する。このため、配線10dの周囲にはエアギャップ601が形成されない。

【0117】

図12(b)に示すように、ガードリング604cは、第1の領域600aと第2の領域600bを分離しないパターンを有する。このため、第1の領域600aおよび第2の領域600bにおいて、配線10cの周囲にエアギャップ601が形成される。

【0118】

図12(c)に示すように、ガードリング604bは、第1の領域600aと第2の領域600bを分離するパターンを有する。このため、第1の領域600aの配線10bの周囲にエアギャップ601が形成される。

【0119】

(第6の実施の形態の効果)

本発明の第6の実施の形態によれば、配線層ごとにガードリングのパターンを変えることにより、配線層毎にエアギャップの形成される水平方向の領域を制御することができる。

【0120】

〔第7の実施の形態〕

第7の実施の形態は、配線の周囲にエアギャップを形成しない層のガードリングの内側にスルーホールリングを形成し、スルーホールをスルーホールリング内に形成し、配線をガードリングとスルーホールリングの間に形成する。なお、第1の実施の形態と同様の点については、説明を省略または簡略化する。

【0121】

(半導体装置の構成)

図13は、本発明の第7の実施の形態に係る半導体装置700の垂直断面図である。図14(a)、(b)は、それぞれ図13の破線XIVa−XIVa、XIVb−XIVbに沿った半導体装置700の水平断面図である。

【0122】

半導体装置700は、表面に半導体素子(図示しない)を有する半導体基板1と、半導体基板1の上方に形成された多層配線構造705と、半導体基板1の半導体素子と多層配線構造705の配線とを接続するコンタクトプラグ9を含むコンタクト層絶縁膜2と、を有する。

【0123】

多層配線構造705は、配線層絶縁膜3a、3b、3c、3dおよびビア層絶縁膜4a、4b、4c中に配線を形成する領域を区画するガードリング704a、704b、704c、704dと、配線層絶縁膜3b中のスルーホールストッパー703と、ガードリング704dの内側にスルーホール702を囲むように形成されたスルーホールリング706と、配線層絶縁膜3c、3dおよびビア層絶縁膜4b、4cを貫通するように形成されたスルーホールストッパー703上のスルーホール702と、ガードリング704cの内側の配線10cが設けられた層に形成されたエアギャップ701と、を含む。

【0124】

エアギャップ701は、スルーホール702を通してガードリング704cの内側の配線層絶縁膜3cを除去することにより形成される。このため、ガードリング704cの内側の配線10cの周囲にエアギャップ701が形成される。

【0125】

スルーホール702は、スルーホールストッパー703をストッパーとして用いて、ガードリング704cの内側のハードマスク7、拡散防止膜6d、キャップ膜5d、配線層絶縁膜3d、ビア層絶縁膜4c、拡散防止膜6c、キャップ膜5c、配線層絶縁膜3c、ビア層絶縁膜4b、拡散防止膜6bをエッチングすることにより形成される。

【0126】

図14(a)に示すように、スルーホール702は、スルーホールリング706のリングの内側に形成され、配線10dは、ガードリング704dとスルーホールリング706との間に形成される。

【0127】

このため、スルーホール702と配線10dは、スルーホールリング706により分離され、配線10dの周囲にはエアギャップ701が形成されない。

【0128】

また、ガードリング704dとスルーホールリング706は分離して形成されているため、ガードリング704dとスルーホールリング706との間に自由に配線10dをレイアウトすることができる。すなわち、エアギャップを形成しない配線層において、スルーホールの周囲に配線を自由にレイアウトすることができる。

【0129】

図14(b)に示すように、ガードリング604cは、スルーホール702と配線10cを分離しない。このため、配線10cの周囲にエアギャップ701が形成される。

【0130】

(第7の実施の形態の効果)

本発明の第7の実施の形態によれば、エアギャップを形成しない配線層においてスルーホールリングを形成することにより、スルーホールの周囲に配線を自由にレイアウトすることができる。

【0131】

〔他の実施の形態〕

本発明は、上記実施の形態に限定されず、発明の主旨を逸脱しない範囲内において種々変形実施が可能である。

【0132】

また、発明の主旨を逸脱しない範囲内において上記各実施の形態の構成要素を任意に組み合わせることができる。

【符号の説明】

【0133】

100、200、300、400、500、600、700 半導体装置、100a、200a、300a、400a、500a、600a 第1の領域、 100b、200b、300b、400b、500b、600b 第2の領域、 101、201a、201b、301、401、501、601、701 エアギャップ、 102、202a、202b、302、402、502、602、702 スルーホール、 103、203a、203b、303、403、503、603、703 スルーホールストッパー、 104、204a、204b、304、404、504、604、704 ガードリング、 105、205、305、405、505、605、705 多層配線構造、 9 コンタクトプラグ

【特許請求の範囲】

【請求項1】

半導体素子を有する半導体基板と、

前記半導体基板の上方に形成され、配線、前記配線の少なくとも一部の周囲に位置するエアギャップ、および前記エアギャップに連続するスルーホールを含む配線構造と、

前記スルーホール下に形成されたスルーホールストッパーと、

を有する半導体装置。

【請求項2】

前記スルーホールストッパーは前記配線構造中に形成され、

前記スルーホールストッパーの下に下層配線が形成された、

請求項1に記載の半導体装置。

【請求項3】

前記配線構造中において、前記配線、前記スルーホールおよび前記エアギャップを含む領域を区画するガードリングと、

前記配線構造中の前記ガードリングの一部の下に形成された他の配線と、

をさらに有する請求項1または2に記載の半導体装置。

【請求項4】

前記スルーホールストッパーは、前記配線構造と前記半導体素子とを接続するコンタクトプラグと同じ層に形成される、

請求項1に記載の半導体装置。

【請求項5】

半導体素子を有する半導体基板と、

前記半導体基板の上方に形成された配線構造と、

前記配線構造中において、第1の配線、前記第1の配線の少なくとも一部の周囲に位置する第1のエアギャップ、および前記第1のエアギャップに連続する第1のスルーホールを含む第1の領域と、第2の配線、前記第2の配線の少なくとも一部の周囲に位置する第2のエアギャップ、および前記第2のエアギャップに連続する第2のスルーホールを含む第2の領域とを区画するガードリングと、

前記第1のスルーホール下に形成された第1のスルーホールストッパーと、

前記第2のスルーホール下の、前記第1のスルーホールストッパーよりも高い位置に形成された第2のスルーホールストッパーと、

を有する半導体装置。

【請求項1】

半導体素子を有する半導体基板と、

前記半導体基板の上方に形成され、配線、前記配線の少なくとも一部の周囲に位置するエアギャップ、および前記エアギャップに連続するスルーホールを含む配線構造と、

前記スルーホール下に形成されたスルーホールストッパーと、

を有する半導体装置。

【請求項2】

前記スルーホールストッパーは前記配線構造中に形成され、

前記スルーホールストッパーの下に下層配線が形成された、

請求項1に記載の半導体装置。

【請求項3】

前記配線構造中において、前記配線、前記スルーホールおよび前記エアギャップを含む領域を区画するガードリングと、

前記配線構造中の前記ガードリングの一部の下に形成された他の配線と、

をさらに有する請求項1または2に記載の半導体装置。

【請求項4】

前記スルーホールストッパーは、前記配線構造と前記半導体素子とを接続するコンタクトプラグと同じ層に形成される、

請求項1に記載の半導体装置。

【請求項5】

半導体素子を有する半導体基板と、

前記半導体基板の上方に形成された配線構造と、

前記配線構造中において、第1の配線、前記第1の配線の少なくとも一部の周囲に位置する第1のエアギャップ、および前記第1のエアギャップに連続する第1のスルーホールを含む第1の領域と、第2の配線、前記第2の配線の少なくとも一部の周囲に位置する第2のエアギャップ、および前記第2のエアギャップに連続する第2のスルーホールを含む第2の領域とを区画するガードリングと、

前記第1のスルーホール下に形成された第1のスルーホールストッパーと、

前記第2のスルーホール下の、前記第1のスルーホールストッパーよりも高い位置に形成された第2のスルーホールストッパーと、

を有する半導体装置。

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2011−60803(P2011−60803A)

【公開日】平成23年3月24日(2011.3.24)

【国際特許分類】

【出願番号】特願2009−205557(P2009−205557)

【出願日】平成21年9月7日(2009.9.7)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成23年3月24日(2011.3.24)

【国際特許分類】

【出願日】平成21年9月7日(2009.9.7)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]