半導体装置

【課題】ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11上にGaN層12およびAlGaN層13がこの順で形成され、AlGaN層13上にドレイン電極14、ソース電極15およびゲート電極16が形成された半導体装置であって、ゲート電極16の下方には、SiC基板11を貫通するように第1の開口23が形成されている。さらに、GaN層12上に形成され、ソース電極15に接続されるソースパッド19の一部が、SiC基板11の裏面側から露出するように、第2の開口24が形成されている。そして、第1の開口23内にソースフィールドプレート電極25−1を形成すると同時に、第2の開口24から露出するソースパッド19に接触するようにSiC基板11の裏面に接地導体25−2を形成する。

【解決手段】SiC基板11上にGaN層12およびAlGaN層13がこの順で形成され、AlGaN層13上にドレイン電極14、ソース電極15およびゲート電極16が形成された半導体装置であって、ゲート電極16の下方には、SiC基板11を貫通するように第1の開口23が形成されている。さらに、GaN層12上に形成され、ソース電極15に接続されるソースパッド19の一部が、SiC基板11の裏面側から露出するように、第2の開口24が形成されている。そして、第1の開口23内にソースフィールドプレート電極25−1を形成すると同時に、第2の開口24から露出するソースパッド19に接触するようにSiC基板11の裏面に接地導体25−2を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、化合物半導体を用いたトランジスタに関する。

【背景技術】

【0002】

GaNなどの化合物半導体を用いた電界効果トランジスタ(FET:Field effect transistor)や高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)は、優れた高周波特性を有しており、マイクロ波帯で動作する半導体装置として、広く実用化されている。近年、これらのFET、HEMT等の半導体装置において、更なる高性能化が求められている。このため、従来の半導体装置は、フィールドプレート構造が用いられている。以下に、従来のソースフィールドプレート電極を有するHEMTについて説明する。

【0003】

この従来のHEMTは、SiC基板上にGaN層からなる電子走行層が形成され、このGaN層上の一部にAlGaN層からなる電子供給層が形成されている。AlGaN層上には、ドレイン電極およびソース電極が互いに離間して形成されており、これらのドレイン電極とソース電極との間に、ゲート電極が形成されている。

【0004】

また、ソース電極上には、ソースフィールドプレート電極が、ソース電極に接触して形成される。このソースフィールドプレート電極は、ソース電極上から、ゲート電極上を通ってドレイン電極の近傍に至る領域まで延長形成されている。このようにソースフィールドプレート電極を形成することにより、ソースフィールドプレート電極下のポテンシャルは等しくなるため、ソース電極とドレイン電極との間の電気力線を均等に分布させる。従って、ソースフィールドプレート電極が形成されない場合にゲート電極のドレイン電極側端部に集中する電気力線の密度を低下させることができる。これにより、ゲート電極のドレイン側端部が不意に高電位になることによる耐圧の低下や、ゲートリーク電流に起因するバーチャルゲート効果による装置の性能の劣化を抑制することができるため、高性能なHEMTを提供することができる(特許文献1、2等参照)。

【0005】

なお、SiC基板上にGaN層を有し、このGaN層上にドレイン電極、ソース電極およびゲート電極が形成されたFETにおいても、上述と同様にソースフィールドプレート電極が形成されることにより、高性能なFETを提供することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特表2007−537594号公報

【特許文献2】特表2008−533717号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、近年のFETまたはHEMT等の半導体装置は、装置の小型化に伴い、ゲート電極の幅やソース電極とドレイン電極との距離が短くなる傾向がある。従って、ソースフィールドプレート電極とドレイン電極との距離が短くなるため、この間に発生する浮遊容量が大きくなる。さらに、例えば実際に製造されたドレイン電極は、その断面形状が、AlGaN層に接触する部分が広がった台形形状になる。従って、ソースフィールドプレート電極の端部とドレイン電極の広がった部分とが絶縁膜を介して重なり、ソースフィールドプレート電極とドレイン電極との間に発生する浮遊容量が、より大きくなる。この浮遊容量の増大は、半導体装置の性能を劣化させる要因となる。

【0008】

また、ソースフィールドプレート電極は、ゲート電極上に薄い絶縁膜を介して形成されるため、ソースフィールドプレート電極の形成に伴い、ゲート電極の形状がドレイン電極側に傾いた形状になり、これによる装置の性能の劣化も問題であった。

【0009】

そこで、本発明の課題は、ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供することにある。

【課題を解決するための手段】

【0010】

本発明による半導体装置は、基板上に形成された電子走行層と、この電子走行層上に帯状に形成された電子供給層と、この電子供給層上に形成され、前記電子走行層上に形成されたドレインパッドに接続されたドレイン電極と、前記電子供給層上に前記ドレイン電極と離間して形成され、前記電子走行層上に形成されたソースパッドに接続されたソース電極と、このソース電極および前記ドレイン電極の間に形成され、前記電子走行層上に形成されたゲートパッドに接続されたゲート電極と、このゲート電極の下方において、前記基板を貫通するように形成された第1の開口と、前記ソースパッドの一部が前記基板の裏面側から露出するように設けられた第2の開口と、前記第1の開口内に形成されたソースフィールドプレート電極と、前記第2の開口から露出した前記ソースパッドに接触するように前記基板の裏面に設けられ、前記ソースフィールドプレート電極と一体形成された接地導体と、を具備することを特徴とするものである。

【0011】

また、本発明による半導体装置は、基板上に形成された、第1導電型の不純物領域およびこの第1の不純物領域の表面の第2導電型の不純物領域からなる素子領域と、この素子領域の周囲に素子分離層を介して形成された非素子領域と、前記第2導電型の不純物領域上に形成され、前記非素子領域上に形成されたドレインパッドに接続されたドレイン電極と、前記第2導電型の不純物領域上に前記ドレイン電極と離間して形成され、前記非素子領域上に形成されたソースパッドに接続されたソース電極と、このソース電極と前記ドレイン電極との間の前記第2導電型の不純物領域上に形成され、前記非素子領域上に形成されたゲートパッドに接続されたゲート電極と、このゲート電極の下方において、前記基板を貫通するように形成された第1の開口と、前記ソースパッドの一部が前記基板の裏面側から露出するように設けられた第2の開口と、前記第1の開口内に形成されたソースフィールドプレート電極と、前記第2の開口から露出した前記ソースパッドに接触するように前記基板の裏面に設けられ、前記ソースフィールドプレート電極と一体形成された接地導体と、を具備することを特徴とするものである。

【発明の効果】

【0012】

本発明によれば、ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の第1の実施形態に係る半導体装置を示す上面図である。

【図2】図1の一点鎖線A−A´に沿った断面を、拡大して示す部分断面図である。

【図3】図1の一点鎖線B−B´に沿って示す断面図である。

【図4】本発明の第2の実施形態に係る半導体装置を示す上面図である。

【図5】図4の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。

【図6】図4の一点鎖線B−B´に沿って示す断面図である。

【図7】本発明の第3の実施形態に係る半導体装置であって、図4の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。

【図8】本発明の第1の実施形態に係る半導体装置の変形例であって、図1の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。

【図9】本発明の第1の実施形態に係る半導体装置の他の変形例であって、図1の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。

【発明を実施するための形態】

【0014】

以下に、本発明の実施形態の半導体装置について、図面を参照して詳細に説明する。

【0015】

(第1の実施形態)

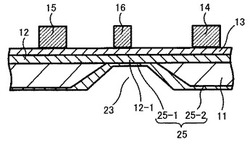

図1は、本発明の第1の実施形態に係る半導体装置を示す上面図である。また、図2は、図1の一点鎖線A−A´に沿った断面の一部を拡大して示す部分断面図であり、図3は、図1の一点鎖線B−B´に沿った断面図である。

【0016】

図2に示すように、本実施形態の半導体装置において、例えばSiC基板11の表面上には、エピタキシャル成長によりGaN層12が形成されている。このGaN層12は、電子走行層となる層である。そして、GaN層12上の一部には、同じくエピタキシャル成長によりアンドープAlGaN層13が形成されている。このAlGaN層13は、電子供給層となる層である。なお、このAlGaN層13は、n型にドーピングされた層であってもよい。

【0017】

図1に示すように、AlGaN層13は、帯状に形成されている。そして、この帯状のAlGaN層13上には、複数のドレイン電極14および複数のソース電極15が、互いに離間して交互に配列形成されており、これらのドレイン電極14とソース電極15との間には、それぞれゲート電極16が形成されている。なお、本実施形態において、AlGaN層13の周囲には、絶縁層は形成されないが、絶縁層が形成されていてもよい。

【0018】

本実施形態の半導体装置は、上述したように、複数のドレイン電極14、複数のソース電極15および複数ゲート電極16を有しており、これらを1つずつ有するHEMT17が列状に複数形成されたものである。

【0019】

GaN層12上において、AlGaN層13の周囲の領域には、ドレインパッド18、ソースパッド19、ゲートバスライン20およびゲートパッド21が形成されている。このうち、ドレインパッド18は、AlGaN層13に沿って形成されており、複数のドレイン電極14は、このドレインパッド18に接続されている。同様に、ソースパッド19は、AlGaN層13を介してドレインパッド18に対向する領域に、AlGaN層13に沿って形成されており、複数のソース電極15は、このソースパッド19に接続されている。さらに、AlGaN層13とソースパッド19との間には、AlGaN層13に沿ってゲートバスライン20が形成されており、複数のゲート電極16は、このゲートバスライン20に接続されている。そして、ソースパッド19を介してゲートバスライン20に対向する領域には、ゲートバスライン20に沿ってゲートパッド21が形成されており、ゲートバスライン20とこのゲートパッド21とは、少なくとも1本の引き出し線22によって接続されている。

【0020】

また、図2に示すように、ゲート電極16の下方には、SiC基板11を貫通するように、テーパ状の第1の開口23が形成されている。この第1の開口23は、SiC基板11の裏面からドライエッチングすることにより形成されている。なお、第1の開口23は、少なくとも、第1の開口23によってGaN層12が露出する部分12−1上にゲート電極16が完全に位置するように形成されればよい。

【0021】

さらに、図3に示すように、ソースパッド19の一部がSiC基板11の裏面側から露出するように、複数のテーパ状の第2の開口24が形成されている。これらの第2の開口24は、SiC基板11の裏面からドライエッチングすることにより、SiC基板11およびGaN層12を貫通するように形成されている。

【0022】

このように第1の開口23および第2の開口24が形成されたSiC基板11の裏面全体には、図2、図3に示すように、例えばAuからなる金属25が蒸着により形成されている。このうち、図2に示すように、第1の開口23からGaN層が露出する部分12−1に形成された金属25は、ソースフィールドプレート電極25−1として機能する。一方で、図2、図3に示すように、SiC基板11の裏面に形成された金属25は、接地導体25−2として機能する。なお、接地導体25−2は、図3に示すように、ソースパッド19に接触して形成されている。

【0023】

上述のソースフィールドプレート電極25−1についてさらに説明すると、従来のソースフィールド電極は、ゲート電極上に薄い絶縁膜を介して形成されることにより、ソースフィールドプレート電極下AlGaN層表面のポテンシャルは等しくなるため、ソース電極とドレイン電極との間の電気力線を均等に分布させる。従って、ゲート電極のドレイン電極側端部に集中する電気力線の密度を低下させる。これに対して本実施形態に係る半導体装置においては、ゲート電極16の下方に、薄いGaN層12およびAlGaN層13を介してソースフィールドプレート電極25−1を形成することにより、従来のソースフィールドプレート電極と同様に、ゲート電極16のドレイン電極14側端部に集中する電気力線の密度を低下させ、ゲート電極16のドレイン側14端部が不意に高電位になることによる耐圧の低下および、ゲートリーク電流に起因するバーチャルゲート効果の影響を軽減し、半導体装置の性能の劣化を抑制させる。

【0024】

以上に説明した本実施形態に係る半導体装置においては、ソースフィールドプレート電極25−1がSiC基板11の裏面側に形成されるため、従来のHEMTを有する半導体装置と比較して、ドレイン電極14とソースフィールドプレート電極25−1の端部との距離を長くすることができる。従って、たとえ、ドレイン電極14が、その断面形状が、AlGaN層13に接触する部分が広がった台形形状になっても、ドレイン電極14とソースフィールドプレート電極25−1との間に発生する浮遊容量を、従来の半導体装置よりも小さくすることができる。従って、浮遊容量に起因する半導体装置の性能の劣化を抑制し、より高性能な半導体装置を実現することができる。

【0025】

また、ソースフィールドプレート電極25−1は、SiC基板11の裏面側に形成されるため、ソースフィールドプレート電極25−1の形成に伴ってゲート電極16の形状が変形することを防止することができる。従って、ゲート電極16の変形に伴う半導体装置の性能の劣化も防止することができる。

【0026】

また、ソースパッド19の下方には、SiC基板11およびGaN層12を貫通する第2の開口24が形成されているため、ソースパッド19に発生する熱の熱抵抗および、ソースパッド19の電気的な抵抗を低下させることができる。従って、熱抵抗および電気的な抵抗に起因する半導体装置の性能の劣化も抑制することができる。

【0027】

(第2の実施形態)

図4は、本発明の第2の実施形態に係る半導体装置を示す上面図である。また、図5は、図4の一点鎖線A−A´に沿った断面の一部を拡大して示す部分断面図であり、図6は、図4の一点鎖線B−B´に沿った断面図である。

【0028】

図5に示すように、本実施形態の半導体装置において、例えばSiC基板31の表面上には、エピタキシャル成長により、GaN層32が形成されている。

【0029】

図4に示すように、GaN層32は、素子領域34−1およびこの周囲の非素子領域34−2により構成され、枠状の素子分離層33により区分けされている。このようなGaN層32のうち、素子領域34−1上には、複数のドレイン電極35および複数のソース電極36が、互いに離間して交互に配列形成されており、これらのドレイン電極35とソース電極36との間には、それぞれゲート電極37が形成されている。

【0030】

本実施形態の半導体装置は、複数のドレイン電極35、複数のソース電極36および複数ゲート電極37を有しており、これらを1つずつ有するFET40が列状に複数形成されたものである。

【0031】

ここで、再び図5を参照すると、少なくとも素子領域34−1は、p型のGaN層34−1からなり、このp型のGaN層32−1の表面には、n型GaN層32−2が形成されている。このn型GaN層32−2は、各FET40毎に形成されている。なお、p型のGaN層32−1とn型GaN層32−2とは、反対の導電型であってもよい。

【0032】

一つのn型GaN層34−2上には、ドレイン電極35およびソース電極36が互いに離間して形成されており、これらの電極35、36間には、ゲート電極37が形成されている。

【0033】

非素子領域34−2上には、ドレインパッド41、ソースパッド42、ゲートバスライン43およびゲートパッド44が形成されている。このうち、ドレインパッド41は、素子領域34−1に沿って形成されており、複数のドレイン電極35は、このドレインパッド41に接続されている。同様に、ソースパッド42は、素子領域34−1を介してドレインパッド41に対向する領域に、素子領域34−1に沿って形成されており、複数のソース電極36は、このソースパッド42に接続されている。さらに、素子領域34−1とソースパッド42との間には、素子領域34−1に沿ってゲートバスライン43が形成されており、複数のゲート電極37は、ゲートバスライン43に接続されている。そして、ソースパッド42を介してゲートバスライン43に対向する領域には、ゲートバスライン43に沿ってゲートパッド44が形成されており、ゲートバスライン43とこのゲートパッド44とは、少なくとも1本の引き出し線45によって接続されている。

【0034】

また、図5に示すように、ゲート電極37の下方には、第1の実施形態と同様に、テーパ状の第1の開口46が形成されている。なお、第1の開口46は、少なくとも、第1の開口46によってp型GaN層32−1が露出する部分32−3上にゲート電極37が完全に位置するように形成されればよい。

【0035】

また、図6に示すように、ソースパッド42の一部がSiC基板31の裏面側から露出するように、複数のテーパ状の第2の開口47が形成されている。これらの第2の開口47も、第1の実施形態と同様に形成されている。

【0036】

このように第1の開口46および第2の開口47が形成されたSiC基板31の裏面全体には、図5、図6に示すように、例えばAuからなる金属48が蒸着により形成されている。このうち、図5に示すように、第1の開口46からGaN層32が露出する部分32−1に形成された金属48は、第1の実施形態と同様に、ソースフィールドプレート電極48−1として機能する。一方で、図5、図6に示すように、SiC基板31の裏面に形成された金属48は、接地導体48−2として機能する。なお、接地導体48−2は、図6に示すように、ソースパッド42に接触して形成されている。

【0037】

以上に説明した本実施形態に係る半導体装置においては、ソースフィールドプレート電極48−1がSiC基板31の裏面側に形成されるため、従来のFETを有する半導体装置と比較して、ドレイン電極35とソースフィールドプレート電極48−1との距離を長くすることができる。従って、たとえ、ドレイン電極35が、その断面形状がn型GaN層32−2に接触する部分が広がった台形形状になっても、ドレイン電極35とソースフィールドプレート電極48−1との間に発生する浮遊容量を、従来の半導体装置よりも小さくすることができる。従って、浮遊容量に起因する半導体装置の性能の劣化を抑制し、より高性能な半導体装置を実現することができる。

【0038】

また、ソースフィールドプレート電極48−1は、SiC基板31の裏面側に形成されるため、ソースフィールドプレート電極48−1の形成に伴ってゲート電極37の形状が変形することを防止することができる。従って、ゲート電極37の変形に伴う半導体装置の性能の劣化も防止することができる。

【0039】

また、ソースパッド42の下方には、SiC基板31およびGaN層32を貫通する第2の開口47が形成されているため、ソースパッド42に発生する熱の熱抵抗および、ソースパッド42の電気的な抵抗を低下させることができる。従って、熱抵抗および電気的な抵抗に起因する半導体装置の性能の劣化も抑制することができる。

【0040】

(第3の実施形態)

次に、第3の実施形態の半導体装置について説明する。なお、この説明においては、第2の実施形態の半導体装置と異なる箇所について説明する。ここで、上面図については、図4と同様であるため、ここでは図4のA−A´に沿った断面の要部を拡大して示す図7を参照して説明する。

【0041】

図7に示すように、本実施形態の半導体装置は、第2の実施形態の半導体装置と比較して、図5に示されるSiC基板31がp型のGaN層32−1と同一材料により構成され、かつ、これらが一体構造である点が異なる。すなわち、第3の実施形態の半導体装置は、p型のGaNからなるバルク型のGaN上にFET40が形成された例である。従って、第2の実施形態における非素子領域34−2も、p型のGaN層からなる。

【0042】

なお、図7に示すように、第1の開口46は、バルク型のGaNの裏面から所定の深さで設けられている。

【0043】

このような第3の実施形態の半導体装置であっても、第2の実施形態の半導体装置と同様の効果を得ることができる。

【0044】

以上に、本発明の実施形態に係る半導体装置について説明した。上述の各実施形態においては、第1の開口23、46の形状は、必ずしもテーパ状の形状である必要はない。図8は、第1の実施形態の半導体装置の変形例であって、図1の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。図8に示すように、第1の開口49の形状は、例えば第1の開口49の内側面が傾斜しない形状であってもよい。なお、第2の実施形態の半導体装置に形成された第1の開口46の形状も同様に、必ずしもテーパ状の形状である必要はなく、図8に示されたような形状であってもよい。

【0045】

また、各実施形態の半導体装置に形成された第2の開口24、47の形状も、必ずしもテーパ状の形状である必要はなく、例えば図7に示されたような形状であってもよい。さらに、第2の開口24、47が形成される数も、図3および図6に示されるように2箇所に限定されない。

【0046】

また、上述の各実施形態の半導体装置において、第1の開口23、46に形成されるソースフィールドプレート電極25−1、48−1の厚さおよび、第2の開口24、47に形成される金属25、48の厚さは、図2、図3および図5、図6に示されるように、必ずしも第1の開口23、46、第2の開口24、47の一部にのみ形成される程度の厚さである必要はない。図9は、第1の実施形態の半導体装置の他の変形例であって、図1の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。図9に示すように、ソースフィールドプレート電極50−1は、例えば第1の開口23を埋める程度の厚さであってもよい。なお、第2の実施形態の半導体装置に形成されたソースフィールドプレート電極48−1の厚さおよび、第1、第2の実施形態の半導体装置が有する第2の開口24、47に形成される金属25、48の厚さも、例えば図9と同様に、第1の開口46、第2の開口24、47を埋める程度の厚さであってもよい。

【0047】

また、上述の各実施形態の半導体装置においては、GaN系の半導体装置の場合について説明した。しかし、本発明は、例えば第1の実施形態の半導体装置においては、電子走行層がGaAs層、電子供給層がAlGaAs層からなる半導体装置においても、同様に適用可能である。その他、GaN系若しくはGaAs系の半導体装置についても、同様に適用可能である。

【0048】

また、上述した各実施形態の半導体装置においては、複数のFET40若しくはHEMT17が形成されたものであったが、FET40若しくはHEMT17の数は限定されず、例えば、GaN系の材料またはGaAs系の材料を用いた単一のFETまたはHEMTからなる半導体装置においても、同様に適用可能である。

【0049】

また、上述の各実施形態の半導体装置において、基板は、SiC基板11、31に限定されるものではなく、Si基板、Al基板、サファイア基板であってもよい。

【符号の説明】

【0050】

11、31・・・SiC基板

12、32・・・GaN層

12−1、32−3・・・第1の開口によって露出する部分

13・・・AlGaN層

14、35・・・ドレイン電極

15、36・・・ソース電極

16、37・・・ゲート電極

17・・・HEMT

18、41・・・ドレインパッド

19、42・・・ソースパッド

20、43・・・ゲートバスライン

21、44・・・ゲートパッド

22、45・・・引き出し線

23、46、49・・・第1の開口

24、47・・・第2の開口

25、48・・・金属

25−1、48−1、50−1・・・ソースフィールドプレート電極

25−2、48−2・・・接地導体

32−1・・・p型GaN層

32−2・・・n型GaN層

33・・・素子分離層

34−1・・・素子領域

34−2・・・非素子領域

40・・・FET

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、化合物半導体を用いたトランジスタに関する。

【背景技術】

【0002】

GaNなどの化合物半導体を用いた電界効果トランジスタ(FET:Field effect transistor)や高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)は、優れた高周波特性を有しており、マイクロ波帯で動作する半導体装置として、広く実用化されている。近年、これらのFET、HEMT等の半導体装置において、更なる高性能化が求められている。このため、従来の半導体装置は、フィールドプレート構造が用いられている。以下に、従来のソースフィールドプレート電極を有するHEMTについて説明する。

【0003】

この従来のHEMTは、SiC基板上にGaN層からなる電子走行層が形成され、このGaN層上の一部にAlGaN層からなる電子供給層が形成されている。AlGaN層上には、ドレイン電極およびソース電極が互いに離間して形成されており、これらのドレイン電極とソース電極との間に、ゲート電極が形成されている。

【0004】

また、ソース電極上には、ソースフィールドプレート電極が、ソース電極に接触して形成される。このソースフィールドプレート電極は、ソース電極上から、ゲート電極上を通ってドレイン電極の近傍に至る領域まで延長形成されている。このようにソースフィールドプレート電極を形成することにより、ソースフィールドプレート電極下のポテンシャルは等しくなるため、ソース電極とドレイン電極との間の電気力線を均等に分布させる。従って、ソースフィールドプレート電極が形成されない場合にゲート電極のドレイン電極側端部に集中する電気力線の密度を低下させることができる。これにより、ゲート電極のドレイン側端部が不意に高電位になることによる耐圧の低下や、ゲートリーク電流に起因するバーチャルゲート効果による装置の性能の劣化を抑制することができるため、高性能なHEMTを提供することができる(特許文献1、2等参照)。

【0005】

なお、SiC基板上にGaN層を有し、このGaN層上にドレイン電極、ソース電極およびゲート電極が形成されたFETにおいても、上述と同様にソースフィールドプレート電極が形成されることにより、高性能なFETを提供することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特表2007−537594号公報

【特許文献2】特表2008−533717号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、近年のFETまたはHEMT等の半導体装置は、装置の小型化に伴い、ゲート電極の幅やソース電極とドレイン電極との距離が短くなる傾向がある。従って、ソースフィールドプレート電極とドレイン電極との距離が短くなるため、この間に発生する浮遊容量が大きくなる。さらに、例えば実際に製造されたドレイン電極は、その断面形状が、AlGaN層に接触する部分が広がった台形形状になる。従って、ソースフィールドプレート電極の端部とドレイン電極の広がった部分とが絶縁膜を介して重なり、ソースフィールドプレート電極とドレイン電極との間に発生する浮遊容量が、より大きくなる。この浮遊容量の増大は、半導体装置の性能を劣化させる要因となる。

【0008】

また、ソースフィールドプレート電極は、ゲート電極上に薄い絶縁膜を介して形成されるため、ソースフィールドプレート電極の形成に伴い、ゲート電極の形状がドレイン電極側に傾いた形状になり、これによる装置の性能の劣化も問題であった。

【0009】

そこで、本発明の課題は、ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供することにある。

【課題を解決するための手段】

【0010】

本発明による半導体装置は、基板上に形成された電子走行層と、この電子走行層上に帯状に形成された電子供給層と、この電子供給層上に形成され、前記電子走行層上に形成されたドレインパッドに接続されたドレイン電極と、前記電子供給層上に前記ドレイン電極と離間して形成され、前記電子走行層上に形成されたソースパッドに接続されたソース電極と、このソース電極および前記ドレイン電極の間に形成され、前記電子走行層上に形成されたゲートパッドに接続されたゲート電極と、このゲート電極の下方において、前記基板を貫通するように形成された第1の開口と、前記ソースパッドの一部が前記基板の裏面側から露出するように設けられた第2の開口と、前記第1の開口内に形成されたソースフィールドプレート電極と、前記第2の開口から露出した前記ソースパッドに接触するように前記基板の裏面に設けられ、前記ソースフィールドプレート電極と一体形成された接地導体と、を具備することを特徴とするものである。

【0011】

また、本発明による半導体装置は、基板上に形成された、第1導電型の不純物領域およびこの第1の不純物領域の表面の第2導電型の不純物領域からなる素子領域と、この素子領域の周囲に素子分離層を介して形成された非素子領域と、前記第2導電型の不純物領域上に形成され、前記非素子領域上に形成されたドレインパッドに接続されたドレイン電極と、前記第2導電型の不純物領域上に前記ドレイン電極と離間して形成され、前記非素子領域上に形成されたソースパッドに接続されたソース電極と、このソース電極と前記ドレイン電極との間の前記第2導電型の不純物領域上に形成され、前記非素子領域上に形成されたゲートパッドに接続されたゲート電極と、このゲート電極の下方において、前記基板を貫通するように形成された第1の開口と、前記ソースパッドの一部が前記基板の裏面側から露出するように設けられた第2の開口と、前記第1の開口内に形成されたソースフィールドプレート電極と、前記第2の開口から露出した前記ソースパッドに接触するように前記基板の裏面に設けられ、前記ソースフィールドプレート電極と一体形成された接地導体と、を具備することを特徴とするものである。

【発明の効果】

【0012】

本発明によれば、ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の第1の実施形態に係る半導体装置を示す上面図である。

【図2】図1の一点鎖線A−A´に沿った断面を、拡大して示す部分断面図である。

【図3】図1の一点鎖線B−B´に沿って示す断面図である。

【図4】本発明の第2の実施形態に係る半導体装置を示す上面図である。

【図5】図4の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。

【図6】図4の一点鎖線B−B´に沿って示す断面図である。

【図7】本発明の第3の実施形態に係る半導体装置であって、図4の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。

【図8】本発明の第1の実施形態に係る半導体装置の変形例であって、図1の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。

【図9】本発明の第1の実施形態に係る半導体装置の他の変形例であって、図1の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。

【発明を実施するための形態】

【0014】

以下に、本発明の実施形態の半導体装置について、図面を参照して詳細に説明する。

【0015】

(第1の実施形態)

図1は、本発明の第1の実施形態に係る半導体装置を示す上面図である。また、図2は、図1の一点鎖線A−A´に沿った断面の一部を拡大して示す部分断面図であり、図3は、図1の一点鎖線B−B´に沿った断面図である。

【0016】

図2に示すように、本実施形態の半導体装置において、例えばSiC基板11の表面上には、エピタキシャル成長によりGaN層12が形成されている。このGaN層12は、電子走行層となる層である。そして、GaN層12上の一部には、同じくエピタキシャル成長によりアンドープAlGaN層13が形成されている。このAlGaN層13は、電子供給層となる層である。なお、このAlGaN層13は、n型にドーピングされた層であってもよい。

【0017】

図1に示すように、AlGaN層13は、帯状に形成されている。そして、この帯状のAlGaN層13上には、複数のドレイン電極14および複数のソース電極15が、互いに離間して交互に配列形成されており、これらのドレイン電極14とソース電極15との間には、それぞれゲート電極16が形成されている。なお、本実施形態において、AlGaN層13の周囲には、絶縁層は形成されないが、絶縁層が形成されていてもよい。

【0018】

本実施形態の半導体装置は、上述したように、複数のドレイン電極14、複数のソース電極15および複数ゲート電極16を有しており、これらを1つずつ有するHEMT17が列状に複数形成されたものである。

【0019】

GaN層12上において、AlGaN層13の周囲の領域には、ドレインパッド18、ソースパッド19、ゲートバスライン20およびゲートパッド21が形成されている。このうち、ドレインパッド18は、AlGaN層13に沿って形成されており、複数のドレイン電極14は、このドレインパッド18に接続されている。同様に、ソースパッド19は、AlGaN層13を介してドレインパッド18に対向する領域に、AlGaN層13に沿って形成されており、複数のソース電極15は、このソースパッド19に接続されている。さらに、AlGaN層13とソースパッド19との間には、AlGaN層13に沿ってゲートバスライン20が形成されており、複数のゲート電極16は、このゲートバスライン20に接続されている。そして、ソースパッド19を介してゲートバスライン20に対向する領域には、ゲートバスライン20に沿ってゲートパッド21が形成されており、ゲートバスライン20とこのゲートパッド21とは、少なくとも1本の引き出し線22によって接続されている。

【0020】

また、図2に示すように、ゲート電極16の下方には、SiC基板11を貫通するように、テーパ状の第1の開口23が形成されている。この第1の開口23は、SiC基板11の裏面からドライエッチングすることにより形成されている。なお、第1の開口23は、少なくとも、第1の開口23によってGaN層12が露出する部分12−1上にゲート電極16が完全に位置するように形成されればよい。

【0021】

さらに、図3に示すように、ソースパッド19の一部がSiC基板11の裏面側から露出するように、複数のテーパ状の第2の開口24が形成されている。これらの第2の開口24は、SiC基板11の裏面からドライエッチングすることにより、SiC基板11およびGaN層12を貫通するように形成されている。

【0022】

このように第1の開口23および第2の開口24が形成されたSiC基板11の裏面全体には、図2、図3に示すように、例えばAuからなる金属25が蒸着により形成されている。このうち、図2に示すように、第1の開口23からGaN層が露出する部分12−1に形成された金属25は、ソースフィールドプレート電極25−1として機能する。一方で、図2、図3に示すように、SiC基板11の裏面に形成された金属25は、接地導体25−2として機能する。なお、接地導体25−2は、図3に示すように、ソースパッド19に接触して形成されている。

【0023】

上述のソースフィールドプレート電極25−1についてさらに説明すると、従来のソースフィールド電極は、ゲート電極上に薄い絶縁膜を介して形成されることにより、ソースフィールドプレート電極下AlGaN層表面のポテンシャルは等しくなるため、ソース電極とドレイン電極との間の電気力線を均等に分布させる。従って、ゲート電極のドレイン電極側端部に集中する電気力線の密度を低下させる。これに対して本実施形態に係る半導体装置においては、ゲート電極16の下方に、薄いGaN層12およびAlGaN層13を介してソースフィールドプレート電極25−1を形成することにより、従来のソースフィールドプレート電極と同様に、ゲート電極16のドレイン電極14側端部に集中する電気力線の密度を低下させ、ゲート電極16のドレイン側14端部が不意に高電位になることによる耐圧の低下および、ゲートリーク電流に起因するバーチャルゲート効果の影響を軽減し、半導体装置の性能の劣化を抑制させる。

【0024】

以上に説明した本実施形態に係る半導体装置においては、ソースフィールドプレート電極25−1がSiC基板11の裏面側に形成されるため、従来のHEMTを有する半導体装置と比較して、ドレイン電極14とソースフィールドプレート電極25−1の端部との距離を長くすることができる。従って、たとえ、ドレイン電極14が、その断面形状が、AlGaN層13に接触する部分が広がった台形形状になっても、ドレイン電極14とソースフィールドプレート電極25−1との間に発生する浮遊容量を、従来の半導体装置よりも小さくすることができる。従って、浮遊容量に起因する半導体装置の性能の劣化を抑制し、より高性能な半導体装置を実現することができる。

【0025】

また、ソースフィールドプレート電極25−1は、SiC基板11の裏面側に形成されるため、ソースフィールドプレート電極25−1の形成に伴ってゲート電極16の形状が変形することを防止することができる。従って、ゲート電極16の変形に伴う半導体装置の性能の劣化も防止することができる。

【0026】

また、ソースパッド19の下方には、SiC基板11およびGaN層12を貫通する第2の開口24が形成されているため、ソースパッド19に発生する熱の熱抵抗および、ソースパッド19の電気的な抵抗を低下させることができる。従って、熱抵抗および電気的な抵抗に起因する半導体装置の性能の劣化も抑制することができる。

【0027】

(第2の実施形態)

図4は、本発明の第2の実施形態に係る半導体装置を示す上面図である。また、図5は、図4の一点鎖線A−A´に沿った断面の一部を拡大して示す部分断面図であり、図6は、図4の一点鎖線B−B´に沿った断面図である。

【0028】

図5に示すように、本実施形態の半導体装置において、例えばSiC基板31の表面上には、エピタキシャル成長により、GaN層32が形成されている。

【0029】

図4に示すように、GaN層32は、素子領域34−1およびこの周囲の非素子領域34−2により構成され、枠状の素子分離層33により区分けされている。このようなGaN層32のうち、素子領域34−1上には、複数のドレイン電極35および複数のソース電極36が、互いに離間して交互に配列形成されており、これらのドレイン電極35とソース電極36との間には、それぞれゲート電極37が形成されている。

【0030】

本実施形態の半導体装置は、複数のドレイン電極35、複数のソース電極36および複数ゲート電極37を有しており、これらを1つずつ有するFET40が列状に複数形成されたものである。

【0031】

ここで、再び図5を参照すると、少なくとも素子領域34−1は、p型のGaN層34−1からなり、このp型のGaN層32−1の表面には、n型GaN層32−2が形成されている。このn型GaN層32−2は、各FET40毎に形成されている。なお、p型のGaN層32−1とn型GaN層32−2とは、反対の導電型であってもよい。

【0032】

一つのn型GaN層34−2上には、ドレイン電極35およびソース電極36が互いに離間して形成されており、これらの電極35、36間には、ゲート電極37が形成されている。

【0033】

非素子領域34−2上には、ドレインパッド41、ソースパッド42、ゲートバスライン43およびゲートパッド44が形成されている。このうち、ドレインパッド41は、素子領域34−1に沿って形成されており、複数のドレイン電極35は、このドレインパッド41に接続されている。同様に、ソースパッド42は、素子領域34−1を介してドレインパッド41に対向する領域に、素子領域34−1に沿って形成されており、複数のソース電極36は、このソースパッド42に接続されている。さらに、素子領域34−1とソースパッド42との間には、素子領域34−1に沿ってゲートバスライン43が形成されており、複数のゲート電極37は、ゲートバスライン43に接続されている。そして、ソースパッド42を介してゲートバスライン43に対向する領域には、ゲートバスライン43に沿ってゲートパッド44が形成されており、ゲートバスライン43とこのゲートパッド44とは、少なくとも1本の引き出し線45によって接続されている。

【0034】

また、図5に示すように、ゲート電極37の下方には、第1の実施形態と同様に、テーパ状の第1の開口46が形成されている。なお、第1の開口46は、少なくとも、第1の開口46によってp型GaN層32−1が露出する部分32−3上にゲート電極37が完全に位置するように形成されればよい。

【0035】

また、図6に示すように、ソースパッド42の一部がSiC基板31の裏面側から露出するように、複数のテーパ状の第2の開口47が形成されている。これらの第2の開口47も、第1の実施形態と同様に形成されている。

【0036】

このように第1の開口46および第2の開口47が形成されたSiC基板31の裏面全体には、図5、図6に示すように、例えばAuからなる金属48が蒸着により形成されている。このうち、図5に示すように、第1の開口46からGaN層32が露出する部分32−1に形成された金属48は、第1の実施形態と同様に、ソースフィールドプレート電極48−1として機能する。一方で、図5、図6に示すように、SiC基板31の裏面に形成された金属48は、接地導体48−2として機能する。なお、接地導体48−2は、図6に示すように、ソースパッド42に接触して形成されている。

【0037】

以上に説明した本実施形態に係る半導体装置においては、ソースフィールドプレート電極48−1がSiC基板31の裏面側に形成されるため、従来のFETを有する半導体装置と比較して、ドレイン電極35とソースフィールドプレート電極48−1との距離を長くすることができる。従って、たとえ、ドレイン電極35が、その断面形状がn型GaN層32−2に接触する部分が広がった台形形状になっても、ドレイン電極35とソースフィールドプレート電極48−1との間に発生する浮遊容量を、従来の半導体装置よりも小さくすることができる。従って、浮遊容量に起因する半導体装置の性能の劣化を抑制し、より高性能な半導体装置を実現することができる。

【0038】

また、ソースフィールドプレート電極48−1は、SiC基板31の裏面側に形成されるため、ソースフィールドプレート電極48−1の形成に伴ってゲート電極37の形状が変形することを防止することができる。従って、ゲート電極37の変形に伴う半導体装置の性能の劣化も防止することができる。

【0039】

また、ソースパッド42の下方には、SiC基板31およびGaN層32を貫通する第2の開口47が形成されているため、ソースパッド42に発生する熱の熱抵抗および、ソースパッド42の電気的な抵抗を低下させることができる。従って、熱抵抗および電気的な抵抗に起因する半導体装置の性能の劣化も抑制することができる。

【0040】

(第3の実施形態)

次に、第3の実施形態の半導体装置について説明する。なお、この説明においては、第2の実施形態の半導体装置と異なる箇所について説明する。ここで、上面図については、図4と同様であるため、ここでは図4のA−A´に沿った断面の要部を拡大して示す図7を参照して説明する。

【0041】

図7に示すように、本実施形態の半導体装置は、第2の実施形態の半導体装置と比較して、図5に示されるSiC基板31がp型のGaN層32−1と同一材料により構成され、かつ、これらが一体構造である点が異なる。すなわち、第3の実施形態の半導体装置は、p型のGaNからなるバルク型のGaN上にFET40が形成された例である。従って、第2の実施形態における非素子領域34−2も、p型のGaN層からなる。

【0042】

なお、図7に示すように、第1の開口46は、バルク型のGaNの裏面から所定の深さで設けられている。

【0043】

このような第3の実施形態の半導体装置であっても、第2の実施形態の半導体装置と同様の効果を得ることができる。

【0044】

以上に、本発明の実施形態に係る半導体装置について説明した。上述の各実施形態においては、第1の開口23、46の形状は、必ずしもテーパ状の形状である必要はない。図8は、第1の実施形態の半導体装置の変形例であって、図1の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。図8に示すように、第1の開口49の形状は、例えば第1の開口49の内側面が傾斜しない形状であってもよい。なお、第2の実施形態の半導体装置に形成された第1の開口46の形状も同様に、必ずしもテーパ状の形状である必要はなく、図8に示されたような形状であってもよい。

【0045】

また、各実施形態の半導体装置に形成された第2の開口24、47の形状も、必ずしもテーパ状の形状である必要はなく、例えば図7に示されたような形状であってもよい。さらに、第2の開口24、47が形成される数も、図3および図6に示されるように2箇所に限定されない。

【0046】

また、上述の各実施形態の半導体装置において、第1の開口23、46に形成されるソースフィールドプレート電極25−1、48−1の厚さおよび、第2の開口24、47に形成される金属25、48の厚さは、図2、図3および図5、図6に示されるように、必ずしも第1の開口23、46、第2の開口24、47の一部にのみ形成される程度の厚さである必要はない。図9は、第1の実施形態の半導体装置の他の変形例であって、図1の一点鎖線A−A´に沿った断面を拡大して示す部分断面図である。図9に示すように、ソースフィールドプレート電極50−1は、例えば第1の開口23を埋める程度の厚さであってもよい。なお、第2の実施形態の半導体装置に形成されたソースフィールドプレート電極48−1の厚さおよび、第1、第2の実施形態の半導体装置が有する第2の開口24、47に形成される金属25、48の厚さも、例えば図9と同様に、第1の開口46、第2の開口24、47を埋める程度の厚さであってもよい。

【0047】

また、上述の各実施形態の半導体装置においては、GaN系の半導体装置の場合について説明した。しかし、本発明は、例えば第1の実施形態の半導体装置においては、電子走行層がGaAs層、電子供給層がAlGaAs層からなる半導体装置においても、同様に適用可能である。その他、GaN系若しくはGaAs系の半導体装置についても、同様に適用可能である。

【0048】

また、上述した各実施形態の半導体装置においては、複数のFET40若しくはHEMT17が形成されたものであったが、FET40若しくはHEMT17の数は限定されず、例えば、GaN系の材料またはGaAs系の材料を用いた単一のFETまたはHEMTからなる半導体装置においても、同様に適用可能である。

【0049】

また、上述の各実施形態の半導体装置において、基板は、SiC基板11、31に限定されるものではなく、Si基板、Al基板、サファイア基板であってもよい。

【符号の説明】

【0050】

11、31・・・SiC基板

12、32・・・GaN層

12−1、32−3・・・第1の開口によって露出する部分

13・・・AlGaN層

14、35・・・ドレイン電極

15、36・・・ソース電極

16、37・・・ゲート電極

17・・・HEMT

18、41・・・ドレインパッド

19、42・・・ソースパッド

20、43・・・ゲートバスライン

21、44・・・ゲートパッド

22、45・・・引き出し線

23、46、49・・・第1の開口

24、47・・・第2の開口

25、48・・・金属

25−1、48−1、50−1・・・ソースフィールドプレート電極

25−2、48−2・・・接地導体

32−1・・・p型GaN層

32−2・・・n型GaN層

33・・・素子分離層

34−1・・・素子領域

34−2・・・非素子領域

40・・・FET

【特許請求の範囲】

【請求項1】

基板上に形成された電子走行層と、

この電子走行層上に帯状に形成された電子供給層と、

この電子供給層上に形成され、前記電子走行層上に形成されたドレインパッドに接続されたドレイン電極と、

前記電子供給層上に前記ドレイン電極と離間して形成され、前記電子走行層上に形成されたソースパッドに接続されたソース電極と、

このソース電極および前記ドレイン電極の間に形成され、前記電子走行層上に形成されたゲートパッドに接続されたゲート電極と、

このゲート電極の下方において、前記基板を貫通するように形成された第1の開口と、

前記ソースパッドの一部が前記基板の裏面側から露出するように設けられた第2の開口と、

前記第1の開口内に形成されたソースフィールドプレート電極と、

前記第2の開口から露出した前記ソースパッドに接触するように前記基板の裏面に設けられ、前記ソースフィールドプレート電極と一体形成された接地導体と、

を具備することを特徴とする半導体装置。

【請求項2】

前記ドレイン電極、前記ソース電極および前記ゲート電極は、それぞれ前記電子供給層上に複数形成され、

複数の前記ドレイン電極と複数の前記ソース電極とは、交互に配列形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記電子走行層は、GaN若しくはGaAsからなり、前記電子供給層は、AlGaN若しくはAlGaAsからなることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

基板上に形成された、第1導電型の不純物領域およびこの第1の不純物領域の表面の第2導電型の不純物領域からなる素子領域と、

この素子領域の周囲に素子分離層を介して形成された非素子領域と、

前記第2導電型の不純物領域上に形成され、前記非素子領域上に形成されたドレインパッドに接続されたドレイン電極と、

前記第2導電型の不純物領域上に前記ドレイン電極と離間して形成され、前記非素子領域上に形成されたソースパッドに接続されたソース電極と、

このソース電極と前記ドレイン電極との間の前記第2導電型の不純物領域上に形成され、前記非素子領域上に形成されたゲートパッドに接続されたゲート電極と、

このゲート電極の下方において、前記基板を貫通するように形成された第1の開口と、

前記ソースパッドの一部が前記基板の裏面側から露出するように設けられた第2の開口と、

前記第1の開口内に形成されたソースフィールドプレート電極と、

前記第2の開口から露出した前記ソースパッドに接触するように前記基板の裏面に設けられ、前記ソースフィールドプレート電極と一体形成された接地導体と、

を具備することを特徴とする半導体装置。

【請求項5】

前記基板は、前記第1導電型の不純物領域と同一材料により構成され、かつ、前記基板と前記第1導電型の不純物領域とは、一体構造であることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記ドレイン電極、前記ソース電極および前記ゲート電極は、それぞれ前記素子領域上に複数形成され、

複数の前記ドレイン電極と複数の前記ソース電極とは、交互に配列形成されていることを特徴とする請求項4または5に記載の半導体装置。

【請求項7】

前記素子領域は、GaN若しくはGaAsからなることを特徴とする請求項4乃至6のいずれかに記載の半導体装置。

【請求項8】

前記第1の開口は、テーパ状の開口であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【請求項9】

前記ソースフィールドプレート電極は、前記第1の開口を埋めるように形成されたことを特徴とする請求項1乃至8のいずれかに記載の半導体装置。

【請求項1】

基板上に形成された電子走行層と、

この電子走行層上に帯状に形成された電子供給層と、

この電子供給層上に形成され、前記電子走行層上に形成されたドレインパッドに接続されたドレイン電極と、

前記電子供給層上に前記ドレイン電極と離間して形成され、前記電子走行層上に形成されたソースパッドに接続されたソース電極と、

このソース電極および前記ドレイン電極の間に形成され、前記電子走行層上に形成されたゲートパッドに接続されたゲート電極と、

このゲート電極の下方において、前記基板を貫通するように形成された第1の開口と、

前記ソースパッドの一部が前記基板の裏面側から露出するように設けられた第2の開口と、

前記第1の開口内に形成されたソースフィールドプレート電極と、

前記第2の開口から露出した前記ソースパッドに接触するように前記基板の裏面に設けられ、前記ソースフィールドプレート電極と一体形成された接地導体と、

を具備することを特徴とする半導体装置。

【請求項2】

前記ドレイン電極、前記ソース電極および前記ゲート電極は、それぞれ前記電子供給層上に複数形成され、

複数の前記ドレイン電極と複数の前記ソース電極とは、交互に配列形成されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記電子走行層は、GaN若しくはGaAsからなり、前記電子供給層は、AlGaN若しくはAlGaAsからなることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

基板上に形成された、第1導電型の不純物領域およびこの第1の不純物領域の表面の第2導電型の不純物領域からなる素子領域と、

この素子領域の周囲に素子分離層を介して形成された非素子領域と、

前記第2導電型の不純物領域上に形成され、前記非素子領域上に形成されたドレインパッドに接続されたドレイン電極と、

前記第2導電型の不純物領域上に前記ドレイン電極と離間して形成され、前記非素子領域上に形成されたソースパッドに接続されたソース電極と、

このソース電極と前記ドレイン電極との間の前記第2導電型の不純物領域上に形成され、前記非素子領域上に形成されたゲートパッドに接続されたゲート電極と、

このゲート電極の下方において、前記基板を貫通するように形成された第1の開口と、

前記ソースパッドの一部が前記基板の裏面側から露出するように設けられた第2の開口と、

前記第1の開口内に形成されたソースフィールドプレート電極と、

前記第2の開口から露出した前記ソースパッドに接触するように前記基板の裏面に設けられ、前記ソースフィールドプレート電極と一体形成された接地導体と、

を具備することを特徴とする半導体装置。

【請求項5】

前記基板は、前記第1導電型の不純物領域と同一材料により構成され、かつ、前記基板と前記第1導電型の不純物領域とは、一体構造であることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記ドレイン電極、前記ソース電極および前記ゲート電極は、それぞれ前記素子領域上に複数形成され、

複数の前記ドレイン電極と複数の前記ソース電極とは、交互に配列形成されていることを特徴とする請求項4または5に記載の半導体装置。

【請求項7】

前記素子領域は、GaN若しくはGaAsからなることを特徴とする請求項4乃至6のいずれかに記載の半導体装置。

【請求項8】

前記第1の開口は、テーパ状の開口であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【請求項9】

前記ソースフィールドプレート電極は、前記第1の開口を埋めるように形成されたことを特徴とする請求項1乃至8のいずれかに記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2011−60912(P2011−60912A)

【公開日】平成23年3月24日(2011.3.24)

【国際特許分類】

【出願番号】特願2009−207442(P2009−207442)

【出願日】平成21年9月8日(2009.9.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成23年3月24日(2011.3.24)

【国際特許分類】

【出願日】平成21年9月8日(2009.9.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]