半導体装置

【課題】工程の増加や占有面積の増加もなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】ESD保護用のN型MOSトランジスタの基板電位固定用P型拡散領域とESD保護用のN型MOSトランジスタのソースおよびドレイン領域との間に設置されたトレンチ分離領域の深さは、内部素子のN型MOSトランジスタの基板電位固定用P型拡散領域と内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さに比べて深く設定されている半導体装置とした。

【解決手段】ESD保護用のN型MOSトランジスタの基板電位固定用P型拡散領域とESD保護用のN型MOSトランジスタのソースおよびドレイン領域との間に設置されたトレンチ分離領域の深さは、内部素子のN型MOSトランジスタの基板電位固定用P型拡散領域と内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さに比べて深く設定されている半導体装置とした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、外部接続端子と内部回路領域との間に前記内部回路領域に形成された内部素子をESDによる破壊から保護するために形成された、ESD保護素子を有する半導体装置に関する。

【背景技術】

【0002】

MOS型トランジスタを有する半導体装置では、外部接続用のPADからの静電気による内部回路の破壊を防止するためのESD保護素子として、N型MOSトランジスタのゲート電位をグランド(Vss)に固定してオフ状態として設置する、いわゆるオフトランジスタが知られている。

【0003】

内部回路素子のESD破壊を防止するために、できる限り多くの割合の静電気パルスをオフトランジスタに引き込みつつ内部回路素子には伝播させない、あるいは早く大きな静電気パルスを遅く小さな信号に変化させてから伝えるようにすることが重要になる。

【0004】

また、オフトランジスタは、他ロジック回路などの内部回路を構成するMOS型トランジスタと異なり、一時に引き込んだ多量の静電気による電流を流しきる必要があるため、数百ミクロンレベルの大きなトランジスタ幅(W幅)にて設定されることが多い。

【0005】

このためオフトランジスタの占有面積は大きく、特に小さなICチップではIC全体のコストアップ原因となるという問題点を有していた。

【0006】

また、オフトランジスタは複数のドレイン領域、ソース領域、ゲート電極を櫛形に組み合わせた形態を取ることが多いが、複数のトランジスタを組み合わせた構造をとることにより、ESD保護用のN型MOSトランジスタ全体で均一な動作をさせることは難しく、例えば外部接続端子からの距離が近い部分に電流集中が起こり、本来のESD保護機能を十分に発揮できずに破壊してしまうことがあった。

【0007】

この改善策として、外部接続端子からの距離に応じて、特にドレイン領域上のコンタクトホールとゲート電極との距離を、外部接続端子からの距離が遠いほど小さくして、トランジスタの動作を速める工夫をした例も提案されている(例えば、特開文献1参照)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平7−45829号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、オフトランジスタの占有面積を小さくしようとして、W幅を小さくすると、十分な保護機能を果たせなくなってしまい。また改善例では、ドレイン領域における、コンタクトからゲート電極までの距離を調整することにより、局所的にトランジスタ動作速度を調整するものであるが、ドレイン領域の幅の縮小化に伴って所望のコンタクト幅を確保できない、近年の高融点金属を含む配線による配線の低抵抗化で、サージの伝播スピードがさらに速くなり、コンタクトとゲート電極までの距離だけでは調整しきれない場合が生じること、などの問題点を有しており、また、内部回路素子のESD破壊を防止するために、内部回路素子に比べて低い電圧でオフトラ動作を可能とし、できる限り多くの割合の静電気パルスをオフトランジスタに引き込みつつ内部回路素子には伝播させないための改善策は開示されていなかった。

【課題を解決するための手段】

【0010】

上記問題点を解決するために、本発明は半導体装置を以下のように構成した。

【0011】

内部回路領域に少なくとも内部素子のN型MOSトランジスタを有し、外部接続端子と前記内部回路領域との間に、前記内部素子のN型MOSトランジスタやその他の内部素子をESDによる破壊から保護するためのESD保護用のN型MOSトランジスタを有する、トレンチ分離領域を有する半導体装置において、前記ESD保護用のN型MOSトランジスタの基板電位固定用P型拡散領域と前記ESD保護用のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さは、前記内部素子のN型MOSトランジスタの基板電位固定用P型拡散領域と前記内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さに比べて深く設定されている半導体装置とした。

【0012】

これらの手段によって、工程の増加や占有面積の増加もなく、ESD保護用のN型MOSトランジスタのバイポーラ動作を継続するためのホールド電圧を内部素子のN型MOSトランジスタのホールド電圧よりも低くすることが可能となり、十分なESD保護機能を持たせたESD保護用のN型MOSトランジスタを有する半導体装置を得ることができる。

【発明の効果】

【0013】

以上説明したように、本発明によれば、内部回路領域に少なくとも内部素子のN型MOSトランジスタを有し、外部接続端子と前記内部回路領域との間に、前記内部素子のN型MOSトランジスタやその他の内部素子をESDによる破壊から保護するためのESD保護用のN型MOSトランジスタを有する、トレンチ分離領域を有する半導体装置において、前記ESD保護用のN型MOSトランジスタの基板電位固定用P型拡散領域と前記ESD保護用のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さは、前記内部素子のN型MOSトランジスタの基板電位固定用P型拡散領域と前記内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さに比べて深く設定されている半導体装置とした。

【0014】

これらの手段によって、工程の増加や占有面積の増加もなく、ESD保護用のN型MOSトランジスタのバイポーラ動作を継続するためのホールド電圧を内部素子のN型MOSトランジスタのホールド電圧よりも低くすることが可能となり、十分なESD保護機能を持たせたESD保護用のN型MOSトランジスタを有する半導体装置を得ることができる。

【図面の簡単な説明】

【0015】

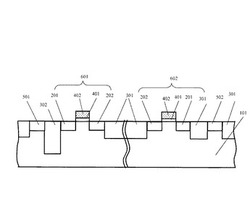

【図1】本発明の半導体装置のESD保護用のN型MOSトランジスタと内部素子のN型MOSトランジスタの1実施例を示す模式的断面図である。

【発明を実施するための形態】

【0016】

以下に、本発明を実施するための形態について図面を参照して説明する。

【実施例1】

【0017】

図1は、本発明の半導体装置のESD保護用のN型MOSトランジスタと内部素子のN型MOSトランジスタの1実施例を示す模式的断面図である。

【0018】

まず、ESD保護用のN型MOSトランジスタ601から説明する。

【0019】

第1導電型半導体基板としてのP型のシリコン基板101上には、一対のN型の高濃度不純物領域からなるソース領域201とドレイン領域202が形成されており、その他の素子との間にはシャロートレンチアイソレーションによる第1のトレンチ分離領域301が形成されて絶縁分離されている。

【0020】

ソース領域201とドレイン領域202の間のP型のシリコン基板101によるチャネル領域の上部にはシリコン酸化膜などからなるゲート絶縁膜401を介してポリシリコン膜などからなるゲート電極402が形成される。また、ESD保護用のN型MOSトランジスタ601の基板電位固定用P型拡散領域501とソース領域201との間には、第2のトレンチ分離領域302が設置される。ここで第2のトレンチ分離領域302の深さは、その他の第1のトレンチ分離領域に比べて深く形成されている。

【0021】

なお、図示しないがソース領域201はゲート電極402と同一のグランド電位(Vss)となるように電気的に接続されており、これによって、ESD保護用のN型MOSトランジスタ601はオフ状態を保持する、いわゆるオフトランジスタの状態を作っている。またドレイン領域202は外部接続端子に接続されている。

【0022】

なお、図1の例では簡単のため、一対のN型の高濃度不純物領域からなるソース領域201とドレイン領域202からなるESD保護用のN型MOSトランジスタしか表さなかったが、実際のESD保護用のN型MOSトランジスタでは、静電気による大電流を流すために大きなトランジスタ幅が必要となり、多数のソースおよびドレイン領域を有する形で形成されることが多くなる。

【0023】

次に、内部素子のN型MOSトランジスタ602について説明する。

第1導電型半導体基板としてのP型のシリコン基板101上には、一対のN型の高濃度不純物領域からなるソース領域201とドレイン領域202が形成されており、その他の素子との間にはシャロートレンチアイソレーションによるトレンチ分離領域301が形成されて絶縁分離されている。

【0024】

ソース領域201とドレイン領域202の間の内部素子のP型シリコン基板101上部にはシリコン酸化膜などからなるゲート絶縁膜401を介してポリシリコン膜などからなるゲート電極402が形成される。内部素子のN型MOSトランジスタ602の基板電位固定用P型拡散領域502とソース領域201との間には、第1のトレンチ分離領域301設置される。なお、簡単のため、内部素子についてN型MOSトランジスタ602のみを図示したが、実際のICにおいてはP型のMOSトランジスタやその他半導体回路を構成する要素素子が多数形成されている。

【0025】

続いて、ESD保護用のN型MOSトランジスタ601と内部素子のN型MOSトランジスタ602を比較しながら、本発明の特徴を説明する。

【0026】

ESD保護用のN型MOSトランジスタ601の基板電位固定用P型拡散領域501と前記ESD保護用のN型MOSトランジスタのソース領域201およびドレイン領域202との間に設置された第2のトレンチ分離領域302の深さは、内部素子のN型MOSトランジスタ602の基板電位固定用P型拡散領域502と前記内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域301に比べて深く設定してある。

【0027】

これによって、ESD保護用のN型MOSトランジスタ601のバイポーラ動作を継続するためのホールド電圧を内部素子のN型MOSトランジスタ602のホールド電圧よりも低くすることが可能となり、外部から大量の電流やパルスが印加された場合、ESD保護用のN型MOSトランジスタ601に早く優先的に流すことができるようになる。このため、十分なESD保護機能を持たせたESD保護用のN型MOSトランジスタ601を有する半導体装置を得ることができる。

【0028】

なお、実施例1では簡便のため、ESD保護用のN型MOSトランジスタ601および、内部素子のN型MOSトランジスタ602はコンベンショナル構造の場合を示したが、ESD保護用のN型MOSトランジスタ601および、内部素子のN型MOSトランジスタ602はDDD構造やオフセットドレイン構造であっても構わない。

【符号の説明】

【0029】

101 P型のシリコン基板

201 ソース領域

202 ドレイン領域

301 第1のトレンチ分離領域

302 第2のトレンチ分離領域

401 ゲート酸化膜

402 ゲート電極

501 ESD保護用のN型のMOSトランジスタ601の基板電位固定用P型拡散領域

502 内部素子のN型MOSトランジスタ602の基板電位固定用P型拡散領域

601 ESD保護用のN型のMOSトランジスタ

602 内部素子のN型MOSトランジスタ

【技術分野】

【0001】

本発明は、外部接続端子と内部回路領域との間に前記内部回路領域に形成された内部素子をESDによる破壊から保護するために形成された、ESD保護素子を有する半導体装置に関する。

【背景技術】

【0002】

MOS型トランジスタを有する半導体装置では、外部接続用のPADからの静電気による内部回路の破壊を防止するためのESD保護素子として、N型MOSトランジスタのゲート電位をグランド(Vss)に固定してオフ状態として設置する、いわゆるオフトランジスタが知られている。

【0003】

内部回路素子のESD破壊を防止するために、できる限り多くの割合の静電気パルスをオフトランジスタに引き込みつつ内部回路素子には伝播させない、あるいは早く大きな静電気パルスを遅く小さな信号に変化させてから伝えるようにすることが重要になる。

【0004】

また、オフトランジスタは、他ロジック回路などの内部回路を構成するMOS型トランジスタと異なり、一時に引き込んだ多量の静電気による電流を流しきる必要があるため、数百ミクロンレベルの大きなトランジスタ幅(W幅)にて設定されることが多い。

【0005】

このためオフトランジスタの占有面積は大きく、特に小さなICチップではIC全体のコストアップ原因となるという問題点を有していた。

【0006】

また、オフトランジスタは複数のドレイン領域、ソース領域、ゲート電極を櫛形に組み合わせた形態を取ることが多いが、複数のトランジスタを組み合わせた構造をとることにより、ESD保護用のN型MOSトランジスタ全体で均一な動作をさせることは難しく、例えば外部接続端子からの距離が近い部分に電流集中が起こり、本来のESD保護機能を十分に発揮できずに破壊してしまうことがあった。

【0007】

この改善策として、外部接続端子からの距離に応じて、特にドレイン領域上のコンタクトホールとゲート電極との距離を、外部接続端子からの距離が遠いほど小さくして、トランジスタの動作を速める工夫をした例も提案されている(例えば、特開文献1参照)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平7−45829号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、オフトランジスタの占有面積を小さくしようとして、W幅を小さくすると、十分な保護機能を果たせなくなってしまい。また改善例では、ドレイン領域における、コンタクトからゲート電極までの距離を調整することにより、局所的にトランジスタ動作速度を調整するものであるが、ドレイン領域の幅の縮小化に伴って所望のコンタクト幅を確保できない、近年の高融点金属を含む配線による配線の低抵抗化で、サージの伝播スピードがさらに速くなり、コンタクトとゲート電極までの距離だけでは調整しきれない場合が生じること、などの問題点を有しており、また、内部回路素子のESD破壊を防止するために、内部回路素子に比べて低い電圧でオフトラ動作を可能とし、できる限り多くの割合の静電気パルスをオフトランジスタに引き込みつつ内部回路素子には伝播させないための改善策は開示されていなかった。

【課題を解決するための手段】

【0010】

上記問題点を解決するために、本発明は半導体装置を以下のように構成した。

【0011】

内部回路領域に少なくとも内部素子のN型MOSトランジスタを有し、外部接続端子と前記内部回路領域との間に、前記内部素子のN型MOSトランジスタやその他の内部素子をESDによる破壊から保護するためのESD保護用のN型MOSトランジスタを有する、トレンチ分離領域を有する半導体装置において、前記ESD保護用のN型MOSトランジスタの基板電位固定用P型拡散領域と前記ESD保護用のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さは、前記内部素子のN型MOSトランジスタの基板電位固定用P型拡散領域と前記内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さに比べて深く設定されている半導体装置とした。

【0012】

これらの手段によって、工程の増加や占有面積の増加もなく、ESD保護用のN型MOSトランジスタのバイポーラ動作を継続するためのホールド電圧を内部素子のN型MOSトランジスタのホールド電圧よりも低くすることが可能となり、十分なESD保護機能を持たせたESD保護用のN型MOSトランジスタを有する半導体装置を得ることができる。

【発明の効果】

【0013】

以上説明したように、本発明によれば、内部回路領域に少なくとも内部素子のN型MOSトランジスタを有し、外部接続端子と前記内部回路領域との間に、前記内部素子のN型MOSトランジスタやその他の内部素子をESDによる破壊から保護するためのESD保護用のN型MOSトランジスタを有する、トレンチ分離領域を有する半導体装置において、前記ESD保護用のN型MOSトランジスタの基板電位固定用P型拡散領域と前記ESD保護用のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さは、前記内部素子のN型MOSトランジスタの基板電位固定用P型拡散領域と前記内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さに比べて深く設定されている半導体装置とした。

【0014】

これらの手段によって、工程の増加や占有面積の増加もなく、ESD保護用のN型MOSトランジスタのバイポーラ動作を継続するためのホールド電圧を内部素子のN型MOSトランジスタのホールド電圧よりも低くすることが可能となり、十分なESD保護機能を持たせたESD保護用のN型MOSトランジスタを有する半導体装置を得ることができる。

【図面の簡単な説明】

【0015】

【図1】本発明の半導体装置のESD保護用のN型MOSトランジスタと内部素子のN型MOSトランジスタの1実施例を示す模式的断面図である。

【発明を実施するための形態】

【0016】

以下に、本発明を実施するための形態について図面を参照して説明する。

【実施例1】

【0017】

図1は、本発明の半導体装置のESD保護用のN型MOSトランジスタと内部素子のN型MOSトランジスタの1実施例を示す模式的断面図である。

【0018】

まず、ESD保護用のN型MOSトランジスタ601から説明する。

【0019】

第1導電型半導体基板としてのP型のシリコン基板101上には、一対のN型の高濃度不純物領域からなるソース領域201とドレイン領域202が形成されており、その他の素子との間にはシャロートレンチアイソレーションによる第1のトレンチ分離領域301が形成されて絶縁分離されている。

【0020】

ソース領域201とドレイン領域202の間のP型のシリコン基板101によるチャネル領域の上部にはシリコン酸化膜などからなるゲート絶縁膜401を介してポリシリコン膜などからなるゲート電極402が形成される。また、ESD保護用のN型MOSトランジスタ601の基板電位固定用P型拡散領域501とソース領域201との間には、第2のトレンチ分離領域302が設置される。ここで第2のトレンチ分離領域302の深さは、その他の第1のトレンチ分離領域に比べて深く形成されている。

【0021】

なお、図示しないがソース領域201はゲート電極402と同一のグランド電位(Vss)となるように電気的に接続されており、これによって、ESD保護用のN型MOSトランジスタ601はオフ状態を保持する、いわゆるオフトランジスタの状態を作っている。またドレイン領域202は外部接続端子に接続されている。

【0022】

なお、図1の例では簡単のため、一対のN型の高濃度不純物領域からなるソース領域201とドレイン領域202からなるESD保護用のN型MOSトランジスタしか表さなかったが、実際のESD保護用のN型MOSトランジスタでは、静電気による大電流を流すために大きなトランジスタ幅が必要となり、多数のソースおよびドレイン領域を有する形で形成されることが多くなる。

【0023】

次に、内部素子のN型MOSトランジスタ602について説明する。

第1導電型半導体基板としてのP型のシリコン基板101上には、一対のN型の高濃度不純物領域からなるソース領域201とドレイン領域202が形成されており、その他の素子との間にはシャロートレンチアイソレーションによるトレンチ分離領域301が形成されて絶縁分離されている。

【0024】

ソース領域201とドレイン領域202の間の内部素子のP型シリコン基板101上部にはシリコン酸化膜などからなるゲート絶縁膜401を介してポリシリコン膜などからなるゲート電極402が形成される。内部素子のN型MOSトランジスタ602の基板電位固定用P型拡散領域502とソース領域201との間には、第1のトレンチ分離領域301設置される。なお、簡単のため、内部素子についてN型MOSトランジスタ602のみを図示したが、実際のICにおいてはP型のMOSトランジスタやその他半導体回路を構成する要素素子が多数形成されている。

【0025】

続いて、ESD保護用のN型MOSトランジスタ601と内部素子のN型MOSトランジスタ602を比較しながら、本発明の特徴を説明する。

【0026】

ESD保護用のN型MOSトランジスタ601の基板電位固定用P型拡散領域501と前記ESD保護用のN型MOSトランジスタのソース領域201およびドレイン領域202との間に設置された第2のトレンチ分離領域302の深さは、内部素子のN型MOSトランジスタ602の基板電位固定用P型拡散領域502と前記内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域301に比べて深く設定してある。

【0027】

これによって、ESD保護用のN型MOSトランジスタ601のバイポーラ動作を継続するためのホールド電圧を内部素子のN型MOSトランジスタ602のホールド電圧よりも低くすることが可能となり、外部から大量の電流やパルスが印加された場合、ESD保護用のN型MOSトランジスタ601に早く優先的に流すことができるようになる。このため、十分なESD保護機能を持たせたESD保護用のN型MOSトランジスタ601を有する半導体装置を得ることができる。

【0028】

なお、実施例1では簡便のため、ESD保護用のN型MOSトランジスタ601および、内部素子のN型MOSトランジスタ602はコンベンショナル構造の場合を示したが、ESD保護用のN型MOSトランジスタ601および、内部素子のN型MOSトランジスタ602はDDD構造やオフセットドレイン構造であっても構わない。

【符号の説明】

【0029】

101 P型のシリコン基板

201 ソース領域

202 ドレイン領域

301 第1のトレンチ分離領域

302 第2のトレンチ分離領域

401 ゲート酸化膜

402 ゲート電極

501 ESD保護用のN型のMOSトランジスタ601の基板電位固定用P型拡散領域

502 内部素子のN型MOSトランジスタ602の基板電位固定用P型拡散領域

601 ESD保護用のN型のMOSトランジスタ

602 内部素子のN型MOSトランジスタ

【特許請求の範囲】

【請求項1】

内部回路領域に少なくとも内部素子のN型MOSトランジスタを有し、外部接続端子と前記内部回路領域との間に、前記内部素子のN型MOSトランジスタやその他の内部素子をESDによる破壊から保護するためのESD保護用のN型MOSトランジスタを有する、トレンチ分離領域を有する半導体装置において、前記ESD保護用のN型MOSトランジスタの基板電位固定用P型拡散領域と前記ESD保護用のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さは、前記内部素子のN型MOSトランジスタの基板電位固定用P型拡散領域と前記内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さに比べて深く設定されている半導体装置。

【請求項2】

前記ESD保護用のN型MOSトランジスタおよび、前記内部素子のN型MOSトランジスタはDDD構造である請求項1記載の半導体装置。

【請求項3】

前記ESD保護用のN型MOSトランジスタおよび前記内部素子のN型MOSトランジスタは、オフセットドレイン構造である請求項1記載の半導体装置。

【請求項1】

内部回路領域に少なくとも内部素子のN型MOSトランジスタを有し、外部接続端子と前記内部回路領域との間に、前記内部素子のN型MOSトランジスタやその他の内部素子をESDによる破壊から保護するためのESD保護用のN型MOSトランジスタを有する、トレンチ分離領域を有する半導体装置において、前記ESD保護用のN型MOSトランジスタの基板電位固定用P型拡散領域と前記ESD保護用のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さは、前記内部素子のN型MOSトランジスタの基板電位固定用P型拡散領域と前記内部素子のN型MOSトランジスタのソースおよびドレイン領域との間に設置された前記トレンチ分離領域の深さに比べて深く設定されている半導体装置。

【請求項2】

前記ESD保護用のN型MOSトランジスタおよび、前記内部素子のN型MOSトランジスタはDDD構造である請求項1記載の半導体装置。

【請求項3】

前記ESD保護用のN型MOSトランジスタおよび前記内部素子のN型MOSトランジスタは、オフセットドレイン構造である請求項1記載の半導体装置。

【図1】

【公開番号】特開2011−71327(P2011−71327A)

【公開日】平成23年4月7日(2011.4.7)

【国際特許分類】

【出願番号】特願2009−221241(P2009−221241)

【出願日】平成21年9月25日(2009.9.25)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

【公開日】平成23年4月7日(2011.4.7)

【国際特許分類】

【出願日】平成21年9月25日(2009.9.25)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

[ Back to top ]