半導体装置

【課題】高電圧が印加される金属電極による耐圧低下を緩和する半導体装置を提供する。

【解決手段】高電位島領域101内のn-半導体層3とp-半導体基板1との界面にはn+埋め込み不純物領域2が形成されている。n+埋め込み不純物領域2の上方ではn-半導体層3表面にpチャネルMOSFET130が形成されている。p+不純物領域6及びn+不純物領域45を有するダイオード102が、領域105内のn-半導体層3表面に形成されている。n+不純物領域45に接続された金属電極14は、p+不純物領域6及びp+不純物領域4の上方を通ってpチャネルMOSFET130に接続される。p+不純物領域6に接続されたp-不純物領域61は金属電極14の下方に位置している。p-半導体基板1及びp+不純物領域4は、p+不純物領域6及びn+不純物領域45よりも低い電位が与えられる。

【解決手段】高電位島領域101内のn-半導体層3とp-半導体基板1との界面にはn+埋め込み不純物領域2が形成されている。n+埋め込み不純物領域2の上方ではn-半導体層3表面にpチャネルMOSFET130が形成されている。p+不純物領域6及びn+不純物領域45を有するダイオード102が、領域105内のn-半導体層3表面に形成されている。n+不純物領域45に接続された金属電極14は、p+不純物領域6及びp+不純物領域4の上方を通ってpチャネルMOSFET130に接続される。p+不純物領域6に接続されたp-不純物領域61は金属電極14の下方に位置している。p-半導体基板1及びp+不純物領域4は、p+不純物領域6及びn+不純物領域45よりも低い電位が与えられる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は半導体装置、特にブートストラップダイオードを備える高耐圧IC(以後、「HVIC」と呼ぶ)に関する。

【背景技術】

【0002】

図29は従来のHVIC110及びその周辺回路を示す回路図である。図29に示すように、従来のHVIC110はブートストラップダイオード102と高電位島領域101に形成されているロジック回路103とを備えている。また、HVIC110の周辺にはブートストラップ容量200がロジック回路103と並列に設けられている。ブートストラップダイオード102のカソードはロジック回路103の一端に接続されている。そして、電圧源150Lはブートストラップダイオード102のアノードに接続されている。

【0003】

次に図29で示した回路図の動作について説明する。電圧源150Lの電圧がロジック回路103の他端の電位を決定する仮想的な可変電圧源である仮想電圧源150Hの電圧よりも高いとき、ブートストラップダイオード102が順バイアスされ、電圧源150Lからロジック回路103に電圧が供給される。また、ブートストラップ容量200に電荷が充電され、ブートストラップダイオード102の順方向電圧をVrec、電圧源150Lの電圧をV1として、ブートストラップダイオード102のカソードの電位はV1−Vrecまで上昇する。

【0004】

次にブートストラップ容量200が充電された状態で仮想電圧源150Hの電圧がΔV(>Vrec)上昇すると、ブートストラップダイオード102のカソードの電位はV1−Vrec+ΔV(>V1)となる。そのためブートストラップダイオード102は逆バイアスされ、電圧源150Lからロジック回路103への電流供給が停止される。このときロジック回路103にはブートストラップ容量200に充電された電荷が供給される。

【0005】

図30は従来のHVIC110の構造を模式的に示す平面図であって、図31は図30の矢視F−Fにおける断面図である。図30では図面の煩雑さを避けるために、図31での絶縁膜8の記載を省略し、絶縁膜18上に形成されている各電極のうち、ブートストラップダイオード102のカソード電極15、アノード電極16及び金属電極14のみを記載している。従来のHVIC110はRESURF(REduced SURface Field)効果を利用して、ロジック回路103とブートストラップダイオード102とを分離している。

【0006】

図30,31に示すように、従来のHVIC110ではp-半導体基板1上にn-半導体層3が形成されている。p-半導体基板1とn-半導体層3との界面にはn+埋め込み不純物領域2が選択的に形成されており、その上方のn-半導体層3の表面にはロジック回路103が形成されている。そして、n+埋め込み不純物領域2の略端部には、n-半導体層3の表面からn+埋め込み不純物領域2にかけてn+不純物領域5が形成されており、ロジック回路103を取り囲んでいる。

【0007】

n+不純物領域5はn+不純物領域5aとn+不純物領域5bとを有している。n+不純物領域5aはn-半導体層3の表面上に形成されており、後述する金属電極55と接続される。n+不純物領域5bはn+不純物領域5aと接続されてn+埋め込み不純物領域2まで延びている。

【0008】

また、n+不純物領域5と離れてロジック回路103と反対側にp+不純物領域7がn-半導体層3の表面に形成されており、ロジック回路103及びn+不純物領域5を取り囲んでいる。そして、p+不純物領域7とn+不純物領域5との間のn-半導体層3の表面には酸化膜12が形成されており、その酸化膜12上には電極19bが形成されている。この電極19bはいわゆる「マルチフィールドプレート」を形成しており、耐圧向上を担っている。

【0009】

ロジック回路103は例えばpチャネルMOSFET130を備えている。pチャネルMOSFET130は、p+型のドレイン領域31とソース領域32及びゲート電極36を有している。ドレイン領域31とソース領域32とは所定距離を成してn-半導体層3の表面に形成されており、ゲート電極36はドレイン領域31とソース領域32とで挟まれたn-半導体層3上にゲート絶縁膜34を介して形成されている。また、ドレイン領域31の隣には酸化膜12を介してn+不純物領域30がn-半導体層3の表面に形成されている。

【0010】

埋め込み不純物領域28は埋め込み不純物領域2と離れてp-半導体基板1とn-半導体層3との界面に選択的に形成されている。この埋め込み不純物領域28からn-半導体層3の表面にかけて、ブートストラップダイオード102のカソード領域であるn+不純物領域45が形成されている。n+不純物領域45はn+不純物領域45aとn+不純物領域45bとを有している。n+不純物領域45aはn-半導体層3の表面上に形成されており、後述するカソード電極15と接続される。n+不純物領域45bはn+不純物領域45aと接続されてn+埋め込み不純物領域28まで延びている。

【0011】

ブートストラップダイオード102のアノード領域であるp+不純物領域6は、p+不純物領域7と離れて、n+不純物領域45を取り囲むようにn-半導体層3の表面に形成されている。n+不純物領域45とp+不純物領域6との間のn-半導体層3の表面には酸化膜12が形成されており、その酸化膜12上には電極19aが形成されている。この電極19aもマルチフィールドプレートを形成している。

【0012】

p+不純物領域7とp+不純物領域6との間には、p-半導体基板1とn-半導体層3との界面からn-半導体層3の表面にかけてp+不純物領域4が形成されており、p+不純物領域4はp+不純物領域7のみと接続している。また、p+不純物領域4はn+不純物領域45及びp+不純物領域6を取り囲むように形成され、かつp+不純物領域7、n+不純物領域5及びロジック回路103を取り囲むように形成されている。つまり、ブートストラップダイオード102と高電位島領域101とはp+不純物領域4で分離されている。

【0013】

絶縁膜18はn-半導体層3、酸化膜12、ゲート電極36及び電極19a,19bを覆うように形成されている。そして絶縁膜18を貫通して、p+不純物領域6にはアノード電極16、n+不純物領域45にはカソード電極15、n+不純物領域5には金属電極55が接続されている。また、ドレイン領域31、ソース領域32、ゲート電極36及びn+不純物領域30のそれぞれには絶縁膜18を貫通して金属電極35が接続されている。カソード電極15は金属電極14によって金属電極55に接続されており、ドレイン領域31及びn+不純物領域30上の金属電極35にも接続されている。この結果、図29に示すようにブートストラップダイオード102のカソードとロジック回路103とが接続される。また、電極19aの上方の絶縁膜18上には金属電極50がフローティングで配置されており、電極19aとの容量結合により耐圧を向上している。そして、絶縁膜18上には各電極を覆うように絶縁膜8が形成されている。

【0014】

次に図30で示している分離領域104及び領域105について説明する。ロジック回路103はn+不純物領域5に取り囲まれ、さらにn+不純物領域5の外側のp+不純物領域4によって取り囲まれている。p+不純物領域4とn+不純物領域5との間のn-半導体層3は、RESURF効果によって空乏層に覆われる。具体的には、例えばp-半導体基板1及びp+不純物領域4がグランド電位に接続され、n-半導体層3及びn+不純物領域5に正の電圧が印加される際、p-半導体基板1及びp+不純物領域4と、n-半導体層3及びn+不純物領域5とで形成されるpn接合には逆電圧が印加されることになり、RESURF効果によって、p+不純物領域4とn+不純物領域5との間のn-半導体層3はその全領域にわたって空乏層が形成される。分離領域104はこの空乏層が形成される領域を示している。ここで、ロジック回路103はn+不純物領域5及びp+不純物領域4によって取り囲まれているが、言い換えれば、図30に示すようにロジック回路103は分離領域104に取り囲まれている。

【0015】

n+不純物領域45とp+不純物領域4との間のn-半導体層3は、上述と同様にRESURF効果によってその全領域に空乏層が形成される。つまり、p+不純物領域4によって取り囲まれ、ブートストラップダイオード102が形成されているn-半導体層3は、そのほぼ全領域が空乏層に覆われることになる。領域105はこの空乏層が形成されている領域を示している。

【発明の概要】

【発明が解決しようとする課題】

【0016】

上述のような構造を備える従来のHVIC110は、p-半導体基板1とn-半導体層3とのRESURF効果によって、n-半導体層3の表面まで空乏層で覆われ高耐圧を実現している。しかし、p-半導体基板1と接続されているp+不純物領域4の上には、例えば数百Vもの高電圧が印加される金属電極14が配置されているため、n-半導体層3内での空乏層の広がりが阻害される。その結果、耐圧が低下するという問題があった。

【0017】

そこで、本発明は上述のような問題を解決するためになされたものであり、高電圧が印加される金属電極による耐圧低下を緩和する半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0018】

本発明に係る第1の半導体装置は、p型の半導体基板と、前記半導体基板上に形成されたn型の半導体層と、前記半導体層の表面から前記半導体基板との界面にかけて前記半導体層内部に形成され、第1の島領域と第2の島領域とを区分する前記p型の第1不純物領域と、前記第1の島領域内の前記半導体層と前記半導体基板との界面に前記第1不純物領域と離れて形成された、前記半導体層よりも高濃度の前記n型の埋め込み不純物領域と、前記埋め込み不純物領域の上方で前記半導体層表面に形成された半導体素子と、前記第2の島領域内の前記半導体層表面に形成された前記p型の第2不純物領域及び前記n型の第3不純物領域を有し、前記第2不純物領域は前記第3不純物領域よりも前記半導体素子側に位置するダイオードと、前記第3不純物領域に接続され、前記第2不純物領域及び前記第1不純物領域の上方を通って前記半導体素子に接続される金属電極と、前記第2不純物領域に接続されて、前記金属電極の下方に位置するように前記半導体層表面に形成される、前記第2不純物領域より低濃度の前記p型の第4不純物領域とを備え、前記半導体基板及び前記第1不純物領域は前記第2不純物領域及び前記第3不純物領域よりも低い電位が与えられるものである。

【0019】

また、本発明に係る第2の半導体装置は、p型の半導体基板と、前記半導体基板上に形成されたn型の半導体層と、前記半導体層の表面から前記半導体基板との界面にかけて前記半導体層内部に形成され、第1の島領域と第2の島領域とを区分する前記p型の第1不純物領域と、前記第1の島領域内の前記半導体層と前記半導体基板との界面に前記第1不純物領域と離れて形成された、前記半導体層よりも高濃度の前記n型の埋め込み不純物領域と、前記埋め込み不純物領域の上方で前記半導体層表面に形成された半導体素子と、前記第2の島領域内の前記半導体層表面に形成された前記p型の第2不純物領域及び前記n型の第3不純物領域を有するダイオードと、前記第3不純物領域に接続され、前記第1不純物領域の上方を通って前記半導体素子に接続される金属電極と、前記第1不純物領域に接続されて、前記金属電極の下方に位置するように前記半導体層表面に形成される、前記第1不純物領域より低濃度の前記p型の第4不純物領域とを備え、前記半導体基板及び前記第1不純物領域は前記第2不純物領域及び前記第3不純物領域よりも低い電位が与えられるものである。

【発明の効果】

【0020】

本発明に係る第1の半導体装置によれば、金属電極の下方に第2不純物領域に接続されて第4不純物領域が形成されているため、ダイオードに逆方向電圧が印加されたとき、第4不純物領域の半導体層との接合部分から空乏層が形成される。そのため、第1不純物領域の上方を通る金属電極に高電圧が印加され、半導体層での空乏層の広がりが抑制されたとしても、耐圧低下を減少することができる。

【0021】

また、本発明に係る第2の半導体装置によれば、金属電極の下方に第1不純物領域に接続されて第4不純物領域が形成され、半導体基板及び第1不純物領域は第2不純物領域及び第3不純物領域よりも低い電位が与えられるため、ダイオードに逆方向電圧が印加されたとき、第4不純物領域の半導体層との接合部分から空乏層が形成される。そのため、第1不純物領域の上方を通る金属電極に高電圧が印加され、半導体層での空乏層の広がりが抑制されたとしても、耐圧低下を減少することができる。

【図面の簡単な説明】

【0022】

【図1】本実施の形態1のHVIC100及びその周辺回路を示す回路図である。

【図2】本実施の形態1に係るHVIC100の構造を模式的に示す平面図である。

【図3】本実施の形態1に係るHVIC100の構造を模式的に示す断面図である。

【図4】本実施の形態1に係るHVIC100の構造を模式的に示す断面図である。

【図5】本実施の形態1に係るHVIC100のn-半導体層3が空乏層に覆われる様子を示した図である。

【図6】本実施の形態1に係るHVIC100に形成される寄生バイポーラトランジスタの様子を示す図である。

【図7】本実施の形態2に係るHVICの構造を模式的に示す平面図である。

【図8】本実施の形態2に係るHVICの構造を模式的に示す断面図である。

【図9】本実施の形態2に係るHVICの構造を模式的に示す断面図である。

【図10】本実施の形態2に係るHVICのホール及び電子の動きを示した図である。

【図11】本実施の形態2に係るHVICのホール及び電子の動きを示した図である。

【図12】ブートストラップダイオード102のリカバリー特性を示す図である。

【図13】本実施の形態3に係るHVICの構造を模式的に示す平面図である。

【図14】本実施の形態3に係るHVICの利点を説明するための図である。

【図15】本実施の形態4に係るHVICの構造を模式的に示す平面図である。

【図16】本実施の形態4に係るHVICの構造を模式的に示す平面図である。

【図17】図18と図19との位置関係を示す説明図である。

【図18】本実施の形態5に係るHVICの構造を模式的に示す平面図である。

【図19】本実施の形態5に係るHVICの構造を模式的に示す平面図である。

【図20】本実施の形態5に係るHVICの構造を拡大して示す平面図である。

【図21】本実施の形態5に係るHVICの構造を拡大して示す平面図である。

【図22】本実施の形態5に係るHVICの構造を模式的に示す断面図である。

【図23】図24と図25との位置関係を示す説明図である。

【図24】本実施の形態5に係るHVICの変形例の構造を示す平面図である。

【図25】本実施の形態5に係るHVICの変形例の構造を示す平面図である。

【図26】本実施の形態5に係るHVICの変形例の構造を拡大して示す平面図である。

【図27】本実施の形態5に係るHVICの変形例の構造を拡大して示す平面図である。

【図28】本実施の形態5に係るHVICの変形例の構造を示す断面図である。

【図29】従来のHVIC110及びその周辺回路を示す回路図である。

【図30】従来のHVIC110の構造を模式的に示す平面図である。

【図31】従来のHVIC110の構造を模式的に示す断面図である。

【発明を実施するための形態】

【0023】

実施の形態1.

図1は本実施の形態1に係るHVIC100及びその周辺回路を示す回路図である。図1に示すように、本実施の形態1のHVIC100は高電位島領域101に、ロジック回路103とそのロジック回路103の一端にカソードが接続されているブートストラップダイオード102とを備えている。また、HVIC100の周辺にはブートストラップ容量200がロジック回路103と並列に接続されて設けられている。そして、電圧源150Lはブートストラップダイオード102のアノードに接続されている。なお、電圧源150Lは例えば定電圧源であり、仮想電圧源150Hは後述するように仮想的な可変電圧源である。

【0024】

次に図1で示した回路図の動作について説明する。ブートストラップダイオード102のカソード及びブートストラップ容量200の一端は、例えばロジック回路103のプラス電源に接続されている。また、ブートストラップ容量200の他端は、例えばロジック回路103のマイナス電源と共に、図示されない負荷に接続される。その接続点の電位は負荷の状態によって変動するので、仮想電圧源150Hによって与えられると見ることができる。ここで、電圧源150Lが発生するグランド電位に対する電位(以後、グランド電位に対する電位を単に「電圧」と呼ぶ)をV1、仮想電圧源150Hが発生する初期電圧をV2とする。ブートストラップ容量200に電荷が充電されていない状態で、V1>V2を満足する電圧V1,V2を電圧源150L,仮想電圧源150Hがそれぞれ発生すると、ブートストラップダイオード102が順バイアスされ、ロジック回路103のプラス電源に電圧V1が印加される。そして、電圧(V1−V2)がブートストラップ容量200に充電される。これによりロジック回路103には電圧(V1−V2)が印加され、動作する。ロジック回路103のプラス電源に印加される電圧は、厳密にはV1からブートストラップダイオード102の順方向電圧降下分を引いた値であるが、本発明の本質と関係しないためここではこの順方向電圧降下分を無視している。

【0025】

次にブートストラップ容量200が充電された状態で仮想電圧源150Hの電圧がΔV2上昇すると、ブートストラップダイオード102が接続されているブートストラップ容量200の一端の電圧がΔV2上昇し、(V1+ΔV2)となる。そのためブートストラップダイオード102は逆バイアスされ、電圧源150Lからロジック回路103のプラス電源への電流の供給が停止される。このときロジック回路103のプラス電源にはブートストラップ容量200に充電された電荷が供給される。つまり、ロジック回路103のプラス電源には電圧(V1+ΔV2)が印加され、マイナス電源には電圧(V2+ΔV2)が印加される。このようにロジック回路103の電源には常に電圧(V1−V2)が供給され、仮想電圧源150Hの電圧にかかわらずロジック回路103は動作することができる。ちなみに、電圧源150Lの発生する電圧は例えば数十Vであり、仮想電圧源150Hが発生する(即ち負荷において発生する)電圧は例えば0V〜数百Vである。つまり、ブートストラップダイオード102のカソードには数百Vの逆方向電圧が印加されることがある。

【0026】

図2は本実施の形態1に係るHVIC100の構造を模式的に示す平面図である。図2(a)はHVIC100全体を示す平面図であって、図2(b)は図2(a)中の部分Lを拡大して示す平面図である。また、図3は図2(a)の矢視A−Aにおける断面図であって、図4は図2(a)の矢視B−Bにおける断面図である。図2では図面の煩雑さを避けるために、図3及び図4での絶縁膜8の記載を省略し、絶縁膜18上に形成されている各電極のうち、ブートストラップダイオード102のカソード電極15、アノード電極16、金属電極13,17のみを記載している。また、図2(b)では、図2(a)中のブートストラップダイオード102を示す破線及び分離領域104を示す斜線の記載を省略している。

【0027】

図2〜4に示すように、本実施の形態1に係るHVIC100ではp-半導体基板1上にn-半導体層3が形成されている。p+不純物領域4はn-半導体層3の表面からp-半導体基板1との界面にかけてn-半導体層3内部に形成されている。そして、p+不純物領域4はn-半導体層3の一部を取り囲むように形成されており、ロジック回路103及びブートストラップダイオード102が配置される高電位島領域101を形成している。

【0028】

高電位島領域101内のn-半導体層3とp-半導体基板1との界面には、p+不純物領域4と離れてn+埋め込み不純物領域2が選択的に形成されている。n+埋め込み不純物領域2の上方でn-半導体層3の表面にはロジック回路103が形成されている。

【0029】

ロジック回路103は例えばpチャネルMOSFET130及びnチャネルMOSFET131を備えている。pチャネルMOSFET130は、p+型のドレイン領域31とソース領域32及びゲート電極36を有している。ドレイン領域31とソース領域32とは所定距離を成してn-半導体層3の表面に形成されており、ゲート電極36はドレイン領域31とソース領域32とで挟まれたn-半導体層3上にゲート絶縁膜34を介して形成されている。また、ドレイン領域31の隣には酸化膜12を介してn+不純物領域30がn-半導体層3の表面に形成されている。

【0030】

nチャネルMOSFET131は、pチャネルMOSFET130の隣りに配置されており、n-半導体層3に形成されているpウェル領域20の中に形成されている。nチャネルMOSFET131はn+型のドレイン領域23とソース領域22及びゲート電極26を有している。ドレイン領域23とソース領域22とは所定距離を成してpウェル領域20の表面に形成されており、ゲート電極26はドレイン領域23とソース領域22とで挟まれたpウェル領域20上にゲート絶縁膜24を介して形成されている。また、ソース領域22の隣には酸化膜12を介してp+不純物領域21がpウェル領域20の表面に形成されている。

【0031】

なお、pチャネルMOSFET130とnチャネルMOSFET131との配置を入れ替えて形成しても良い。つまり、nチャネルMOSFET131をpチャネルMOSFET130よりもブートストラップダイオード102に近づけるように配置しても良い。

【0032】

ブートストラップダイオード102のアノード領域となるp+不純物領域6は、p+不純物領域4とn+埋め込み不純物領域2との間における、p-半導体基板1とn-半導体層3との界面上のn-半導体層3の表面に形成されている。ブートストラップダイオード102のカソード領域となるn+不純物領域5はp+不純物領域6とロジック回路103との間で両者と離れてn-半導体層3に形成されている。具体的には、n+不純物領域5はn-半導体層3の表面からn+埋め込み不純物領域2にかけて、n+埋め込み不純物領域2の略端部に形成されており、ロジック回路103を取り囲んでいる。n+不純物領域5はn+不純物領域5aとn+不純物領域5bとを有している。n+不純物領域5aはn-半導体層3の表面上に形成されており、後述するカソード電極15と接続される。n+不純物領域5bはn+不純物領域5aと接続されてn+埋め込み不純物領域2まで延びている。

【0033】

n+不純物領域5とp+不純物領域6との間のn-半導体層3の表面には酸化膜12が選択的に形成されている。その酸化膜12上には電極9がn+不純物領域5及びロジック回路103を取り囲むように形成されている。この電極9はマルチフィールドプレートを形成しており、これによって耐圧の向上を図っている。また、電極9は例えばゲート電極26と同様にポリシリコンを材料としている。

【0034】

n+不純物領域5とp+不純物領域4との間のn-半導体層3の表面上には、p+不純物領域7がp+不純物領域4と接続して形成されている。図2(b)に示すように、p+不純物領域7は、p+不純物領域6が形成されている領域付近まで、n+不純物領域5及びロジック回路103を取り囲むように配置されている。

【0035】

絶縁膜18はn-半導体層3、酸化膜12、ゲート電極26,36及び電極9を覆うように形成されている。そして絶縁膜18を貫通して、p+不純物領域6にはアノード電極16、n+不純物領域5にはカソード電極15、p+不純物領域7には金属電極17が接続されている。また、pチャネルMOSFET130のドレイン領域31、ソース領域32、ゲート電極36及びn+不純物領域30のそれぞれには絶縁膜18を貫通して金属電極35が接続されている。nチャネルMOSFET131のドレイン領域23、ソース領域22、ゲート電極26及びp+不純物領域21のそれぞれには絶縁膜18を貫通して金属電極25が接続されている。

【0036】

カソード電極15はそれ自身が接続されているn+不純物領域5に沿って、ロジック回路103を取り囲むように配置されている。そして、カソード電極15はドレイン領域31及びn+不純物領域30上の金属電極35と、例えばアルミニウムで形成されている金属電極13によって接続されている。この結果、図1に示すようにブートストラップダイオード102のカソードとロジック回路103とが接続される。また、金属電極17はそれ自身が接続されているp+不純物領域7に沿って、かつアノード電極16に対してロジック回路103の反対側でロジック回路103及びカソード電極15を取り囲むように形成されている。

【0037】

電極9の上方の絶縁膜18上には金属電極10がフローティングで配置されており、電極9との容量結合により耐圧を向上している。そして、絶縁膜18上には各電極を覆うように絶縁膜8が形成されている。

【0038】

次に図2で示している分離領域104について説明する。ロジック回路103はp+不純物領域4及びn+不純物領域5によって取り囲まれている。そして、p+不純物領域4とn+不純物領域5との間のn-半導体層3は、RESURF効果によって空乏層に覆われる。つまりロジック回路103は空乏層に取り囲まれる。図5はRESURF効果によってn-半導体層3が空乏層に覆われる様子を示した図であって、破線300が形成される空乏層の輪郭を示している。また、図面の煩雑さを避けるためにアノード電極16、カソード電極15、電極9、金属電極10,17及び絶縁膜8,18の記載を省略している。

【0039】

例えばp-半導体基板1はグランド電位に接続される。そのため、p-半導体基板1と接続されているp+不純物領域4もグランド電位となる。上述のように例えばブートストラップダイオード102のアノードには電圧源150Lが接続されるため、p+不純物領域6にプラス電位が印加される。また、ブートストラップダイオード102のカソードにはブートストラップ容量200を介して仮想電圧源150Hが接続されるため、n+不純物領域5にプラス電位が印加される。n+不純物領域5はn-半導体層3及びn+埋め込み不純物領域2と接続されているため、各領域にプラス電位が印加される。このように、p型の各領域とn型の各領域とで形成されるpn接合には逆電圧が印加されることになり、RESURF効果によって、p+不純物領域4とn+不純物領域5との間のn-半導体層3はその全領域にわたって空乏層が形成される。分離領域104はこの空乏層が形成される領域を示している。図2に示すように、本実施の形態1に係るHVIC100は、ロジック回路103が分離領域104、つまり空乏層に覆われることによって高耐圧を実現している。

【0040】

このように本実施の形態1に係るHVIC100は、p+不純物領域4に取り囲まれた高電位島領域101内にブートストラップダイオード102とロジック回路103とを備えている。そのため、ブートストラップダイオード102とロジック回路103とを接続する際に、数百Vもの高電圧が印加される金属電極13がp+不純物領域4の上を通ることがない。その結果、RESURF効果によって生じるn-半導体層3での空乏層の広がりが阻害されることはない。つまり、設計当初に確保した耐圧が維持される。

【0041】

また従来のHVIC110では、RESURF効果で空乏化する二つの領域にブートストラップダイオード102とロジック回路103とを設けていたが、本実施の形態1のHVIC100ではロジック回路103を取り囲む分離領域104の一部を利用してブートストラップダイオード102を形成しているため、従来のHVIC110と比べて面積を縮小することができる。

【0042】

なお、本実施の形態1ではn+不純物領域5をn+埋め込み不純物領域2まで形成していたが、p+不純物領域6のように浅く領域を形成しても良い。本実施の形態1では、n-半導体層3に形成される空乏層の広がりをn+不純物領域5が抑制し、ロジック回路103の形成領域まで空乏層が広がることを防止していた。上述のようにn+不純物流域5が浅く形成されると、空乏層の広がりの抑制効果は低減する。しかし、n-半導体層3の濃度及び厚みを調整することによって、本実施の形態1と同様の分離領域104を形成することが可能であり、ロジック回路103の形成領域まで空乏層が広がることを防止することができる。また、n+不純物領域5はロジック回路103を取り囲むように形成されているが、p+不純物領域6のように部分的に設けても良い。また、各領域の不純物の導電型(p型及びn型)を入れ替えても良い。

【0043】

本実施の形態1にかかるHVIC100では、寄生バイポーラトランジスタが形成され耐圧性能に影響を与える。図6は本実施の形態1に係るHVIC100に形成される寄生バイポーラトランジスタの様子を示す図であって、図面の煩雑さを避けるためにアノード電極16、電極9、金属電極10,17及び絶縁膜8,18の記載を省略している。

【0044】

p+不純物領域4はn-半導体層3及びp+不純物領域6と共に、pnp寄生バイポーラトランジスタ160を形成する。また、p-半導体基板1はn-半導体層3及びp+不純物領域6と共にpnp寄生バイポーラトランジスタ161を形成する。そして、各pnp寄生バイポーラトランジスタは並列に接続されている。具体的にはp-半導体基板1及びp+不純物領域4をエミッタ、p+不純物領域6をコレクタ、n-半導体層3をベースとするpnp寄生バイポーラトランジスタを形成している。このpnp寄生バイポーラトランジスタのベース−エミッタ間及びベース−コレクタ間は、RESURF効果によってベースとなるn-半導体層3がすべて空乏層によって覆われているため、数百Vの耐圧を確保することができる。

【0045】

しかし、エミッタ−コレクタ間の耐圧はp+不純物領域6のp-半導体基板1方向への深さ及びp+不純物領域4との距離によって決定される。具体的には、p+不純物領域6とp+不純物領域4との距離が近づくにつれて、pnp寄生バイポーラトランジスタ160のエミッタ−コレクタ間の耐圧が低下する。また、p+不純物領域6がp-半導体基板1方向に近づくにつれてpnp寄生バイポーラトランジスタ161のエミッタ−コレクタ間の耐圧が低下する。各pnp寄生バイポーラトランジスタのエミッタ−コレクタ間の耐圧低下はHVIC全体の耐圧低下につながるため、エミッタ−コレクタ間で所望の耐圧が得られるようにp-半導体基板1方向への深さ及びp+不純物領域4との距離を設定することがより望ましい。

【0046】

実施の形態2.

図7は本実施の形態2に係るHVICの構造を模式的に示す平面図である。図7(a)は本実施の形態2に係るHVIC全体を示す平面図であって、図7(b)は図7(a)中の部分Mを拡大して示す平面図である。また、図8は図7(a)の矢視C−Cにおける断面図であって、図9は図7(a)の矢視D−Dにおける断面図である。本実施の形態2に係るHVICは上述の実施の形態1に係るHVIC100において、p-不純物領域60をさらに備えるものである。なお、図7(b)では、図7(a)中のブートストラップダイオード102を示す破線及び分離領域104を示す斜線の記載は省略している。

【0047】

図7〜9に示すように、p-不純物領域60はn-半導体層3の表面に形成されている。そして、ブートストラップダイオード102のアノード領域であるp+不純物領域6に接続されてブートストラップダイオード102のカソード領域であるn+不純物領域5に向かって延在している。

【0048】

上述のような構造を備える本実施の形態2に係るHVICは、ブートストラップダイオード102のリカバリー動作時間を短縮することができる。図10はブートストラップダイオード102に順方向電圧が印加されているときのホール及び電子の動きを示した図であり、図11はブートストラップダイオード102に印加されている電圧を順方向から逆方向へ切り替えたときのホール及び電子の動きを示した図である。なお図10,11では図面の煩雑さを避けるためにアノード電極16、カソード電極15、電極9、金属電極10,17及び絶縁膜8,18の記載を省略している。

【0049】

図10に示すように、カソード領域のn+不純物領域5よりも大きい電圧がアノード領域のp+不純物領域6に印加されると、つまりブートストラップダイオード102に順方向電圧が印加されると、p+不純物領域6及びp-不純物領域60からはホールhが、n+不純物領域5からは電子eがn-半導体層3に注入され、ブートストラップダイオード102に電流が流れる。

【0050】

図11に示すように、n+不純物領域5に印加される電圧がp+不純物領域6よりも大きくなると、つまりブートストラップダイオード102に逆方向電圧が印加されると、空乏層がn-半導体層3に形成され、n-半導体層3に存在しているホールhはp+不純物領域6及びp-不純物領域60へ、電子eはn+不純物領域5へ引き戻される。ホールh及び電子eの引き戻しが完了するまで、ブートストラップダイオード102にはテール電流と呼ばれる逆電流が流れる。このテール電流が流れなくなるまでの時間がリカバリー動作時間である。

【0051】

図12はブートストラップダイオード102のリカバリー特性を示す図である。横軸tは時間、縦軸Iはブートストラップダイオード102に流れる電流を示しており、順方向に流れる電流を正としている。図中の実線は、本実施の形態2に係るHVICのリカバリー特性を示しており、破線は上述の実施の形態1に係るHVIC100のリカバリー特性を示している。また、図中のt1及びt2は、それぞれの実施の形態のリカバリー動作時間を示している。

【0052】

本実施の形態2では、n+不純物領域5に向かってp-不純物領域60が延在して形成されているため、n+不純物領域5付近に存在するホールhが引き戻される時間は、実施の形態1と比べて短くなる。ゆえに、図12に示すように本実施の形態2のリカバリー動作時間t1は実施の形態1のリカバリー動作時間t2よりも短くなり、リカバリー特性の良好なブートストラップダイオード102が得られる。

【0053】

また、公知のRESURF技術を使用することによって、p-不純物領域60の全領域に空乏層を形成し、n-半導体層3の表面付近の耐圧を向上することができる。

【0054】

実施の形態3.

図13は本実施の形態3に係るHVICの構造を模式的に示す平面図である。本実施の形態3に係るHVICは、上述の実施の形態1に係るHVIC100において、p+不純物領域6及びn+不純物領域5が、高電位島領域101を形成しているp+不純物領域4の屈曲している部分に沿って互いに対向して設けられているものである。そして、各領域上にはアノード電極16またはカソード電極15が配置されている。

【0055】

図中の破線160は、p+不純物領域4のロジック回路103側の輪郭を示している。その他の構造については上述の実施の形態1に係るHVIC100と同じであるため説明を省略する。

【0056】

図14は本実施の形態3に係るHVICの利点を説明するための図であって、p+不純物領域6及びn+不純物領域5をp+不純物領域4の直線部分に沿って設けたときのHVICの構造を模式的に示す図である。図13,図14のいずれかに示された場合もブートストラップダイオード102の順方向電圧降下を抑えるために、アノード領域であるp+不純物領域6の面積がn+不純物領域5よりも大きくなるように形成している。

【0057】

図14に示すように、p+不純物領域4の直線部に沿ってp+不純物領域6及びn+不純物領域4を互いに対向して設ける場合、p+不純物領域6からn+不純物領域5へ向かうホールhが、ロジック回路103が形成されている領域まで入り込みやすくなり、ロジック回路103の動作を不安定にすることがあった。

【0058】

しかし、本実施の形態3に係るHVICでは、p+不純物領域6及びn+不純物領域5は、p+不純物領域4が屈曲している部分に沿って互いに対向して配置されているため、ブートストラップダイオード102の順方句電圧降下を抑えるために図14で示すp+不純物領域6と同じ面積でp+不純物領域6を形成したとしても、ロジック回路103が形成されている領域に入り込むホールhの量を抑えることができる。そのため、ロジック回路103の不安定動作を低減することができる。

【0059】

実施の形態4.

図15,16は本実施の形態4に係るHVICの構造を模式的に示す平面図である。図15,16で示すように、本実施の形態4に係るHVICは、上述の実施の形態1に係るHVIC100において、p+不純物領域6及びn+不純物領域5がp+不純物領域4に沿って互いに対向するように形成されており、n+不純物領域5は、n-半導体層3の表面に沿った長さがp+不純物領域6よりも長い。そして、p+不純物領域6の上にはアノード電極16が、n+不純物領域5の上にはカソード電極15が設けられている。

【0060】

図15に示す本実施の形態4に係るHVICはp+不純物領域4の直線部分にそってp+不純物領域6及びn+不純物領域5が設けられている。図16に示す本実施の形態4に係るHVICはp+不純物領域4の屈曲している部分に沿ってp+不純物領域6及びn+不純物領域5が形成されている。その他の構造については上述の実施の形態1に係るHVIC100と同じであるため説明を省略する。

【0061】

ブートストラップダイオード102に順方向電圧が印加されると、p+不純物流域6のホールhはn-半導体層3を通ってn+不純物領域5へ向かう。このときホールhはp+不純物領域6の外側に広がってn+不純物領域5へ向かう。そのためホールhの一部はn+不純物領域5に取り込まれることなくロジック回路103が形成されている領域へ入り込み、ロジック回路103の動作が不安定になることがあった。本実施の形態4に係るHVICは、互いに対向して配置されるp+不純物領域6及びn+不純物領域5において、n+不純物領域5はn-半導体層3の表面に沿った長さがp+不純物領域6よりも長いため、p+不純物領域6からのホールhをより多くn+不純物領域5に取り込むことが可能となる。そのため、ロジック回路103の不安定動作を低減することができる。

【0062】

また図15,16で示すように、p+不純領域6の端部からn+不純物領域5の端部に引いた直線と、p+不純物領域6の端部からn+不純物領域5のp+不純物領域6に対向している面に向けて垂直に引いた直線とが角度αを成すように、p+不純物領域6及びn+不純物領域5は形成されている。このαの値が45°以上に成るようにp+不純物領域6及びn+不純物領域5を形成することによってホールhのほとんどをn+不純物領域5に取り込むことができるため、さらにロジック回路103の不安定動作を低減することができる。

【0063】

実施の形態5.

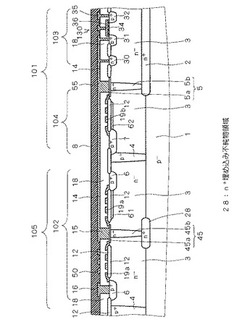

図17〜22は本実施の形態5に係るHVICを示す図である。図17は図18と図19との位置関係を示す説明図であって、図18,19は本実施の形態5に係るHVICの構造を模式的に示す平面図であって、図20は図18中の部分Nを拡大して示す平面図であって、図21は図18中の部分Oを拡大して示す平面図である。また、図22は図18,19中の矢視E−Eにおける断面図である。本実施の形態5に係るHVICは上述の従来のHVIC110において、p-不純物領域61,62を金属電極14の下にさらに設けたものである。なお、図20,21では、図18中のブートストラップダイオード102を示す一点鎖線及び領域105を示す斜線の記載を省略している。

【0064】

図17〜22に示すように、p-不純物領域61は、金属電極14の下に配置されているp+不純物領域6に接続されて、金属電極14の下に位置するようにn-半導体層3の表面に形成されている。また、p-不純物領域62は、金属電極14の下に配置されているp+不純物領域7に接続されて、金属電極14の下に位置するようにn-半導体層3の表面に形成されている。ここでp+不純物領域7はp+不純物領域4に接続されており、p+不純物領域4と同様にロジック回路103を取り囲むように形成されているため、p+不純物領域7をp+不純物領域4と一体的な領域と見ることができる。つまり、p-不純物領域62はp+不純物領域4と接続されて、金属電極14の下に配置されていると考えることができる。なお、図19中の破線150は分離領域104を形成するp+不純物領域4のロジック回路103側の輪郭を示しており、図18,20,21中の二点鎖線151は領域105を形成するp+不純物領域4のブートストラップダイオード102側の輪郭を示している。その他の構造については上述の従来のHVIC110と同じであるため説明を省略する。

【0065】

従来のHVIC110では、p+不純物領域4の上に、例えば数百Vもの高電圧が印加される金属電極14が配置されているため、n-半導体層3での空乏層の広がりが阻害され、耐圧が低下するという問題があった。金属電極14の下に位置するn-半導体層3の表面には、特に空乏層が広がりにくかった。しかし本実施の形態5に係るHVICでは、金属電極14の下にp-不純物領域60,61を形成しているため、ブートストラップダイオード102に逆方向電圧が印加されると、金属電極14の下に位置するn-半導体層3の表面付近にまで空乏層を形成することができる。また、公知のRESURF技術を使用することによって、p-不純物領域61,62の全領域に空乏層を形成することも可能である。そのため、金属電極14の影響による耐圧低下を低減することができる。

【0066】

図23〜図28は本実施の形態5に係るHVICの変形例を示す図である。図23は図24と図25との位置関係を示す説明図であって、図24,25は本実施の形態5に係るHVICの変形例の構造を示す平面図であって、図26は図24中の部分Pを拡大して示す平面図であって、図27は図24中の部分Qを拡大して示す平面図である。また、図28は図24,25中の矢視G−Gにおける断面図である。なお、図26,27では、図24中のブートストラップダイオード102を示す一点鎖線及び領域105を示す斜線の記載を省略している。

【0067】

上述の図17〜22で示すHVICでは、p+不純物領域6はn+不純物領域45を取り囲むように一周形成されていた。図23〜28で示すHVICではp+不純物領域6は金属電極14の下では形成されておらず、部分的にn+不純物領域45を取り囲んでおり、金属電極14の下にはp+不純物領域4と接続されたp+不純物領域70がn-半導体層3の表面に形成されている。そして、p-不純物領域61はこのp+不純物領域70に接続され、金属電極14の下に配置されている。このような構造であっても、図17〜22で示すHVICと同様の効果を生じる。

【符号の説明】

【0068】

1 p-半導体基板、2 n+埋め込み不純物領域、3 n-半導体層、4,6 p+不純物領域、14 金属電極、45 n+不純物領域、61 p-不純物領域、101 高電位島領域。

【技術分野】

【0001】

この発明は半導体装置、特にブートストラップダイオードを備える高耐圧IC(以後、「HVIC」と呼ぶ)に関する。

【背景技術】

【0002】

図29は従来のHVIC110及びその周辺回路を示す回路図である。図29に示すように、従来のHVIC110はブートストラップダイオード102と高電位島領域101に形成されているロジック回路103とを備えている。また、HVIC110の周辺にはブートストラップ容量200がロジック回路103と並列に設けられている。ブートストラップダイオード102のカソードはロジック回路103の一端に接続されている。そして、電圧源150Lはブートストラップダイオード102のアノードに接続されている。

【0003】

次に図29で示した回路図の動作について説明する。電圧源150Lの電圧がロジック回路103の他端の電位を決定する仮想的な可変電圧源である仮想電圧源150Hの電圧よりも高いとき、ブートストラップダイオード102が順バイアスされ、電圧源150Lからロジック回路103に電圧が供給される。また、ブートストラップ容量200に電荷が充電され、ブートストラップダイオード102の順方向電圧をVrec、電圧源150Lの電圧をV1として、ブートストラップダイオード102のカソードの電位はV1−Vrecまで上昇する。

【0004】

次にブートストラップ容量200が充電された状態で仮想電圧源150Hの電圧がΔV(>Vrec)上昇すると、ブートストラップダイオード102のカソードの電位はV1−Vrec+ΔV(>V1)となる。そのためブートストラップダイオード102は逆バイアスされ、電圧源150Lからロジック回路103への電流供給が停止される。このときロジック回路103にはブートストラップ容量200に充電された電荷が供給される。

【0005】

図30は従来のHVIC110の構造を模式的に示す平面図であって、図31は図30の矢視F−Fにおける断面図である。図30では図面の煩雑さを避けるために、図31での絶縁膜8の記載を省略し、絶縁膜18上に形成されている各電極のうち、ブートストラップダイオード102のカソード電極15、アノード電極16及び金属電極14のみを記載している。従来のHVIC110はRESURF(REduced SURface Field)効果を利用して、ロジック回路103とブートストラップダイオード102とを分離している。

【0006】

図30,31に示すように、従来のHVIC110ではp-半導体基板1上にn-半導体層3が形成されている。p-半導体基板1とn-半導体層3との界面にはn+埋め込み不純物領域2が選択的に形成されており、その上方のn-半導体層3の表面にはロジック回路103が形成されている。そして、n+埋め込み不純物領域2の略端部には、n-半導体層3の表面からn+埋め込み不純物領域2にかけてn+不純物領域5が形成されており、ロジック回路103を取り囲んでいる。

【0007】

n+不純物領域5はn+不純物領域5aとn+不純物領域5bとを有している。n+不純物領域5aはn-半導体層3の表面上に形成されており、後述する金属電極55と接続される。n+不純物領域5bはn+不純物領域5aと接続されてn+埋め込み不純物領域2まで延びている。

【0008】

また、n+不純物領域5と離れてロジック回路103と反対側にp+不純物領域7がn-半導体層3の表面に形成されており、ロジック回路103及びn+不純物領域5を取り囲んでいる。そして、p+不純物領域7とn+不純物領域5との間のn-半導体層3の表面には酸化膜12が形成されており、その酸化膜12上には電極19bが形成されている。この電極19bはいわゆる「マルチフィールドプレート」を形成しており、耐圧向上を担っている。

【0009】

ロジック回路103は例えばpチャネルMOSFET130を備えている。pチャネルMOSFET130は、p+型のドレイン領域31とソース領域32及びゲート電極36を有している。ドレイン領域31とソース領域32とは所定距離を成してn-半導体層3の表面に形成されており、ゲート電極36はドレイン領域31とソース領域32とで挟まれたn-半導体層3上にゲート絶縁膜34を介して形成されている。また、ドレイン領域31の隣には酸化膜12を介してn+不純物領域30がn-半導体層3の表面に形成されている。

【0010】

埋め込み不純物領域28は埋め込み不純物領域2と離れてp-半導体基板1とn-半導体層3との界面に選択的に形成されている。この埋め込み不純物領域28からn-半導体層3の表面にかけて、ブートストラップダイオード102のカソード領域であるn+不純物領域45が形成されている。n+不純物領域45はn+不純物領域45aとn+不純物領域45bとを有している。n+不純物領域45aはn-半導体層3の表面上に形成されており、後述するカソード電極15と接続される。n+不純物領域45bはn+不純物領域45aと接続されてn+埋め込み不純物領域28まで延びている。

【0011】

ブートストラップダイオード102のアノード領域であるp+不純物領域6は、p+不純物領域7と離れて、n+不純物領域45を取り囲むようにn-半導体層3の表面に形成されている。n+不純物領域45とp+不純物領域6との間のn-半導体層3の表面には酸化膜12が形成されており、その酸化膜12上には電極19aが形成されている。この電極19aもマルチフィールドプレートを形成している。

【0012】

p+不純物領域7とp+不純物領域6との間には、p-半導体基板1とn-半導体層3との界面からn-半導体層3の表面にかけてp+不純物領域4が形成されており、p+不純物領域4はp+不純物領域7のみと接続している。また、p+不純物領域4はn+不純物領域45及びp+不純物領域6を取り囲むように形成され、かつp+不純物領域7、n+不純物領域5及びロジック回路103を取り囲むように形成されている。つまり、ブートストラップダイオード102と高電位島領域101とはp+不純物領域4で分離されている。

【0013】

絶縁膜18はn-半導体層3、酸化膜12、ゲート電極36及び電極19a,19bを覆うように形成されている。そして絶縁膜18を貫通して、p+不純物領域6にはアノード電極16、n+不純物領域45にはカソード電極15、n+不純物領域5には金属電極55が接続されている。また、ドレイン領域31、ソース領域32、ゲート電極36及びn+不純物領域30のそれぞれには絶縁膜18を貫通して金属電極35が接続されている。カソード電極15は金属電極14によって金属電極55に接続されており、ドレイン領域31及びn+不純物領域30上の金属電極35にも接続されている。この結果、図29に示すようにブートストラップダイオード102のカソードとロジック回路103とが接続される。また、電極19aの上方の絶縁膜18上には金属電極50がフローティングで配置されており、電極19aとの容量結合により耐圧を向上している。そして、絶縁膜18上には各電極を覆うように絶縁膜8が形成されている。

【0014】

次に図30で示している分離領域104及び領域105について説明する。ロジック回路103はn+不純物領域5に取り囲まれ、さらにn+不純物領域5の外側のp+不純物領域4によって取り囲まれている。p+不純物領域4とn+不純物領域5との間のn-半導体層3は、RESURF効果によって空乏層に覆われる。具体的には、例えばp-半導体基板1及びp+不純物領域4がグランド電位に接続され、n-半導体層3及びn+不純物領域5に正の電圧が印加される際、p-半導体基板1及びp+不純物領域4と、n-半導体層3及びn+不純物領域5とで形成されるpn接合には逆電圧が印加されることになり、RESURF効果によって、p+不純物領域4とn+不純物領域5との間のn-半導体層3はその全領域にわたって空乏層が形成される。分離領域104はこの空乏層が形成される領域を示している。ここで、ロジック回路103はn+不純物領域5及びp+不純物領域4によって取り囲まれているが、言い換えれば、図30に示すようにロジック回路103は分離領域104に取り囲まれている。

【0015】

n+不純物領域45とp+不純物領域4との間のn-半導体層3は、上述と同様にRESURF効果によってその全領域に空乏層が形成される。つまり、p+不純物領域4によって取り囲まれ、ブートストラップダイオード102が形成されているn-半導体層3は、そのほぼ全領域が空乏層に覆われることになる。領域105はこの空乏層が形成されている領域を示している。

【発明の概要】

【発明が解決しようとする課題】

【0016】

上述のような構造を備える従来のHVIC110は、p-半導体基板1とn-半導体層3とのRESURF効果によって、n-半導体層3の表面まで空乏層で覆われ高耐圧を実現している。しかし、p-半導体基板1と接続されているp+不純物領域4の上には、例えば数百Vもの高電圧が印加される金属電極14が配置されているため、n-半導体層3内での空乏層の広がりが阻害される。その結果、耐圧が低下するという問題があった。

【0017】

そこで、本発明は上述のような問題を解決するためになされたものであり、高電圧が印加される金属電極による耐圧低下を緩和する半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0018】

本発明に係る第1の半導体装置は、p型の半導体基板と、前記半導体基板上に形成されたn型の半導体層と、前記半導体層の表面から前記半導体基板との界面にかけて前記半導体層内部に形成され、第1の島領域と第2の島領域とを区分する前記p型の第1不純物領域と、前記第1の島領域内の前記半導体層と前記半導体基板との界面に前記第1不純物領域と離れて形成された、前記半導体層よりも高濃度の前記n型の埋め込み不純物領域と、前記埋め込み不純物領域の上方で前記半導体層表面に形成された半導体素子と、前記第2の島領域内の前記半導体層表面に形成された前記p型の第2不純物領域及び前記n型の第3不純物領域を有し、前記第2不純物領域は前記第3不純物領域よりも前記半導体素子側に位置するダイオードと、前記第3不純物領域に接続され、前記第2不純物領域及び前記第1不純物領域の上方を通って前記半導体素子に接続される金属電極と、前記第2不純物領域に接続されて、前記金属電極の下方に位置するように前記半導体層表面に形成される、前記第2不純物領域より低濃度の前記p型の第4不純物領域とを備え、前記半導体基板及び前記第1不純物領域は前記第2不純物領域及び前記第3不純物領域よりも低い電位が与えられるものである。

【0019】

また、本発明に係る第2の半導体装置は、p型の半導体基板と、前記半導体基板上に形成されたn型の半導体層と、前記半導体層の表面から前記半導体基板との界面にかけて前記半導体層内部に形成され、第1の島領域と第2の島領域とを区分する前記p型の第1不純物領域と、前記第1の島領域内の前記半導体層と前記半導体基板との界面に前記第1不純物領域と離れて形成された、前記半導体層よりも高濃度の前記n型の埋め込み不純物領域と、前記埋め込み不純物領域の上方で前記半導体層表面に形成された半導体素子と、前記第2の島領域内の前記半導体層表面に形成された前記p型の第2不純物領域及び前記n型の第3不純物領域を有するダイオードと、前記第3不純物領域に接続され、前記第1不純物領域の上方を通って前記半導体素子に接続される金属電極と、前記第1不純物領域に接続されて、前記金属電極の下方に位置するように前記半導体層表面に形成される、前記第1不純物領域より低濃度の前記p型の第4不純物領域とを備え、前記半導体基板及び前記第1不純物領域は前記第2不純物領域及び前記第3不純物領域よりも低い電位が与えられるものである。

【発明の効果】

【0020】

本発明に係る第1の半導体装置によれば、金属電極の下方に第2不純物領域に接続されて第4不純物領域が形成されているため、ダイオードに逆方向電圧が印加されたとき、第4不純物領域の半導体層との接合部分から空乏層が形成される。そのため、第1不純物領域の上方を通る金属電極に高電圧が印加され、半導体層での空乏層の広がりが抑制されたとしても、耐圧低下を減少することができる。

【0021】

また、本発明に係る第2の半導体装置によれば、金属電極の下方に第1不純物領域に接続されて第4不純物領域が形成され、半導体基板及び第1不純物領域は第2不純物領域及び第3不純物領域よりも低い電位が与えられるため、ダイオードに逆方向電圧が印加されたとき、第4不純物領域の半導体層との接合部分から空乏層が形成される。そのため、第1不純物領域の上方を通る金属電極に高電圧が印加され、半導体層での空乏層の広がりが抑制されたとしても、耐圧低下を減少することができる。

【図面の簡単な説明】

【0022】

【図1】本実施の形態1のHVIC100及びその周辺回路を示す回路図である。

【図2】本実施の形態1に係るHVIC100の構造を模式的に示す平面図である。

【図3】本実施の形態1に係るHVIC100の構造を模式的に示す断面図である。

【図4】本実施の形態1に係るHVIC100の構造を模式的に示す断面図である。

【図5】本実施の形態1に係るHVIC100のn-半導体層3が空乏層に覆われる様子を示した図である。

【図6】本実施の形態1に係るHVIC100に形成される寄生バイポーラトランジスタの様子を示す図である。

【図7】本実施の形態2に係るHVICの構造を模式的に示す平面図である。

【図8】本実施の形態2に係るHVICの構造を模式的に示す断面図である。

【図9】本実施の形態2に係るHVICの構造を模式的に示す断面図である。

【図10】本実施の形態2に係るHVICのホール及び電子の動きを示した図である。

【図11】本実施の形態2に係るHVICのホール及び電子の動きを示した図である。

【図12】ブートストラップダイオード102のリカバリー特性を示す図である。

【図13】本実施の形態3に係るHVICの構造を模式的に示す平面図である。

【図14】本実施の形態3に係るHVICの利点を説明するための図である。

【図15】本実施の形態4に係るHVICの構造を模式的に示す平面図である。

【図16】本実施の形態4に係るHVICの構造を模式的に示す平面図である。

【図17】図18と図19との位置関係を示す説明図である。

【図18】本実施の形態5に係るHVICの構造を模式的に示す平面図である。

【図19】本実施の形態5に係るHVICの構造を模式的に示す平面図である。

【図20】本実施の形態5に係るHVICの構造を拡大して示す平面図である。

【図21】本実施の形態5に係るHVICの構造を拡大して示す平面図である。

【図22】本実施の形態5に係るHVICの構造を模式的に示す断面図である。

【図23】図24と図25との位置関係を示す説明図である。

【図24】本実施の形態5に係るHVICの変形例の構造を示す平面図である。

【図25】本実施の形態5に係るHVICの変形例の構造を示す平面図である。

【図26】本実施の形態5に係るHVICの変形例の構造を拡大して示す平面図である。

【図27】本実施の形態5に係るHVICの変形例の構造を拡大して示す平面図である。

【図28】本実施の形態5に係るHVICの変形例の構造を示す断面図である。

【図29】従来のHVIC110及びその周辺回路を示す回路図である。

【図30】従来のHVIC110の構造を模式的に示す平面図である。

【図31】従来のHVIC110の構造を模式的に示す断面図である。

【発明を実施するための形態】

【0023】

実施の形態1.

図1は本実施の形態1に係るHVIC100及びその周辺回路を示す回路図である。図1に示すように、本実施の形態1のHVIC100は高電位島領域101に、ロジック回路103とそのロジック回路103の一端にカソードが接続されているブートストラップダイオード102とを備えている。また、HVIC100の周辺にはブートストラップ容量200がロジック回路103と並列に接続されて設けられている。そして、電圧源150Lはブートストラップダイオード102のアノードに接続されている。なお、電圧源150Lは例えば定電圧源であり、仮想電圧源150Hは後述するように仮想的な可変電圧源である。

【0024】

次に図1で示した回路図の動作について説明する。ブートストラップダイオード102のカソード及びブートストラップ容量200の一端は、例えばロジック回路103のプラス電源に接続されている。また、ブートストラップ容量200の他端は、例えばロジック回路103のマイナス電源と共に、図示されない負荷に接続される。その接続点の電位は負荷の状態によって変動するので、仮想電圧源150Hによって与えられると見ることができる。ここで、電圧源150Lが発生するグランド電位に対する電位(以後、グランド電位に対する電位を単に「電圧」と呼ぶ)をV1、仮想電圧源150Hが発生する初期電圧をV2とする。ブートストラップ容量200に電荷が充電されていない状態で、V1>V2を満足する電圧V1,V2を電圧源150L,仮想電圧源150Hがそれぞれ発生すると、ブートストラップダイオード102が順バイアスされ、ロジック回路103のプラス電源に電圧V1が印加される。そして、電圧(V1−V2)がブートストラップ容量200に充電される。これによりロジック回路103には電圧(V1−V2)が印加され、動作する。ロジック回路103のプラス電源に印加される電圧は、厳密にはV1からブートストラップダイオード102の順方向電圧降下分を引いた値であるが、本発明の本質と関係しないためここではこの順方向電圧降下分を無視している。

【0025】

次にブートストラップ容量200が充電された状態で仮想電圧源150Hの電圧がΔV2上昇すると、ブートストラップダイオード102が接続されているブートストラップ容量200の一端の電圧がΔV2上昇し、(V1+ΔV2)となる。そのためブートストラップダイオード102は逆バイアスされ、電圧源150Lからロジック回路103のプラス電源への電流の供給が停止される。このときロジック回路103のプラス電源にはブートストラップ容量200に充電された電荷が供給される。つまり、ロジック回路103のプラス電源には電圧(V1+ΔV2)が印加され、マイナス電源には電圧(V2+ΔV2)が印加される。このようにロジック回路103の電源には常に電圧(V1−V2)が供給され、仮想電圧源150Hの電圧にかかわらずロジック回路103は動作することができる。ちなみに、電圧源150Lの発生する電圧は例えば数十Vであり、仮想電圧源150Hが発生する(即ち負荷において発生する)電圧は例えば0V〜数百Vである。つまり、ブートストラップダイオード102のカソードには数百Vの逆方向電圧が印加されることがある。

【0026】

図2は本実施の形態1に係るHVIC100の構造を模式的に示す平面図である。図2(a)はHVIC100全体を示す平面図であって、図2(b)は図2(a)中の部分Lを拡大して示す平面図である。また、図3は図2(a)の矢視A−Aにおける断面図であって、図4は図2(a)の矢視B−Bにおける断面図である。図2では図面の煩雑さを避けるために、図3及び図4での絶縁膜8の記載を省略し、絶縁膜18上に形成されている各電極のうち、ブートストラップダイオード102のカソード電極15、アノード電極16、金属電極13,17のみを記載している。また、図2(b)では、図2(a)中のブートストラップダイオード102を示す破線及び分離領域104を示す斜線の記載を省略している。

【0027】

図2〜4に示すように、本実施の形態1に係るHVIC100ではp-半導体基板1上にn-半導体層3が形成されている。p+不純物領域4はn-半導体層3の表面からp-半導体基板1との界面にかけてn-半導体層3内部に形成されている。そして、p+不純物領域4はn-半導体層3の一部を取り囲むように形成されており、ロジック回路103及びブートストラップダイオード102が配置される高電位島領域101を形成している。

【0028】

高電位島領域101内のn-半導体層3とp-半導体基板1との界面には、p+不純物領域4と離れてn+埋め込み不純物領域2が選択的に形成されている。n+埋め込み不純物領域2の上方でn-半導体層3の表面にはロジック回路103が形成されている。

【0029】

ロジック回路103は例えばpチャネルMOSFET130及びnチャネルMOSFET131を備えている。pチャネルMOSFET130は、p+型のドレイン領域31とソース領域32及びゲート電極36を有している。ドレイン領域31とソース領域32とは所定距離を成してn-半導体層3の表面に形成されており、ゲート電極36はドレイン領域31とソース領域32とで挟まれたn-半導体層3上にゲート絶縁膜34を介して形成されている。また、ドレイン領域31の隣には酸化膜12を介してn+不純物領域30がn-半導体層3の表面に形成されている。

【0030】

nチャネルMOSFET131は、pチャネルMOSFET130の隣りに配置されており、n-半導体層3に形成されているpウェル領域20の中に形成されている。nチャネルMOSFET131はn+型のドレイン領域23とソース領域22及びゲート電極26を有している。ドレイン領域23とソース領域22とは所定距離を成してpウェル領域20の表面に形成されており、ゲート電極26はドレイン領域23とソース領域22とで挟まれたpウェル領域20上にゲート絶縁膜24を介して形成されている。また、ソース領域22の隣には酸化膜12を介してp+不純物領域21がpウェル領域20の表面に形成されている。

【0031】

なお、pチャネルMOSFET130とnチャネルMOSFET131との配置を入れ替えて形成しても良い。つまり、nチャネルMOSFET131をpチャネルMOSFET130よりもブートストラップダイオード102に近づけるように配置しても良い。

【0032】

ブートストラップダイオード102のアノード領域となるp+不純物領域6は、p+不純物領域4とn+埋め込み不純物領域2との間における、p-半導体基板1とn-半導体層3との界面上のn-半導体層3の表面に形成されている。ブートストラップダイオード102のカソード領域となるn+不純物領域5はp+不純物領域6とロジック回路103との間で両者と離れてn-半導体層3に形成されている。具体的には、n+不純物領域5はn-半導体層3の表面からn+埋め込み不純物領域2にかけて、n+埋め込み不純物領域2の略端部に形成されており、ロジック回路103を取り囲んでいる。n+不純物領域5はn+不純物領域5aとn+不純物領域5bとを有している。n+不純物領域5aはn-半導体層3の表面上に形成されており、後述するカソード電極15と接続される。n+不純物領域5bはn+不純物領域5aと接続されてn+埋め込み不純物領域2まで延びている。

【0033】

n+不純物領域5とp+不純物領域6との間のn-半導体層3の表面には酸化膜12が選択的に形成されている。その酸化膜12上には電極9がn+不純物領域5及びロジック回路103を取り囲むように形成されている。この電極9はマルチフィールドプレートを形成しており、これによって耐圧の向上を図っている。また、電極9は例えばゲート電極26と同様にポリシリコンを材料としている。

【0034】

n+不純物領域5とp+不純物領域4との間のn-半導体層3の表面上には、p+不純物領域7がp+不純物領域4と接続して形成されている。図2(b)に示すように、p+不純物領域7は、p+不純物領域6が形成されている領域付近まで、n+不純物領域5及びロジック回路103を取り囲むように配置されている。

【0035】

絶縁膜18はn-半導体層3、酸化膜12、ゲート電極26,36及び電極9を覆うように形成されている。そして絶縁膜18を貫通して、p+不純物領域6にはアノード電極16、n+不純物領域5にはカソード電極15、p+不純物領域7には金属電極17が接続されている。また、pチャネルMOSFET130のドレイン領域31、ソース領域32、ゲート電極36及びn+不純物領域30のそれぞれには絶縁膜18を貫通して金属電極35が接続されている。nチャネルMOSFET131のドレイン領域23、ソース領域22、ゲート電極26及びp+不純物領域21のそれぞれには絶縁膜18を貫通して金属電極25が接続されている。

【0036】

カソード電極15はそれ自身が接続されているn+不純物領域5に沿って、ロジック回路103を取り囲むように配置されている。そして、カソード電極15はドレイン領域31及びn+不純物領域30上の金属電極35と、例えばアルミニウムで形成されている金属電極13によって接続されている。この結果、図1に示すようにブートストラップダイオード102のカソードとロジック回路103とが接続される。また、金属電極17はそれ自身が接続されているp+不純物領域7に沿って、かつアノード電極16に対してロジック回路103の反対側でロジック回路103及びカソード電極15を取り囲むように形成されている。

【0037】

電極9の上方の絶縁膜18上には金属電極10がフローティングで配置されており、電極9との容量結合により耐圧を向上している。そして、絶縁膜18上には各電極を覆うように絶縁膜8が形成されている。

【0038】

次に図2で示している分離領域104について説明する。ロジック回路103はp+不純物領域4及びn+不純物領域5によって取り囲まれている。そして、p+不純物領域4とn+不純物領域5との間のn-半導体層3は、RESURF効果によって空乏層に覆われる。つまりロジック回路103は空乏層に取り囲まれる。図5はRESURF効果によってn-半導体層3が空乏層に覆われる様子を示した図であって、破線300が形成される空乏層の輪郭を示している。また、図面の煩雑さを避けるためにアノード電極16、カソード電極15、電極9、金属電極10,17及び絶縁膜8,18の記載を省略している。

【0039】

例えばp-半導体基板1はグランド電位に接続される。そのため、p-半導体基板1と接続されているp+不純物領域4もグランド電位となる。上述のように例えばブートストラップダイオード102のアノードには電圧源150Lが接続されるため、p+不純物領域6にプラス電位が印加される。また、ブートストラップダイオード102のカソードにはブートストラップ容量200を介して仮想電圧源150Hが接続されるため、n+不純物領域5にプラス電位が印加される。n+不純物領域5はn-半導体層3及びn+埋め込み不純物領域2と接続されているため、各領域にプラス電位が印加される。このように、p型の各領域とn型の各領域とで形成されるpn接合には逆電圧が印加されることになり、RESURF効果によって、p+不純物領域4とn+不純物領域5との間のn-半導体層3はその全領域にわたって空乏層が形成される。分離領域104はこの空乏層が形成される領域を示している。図2に示すように、本実施の形態1に係るHVIC100は、ロジック回路103が分離領域104、つまり空乏層に覆われることによって高耐圧を実現している。

【0040】

このように本実施の形態1に係るHVIC100は、p+不純物領域4に取り囲まれた高電位島領域101内にブートストラップダイオード102とロジック回路103とを備えている。そのため、ブートストラップダイオード102とロジック回路103とを接続する際に、数百Vもの高電圧が印加される金属電極13がp+不純物領域4の上を通ることがない。その結果、RESURF効果によって生じるn-半導体層3での空乏層の広がりが阻害されることはない。つまり、設計当初に確保した耐圧が維持される。

【0041】

また従来のHVIC110では、RESURF効果で空乏化する二つの領域にブートストラップダイオード102とロジック回路103とを設けていたが、本実施の形態1のHVIC100ではロジック回路103を取り囲む分離領域104の一部を利用してブートストラップダイオード102を形成しているため、従来のHVIC110と比べて面積を縮小することができる。

【0042】

なお、本実施の形態1ではn+不純物領域5をn+埋め込み不純物領域2まで形成していたが、p+不純物領域6のように浅く領域を形成しても良い。本実施の形態1では、n-半導体層3に形成される空乏層の広がりをn+不純物領域5が抑制し、ロジック回路103の形成領域まで空乏層が広がることを防止していた。上述のようにn+不純物流域5が浅く形成されると、空乏層の広がりの抑制効果は低減する。しかし、n-半導体層3の濃度及び厚みを調整することによって、本実施の形態1と同様の分離領域104を形成することが可能であり、ロジック回路103の形成領域まで空乏層が広がることを防止することができる。また、n+不純物領域5はロジック回路103を取り囲むように形成されているが、p+不純物領域6のように部分的に設けても良い。また、各領域の不純物の導電型(p型及びn型)を入れ替えても良い。

【0043】

本実施の形態1にかかるHVIC100では、寄生バイポーラトランジスタが形成され耐圧性能に影響を与える。図6は本実施の形態1に係るHVIC100に形成される寄生バイポーラトランジスタの様子を示す図であって、図面の煩雑さを避けるためにアノード電極16、電極9、金属電極10,17及び絶縁膜8,18の記載を省略している。

【0044】

p+不純物領域4はn-半導体層3及びp+不純物領域6と共に、pnp寄生バイポーラトランジスタ160を形成する。また、p-半導体基板1はn-半導体層3及びp+不純物領域6と共にpnp寄生バイポーラトランジスタ161を形成する。そして、各pnp寄生バイポーラトランジスタは並列に接続されている。具体的にはp-半導体基板1及びp+不純物領域4をエミッタ、p+不純物領域6をコレクタ、n-半導体層3をベースとするpnp寄生バイポーラトランジスタを形成している。このpnp寄生バイポーラトランジスタのベース−エミッタ間及びベース−コレクタ間は、RESURF効果によってベースとなるn-半導体層3がすべて空乏層によって覆われているため、数百Vの耐圧を確保することができる。

【0045】

しかし、エミッタ−コレクタ間の耐圧はp+不純物領域6のp-半導体基板1方向への深さ及びp+不純物領域4との距離によって決定される。具体的には、p+不純物領域6とp+不純物領域4との距離が近づくにつれて、pnp寄生バイポーラトランジスタ160のエミッタ−コレクタ間の耐圧が低下する。また、p+不純物領域6がp-半導体基板1方向に近づくにつれてpnp寄生バイポーラトランジスタ161のエミッタ−コレクタ間の耐圧が低下する。各pnp寄生バイポーラトランジスタのエミッタ−コレクタ間の耐圧低下はHVIC全体の耐圧低下につながるため、エミッタ−コレクタ間で所望の耐圧が得られるようにp-半導体基板1方向への深さ及びp+不純物領域4との距離を設定することがより望ましい。

【0046】

実施の形態2.

図7は本実施の形態2に係るHVICの構造を模式的に示す平面図である。図7(a)は本実施の形態2に係るHVIC全体を示す平面図であって、図7(b)は図7(a)中の部分Mを拡大して示す平面図である。また、図8は図7(a)の矢視C−Cにおける断面図であって、図9は図7(a)の矢視D−Dにおける断面図である。本実施の形態2に係るHVICは上述の実施の形態1に係るHVIC100において、p-不純物領域60をさらに備えるものである。なお、図7(b)では、図7(a)中のブートストラップダイオード102を示す破線及び分離領域104を示す斜線の記載は省略している。

【0047】

図7〜9に示すように、p-不純物領域60はn-半導体層3の表面に形成されている。そして、ブートストラップダイオード102のアノード領域であるp+不純物領域6に接続されてブートストラップダイオード102のカソード領域であるn+不純物領域5に向かって延在している。

【0048】

上述のような構造を備える本実施の形態2に係るHVICは、ブートストラップダイオード102のリカバリー動作時間を短縮することができる。図10はブートストラップダイオード102に順方向電圧が印加されているときのホール及び電子の動きを示した図であり、図11はブートストラップダイオード102に印加されている電圧を順方向から逆方向へ切り替えたときのホール及び電子の動きを示した図である。なお図10,11では図面の煩雑さを避けるためにアノード電極16、カソード電極15、電極9、金属電極10,17及び絶縁膜8,18の記載を省略している。

【0049】

図10に示すように、カソード領域のn+不純物領域5よりも大きい電圧がアノード領域のp+不純物領域6に印加されると、つまりブートストラップダイオード102に順方向電圧が印加されると、p+不純物領域6及びp-不純物領域60からはホールhが、n+不純物領域5からは電子eがn-半導体層3に注入され、ブートストラップダイオード102に電流が流れる。

【0050】

図11に示すように、n+不純物領域5に印加される電圧がp+不純物領域6よりも大きくなると、つまりブートストラップダイオード102に逆方向電圧が印加されると、空乏層がn-半導体層3に形成され、n-半導体層3に存在しているホールhはp+不純物領域6及びp-不純物領域60へ、電子eはn+不純物領域5へ引き戻される。ホールh及び電子eの引き戻しが完了するまで、ブートストラップダイオード102にはテール電流と呼ばれる逆電流が流れる。このテール電流が流れなくなるまでの時間がリカバリー動作時間である。

【0051】

図12はブートストラップダイオード102のリカバリー特性を示す図である。横軸tは時間、縦軸Iはブートストラップダイオード102に流れる電流を示しており、順方向に流れる電流を正としている。図中の実線は、本実施の形態2に係るHVICのリカバリー特性を示しており、破線は上述の実施の形態1に係るHVIC100のリカバリー特性を示している。また、図中のt1及びt2は、それぞれの実施の形態のリカバリー動作時間を示している。

【0052】

本実施の形態2では、n+不純物領域5に向かってp-不純物領域60が延在して形成されているため、n+不純物領域5付近に存在するホールhが引き戻される時間は、実施の形態1と比べて短くなる。ゆえに、図12に示すように本実施の形態2のリカバリー動作時間t1は実施の形態1のリカバリー動作時間t2よりも短くなり、リカバリー特性の良好なブートストラップダイオード102が得られる。

【0053】

また、公知のRESURF技術を使用することによって、p-不純物領域60の全領域に空乏層を形成し、n-半導体層3の表面付近の耐圧を向上することができる。

【0054】

実施の形態3.

図13は本実施の形態3に係るHVICの構造を模式的に示す平面図である。本実施の形態3に係るHVICは、上述の実施の形態1に係るHVIC100において、p+不純物領域6及びn+不純物領域5が、高電位島領域101を形成しているp+不純物領域4の屈曲している部分に沿って互いに対向して設けられているものである。そして、各領域上にはアノード電極16またはカソード電極15が配置されている。

【0055】

図中の破線160は、p+不純物領域4のロジック回路103側の輪郭を示している。その他の構造については上述の実施の形態1に係るHVIC100と同じであるため説明を省略する。

【0056】

図14は本実施の形態3に係るHVICの利点を説明するための図であって、p+不純物領域6及びn+不純物領域5をp+不純物領域4の直線部分に沿って設けたときのHVICの構造を模式的に示す図である。図13,図14のいずれかに示された場合もブートストラップダイオード102の順方向電圧降下を抑えるために、アノード領域であるp+不純物領域6の面積がn+不純物領域5よりも大きくなるように形成している。

【0057】

図14に示すように、p+不純物領域4の直線部に沿ってp+不純物領域6及びn+不純物領域4を互いに対向して設ける場合、p+不純物領域6からn+不純物領域5へ向かうホールhが、ロジック回路103が形成されている領域まで入り込みやすくなり、ロジック回路103の動作を不安定にすることがあった。

【0058】

しかし、本実施の形態3に係るHVICでは、p+不純物領域6及びn+不純物領域5は、p+不純物領域4が屈曲している部分に沿って互いに対向して配置されているため、ブートストラップダイオード102の順方句電圧降下を抑えるために図14で示すp+不純物領域6と同じ面積でp+不純物領域6を形成したとしても、ロジック回路103が形成されている領域に入り込むホールhの量を抑えることができる。そのため、ロジック回路103の不安定動作を低減することができる。

【0059】

実施の形態4.

図15,16は本実施の形態4に係るHVICの構造を模式的に示す平面図である。図15,16で示すように、本実施の形態4に係るHVICは、上述の実施の形態1に係るHVIC100において、p+不純物領域6及びn+不純物領域5がp+不純物領域4に沿って互いに対向するように形成されており、n+不純物領域5は、n-半導体層3の表面に沿った長さがp+不純物領域6よりも長い。そして、p+不純物領域6の上にはアノード電極16が、n+不純物領域5の上にはカソード電極15が設けられている。

【0060】

図15に示す本実施の形態4に係るHVICはp+不純物領域4の直線部分にそってp+不純物領域6及びn+不純物領域5が設けられている。図16に示す本実施の形態4に係るHVICはp+不純物領域4の屈曲している部分に沿ってp+不純物領域6及びn+不純物領域5が形成されている。その他の構造については上述の実施の形態1に係るHVIC100と同じであるため説明を省略する。

【0061】

ブートストラップダイオード102に順方向電圧が印加されると、p+不純物流域6のホールhはn-半導体層3を通ってn+不純物領域5へ向かう。このときホールhはp+不純物領域6の外側に広がってn+不純物領域5へ向かう。そのためホールhの一部はn+不純物領域5に取り込まれることなくロジック回路103が形成されている領域へ入り込み、ロジック回路103の動作が不安定になることがあった。本実施の形態4に係るHVICは、互いに対向して配置されるp+不純物領域6及びn+不純物領域5において、n+不純物領域5はn-半導体層3の表面に沿った長さがp+不純物領域6よりも長いため、p+不純物領域6からのホールhをより多くn+不純物領域5に取り込むことが可能となる。そのため、ロジック回路103の不安定動作を低減することができる。

【0062】

また図15,16で示すように、p+不純領域6の端部からn+不純物領域5の端部に引いた直線と、p+不純物領域6の端部からn+不純物領域5のp+不純物領域6に対向している面に向けて垂直に引いた直線とが角度αを成すように、p+不純物領域6及びn+不純物領域5は形成されている。このαの値が45°以上に成るようにp+不純物領域6及びn+不純物領域5を形成することによってホールhのほとんどをn+不純物領域5に取り込むことができるため、さらにロジック回路103の不安定動作を低減することができる。

【0063】

実施の形態5.

図17〜22は本実施の形態5に係るHVICを示す図である。図17は図18と図19との位置関係を示す説明図であって、図18,19は本実施の形態5に係るHVICの構造を模式的に示す平面図であって、図20は図18中の部分Nを拡大して示す平面図であって、図21は図18中の部分Oを拡大して示す平面図である。また、図22は図18,19中の矢視E−Eにおける断面図である。本実施の形態5に係るHVICは上述の従来のHVIC110において、p-不純物領域61,62を金属電極14の下にさらに設けたものである。なお、図20,21では、図18中のブートストラップダイオード102を示す一点鎖線及び領域105を示す斜線の記載を省略している。

【0064】

図17〜22に示すように、p-不純物領域61は、金属電極14の下に配置されているp+不純物領域6に接続されて、金属電極14の下に位置するようにn-半導体層3の表面に形成されている。また、p-不純物領域62は、金属電極14の下に配置されているp+不純物領域7に接続されて、金属電極14の下に位置するようにn-半導体層3の表面に形成されている。ここでp+不純物領域7はp+不純物領域4に接続されており、p+不純物領域4と同様にロジック回路103を取り囲むように形成されているため、p+不純物領域7をp+不純物領域4と一体的な領域と見ることができる。つまり、p-不純物領域62はp+不純物領域4と接続されて、金属電極14の下に配置されていると考えることができる。なお、図19中の破線150は分離領域104を形成するp+不純物領域4のロジック回路103側の輪郭を示しており、図18,20,21中の二点鎖線151は領域105を形成するp+不純物領域4のブートストラップダイオード102側の輪郭を示している。その他の構造については上述の従来のHVIC110と同じであるため説明を省略する。

【0065】

従来のHVIC110では、p+不純物領域4の上に、例えば数百Vもの高電圧が印加される金属電極14が配置されているため、n-半導体層3での空乏層の広がりが阻害され、耐圧が低下するという問題があった。金属電極14の下に位置するn-半導体層3の表面には、特に空乏層が広がりにくかった。しかし本実施の形態5に係るHVICでは、金属電極14の下にp-不純物領域60,61を形成しているため、ブートストラップダイオード102に逆方向電圧が印加されると、金属電極14の下に位置するn-半導体層3の表面付近にまで空乏層を形成することができる。また、公知のRESURF技術を使用することによって、p-不純物領域61,62の全領域に空乏層を形成することも可能である。そのため、金属電極14の影響による耐圧低下を低減することができる。

【0066】

図23〜図28は本実施の形態5に係るHVICの変形例を示す図である。図23は図24と図25との位置関係を示す説明図であって、図24,25は本実施の形態5に係るHVICの変形例の構造を示す平面図であって、図26は図24中の部分Pを拡大して示す平面図であって、図27は図24中の部分Qを拡大して示す平面図である。また、図28は図24,25中の矢視G−Gにおける断面図である。なお、図26,27では、図24中のブートストラップダイオード102を示す一点鎖線及び領域105を示す斜線の記載を省略している。

【0067】

上述の図17〜22で示すHVICでは、p+不純物領域6はn+不純物領域45を取り囲むように一周形成されていた。図23〜28で示すHVICではp+不純物領域6は金属電極14の下では形成されておらず、部分的にn+不純物領域45を取り囲んでおり、金属電極14の下にはp+不純物領域4と接続されたp+不純物領域70がn-半導体層3の表面に形成されている。そして、p-不純物領域61はこのp+不純物領域70に接続され、金属電極14の下に配置されている。このような構造であっても、図17〜22で示すHVICと同様の効果を生じる。

【符号の説明】

【0068】

1 p-半導体基板、2 n+埋め込み不純物領域、3 n-半導体層、4,6 p+不純物領域、14 金属電極、45 n+不純物領域、61 p-不純物領域、101 高電位島領域。

【特許請求の範囲】

【請求項1】

p型の半導体基板と、

前記半導体基板上に形成されたn型の半導体層と、

前記半導体層の表面から前記半導体基板との界面にかけて前記半導体層内部に形成され、第1の島領域と第2の島領域とを区分する前記p型の第1不純物領域と、

前記第1の島領域内の前記半導体層と前記半導体基板との界面に前記第1不純物領域と離れて形成された、前記半導体層よりも高濃度の前記n型の埋め込み不純物領域と、

前記埋め込み不純物領域の上方で前記半導体層表面に形成された半導体素子と、

前記第2の島領域内の前記半導体層表面に形成された前記p型の第2不純物領域及び前記n型の第3不純物領域を有し、前記第2不純物領域は前記第3不純物領域よりも前記半導体素子側に位置するダイオードと、

前記第3不純物領域に接続され、前記第2不純物領域及び前記第1不純物領域の上方を通って前記半導体素子に接続される金属電極と、

前記第2不純物領域に接続されて、前記金属電極の下方に位置するように前記半導体層表面に形成される、前記第2不純物領域より低濃度の前記p型の第4不純物領域と

を備え、

前記半導体基板及び前記第1不純物領域は前記第2不純物領域及び前記第3不純物領域よりも低い電位が与えられる半導体装置。

【請求項2】

p型の半導体基板と、

前記半導体基板上に形成されたn型の半導体層と、

前記半導体層の表面から前記半導体基板との界面にかけて前記半導体層内部に形成され、第1の島領域と第2の島領域とを区分する前記p型の第1不純物領域と、

前記第1の島領域内の前記半導体層と前記半導体基板との界面に前記第1不純物領域と離れて形成された、前記半導体層よりも高濃度の前記n型の埋め込み不純物領域と、

前記埋め込み不純物領域の上方で前記半導体層表面に形成された半導体素子と、

前記第2の島領域内の前記半導体層表面に形成された前記p型の第2不純物領域及び前記n型の第3不純物領域を有するダイオードと、

前記第3不純物領域に接続され、前記第1不純物領域の上方を通って前記半導体素子に接続される金属電極と、

前記第1不純物領域に接続されて、前記金属電極の下方に位置するように前記半導体層表面に形成される、前記第1不純物領域より低濃度の前記p型の第4不純物領域と

を備え、

前記半導体基板及び前記第1不純物領域は前記第2不純物領域及び前記第3不純物領域よりも低い電位が与えられる半導体装置。

【請求項3】

前記第4不純物領域は全領域に空乏層が形成される、請求項1及び請求項2のいずれか一つに記載の半導体装置。

【請求項1】

p型の半導体基板と、

前記半導体基板上に形成されたn型の半導体層と、

前記半導体層の表面から前記半導体基板との界面にかけて前記半導体層内部に形成され、第1の島領域と第2の島領域とを区分する前記p型の第1不純物領域と、

前記第1の島領域内の前記半導体層と前記半導体基板との界面に前記第1不純物領域と離れて形成された、前記半導体層よりも高濃度の前記n型の埋め込み不純物領域と、

前記埋め込み不純物領域の上方で前記半導体層表面に形成された半導体素子と、

前記第2の島領域内の前記半導体層表面に形成された前記p型の第2不純物領域及び前記n型の第3不純物領域を有し、前記第2不純物領域は前記第3不純物領域よりも前記半導体素子側に位置するダイオードと、

前記第3不純物領域に接続され、前記第2不純物領域及び前記第1不純物領域の上方を通って前記半導体素子に接続される金属電極と、

前記第2不純物領域に接続されて、前記金属電極の下方に位置するように前記半導体層表面に形成される、前記第2不純物領域より低濃度の前記p型の第4不純物領域と

を備え、

前記半導体基板及び前記第1不純物領域は前記第2不純物領域及び前記第3不純物領域よりも低い電位が与えられる半導体装置。

【請求項2】

p型の半導体基板と、

前記半導体基板上に形成されたn型の半導体層と、

前記半導体層の表面から前記半導体基板との界面にかけて前記半導体層内部に形成され、第1の島領域と第2の島領域とを区分する前記p型の第1不純物領域と、

前記第1の島領域内の前記半導体層と前記半導体基板との界面に前記第1不純物領域と離れて形成された、前記半導体層よりも高濃度の前記n型の埋め込み不純物領域と、

前記埋め込み不純物領域の上方で前記半導体層表面に形成された半導体素子と、

前記第2の島領域内の前記半導体層表面に形成された前記p型の第2不純物領域及び前記n型の第3不純物領域を有するダイオードと、

前記第3不純物領域に接続され、前記第1不純物領域の上方を通って前記半導体素子に接続される金属電極と、

前記第1不純物領域に接続されて、前記金属電極の下方に位置するように前記半導体層表面に形成される、前記第1不純物領域より低濃度の前記p型の第4不純物領域と

を備え、

前記半導体基板及び前記第1不純物領域は前記第2不純物領域及び前記第3不純物領域よりも低い電位が与えられる半導体装置。

【請求項3】

前記第4不純物領域は全領域に空乏層が形成される、請求項1及び請求項2のいずれか一つに記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【公開番号】特開2011−9768(P2011−9768A)

【公開日】平成23年1月13日(2011.1.13)

【国際特許分類】

【出願番号】特願2010−182936(P2010−182936)

【出願日】平成22年8月18日(2010.8.18)

【分割の表示】特願2001−146256(P2001−146256)の分割

【原出願日】平成13年5月16日(2001.5.16)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成23年1月13日(2011.1.13)

【国際特許分類】

【出願日】平成22年8月18日(2010.8.18)

【分割の表示】特願2001−146256(P2001−146256)の分割

【原出願日】平成13年5月16日(2001.5.16)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]