半導体装置

【課題】クロック伝送回路3の電流消費量の増大を抑えつつ、リードデータのジッタを軽減する。

【解決手段】半導体装置10は、アクティブ期間内に内部クロック信号LCLKよりも周期の長い長周期クロック信号を供給し、アクティブ期間に続くリード期間内に内部クロック信号LCLKを供給するクロック出力制御回路73と、クロック出力制御回路73から出力された内部クロック信号LCLK及び長周期クロック信号を伝送するクロック伝送回路3と、データ入出力端子14と、クロック伝送回路3によって伝送された内部クロック信号LCLKに同期して、データ入出力端子14にリードデータを出力する入出力回路64とを備える。

【解決手段】半導体装置10は、アクティブ期間内に内部クロック信号LCLKよりも周期の長い長周期クロック信号を供給し、アクティブ期間に続くリード期間内に内部クロック信号LCLKを供給するクロック出力制御回路73と、クロック出力制御回路73から出力された内部クロック信号LCLK及び長周期クロック信号を伝送するクロック伝送回路3と、データ入出力端子14と、クロック伝送回路3によって伝送された内部クロック信号LCLKに同期して、データ入出力端子14にリードデータを出力する入出力回路64とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関し、特に、外部クロック信号に同期してリードデータを出力する半導体装置に関する。

【背景技術】

【0002】

近年、高速化するクロックに同期した動作を行う半導体装置としてパーソナルコンピュータなどのメインメモリとして用いられるDDR(Double Data Rate)型のシンクロナスメモリが多く用いられている。このような半導体装置は、リードデータの出力タイミングを外部クロック信号に対して同期させる構成を採用する。これは、コントローラと半導体装置間のデータ送受信を外部クロック信号に同期したタイミングで行うように取り決めておくことで互いのデータ送受信をミスなく実行するためである。しかしながら、半導体装置自身にも内部遅延は存在するため、その遅延時間を考慮しつつリードデータの出力タイミングが外部クロックに同期出来るように半導体装置内部において内部クロックを生成する必要がある。それを実現するための回路がDLL(Delay Locked Loop)回路である。特許文献1には、このようなDLL回路の例が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−278528号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ここで、半導体装置は近年、低消費電力化が進んでいる。一般に消費電力が大きいとされるDLL回路における消費電力の削減は、半導体装置そのものの低消費電力化に大きく寄与する事が出来るが、一方で、半導体装置は高速化もまた進んでおり、高速化に伴うタイミング調整の高精度化を考慮すれば、DLL回路における消費電力は大きくなる方向である。本発明は、そのようなDLL回路において消費電力を抑えつつタイミング調整も高精度とする半導体装置を提供することを課題とするものである。

【課題を解決するための手段】

【0005】

本発明による半導体装置は、アクティブ期間内に内部クロック信号よりも周期の長い長周期クロック信号を供給し、前記アクティブ期間に続くリード期間内に前記内部クロック信号を供給するクロック出力制御回路と、前記クロック出力制御回路から出力された前記内部クロック信号及び前記長周期クロック信号を伝送するクロック伝送回路と、外部データ端子と、前記クロック伝送回路によって伝送された前記内部クロック信号に同期して、前記外部データ端子にリードデータを出力する出力回路とを備えることを特徴とする。

【発明の効果】

【0006】

本発明によれば、アクティブ期間内からクロック信号がクロック伝送回路に供給されるので、リード期間の開始期における内部電圧VPERI2の低下幅が小さくなり、リードデータのジッタが軽減される。また、アクティブ期間内には、クロック出力制御回路に内部クロック信号よりも周期の長い長周期クロック信号を供給させるので、アクティブ期間内にも内部クロック信号を供給させ続ける場合に比べ、クロック伝送回路の電流消費量を抑えることが可能になる。

【図面の簡単な説明】

【0007】

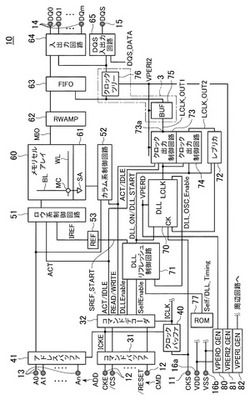

【図1】本発明の好ましい実施の形態による半導体装置の全体構成を示すブロック図である。

【図2】外部クロック信号CKS、内部クロック信号LCLK,LCLK2_2,LCLK4_2、クロック出力制御回路の出力ノードの電位、及び内部電圧VPERI2の時間変化を示すグラフである。

【図3】外部クロック信号CKS、内部クロック信号LCLK,LCLK2_2,LCLK4_2、クロック出力制御回路の出力ノードの電位、及び内部電圧VPERI2の時間変化を示すグラフである。

【図4】本発明の好ましい第1の実施の形態によるクロック出力制御回路及びその周辺回路の構成を示す図である。

【図5】本発明の好ましい第1の実施の形態によるクロック出力制御回路の内部構成を示す回路図である。

【図6】本発明の好ましい第1の実施の形態によるクロック出力制御回路に関わる各信号の、長周期クロック出力モードにおける時間変化を示すタイミング図である。

【図7】本発明の好ましい第2の実施の形態による半導体装置が備えるクロック出力制御回路の内部構成を示す回路図である。

【図8】本発明の好ましい第2の実施の形態によるクロック出力制御回路に関わる各信号の、長周期クロック出力モードにおける時間変化を示すタイミング図である。

【図9】本発明の好ましい第2の実施の形態の変形例による半導体装置が備えるクロック出力制御回路の内部構成を示す回路図である。

【図10】本発明の好ましい第3の実施の形態による半導体装置が備えるクロック出力制御回路の内部構成を示す回路図である。

【発明を実施するための形態】

【0008】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について詳細に説明する。

【0009】

まず初めに、発明の特徴部分の理解を容易ならしめるために、本発明者が検討した本願発明の技術思想について説明する。

【0010】

本願発明者は、DLL回路及びその周辺回路の設計に当たり、その消費電力を削減しつつも位相制御等の精度を維持出来る手段について次のように検討した。まず消費電力の削減については、DLL回路が出力する内部クロック信号LCLKがリード時に用いられる一方、ライト等他のタイミングでは用いられない点に着目し、必要とされるリード時以外のタイミングにおいて停止させれば良いことを発見した。それによって図1におけるバッファ回路75及びクロックツリー76における消費電力をリード時以外の期間において削減することが可能となる。半導体装置の動作スペックとの兼ね合いではあるが、所謂動作速度の比較的遅い高精度が要求されない半導体装置であれば、そのような制御でも足りる。

【0011】

一方、動作速度の早い高精度を要求する半導体装置においてもそのような制御を行うと確かに消費電力は削減されるが、DLL回路の出力する内部クロック信号LCLKについて不都合を生じ、高精度の要求に合わなくなることも併せて発見した。上記停止はリードコマンド時の動作開始直後における過渡的な内部電圧VPERI2の変化を大きくしてしまい、その結果、バッファ回路75及びクロックツリー76において特にクロックのデューティーを乱すジッタが発生されてしまうからである。

【0012】

内部電圧VPERI2の電位は図1における内部電源発生回路VPEIR2_GENによって所定のリファレンス電位と内部電圧VPERI2を比較することで所定のリファレンス電位と等しくなるように制御されるが、そのような過渡的な電圧変化には追随出来ないため、具体的には短時間に内部電圧VPERI2の電位は第1の電位→第2の電位→第3の電位(第1>第2>第3の電位)として変化する。それぞれの電位は、

第1の電位…バッファ回路75及びクロックツリー76が動作していない状況において内部電源発生回路VPERI2_GENにより上昇された電位

第2の電位…リードコマンド時のバッファ回路75及びクロックツリー76動作開始直後による過渡的な電位降下(まだ内部電圧発生回路VPERI2_GENの動作が内部電圧VPERI2に反映されていない)を受けた電位

第3の電位…内部電圧発生回路VPERI2_GEN及びバッファ回路75及びクロックツリー76が動作することによってバランスされる電位

である。バッファ回路75もクロックツリー76も内部電圧VPERI2をソースとするトランジスタにより構成されるものであるから、そのソース電位が変化すればクロックの遷移時間も変わる(ソース電位が高い…変化が早い。ソース電位が低い…変化が遅い)。具体的に、あるクロックの立ち上がり時にソース電位が高く、下がり時にソース電位が低く、次の立ち上がり時にはソース電位が高くなったケースにおいてトランジスタを介して出力されるクロックはハイ幅が大きく、ロー幅が小さいものとなってしまい、出力されるクロックの位相や特にデューティー比が大きく崩れてしまう。

【0013】

そのような問題に対処するため、本願発明者はリードコマンド時の手前のタイミングにおいて内部電圧VPERI2を多少消費する動作を行うことで、内部電圧VPERI2の電位を上記第1の電位よりも低く且つ第3の電位よりも高い電位に待機させておき、リードコマンド時においても内部電圧VPERI2の大きな変化が生じないように制御させることを発明した。このような制御を行うことで相対的な内部電圧VPERI2の変化を小さく抑えることが可能となり、それによる上記位相やデューティー比の悪化を防止することが可能となる。

【0014】

図1は、本発明の好ましい実施の形態による半導体装置10の全体構成を示すブロック図である。

【0015】

本実施の形態による半導体装置10はDDR型のSDRAM(Synchronous Dynamic Random Access Memory)であり、外部端子として、クロック端子11、コマンド端子12、アドレス端子13、データ入出力端子14(外部データ端子)、データストローブ端子15、電源端子16a,16bを備えている。

【0016】

クロック端子11は外部クロック信号CKSが供給される端子であり、供給された外部クロック信号CKSは、クロックバッファ40及びDLL回路70に供給される。クロックバッファ40は、外部クロック信号CKSに基づいて単相の内部クロック信号ICLKを生成し、これをコマンドデコーダ32及び図示しないその他の回路に供給する。

【0017】

DLL回路70は、外部クロック信号CKSを受けて、外部クロック信号CKSに対して位相制御され、かつデューティー制御された内部クロック信号LCLKを生成する回路である。ここで具体的に、位相制御とはクロックのライズエッジの位相を調整する制御であり、デューティー制御とはクロックのフォールエッジの位相を調整することでクロックの1周期におけるライズ期間及びフォール期間の比(デューティー比)を50:50にする制御である。生成された内部クロック信号LCLKは、クロック出力制御回路73,74に供給される。

【0018】

また、DLL回路70は、内部クロック信号LCLKの位相及びデューティー比がそれぞれ目標値になった(ロックした)か否かを判定する機能と、ロックしたと判定した場合に、オシレータ起動信号DLL_OSC_Enableを活性化する機能とを有する。オシレータ起動信号DLL_OSC_Enableは、DLLリフレッシュ制御回路71に供給される。

【0019】

DLLリフレッシュ制御回路71については後述するが、DLL回路70は、一旦位相制御及びデューティー制御を終えても(ロックしても)半導体装置の温度変化等に追随して再度位相制御等を行うことが望ましく、従って適切な期間を経て再調整を行うべきものである。オシレータ起動信号DLL_OSC_Enableは、一旦の位相制御を終えた後に、次の位相制御を行うまでの期間を測定開始するための起動信号である。実際にその期間の測定は、DLLリフレッシュ制御回路71に含まれるオシレータ回路がオシレータ起動信号DLL_OSC_Enableを受けて動作し、所定数のクロック信号をカウントした後にDLLリフレッシュ制御回路71が再調整を指示するDLLスタート信号DLL_STARTを活性化させることで実現される。そして、該DLLスタート信号DLL_STARTを受けてDLL回路70が再度位相制御等を実行するものである。

【0020】

クロック出力制御回路73は、上記内部クロック信号LCLKを受け、後述する内部アクティブコマンドACT及び内部リードコマンドREADそれぞれの活性状態に応じて動作モードを切り替えながら内部クロック信号LCLK_OUT1を生成し、出力ノード73aに出力する回路である。この動作モードには、内部クロック信号LCLK_OUT1を出力せず、出力ノード73aの電位をロウレベル又はハイレベルに固定するクロック停止モード、内部クロック信号LCLKよりも周期の長いクロック信号(長周期クロック信号)を生成し、内部クロック信号LCLK_OUT1として出力する長周期クロック出力モード、及び、内部クロック信号LCLKを内部クロック信号LCLK_OUT1として出力する通常クロック出力モード、の3つの動作モードが含まれる。出力ノード73aの出力電位は、クロック伝送回路3を経て、FIFO63、入出力回路64、及びDQS入出力回路65に供給される。

【0021】

クロック伝送回路3は、バッファ回路75及びクロックツリー76を含んで構成される。バッファ回路75は、例えば直列に接続された複数のCMOSによって構成される回路であり、内部クロック信号LCLK_OUT1を、FIFO63及びクロックツリー76に出力する。クロックツリー76は、供給された内部クロック信号LCLK_OUT1を入出力回路64及びDQS入出力回路65に分配する回路である。クロックツリー76も、例えば内部に複数のCMOSを含んで構成される。

【0022】

クロック出力制御回路74は、後述するDLLオン信号DLL_ON及びDLLスタート信号DLL_STARTのいずれかが活性化している場合に、内部クロック信号LCLKを内部クロック信号LCLK_OUT2としてレプリカ回路72に供給する回路である。いずれもが活性化していない場合には、クロック出力制御回路74の出力はロウレベル又はハイレベルに固定されるように制御される。

【0023】

レプリカ回路72は、クロック伝送回路3を疑似的に再現した回路である。レプリカ回路72に入力した内部クロック信号LCLK_OUT2は、内部クロック信号LCLK_OUT1がクロック伝送回路3の通過中に受ける遅延や波形変化と実質的に同等の遅延や波形変化を受けて、DLL回路70に供給される。

【0024】

このレプリカ回路によって半導体装置自身が持つ内部遅延を再現し、それをDLL回路にフィードバックして内部クロック信号LCLKのタイミング制御を行うことで半導体装置が外部クロックに同期したタイミングでリードデータを出力することが可能となる

【0025】

コマンド端子12は、クロックイネーブル信号CKE、ロウアドレスストローブ信号/RAS、カラムアドレスストローブ信号/CAS、ライトイネーブル信号/WE、チップセレクト信号/CS、オンダイターミネーション信号ODT、リセット信号/RESET、アクティブコマンド信号ACT、リードコマンド信号READ、アイドルコマンド信号IDLE、プリチャージコマンド信号PRE、パワーダウンコマンド信号PWDNなどの各種コマンド信号CMDが供給される端子である。なお、本明細書において信号名の先頭に「/」が付されている信号は、対応する信号の反転信号又はローアクティブな信号であることを意味する。

【0026】

コマンド端子12に供給されたコマンド信号CMDは、コマンドバッファ31を介してコマンドデコーダ32に供給される。クロックイネーブル信号CKEをバッファリングした内部クロックイネーブル信号ICKEは、クロックバッファ40及びアドレスバッファ41にも供給される。クロックイネーブル信号CKEが非活性状態(内部クロックイネーブル信号ICKEが非活性状態)、所謂パワーダウンモードのときにクロックバッファ40及びアドレスバッファ41の動作を停止させることで消費電力の削減を図るためである。一方、活性状態のときは、クロックバッファ40及びアドレスバッファ41は其々バッファリング動作を行う。

【0027】

コマンドデコーダ32は、コマンドバッファ31からの各種コマンド信号CMDを受け、該コマンド信号CMDの保持、デコード及びカウントなどを行うことによって各種内部コマンドを生成する回路である。これら内部コマンドには、内部アクティブコマンドACT、内部アイドルコマンドIDLE、内部リードコマンドREAD、内部ライトコマンドWRITEなどメモリセルのリード/ライトに関わる各種内部コマンドが含まれる他、DLL回路70の活性化/非活性化を指示するDLLイネーブルコマンドDLLEnableや、メモリセルアレイ60のセルフリフレッシュの開始/停止を指示するセルフリフレッシュコマンドSelfEnableなども含まれる。

【0028】

コマンドデコーダ32によって生成された各内部コマンドは、半導体装置10内の各回路に供給される。具体的には、ロウ系制御回路51に内部アクティブコマンドACTが、クロック出力制御回路73に内部アクティブコマンドACT、内部リードコマンドREAD、及び内部アイドルコマンドIDLEが、カラム系制御回路52に内部リードコマンドREADが、DLLリフレッシュ制御回路71にDLLイネーブルコマンドDLLEnable及びセルフリフレッシュコマンドSelfEnableが、それぞれ供給される。

【0029】

アドレス端子13は、n+1個のアドレスビットA0〜Anからなるアドレス信号ADDが供給される端子であり、供給されたアドレス信号ADDは、アドレスバッファ41においてバッファリングされ、ロウアドレスについてはロウ系制御回路51に、カラムアドレスについてはカラム系制御回路52に、それぞれ供給されてラッチされる。また、モードレジスタセットにエントリしている場合には、一部のアドレス信号ADDは図示しないモードレジスタに供給され、これによって半導体装置の動作モード(バースト長やリードレイテンシー等)を切り替えるモードレジスタの内容が更新される。

【0030】

ロウ系制御回路51は、アドレスバッファ41より供給されるロウアドレスに基づいて、メモリセルアレイ60に含まれるいずれかのワード線WLを選択する回路である。メモリセルアレイ60内においては、複数のワード線WLと複数のビット線BLが交差しており、その交点にはメモリセルMCが配置されている(図1では、1本のワード線WL、1本のビット線BL及び1個のメモリセルMCのみを示している)。ビット線BLは、センス回路61内の対応するセンスアンプSAに接続されている。

【0031】

カラム系制御回路52は、センス回路61に含まれるいずれかのセンスアンプSAを選択する回路である。カラム系制御回路52によって選択されたセンスアンプSAは、メインI/O線MIOを介してリードライトアンプ(RWAMP)62に接続される。

【0032】

リード動作時においては、センスアンプSAによって増幅されたリードデータDQはリードライトアンプ62でさらに増幅され、FIFO63及び入出力回路64を経て、データ入出力端子14から外部に出力される。一方、ライト動作時においては、データ入出力端子14を通じて外部から入力されたライトデータDQは、順に入出力回路64、FIFO63を経てリードライトアンプ62に入力され、増幅されたうえでセンスアンプSAに供給される。

【0033】

データ入出力端子14は、リードデータDQの出力及びライトデータDQの入力を行うための端子である。半導体装置10にはm+1個(m≧0)のデータ入出力端子14が設けられ、m+1ビットのデータを同時に入力又は出力可能とされている。

【0034】

FIFO63はリードデータDQ又はライトデータDQのキューイングを行う先入れ先出しの回路であり、データ入出力端子14ごとに設けられる。リード動作時に着目して説明すると、リードライトアンプ62から出力されたリードデータDQは、図示しないマルチプレクサによってデータ入出力端子14ごとに振り分けられ、対応するFIFO63にキューイングされる。FIFO63は、キューイングしたリードデータDQを内部クロック信号LCLKに同期したタイミングで、入出力回路64に出力する。

【0035】

入出力回路64は、それぞれデータ入出力端子14ごとに設けられた出力回路及び入力回路を有して構成される。リード動作時に着目して説明すると、出力バッファは、対応するFIFO63から出力されたリードデータDQを整形し、内部クロック信号LCLK_OUT1に同期したタイミングで、対応するデータ入出力端子14から外部に出力する。

【0036】

データストローブ端子15は、DQS入出力回路65と外部のコントローラとの間で、データ入出力の動作基準となるデータストローブ信号DQSの入出力を行うための端子である。DQS入出力回路65は、それぞれデータ入出力端子14ごとに設けられた出力回路及び入力回路を有して構成される。

【0037】

ライト時には、データストローブ端子15を通じて、外部からDQS入出力回路65にデータストローブ信号DQSが入力される。DQS入出力回路65は、こうして入力されたデータストローブ信号DQSに基づいて、入出力回路64がデータ入出力端子14からライトデータDQを取り込むタイミングを制御する。

【0038】

一方、リード時には、半導体装置10の内部からDQS入出力回路65に、データストローブデータ信号DQS_DATAが供給される。DQS入出力回路65は、クロックツリー76から供給される内部クロック信号LCLK_OUT1に同期して、データストローブデータ信号DQS_DATAをデータストローブ端子15に出力する。外部のコントローラは、こうして出力されたデータストローブデータ信号DQS_DATAに同期して、データ入出力端子14から出力されるリードデータDQを取り込む。つまり、DLL回路70はこのデータストローブデータ信号DQS_DATAが外部クロック信号CKSと同期するように内部クロック信号LCLKを制御するものである。

【0039】

DLLリフレッシュ制御回路71は、メモリセルアレイ60のセルフリフレッシュを行うタイミングと、DLL回路70が起動するタイミングとを制御する回路である。DLLの高精度化及び低消費電力を課題とする本発明において、セルフリフレッシュの制御方法は関知されないものではあるが、セルフリフレッシュの制御タイミングもDLL回路70の起動タイミングもDLLリフレッシュ制御回路71に含まれる共通のオシレータ回路を用いることで面積の削減を行うことが出来るため、このように共通の回路としている。本発明の思想は共通化せずにセルフリフレッシュ用、DLL制御用のものを其々設けることも含むものである。DLLリフレッシュ制御回路71には、上述したDLLイネーブルコマンドDLLEnable、セルフリフレッシュコマンドSelfEnable、及びオシレータ起動信号DLL_OSC_Enableの他に、セルフリフレッシュの間隔を示すデータSelf_Timing及びDLL回路70の定期起動の間隔を示すデータDLL_Timingが、ROM77から供給される。これらのデータは、製造中の時点でROM77に書き込まれる。

【0040】

DLLリフレッシュ制御回路71は、まずDLL回路70に関しては、入力されるDLLイネーブルコマンドDLLEnableが活性化されている場合に、DLLの起動期間を示すDLLオン信号DLL_ONを活性化し、そうでない場合にDLLオン信号DLL_ONを非活性化する。DLLオン信号DLL_ONはDLL回路70、クロック出力制御回路74、及びレプリカ回路72に供給される。DLL回路70は、DLLオン信号DLL_ONが活性化されている場合に、内部クロック信号LCLKの位相制御、デューティー制御を行い、それらが調整された内部クロック信号LCLKを生成する。これを最初の調整と呼ぶこととする。その最初の調整が終わった(DLL回路がロックした)時にDLL回路70はオシレータ起動信号DLL_OSC_Enableを活性化する。

【0041】

続いて、DLLリフレッシュ制御回路71は、入力されるオシレータ起動信号DLL_OSC_Enableが活性化されている場合に、データDLL_Timingによって示される間隔で定期的に、DLL回路70の更新期間を示すDLLスタート信号DLL_STARTを活性化する。DLLスタート信号DLL_STARTは、オシレータ起動信号DLL_OSC_EnableがDLLリフレッシュ制御回路71内の図示しないオシレータ回路に入力されてクロックの発振を行い、該クロックを所定数カウントした後に活性化されるように構成されている。DLLスタート信号DLL_STARTにより、DLL回路において2回目以降の内部クロックLCLKの調整を行うためである。このようにして、DLL回路70は、定期的に内部クロック信号LCLKを調整してリードデータの出力タイミングが外部クロックにどのようなタイミングにおいても同期出来るように半導体装置内部において内部クロックLCLKを生成することを可能としている。

【0042】

セルフリフレッシュに関しては、DLLリフレッシュ制御回路71は、セルフリフレッシュコマンドSelfEnableが活性化されている場合に、データSelf_Timingによって示される間隔で定期的にセルフリフレッシュ開始信号SREF_STARTを生成し、リフレッシュ回路(REF)53に出力する。このセルフリフレッシュ開始信号SREF_STARTを活性化するのもまた上記オシレータの制御による。リフレッシュ回路53は、ロウアドレスを所定の順序で出力する回路である。リフレッシュ回路53は、セルフリフレッシュ開始信号SREF_STARTを受けると、前回出力したロウアドレスの次のロウドレスをロウ系制御回路51に出力する。この処理を繰り返すことで、最終的には全ロウアドレスについて、セルフリフレッシュが行われる。

【0043】

電源端子16a,16bはそれぞれ、外部電源電圧VDD,VSSが供給される端子である。内部電圧発生回路80〜82はそれぞれ、これら外部電源電圧VDD,VSSに基づいて内部電圧VPERD,VPERI2,VPERIを生成し、半導体装置10内部の各回路に供給する。具体的には、内部電圧VPERDは、DLL回路70の動作電源として供給される。また、内部電圧VPERI2は、クロック出力制御回路73,74及びクロック伝送回路3(バッファ回路75及びクロックツリー76)の動作電源として供給される。内部電圧VPERIは、図示しない周辺回路の動作電源として供給される。

【0044】

内部電圧発生回路80〜82は、図示していないが、それぞれ差動アンプとドライバトランジスタを有している。ドライバトランジスタは、外部電源電圧VDDが供給される電源配線と、対応する内部電圧が供給される内部電源配線との間に挿入される。ドライバトランジスタの制御端子は、差動アンプの出力端子に接続される。差動アンプは、生成する内部電圧の目標値の電圧を有するリファレンス電圧を受け、ドライバトランジスタの制御端子に与える電圧(ドライバトランジスタのゲート−ソース間電圧)を調整することにより、対応する内部電源配線の電位がリファレンス電圧と同一値となるように動作する回路である。ただし、実際には完全には同一とならず、内部電源配線の電位は、内部電圧の供給先回路の電流消費量とバランスして相対的にリファレンス電位よりも小さい値となる。また、内部電圧の供給先回路の電流消費量が急激に増大した場合には、既述のように差動アンプの制御が追い付かず、対応する内部電源配線の電位が一時的に大きく低下することがある。

【0045】

ここで、上記回路構成における特にDLL回路及びその周辺回路の動作について図2及び図3を参照して説明する。図2及び図3はそれぞれ、外部クロック信号CKS、内部クロック信号LCLK,LCLK2_2,LCLK4_2、出力ノード73aの電位、及びクロック伝送回路3の動作電圧である内部電圧VPERI2の時間変化を示すグラフである。なお、内部クロック信号LCLK2_2,LCLK4_2はそれぞれ、内部クロック信号LCLKの周期を2倍,4倍に延ばした信号である。

【0046】

外部コントローラからコマンド端子12にアイドルコマンド信号IDLEが供給されると、これに応じてDLL回路70が活性化し、図2に示すように、内部クロック信号LCLKの生成とクロック出力制御回路73等への供給が開始される。これを受け、クロック出力制御回路73は、内部処理として内部クロック信号LCLK2_2,LCLK4_2の生成を開始する。この時点では、出力ノード73aの電位はロウレベルに固定され(クロック停止モード)、内部電圧VPERI2は所定のリファレンス電位REFとなっている。

【0047】

続いて、アクティブコマンド信号ACTが供給されると、コマンドデコーダ32は内部アクティブコマンドACTを活性化する。なお、本発明では、内部アクティブコマンドACTが活性化されてから内部リードコマンドREADが活性化されるまでの期間を「アクティブ期間」と称する。アクティブ期間に入ると、クロック出力制御回路73は、内部クロック信号LCLK_OUT1の生成とクロック伝送回路3への供給を開始する。内部クロック信号LCLK_OUT1の生成は、内部クロック信号LCLK2_2,LCLK4_2を利用して行われるが、その詳細については後述する。

【0048】

アクティブ期間内において生成される内部クロック信号LCLK_OUT1は、内部クロック信号LCLKより長い周期を有する長周期クロック信号となる。図2には、例として4倍の周期を有する場合を描画している。内部クロック信号LCLK_OUT1の生成が開始されたことにより、内部電圧VPERI2の電位は、図2に示すように、アクティブ期間の開始時点において一旦大きく低下した後に漸増し、リファレンス電位REF−ΔV1の電位で安定する。

【0049】

なお、図2には2種類の内部クロック信号LCLK_OUT1を記載している。これらはともに内部クロック信号LCLKの4倍の周期を有する長周期クロック信号であるが、ハイのパルス幅が異なっている。内部クロック信号LCLK_OUT1(図6)のハイのパルス幅は内部クロック信号LCLKと同一であり、後に第1の実施の形態で詳しく説明する。内部クロック信号LCLK_OUT1(図8)のハイのパルス幅は内部クロック信号LCLKの4倍であり、後に第2の実施の形態で詳しく説明する。

【0050】

次に、リードコマンド信号READが供給されると、コマンドデコーダ32は内部リードコマンドREADを活性化する。なお、本発明では、内部リードコマンドREADが活性化されてからリードデータの出力が完了するまでの期間を「リード期間」と称する。リード期間内における内部クロック信号LCLK_OUT1は、内部クロック信号LCLKと同一の周期を有する通常のクロック信号に切り替えられる。これにより、内部電圧VPERI2の電位は、図2に示すように、リード期間の開始時点において一旦大きく低下した後漸増し、リファレンス電位REF−ΔV1−ΔV2の電位で安定する。

【0051】

図2から明らかなように、アクティブ期間内に長周期の内部クロック信号LCLK_OUT1を生成するようにしたことで、アクティブ期間とリード期間とでの内部電圧VPERI2の電位の差は縮小している。つまり、アクティブ期間内に内部クロック信号LCLK_OUT1を生成しない背景技術においては、この差はΔV1+ΔV2(図示したΔVB)となるが、アクティブ期間内に内部クロック信号LCLK_OUT1を生成するようにしたことで、ΔV2に縮小している。これにより、リード期間の開始時点における一時的な電位低下の幅も小さくなっている。

【0052】

このような電位低下幅の縮小により、半導体装置10では、リード期間の開始期における信号の立ち上がり時間及び立ち下がり時間の揺らぎが、背景技術に比べて小さくなる。したがって、クロック伝送回路3を介して入出力回路64に供給される内部クロック信号のデューティー比の崩れ(ジッタ)が、背景技術に比べて軽減される。内部クロック信号のジッタが軽減されれば、この内部クロック信号に同期して出力されるリードデータDQのジッタも軽減される。

【0053】

また、図3に示すように、外部からパワーダウンコマンド信号PWDNが供給されると、次にアイドルコマンド信号IDLEが供給されるまでの間、DLL回路70は内部クロック信号LCLKの生成を停止する。なお、本発明では、パワーダウンコマンド信号PWDNが供給されてからアイドルコマンド信号IDLEが供給されるまでの期間を「パワーダウン期間」と称する。パワーダウン期間においては、クロック出力制御回路73による内部クロック信号LCLK2_2,LCLK4_2の生成も停止され、出力ノード73aの電位はロウレベルに固定される。これにより、パワーダウン期間内の電流消費量が軽減される。

【0054】

以上説明したように、本実施の形態による半導体装置10によれば、アクティブ期間内から内部クロック信号LCLK_OUT1がクロック伝送回路3に供給されるので、リード期間の開始期における内部電圧VPERI2の低下幅が小さくなり、リードデータDQのジッタが軽減される。また、アクティブ期間内にクロック出力制御回路73が供給するクロック信号は、内部クロック信号LCLKの4倍の周期を有する長周期クロック信号となるので、アクティブ期間内にも内部クロック信号LCLKを供給する場合に比べ、クロック伝送回路3の電流消費量を抑えることが可能になる。さらに、パワーダウン期間内の電流消費量を抑えることも可能になる。

【0055】

以上が本実施の形態による半導体装置10の全体構成である。次に、クロック出力制御回路73について、詳細に説明する。

【0056】

図4は、本発明の第1の実施の形態によるクロック出力制御回路73及びその周辺回路の構成を示す図である。また、図5は、クロック出力制御回路73の内部構成を示す回路図である。本実施の形態では、アクティブ期間内において活性化される長周期の内部クロック信号LCLK_OUT1は、内部クロック信号LCLKの4倍の周期を有し、かつ内部クロック信号LCLKに等しいハイのパルス幅と有する信号である。

【0057】

図4に開示されるDLL回路70には、上述したように、外部クロック信号CKS、DLLオン信号DLL_ON、DLLスタート信号DLL_START、及びオシレータ起動信号DLL_OSC_Enableが供給される。DLLオン信号DLL_ON及びDLLスタート信号DLL_STARTはOR回路90にも供給され、OR回路90から、これらのうちいずれか一方が活性化されているときに活性化し、それ以外のときに非活性となるDLL起動信号S1が出力される。DLL起動信号S1は、クロック出力制御回路74及びレプリカ回路72に供給される。

【0058】

DLL回路70は、上述したように、外部クロック信号CKSを受けて、外部クロック信号CKSに対して位相制御され、かつデューティー制御された内部クロック信号LCLKを生成する回路である。具体的には、図示していないが、遅延回路、位相比較回路、デューティー比較回路、分周回路、及びカウンタ回路を有して構成される。遅延回路は、外部クロック信号を遅延させて内部クロック信号を生成する回路であり、その遅延量はカウンタ回路のカウンタ値によって制御される。遅延回路が生成した内部クロック信号LCLKは、クロック出力制御回路73,74それぞれに入力され、其々において所定の制御を受けて、内部クロック信号LCLK_OUT1,LCLK_OUT2として出力される。

【0059】

このうち、内部クロック信号LCLK_OUT2は、上述したように、レプリカ回路72を経てDLL回路70に戻される。レプリカ回路72は、内部クロック信号LCLKが伝送されるバッファ回路75、クロックツリー76、DQS出力回路65の遅延量を模倣して構成される回路である。内部クロック信号LCLKを、DQS入出力回路15を介して外部へ出力されるタイミングにおいて外部クロック信号CKSと同期させるためである。レプリカ回路72を経てDLL回路70に戻った内部クロック信号LCLK_OUT2は、位相比較回路及びデューティー比較回路に供給される。位相比較回路は、外部クロック信号CKSの位相と内部クロック信号LCLK_OUT2の位相とを比較し、その結果をカウンタ回路に出力する。デューティー比較回路は、内部クロック信号LCLK_OUT2のデューティー比を予め記憶している所定値と比較し、その結果をカウンタ回路に出力する。カウンタ回路は、こうして入力された比較結果に基づき、カウント値のアップ又はダウンを行う。ここで、分周回路は、オシレータ起動信号DLL_OSC_Enableが活性化している場合に、外部クロック信号CKSを分周し、分周クロックとして出力する回路である。カウンタ回路によるカウント値の更新は、DLLオン信号DLL_ON及びDLLスタート信号DLL_STARTのいずれかが活性化している場合に、分周回路から出力される分周クロックに同期して行われる。

【0060】

以上の各回路の処理により、遅延回路の出力する内部クロック信号LCLKは、それ自身がDQS入出力回路15を介して外部へ出力されるタイミングにおいて外部クロック信号CKSと同期し、かつデューティー比が上記所定値50:50となるように制御される。

【0061】

次に、図5に示すように、クロック出力制御回路73は、供給制御回路20及び周期伸長回路21を有して構成される。

【0062】

供給制御回路20は、周期伸長回路21により得られる信号から長周期クロック信号を生成し、内部アクティブコマンドACTの活性化に応じてこの長周期クロック信号を出力ノード73aへ供給し、内部リードコマンドREADの活性化に応じて長周期クロック信号から内部クロック信号LCLKに供給を切り替える回路である。

【0063】

このような制御を行うことで、内部アクティブコマンドACT〜内部リードコマンドREADのアクティブ期間内において、クロック出力制御回路73は長周期クロック信号を出力する事となる。この長周期クロック信号は、内部電圧VPERI2の電位を図2に示したようにΔV1だけ下げる役割を果たし、続いて内部リードコマンドREADが活性化しても、その際の電位降下量(及びその後の電位上昇も含めた電位変化量)をΔV2として小さく抑えることが可能となる。尚、ΔV1及びΔV2の絶対値は周期伸張回路21においてその伸張量をどの程度とするかによって調整可能である。図5においては長周期クロック信号の周期を内部クロック信号LCLKの4倍となるようにしているが、4倍が必然ではなく2倍や8倍であっても良い。2倍とすることで上記ΔV2の値を4倍のときよりも更に小さく抑えることが出来る(ΔV1が大きくなる)。一方、8倍とするとΔV2の値は大きくはなるが、アクティブ期間内の消費電力を抑えることが出来る。

【0064】

回路構成として、供給制御回路20は、図5に示すように、NAND回路NA1〜NA4,インバータINV1〜INV5を有している。NAND回路NA1には、内部クロック信号LCLKと内部アイドルコマンドIDLEとが供給される。ここで、内部アイドルコマンドIDLEは、半導体装置10がスリープモードになっているとき(パワーダウン期間)にロウレベル、それ以外のときにハイレベルとなる信号である。したがって、NAND回路NA1の出力は、パワーダウン期間内にはハイレベルに固定され、それ以外のときには内部クロック信号LCLKの反転信号となる。

【0065】

インバータINV1〜INV3は、NAND回路NA1の出力端から順に直列に接続される。したがって、半導体装置10の電源が投入されているとき、インバータINV1,INV3の出力信号は内部クロック信号LCLKと等しくなる。一方、インバータINV2の出力信号は内部クロック信号LCLKの反転信号/LCLKと等しくなる。インバータINV1,INV2の出力信号は、周期伸長回路21に供給される。

【0066】

インバータINV4には、内部リードコマンドREADが供給される。ここで供給される内部リードコマンドREADは、外部からコマンド端子12にリードコマンドREADが入力されてから、入出力回路64によるリードデータDQの出力が完了するまでの期間、継続的に活性化されるハイアクティブな信号である。内部リードコマンドREADが活性化される期間は、上述したリード期間に相当する。インバータINV4の出力信号は、内部リードコマンドREADの反転信号となる。

【0067】

NAND回路NA2には、内部アクティブコマンドACTと、周期伸長回路21が出力するクロック信号LCLK2_2,LCLK4_2とが供給される。ここで供給される内部アクティブコマンドACTは、外部からコマンド端子12にアクティブコマンドACTが入力されてから、入出力回路64によるリードデータDQの出力が完了するまでの期間、継続的に活性化されるハイアクティブな信号である。なお、外部からのコマンドの入力は、必ずアクティブコマンドACT、リードコマンドREADの順で行われ、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間は、上述したアクティブ期間に相当する。NAND回路NA2の出力信号は、内部アクティブコマンドACT、クロック信号LCLK2_2,LCLK4_2がすべてハイレベルであるときにロウレベル、そうでないときにハイレベルとなる。

【0068】

NAND回路NA3には、インバータINV4の出力信号とNAND回路NA2の出力信号とが供給される。したがって、NAND回路NA3の出力信号は、これらがともにハイのときにロウレベル、そうでないときにハイレベルとなる。

【0069】

NAND回路NA4には、インバータINV3の出力信号とNAND回路NA3の出力信号とが供給される。したがって、NAND回路NA4の出力信号は、これらがともにハイのときにロウレベル、そうでないときにハイレベルとなる。以下では、NAND回路NA3の出力端とNAND回路NA4の入力端とを接続する配線を配線L1と称する。

【0070】

インバータINV5には、NAND回路NA4の出力信号が供給される。インバータINV5の出力端は出力ノード73aであり、したがって、内部クロック信号LCLK_OUT1はNAND回路NA4の出力信号の反転信号となる。

【0071】

周期伸長回路21は、内部クロック信号LCLKの周期を延ばす機能を有する回路である。具体的には、図5に示すように、それぞれP型チャネルMOSトランジスタ及びN型チャネルMOSトランジスタによって構成される4個のトランスファーゲートTRF2−1,TRF2−2,TRF4−1,TRF4−2と、インバータINV2−1〜INV2−7,INV4−2〜INV4−7とを有している。

【0072】

トランスファーゲートTRF2−1の出力端は、インバータINV2−2の出力端とインバータINV2−3の入力端に接続される。インバータINV2−2の入力端とインバータINV2−3の出力端とはともにインバータINV2−4の入力端に接続され、インバータINV2−4の出力端は、トランスファーゲートTRF2−2の入力端に接続される。トランスファーゲートTRF2−2の出力端は、インバータINV2−5の出力端とインバータINV2−6の入力端に接続される。インバータINV2−5の入力端とインバータINV2−6の出力端とはともにインバータINV2−7の入力端に接続され、インバータINV2−7の出力端は、インバータINV2−1を介して、トランスファーゲートTRF2−1の入力端に接続される。

【0073】

トランスファーゲートTRF2−1のP型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF2−2のN型チャネルMOSトランジスタの制御端子には、供給制御回路20から内部クロック信号LCLKの反転信号/LCLKが供給される。一方、トランスファーゲートTRF2−1のN型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF2−2のP型チャネルMOSトランジスタの制御端子には、供給制御回路20から内部クロック信号LCLKが供給される。インバータINV2−7の出力端からはクロック信号LCLK2_1が取り出され、インバータINV2−1の出力端からはクロック信号LCLK2_2が取り出される。クロック信号LCLK2_2は、上述したように、供給制御回路20内のNAND回路NA2に供給される。

【0074】

以上の構成により、クロック信号LCLK2_2は、図2に示したように、内部クロック信号LCLKの周期を2倍に延ばした信号となる。

【0075】

図5に戻る。トランスファーゲートTRF4−1の出力端は、インバータINV4−2の出力端とインバータINV4−3の入力端に接続される。インバータINV4−2の入力端とインバータINV4−3の出力端とはともにインバータINV4−4の入力端に接続され、インバータINV4−4の出力端は、トランスファーゲートTRF4−2の入力端に接続される。トランスファーゲートTRF4−2の出力端は、インバータINV4−5の出力端とインバータINV4−6の入力端に接続される。インバータINV4−5の入力端とインバータINV4−6の出力端とはともにインバータINV4−7の入力端に接続され、インバータINV4−7の出力端は、インバータINV4−1を介して、トランスファーゲートTRF4−1の入力端に接続される。

【0076】

トランスファーゲートTRF4−1のP型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF4−2のN型チャネルMOSトランジスタの制御端子には、クロック信号LCLK2_2が供給される。一方、トランスファーゲートTRF4−1のN型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF4−2のP型チャネルMOSトランジスタの制御端子には、クロック信号LCLK2_1が供給される。インバータINV4−1の出力端からは、クロック信号LCLK4_2が取り出される。クロック信号LCLK4_2は、上述したように、供給制御回路20内のNAND回路NA2に供給される。

【0077】

以上の構成により、クロック信号LCLK4_2は、図2に示したように、内部クロック信号LCLKの周期を4倍に延ばした信号となる。

【0078】

以上説明した構成により、まず内部アイドルコマンドIDLEがロウレベルとなっている場合、出力ノード73aの電位はロウレベルに固定される(クロック停止モード)。この場合、内部クロック信号LCLK_OUT1はクロック伝送回路3に供給されない。

【0079】

一方、内部アイドルコマンドIDLEがハイレベルとなっている場合には、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間(アクティブ期間)においては、クロック信号LCLK2_2、クロック信号LCLK4_2、及び内部クロック信号LCLKの論理積信号が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(長周期クロック出力モード)。本実施の形態では、この論理積信号が、内部クロック信号LCLKよりも周期の長い長周期クロック信号に相当する。

【0080】

また、内部リードコマンドREADが活性化されてから内部リードコマンドREADが非活性化するまでの期間(リード期間)においては、内部クロック信号LCLKが、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(通常クロック出力モード)。

【0081】

図6には、長周期クロック出力モードである場合を前提として、配線L1の電位の変化と、内部クロック信号LCLK_OUT1とについても図示している。同図に示すように、配線L1の電位はクロック信号LCLK2_2とクロック信号LCLK4_2との論理積信号となっており、内部クロック信号LCLK_OUT1は配線L1の電位と内部クロック信号LCLKとの論理積信号となっている。その結果、長周期クロック出力モードでの内部クロック信号LCLK_OUT1は、図2にも示したように、内部クロック信号LCLKの4倍の周期を有する長周期クロック信号となる。

【0082】

図7は、本発明の好ましい第2の実施の形態による半導体装置が備えるクロック出力制御回路73の内部構成を示す回路図である。本実施の形態による半導体装置は、クロック出力制御回路73の内部構成以外の点では、第1の実施の形態による半導体装置10と同一であるので、以下ではクロック出力制御回路73の内部構成についてのみ説明する。

【0083】

図7に示すように、本実施の形態によるクロック出力制御回路73も、供給制御回路20及び周期伸長回路21を有して構成される。ただし、これらの内部構成は第1の実施の形態で説明したものと異なっており、その結果、本実施の形態では、アクティブ期間内において活性化される長周期の内部クロック信号LCLK_OUT1は、内部クロック信号LCLKの4倍の周期を有し、かつハイのパルス幅が内部クロック信号LCLKの4倍である信号となる。以下、詳しく説明する。

【0084】

本実施の形態による供給制御回路20は、図7に示すように、NAND回路NA1〜NA6,インバータINV1〜INV6を有している。内部クロック信号LCLKと内部アイドルコマンドIDLEとは、NAND回路NA1の入力端に供給される。内部リードコマンドREADは、インバータINV3の入力端に供給される。内部アクティブコマンドACTは、インバータINV4の入力端及びNAND回路NA2の入力端に供給される。

【0085】

NAND回路NA1の出力端は、インバータINV1,INV2をこの順で介して、NAND回路NA3の入力端に接続される。NAND回路NA2の出力端も、NAND回路NA3の入力端に接続される。インバータINV3の出力端は、NAND回路NA2の入力端及びNAND回路NA5の入力端に接続される。インバータINV4の出力端は、インバータINV5を介して、NAND回路NA4の入力端に接続される。NAND回路NA4の出力端は、NAND回路NA5の入力端に接続される。

【0086】

NAND回路NA3,NA5の出力端は、ともにNAND回路NA6の入力端に接続される。以下では、NAND回路NA5の出力端とNAND回路NA6の入力端とを接続する配線を配線L2と称する。NAND回路NA6の出力端は、インバータINV6を介して、出力ノード73aに出力される。したがって、内部クロック信号LCLK_OUT1はNAND回路NA6の出力信号の反転信号となる。

【0087】

本実施の形態による周期伸長回路21は、図7に示すように、クロック信号LCLK2_2が供給制御回路20に供給されることがない点で、図5に示した周期伸長回路21と異なっている。これ以外の点では両者は同一であるので、詳しい説明は省略する。

【0088】

以上説明した構成により、まず内部アイドルコマンドIDLEがロウレベルとなっている場合、出力ノード73aの電位はロウレベルに固定される(クロック停止モード)。この場合、内部クロック信号LCLK_OUT1はクロック伝送回路3に供給されない。

【0089】

一方、内部アイドルコマンドIDLEがハイレベルとなっている場合には、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間(アクティブ期間)においては、クロック信号LCLK4_2が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(長周期クロック出力モード)。本実施の形態では、クロック信号LCLK4_2が、内部クロック信号LCLKよりも周期の長い長周期クロック信号に相当する。

【0090】

また、内部リードコマンドREADが活性化されてから内部リードコマンドREADが非活性化するまでの期間(リード期間)においては、内部クロック信号LCLKが、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(通常クロック出力モード)。

【0091】

図8は、本実施の形態によるクロック出力制御回路73に関わる各信号の、長周期クロック出力モードにおける時間変化を示すタイミング図である。同図に示す各信号のうち、内部クロック信号LCLKとクロック信号LCLK4_2については、図6に示したものと同一である。

【0092】

図8に示すように、配線L2の電位はクロック信号LCLK4_2と同一となっており、内部クロック信号LCLK_OUT1にもクロック信号LCLK4_2がそのまま現れている。その結果、本実施の形態による長周期クロック信号は、図6に示した内部クロック信号LCLK_OUT1のようなパルス状の信号ではなく、図8に示すようなデューティー比50:50の信号となる。

【0093】

以上説明したように、本実施の形態による半導体装置10によれば、長周期クロック出力モードでクロック伝送回路3に供給する長周期クロック信号を、デューティー比50:50の信号とすることが可能になる。

【0094】

図9は、本発明の好ましい第2の実施の形態の変形例による半導体装置が備えるクロック出力制御回路73の内部構成を示す回路図である。本変形例では、クロック出力制御回路73から出力される内部クロック信号LCLK_OUT1は第2の実施の形態によるものと同一であるが、供給制御回路20の内部構成が第2の実施の形態によるものと異なっている。そこで以下では、本変形例による供給制御回路20の内部構成について、詳しく説明する。

【0095】

本変形例による供給制御回路20は、図9に示すように、NAND回路NA1,インバータINV1〜INV5、NOR回路NOR1、及びセレクタ回路SEL1を有している。内部クロック信号LCLKと内部アイドルコマンドIDLEとは、NAND回路NA1の入力端に供給される。内部リードコマンドREADは、NOR回路NOR1の入力端に供給される。内部アクティブコマンドACTは、インバータINV5を介して、NOR回路NOR1の入力端に供給される。

【0096】

NAND回路NA1の出力端は、インバータINV1〜INV3をこの順で介して、セレクタ回路SEL1の一方入力端に接続される。セレクタ回路SEL1の他方入力端には、周期伸長回路21からクロック信号LCLK4_2が供給される。

【0097】

セレクタ回路SEL1は、NOR回路NOR1の出力がハイレベルである場合にクロック信号LCLK4_2の反転信号を出力し、ロウレベルである場合にインバータINV3の出力信号の反転信号を出力するよう構成される。セレクタ回路SEL1の出力信号は、インバータINV4を介して、出力ノード73aに出力される。したがって、内部クロック信号LCLK_OUT1はセレクタ回路SEL1の出力信号の反転信号となる。

【0098】

以上説明した構成により、まず内部アイドルコマンドIDLEがロウレベルとなっている場合、この場合には内部アクティブコマンドACT及び内部リードコマンドREADもロウレベルになっているので、セレクタ回路SEL1の出力信号はハイレベルに固定される。したがって、出力ノード73aの電位はロウレベルに固定される(クロック停止モード)。

【0099】

一方、内部アイドルコマンドIDLEがハイレベルとなっている場合には、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間(アクティブ期間)においては、クロック信号LCLK4_2が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(長周期クロック出力モード)。本変形例でも、クロック信号LCLK4_2が、内部クロック信号LCLKよりも周期の長い長周期クロック信号に相当する。

【0100】

また、内部リードコマンドREADが活性化されてから内部リードコマンドREADが非活性化するまでの期間(リード期間)においては、内部クロック信号LCLKが、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(通常クロック出力モード)。

【0101】

つまり、本実施の形態によれば、第2の実施の形態とは異なる内部構成を有する供給制御回路20を用いて、第2の実施の形態と同一の内部クロック信号LCLK_OUT1を得ることが可能になっている。

【0102】

図10は、本発明の好ましい第3の実施の形態による半導体装置が備えるクロック出力制御回路73の内部構成を示す回路図である。本実施の形態による半導体装置も、クロック出力制御回路73の内部構成以外の点では、第1の実施の形態による半導体装置10と同一であるので、以下ではクロック出力制御回路73の内部構成についてのみ説明する。

【0103】

図10に示すように、本実施の形態によるクロック出力制御回路73も、供給制御回路20及び周期伸長回路21を有して構成される。ただし、これらの内部構成は第1の実施の形態で説明したものと異なっており、その結果、長周期クロック信号の波形が第1の実施の形態と異なっている。以下、詳しく説明する。

【0104】

本実施の形態による供給制御回路20は、図10に示すように、NAND回路NA2が4入力で構成され、内部アクティブコマンドACT及びクロック信号LCLK2_2,LCLK4_2の他に、周期伸長回路21が出力するクロック信号LCLK8_2も供給される点で、図3に示した供給制御回路20と異なっている。これ以外の点では両者は同一であるので、詳しい説明は省略する。

【0105】

本実施の形態による周期伸長回路21は、図10に示すように、それぞれP型チャネルMOSトランジスタ及びN型チャネルMOSトランジスタによって構成される2個のトランスファーゲートTRF8−1,TRF8−2と、インバータINV8−1〜INV8−7をさらに有する点で、図5に示した周期伸長回路21と異なっている。また、本実施の形態による周期伸長回路21では、インバータINV4−7の出力端からクロック信号LCLK4_1が取り出される点でも、図5に示した周期伸長回路21と異なっている。以下、これらの相違点を中心に説明する。

【0106】

トランスファーゲートTRF8−1の出力端は、インバータINV8−2の出力端とインバータINV8−3の入力端に接続される。インバータINV8−2の入力端とインバータINV8−3の出力端とはともにインバータINV8−4の入力端に接続され、インバータINV8−4の出力端は、トランスファーゲートTRF8−2の入力端に接続される。トランスファーゲートTRF8−2の出力端は、インバータINV8−5の出力端とインバータINV8−6の入力端に接続される。インバータINV8−5の入力端とインバータINV8−6の出力端とはともにインバータINV8−7の入力端に接続され、インバータINV8−7の出力端は、インバータINV8−1を介して、トランスファーゲートTRF8−1の入力端に接続される。

【0107】

トランスファーゲートTRF8−1のP型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF8−2のN型チャネルMOSトランジスタの制御端子には、クロック信号LCLK4_2が供給される。一方、トランスファーゲートTRF8−1のN型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF8−2のP型チャネルMOSトランジスタの制御端子には、クロック信号LCLK4_1が供給される。インバータINV8−1の出力端からはクロック信号LCLK8_2が取り出される。クロック信号LCLK8_2は、上述したように、供給制御回路20内のNAND回路NA2に供給される。

【0108】

以上説明した構成により、まず内部アイドルコマンドIDLEがロウレベルとなっている場合、出力ノード73aの電位はロウレベルに固定される(クロック停止モード)。

【0109】

一方、内部アイドルコマンドIDLEがハイレベルとなっている場合には、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間(アクティブ期間)においては、クロック信号LCLK2_2、クロック信号LCLK4_2、クロック信号LCLK8_2、及び内部クロック信号LCLKの論理積信号が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(長周期クロック出力モード)。本実施の形態では、この論理積信号が、内部クロック信号LCLKよりも周期の長い長周期クロック信号に相当する。

【0110】

また、内部リードコマンドREADが活性化されてから内部リードコマンドREADが非活性化するまでの期間(リード期間)においては、内部クロック信号LCLK(第2のクロック信号)が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(通常クロック出力モード)。

【0111】

クロック信号LCLK8_2は、内部クロック信号LCLKの8倍の周期を有する周期信号である。したがって、本実施の形態による長周期クロック信号は、内部クロック信号LCLKの8倍の周期を有する周期信号となる。

【0112】

以上説明したように、本実施の形態による半導体装置10によれば、アクティブ期間内にクロック伝送回路3に供給する長周期クロック信号の周期を、内部クロック信号LCLKの周期の8倍とすることができる。したがって、クロック伝送回路3の電流消費量を、より抑えることが可能になる。

【0113】

以上、本発明の好ましい実施の形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【符号の説明】

【0114】

3 クロック伝送回路

10 半導体装置

11 クロック端子

12 コマンド端子

13 アドレス端子

14 データ入出力端子

15 データストローブ端子

16 入出力回路

16a,16b 電源端子

20 供給制御回路

21 周期伸長回路

31 コマンドバッファ

32 コマンドデコーダ

40 クロックバッファ

41 アドレスバッファ

51 ロウ系制御回路

52 カラム系制御回路

53 リフレッシュ回路

60 メモリセルアレイ

61 センス回路

62 リードライトアンプ

64 入出力回路

65 DQS入出力回路

70 DLL回路

71 DLLリフレッシュ制御回路

72 レプリカ回路

73,74 クロック出力制御回路

73a 出力ノード

75 バッファ回路

76 クロックツリー

77 ROM

80〜82 内部電圧発生回路

90 OR回路

ACT アクティブコマンド,内部アクティブコマンド

IDLE 内部アイドルコマンド

INV1〜INV6,INV2−1〜INV2−7,INV4−1〜INV4−7,INV8−1〜INV8−7 インバータ

L1,L2 配線

LCLK,LCLK_OUT1,LCLK_OUT2 内部クロック信号

LCLK2_1,LCLK2−2,LCLK4−1,LCLK4−2,LCLK8−2 クロック信号

NA1〜NA6 NAND回路

NOR1 NOR回路

READ リードコマンド,内部リードコマンド

S1 起動信号

SEL1 セレクタ回路

TRF2−1,TRF2−2,TRF4−1,TRF4−2,TRF8−1,TRF8−2 トランスファーゲート

VDD,VSS 外部電源電圧

VPERD,VPERI2,VPERI 内部電圧

【技術分野】

【0001】

本発明は半導体装置に関し、特に、外部クロック信号に同期してリードデータを出力する半導体装置に関する。

【背景技術】

【0002】

近年、高速化するクロックに同期した動作を行う半導体装置としてパーソナルコンピュータなどのメインメモリとして用いられるDDR(Double Data Rate)型のシンクロナスメモリが多く用いられている。このような半導体装置は、リードデータの出力タイミングを外部クロック信号に対して同期させる構成を採用する。これは、コントローラと半導体装置間のデータ送受信を外部クロック信号に同期したタイミングで行うように取り決めておくことで互いのデータ送受信をミスなく実行するためである。しかしながら、半導体装置自身にも内部遅延は存在するため、その遅延時間を考慮しつつリードデータの出力タイミングが外部クロックに同期出来るように半導体装置内部において内部クロックを生成する必要がある。それを実現するための回路がDLL(Delay Locked Loop)回路である。特許文献1には、このようなDLL回路の例が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−278528号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ここで、半導体装置は近年、低消費電力化が進んでいる。一般に消費電力が大きいとされるDLL回路における消費電力の削減は、半導体装置そのものの低消費電力化に大きく寄与する事が出来るが、一方で、半導体装置は高速化もまた進んでおり、高速化に伴うタイミング調整の高精度化を考慮すれば、DLL回路における消費電力は大きくなる方向である。本発明は、そのようなDLL回路において消費電力を抑えつつタイミング調整も高精度とする半導体装置を提供することを課題とするものである。

【課題を解決するための手段】

【0005】

本発明による半導体装置は、アクティブ期間内に内部クロック信号よりも周期の長い長周期クロック信号を供給し、前記アクティブ期間に続くリード期間内に前記内部クロック信号を供給するクロック出力制御回路と、前記クロック出力制御回路から出力された前記内部クロック信号及び前記長周期クロック信号を伝送するクロック伝送回路と、外部データ端子と、前記クロック伝送回路によって伝送された前記内部クロック信号に同期して、前記外部データ端子にリードデータを出力する出力回路とを備えることを特徴とする。

【発明の効果】

【0006】

本発明によれば、アクティブ期間内からクロック信号がクロック伝送回路に供給されるので、リード期間の開始期における内部電圧VPERI2の低下幅が小さくなり、リードデータのジッタが軽減される。また、アクティブ期間内には、クロック出力制御回路に内部クロック信号よりも周期の長い長周期クロック信号を供給させるので、アクティブ期間内にも内部クロック信号を供給させ続ける場合に比べ、クロック伝送回路の電流消費量を抑えることが可能になる。

【図面の簡単な説明】

【0007】

【図1】本発明の好ましい実施の形態による半導体装置の全体構成を示すブロック図である。

【図2】外部クロック信号CKS、内部クロック信号LCLK,LCLK2_2,LCLK4_2、クロック出力制御回路の出力ノードの電位、及び内部電圧VPERI2の時間変化を示すグラフである。

【図3】外部クロック信号CKS、内部クロック信号LCLK,LCLK2_2,LCLK4_2、クロック出力制御回路の出力ノードの電位、及び内部電圧VPERI2の時間変化を示すグラフである。

【図4】本発明の好ましい第1の実施の形態によるクロック出力制御回路及びその周辺回路の構成を示す図である。

【図5】本発明の好ましい第1の実施の形態によるクロック出力制御回路の内部構成を示す回路図である。

【図6】本発明の好ましい第1の実施の形態によるクロック出力制御回路に関わる各信号の、長周期クロック出力モードにおける時間変化を示すタイミング図である。

【図7】本発明の好ましい第2の実施の形態による半導体装置が備えるクロック出力制御回路の内部構成を示す回路図である。

【図8】本発明の好ましい第2の実施の形態によるクロック出力制御回路に関わる各信号の、長周期クロック出力モードにおける時間変化を示すタイミング図である。

【図9】本発明の好ましい第2の実施の形態の変形例による半導体装置が備えるクロック出力制御回路の内部構成を示す回路図である。

【図10】本発明の好ましい第3の実施の形態による半導体装置が備えるクロック出力制御回路の内部構成を示す回路図である。

【発明を実施するための形態】

【0008】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について詳細に説明する。

【0009】

まず初めに、発明の特徴部分の理解を容易ならしめるために、本発明者が検討した本願発明の技術思想について説明する。

【0010】

本願発明者は、DLL回路及びその周辺回路の設計に当たり、その消費電力を削減しつつも位相制御等の精度を維持出来る手段について次のように検討した。まず消費電力の削減については、DLL回路が出力する内部クロック信号LCLKがリード時に用いられる一方、ライト等他のタイミングでは用いられない点に着目し、必要とされるリード時以外のタイミングにおいて停止させれば良いことを発見した。それによって図1におけるバッファ回路75及びクロックツリー76における消費電力をリード時以外の期間において削減することが可能となる。半導体装置の動作スペックとの兼ね合いではあるが、所謂動作速度の比較的遅い高精度が要求されない半導体装置であれば、そのような制御でも足りる。

【0011】

一方、動作速度の早い高精度を要求する半導体装置においてもそのような制御を行うと確かに消費電力は削減されるが、DLL回路の出力する内部クロック信号LCLKについて不都合を生じ、高精度の要求に合わなくなることも併せて発見した。上記停止はリードコマンド時の動作開始直後における過渡的な内部電圧VPERI2の変化を大きくしてしまい、その結果、バッファ回路75及びクロックツリー76において特にクロックのデューティーを乱すジッタが発生されてしまうからである。

【0012】

内部電圧VPERI2の電位は図1における内部電源発生回路VPEIR2_GENによって所定のリファレンス電位と内部電圧VPERI2を比較することで所定のリファレンス電位と等しくなるように制御されるが、そのような過渡的な電圧変化には追随出来ないため、具体的には短時間に内部電圧VPERI2の電位は第1の電位→第2の電位→第3の電位(第1>第2>第3の電位)として変化する。それぞれの電位は、

第1の電位…バッファ回路75及びクロックツリー76が動作していない状況において内部電源発生回路VPERI2_GENにより上昇された電位

第2の電位…リードコマンド時のバッファ回路75及びクロックツリー76動作開始直後による過渡的な電位降下(まだ内部電圧発生回路VPERI2_GENの動作が内部電圧VPERI2に反映されていない)を受けた電位

第3の電位…内部電圧発生回路VPERI2_GEN及びバッファ回路75及びクロックツリー76が動作することによってバランスされる電位

である。バッファ回路75もクロックツリー76も内部電圧VPERI2をソースとするトランジスタにより構成されるものであるから、そのソース電位が変化すればクロックの遷移時間も変わる(ソース電位が高い…変化が早い。ソース電位が低い…変化が遅い)。具体的に、あるクロックの立ち上がり時にソース電位が高く、下がり時にソース電位が低く、次の立ち上がり時にはソース電位が高くなったケースにおいてトランジスタを介して出力されるクロックはハイ幅が大きく、ロー幅が小さいものとなってしまい、出力されるクロックの位相や特にデューティー比が大きく崩れてしまう。

【0013】

そのような問題に対処するため、本願発明者はリードコマンド時の手前のタイミングにおいて内部電圧VPERI2を多少消費する動作を行うことで、内部電圧VPERI2の電位を上記第1の電位よりも低く且つ第3の電位よりも高い電位に待機させておき、リードコマンド時においても内部電圧VPERI2の大きな変化が生じないように制御させることを発明した。このような制御を行うことで相対的な内部電圧VPERI2の変化を小さく抑えることが可能となり、それによる上記位相やデューティー比の悪化を防止することが可能となる。

【0014】

図1は、本発明の好ましい実施の形態による半導体装置10の全体構成を示すブロック図である。

【0015】

本実施の形態による半導体装置10はDDR型のSDRAM(Synchronous Dynamic Random Access Memory)であり、外部端子として、クロック端子11、コマンド端子12、アドレス端子13、データ入出力端子14(外部データ端子)、データストローブ端子15、電源端子16a,16bを備えている。

【0016】

クロック端子11は外部クロック信号CKSが供給される端子であり、供給された外部クロック信号CKSは、クロックバッファ40及びDLL回路70に供給される。クロックバッファ40は、外部クロック信号CKSに基づいて単相の内部クロック信号ICLKを生成し、これをコマンドデコーダ32及び図示しないその他の回路に供給する。

【0017】

DLL回路70は、外部クロック信号CKSを受けて、外部クロック信号CKSに対して位相制御され、かつデューティー制御された内部クロック信号LCLKを生成する回路である。ここで具体的に、位相制御とはクロックのライズエッジの位相を調整する制御であり、デューティー制御とはクロックのフォールエッジの位相を調整することでクロックの1周期におけるライズ期間及びフォール期間の比(デューティー比)を50:50にする制御である。生成された内部クロック信号LCLKは、クロック出力制御回路73,74に供給される。

【0018】

また、DLL回路70は、内部クロック信号LCLKの位相及びデューティー比がそれぞれ目標値になった(ロックした)か否かを判定する機能と、ロックしたと判定した場合に、オシレータ起動信号DLL_OSC_Enableを活性化する機能とを有する。オシレータ起動信号DLL_OSC_Enableは、DLLリフレッシュ制御回路71に供給される。

【0019】

DLLリフレッシュ制御回路71については後述するが、DLL回路70は、一旦位相制御及びデューティー制御を終えても(ロックしても)半導体装置の温度変化等に追随して再度位相制御等を行うことが望ましく、従って適切な期間を経て再調整を行うべきものである。オシレータ起動信号DLL_OSC_Enableは、一旦の位相制御を終えた後に、次の位相制御を行うまでの期間を測定開始するための起動信号である。実際にその期間の測定は、DLLリフレッシュ制御回路71に含まれるオシレータ回路がオシレータ起動信号DLL_OSC_Enableを受けて動作し、所定数のクロック信号をカウントした後にDLLリフレッシュ制御回路71が再調整を指示するDLLスタート信号DLL_STARTを活性化させることで実現される。そして、該DLLスタート信号DLL_STARTを受けてDLL回路70が再度位相制御等を実行するものである。

【0020】

クロック出力制御回路73は、上記内部クロック信号LCLKを受け、後述する内部アクティブコマンドACT及び内部リードコマンドREADそれぞれの活性状態に応じて動作モードを切り替えながら内部クロック信号LCLK_OUT1を生成し、出力ノード73aに出力する回路である。この動作モードには、内部クロック信号LCLK_OUT1を出力せず、出力ノード73aの電位をロウレベル又はハイレベルに固定するクロック停止モード、内部クロック信号LCLKよりも周期の長いクロック信号(長周期クロック信号)を生成し、内部クロック信号LCLK_OUT1として出力する長周期クロック出力モード、及び、内部クロック信号LCLKを内部クロック信号LCLK_OUT1として出力する通常クロック出力モード、の3つの動作モードが含まれる。出力ノード73aの出力電位は、クロック伝送回路3を経て、FIFO63、入出力回路64、及びDQS入出力回路65に供給される。

【0021】

クロック伝送回路3は、バッファ回路75及びクロックツリー76を含んで構成される。バッファ回路75は、例えば直列に接続された複数のCMOSによって構成される回路であり、内部クロック信号LCLK_OUT1を、FIFO63及びクロックツリー76に出力する。クロックツリー76は、供給された内部クロック信号LCLK_OUT1を入出力回路64及びDQS入出力回路65に分配する回路である。クロックツリー76も、例えば内部に複数のCMOSを含んで構成される。

【0022】

クロック出力制御回路74は、後述するDLLオン信号DLL_ON及びDLLスタート信号DLL_STARTのいずれかが活性化している場合に、内部クロック信号LCLKを内部クロック信号LCLK_OUT2としてレプリカ回路72に供給する回路である。いずれもが活性化していない場合には、クロック出力制御回路74の出力はロウレベル又はハイレベルに固定されるように制御される。

【0023】

レプリカ回路72は、クロック伝送回路3を疑似的に再現した回路である。レプリカ回路72に入力した内部クロック信号LCLK_OUT2は、内部クロック信号LCLK_OUT1がクロック伝送回路3の通過中に受ける遅延や波形変化と実質的に同等の遅延や波形変化を受けて、DLL回路70に供給される。

【0024】

このレプリカ回路によって半導体装置自身が持つ内部遅延を再現し、それをDLL回路にフィードバックして内部クロック信号LCLKのタイミング制御を行うことで半導体装置が外部クロックに同期したタイミングでリードデータを出力することが可能となる

【0025】

コマンド端子12は、クロックイネーブル信号CKE、ロウアドレスストローブ信号/RAS、カラムアドレスストローブ信号/CAS、ライトイネーブル信号/WE、チップセレクト信号/CS、オンダイターミネーション信号ODT、リセット信号/RESET、アクティブコマンド信号ACT、リードコマンド信号READ、アイドルコマンド信号IDLE、プリチャージコマンド信号PRE、パワーダウンコマンド信号PWDNなどの各種コマンド信号CMDが供給される端子である。なお、本明細書において信号名の先頭に「/」が付されている信号は、対応する信号の反転信号又はローアクティブな信号であることを意味する。

【0026】

コマンド端子12に供給されたコマンド信号CMDは、コマンドバッファ31を介してコマンドデコーダ32に供給される。クロックイネーブル信号CKEをバッファリングした内部クロックイネーブル信号ICKEは、クロックバッファ40及びアドレスバッファ41にも供給される。クロックイネーブル信号CKEが非活性状態(内部クロックイネーブル信号ICKEが非活性状態)、所謂パワーダウンモードのときにクロックバッファ40及びアドレスバッファ41の動作を停止させることで消費電力の削減を図るためである。一方、活性状態のときは、クロックバッファ40及びアドレスバッファ41は其々バッファリング動作を行う。

【0027】

コマンドデコーダ32は、コマンドバッファ31からの各種コマンド信号CMDを受け、該コマンド信号CMDの保持、デコード及びカウントなどを行うことによって各種内部コマンドを生成する回路である。これら内部コマンドには、内部アクティブコマンドACT、内部アイドルコマンドIDLE、内部リードコマンドREAD、内部ライトコマンドWRITEなどメモリセルのリード/ライトに関わる各種内部コマンドが含まれる他、DLL回路70の活性化/非活性化を指示するDLLイネーブルコマンドDLLEnableや、メモリセルアレイ60のセルフリフレッシュの開始/停止を指示するセルフリフレッシュコマンドSelfEnableなども含まれる。

【0028】

コマンドデコーダ32によって生成された各内部コマンドは、半導体装置10内の各回路に供給される。具体的には、ロウ系制御回路51に内部アクティブコマンドACTが、クロック出力制御回路73に内部アクティブコマンドACT、内部リードコマンドREAD、及び内部アイドルコマンドIDLEが、カラム系制御回路52に内部リードコマンドREADが、DLLリフレッシュ制御回路71にDLLイネーブルコマンドDLLEnable及びセルフリフレッシュコマンドSelfEnableが、それぞれ供給される。

【0029】

アドレス端子13は、n+1個のアドレスビットA0〜Anからなるアドレス信号ADDが供給される端子であり、供給されたアドレス信号ADDは、アドレスバッファ41においてバッファリングされ、ロウアドレスについてはロウ系制御回路51に、カラムアドレスについてはカラム系制御回路52に、それぞれ供給されてラッチされる。また、モードレジスタセットにエントリしている場合には、一部のアドレス信号ADDは図示しないモードレジスタに供給され、これによって半導体装置の動作モード(バースト長やリードレイテンシー等)を切り替えるモードレジスタの内容が更新される。

【0030】

ロウ系制御回路51は、アドレスバッファ41より供給されるロウアドレスに基づいて、メモリセルアレイ60に含まれるいずれかのワード線WLを選択する回路である。メモリセルアレイ60内においては、複数のワード線WLと複数のビット線BLが交差しており、その交点にはメモリセルMCが配置されている(図1では、1本のワード線WL、1本のビット線BL及び1個のメモリセルMCのみを示している)。ビット線BLは、センス回路61内の対応するセンスアンプSAに接続されている。

【0031】

カラム系制御回路52は、センス回路61に含まれるいずれかのセンスアンプSAを選択する回路である。カラム系制御回路52によって選択されたセンスアンプSAは、メインI/O線MIOを介してリードライトアンプ(RWAMP)62に接続される。

【0032】

リード動作時においては、センスアンプSAによって増幅されたリードデータDQはリードライトアンプ62でさらに増幅され、FIFO63及び入出力回路64を経て、データ入出力端子14から外部に出力される。一方、ライト動作時においては、データ入出力端子14を通じて外部から入力されたライトデータDQは、順に入出力回路64、FIFO63を経てリードライトアンプ62に入力され、増幅されたうえでセンスアンプSAに供給される。

【0033】

データ入出力端子14は、リードデータDQの出力及びライトデータDQの入力を行うための端子である。半導体装置10にはm+1個(m≧0)のデータ入出力端子14が設けられ、m+1ビットのデータを同時に入力又は出力可能とされている。

【0034】

FIFO63はリードデータDQ又はライトデータDQのキューイングを行う先入れ先出しの回路であり、データ入出力端子14ごとに設けられる。リード動作時に着目して説明すると、リードライトアンプ62から出力されたリードデータDQは、図示しないマルチプレクサによってデータ入出力端子14ごとに振り分けられ、対応するFIFO63にキューイングされる。FIFO63は、キューイングしたリードデータDQを内部クロック信号LCLKに同期したタイミングで、入出力回路64に出力する。

【0035】

入出力回路64は、それぞれデータ入出力端子14ごとに設けられた出力回路及び入力回路を有して構成される。リード動作時に着目して説明すると、出力バッファは、対応するFIFO63から出力されたリードデータDQを整形し、内部クロック信号LCLK_OUT1に同期したタイミングで、対応するデータ入出力端子14から外部に出力する。

【0036】

データストローブ端子15は、DQS入出力回路65と外部のコントローラとの間で、データ入出力の動作基準となるデータストローブ信号DQSの入出力を行うための端子である。DQS入出力回路65は、それぞれデータ入出力端子14ごとに設けられた出力回路及び入力回路を有して構成される。

【0037】

ライト時には、データストローブ端子15を通じて、外部からDQS入出力回路65にデータストローブ信号DQSが入力される。DQS入出力回路65は、こうして入力されたデータストローブ信号DQSに基づいて、入出力回路64がデータ入出力端子14からライトデータDQを取り込むタイミングを制御する。

【0038】

一方、リード時には、半導体装置10の内部からDQS入出力回路65に、データストローブデータ信号DQS_DATAが供給される。DQS入出力回路65は、クロックツリー76から供給される内部クロック信号LCLK_OUT1に同期して、データストローブデータ信号DQS_DATAをデータストローブ端子15に出力する。外部のコントローラは、こうして出力されたデータストローブデータ信号DQS_DATAに同期して、データ入出力端子14から出力されるリードデータDQを取り込む。つまり、DLL回路70はこのデータストローブデータ信号DQS_DATAが外部クロック信号CKSと同期するように内部クロック信号LCLKを制御するものである。

【0039】

DLLリフレッシュ制御回路71は、メモリセルアレイ60のセルフリフレッシュを行うタイミングと、DLL回路70が起動するタイミングとを制御する回路である。DLLの高精度化及び低消費電力を課題とする本発明において、セルフリフレッシュの制御方法は関知されないものではあるが、セルフリフレッシュの制御タイミングもDLL回路70の起動タイミングもDLLリフレッシュ制御回路71に含まれる共通のオシレータ回路を用いることで面積の削減を行うことが出来るため、このように共通の回路としている。本発明の思想は共通化せずにセルフリフレッシュ用、DLL制御用のものを其々設けることも含むものである。DLLリフレッシュ制御回路71には、上述したDLLイネーブルコマンドDLLEnable、セルフリフレッシュコマンドSelfEnable、及びオシレータ起動信号DLL_OSC_Enableの他に、セルフリフレッシュの間隔を示すデータSelf_Timing及びDLL回路70の定期起動の間隔を示すデータDLL_Timingが、ROM77から供給される。これらのデータは、製造中の時点でROM77に書き込まれる。

【0040】

DLLリフレッシュ制御回路71は、まずDLL回路70に関しては、入力されるDLLイネーブルコマンドDLLEnableが活性化されている場合に、DLLの起動期間を示すDLLオン信号DLL_ONを活性化し、そうでない場合にDLLオン信号DLL_ONを非活性化する。DLLオン信号DLL_ONはDLL回路70、クロック出力制御回路74、及びレプリカ回路72に供給される。DLL回路70は、DLLオン信号DLL_ONが活性化されている場合に、内部クロック信号LCLKの位相制御、デューティー制御を行い、それらが調整された内部クロック信号LCLKを生成する。これを最初の調整と呼ぶこととする。その最初の調整が終わった(DLL回路がロックした)時にDLL回路70はオシレータ起動信号DLL_OSC_Enableを活性化する。

【0041】

続いて、DLLリフレッシュ制御回路71は、入力されるオシレータ起動信号DLL_OSC_Enableが活性化されている場合に、データDLL_Timingによって示される間隔で定期的に、DLL回路70の更新期間を示すDLLスタート信号DLL_STARTを活性化する。DLLスタート信号DLL_STARTは、オシレータ起動信号DLL_OSC_EnableがDLLリフレッシュ制御回路71内の図示しないオシレータ回路に入力されてクロックの発振を行い、該クロックを所定数カウントした後に活性化されるように構成されている。DLLスタート信号DLL_STARTにより、DLL回路において2回目以降の内部クロックLCLKの調整を行うためである。このようにして、DLL回路70は、定期的に内部クロック信号LCLKを調整してリードデータの出力タイミングが外部クロックにどのようなタイミングにおいても同期出来るように半導体装置内部において内部クロックLCLKを生成することを可能としている。

【0042】

セルフリフレッシュに関しては、DLLリフレッシュ制御回路71は、セルフリフレッシュコマンドSelfEnableが活性化されている場合に、データSelf_Timingによって示される間隔で定期的にセルフリフレッシュ開始信号SREF_STARTを生成し、リフレッシュ回路(REF)53に出力する。このセルフリフレッシュ開始信号SREF_STARTを活性化するのもまた上記オシレータの制御による。リフレッシュ回路53は、ロウアドレスを所定の順序で出力する回路である。リフレッシュ回路53は、セルフリフレッシュ開始信号SREF_STARTを受けると、前回出力したロウアドレスの次のロウドレスをロウ系制御回路51に出力する。この処理を繰り返すことで、最終的には全ロウアドレスについて、セルフリフレッシュが行われる。

【0043】

電源端子16a,16bはそれぞれ、外部電源電圧VDD,VSSが供給される端子である。内部電圧発生回路80〜82はそれぞれ、これら外部電源電圧VDD,VSSに基づいて内部電圧VPERD,VPERI2,VPERIを生成し、半導体装置10内部の各回路に供給する。具体的には、内部電圧VPERDは、DLL回路70の動作電源として供給される。また、内部電圧VPERI2は、クロック出力制御回路73,74及びクロック伝送回路3(バッファ回路75及びクロックツリー76)の動作電源として供給される。内部電圧VPERIは、図示しない周辺回路の動作電源として供給される。

【0044】

内部電圧発生回路80〜82は、図示していないが、それぞれ差動アンプとドライバトランジスタを有している。ドライバトランジスタは、外部電源電圧VDDが供給される電源配線と、対応する内部電圧が供給される内部電源配線との間に挿入される。ドライバトランジスタの制御端子は、差動アンプの出力端子に接続される。差動アンプは、生成する内部電圧の目標値の電圧を有するリファレンス電圧を受け、ドライバトランジスタの制御端子に与える電圧(ドライバトランジスタのゲート−ソース間電圧)を調整することにより、対応する内部電源配線の電位がリファレンス電圧と同一値となるように動作する回路である。ただし、実際には完全には同一とならず、内部電源配線の電位は、内部電圧の供給先回路の電流消費量とバランスして相対的にリファレンス電位よりも小さい値となる。また、内部電圧の供給先回路の電流消費量が急激に増大した場合には、既述のように差動アンプの制御が追い付かず、対応する内部電源配線の電位が一時的に大きく低下することがある。

【0045】

ここで、上記回路構成における特にDLL回路及びその周辺回路の動作について図2及び図3を参照して説明する。図2及び図3はそれぞれ、外部クロック信号CKS、内部クロック信号LCLK,LCLK2_2,LCLK4_2、出力ノード73aの電位、及びクロック伝送回路3の動作電圧である内部電圧VPERI2の時間変化を示すグラフである。なお、内部クロック信号LCLK2_2,LCLK4_2はそれぞれ、内部クロック信号LCLKの周期を2倍,4倍に延ばした信号である。

【0046】

外部コントローラからコマンド端子12にアイドルコマンド信号IDLEが供給されると、これに応じてDLL回路70が活性化し、図2に示すように、内部クロック信号LCLKの生成とクロック出力制御回路73等への供給が開始される。これを受け、クロック出力制御回路73は、内部処理として内部クロック信号LCLK2_2,LCLK4_2の生成を開始する。この時点では、出力ノード73aの電位はロウレベルに固定され(クロック停止モード)、内部電圧VPERI2は所定のリファレンス電位REFとなっている。

【0047】

続いて、アクティブコマンド信号ACTが供給されると、コマンドデコーダ32は内部アクティブコマンドACTを活性化する。なお、本発明では、内部アクティブコマンドACTが活性化されてから内部リードコマンドREADが活性化されるまでの期間を「アクティブ期間」と称する。アクティブ期間に入ると、クロック出力制御回路73は、内部クロック信号LCLK_OUT1の生成とクロック伝送回路3への供給を開始する。内部クロック信号LCLK_OUT1の生成は、内部クロック信号LCLK2_2,LCLK4_2を利用して行われるが、その詳細については後述する。

【0048】

アクティブ期間内において生成される内部クロック信号LCLK_OUT1は、内部クロック信号LCLKより長い周期を有する長周期クロック信号となる。図2には、例として4倍の周期を有する場合を描画している。内部クロック信号LCLK_OUT1の生成が開始されたことにより、内部電圧VPERI2の電位は、図2に示すように、アクティブ期間の開始時点において一旦大きく低下した後に漸増し、リファレンス電位REF−ΔV1の電位で安定する。

【0049】

なお、図2には2種類の内部クロック信号LCLK_OUT1を記載している。これらはともに内部クロック信号LCLKの4倍の周期を有する長周期クロック信号であるが、ハイのパルス幅が異なっている。内部クロック信号LCLK_OUT1(図6)のハイのパルス幅は内部クロック信号LCLKと同一であり、後に第1の実施の形態で詳しく説明する。内部クロック信号LCLK_OUT1(図8)のハイのパルス幅は内部クロック信号LCLKの4倍であり、後に第2の実施の形態で詳しく説明する。

【0050】

次に、リードコマンド信号READが供給されると、コマンドデコーダ32は内部リードコマンドREADを活性化する。なお、本発明では、内部リードコマンドREADが活性化されてからリードデータの出力が完了するまでの期間を「リード期間」と称する。リード期間内における内部クロック信号LCLK_OUT1は、内部クロック信号LCLKと同一の周期を有する通常のクロック信号に切り替えられる。これにより、内部電圧VPERI2の電位は、図2に示すように、リード期間の開始時点において一旦大きく低下した後漸増し、リファレンス電位REF−ΔV1−ΔV2の電位で安定する。

【0051】

図2から明らかなように、アクティブ期間内に長周期の内部クロック信号LCLK_OUT1を生成するようにしたことで、アクティブ期間とリード期間とでの内部電圧VPERI2の電位の差は縮小している。つまり、アクティブ期間内に内部クロック信号LCLK_OUT1を生成しない背景技術においては、この差はΔV1+ΔV2(図示したΔVB)となるが、アクティブ期間内に内部クロック信号LCLK_OUT1を生成するようにしたことで、ΔV2に縮小している。これにより、リード期間の開始時点における一時的な電位低下の幅も小さくなっている。

【0052】

このような電位低下幅の縮小により、半導体装置10では、リード期間の開始期における信号の立ち上がり時間及び立ち下がり時間の揺らぎが、背景技術に比べて小さくなる。したがって、クロック伝送回路3を介して入出力回路64に供給される内部クロック信号のデューティー比の崩れ(ジッタ)が、背景技術に比べて軽減される。内部クロック信号のジッタが軽減されれば、この内部クロック信号に同期して出力されるリードデータDQのジッタも軽減される。

【0053】

また、図3に示すように、外部からパワーダウンコマンド信号PWDNが供給されると、次にアイドルコマンド信号IDLEが供給されるまでの間、DLL回路70は内部クロック信号LCLKの生成を停止する。なお、本発明では、パワーダウンコマンド信号PWDNが供給されてからアイドルコマンド信号IDLEが供給されるまでの期間を「パワーダウン期間」と称する。パワーダウン期間においては、クロック出力制御回路73による内部クロック信号LCLK2_2,LCLK4_2の生成も停止され、出力ノード73aの電位はロウレベルに固定される。これにより、パワーダウン期間内の電流消費量が軽減される。

【0054】

以上説明したように、本実施の形態による半導体装置10によれば、アクティブ期間内から内部クロック信号LCLK_OUT1がクロック伝送回路3に供給されるので、リード期間の開始期における内部電圧VPERI2の低下幅が小さくなり、リードデータDQのジッタが軽減される。また、アクティブ期間内にクロック出力制御回路73が供給するクロック信号は、内部クロック信号LCLKの4倍の周期を有する長周期クロック信号となるので、アクティブ期間内にも内部クロック信号LCLKを供給する場合に比べ、クロック伝送回路3の電流消費量を抑えることが可能になる。さらに、パワーダウン期間内の電流消費量を抑えることも可能になる。

【0055】

以上が本実施の形態による半導体装置10の全体構成である。次に、クロック出力制御回路73について、詳細に説明する。

【0056】

図4は、本発明の第1の実施の形態によるクロック出力制御回路73及びその周辺回路の構成を示す図である。また、図5は、クロック出力制御回路73の内部構成を示す回路図である。本実施の形態では、アクティブ期間内において活性化される長周期の内部クロック信号LCLK_OUT1は、内部クロック信号LCLKの4倍の周期を有し、かつ内部クロック信号LCLKに等しいハイのパルス幅と有する信号である。

【0057】

図4に開示されるDLL回路70には、上述したように、外部クロック信号CKS、DLLオン信号DLL_ON、DLLスタート信号DLL_START、及びオシレータ起動信号DLL_OSC_Enableが供給される。DLLオン信号DLL_ON及びDLLスタート信号DLL_STARTはOR回路90にも供給され、OR回路90から、これらのうちいずれか一方が活性化されているときに活性化し、それ以外のときに非活性となるDLL起動信号S1が出力される。DLL起動信号S1は、クロック出力制御回路74及びレプリカ回路72に供給される。

【0058】

DLL回路70は、上述したように、外部クロック信号CKSを受けて、外部クロック信号CKSに対して位相制御され、かつデューティー制御された内部クロック信号LCLKを生成する回路である。具体的には、図示していないが、遅延回路、位相比較回路、デューティー比較回路、分周回路、及びカウンタ回路を有して構成される。遅延回路は、外部クロック信号を遅延させて内部クロック信号を生成する回路であり、その遅延量はカウンタ回路のカウンタ値によって制御される。遅延回路が生成した内部クロック信号LCLKは、クロック出力制御回路73,74それぞれに入力され、其々において所定の制御を受けて、内部クロック信号LCLK_OUT1,LCLK_OUT2として出力される。

【0059】

このうち、内部クロック信号LCLK_OUT2は、上述したように、レプリカ回路72を経てDLL回路70に戻される。レプリカ回路72は、内部クロック信号LCLKが伝送されるバッファ回路75、クロックツリー76、DQS出力回路65の遅延量を模倣して構成される回路である。内部クロック信号LCLKを、DQS入出力回路15を介して外部へ出力されるタイミングにおいて外部クロック信号CKSと同期させるためである。レプリカ回路72を経てDLL回路70に戻った内部クロック信号LCLK_OUT2は、位相比較回路及びデューティー比較回路に供給される。位相比較回路は、外部クロック信号CKSの位相と内部クロック信号LCLK_OUT2の位相とを比較し、その結果をカウンタ回路に出力する。デューティー比較回路は、内部クロック信号LCLK_OUT2のデューティー比を予め記憶している所定値と比較し、その結果をカウンタ回路に出力する。カウンタ回路は、こうして入力された比較結果に基づき、カウント値のアップ又はダウンを行う。ここで、分周回路は、オシレータ起動信号DLL_OSC_Enableが活性化している場合に、外部クロック信号CKSを分周し、分周クロックとして出力する回路である。カウンタ回路によるカウント値の更新は、DLLオン信号DLL_ON及びDLLスタート信号DLL_STARTのいずれかが活性化している場合に、分周回路から出力される分周クロックに同期して行われる。

【0060】

以上の各回路の処理により、遅延回路の出力する内部クロック信号LCLKは、それ自身がDQS入出力回路15を介して外部へ出力されるタイミングにおいて外部クロック信号CKSと同期し、かつデューティー比が上記所定値50:50となるように制御される。

【0061】

次に、図5に示すように、クロック出力制御回路73は、供給制御回路20及び周期伸長回路21を有して構成される。

【0062】

供給制御回路20は、周期伸長回路21により得られる信号から長周期クロック信号を生成し、内部アクティブコマンドACTの活性化に応じてこの長周期クロック信号を出力ノード73aへ供給し、内部リードコマンドREADの活性化に応じて長周期クロック信号から内部クロック信号LCLKに供給を切り替える回路である。

【0063】

このような制御を行うことで、内部アクティブコマンドACT〜内部リードコマンドREADのアクティブ期間内において、クロック出力制御回路73は長周期クロック信号を出力する事となる。この長周期クロック信号は、内部電圧VPERI2の電位を図2に示したようにΔV1だけ下げる役割を果たし、続いて内部リードコマンドREADが活性化しても、その際の電位降下量(及びその後の電位上昇も含めた電位変化量)をΔV2として小さく抑えることが可能となる。尚、ΔV1及びΔV2の絶対値は周期伸張回路21においてその伸張量をどの程度とするかによって調整可能である。図5においては長周期クロック信号の周期を内部クロック信号LCLKの4倍となるようにしているが、4倍が必然ではなく2倍や8倍であっても良い。2倍とすることで上記ΔV2の値を4倍のときよりも更に小さく抑えることが出来る(ΔV1が大きくなる)。一方、8倍とするとΔV2の値は大きくはなるが、アクティブ期間内の消費電力を抑えることが出来る。

【0064】

回路構成として、供給制御回路20は、図5に示すように、NAND回路NA1〜NA4,インバータINV1〜INV5を有している。NAND回路NA1には、内部クロック信号LCLKと内部アイドルコマンドIDLEとが供給される。ここで、内部アイドルコマンドIDLEは、半導体装置10がスリープモードになっているとき(パワーダウン期間)にロウレベル、それ以外のときにハイレベルとなる信号である。したがって、NAND回路NA1の出力は、パワーダウン期間内にはハイレベルに固定され、それ以外のときには内部クロック信号LCLKの反転信号となる。

【0065】

インバータINV1〜INV3は、NAND回路NA1の出力端から順に直列に接続される。したがって、半導体装置10の電源が投入されているとき、インバータINV1,INV3の出力信号は内部クロック信号LCLKと等しくなる。一方、インバータINV2の出力信号は内部クロック信号LCLKの反転信号/LCLKと等しくなる。インバータINV1,INV2の出力信号は、周期伸長回路21に供給される。

【0066】

インバータINV4には、内部リードコマンドREADが供給される。ここで供給される内部リードコマンドREADは、外部からコマンド端子12にリードコマンドREADが入力されてから、入出力回路64によるリードデータDQの出力が完了するまでの期間、継続的に活性化されるハイアクティブな信号である。内部リードコマンドREADが活性化される期間は、上述したリード期間に相当する。インバータINV4の出力信号は、内部リードコマンドREADの反転信号となる。

【0067】

NAND回路NA2には、内部アクティブコマンドACTと、周期伸長回路21が出力するクロック信号LCLK2_2,LCLK4_2とが供給される。ここで供給される内部アクティブコマンドACTは、外部からコマンド端子12にアクティブコマンドACTが入力されてから、入出力回路64によるリードデータDQの出力が完了するまでの期間、継続的に活性化されるハイアクティブな信号である。なお、外部からのコマンドの入力は、必ずアクティブコマンドACT、リードコマンドREADの順で行われ、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間は、上述したアクティブ期間に相当する。NAND回路NA2の出力信号は、内部アクティブコマンドACT、クロック信号LCLK2_2,LCLK4_2がすべてハイレベルであるときにロウレベル、そうでないときにハイレベルとなる。

【0068】

NAND回路NA3には、インバータINV4の出力信号とNAND回路NA2の出力信号とが供給される。したがって、NAND回路NA3の出力信号は、これらがともにハイのときにロウレベル、そうでないときにハイレベルとなる。

【0069】

NAND回路NA4には、インバータINV3の出力信号とNAND回路NA3の出力信号とが供給される。したがって、NAND回路NA4の出力信号は、これらがともにハイのときにロウレベル、そうでないときにハイレベルとなる。以下では、NAND回路NA3の出力端とNAND回路NA4の入力端とを接続する配線を配線L1と称する。

【0070】

インバータINV5には、NAND回路NA4の出力信号が供給される。インバータINV5の出力端は出力ノード73aであり、したがって、内部クロック信号LCLK_OUT1はNAND回路NA4の出力信号の反転信号となる。

【0071】

周期伸長回路21は、内部クロック信号LCLKの周期を延ばす機能を有する回路である。具体的には、図5に示すように、それぞれP型チャネルMOSトランジスタ及びN型チャネルMOSトランジスタによって構成される4個のトランスファーゲートTRF2−1,TRF2−2,TRF4−1,TRF4−2と、インバータINV2−1〜INV2−7,INV4−2〜INV4−7とを有している。

【0072】

トランスファーゲートTRF2−1の出力端は、インバータINV2−2の出力端とインバータINV2−3の入力端に接続される。インバータINV2−2の入力端とインバータINV2−3の出力端とはともにインバータINV2−4の入力端に接続され、インバータINV2−4の出力端は、トランスファーゲートTRF2−2の入力端に接続される。トランスファーゲートTRF2−2の出力端は、インバータINV2−5の出力端とインバータINV2−6の入力端に接続される。インバータINV2−5の入力端とインバータINV2−6の出力端とはともにインバータINV2−7の入力端に接続され、インバータINV2−7の出力端は、インバータINV2−1を介して、トランスファーゲートTRF2−1の入力端に接続される。

【0073】

トランスファーゲートTRF2−1のP型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF2−2のN型チャネルMOSトランジスタの制御端子には、供給制御回路20から内部クロック信号LCLKの反転信号/LCLKが供給される。一方、トランスファーゲートTRF2−1のN型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF2−2のP型チャネルMOSトランジスタの制御端子には、供給制御回路20から内部クロック信号LCLKが供給される。インバータINV2−7の出力端からはクロック信号LCLK2_1が取り出され、インバータINV2−1の出力端からはクロック信号LCLK2_2が取り出される。クロック信号LCLK2_2は、上述したように、供給制御回路20内のNAND回路NA2に供給される。

【0074】

以上の構成により、クロック信号LCLK2_2は、図2に示したように、内部クロック信号LCLKの周期を2倍に延ばした信号となる。

【0075】

図5に戻る。トランスファーゲートTRF4−1の出力端は、インバータINV4−2の出力端とインバータINV4−3の入力端に接続される。インバータINV4−2の入力端とインバータINV4−3の出力端とはともにインバータINV4−4の入力端に接続され、インバータINV4−4の出力端は、トランスファーゲートTRF4−2の入力端に接続される。トランスファーゲートTRF4−2の出力端は、インバータINV4−5の出力端とインバータINV4−6の入力端に接続される。インバータINV4−5の入力端とインバータINV4−6の出力端とはともにインバータINV4−7の入力端に接続され、インバータINV4−7の出力端は、インバータINV4−1を介して、トランスファーゲートTRF4−1の入力端に接続される。

【0076】

トランスファーゲートTRF4−1のP型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF4−2のN型チャネルMOSトランジスタの制御端子には、クロック信号LCLK2_2が供給される。一方、トランスファーゲートTRF4−1のN型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF4−2のP型チャネルMOSトランジスタの制御端子には、クロック信号LCLK2_1が供給される。インバータINV4−1の出力端からは、クロック信号LCLK4_2が取り出される。クロック信号LCLK4_2は、上述したように、供給制御回路20内のNAND回路NA2に供給される。

【0077】

以上の構成により、クロック信号LCLK4_2は、図2に示したように、内部クロック信号LCLKの周期を4倍に延ばした信号となる。

【0078】

以上説明した構成により、まず内部アイドルコマンドIDLEがロウレベルとなっている場合、出力ノード73aの電位はロウレベルに固定される(クロック停止モード)。この場合、内部クロック信号LCLK_OUT1はクロック伝送回路3に供給されない。

【0079】

一方、内部アイドルコマンドIDLEがハイレベルとなっている場合には、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間(アクティブ期間)においては、クロック信号LCLK2_2、クロック信号LCLK4_2、及び内部クロック信号LCLKの論理積信号が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(長周期クロック出力モード)。本実施の形態では、この論理積信号が、内部クロック信号LCLKよりも周期の長い長周期クロック信号に相当する。

【0080】

また、内部リードコマンドREADが活性化されてから内部リードコマンドREADが非活性化するまでの期間(リード期間)においては、内部クロック信号LCLKが、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(通常クロック出力モード)。

【0081】

図6には、長周期クロック出力モードである場合を前提として、配線L1の電位の変化と、内部クロック信号LCLK_OUT1とについても図示している。同図に示すように、配線L1の電位はクロック信号LCLK2_2とクロック信号LCLK4_2との論理積信号となっており、内部クロック信号LCLK_OUT1は配線L1の電位と内部クロック信号LCLKとの論理積信号となっている。その結果、長周期クロック出力モードでの内部クロック信号LCLK_OUT1は、図2にも示したように、内部クロック信号LCLKの4倍の周期を有する長周期クロック信号となる。

【0082】

図7は、本発明の好ましい第2の実施の形態による半導体装置が備えるクロック出力制御回路73の内部構成を示す回路図である。本実施の形態による半導体装置は、クロック出力制御回路73の内部構成以外の点では、第1の実施の形態による半導体装置10と同一であるので、以下ではクロック出力制御回路73の内部構成についてのみ説明する。

【0083】

図7に示すように、本実施の形態によるクロック出力制御回路73も、供給制御回路20及び周期伸長回路21を有して構成される。ただし、これらの内部構成は第1の実施の形態で説明したものと異なっており、その結果、本実施の形態では、アクティブ期間内において活性化される長周期の内部クロック信号LCLK_OUT1は、内部クロック信号LCLKの4倍の周期を有し、かつハイのパルス幅が内部クロック信号LCLKの4倍である信号となる。以下、詳しく説明する。

【0084】

本実施の形態による供給制御回路20は、図7に示すように、NAND回路NA1〜NA6,インバータINV1〜INV6を有している。内部クロック信号LCLKと内部アイドルコマンドIDLEとは、NAND回路NA1の入力端に供給される。内部リードコマンドREADは、インバータINV3の入力端に供給される。内部アクティブコマンドACTは、インバータINV4の入力端及びNAND回路NA2の入力端に供給される。

【0085】

NAND回路NA1の出力端は、インバータINV1,INV2をこの順で介して、NAND回路NA3の入力端に接続される。NAND回路NA2の出力端も、NAND回路NA3の入力端に接続される。インバータINV3の出力端は、NAND回路NA2の入力端及びNAND回路NA5の入力端に接続される。インバータINV4の出力端は、インバータINV5を介して、NAND回路NA4の入力端に接続される。NAND回路NA4の出力端は、NAND回路NA5の入力端に接続される。

【0086】

NAND回路NA3,NA5の出力端は、ともにNAND回路NA6の入力端に接続される。以下では、NAND回路NA5の出力端とNAND回路NA6の入力端とを接続する配線を配線L2と称する。NAND回路NA6の出力端は、インバータINV6を介して、出力ノード73aに出力される。したがって、内部クロック信号LCLK_OUT1はNAND回路NA6の出力信号の反転信号となる。

【0087】

本実施の形態による周期伸長回路21は、図7に示すように、クロック信号LCLK2_2が供給制御回路20に供給されることがない点で、図5に示した周期伸長回路21と異なっている。これ以外の点では両者は同一であるので、詳しい説明は省略する。

【0088】

以上説明した構成により、まず内部アイドルコマンドIDLEがロウレベルとなっている場合、出力ノード73aの電位はロウレベルに固定される(クロック停止モード)。この場合、内部クロック信号LCLK_OUT1はクロック伝送回路3に供給されない。

【0089】

一方、内部アイドルコマンドIDLEがハイレベルとなっている場合には、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間(アクティブ期間)においては、クロック信号LCLK4_2が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(長周期クロック出力モード)。本実施の形態では、クロック信号LCLK4_2が、内部クロック信号LCLKよりも周期の長い長周期クロック信号に相当する。

【0090】

また、内部リードコマンドREADが活性化されてから内部リードコマンドREADが非活性化するまでの期間(リード期間)においては、内部クロック信号LCLKが、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(通常クロック出力モード)。

【0091】

図8は、本実施の形態によるクロック出力制御回路73に関わる各信号の、長周期クロック出力モードにおける時間変化を示すタイミング図である。同図に示す各信号のうち、内部クロック信号LCLKとクロック信号LCLK4_2については、図6に示したものと同一である。

【0092】

図8に示すように、配線L2の電位はクロック信号LCLK4_2と同一となっており、内部クロック信号LCLK_OUT1にもクロック信号LCLK4_2がそのまま現れている。その結果、本実施の形態による長周期クロック信号は、図6に示した内部クロック信号LCLK_OUT1のようなパルス状の信号ではなく、図8に示すようなデューティー比50:50の信号となる。

【0093】

以上説明したように、本実施の形態による半導体装置10によれば、長周期クロック出力モードでクロック伝送回路3に供給する長周期クロック信号を、デューティー比50:50の信号とすることが可能になる。

【0094】

図9は、本発明の好ましい第2の実施の形態の変形例による半導体装置が備えるクロック出力制御回路73の内部構成を示す回路図である。本変形例では、クロック出力制御回路73から出力される内部クロック信号LCLK_OUT1は第2の実施の形態によるものと同一であるが、供給制御回路20の内部構成が第2の実施の形態によるものと異なっている。そこで以下では、本変形例による供給制御回路20の内部構成について、詳しく説明する。

【0095】

本変形例による供給制御回路20は、図9に示すように、NAND回路NA1,インバータINV1〜INV5、NOR回路NOR1、及びセレクタ回路SEL1を有している。内部クロック信号LCLKと内部アイドルコマンドIDLEとは、NAND回路NA1の入力端に供給される。内部リードコマンドREADは、NOR回路NOR1の入力端に供給される。内部アクティブコマンドACTは、インバータINV5を介して、NOR回路NOR1の入力端に供給される。

【0096】

NAND回路NA1の出力端は、インバータINV1〜INV3をこの順で介して、セレクタ回路SEL1の一方入力端に接続される。セレクタ回路SEL1の他方入力端には、周期伸長回路21からクロック信号LCLK4_2が供給される。

【0097】

セレクタ回路SEL1は、NOR回路NOR1の出力がハイレベルである場合にクロック信号LCLK4_2の反転信号を出力し、ロウレベルである場合にインバータINV3の出力信号の反転信号を出力するよう構成される。セレクタ回路SEL1の出力信号は、インバータINV4を介して、出力ノード73aに出力される。したがって、内部クロック信号LCLK_OUT1はセレクタ回路SEL1の出力信号の反転信号となる。

【0098】

以上説明した構成により、まず内部アイドルコマンドIDLEがロウレベルとなっている場合、この場合には内部アクティブコマンドACT及び内部リードコマンドREADもロウレベルになっているので、セレクタ回路SEL1の出力信号はハイレベルに固定される。したがって、出力ノード73aの電位はロウレベルに固定される(クロック停止モード)。

【0099】

一方、内部アイドルコマンドIDLEがハイレベルとなっている場合には、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間(アクティブ期間)においては、クロック信号LCLK4_2が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(長周期クロック出力モード)。本変形例でも、クロック信号LCLK4_2が、内部クロック信号LCLKよりも周期の長い長周期クロック信号に相当する。

【0100】

また、内部リードコマンドREADが活性化されてから内部リードコマンドREADが非活性化するまでの期間(リード期間)においては、内部クロック信号LCLKが、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(通常クロック出力モード)。

【0101】

つまり、本実施の形態によれば、第2の実施の形態とは異なる内部構成を有する供給制御回路20を用いて、第2の実施の形態と同一の内部クロック信号LCLK_OUT1を得ることが可能になっている。

【0102】

図10は、本発明の好ましい第3の実施の形態による半導体装置が備えるクロック出力制御回路73の内部構成を示す回路図である。本実施の形態による半導体装置も、クロック出力制御回路73の内部構成以外の点では、第1の実施の形態による半導体装置10と同一であるので、以下ではクロック出力制御回路73の内部構成についてのみ説明する。

【0103】

図10に示すように、本実施の形態によるクロック出力制御回路73も、供給制御回路20及び周期伸長回路21を有して構成される。ただし、これらの内部構成は第1の実施の形態で説明したものと異なっており、その結果、長周期クロック信号の波形が第1の実施の形態と異なっている。以下、詳しく説明する。

【0104】

本実施の形態による供給制御回路20は、図10に示すように、NAND回路NA2が4入力で構成され、内部アクティブコマンドACT及びクロック信号LCLK2_2,LCLK4_2の他に、周期伸長回路21が出力するクロック信号LCLK8_2も供給される点で、図3に示した供給制御回路20と異なっている。これ以外の点では両者は同一であるので、詳しい説明は省略する。

【0105】

本実施の形態による周期伸長回路21は、図10に示すように、それぞれP型チャネルMOSトランジスタ及びN型チャネルMOSトランジスタによって構成される2個のトランスファーゲートTRF8−1,TRF8−2と、インバータINV8−1〜INV8−7をさらに有する点で、図5に示した周期伸長回路21と異なっている。また、本実施の形態による周期伸長回路21では、インバータINV4−7の出力端からクロック信号LCLK4_1が取り出される点でも、図5に示した周期伸長回路21と異なっている。以下、これらの相違点を中心に説明する。

【0106】

トランスファーゲートTRF8−1の出力端は、インバータINV8−2の出力端とインバータINV8−3の入力端に接続される。インバータINV8−2の入力端とインバータINV8−3の出力端とはともにインバータINV8−4の入力端に接続され、インバータINV8−4の出力端は、トランスファーゲートTRF8−2の入力端に接続される。トランスファーゲートTRF8−2の出力端は、インバータINV8−5の出力端とインバータINV8−6の入力端に接続される。インバータINV8−5の入力端とインバータINV8−6の出力端とはともにインバータINV8−7の入力端に接続され、インバータINV8−7の出力端は、インバータINV8−1を介して、トランスファーゲートTRF8−1の入力端に接続される。

【0107】

トランスファーゲートTRF8−1のP型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF8−2のN型チャネルMOSトランジスタの制御端子には、クロック信号LCLK4_2が供給される。一方、トランスファーゲートTRF8−1のN型チャネルMOSトランジスタの制御端子、及びトランスファーゲートTRF8−2のP型チャネルMOSトランジスタの制御端子には、クロック信号LCLK4_1が供給される。インバータINV8−1の出力端からはクロック信号LCLK8_2が取り出される。クロック信号LCLK8_2は、上述したように、供給制御回路20内のNAND回路NA2に供給される。

【0108】

以上説明した構成により、まず内部アイドルコマンドIDLEがロウレベルとなっている場合、出力ノード73aの電位はロウレベルに固定される(クロック停止モード)。

【0109】

一方、内部アイドルコマンドIDLEがハイレベルとなっている場合には、内部アクティブコマンドACTが活性化してから内部リードコマンドREADが活性化するまでの期間(アクティブ期間)においては、クロック信号LCLK2_2、クロック信号LCLK4_2、クロック信号LCLK8_2、及び内部クロック信号LCLKの論理積信号が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(長周期クロック出力モード)。本実施の形態では、この論理積信号が、内部クロック信号LCLKよりも周期の長い長周期クロック信号に相当する。

【0110】

また、内部リードコマンドREADが活性化されてから内部リードコマンドREADが非活性化するまでの期間(リード期間)においては、内部クロック信号LCLK(第2のクロック信号)が、内部クロック信号LCLK_OUT1として出力ノード73aに出力される(通常クロック出力モード)。

【0111】

クロック信号LCLK8_2は、内部クロック信号LCLKの8倍の周期を有する周期信号である。したがって、本実施の形態による長周期クロック信号は、内部クロック信号LCLKの8倍の周期を有する周期信号となる。

【0112】

以上説明したように、本実施の形態による半導体装置10によれば、アクティブ期間内にクロック伝送回路3に供給する長周期クロック信号の周期を、内部クロック信号LCLKの周期の8倍とすることができる。したがって、クロック伝送回路3の電流消費量を、より抑えることが可能になる。

【0113】

以上、本発明の好ましい実施の形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【符号の説明】

【0114】

3 クロック伝送回路

10 半導体装置

11 クロック端子

12 コマンド端子

13 アドレス端子

14 データ入出力端子

15 データストローブ端子

16 入出力回路

16a,16b 電源端子

20 供給制御回路

21 周期伸長回路

31 コマンドバッファ

32 コマンドデコーダ

40 クロックバッファ

41 アドレスバッファ

51 ロウ系制御回路

52 カラム系制御回路

53 リフレッシュ回路

60 メモリセルアレイ

61 センス回路

62 リードライトアンプ

64 入出力回路

65 DQS入出力回路

70 DLL回路

71 DLLリフレッシュ制御回路

72 レプリカ回路

73,74 クロック出力制御回路

73a 出力ノード

75 バッファ回路

76 クロックツリー

77 ROM

80〜82 内部電圧発生回路

90 OR回路

ACT アクティブコマンド,内部アクティブコマンド

IDLE 内部アイドルコマンド

INV1〜INV6,INV2−1〜INV2−7,INV4−1〜INV4−7,INV8−1〜INV8−7 インバータ

L1,L2 配線

LCLK,LCLK_OUT1,LCLK_OUT2 内部クロック信号

LCLK2_1,LCLK2−2,LCLK4−1,LCLK4−2,LCLK8−2 クロック信号

NA1〜NA6 NAND回路

NOR1 NOR回路

READ リードコマンド,内部リードコマンド

S1 起動信号

SEL1 セレクタ回路

TRF2−1,TRF2−2,TRF4−1,TRF4−2,TRF8−1,TRF8−2 トランスファーゲート

VDD,VSS 外部電源電圧

VPERD,VPERI2,VPERI 内部電圧

【特許請求の範囲】

【請求項1】

アクティブ期間内に内部クロック信号よりも周期の長い長周期クロック信号を供給し、前記アクティブ期間に続くリード期間内に前記内部クロック信号を供給するクロック出力制御回路と、

前記クロック出力制御回路から出力された前記内部クロック信号及び前記長周期クロック信号を伝送するクロック伝送回路と、

外部データ端子と、

前記クロック伝送回路によって伝送された前記内部クロック信号に同期して、前記外部データ端子にリードデータを出力する出力回路と

を備えることを特徴とする半導体装置。

【請求項2】

前記出力回路は、前記アクティブ期間内には前記リードデータを出力しない

ことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記クロック出力制御回路は、パワーダウン期間内に、前記内部クロック信号及び前記長周期クロック信号の供給を行わない

ことを特徴とする請求項1又は2のいずれか一項に記載の半導体装置。

【請求項4】

前記クロック伝送回路は、内部電圧を動作電源として動作し、

前記半導体装置は、前記内部電圧を生成し、前記クロック伝送回路に供給する内部電圧生成回路を備え、

前記内部電圧の電位は、前記アクティブ期間内に第1の電位から第2の電位に降下し、前記リード期間内に前記第2の電位から第3の電位に降下する

ことを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

前記内部クロック信号を生成して前記クロック出力制御回路に供給するDLL回路を備え、

前記クロック出力制御回路は、前記DLL回路から供給された前記内部クロック信号の周期を延ばすことによって、前記長周期クロック信号を生成する

ことを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

前記クロック出力制御回路は、

前記DLL回路から供給された前記内部クロック信号の周期を延ばす周期伸長回路と、

前記周期伸長回路により得られる信号から前記長周期クロック信号を生成し、アクティブコマンドの活性化に応じて該長周期クロック信号の供給を開始するとともに、リードコマンドの活性化に応じて前記内部クロック信号の供給を開始する供給制御回路とを有する

ことを特徴とする請求項5に記載の半導体装置。

【請求項1】

アクティブ期間内に内部クロック信号よりも周期の長い長周期クロック信号を供給し、前記アクティブ期間に続くリード期間内に前記内部クロック信号を供給するクロック出力制御回路と、

前記クロック出力制御回路から出力された前記内部クロック信号及び前記長周期クロック信号を伝送するクロック伝送回路と、

外部データ端子と、

前記クロック伝送回路によって伝送された前記内部クロック信号に同期して、前記外部データ端子にリードデータを出力する出力回路と

を備えることを特徴とする半導体装置。

【請求項2】

前記出力回路は、前記アクティブ期間内には前記リードデータを出力しない

ことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記クロック出力制御回路は、パワーダウン期間内に、前記内部クロック信号及び前記長周期クロック信号の供給を行わない

ことを特徴とする請求項1又は2のいずれか一項に記載の半導体装置。

【請求項4】

前記クロック伝送回路は、内部電圧を動作電源として動作し、

前記半導体装置は、前記内部電圧を生成し、前記クロック伝送回路に供給する内部電圧生成回路を備え、

前記内部電圧の電位は、前記アクティブ期間内に第1の電位から第2の電位に降下し、前記リード期間内に前記第2の電位から第3の電位に降下する

ことを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

前記内部クロック信号を生成して前記クロック出力制御回路に供給するDLL回路を備え、

前記クロック出力制御回路は、前記DLL回路から供給された前記内部クロック信号の周期を延ばすことによって、前記長周期クロック信号を生成する

ことを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

前記クロック出力制御回路は、

前記DLL回路から供給された前記内部クロック信号の周期を延ばす周期伸長回路と、

前記周期伸長回路により得られる信号から前記長周期クロック信号を生成し、アクティブコマンドの活性化に応じて該長周期クロック信号の供給を開始するとともに、リードコマンドの活性化に応じて前記内部クロック信号の供給を開始する供給制御回路とを有する

ことを特徴とする請求項5に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−129630(P2012−129630A)

【公開日】平成24年7月5日(2012.7.5)

【国際特許分類】

【出願番号】特願2010−277264(P2010−277264)

【出願日】平成22年12月13日(2010.12.13)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成24年7月5日(2012.7.5)

【国際特許分類】

【出願日】平成22年12月13日(2010.12.13)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]