半導体装置

【課題】半導体装置の寄生容量成分を好適に調整する。

【解決手段】半導体装置10は、複数個のエミッタ領域20を備える。半導体層の表面から所定の深さまでの領域に形成されているボディ領域12を備える。ボディ領域12の下部に形成されているドリフト領域4を備える。ドリフト領域4の下部に形成されているコレクタ領域3を備える。各エミッタ領域20の表面からボディ領域12を貫通して伸びている第1トレンチ31を備える。第1トレンチ31の内面を覆っているゲート絶縁膜18を備える。第1トレンチ31内に収容されているゲート電極8を備える。隣接している第1トレンチ31間に形成され、ボディ領域12を貫通して伸びている第2トレンチ32を備える。第2トレンチ32の内面を覆っているトレンチ絶縁膜33を備える。第2トレンチ32内に収容されている導電層35を備える。導電層35がゲート電極8に電気的に接続されている。

【解決手段】半導体装置10は、複数個のエミッタ領域20を備える。半導体層の表面から所定の深さまでの領域に形成されているボディ領域12を備える。ボディ領域12の下部に形成されているドリフト領域4を備える。ドリフト領域4の下部に形成されているコレクタ領域3を備える。各エミッタ領域20の表面からボディ領域12を貫通して伸びている第1トレンチ31を備える。第1トレンチ31の内面を覆っているゲート絶縁膜18を備える。第1トレンチ31内に収容されているゲート電極8を備える。隣接している第1トレンチ31間に形成され、ボディ領域12を貫通して伸びている第2トレンチ32を備える。第2トレンチ32の内面を覆っているトレンチ絶縁膜33を備える。第2トレンチ32内に収容されている導電層35を備える。導電層35がゲート電極8に電気的に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本願は、半導体装置の寄生容量成分を好適に調整することが可能な技術に関する。

【背景技術】

【0002】

第1導電型(例えばn型)のドリフト領域の表面に、第2導電型(例えばp型)のボディ領域が積層されている半導体基板に、半導体装置として機能する半導体構造(MOS、IGBT等)を作り込む技術が発達している。このような半導体装置では、ゲート周辺に寄生成分として形成される容量が、スイッチング特性を決定する重要なパラメータとなる。寄生容量成分は、ゲート周辺における、ゲート電極、絶縁膜、ドリフト領域等の構成によって形成される。例えば、低損失で高速なスイッチング動作を実現するためには、ゲート−コレクタ(ドレイン)間の帰還容量を低減させる必要がある。

【0003】

特許文献1には、厚い酸化膜をトレンチゲートの底部に備えている半導体装置が開示されている。厚い絶縁層によって、トレンチゲートとドレイン領域はトレンチの底部において隔てられる。これにより、帰還容量を低減させることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特表2004−538648号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

特許文献1の技術では、トレンチゲート底部の酸化膜を厚くすることにより、寄生容量成分の調整を行っている。このため、寄生容量成分を小さくするためには、トレンチゲート底部の酸化膜を厚くしなければならないが、トレンチゲート底部の酸化膜を厚くしすぎると、チャネルが形成されなくなり、半導体装置の主要特性(スイッチ特性や導通性能など)が得られなくなる。したがって、半導体装置の主要特性を確保できる範囲内でしか、寄生容量成分を調整することができず、寄生容量の調整機能を十分に得ることができないという問題があった。

【0006】

本願の技術は、上記の問題を解決するために創案された。すなわち、本願は、半導体装置の主要特性に影響を与えることなく、半導体装置の寄生容量成分を好適に調整することが可能な技術を提供する。

【課題を解決するための手段】

【0007】

本願に開示される半導体装置は、半導体層の表面の一部に臨んで形成されている第1導電型の複数個の第1半導体領域と、第1半導体領域を取り囲んでいるとともに、半導体層の表面から所定の深さまでの領域に形成されている第2導電型のボディ領域と、ボディ領域の下部に形成されており、ボディ領域によって第1半導体領域から分離されている第1導電型のドリフト領域と、ドリフト領域の下部に形成されている第2半導体領域と、各第1半導体領域の表面からボディ領域を貫通して伸びており、その底面がドリフト領域に突出している複数の第1トレンチと、各第1トレンチの内面を覆っているゲート絶縁層と、ゲート絶縁層で取り囲まれた状態で各第1トレンチ内に収容されている第1トレンチゲート電極と、隣接している第1トレンチ間に形成されているとともに、ボディ領域を貫通して伸びており、その底面がドリフト領域に突出している複数の第2トレンチと、各第2トレンチの内面を覆っているトレンチ絶縁層と、トレンチ絶縁層で取り囲まれた状態で各第2トレンチ内に収容されている複数の導電層と、を備える。また、複数の導電層のうち少なくとも1つが、第1トレンチゲート電極に電気的に接続可能とされるか、または、第1半導体領域に選択的に電気接続可能とされている。

【0008】

第1トレンチは、トレンチゲートとして動作する。第2トレンチは、導電層が第1トレンチゲート電極に電気的に接続されている場合には、入力容量(ゲート−第1半導体領域間の容量成分)を増加させるためのキャパシタとして機能する。また、第2トレンチは、導電層が第1半導体領域に電気的に接続されている場合には、出力容量(第1半導体領域−第2半導体領域の容量成分)を増加させるためのキャパシタとして機能する。第1半導体領域の例としてはエミッタ領域又はソース領域が挙げられる。また、第2半導体領域の例としてはコレクタ領域又はドレイン領域が挙げられる。

【0009】

そして、入力容量や出力容量を増加させるために、第1トレンチの構造を変える必要がないため、半導体装置の主要特性(スイッチ特性や導通性能など)に影響を与えることを防止できる。以上より、半導体装置の主要特性に影響を与えずに、容量の調整機能を十分に得ることができる。

【0010】

また、本願に開示される半導体装置では、トレンチ絶縁層で取り囲まれた状態で第2トレンチ内の底部には底部絶縁層が形成されており、底部絶縁層の上面は、ボディ領域とドリフト領域との界面よりもボディ領域側に位置しており、底部絶縁層の上層に導電層が形成されており、導電層が第1トレンチゲート電極に電気的に接続されていてもよい。

【0011】

第2トレンチ内の底部に形成された底部絶縁層の上面が、ボディ領域とドリフト領域との界面よりもボディ領域側に位置していることにより、半導体装置のターンオン時において、チャネルが導通しない。よって、第2トレンチでは、電気的動作が行われない。これにより、第2トレンチを、入力容量(ゲート−第1半導体領域間の容量成分)を増加させるためのキャパシタとして好適に機能させることができる。

【0012】

トレンチゲートに別途外付でキャパシタ素子を接続する場合には、配線長が長くなる。すると、配線の寄生インダクタンスが大きくなることで、キャパシタ素子と寄生インダクタンスによるLC共振を無視できなくなってしまう場合がある。一方、本願では、トレンチゲートである第1トレンチの直近に、キャパシタである第2トレンチが位置しているため、トレンチゲートにキャパシタを接続する際の配線長を短くすることができる。よって、配線の寄生インダクタンスを小さくすることができるため、共振の影響を小さくすることができる。

【0013】

また、半導体装置は高温になる場合がある。トレンチゲートに別途外付でキャパシタ素子を接続する場合には、キャパシタ素子の高温信頼性を考慮する必要がある。一方本願では、第2トレンチを、入力容量(ゲート−第1半導体領域間の容量成分)を増加させるためのキャパシタとして機能させる。よって、キャパシタの高温信頼性を、半導体装置と同等にすることができる。

【0014】

また、本願に開示される半導体装置では、導電層が第1トレンチゲート電極に接続されている場合における、ゲート電圧の供給源から第1トレンチゲート電極までの経路の抵抗成分である第1のゲート抵抗成分が、導電層が第1トレンチゲート電極に接続されていない場合における、ゲート電圧の供給源から第1トレンチゲート電極までの経路の抵抗成分である第2のゲート抵抗成分よりも小さくされていてもよい。また、第1トレンチの容量成分と第2トレンチの容量成分との和と第1のゲート抵抗成分との積算値が、第1トレンチの容量成分と第2のゲート抵抗成分との積算値以下となるように、第1のゲート抵抗成分が設定されていてもよい。

【0015】

第1トレンチの容量成分は、第1トレンチゲート電極、ゲート絶縁層および第1トレンチの底面と第2半導体領域との間の領域の構成によって形成される容量である。第2トレンチの容量成分は、導電層、トレンチ絶縁層および第2トレンチの底面と第2半導体領域との間の領域の構成によって形成される容量である。半導体装置のターンオフ時の動作を説明する。ゲート抵抗成分を小さくすると、ターンオフ時における素子電圧の立ち上がり時間が短くなるため、スイッチング損失を低下させることができる。しかし同時に、素子電流の減少率が大きくなるため、サージ電圧が増大するというトレードオフの関係が存在している。本願では、第1トレンチの容量成分に第2トレンチの容量成分を付加することによって、容量成分の総和値を増加させることができる。これにより、素子電圧の立ち上がり時間を短い状態に維持したまま、素子電流の減少率のみを小さくすることができる。よって、サージ電圧の増大を抑制しながら、ターンオフ損失を減少させることができる。以上より、スイッチング損失の低下とサージ電圧の抑制とを両立することができる。

【0016】

また、本願に開示される半導体装置では、第2トレンチは、ボディ領域が半導体層の表面に露出している領域に複数形成されており、複数の第2トレンチの各々内に収容されている導電層の少なくとも1つが、第1半導体領域と選択的に電気接続されていてもよい。

【0017】

第2トレンチは、ボディ領域が半導体層の表面に露出している領域に形成されているため、第2トレンチの周囲には第1半導体領域が存在しない。よって、第2トレンチでは、電気的動作が行われない。これにより、第2トレンチを、出力容量(第1半導体領域−第2半導体領域間の容量成分)を増加させるためのキャパシタとして好適に機能させることができる。

【0018】

半導体装置を配線を用いて各種の装置に搭載する場合には、半導体装置の出力容量と配線インダクタンスとによって、共振周波数が決定される。そして、共振周波数が搭載装置にとって不適切な場合には、共振が発生する場合がある。本願では、第2トレンチゲート内の導電層の少なくとも1つが第1半導体領域と選択的に電気接続可能とされている。第1半導体領域に接続される第2トレンチゲート内の導電層の数を変えることに応じて、出力容量を変化させることができる。これにより、共振周波数を意図的にシフトすることが可能となる。よって、共振周波数を共振が発生しない値に設定することが可能となるため、共振の発生を防止できる。これにより、共振によって半導体装置の寿命が短くなってしまう事態等を防止できる。

【0019】

また、本願では、トレンチゲートである第1トレンチの直近に、キャパシタである第2トレンチが位置しているため、トレンチゲートにキャパシタを接続する際の配線長を短くすることができる。よって、配線の寄生インダクタンスを小さくすることができるため、共振の影響を小さくすることができる。また本願では、第2トレンチを、出力容量(第2半導体領域−第1半導体領域間の容量成分)を増加させるためのキャパシタとして機能させる。よって、キャパシタの高温信頼性を、半導体装置と同等にすることができる。

【0020】

また、本願に開示される半導体装置では、第1トレンチおよび第2トレンチの上層には、上部絶縁層が形成されており、上部絶縁層および第1半導体領域の上層には、上部電極が形成されており、複数の第2トレンチの各々内に収容されている導電層に接続されているパッド部をさらに備え、パッド部と上部電極とが電気的に接続可能とされていてもよい。

【0021】

パッド部と上部電極とを電気的に接続する方法の一例としては、ワイヤで両者を接続する方法が挙げられる。これにより、キャパシタとして機能する第2トレンチを、選択的に第1半導体領域に接続することが可能となる。よって、出力容量を適切に変化させ、共振周波数をシフトさせることが可能となる。

【図面の簡単な説明】

【0022】

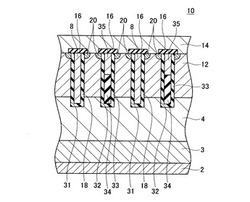

【図1】実施例1の半導体装置の断面図である。

【図2】実施例1の半導体装置の動作を示すグラフである。

【図3】従来構造の半導体装置の断面図である。

【図4】実施例2の半導体装置の平面図である。

【図5】実施例2の半導体装置の断面図である。

【図6】実施例2の半導体装置の等価回路である。

【図7】フルブリッジ回路を示す図である。

【図8】共振部の等価回路を示す図である。

【図9】共振部の等価回路を示す図である。

【図10】共振部の発振動作を示すグラフである。

【発明を実施するための形態】

【0023】

以下に説明する実施例の主要な特徴を列記しておく。

(特徴1)半導体基板はSiである。

(特徴2)セルエリアに形成されている半導体構造はIGBT構造である。

(特徴3)セルエリアに形成されている半導体構造はMOS構造である。

【実施例】

【0024】

(実施例1)

本発明に係る半導体素子駆動回路の基本原理について、半導体素子としてIGBT(絶縁ゲートバイポーラトランジスタ)素子を例にとり説明する。もちろん、IGBTに限定されるものではなく、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)でもよい。

【0025】

図1に示すように、実施例1の半導体装置10の裏面には、コレクタ電極2が形成されている。コレクタ電極2の表面に、p+型(第2導電型)の第2半導体領域(コレクタ領域)3が形成されている。コレクタ領域3の表面に、n−型のドリフト領域4が形成されている。ドリフト領域4の表面に、p型(第2導電型)のボディ領域12が形成されている。ボディ領域12の表面に、複数個のn+型(第1導電型)の第1半導体領域(エミッタ領域)20が形成されている。ボディ領域12は、エミッタ領域20を取り囲んでいる。各々のエミッタ領域20は、ボディ領域12によってドリフト領域4から分離されている。

【0026】

各エミッタ領域20の表面からボディ領域12を貫通して伸びている、第1トレンチ31が形成されている。第1トレンチ31の底面は、ドリフト領域4に突出している。第1トレンチ31の内壁は、ゲート絶縁膜18で被覆されている。第1トレンチ31内には、ゲート絶縁膜18で取り囲まれた状態で、ゲート電極8が収容されている。ゲート電極8は、ドリフト領域4とエミッタ領域20を分離している範囲のボディ領域12に、ゲート絶縁膜18を介して対向している。

【0027】

また、隣接している第1トレンチ31の間に、第2トレンチ32が形成されている。第2トレンチ32は、エミッタ領域20の表面からボディ領域12を貫通して伸びており、その底面がドリフト領域4に突出している。第2トレンチの内壁は、トレンチ絶縁膜33で被覆されている。トレンチ絶縁膜33で取り囲まれた状態で、第2トレンチ32内の底部には、絶縁層34が配置されている。絶縁層34の一例としては、n型多結晶シリコン(n-polySi)が挙げられる。絶縁層34の上面は、ボディ領域12とドリフト領域4との界面よりもボディ領域12側に位置している。絶縁層34の上層には、トレンチ絶縁膜33で取り囲まれた状態で、導電層35が収容されている。

【0028】

ボディ領域12とエミッタ領域20の表面に、エミッタ電極14が形成されている。ゲート電極8および導電層35は、絶縁膜16によって、エミッタ電極14に対して絶縁されている。絶縁膜16には、図1の奥行き方向のいずれかの断面で、ゲート電極8および導電層35の表面を露出させるコンタクトホール(不図示)が形成されている。これらのコンタクトホールを介して、導電層35とゲート電極8とが電気的に接続されている。また、導電層35とゲート電極8は、コンタクトホールを介して、ゲート電圧を供給するドライブ回路(不図示)に接続されている。

【0029】

第1トレンチ31の機能について説明する。半導体装置10では、ドライブ回路から出力されるゲート電圧(例えば15Vと0V)が、ドライブ回路からゲート電極8までの経路を介して、ゲート電極8に供給される。これにより、第1トレンチ31の各々はトレンチゲートとして動作し、半導体装置10のターンオン・ターンオフの制御が行われる。第1トレンチ31は、第1トレンチ容量成分を有している。第1トレンチ容量成分は、ゲート電極8、ゲート絶縁膜18、第1トレンチ31の底面とコレクタ領域3との間の領域、の構成によって形成される容量成分である。

【0030】

第2トレンチ32の機能について説明する。第2トレンチ32内の底部に形成された絶縁層34の上面が、ボディ領域12とドリフト領域4との界面よりもボディ領域12側に位置していることにより、半導体装置10のターンオン時において、チャネルが導通しない。よって、第2トレンチ32では、電気的動作が行われない。このようにトレンチ底部を電気的に動作させない構造にすることで、第2トレンチ32を、キャパシタとして好適に機能させることができる。第2トレンチ32がキャパシタとして機能する際の容量成分は、導電層35、絶縁層34、トレンチ絶縁膜33、第2トレンチ32の底面とコレクタ領域3との間の領域、の構成によって形成される。

【0031】

そして、第2トレンチ32の導電層35は、ゲート電極8に電気的に接続されている。これにより、第2トレンチ32を、入力容量(ゲート電極8−エミッタ領域20間の容量成分)を増加させるためのキャパシタとして機能させることができる。

【0032】

また、本願の半導体装置10と対比する対象として、従来構造の半導体装置100を、図3を用いて説明する。半導体装置100は、ダミートレンチとして機能する第2トレンチ132を備えた、ダミートレンチ型のIGBTである。第2トレンチ132は、ボディ領域12の表面からボディ領域12を貫通して伸びており、その底面がドリフト領域4に突出している。また、第2トレンチ132の内部の全領域に、導電層135が収容されている。また第2トレンチ132の上部には、導電層135を絶縁する絶縁膜16が形成されていないため、導電層135がエミッタ電極14に電気的に接続されている。なお、その他の構造は、図1の半導体装置10と同様であるため、ここでは詳細な説明を省略する。

【0033】

ダミートレンチの機能を説明する。オン抵抗を低減するために、トレンチゲート(第1トレンチ31)同士の間の距離をある程度大きくすることが望ましい場合がある。しかし、第1トレンチ31のトレンチ間距離を大きくすると、第1トレンチ31の間の領域において、ボディ領域12とドリフト領域4の間のpn接合に、大きな電界が加わることがある。そこで、当該領域にダミートレンチ(第2トレンチ132)を形成することで、pn空乏層を均等に拡げ、電界集中を緩和することができる。

【0034】

また、ゲート抵抗成分について説明する。ゲート抵抗成分は、ゲート電圧を供給するドライブ回路(不図示)から、ゲート電極8までの経路の抵抗成分である。なお、ゲート抵抗成分は、抵抗器を経路上に挿入することによって、任意の値に調整することが可能である。ここで、従来構造の半導体装置100(図3)でのゲート抵抗成分を、ゲート抵抗成分Rg1とする。また、本願の半導体装置10(図1)でのゲート抵抗成分を、ゲート抵抗成分Rg2とする。半導体装置10のゲート抵抗成分Rg2は、半導体装置100のゲート抵抗成分Rg1よりも小さくされている。

【0035】

また、従来の半導体装置100において、全ての第1トレンチ31の合成容量成分と、ゲート抵抗成分Rg1との積算値を、第1積算値とする。一方、本願の半導体装置10において、全ての第1トレンチ31の合成容量成分と全ての第2トレンチ32の合成容量成分との和と、ゲート抵抗成分Rg2との積算値を、第2積算値とする。そして、ゲート抵抗成分Rg2の値は、第2積算値が第1積算値以下となるように設定されている。

【0036】

半導体装置10の動作について説明する。例として、従来の半導体装置100(図3)の動作と、本願の半導体装置10(図1)の動作を比較して説明する。ターンオフ動作について、図2を用いて説明する。図2は、時刻t1において、ターンオフ動作が開始された場合の動作を示す図である。図2(A)はゲート電圧Vgの時間変化を示すグラフ、図2(B)はコレクタ電流Icの時間変化を示すグラフ、図2(C)はコレクタ電圧Vcの時間変化を示すグラフ、図2(D)はスイッチング損失の時間変化を示すグラフ、である。なお、図2において、実線が本願の半導体装置10の場合の特性であり、破線が従来構造の半導体装置100の場合の特性である。

【0037】

従来の半導体装置100(図2、点線)のスイッチング損失を説明する。スイッチング損失は、コレクタ電流Icとコレクタ電圧Vcで決定され、図2(D)に示す領域R1の斜線部の面積で表される。スイッチング損失を小さくするためには、コレクタ電圧Vcの立ち上がり時間P1(図2(C))を短くするか、コレクタ電圧Vcの最大値を小さくすることが必要である。

【0038】

ここで、ゲート抵抗成分を小さくすると、ターンオフ時におけるコレクタ電圧Vcの立ち上がり時間が短くなる。しかし同時に、コレクタ電流Icの減少率(di/dt)(図2(B)、領域R3)が大きくなる。また、ターンオフ時にサージ電圧(図2(C)、領域R4)が発生するが、サージ電圧はdi/dt×Lp(Lp:寄生成分のインダクタンス)で与えられる。よって、コレクタ電圧Vcの立ち上がり時間を短くすると、サージ電圧が増大するというトレードオフの関係が存在している。すると、単にゲート抵抗成分を小さくするだけでは、サージ電圧の増大によってコレクタ電圧Vcの最大値が増加してしまうため、スイッチング損失を小さくできない。

【0039】

本願の半導体装置10(図2、実線)のスイッチング損失を説明する。前述したように、ゲート抵抗成分を小さくすると、ターンオフ時におけるコレクタ電圧Vcの立ち上がり時間が短くなる。また、半導体装置10の入力容量(ゲート電極8−エミッタ領域20間の容量成分の合計値)を増加させると、コレクタ電圧Vcの立ち上がり時間を一定値に維持したまま、コレクタ電流Icの減少率のみを小さくすることができ、その結果サージ電圧を小さくすることができる。そこで、本願の半導体装置10では、ゲート抵抗成分をRg1からRg2へ小さくしている。また、ゲート抵抗成分Rg1で駆動した場合の電流の減少率(領域R3)と、ゲート抵抗成分Rg2で駆動した場合の電流の減少率(領域R5)とが同じになるように、第2トレンチ32の容量成分(複数の第2トレンチ32の容量成分の合計値)を設定している。そして、入力容量に第2トレンチ32の容量成分を付加することで、入力容量を増加させている。これにより、ゲート抵抗成分Rg1のサージ電圧(領域R4)と同じサージ電圧(領域R6)でありながら、コレクタ電圧Vcの立ち上がり時間を時間P1からP2へより短くすることができる。そして、本願の半導体装置10でのスイッチング損失は、図2(D)に示す領域R2の斜線部の面積で表される。領域R1に比して領域R2の面積が小さくなっていることから、従来の半導体装置100に比して、本願の半導体装置10では、ターンオフ損失が低下していることが分かる。以上より、スイッチング損失の低下とサージ電圧の抑制とを両立することができる。

【0040】

半導体装置10の製造方法について説明する。なお、本願の半導体装置10(図1)は、従来のダミートレンチ型の半導体装置100(図3)の構造を一部変更したものである。まず、n型の不純物を含む半導体基板を用意する。半導体基板の表面にp型の不純物をイオン注入して、ボディ領域12を形成する。半導体基板の裏面にp型の不純物をイオン注入して、コレクタ領域3を形成する。次に、ボディ領域12の表面の所定部分にマスク層を形成した後、図1に示しているエミッタ領域20を形成する。

【0041】

表面に開口を有するマスク層を形成し、表面からエミッタ領域20とボディ領域12をエッチングして、ドリフト領域4に達する第1トレンチ31および第2トレンチ32を形成する。エッチングにはRIE(Reactive Ion Etching)等のドライエッチングを利用することができる。次に、第1トレンチ31の内壁にゲート絶縁膜18を形成するとともに、第2トレンチ32の内壁にトレンチ絶縁膜33を形成する。ゲート絶縁膜18およびトレンチ絶縁膜33は、熱酸化により、同時に形成することができる。そして、第2トレンチ32の底部にのみ、選択的に絶縁層34(n−polySi)を埋め込む。その後、第1トレンチ31および第2トレンチ32内に、ポリシリコン等の導電層を同時に充填する。これにより、ゲート電極8および導電層35を同時に形成することができる。次に、絶縁膜16を形成した後に、ゲート電極8と導電層35とをゲート配線に電気的に接続すると共に、ボディ領域12とエミッタ領域20と絶縁膜16の表面にエミッタ電極14を形成する。なお、導電層35をゲート配線に接続する工程は、ゲート電極8をゲート配線に接続する工程において同時に行うことができる。次いで、コレクタ領域3の裏面にコレクタ電極2を形成する。上記の工程を経て、図1に示している半導体装置10を得ることができる。

【0042】

上述した本願の半導体装置10の製造フローでは、従来の半導体装置100の製造フローに対して、絶縁層34を埋め込む工程を追加するだけでよい。よって、従来の半導体装置100の製造フローを流用することができるため、容易に半導体装置10を製造することが可能である。

【0043】

半導体装置10の効果について説明する。半導体装置10の入力容量を増加させるために、第2トレンチ32を用いることで、第1トレンチ31の構造を変える必要がない。よって、半導体装置10の主要特性(スイッチ特性や導通性能など)に影響を与えることなく、入力容量の調整機能を十分に得ることができる。

【0044】

また、入力容量を増加させる場合に、第1トレンチ31に別途外付でキャパシタ素子を接続する場合には、配線長が長くなる。すると、配線の寄生インダクタンスが大きくなることで、キャパシタ素子と寄生インダクタンスによるLC共振を無視できなくなってしまう場合がある。一方、本願の半導体装置10では、第1トレンチ31の直近に、キャパシタとして機能する第2トレンチ32が位置しているため、第1トレンチ31にキャパシタを接続する際の配線長を短くすることができる。よって、配線の寄生インダクタンスを小さくすることができるため、共振の影響を小さくすることができる。

【0045】

また、半導体装置は高温になる場合があるため、第1トレンチ31に別途外付でキャパシタ素子を接続する場合には、キャパシタ素子の高温信頼性を考慮する必要がある。本願の半導体装置10では、半導体装置10の内部に形成されている第2トレンチ32を、キャパシタとして機能させている。よって、キャパシタの高温信頼性を半導体装置10と同等にすることができ、キャパシタの高温信頼性を確保することができる。

【0046】

(実施例2)

図6に、実施例2の半導体装置210の等価回路を示す。半導体装置210は、出力容量成分C0、容量成分C1ないしC3、パッド251ないし253、エミッタ電極14、を備える。出力容量成分C0の一端と、容量成分C1ないしC3の一端は、コレクタに共通接続されている。出力容量成分C0の他端は、エミッタに接続されている。容量成分C1ないしC3の他端は、パッド251ないし253の各々に接続されている。またエミッタ電極14が、エミッタに接続されている。そして、エミッタ電極14と、パッド251ないし253とは、ワイヤ290等を用いることによって互いに接続可能とされている。

【0047】

半導体装置210の適用形態について説明する。例として、図7に示す、フルブリッジ回路300に、本願の半導体装置210を使用する場合を説明する。また、共振部301において、並列アーム間の共振ループを想定した場合を説明する。この場合において、半導体装置210(図6)のパッド251ないし253の何れもがエミッタ電極14に接続されていない場合には、共振部301の等価回路は、図8に示す等価回路310となる。等価回路310の共振周波数f1(Hz)は、半導体装置210の出力容量と配線インダクタンスとによって決定され、下式で表される。

f1=1/2π×(C0×L1)1/2・・・式(1)

ここで、L1は配線インダクタンスである。またC0は、半導体装置210の出力容量成分である。

【0048】

そして、共振周波数f1がフルブリッジ回路300にとって不適切な場合には、フルブリッジ回路300の実駆動時において、共振部301が発振してしまう場合がある。共振部301の発振の例を図10に示す。図10は、時刻t11においてターンオン動作が開始された場合における、発振動作のイメージ図である。図10(A)は、スイッチングアームにおけるゲート電圧Vgの時間変化を示すグラフであり、図10(B)は、スイッチングアームにおけるコレクタ電圧Vcの時間変化を示すグラフである。図10(C)は、還流アームにおけるダイオード電圧Vdの時間変化を示すグラフであり、図10(D)は、還流アームにおけるダイオード電流Idの時間変化を示すグラフである。図10に示すように、発振が発生すると、ゲート電圧Vgやコレクタ電圧Vcの時間変化が大きくなるため、半導体装置210が故障したり、素子寿命が短くなるなどの問題が発生する。

【0049】

そこで、発振防止のために、等価回路310の共振周波数を、フルブリッジ回路300の実駆動時に発振が発生してしまう周波数からシフトさせる必要が出てくる場合がある。この場合、図6において、パッド251ないし253の少なくとも1つを、ワイヤ等でエミッタ電極14に接続すればよい。例として、図4および図6に示すように、ワイヤ290を用いてパッド251をエミッタ電極14に接続する場合を説明する。

【0050】

この場合の共振部301の等価回路は、図9に示す等価回路320となる。出力容量成分C0に対して容量成分C1が並列に接続されるため、出力容量成分の値を増加させることができる。そして、等価回路320の共振周波数f2(Hz)は、下式で表される。

f2=1/2π×((C0+C1)×L1)1/2・・・式(2)

式(1)および式(2)より、容量成分C1を付加することによって、共振周波数を大きくするようにシフトできることが分かる。

【0051】

そして、パッド251ないし253のうち、エミッタ電極14と接続するパッドの数を増やすほど、容量出力容量を増加させることができる。よって、共振周波数をより大きい側にシフトできることが分かる。なお、エミッタ電極14と接続するパッドの数は、フルブリッジ回路300を実動作させながらチューニングしていくことで決定してもよい。

【0052】

次に、図6で説明した半導体装置210の等価回路を実現するための、具体的な構成について説明する。図4に、半導体装置210の平面図を模式的に示す。図5に、図4のV−V線における断面図を模式的に示す。図4に示すように、半導体装置210は、外周204を有する半導体基板202を利用して製造されている。半導体基板202は、トランジスタ動作をする半導体構造が作り込まれているセルエリア271〜273と、そのセルエリア271〜273を取り囲む終端エリア207に区分されている。セルエリア271〜273の内部には、第1トレンチ231および第2トレンチ232が、図4の左右方向に伸びるように多数形成されている。また、セルエリア271〜273の領域内の表面全体には、エミッタ電極14として機能するアルミニウムの金属層(不図示)が形成されている。なお、セルエリアの数は3つに限られず、任意の数に設定することが可能である。

【0053】

半導体装置210には、パッド250〜253が備えられている。パッド250から引き出されたゲート配線280は、セルエリア271〜273の右側側面に配置されている。ゲート配線280は、第1トレンチ231の各々に接続されている。またパッド250は、ゲート電圧を供給するドライブ回路(不図示)に接続される。

【0054】

パッド251から引き出された配線281は、セルエリア271の左側側面に配置されている。配線281は、セルエリア271内に位置する第2トレンチ232の導電層235に接続されている。また、配線282および283の構造は、配線281と同様であるため、ここでは説明を省略する。ゲート配線280、配線281〜283は、互いに分離して引き回されている。

【0055】

終端エリア207には、外周204の内側を、外周204に沿って伸びる4重の終端トレンチ261および262が形成されている。終端トレンチ261および262は、外周204に沿ってセルエリア205を一巡する閉ループ形状となっている。

【0056】

図5を参照して、半導体装置210の内部構造を説明する。図5の第2トレンチ232は、ボディ領域12の表面からボディ領域12を貫通して伸びており、その底面がドリフト領域4に突出している。また、第2トレンチ232の内部の全領域に、導電層235が収容されている。第2トレンチ232の上方に形成されている絶縁膜16には、図5の奥行き方向のいずれかの断面で、配線281と接続するためのコンタクトホール(不図示)が形成されている。また、第1トレンチ231の上方に形成されている絶縁膜16には、図5の手前方向のいずれかの断面で、ゲート配線280と接続するためのコンタクトホール(不図示)が形成されている。なお、その他の構造は、図1の半導体装置10と同様であるため、ここでは詳細な説明を省略する。

【0057】

第2トレンチ232は、第1トレンチ231と比較して、エミッタ領域20を有していない。よって、第2トレンチ232では、半導体装置210のターンオン時において、チャネルが導通しない。すなわち、第2トレンチ232では電気的動作が行われないため、第2トレンチ32をキャパシタとして好適に機能させることができる。そして、図6の容量成分C1は、セルエリア271に含まれている複数の第2トレンチ232の合成容量に該当する。図6の容量成分C2は、セルエリア272に含まれている複数の第2トレンチ232の合成容量に該当する。図6の容量成分C3は、セルエリア273に含まれている複数の第2トレンチ232の合成容量に該当する。また、図6の出力容量成分C0は、セルエリア271〜273に含まれている全ての第1トレンチ231の出力容量成分(エミッタ領域20−コレクタ領域3間の容量成分)の合成値に該当する。これにより、図4および図5に示す半導体装置210の具体的構造によって、図6に示す等価回路を実現できることが分かる。

【0058】

半導体装置210の効果について説明する。半導体装置210では、半導体装置210を組み込んだ実回路の共振周波数を、意図的にシフトすることが可能となる。よって、共振周波数を、実回路に発振が発生してしまう周波数を避けて設定することが可能となるため、共振の発生を防止できる。これにより、半導体装置210の寿命が短くなってしまう事態等を防止できる。

【0059】

また、半導体装置210では、トレンチゲートである第1トレンチ231の直近に、キャパシタとして機能する第2トレンチ232が位置しているため、第1トレンチ231にキャパシタを接続する際の配線長を短くすることができる。よって、配線の寄生インダクタンスを小さくすることができるため、共振の影響を小さくすることができる。また半導体装置210では、半導体装置210の内部に形成されている第2トレンチ232を、キャパシタとして機能させているため、キャパシタの高温信頼性を確保することができる。

【0060】

以上、本発明の具体例を詳細に説明したが、これらは例示にすぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例をさまざまに変形、変更したものが含まれる。

【0061】

第2トレンチの底部に配置される絶縁材は、シリコン酸化膜でもよい。この場合の製造方法を説明する。第1トレンチ31および第2トレンチ32の両方の底部に、CVD法によって厚い酸化膜を堆積させる。次に、第1トレンチのみに開口を有するマスク層を形成し、酸化膜をエッチングすることで、第1トレンチ31内の酸化膜を除去する。その後、第1トレンチ31および第2トレンチ32の各々に、ゲート絶縁膜18およびトレンチ絶縁膜33を形成する。これにより、第1トレンチ31のみチャネル形成できる構造を形成することができる。

【0062】

隣接している第1トレンチ31間に、第2トレンチ32が形成される形態は様々であってよい。実施例1では、隣接している第1トレンチ31の間に、1本の第2トレンチ32が形成されている例を示したが、複数本の第2トレンチ32が形成されてもよい。また、隣接している第1トレンチ31の間に第2トレンチ32が形成されている領域と、隣接している第1トレンチ31の間に第2トレンチ32が形成されていない領域とが混在していてもよい。

【0063】

実施例1において、第2トレンチ32内の底部に絶縁層34が配置されている場合を説明したが、この形態に限られない。第2トレンチ32の深さ方向の何れかの位置に絶縁層34が配置される形態でもよい。

【0064】

実施例2において、パッド251ないし253の少なくとも1つと、エミッタ電極14との接続方法は、様々な方法が挙げられる。例えば、図4において、セルエリア271〜273の領域内の表面全体に金属層を形成する際のマスクパターンを、パッド250〜253への接続部を有するようなパターンとする方法を採用してもよい。これにより、ワイヤを接続する工程を省略することが可能となる。

【0065】

また、実施例1に開示した技術と実施例2に開示した技術とを、同時に実施することも可能である。具体的には、図1に示す第2トレンチ32の構造と、図5に示す第2トレンチ232の構造とを、1つの半導体装置に作成してもよい。これにより、半導体装置の入力容量および出力容量を同時に調整することが可能となる。

【0066】

また、使用される半導体はSiに限らない。SiC、GaN、GaAs等の他の種類の半導体であってもよい。また、本実施形態はIGBT構造について説明したが、この形態に限られない。本願の技術をパワーMOS構造に適用しても、同様の効果を得ることができる。

【0067】

本明細書または図面に説明した技術要素は、単独であるいは各種の組み合わせによって技術的有用性を発揮するものであり、出願時請求項記載の組み合わせに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0068】

3:コレクタ領域、4:ドリフト領域、8:ゲート電極、10および100および210: 半導体装置、12:ボディ領域、14:エミッタ電極、16:絶縁膜、18:ゲート絶縁層、20:エミッタ領域、31:第1トレンチ、32および232:第2トレンチ、33:トレンチ絶縁膜、35および235:導電層、251ないし253:パッド

【技術分野】

【0001】

本願は、半導体装置の寄生容量成分を好適に調整することが可能な技術に関する。

【背景技術】

【0002】

第1導電型(例えばn型)のドリフト領域の表面に、第2導電型(例えばp型)のボディ領域が積層されている半導体基板に、半導体装置として機能する半導体構造(MOS、IGBT等)を作り込む技術が発達している。このような半導体装置では、ゲート周辺に寄生成分として形成される容量が、スイッチング特性を決定する重要なパラメータとなる。寄生容量成分は、ゲート周辺における、ゲート電極、絶縁膜、ドリフト領域等の構成によって形成される。例えば、低損失で高速なスイッチング動作を実現するためには、ゲート−コレクタ(ドレイン)間の帰還容量を低減させる必要がある。

【0003】

特許文献1には、厚い酸化膜をトレンチゲートの底部に備えている半導体装置が開示されている。厚い絶縁層によって、トレンチゲートとドレイン領域はトレンチの底部において隔てられる。これにより、帰還容量を低減させることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特表2004−538648号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

特許文献1の技術では、トレンチゲート底部の酸化膜を厚くすることにより、寄生容量成分の調整を行っている。このため、寄生容量成分を小さくするためには、トレンチゲート底部の酸化膜を厚くしなければならないが、トレンチゲート底部の酸化膜を厚くしすぎると、チャネルが形成されなくなり、半導体装置の主要特性(スイッチ特性や導通性能など)が得られなくなる。したがって、半導体装置の主要特性を確保できる範囲内でしか、寄生容量成分を調整することができず、寄生容量の調整機能を十分に得ることができないという問題があった。

【0006】

本願の技術は、上記の問題を解決するために創案された。すなわち、本願は、半導体装置の主要特性に影響を与えることなく、半導体装置の寄生容量成分を好適に調整することが可能な技術を提供する。

【課題を解決するための手段】

【0007】

本願に開示される半導体装置は、半導体層の表面の一部に臨んで形成されている第1導電型の複数個の第1半導体領域と、第1半導体領域を取り囲んでいるとともに、半導体層の表面から所定の深さまでの領域に形成されている第2導電型のボディ領域と、ボディ領域の下部に形成されており、ボディ領域によって第1半導体領域から分離されている第1導電型のドリフト領域と、ドリフト領域の下部に形成されている第2半導体領域と、各第1半導体領域の表面からボディ領域を貫通して伸びており、その底面がドリフト領域に突出している複数の第1トレンチと、各第1トレンチの内面を覆っているゲート絶縁層と、ゲート絶縁層で取り囲まれた状態で各第1トレンチ内に収容されている第1トレンチゲート電極と、隣接している第1トレンチ間に形成されているとともに、ボディ領域を貫通して伸びており、その底面がドリフト領域に突出している複数の第2トレンチと、各第2トレンチの内面を覆っているトレンチ絶縁層と、トレンチ絶縁層で取り囲まれた状態で各第2トレンチ内に収容されている複数の導電層と、を備える。また、複数の導電層のうち少なくとも1つが、第1トレンチゲート電極に電気的に接続可能とされるか、または、第1半導体領域に選択的に電気接続可能とされている。

【0008】

第1トレンチは、トレンチゲートとして動作する。第2トレンチは、導電層が第1トレンチゲート電極に電気的に接続されている場合には、入力容量(ゲート−第1半導体領域間の容量成分)を増加させるためのキャパシタとして機能する。また、第2トレンチは、導電層が第1半導体領域に電気的に接続されている場合には、出力容量(第1半導体領域−第2半導体領域の容量成分)を増加させるためのキャパシタとして機能する。第1半導体領域の例としてはエミッタ領域又はソース領域が挙げられる。また、第2半導体領域の例としてはコレクタ領域又はドレイン領域が挙げられる。

【0009】

そして、入力容量や出力容量を増加させるために、第1トレンチの構造を変える必要がないため、半導体装置の主要特性(スイッチ特性や導通性能など)に影響を与えることを防止できる。以上より、半導体装置の主要特性に影響を与えずに、容量の調整機能を十分に得ることができる。

【0010】

また、本願に開示される半導体装置では、トレンチ絶縁層で取り囲まれた状態で第2トレンチ内の底部には底部絶縁層が形成されており、底部絶縁層の上面は、ボディ領域とドリフト領域との界面よりもボディ領域側に位置しており、底部絶縁層の上層に導電層が形成されており、導電層が第1トレンチゲート電極に電気的に接続されていてもよい。

【0011】

第2トレンチ内の底部に形成された底部絶縁層の上面が、ボディ領域とドリフト領域との界面よりもボディ領域側に位置していることにより、半導体装置のターンオン時において、チャネルが導通しない。よって、第2トレンチでは、電気的動作が行われない。これにより、第2トレンチを、入力容量(ゲート−第1半導体領域間の容量成分)を増加させるためのキャパシタとして好適に機能させることができる。

【0012】

トレンチゲートに別途外付でキャパシタ素子を接続する場合には、配線長が長くなる。すると、配線の寄生インダクタンスが大きくなることで、キャパシタ素子と寄生インダクタンスによるLC共振を無視できなくなってしまう場合がある。一方、本願では、トレンチゲートである第1トレンチの直近に、キャパシタである第2トレンチが位置しているため、トレンチゲートにキャパシタを接続する際の配線長を短くすることができる。よって、配線の寄生インダクタンスを小さくすることができるため、共振の影響を小さくすることができる。

【0013】

また、半導体装置は高温になる場合がある。トレンチゲートに別途外付でキャパシタ素子を接続する場合には、キャパシタ素子の高温信頼性を考慮する必要がある。一方本願では、第2トレンチを、入力容量(ゲート−第1半導体領域間の容量成分)を増加させるためのキャパシタとして機能させる。よって、キャパシタの高温信頼性を、半導体装置と同等にすることができる。

【0014】

また、本願に開示される半導体装置では、導電層が第1トレンチゲート電極に接続されている場合における、ゲート電圧の供給源から第1トレンチゲート電極までの経路の抵抗成分である第1のゲート抵抗成分が、導電層が第1トレンチゲート電極に接続されていない場合における、ゲート電圧の供給源から第1トレンチゲート電極までの経路の抵抗成分である第2のゲート抵抗成分よりも小さくされていてもよい。また、第1トレンチの容量成分と第2トレンチの容量成分との和と第1のゲート抵抗成分との積算値が、第1トレンチの容量成分と第2のゲート抵抗成分との積算値以下となるように、第1のゲート抵抗成分が設定されていてもよい。

【0015】

第1トレンチの容量成分は、第1トレンチゲート電極、ゲート絶縁層および第1トレンチの底面と第2半導体領域との間の領域の構成によって形成される容量である。第2トレンチの容量成分は、導電層、トレンチ絶縁層および第2トレンチの底面と第2半導体領域との間の領域の構成によって形成される容量である。半導体装置のターンオフ時の動作を説明する。ゲート抵抗成分を小さくすると、ターンオフ時における素子電圧の立ち上がり時間が短くなるため、スイッチング損失を低下させることができる。しかし同時に、素子電流の減少率が大きくなるため、サージ電圧が増大するというトレードオフの関係が存在している。本願では、第1トレンチの容量成分に第2トレンチの容量成分を付加することによって、容量成分の総和値を増加させることができる。これにより、素子電圧の立ち上がり時間を短い状態に維持したまま、素子電流の減少率のみを小さくすることができる。よって、サージ電圧の増大を抑制しながら、ターンオフ損失を減少させることができる。以上より、スイッチング損失の低下とサージ電圧の抑制とを両立することができる。

【0016】

また、本願に開示される半導体装置では、第2トレンチは、ボディ領域が半導体層の表面に露出している領域に複数形成されており、複数の第2トレンチの各々内に収容されている導電層の少なくとも1つが、第1半導体領域と選択的に電気接続されていてもよい。

【0017】

第2トレンチは、ボディ領域が半導体層の表面に露出している領域に形成されているため、第2トレンチの周囲には第1半導体領域が存在しない。よって、第2トレンチでは、電気的動作が行われない。これにより、第2トレンチを、出力容量(第1半導体領域−第2半導体領域間の容量成分)を増加させるためのキャパシタとして好適に機能させることができる。

【0018】

半導体装置を配線を用いて各種の装置に搭載する場合には、半導体装置の出力容量と配線インダクタンスとによって、共振周波数が決定される。そして、共振周波数が搭載装置にとって不適切な場合には、共振が発生する場合がある。本願では、第2トレンチゲート内の導電層の少なくとも1つが第1半導体領域と選択的に電気接続可能とされている。第1半導体領域に接続される第2トレンチゲート内の導電層の数を変えることに応じて、出力容量を変化させることができる。これにより、共振周波数を意図的にシフトすることが可能となる。よって、共振周波数を共振が発生しない値に設定することが可能となるため、共振の発生を防止できる。これにより、共振によって半導体装置の寿命が短くなってしまう事態等を防止できる。

【0019】

また、本願では、トレンチゲートである第1トレンチの直近に、キャパシタである第2トレンチが位置しているため、トレンチゲートにキャパシタを接続する際の配線長を短くすることができる。よって、配線の寄生インダクタンスを小さくすることができるため、共振の影響を小さくすることができる。また本願では、第2トレンチを、出力容量(第2半導体領域−第1半導体領域間の容量成分)を増加させるためのキャパシタとして機能させる。よって、キャパシタの高温信頼性を、半導体装置と同等にすることができる。

【0020】

また、本願に開示される半導体装置では、第1トレンチおよび第2トレンチの上層には、上部絶縁層が形成されており、上部絶縁層および第1半導体領域の上層には、上部電極が形成されており、複数の第2トレンチの各々内に収容されている導電層に接続されているパッド部をさらに備え、パッド部と上部電極とが電気的に接続可能とされていてもよい。

【0021】

パッド部と上部電極とを電気的に接続する方法の一例としては、ワイヤで両者を接続する方法が挙げられる。これにより、キャパシタとして機能する第2トレンチを、選択的に第1半導体領域に接続することが可能となる。よって、出力容量を適切に変化させ、共振周波数をシフトさせることが可能となる。

【図面の簡単な説明】

【0022】

【図1】実施例1の半導体装置の断面図である。

【図2】実施例1の半導体装置の動作を示すグラフである。

【図3】従来構造の半導体装置の断面図である。

【図4】実施例2の半導体装置の平面図である。

【図5】実施例2の半導体装置の断面図である。

【図6】実施例2の半導体装置の等価回路である。

【図7】フルブリッジ回路を示す図である。

【図8】共振部の等価回路を示す図である。

【図9】共振部の等価回路を示す図である。

【図10】共振部の発振動作を示すグラフである。

【発明を実施するための形態】

【0023】

以下に説明する実施例の主要な特徴を列記しておく。

(特徴1)半導体基板はSiである。

(特徴2)セルエリアに形成されている半導体構造はIGBT構造である。

(特徴3)セルエリアに形成されている半導体構造はMOS構造である。

【実施例】

【0024】

(実施例1)

本発明に係る半導体素子駆動回路の基本原理について、半導体素子としてIGBT(絶縁ゲートバイポーラトランジスタ)素子を例にとり説明する。もちろん、IGBTに限定されるものではなく、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)でもよい。

【0025】

図1に示すように、実施例1の半導体装置10の裏面には、コレクタ電極2が形成されている。コレクタ電極2の表面に、p+型(第2導電型)の第2半導体領域(コレクタ領域)3が形成されている。コレクタ領域3の表面に、n−型のドリフト領域4が形成されている。ドリフト領域4の表面に、p型(第2導電型)のボディ領域12が形成されている。ボディ領域12の表面に、複数個のn+型(第1導電型)の第1半導体領域(エミッタ領域)20が形成されている。ボディ領域12は、エミッタ領域20を取り囲んでいる。各々のエミッタ領域20は、ボディ領域12によってドリフト領域4から分離されている。

【0026】

各エミッタ領域20の表面からボディ領域12を貫通して伸びている、第1トレンチ31が形成されている。第1トレンチ31の底面は、ドリフト領域4に突出している。第1トレンチ31の内壁は、ゲート絶縁膜18で被覆されている。第1トレンチ31内には、ゲート絶縁膜18で取り囲まれた状態で、ゲート電極8が収容されている。ゲート電極8は、ドリフト領域4とエミッタ領域20を分離している範囲のボディ領域12に、ゲート絶縁膜18を介して対向している。

【0027】

また、隣接している第1トレンチ31の間に、第2トレンチ32が形成されている。第2トレンチ32は、エミッタ領域20の表面からボディ領域12を貫通して伸びており、その底面がドリフト領域4に突出している。第2トレンチの内壁は、トレンチ絶縁膜33で被覆されている。トレンチ絶縁膜33で取り囲まれた状態で、第2トレンチ32内の底部には、絶縁層34が配置されている。絶縁層34の一例としては、n型多結晶シリコン(n-polySi)が挙げられる。絶縁層34の上面は、ボディ領域12とドリフト領域4との界面よりもボディ領域12側に位置している。絶縁層34の上層には、トレンチ絶縁膜33で取り囲まれた状態で、導電層35が収容されている。

【0028】

ボディ領域12とエミッタ領域20の表面に、エミッタ電極14が形成されている。ゲート電極8および導電層35は、絶縁膜16によって、エミッタ電極14に対して絶縁されている。絶縁膜16には、図1の奥行き方向のいずれかの断面で、ゲート電極8および導電層35の表面を露出させるコンタクトホール(不図示)が形成されている。これらのコンタクトホールを介して、導電層35とゲート電極8とが電気的に接続されている。また、導電層35とゲート電極8は、コンタクトホールを介して、ゲート電圧を供給するドライブ回路(不図示)に接続されている。

【0029】

第1トレンチ31の機能について説明する。半導体装置10では、ドライブ回路から出力されるゲート電圧(例えば15Vと0V)が、ドライブ回路からゲート電極8までの経路を介して、ゲート電極8に供給される。これにより、第1トレンチ31の各々はトレンチゲートとして動作し、半導体装置10のターンオン・ターンオフの制御が行われる。第1トレンチ31は、第1トレンチ容量成分を有している。第1トレンチ容量成分は、ゲート電極8、ゲート絶縁膜18、第1トレンチ31の底面とコレクタ領域3との間の領域、の構成によって形成される容量成分である。

【0030】

第2トレンチ32の機能について説明する。第2トレンチ32内の底部に形成された絶縁層34の上面が、ボディ領域12とドリフト領域4との界面よりもボディ領域12側に位置していることにより、半導体装置10のターンオン時において、チャネルが導通しない。よって、第2トレンチ32では、電気的動作が行われない。このようにトレンチ底部を電気的に動作させない構造にすることで、第2トレンチ32を、キャパシタとして好適に機能させることができる。第2トレンチ32がキャパシタとして機能する際の容量成分は、導電層35、絶縁層34、トレンチ絶縁膜33、第2トレンチ32の底面とコレクタ領域3との間の領域、の構成によって形成される。

【0031】

そして、第2トレンチ32の導電層35は、ゲート電極8に電気的に接続されている。これにより、第2トレンチ32を、入力容量(ゲート電極8−エミッタ領域20間の容量成分)を増加させるためのキャパシタとして機能させることができる。

【0032】

また、本願の半導体装置10と対比する対象として、従来構造の半導体装置100を、図3を用いて説明する。半導体装置100は、ダミートレンチとして機能する第2トレンチ132を備えた、ダミートレンチ型のIGBTである。第2トレンチ132は、ボディ領域12の表面からボディ領域12を貫通して伸びており、その底面がドリフト領域4に突出している。また、第2トレンチ132の内部の全領域に、導電層135が収容されている。また第2トレンチ132の上部には、導電層135を絶縁する絶縁膜16が形成されていないため、導電層135がエミッタ電極14に電気的に接続されている。なお、その他の構造は、図1の半導体装置10と同様であるため、ここでは詳細な説明を省略する。

【0033】

ダミートレンチの機能を説明する。オン抵抗を低減するために、トレンチゲート(第1トレンチ31)同士の間の距離をある程度大きくすることが望ましい場合がある。しかし、第1トレンチ31のトレンチ間距離を大きくすると、第1トレンチ31の間の領域において、ボディ領域12とドリフト領域4の間のpn接合に、大きな電界が加わることがある。そこで、当該領域にダミートレンチ(第2トレンチ132)を形成することで、pn空乏層を均等に拡げ、電界集中を緩和することができる。

【0034】

また、ゲート抵抗成分について説明する。ゲート抵抗成分は、ゲート電圧を供給するドライブ回路(不図示)から、ゲート電極8までの経路の抵抗成分である。なお、ゲート抵抗成分は、抵抗器を経路上に挿入することによって、任意の値に調整することが可能である。ここで、従来構造の半導体装置100(図3)でのゲート抵抗成分を、ゲート抵抗成分Rg1とする。また、本願の半導体装置10(図1)でのゲート抵抗成分を、ゲート抵抗成分Rg2とする。半導体装置10のゲート抵抗成分Rg2は、半導体装置100のゲート抵抗成分Rg1よりも小さくされている。

【0035】

また、従来の半導体装置100において、全ての第1トレンチ31の合成容量成分と、ゲート抵抗成分Rg1との積算値を、第1積算値とする。一方、本願の半導体装置10において、全ての第1トレンチ31の合成容量成分と全ての第2トレンチ32の合成容量成分との和と、ゲート抵抗成分Rg2との積算値を、第2積算値とする。そして、ゲート抵抗成分Rg2の値は、第2積算値が第1積算値以下となるように設定されている。

【0036】

半導体装置10の動作について説明する。例として、従来の半導体装置100(図3)の動作と、本願の半導体装置10(図1)の動作を比較して説明する。ターンオフ動作について、図2を用いて説明する。図2は、時刻t1において、ターンオフ動作が開始された場合の動作を示す図である。図2(A)はゲート電圧Vgの時間変化を示すグラフ、図2(B)はコレクタ電流Icの時間変化を示すグラフ、図2(C)はコレクタ電圧Vcの時間変化を示すグラフ、図2(D)はスイッチング損失の時間変化を示すグラフ、である。なお、図2において、実線が本願の半導体装置10の場合の特性であり、破線が従来構造の半導体装置100の場合の特性である。

【0037】

従来の半導体装置100(図2、点線)のスイッチング損失を説明する。スイッチング損失は、コレクタ電流Icとコレクタ電圧Vcで決定され、図2(D)に示す領域R1の斜線部の面積で表される。スイッチング損失を小さくするためには、コレクタ電圧Vcの立ち上がり時間P1(図2(C))を短くするか、コレクタ電圧Vcの最大値を小さくすることが必要である。

【0038】

ここで、ゲート抵抗成分を小さくすると、ターンオフ時におけるコレクタ電圧Vcの立ち上がり時間が短くなる。しかし同時に、コレクタ電流Icの減少率(di/dt)(図2(B)、領域R3)が大きくなる。また、ターンオフ時にサージ電圧(図2(C)、領域R4)が発生するが、サージ電圧はdi/dt×Lp(Lp:寄生成分のインダクタンス)で与えられる。よって、コレクタ電圧Vcの立ち上がり時間を短くすると、サージ電圧が増大するというトレードオフの関係が存在している。すると、単にゲート抵抗成分を小さくするだけでは、サージ電圧の増大によってコレクタ電圧Vcの最大値が増加してしまうため、スイッチング損失を小さくできない。

【0039】

本願の半導体装置10(図2、実線)のスイッチング損失を説明する。前述したように、ゲート抵抗成分を小さくすると、ターンオフ時におけるコレクタ電圧Vcの立ち上がり時間が短くなる。また、半導体装置10の入力容量(ゲート電極8−エミッタ領域20間の容量成分の合計値)を増加させると、コレクタ電圧Vcの立ち上がり時間を一定値に維持したまま、コレクタ電流Icの減少率のみを小さくすることができ、その結果サージ電圧を小さくすることができる。そこで、本願の半導体装置10では、ゲート抵抗成分をRg1からRg2へ小さくしている。また、ゲート抵抗成分Rg1で駆動した場合の電流の減少率(領域R3)と、ゲート抵抗成分Rg2で駆動した場合の電流の減少率(領域R5)とが同じになるように、第2トレンチ32の容量成分(複数の第2トレンチ32の容量成分の合計値)を設定している。そして、入力容量に第2トレンチ32の容量成分を付加することで、入力容量を増加させている。これにより、ゲート抵抗成分Rg1のサージ電圧(領域R4)と同じサージ電圧(領域R6)でありながら、コレクタ電圧Vcの立ち上がり時間を時間P1からP2へより短くすることができる。そして、本願の半導体装置10でのスイッチング損失は、図2(D)に示す領域R2の斜線部の面積で表される。領域R1に比して領域R2の面積が小さくなっていることから、従来の半導体装置100に比して、本願の半導体装置10では、ターンオフ損失が低下していることが分かる。以上より、スイッチング損失の低下とサージ電圧の抑制とを両立することができる。

【0040】

半導体装置10の製造方法について説明する。なお、本願の半導体装置10(図1)は、従来のダミートレンチ型の半導体装置100(図3)の構造を一部変更したものである。まず、n型の不純物を含む半導体基板を用意する。半導体基板の表面にp型の不純物をイオン注入して、ボディ領域12を形成する。半導体基板の裏面にp型の不純物をイオン注入して、コレクタ領域3を形成する。次に、ボディ領域12の表面の所定部分にマスク層を形成した後、図1に示しているエミッタ領域20を形成する。

【0041】

表面に開口を有するマスク層を形成し、表面からエミッタ領域20とボディ領域12をエッチングして、ドリフト領域4に達する第1トレンチ31および第2トレンチ32を形成する。エッチングにはRIE(Reactive Ion Etching)等のドライエッチングを利用することができる。次に、第1トレンチ31の内壁にゲート絶縁膜18を形成するとともに、第2トレンチ32の内壁にトレンチ絶縁膜33を形成する。ゲート絶縁膜18およびトレンチ絶縁膜33は、熱酸化により、同時に形成することができる。そして、第2トレンチ32の底部にのみ、選択的に絶縁層34(n−polySi)を埋め込む。その後、第1トレンチ31および第2トレンチ32内に、ポリシリコン等の導電層を同時に充填する。これにより、ゲート電極8および導電層35を同時に形成することができる。次に、絶縁膜16を形成した後に、ゲート電極8と導電層35とをゲート配線に電気的に接続すると共に、ボディ領域12とエミッタ領域20と絶縁膜16の表面にエミッタ電極14を形成する。なお、導電層35をゲート配線に接続する工程は、ゲート電極8をゲート配線に接続する工程において同時に行うことができる。次いで、コレクタ領域3の裏面にコレクタ電極2を形成する。上記の工程を経て、図1に示している半導体装置10を得ることができる。

【0042】

上述した本願の半導体装置10の製造フローでは、従来の半導体装置100の製造フローに対して、絶縁層34を埋め込む工程を追加するだけでよい。よって、従来の半導体装置100の製造フローを流用することができるため、容易に半導体装置10を製造することが可能である。

【0043】

半導体装置10の効果について説明する。半導体装置10の入力容量を増加させるために、第2トレンチ32を用いることで、第1トレンチ31の構造を変える必要がない。よって、半導体装置10の主要特性(スイッチ特性や導通性能など)に影響を与えることなく、入力容量の調整機能を十分に得ることができる。

【0044】

また、入力容量を増加させる場合に、第1トレンチ31に別途外付でキャパシタ素子を接続する場合には、配線長が長くなる。すると、配線の寄生インダクタンスが大きくなることで、キャパシタ素子と寄生インダクタンスによるLC共振を無視できなくなってしまう場合がある。一方、本願の半導体装置10では、第1トレンチ31の直近に、キャパシタとして機能する第2トレンチ32が位置しているため、第1トレンチ31にキャパシタを接続する際の配線長を短くすることができる。よって、配線の寄生インダクタンスを小さくすることができるため、共振の影響を小さくすることができる。

【0045】

また、半導体装置は高温になる場合があるため、第1トレンチ31に別途外付でキャパシタ素子を接続する場合には、キャパシタ素子の高温信頼性を考慮する必要がある。本願の半導体装置10では、半導体装置10の内部に形成されている第2トレンチ32を、キャパシタとして機能させている。よって、キャパシタの高温信頼性を半導体装置10と同等にすることができ、キャパシタの高温信頼性を確保することができる。

【0046】

(実施例2)

図6に、実施例2の半導体装置210の等価回路を示す。半導体装置210は、出力容量成分C0、容量成分C1ないしC3、パッド251ないし253、エミッタ電極14、を備える。出力容量成分C0の一端と、容量成分C1ないしC3の一端は、コレクタに共通接続されている。出力容量成分C0の他端は、エミッタに接続されている。容量成分C1ないしC3の他端は、パッド251ないし253の各々に接続されている。またエミッタ電極14が、エミッタに接続されている。そして、エミッタ電極14と、パッド251ないし253とは、ワイヤ290等を用いることによって互いに接続可能とされている。

【0047】

半導体装置210の適用形態について説明する。例として、図7に示す、フルブリッジ回路300に、本願の半導体装置210を使用する場合を説明する。また、共振部301において、並列アーム間の共振ループを想定した場合を説明する。この場合において、半導体装置210(図6)のパッド251ないし253の何れもがエミッタ電極14に接続されていない場合には、共振部301の等価回路は、図8に示す等価回路310となる。等価回路310の共振周波数f1(Hz)は、半導体装置210の出力容量と配線インダクタンスとによって決定され、下式で表される。

f1=1/2π×(C0×L1)1/2・・・式(1)

ここで、L1は配線インダクタンスである。またC0は、半導体装置210の出力容量成分である。

【0048】

そして、共振周波数f1がフルブリッジ回路300にとって不適切な場合には、フルブリッジ回路300の実駆動時において、共振部301が発振してしまう場合がある。共振部301の発振の例を図10に示す。図10は、時刻t11においてターンオン動作が開始された場合における、発振動作のイメージ図である。図10(A)は、スイッチングアームにおけるゲート電圧Vgの時間変化を示すグラフであり、図10(B)は、スイッチングアームにおけるコレクタ電圧Vcの時間変化を示すグラフである。図10(C)は、還流アームにおけるダイオード電圧Vdの時間変化を示すグラフであり、図10(D)は、還流アームにおけるダイオード電流Idの時間変化を示すグラフである。図10に示すように、発振が発生すると、ゲート電圧Vgやコレクタ電圧Vcの時間変化が大きくなるため、半導体装置210が故障したり、素子寿命が短くなるなどの問題が発生する。

【0049】

そこで、発振防止のために、等価回路310の共振周波数を、フルブリッジ回路300の実駆動時に発振が発生してしまう周波数からシフトさせる必要が出てくる場合がある。この場合、図6において、パッド251ないし253の少なくとも1つを、ワイヤ等でエミッタ電極14に接続すればよい。例として、図4および図6に示すように、ワイヤ290を用いてパッド251をエミッタ電極14に接続する場合を説明する。

【0050】

この場合の共振部301の等価回路は、図9に示す等価回路320となる。出力容量成分C0に対して容量成分C1が並列に接続されるため、出力容量成分の値を増加させることができる。そして、等価回路320の共振周波数f2(Hz)は、下式で表される。

f2=1/2π×((C0+C1)×L1)1/2・・・式(2)

式(1)および式(2)より、容量成分C1を付加することによって、共振周波数を大きくするようにシフトできることが分かる。

【0051】

そして、パッド251ないし253のうち、エミッタ電極14と接続するパッドの数を増やすほど、容量出力容量を増加させることができる。よって、共振周波数をより大きい側にシフトできることが分かる。なお、エミッタ電極14と接続するパッドの数は、フルブリッジ回路300を実動作させながらチューニングしていくことで決定してもよい。

【0052】

次に、図6で説明した半導体装置210の等価回路を実現するための、具体的な構成について説明する。図4に、半導体装置210の平面図を模式的に示す。図5に、図4のV−V線における断面図を模式的に示す。図4に示すように、半導体装置210は、外周204を有する半導体基板202を利用して製造されている。半導体基板202は、トランジスタ動作をする半導体構造が作り込まれているセルエリア271〜273と、そのセルエリア271〜273を取り囲む終端エリア207に区分されている。セルエリア271〜273の内部には、第1トレンチ231および第2トレンチ232が、図4の左右方向に伸びるように多数形成されている。また、セルエリア271〜273の領域内の表面全体には、エミッタ電極14として機能するアルミニウムの金属層(不図示)が形成されている。なお、セルエリアの数は3つに限られず、任意の数に設定することが可能である。

【0053】

半導体装置210には、パッド250〜253が備えられている。パッド250から引き出されたゲート配線280は、セルエリア271〜273の右側側面に配置されている。ゲート配線280は、第1トレンチ231の各々に接続されている。またパッド250は、ゲート電圧を供給するドライブ回路(不図示)に接続される。

【0054】

パッド251から引き出された配線281は、セルエリア271の左側側面に配置されている。配線281は、セルエリア271内に位置する第2トレンチ232の導電層235に接続されている。また、配線282および283の構造は、配線281と同様であるため、ここでは説明を省略する。ゲート配線280、配線281〜283は、互いに分離して引き回されている。

【0055】

終端エリア207には、外周204の内側を、外周204に沿って伸びる4重の終端トレンチ261および262が形成されている。終端トレンチ261および262は、外周204に沿ってセルエリア205を一巡する閉ループ形状となっている。

【0056】

図5を参照して、半導体装置210の内部構造を説明する。図5の第2トレンチ232は、ボディ領域12の表面からボディ領域12を貫通して伸びており、その底面がドリフト領域4に突出している。また、第2トレンチ232の内部の全領域に、導電層235が収容されている。第2トレンチ232の上方に形成されている絶縁膜16には、図5の奥行き方向のいずれかの断面で、配線281と接続するためのコンタクトホール(不図示)が形成されている。また、第1トレンチ231の上方に形成されている絶縁膜16には、図5の手前方向のいずれかの断面で、ゲート配線280と接続するためのコンタクトホール(不図示)が形成されている。なお、その他の構造は、図1の半導体装置10と同様であるため、ここでは詳細な説明を省略する。

【0057】

第2トレンチ232は、第1トレンチ231と比較して、エミッタ領域20を有していない。よって、第2トレンチ232では、半導体装置210のターンオン時において、チャネルが導通しない。すなわち、第2トレンチ232では電気的動作が行われないため、第2トレンチ32をキャパシタとして好適に機能させることができる。そして、図6の容量成分C1は、セルエリア271に含まれている複数の第2トレンチ232の合成容量に該当する。図6の容量成分C2は、セルエリア272に含まれている複数の第2トレンチ232の合成容量に該当する。図6の容量成分C3は、セルエリア273に含まれている複数の第2トレンチ232の合成容量に該当する。また、図6の出力容量成分C0は、セルエリア271〜273に含まれている全ての第1トレンチ231の出力容量成分(エミッタ領域20−コレクタ領域3間の容量成分)の合成値に該当する。これにより、図4および図5に示す半導体装置210の具体的構造によって、図6に示す等価回路を実現できることが分かる。

【0058】

半導体装置210の効果について説明する。半導体装置210では、半導体装置210を組み込んだ実回路の共振周波数を、意図的にシフトすることが可能となる。よって、共振周波数を、実回路に発振が発生してしまう周波数を避けて設定することが可能となるため、共振の発生を防止できる。これにより、半導体装置210の寿命が短くなってしまう事態等を防止できる。

【0059】

また、半導体装置210では、トレンチゲートである第1トレンチ231の直近に、キャパシタとして機能する第2トレンチ232が位置しているため、第1トレンチ231にキャパシタを接続する際の配線長を短くすることができる。よって、配線の寄生インダクタンスを小さくすることができるため、共振の影響を小さくすることができる。また半導体装置210では、半導体装置210の内部に形成されている第2トレンチ232を、キャパシタとして機能させているため、キャパシタの高温信頼性を確保することができる。

【0060】

以上、本発明の具体例を詳細に説明したが、これらは例示にすぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例をさまざまに変形、変更したものが含まれる。

【0061】

第2トレンチの底部に配置される絶縁材は、シリコン酸化膜でもよい。この場合の製造方法を説明する。第1トレンチ31および第2トレンチ32の両方の底部に、CVD法によって厚い酸化膜を堆積させる。次に、第1トレンチのみに開口を有するマスク層を形成し、酸化膜をエッチングすることで、第1トレンチ31内の酸化膜を除去する。その後、第1トレンチ31および第2トレンチ32の各々に、ゲート絶縁膜18およびトレンチ絶縁膜33を形成する。これにより、第1トレンチ31のみチャネル形成できる構造を形成することができる。

【0062】

隣接している第1トレンチ31間に、第2トレンチ32が形成される形態は様々であってよい。実施例1では、隣接している第1トレンチ31の間に、1本の第2トレンチ32が形成されている例を示したが、複数本の第2トレンチ32が形成されてもよい。また、隣接している第1トレンチ31の間に第2トレンチ32が形成されている領域と、隣接している第1トレンチ31の間に第2トレンチ32が形成されていない領域とが混在していてもよい。

【0063】

実施例1において、第2トレンチ32内の底部に絶縁層34が配置されている場合を説明したが、この形態に限られない。第2トレンチ32の深さ方向の何れかの位置に絶縁層34が配置される形態でもよい。

【0064】

実施例2において、パッド251ないし253の少なくとも1つと、エミッタ電極14との接続方法は、様々な方法が挙げられる。例えば、図4において、セルエリア271〜273の領域内の表面全体に金属層を形成する際のマスクパターンを、パッド250〜253への接続部を有するようなパターンとする方法を採用してもよい。これにより、ワイヤを接続する工程を省略することが可能となる。

【0065】

また、実施例1に開示した技術と実施例2に開示した技術とを、同時に実施することも可能である。具体的には、図1に示す第2トレンチ32の構造と、図5に示す第2トレンチ232の構造とを、1つの半導体装置に作成してもよい。これにより、半導体装置の入力容量および出力容量を同時に調整することが可能となる。

【0066】

また、使用される半導体はSiに限らない。SiC、GaN、GaAs等の他の種類の半導体であってもよい。また、本実施形態はIGBT構造について説明したが、この形態に限られない。本願の技術をパワーMOS構造に適用しても、同様の効果を得ることができる。

【0067】

本明細書または図面に説明した技術要素は、単独であるいは各種の組み合わせによって技術的有用性を発揮するものであり、出願時請求項記載の組み合わせに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0068】

3:コレクタ領域、4:ドリフト領域、8:ゲート電極、10および100および210: 半導体装置、12:ボディ領域、14:エミッタ電極、16:絶縁膜、18:ゲート絶縁層、20:エミッタ領域、31:第1トレンチ、32および232:第2トレンチ、33:トレンチ絶縁膜、35および235:導電層、251ないし253:パッド

【特許請求の範囲】

【請求項1】

半導体層の表面の一部に臨んで形成されている第1導電型の複数個の第1半導体領域と、

第1半導体領域を取り囲んでいるとともに、半導体層の表面から所定の深さまでの領域に形成されている第2導電型のボディ領域と、

ボディ領域の下部に形成されており、ボディ領域によって第1半導体領域から分離されている第1導電型のドリフト領域と、

ドリフト領域の下部に形成されている第2半導体領域と、

各第1半導体領域の表面からボディ領域を貫通して伸びており、その底面がドリフト領域に突出している複数の第1トレンチと、

各第1トレンチの内面を覆っているゲート絶縁層と、

ゲート絶縁層で取り囲まれた状態で各第1トレンチ内に収容されている第1トレンチゲート電極と、

隣接している第1トレンチ間に形成されているとともに、ボディ領域を貫通して伸びており、その底面がドリフト領域に突出している複数の第2トレンチと、

各第2トレンチの内面を覆っているトレンチ絶縁層と、

トレンチ絶縁層で取り囲まれた状態で各第2トレンチ内に収容されている複数の導電層と、

を備え、

複数の導電層のうち少なくとも1つが、第1トレンチゲート電極に電気的に接続可能とされるか、または、第1半導体領域に選択的に電気接続可能とされていることを特徴とする半導体装置。

【請求項2】

トレンチ絶縁層で取り囲まれた状態で第2トレンチ内の底部には底部絶縁層が形成されており、

底部絶縁層の上面は、ボディ領域とドリフト領域との界面よりもボディ領域側に位置しており、

底部絶縁層の上層に導電層が形成されており、

導電層が第1トレンチゲート電極に電気的に接続されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

導電層が第1トレンチゲート電極に接続されている場合における、ゲート電圧の供給源から第1トレンチゲート電極までの経路の抵抗成分である第1のゲート抵抗成分が、

導電層が第1トレンチゲート電極に接続されていない場合における、ゲート電圧の供給源から第1トレンチゲート電極までの経路の抵抗成分である第2のゲート抵抗成分よりも小さくされており、

第1トレンチの容量成分と第2トレンチの容量成分との和と第1のゲート抵抗成分との積算値が、第1トレンチの容量成分と第2のゲート抵抗成分との積算値以下となるように、第1のゲート抵抗成分が設定されていることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

第2トレンチは、ボディ領域が半導体層の表面に露出している領域に複数形成されており、

複数の第2トレンチの各々内に収容されている導電層の少なくとも1つが、第1半導体領域と選択的に電気接続されていることを特徴とする請求項1に記載の半導体装置。

【請求項5】

第1トレンチおよび第2トレンチの上層には、上部絶縁層が形成されており、

上部絶縁層および第1半導体領域の上層には、上部電極が形成されており、

複数の第2トレンチの各々内に収容されている導電層に接続されているパッド部をさらに備え、

パッド部と上部電極とが電気的に接続可能とされていることを特徴とする請求項4に記載の半導体装置。

【請求項1】

半導体層の表面の一部に臨んで形成されている第1導電型の複数個の第1半導体領域と、

第1半導体領域を取り囲んでいるとともに、半導体層の表面から所定の深さまでの領域に形成されている第2導電型のボディ領域と、

ボディ領域の下部に形成されており、ボディ領域によって第1半導体領域から分離されている第1導電型のドリフト領域と、

ドリフト領域の下部に形成されている第2半導体領域と、

各第1半導体領域の表面からボディ領域を貫通して伸びており、その底面がドリフト領域に突出している複数の第1トレンチと、

各第1トレンチの内面を覆っているゲート絶縁層と、

ゲート絶縁層で取り囲まれた状態で各第1トレンチ内に収容されている第1トレンチゲート電極と、

隣接している第1トレンチ間に形成されているとともに、ボディ領域を貫通して伸びており、その底面がドリフト領域に突出している複数の第2トレンチと、

各第2トレンチの内面を覆っているトレンチ絶縁層と、

トレンチ絶縁層で取り囲まれた状態で各第2トレンチ内に収容されている複数の導電層と、

を備え、

複数の導電層のうち少なくとも1つが、第1トレンチゲート電極に電気的に接続可能とされるか、または、第1半導体領域に選択的に電気接続可能とされていることを特徴とする半導体装置。

【請求項2】

トレンチ絶縁層で取り囲まれた状態で第2トレンチ内の底部には底部絶縁層が形成されており、

底部絶縁層の上面は、ボディ領域とドリフト領域との界面よりもボディ領域側に位置しており、

底部絶縁層の上層に導電層が形成されており、

導電層が第1トレンチゲート電極に電気的に接続されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

導電層が第1トレンチゲート電極に接続されている場合における、ゲート電圧の供給源から第1トレンチゲート電極までの経路の抵抗成分である第1のゲート抵抗成分が、

導電層が第1トレンチゲート電極に接続されていない場合における、ゲート電圧の供給源から第1トレンチゲート電極までの経路の抵抗成分である第2のゲート抵抗成分よりも小さくされており、

第1トレンチの容量成分と第2トレンチの容量成分との和と第1のゲート抵抗成分との積算値が、第1トレンチの容量成分と第2のゲート抵抗成分との積算値以下となるように、第1のゲート抵抗成分が設定されていることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

第2トレンチは、ボディ領域が半導体層の表面に露出している領域に複数形成されており、

複数の第2トレンチの各々内に収容されている導電層の少なくとも1つが、第1半導体領域と選択的に電気接続されていることを特徴とする請求項1に記載の半導体装置。

【請求項5】

第1トレンチおよび第2トレンチの上層には、上部絶縁層が形成されており、

上部絶縁層および第1半導体領域の上層には、上部電極が形成されており、

複数の第2トレンチの各々内に収容されている導電層に接続されているパッド部をさらに備え、

パッド部と上部電極とが電気的に接続可能とされていることを特徴とする請求項4に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−164851(P2012−164851A)

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願番号】特願2011−24756(P2011−24756)

【出願日】平成23年2月8日(2011.2.8)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願日】平成23年2月8日(2011.2.8)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

[ Back to top ]