半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0002】

配線層を複数積層させた積層構造を持つ半導体装置の多くは、所定の配線層の配線とこれとは異なる配線層の配線とを接続するためのビアを備えている。ビアには、単純に上層配線及び下層配線を接続させるものの他、更に、これら上層配線又は下層配線をビア中間部に形成されている中間配線に接続させるものもある。

【0003】

このような中間配線と接続するビアは次のように形成される。ビア形成前、予め中間配線の端部にビア領域に掛かるようにビア接続部を形成しておく。続いて、上層配線形成前、ビアを埋め込むための下層配線に達するスルーホールを形成する。スルーホールは、ビアパターンのレジストマスクを用いてビア接続部が露出するまでエッチングしていき、ビア接続部が露出したら、このビア接続部をマスクとして更にエッチングを進めていくことで形成する。続いて、この形成されたスルーホールにタングステン(W)等のビア材料を埋め込む。最後に、ビアの上面に接続するように上層配線を形成することでビアを介して上層配線、中間配線及び下層配線が接続されることになる。

【0004】

しかし、この方法の場合、ビアにはビア接続部との接続箇所において段差が形成されるため、ビアは下層に行くほど細くなってしまい、下側の中間配線や下層配線とビアとの接触面積を十分に確保できなくなる。さらに、ビアと中間配線の間に合わせずれが生じた場合、下側の中間配線とビアが接触できなくなる恐れもある。したがって、この方法を用いる場合、ビアと配線との合わせずれが発生した場合においてもビアと中間配線が十分な接触面積を確保することを目的とした合わせずれマージンをビアや配線に付加する必要がある。但し、この場合、チップ面積の増大という問題が新たに生じることになる。

【0005】

そこで、このようなビアと配線との合わせずれの問題を解消する方法として、スルーホール形成過程において中間配線も同時に除去し、スルーホールの側面に中間配線の端部を露出させる方法が提案されている。この場合、形成されたスルーホールに配線材料を埋め込めば、ビアの側面と中間配線の端部とを接続することができる。この方法を用いれば、セルフアラインでビアと中間配線とを接触させることが可能であり、ビアと配線との位置合わせが容易になる。

【0006】

しかし、この方法を用いると、もし中間配線の断面積を大きくできない場合、ビアと中間配線との十分な接触面積を確保することができず、接触抵抗が増大してしまう点が問題となる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−177276号

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、配線及びビア間接続の信頼性を向上させた半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態に係る半導体装置のビア周辺部の斜視図である。

【図2】本実施形態に係る半導体装置のビア周辺部の斜視図である。

【図3】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図4】本実施形態に係る半導体装置の製造工程を説明する図である。

【図5】本実施形態に係る半導体装置の製造工程を説明する図である。

【図6】本実施形態に係る半導体装置の製造工程を説明する図である。

【図7】本実施形態に係る半導体装置の製造工程を説明する図である。

【図8】本実施形態に係る半導体装置の製造工程を説明する図である。

【図9】本実施形態に係る半導体装置の製造工程を説明する図である。

【図10】本実施形態に係る半導体装置の製造工程を説明する図である。

【図11】本実施形態に係る半導体装置のビア周辺部の斜視図である。

【図12】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図13】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図14】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図15】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図16】第2の実施形態に係る半導体装置のビア周辺部の斜視図である。

【図17】本実施形態に係る半導体装置のビア周辺部の斜視図である。

【図18】本実施形態に係る半導体装置の製造工程を説明する図である。

【図19】本実施形態に係る半導体装置のビア周辺部の斜視図である。

【図20】比較例に係る半導体装置のビア内における配線の配置図である。

【図21】比較例に係る半導体装置のビア内における配線の配置図である。

【発明を実施するための形態】

【0011】

以下、図面を参照しながら実施形態に係る半導体装置について説明する。

[第1の実施形態]

先ず、第1の実施形態に係る半導体装置の構造について説明する。

【0012】

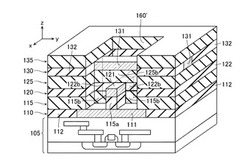

図1は、本実施形態に係る半導体装置の斜視図である。図2は、本実施形態に係る半導体装置の内部構造を分かりやすくするため、図1に示す半導体装置の一部を取り除いた図である。

【0013】

本実施形態の半導体装置は、トランジスタ及び配線が形成されたシリコン(Si)基板105と、このシリコン基板105上のz方向に積層された下層配線層110、絶縁層115、第1配線層120、絶縁層125、第2配線層130及び絶縁層135とを備える。また、下層配線層110の上面を下端とし、絶縁層135の上面を上端とするz方向に柱状に形成されたビア160を備える。

【0014】

下層配線層110は、下層配線111及びこの下層配線111の周辺に形成された絶縁膜112からなる。この下層配線111は、タングステン(W)、アルミニウム(Al)、銅(Cu)等の導電膜から構成され、ビア160の下面に接続している。

【0015】

第1配線層120は、第1配線121及びこの第1配線121の両側に形成された絶縁膜122からなる。第1配線121は、タングステン、アルミニウム、銅等の導電膜から構成され、図2に示すようにビア160の内部をx方向に貫通するように形成されている。

【0016】

第2配線層130は、第2配線131及びこの第2配線131の両側に形成された絶縁膜132からなる。第2配線131は、タングステン、アルミニウム、銅等の導電膜から構成され、図2に示すようにビア160の内部をy方向に貫通するように形成されている。

【0017】

なお、以下において、ビア160の上面と下面との間に配置された第1配線121及び第2配線131のような配線を「中間配線」と呼ぶこともある。

【0018】

ビア160は、層135、130、125、120及び115を貫通するよう、形成されたスルーホール160´をタングステン、アルミニウム、銅等の導電膜を埋め込むことにより形成される。ビア160は、スルーホール160´の形成時にエッチングされず残存した第2配線(中間配線)131及び第1配線(中間配線)121と接触するように形成される。

【0019】

なお、絶縁層115のうち、第1配線121の下に位置する部分には、後述する製造方法によるビア160の形成時において、エッチングされずに残存する絶縁膜115a(以下、「残存絶縁膜」と呼ぶ)が形成されている。

【0020】

同様に、絶縁層115、第1配線層120の絶縁膜122及び絶縁層125のうち、第2配線131の下に位置する部分には、それぞれ残存絶縁膜115b、122b及び125bが形成されている。

【0021】

以上の構造の場合、第1配線121は、残存絶縁膜115aとの接触面である下面を除く、上面と2つの側面においてビア160と接触する。同様に、第2配線131は、残存絶縁膜125bとの接触面である下面を除く、上面と2つの側面においてビア160と接触する。その結果、下層配線111、第1配線121及び第2配線131はビア160によって電気的に接続されることになる。

【0022】

ここで、第1配線121及び第2配線131とビア160との位置関係を図3を参照して説明する。

【0023】

図3は、第1配線121及び第2配線131の位置関係をz方向に見た図である。図中点線で囲まれた領域は、ビア160の形成領域を示している。また、図中一点鎖線は図1のA−A´断面を示している。図3に示すように、第1配線121、第2配線131は、ビア160をそれぞれx方向、y方向に貫通するように形成されている。つまり、これら第1配線121及び第2配線131は、ビア160内においてほぼ直交(90°で交差)するように形成されていることが分かる。

【0024】

次に、本実施形態に係る半導体装置の製造方法を図4〜図10を参照して説明する。

始めに、図4に示すように、周知の方法によって、トランジスタ及び配線が形成されたシリコン基板105を形成する。

【0025】

続いて、図5に示すように、シリコン基板105上に下層配線層110を形成する。その際、始めに、下層配線層110の絶縁膜112となる絶縁材料を積層する。続いて、リソグラフィ法を用いて下層配線111部分の絶縁材料を除去する。最後に、ダマシン法を用いて、絶縁膜材料の除去された部分に配線材料を埋め込み下層配線111を形成する。ここで、下層配線111をビア160の形成領域を囲むように形成させることで、ビア160の底面全体に下層配線111を接触させることができる。その結果、ビア160と下層配線111との接触抵抗を抑制することができる。

【0026】

なお、下層配線層110は、上記工程の他、下層配線111を先に形成する工程でも形成することができる。具体的には、始めに、下層配線111の配線材料を積層する。続いて、積層した配線材料をリソグラフィ法によって加工し下層配線111を形成する。最後に、下層配線111の周辺に絶縁膜112となる絶縁材料を埋め込み、この絶縁材料の上面をCMP等によって下層配線111の上面が露出するまで平坦化する。

以上が、下層配線層110の形成工程となる。

【0027】

続いて、図6に示すように、下層配線層110上に、絶縁層115となる層115´を成膜する。これによって、下層配線111と後に形成する第1配線121との短絡を防ぐことができる。

【0028】

続いて、図7に示すように、絶縁層となる層115´上に第1配線層120となる層120´を下層配線層110の形成工程と同様に形成する。これによって、x方向に延びる第1配線121が形成される。また、第1配線121のy方向の両側には、絶縁膜122となる膜122´が形成される。

【0029】

続いて、図8に示すように、第1配線層となる層120´上に絶縁層125となる層125´を形成する。これによって、第1配線121と後に形成する第2配線131との短絡を防ぐことができる。続いて、絶縁層となる層125´上に第2配線層130となる層130´を第1配線層となる層120´の形成工程と同様に形成する。これによって、y方向に延びる第2配線131が形成される。また、第2配線131のx方向の両側には、絶縁膜132となる膜132´が形成される。

【0030】

ここで、ビア160の中間部で接触する第1配線121及び第2配線131は、図3に示すように、ビア160を貫通し、且つ、ビア160内においてほぼ直交するように配置しておく。

【0031】

続いて、図9に示すように、第2配線層となる層130´上に絶縁層135となる層135´を形成する。これによって、第2配線131の更に上層に配線に設ける場合、第2配線131とこの上層配線との短絡を防ぐことができる。

【0032】

続いて、図10に示すように、絶縁層となる層135´上に犠牲膜170を形成する。続いて、リソグラフィ法を用いて、この犠牲膜170上にビア160のパターンPが形成されたレジスト175を形成する。

【0033】

続いて、図2に示すように、RIE等の異方性エッチングによって第1配線層110上面に達するスルーホール160´を形成する。その際、レジスト175をマスクとして犠牲膜170にビア160のパターンPを転写し、層135´〜115´を加工する。これら層135´〜115´は、ビア160の材料の良好な埋め込み特性を得るために、垂直又は順テーパ形状になるように加工する。なお、このスルーホール160´の形成において、途中で第2配線131及び第1配線121が露出することになるが、これら第2配線131及び第1配線121が残存するように、配線材料及び絶縁材料のエッチング選択比等の条件を適切に設定して異方性エッチングを実行する。それによって、層135´〜115´は、ビア160のパターンP内において第2配線131並びに第1配線121の下に位置する部分125b、122b及び115b並びに115aを除いて除去される。その結果、スルーホール160´内において第2配線131の上面及び側面が露出し、第1配線121も第2配線131の下部分を除いた上面及び側面が露出する。

【0034】

最後に、スルーホール160´内にバリアメタル及びタングステン、アルミニウム、銅等の配線材料を埋め込む。これによって、第1配線121及び第2配線131の上面及び側面で接続するビア160が形成される。その結果、ビア160と3つの配線111、121及び131とを電気的に接続することができる。その後、不要な配線材料をCMPによって除去する。

以上の製造工程によって、図1に示す半導体装置を製造することができる。

【0035】

ここで、図20に示すように、下層配線M1から上層配線M2に掛けて形成されたビア(Via)内において中間配線L1及びL2が交差せずに平行に配置されている場合について考える。この場合であっても、中間配線L1と中間配線L2とがy方向に十分にずれている場合、ビアと中間配線L1及びL2とを接触させることはできる。しかし、通常、上側の中間配線L2の下の残存絶縁膜はテーパ状に形成させるため、中間配線L1と中間配線L2のy方向のずれが十分でない場合、図20のように、中間配線L1が、残存絶縁膜内に埋もれてしまい、ビアと下側の中間配線L1とは非接触の状態となってしまう。

【0036】

その点、本実施形態では、図3に示すように、ビア160内において中間配線である第1配線121及び第2配線131をほぼ直交させている。これによって、第1配線121と第2配線131のとの位置関係が多少ずれたとしても、第1配線121が残存絶縁膜125b、122b及び115bに完全に埋まることはなく、ビア160内において露出されないといった問題を回避することができる。

【0037】

以上の点から、本実施形態によれば、従来のように配線の端部をビアと接触させる構造や、図20に示す比較例のような構造を有する半導体装置に比べ、ビアと配線或いは配線同士の位置合わせのマージンを向上させることができる。

【0038】

また、本実施形態の場合、中間配線の上面及び側面においてビアを接触させることができるため、配線の端部をビアの側面に接触させる構造よりも、ビアと中間配線との接触面積を大きく(接触抵抗を小さく)することができる。

【0039】

なお、前述の製造工程の後、更に、図1に示す半導体装置のビア160、絶縁層135上に上層配線層150を形成しても良い。この上層配線層150は、図11に示すように、ビア160の上面に接触する上層配線151及びこの上層配線151の周辺に形成された絶縁膜152からなる。ここで、この上層配線151を、ビア160の形成領域を囲むように形成しておけば、ビア160の上面全体に上層配線151を接触させることができ、これによってビア160と上層配線151との接触抵抗を抑制することができる。このように図11の製造工程を経ることによって、ビア160と4つの配線111、121、131及び151とを電気的に接続することができる。

次に、本実施形態に係る半導体装置の他の例をいくつか説明する。

【0040】

図12は、ビアを貫通する2つの中間配線L1及びL2を60°(120°)くらいで交差させた例である。この場合であっても、図3のように第1配線121及び第2配線131をほぼ直交させた場合と同様の効果を得ることができる。

【0041】

なお、図12では、2つの中間配線L1、L2の交差角度を60°(120°)くらいで示しているが、この交差角度は、0°を除き任意である。但し、第1配線121のような下側の中間配線は、第2配線131のような上側の中間配線の下に位置する部分が露出しないことに留意しなければいけない。これによって、下側の中間配線ほどビア内における露出面積が小さくなり、その結果、ビアとの接触面積が損なわれることになる。したがって、ビアを貫通させる中間配線L1及びL2は、z方向から見た重複部分が少なくなるように交差させることが望ましい。つまり、中間配線L1及びL2の交差角度が大きい(90°に近い)程、同じビア領域において、より大きなビアと中間第1配線L1との接触面積を確保することができる。

【0042】

図13は、ビアを貫通する中間配線L1及びL2を各2本配置させた例である。この例は、側壁加工等によって中間配線L1及びL2を太くできない場合に有効である。なお、側壁加工とは、リソグラフィ限界以下の線幅のパターンを形成する加工方法である。具体的には、所望の線幅の倍ピッチのレジストパターンを形成する。そして、レジストスリミング後に下層膜を加工して芯材パターンを形成した後に側壁を堆積する。最後に、芯材を剥離した上で下層膜を加工する。以上が側壁加工の工程となる。

【0043】

このように、ビア内に中間配線L1及びL2を各2本貫通させることで、ビアと中間配線L1及びL2との接触面積を図3の1本だけ貫通させる場合よりも約2倍に増大させることができる。なお、ビア内を貫通する本数については、中間配線L1及びL2のいずれか一方のみを2本とし、他方を1本とすることもできる。また、各配線層においてビア内を貫通させる配線の本数は、2本に限らず3本以上あっても良い。

【0044】

図14は、ビアを貫通する中間配線を有する配線層が3層の場合の中間配線の配置例であり、図14は、ビアを貫通する中間配線を有する配線層が4層の場合の中間配線の配置例である。

【0045】

図14の場合、3つの配線層の中間配線L1〜L3がほぼ60°毎の等角度で配置されており、図15の場合、4つの配線層の中間配線L1〜L4がほぼ45°毎の等角度で配置されている。これらの場合、z方向から見た中間配線の重複部分の面積を、他の交差角度にする場合よりも小さくすることができるため、より大きなビアと中間配線との接触面積を確保することができる。なお、一般的には、ビアを貫通する中間配線を有する配線層の数をn(nは2以上の整数)とした場合、180°/nの等角度で配置させれば良い。

【0046】

[第2の実施形態]

第2の実施形態では、ビア中間部に接触する中間配線のうちビアの上側にある中間配線については配線端部でビア側面に接触させ、下側の中間配線については第1の実施形態と同様、ビア内を貫通させるようにする。

【0047】

図16は、第2の実施形態に係る半導体装置の斜視図であり、図17は、本実施形態に係る半導体装置の内部構造を分かりやすくするため、図16に示す半導体装置の一部を取り除いた図である。

【0048】

本実施形態の半導体装置は、第1の実施形態に係る半導体装置のシリコン基板105〜絶縁層135と同様のシリコン基板205〜絶縁層235を備える。更に、本実施形態の場合、絶縁層235上に第3配線層240及び絶縁層245を備える。

【0049】

第3配線層240は、図17に示すように、第3配線(中間配線)241及びこの第3配線241の両側に形成された絶縁膜242からなる。第3配線241は、図17に示すようにビア260が埋め込まれるスルーホール261´の内壁でその端部が露出するように形成されている。また、第3配線241は、第1配線221及び第2配線231よりも断面積(線幅)が大きく形成されている。

次に、本実施形態に係る半導体装置の製造方法について説明する。

【0050】

始めに、シリコン基板205の形成から絶縁層235となる層235´の積層までを、第1の実施形態におけるシリコン基板101の形成から絶縁層となる層107´の形成までと同様に実行する。

【0051】

続いて、図18に示すように、絶縁層となる層235上に第3配線層240となる層240´を形成する。これによって、y方向に延びる第3配線241となる膜241´が形成される。また、第3配線となる膜241´のy方向の両側には、絶縁膜242となる膜242´が形成される。続いて、配線層となる層240´上に絶縁層245となる層245´を積層する。これによって、第3配線241の更に上層に配線を設ける場合、第3配線241とこの上層配線との短絡を防ぐことができる。

【0052】

続いて、図17に示すように、絶縁層となる層245´の上面から下層配線層210の上面に達するスルーホール260´を形成する。この際、断面積が小さい第1配線(中間配線)211及び第2配線(中間配線)231については、第1の実施形態と同様に除去せず、断面積が大きい第3配線となる膜241´については除去する。これによって、第3配線241の端部と後に形成されるビア260の側面とを接触させることができる。本実施形態の場合、上側の第3配線241は、下側の第1配線211及び第2配線231に比べて断面積が大きいことから、ビア260の側面のみで接触させた場合であっても、ある程度の接触面積を確保することができ、接触抵抗をある程度小さくすることができる。これによって、第3配線241が形成される。

【0053】

最後に、図16に示すように、スルーホール260´内にバリアメタル及びタングステン、アルミニウム、銅等の配線材料を埋め込む。これによってビア260が形成され、下層配線211、第1配線221、第2配線231及び第3配線241は電気的に接続されることになる。その後、不要な配線材料をCMPによって除去する。

以上の製造工程によって、図16に示す半導体装置を製造することができる。

【0054】

なお、図19に示すように、第1の実施形態と同様、上記製造工程の後、更に、ビア260及び絶縁層245上に、ビア260の形成領域を囲むように配置された上層配線251と、この上層配線251の周辺に配置された絶縁膜252からなる上層配線層245を形成しても良い。

【0055】

また、本実施形態の第3配線241のようにビア側面で接触させる中間配線を有する配線層を複数積層させることも可能である。この場合、図18と同様の工程を所望の層数分だけ繰り返せば良い。

【0056】

一般に、半導体装置の配線は、上層ほど厚く且つ線幅が太くなる。したがって、例えば、図21に示すように、下層配線M1から上層配線M2に掛けて形成されたビア(Via)の中間部に接触する複数の中間配線L1〜L3のうち、上側の中間配線L3がビアの大部分を覆うほど太い場合を考える。この場合、第1の実施形態のようにビア内で中間配線L1〜L3を全て残すと、上側の中間配線L3の下に位置する残存絶縁膜が大きくなり、ビアと下側の中間配線L1及びL2との接触面積や、ビアとビアの下面で接触する下層配線M1との接触面積が小さくなるという問題がある。

【0057】

その点、本実施形態によれば、第1の実施形態と同様の効果を得られるばかりでなく、断面の大きい上側の中間配線をビア側面で接触させることで、下側の中間配線とビアとの接触面積を損なうことなく、より積層数の多い半導体装置を提供することができる。

【0058】

[その他]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0059】

105、205・・・シリコン基板、110、120、130、150、210、220、230、240、250・・・配線層、120´、130´、220´、230´、240´・・・配線層となる層、111、121、131、151、211、221、231、241、251・・・配線、112、122、132、152、212、222、232、242、252・・・絶縁膜、122´、132´、222´、232´、242´・・・絶縁膜となる膜、115、125、135、215、225、235、245・・・絶縁層、115´、125´、135´、215´、225´、235´、245´・・・絶縁層となる層、115a、115b、122b、125b、215a、215b、222b、225b・・・残存絶縁膜、160、260・・・ビア、160´、260´・・・スルーホール、170・・・犠牲膜、175・・・レジスト、241´・・・配線となる膜。

【技術分野】

【0001】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0002】

配線層を複数積層させた積層構造を持つ半導体装置の多くは、所定の配線層の配線とこれとは異なる配線層の配線とを接続するためのビアを備えている。ビアには、単純に上層配線及び下層配線を接続させるものの他、更に、これら上層配線又は下層配線をビア中間部に形成されている中間配線に接続させるものもある。

【0003】

このような中間配線と接続するビアは次のように形成される。ビア形成前、予め中間配線の端部にビア領域に掛かるようにビア接続部を形成しておく。続いて、上層配線形成前、ビアを埋め込むための下層配線に達するスルーホールを形成する。スルーホールは、ビアパターンのレジストマスクを用いてビア接続部が露出するまでエッチングしていき、ビア接続部が露出したら、このビア接続部をマスクとして更にエッチングを進めていくことで形成する。続いて、この形成されたスルーホールにタングステン(W)等のビア材料を埋め込む。最後に、ビアの上面に接続するように上層配線を形成することでビアを介して上層配線、中間配線及び下層配線が接続されることになる。

【0004】

しかし、この方法の場合、ビアにはビア接続部との接続箇所において段差が形成されるため、ビアは下層に行くほど細くなってしまい、下側の中間配線や下層配線とビアとの接触面積を十分に確保できなくなる。さらに、ビアと中間配線の間に合わせずれが生じた場合、下側の中間配線とビアが接触できなくなる恐れもある。したがって、この方法を用いる場合、ビアと配線との合わせずれが発生した場合においてもビアと中間配線が十分な接触面積を確保することを目的とした合わせずれマージンをビアや配線に付加する必要がある。但し、この場合、チップ面積の増大という問題が新たに生じることになる。

【0005】

そこで、このようなビアと配線との合わせずれの問題を解消する方法として、スルーホール形成過程において中間配線も同時に除去し、スルーホールの側面に中間配線の端部を露出させる方法が提案されている。この場合、形成されたスルーホールに配線材料を埋め込めば、ビアの側面と中間配線の端部とを接続することができる。この方法を用いれば、セルフアラインでビアと中間配線とを接触させることが可能であり、ビアと配線との位置合わせが容易になる。

【0006】

しかし、この方法を用いると、もし中間配線の断面積を大きくできない場合、ビアと中間配線との十分な接触面積を確保することができず、接触抵抗が増大してしまう点が問題となる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−177276号

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、配線及びビア間接続の信頼性を向上させた半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態に係る半導体装置のビア周辺部の斜視図である。

【図2】本実施形態に係る半導体装置のビア周辺部の斜視図である。

【図3】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図4】本実施形態に係る半導体装置の製造工程を説明する図である。

【図5】本実施形態に係る半導体装置の製造工程を説明する図である。

【図6】本実施形態に係る半導体装置の製造工程を説明する図である。

【図7】本実施形態に係る半導体装置の製造工程を説明する図である。

【図8】本実施形態に係る半導体装置の製造工程を説明する図である。

【図9】本実施形態に係る半導体装置の製造工程を説明する図である。

【図10】本実施形態に係る半導体装置の製造工程を説明する図である。

【図11】本実施形態に係る半導体装置のビア周辺部の斜視図である。

【図12】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図13】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図14】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図15】本実施形態に係る半導体装置のビア内における配線の配置例を示す図である。

【図16】第2の実施形態に係る半導体装置のビア周辺部の斜視図である。

【図17】本実施形態に係る半導体装置のビア周辺部の斜視図である。

【図18】本実施形態に係る半導体装置の製造工程を説明する図である。

【図19】本実施形態に係る半導体装置のビア周辺部の斜視図である。

【図20】比較例に係る半導体装置のビア内における配線の配置図である。

【図21】比較例に係る半導体装置のビア内における配線の配置図である。

【発明を実施するための形態】

【0011】

以下、図面を参照しながら実施形態に係る半導体装置について説明する。

[第1の実施形態]

先ず、第1の実施形態に係る半導体装置の構造について説明する。

【0012】

図1は、本実施形態に係る半導体装置の斜視図である。図2は、本実施形態に係る半導体装置の内部構造を分かりやすくするため、図1に示す半導体装置の一部を取り除いた図である。

【0013】

本実施形態の半導体装置は、トランジスタ及び配線が形成されたシリコン(Si)基板105と、このシリコン基板105上のz方向に積層された下層配線層110、絶縁層115、第1配線層120、絶縁層125、第2配線層130及び絶縁層135とを備える。また、下層配線層110の上面を下端とし、絶縁層135の上面を上端とするz方向に柱状に形成されたビア160を備える。

【0014】

下層配線層110は、下層配線111及びこの下層配線111の周辺に形成された絶縁膜112からなる。この下層配線111は、タングステン(W)、アルミニウム(Al)、銅(Cu)等の導電膜から構成され、ビア160の下面に接続している。

【0015】

第1配線層120は、第1配線121及びこの第1配線121の両側に形成された絶縁膜122からなる。第1配線121は、タングステン、アルミニウム、銅等の導電膜から構成され、図2に示すようにビア160の内部をx方向に貫通するように形成されている。

【0016】

第2配線層130は、第2配線131及びこの第2配線131の両側に形成された絶縁膜132からなる。第2配線131は、タングステン、アルミニウム、銅等の導電膜から構成され、図2に示すようにビア160の内部をy方向に貫通するように形成されている。

【0017】

なお、以下において、ビア160の上面と下面との間に配置された第1配線121及び第2配線131のような配線を「中間配線」と呼ぶこともある。

【0018】

ビア160は、層135、130、125、120及び115を貫通するよう、形成されたスルーホール160´をタングステン、アルミニウム、銅等の導電膜を埋め込むことにより形成される。ビア160は、スルーホール160´の形成時にエッチングされず残存した第2配線(中間配線)131及び第1配線(中間配線)121と接触するように形成される。

【0019】

なお、絶縁層115のうち、第1配線121の下に位置する部分には、後述する製造方法によるビア160の形成時において、エッチングされずに残存する絶縁膜115a(以下、「残存絶縁膜」と呼ぶ)が形成されている。

【0020】

同様に、絶縁層115、第1配線層120の絶縁膜122及び絶縁層125のうち、第2配線131の下に位置する部分には、それぞれ残存絶縁膜115b、122b及び125bが形成されている。

【0021】

以上の構造の場合、第1配線121は、残存絶縁膜115aとの接触面である下面を除く、上面と2つの側面においてビア160と接触する。同様に、第2配線131は、残存絶縁膜125bとの接触面である下面を除く、上面と2つの側面においてビア160と接触する。その結果、下層配線111、第1配線121及び第2配線131はビア160によって電気的に接続されることになる。

【0022】

ここで、第1配線121及び第2配線131とビア160との位置関係を図3を参照して説明する。

【0023】

図3は、第1配線121及び第2配線131の位置関係をz方向に見た図である。図中点線で囲まれた領域は、ビア160の形成領域を示している。また、図中一点鎖線は図1のA−A´断面を示している。図3に示すように、第1配線121、第2配線131は、ビア160をそれぞれx方向、y方向に貫通するように形成されている。つまり、これら第1配線121及び第2配線131は、ビア160内においてほぼ直交(90°で交差)するように形成されていることが分かる。

【0024】

次に、本実施形態に係る半導体装置の製造方法を図4〜図10を参照して説明する。

始めに、図4に示すように、周知の方法によって、トランジスタ及び配線が形成されたシリコン基板105を形成する。

【0025】

続いて、図5に示すように、シリコン基板105上に下層配線層110を形成する。その際、始めに、下層配線層110の絶縁膜112となる絶縁材料を積層する。続いて、リソグラフィ法を用いて下層配線111部分の絶縁材料を除去する。最後に、ダマシン法を用いて、絶縁膜材料の除去された部分に配線材料を埋め込み下層配線111を形成する。ここで、下層配線111をビア160の形成領域を囲むように形成させることで、ビア160の底面全体に下層配線111を接触させることができる。その結果、ビア160と下層配線111との接触抵抗を抑制することができる。

【0026】

なお、下層配線層110は、上記工程の他、下層配線111を先に形成する工程でも形成することができる。具体的には、始めに、下層配線111の配線材料を積層する。続いて、積層した配線材料をリソグラフィ法によって加工し下層配線111を形成する。最後に、下層配線111の周辺に絶縁膜112となる絶縁材料を埋め込み、この絶縁材料の上面をCMP等によって下層配線111の上面が露出するまで平坦化する。

以上が、下層配線層110の形成工程となる。

【0027】

続いて、図6に示すように、下層配線層110上に、絶縁層115となる層115´を成膜する。これによって、下層配線111と後に形成する第1配線121との短絡を防ぐことができる。

【0028】

続いて、図7に示すように、絶縁層となる層115´上に第1配線層120となる層120´を下層配線層110の形成工程と同様に形成する。これによって、x方向に延びる第1配線121が形成される。また、第1配線121のy方向の両側には、絶縁膜122となる膜122´が形成される。

【0029】

続いて、図8に示すように、第1配線層となる層120´上に絶縁層125となる層125´を形成する。これによって、第1配線121と後に形成する第2配線131との短絡を防ぐことができる。続いて、絶縁層となる層125´上に第2配線層130となる層130´を第1配線層となる層120´の形成工程と同様に形成する。これによって、y方向に延びる第2配線131が形成される。また、第2配線131のx方向の両側には、絶縁膜132となる膜132´が形成される。

【0030】

ここで、ビア160の中間部で接触する第1配線121及び第2配線131は、図3に示すように、ビア160を貫通し、且つ、ビア160内においてほぼ直交するように配置しておく。

【0031】

続いて、図9に示すように、第2配線層となる層130´上に絶縁層135となる層135´を形成する。これによって、第2配線131の更に上層に配線に設ける場合、第2配線131とこの上層配線との短絡を防ぐことができる。

【0032】

続いて、図10に示すように、絶縁層となる層135´上に犠牲膜170を形成する。続いて、リソグラフィ法を用いて、この犠牲膜170上にビア160のパターンPが形成されたレジスト175を形成する。

【0033】

続いて、図2に示すように、RIE等の異方性エッチングによって第1配線層110上面に達するスルーホール160´を形成する。その際、レジスト175をマスクとして犠牲膜170にビア160のパターンPを転写し、層135´〜115´を加工する。これら層135´〜115´は、ビア160の材料の良好な埋め込み特性を得るために、垂直又は順テーパ形状になるように加工する。なお、このスルーホール160´の形成において、途中で第2配線131及び第1配線121が露出することになるが、これら第2配線131及び第1配線121が残存するように、配線材料及び絶縁材料のエッチング選択比等の条件を適切に設定して異方性エッチングを実行する。それによって、層135´〜115´は、ビア160のパターンP内において第2配線131並びに第1配線121の下に位置する部分125b、122b及び115b並びに115aを除いて除去される。その結果、スルーホール160´内において第2配線131の上面及び側面が露出し、第1配線121も第2配線131の下部分を除いた上面及び側面が露出する。

【0034】

最後に、スルーホール160´内にバリアメタル及びタングステン、アルミニウム、銅等の配線材料を埋め込む。これによって、第1配線121及び第2配線131の上面及び側面で接続するビア160が形成される。その結果、ビア160と3つの配線111、121及び131とを電気的に接続することができる。その後、不要な配線材料をCMPによって除去する。

以上の製造工程によって、図1に示す半導体装置を製造することができる。

【0035】

ここで、図20に示すように、下層配線M1から上層配線M2に掛けて形成されたビア(Via)内において中間配線L1及びL2が交差せずに平行に配置されている場合について考える。この場合であっても、中間配線L1と中間配線L2とがy方向に十分にずれている場合、ビアと中間配線L1及びL2とを接触させることはできる。しかし、通常、上側の中間配線L2の下の残存絶縁膜はテーパ状に形成させるため、中間配線L1と中間配線L2のy方向のずれが十分でない場合、図20のように、中間配線L1が、残存絶縁膜内に埋もれてしまい、ビアと下側の中間配線L1とは非接触の状態となってしまう。

【0036】

その点、本実施形態では、図3に示すように、ビア160内において中間配線である第1配線121及び第2配線131をほぼ直交させている。これによって、第1配線121と第2配線131のとの位置関係が多少ずれたとしても、第1配線121が残存絶縁膜125b、122b及び115bに完全に埋まることはなく、ビア160内において露出されないといった問題を回避することができる。

【0037】

以上の点から、本実施形態によれば、従来のように配線の端部をビアと接触させる構造や、図20に示す比較例のような構造を有する半導体装置に比べ、ビアと配線或いは配線同士の位置合わせのマージンを向上させることができる。

【0038】

また、本実施形態の場合、中間配線の上面及び側面においてビアを接触させることができるため、配線の端部をビアの側面に接触させる構造よりも、ビアと中間配線との接触面積を大きく(接触抵抗を小さく)することができる。

【0039】

なお、前述の製造工程の後、更に、図1に示す半導体装置のビア160、絶縁層135上に上層配線層150を形成しても良い。この上層配線層150は、図11に示すように、ビア160の上面に接触する上層配線151及びこの上層配線151の周辺に形成された絶縁膜152からなる。ここで、この上層配線151を、ビア160の形成領域を囲むように形成しておけば、ビア160の上面全体に上層配線151を接触させることができ、これによってビア160と上層配線151との接触抵抗を抑制することができる。このように図11の製造工程を経ることによって、ビア160と4つの配線111、121、131及び151とを電気的に接続することができる。

次に、本実施形態に係る半導体装置の他の例をいくつか説明する。

【0040】

図12は、ビアを貫通する2つの中間配線L1及びL2を60°(120°)くらいで交差させた例である。この場合であっても、図3のように第1配線121及び第2配線131をほぼ直交させた場合と同様の効果を得ることができる。

【0041】

なお、図12では、2つの中間配線L1、L2の交差角度を60°(120°)くらいで示しているが、この交差角度は、0°を除き任意である。但し、第1配線121のような下側の中間配線は、第2配線131のような上側の中間配線の下に位置する部分が露出しないことに留意しなければいけない。これによって、下側の中間配線ほどビア内における露出面積が小さくなり、その結果、ビアとの接触面積が損なわれることになる。したがって、ビアを貫通させる中間配線L1及びL2は、z方向から見た重複部分が少なくなるように交差させることが望ましい。つまり、中間配線L1及びL2の交差角度が大きい(90°に近い)程、同じビア領域において、より大きなビアと中間第1配線L1との接触面積を確保することができる。

【0042】

図13は、ビアを貫通する中間配線L1及びL2を各2本配置させた例である。この例は、側壁加工等によって中間配線L1及びL2を太くできない場合に有効である。なお、側壁加工とは、リソグラフィ限界以下の線幅のパターンを形成する加工方法である。具体的には、所望の線幅の倍ピッチのレジストパターンを形成する。そして、レジストスリミング後に下層膜を加工して芯材パターンを形成した後に側壁を堆積する。最後に、芯材を剥離した上で下層膜を加工する。以上が側壁加工の工程となる。

【0043】

このように、ビア内に中間配線L1及びL2を各2本貫通させることで、ビアと中間配線L1及びL2との接触面積を図3の1本だけ貫通させる場合よりも約2倍に増大させることができる。なお、ビア内を貫通する本数については、中間配線L1及びL2のいずれか一方のみを2本とし、他方を1本とすることもできる。また、各配線層においてビア内を貫通させる配線の本数は、2本に限らず3本以上あっても良い。

【0044】

図14は、ビアを貫通する中間配線を有する配線層が3層の場合の中間配線の配置例であり、図14は、ビアを貫通する中間配線を有する配線層が4層の場合の中間配線の配置例である。

【0045】

図14の場合、3つの配線層の中間配線L1〜L3がほぼ60°毎の等角度で配置されており、図15の場合、4つの配線層の中間配線L1〜L4がほぼ45°毎の等角度で配置されている。これらの場合、z方向から見た中間配線の重複部分の面積を、他の交差角度にする場合よりも小さくすることができるため、より大きなビアと中間配線との接触面積を確保することができる。なお、一般的には、ビアを貫通する中間配線を有する配線層の数をn(nは2以上の整数)とした場合、180°/nの等角度で配置させれば良い。

【0046】

[第2の実施形態]

第2の実施形態では、ビア中間部に接触する中間配線のうちビアの上側にある中間配線については配線端部でビア側面に接触させ、下側の中間配線については第1の実施形態と同様、ビア内を貫通させるようにする。

【0047】

図16は、第2の実施形態に係る半導体装置の斜視図であり、図17は、本実施形態に係る半導体装置の内部構造を分かりやすくするため、図16に示す半導体装置の一部を取り除いた図である。

【0048】

本実施形態の半導体装置は、第1の実施形態に係る半導体装置のシリコン基板105〜絶縁層135と同様のシリコン基板205〜絶縁層235を備える。更に、本実施形態の場合、絶縁層235上に第3配線層240及び絶縁層245を備える。

【0049】

第3配線層240は、図17に示すように、第3配線(中間配線)241及びこの第3配線241の両側に形成された絶縁膜242からなる。第3配線241は、図17に示すようにビア260が埋め込まれるスルーホール261´の内壁でその端部が露出するように形成されている。また、第3配線241は、第1配線221及び第2配線231よりも断面積(線幅)が大きく形成されている。

次に、本実施形態に係る半導体装置の製造方法について説明する。

【0050】

始めに、シリコン基板205の形成から絶縁層235となる層235´の積層までを、第1の実施形態におけるシリコン基板101の形成から絶縁層となる層107´の形成までと同様に実行する。

【0051】

続いて、図18に示すように、絶縁層となる層235上に第3配線層240となる層240´を形成する。これによって、y方向に延びる第3配線241となる膜241´が形成される。また、第3配線となる膜241´のy方向の両側には、絶縁膜242となる膜242´が形成される。続いて、配線層となる層240´上に絶縁層245となる層245´を積層する。これによって、第3配線241の更に上層に配線を設ける場合、第3配線241とこの上層配線との短絡を防ぐことができる。

【0052】

続いて、図17に示すように、絶縁層となる層245´の上面から下層配線層210の上面に達するスルーホール260´を形成する。この際、断面積が小さい第1配線(中間配線)211及び第2配線(中間配線)231については、第1の実施形態と同様に除去せず、断面積が大きい第3配線となる膜241´については除去する。これによって、第3配線241の端部と後に形成されるビア260の側面とを接触させることができる。本実施形態の場合、上側の第3配線241は、下側の第1配線211及び第2配線231に比べて断面積が大きいことから、ビア260の側面のみで接触させた場合であっても、ある程度の接触面積を確保することができ、接触抵抗をある程度小さくすることができる。これによって、第3配線241が形成される。

【0053】

最後に、図16に示すように、スルーホール260´内にバリアメタル及びタングステン、アルミニウム、銅等の配線材料を埋め込む。これによってビア260が形成され、下層配線211、第1配線221、第2配線231及び第3配線241は電気的に接続されることになる。その後、不要な配線材料をCMPによって除去する。

以上の製造工程によって、図16に示す半導体装置を製造することができる。

【0054】

なお、図19に示すように、第1の実施形態と同様、上記製造工程の後、更に、ビア260及び絶縁層245上に、ビア260の形成領域を囲むように配置された上層配線251と、この上層配線251の周辺に配置された絶縁膜252からなる上層配線層245を形成しても良い。

【0055】

また、本実施形態の第3配線241のようにビア側面で接触させる中間配線を有する配線層を複数積層させることも可能である。この場合、図18と同様の工程を所望の層数分だけ繰り返せば良い。

【0056】

一般に、半導体装置の配線は、上層ほど厚く且つ線幅が太くなる。したがって、例えば、図21に示すように、下層配線M1から上層配線M2に掛けて形成されたビア(Via)の中間部に接触する複数の中間配線L1〜L3のうち、上側の中間配線L3がビアの大部分を覆うほど太い場合を考える。この場合、第1の実施形態のようにビア内で中間配線L1〜L3を全て残すと、上側の中間配線L3の下に位置する残存絶縁膜が大きくなり、ビアと下側の中間配線L1及びL2との接触面積や、ビアとビアの下面で接触する下層配線M1との接触面積が小さくなるという問題がある。

【0057】

その点、本実施形態によれば、第1の実施形態と同様の効果を得られるばかりでなく、断面の大きい上側の中間配線をビア側面で接触させることで、下側の中間配線とビアとの接触面積を損なうことなく、より積層数の多い半導体装置を提供することができる。

【0058】

[その他]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0059】

105、205・・・シリコン基板、110、120、130、150、210、220、230、240、250・・・配線層、120´、130´、220´、230´、240´・・・配線層となる層、111、121、131、151、211、221、231、241、251・・・配線、112、122、132、152、212、222、232、242、252・・・絶縁膜、122´、132´、222´、232´、242´・・・絶縁膜となる膜、115、125、135、215、225、235、245・・・絶縁層、115´、125´、135´、215´、225´、235´、245´・・・絶縁層となる層、115a、115b、122b、125b、215a、215b、222b、225b・・・残存絶縁膜、160、260・・・ビア、160´、260´・・・スルーホール、170・・・犠牲膜、175・・・レジスト、241´・・・配線となる膜。

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、

前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアと

を備え、

前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、

所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差している

ことを特徴とする半導体装置。

【請求項2】

所定の前記ビアを貫通する中間配線は、相互に平行に延びる複数の配線からなる

ことを特徴とする請求項1記載の半導体装置。

【請求項3】

複数の前記ビアを貫通する中間配線は、前記ビア内において前記配線層の積層方向から見て相互に実質等角度で配置されている

ことを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

所定の前記配線層の中間配線は、端部において前記ビアの側面に接触し、前記ビアと貫通する中間配線と電気的に接続される

ことを特徴とする請求項1〜3のいずれか1項記載の半導体装置。

【請求項5】

前記端部においてビアの側面に接触する中間配線は、前記ビアを貫通する中間配線よりも断面積が大きい

ことを特徴とする請求項4記載の半導体装置。

【請求項1】

半導体基板と、

前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、

前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアと

を備え、

前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、

所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差している

ことを特徴とする半導体装置。

【請求項2】

所定の前記ビアを貫通する中間配線は、相互に平行に延びる複数の配線からなる

ことを特徴とする請求項1記載の半導体装置。

【請求項3】

複数の前記ビアを貫通する中間配線は、前記ビア内において前記配線層の積層方向から見て相互に実質等角度で配置されている

ことを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

所定の前記配線層の中間配線は、端部において前記ビアの側面に接触し、前記ビアと貫通する中間配線と電気的に接続される

ことを特徴とする請求項1〜3のいずれか1項記載の半導体装置。

【請求項5】

前記端部においてビアの側面に接触する中間配線は、前記ビアを貫通する中間配線よりも断面積が大きい

ことを特徴とする請求項4記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−164882(P2012−164882A)

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願番号】特願2011−25266(P2011−25266)

【出願日】平成23年2月8日(2011.2.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願日】平成23年2月8日(2011.2.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]