半導体装置

【課題】半導体装置におけるSM不良による信頼性や歩留りの低下を抑えることが可能な半導体装置を提供する。

【解決手段】半導体装置においては、第1の配線と、第1の配線と接続され、第1の配線より細幅の第2の配線と、一方の端部が、第1の配線と第2の配線の接続部の近傍で、第1の配線と接続され、他方の端部より局所的に細幅となる中間部を有する犠牲的配線と、を備える。

【解決手段】半導体装置においては、第1の配線と、第1の配線と接続され、第1の配線より細幅の第2の配線と、一方の端部が、第1の配線と第2の配線の接続部の近傍で、第1の配線と接続され、他方の端部より局所的に細幅となる中間部を有する犠牲的配線と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0002】

近年、半導体装置の微細化、高機能化に伴い、層間絶縁膜として低誘電率膜(以下Low−k膜と記す)が用いられている。そして、このようなLow−k膜に対し、RIE(Reactive Ion Etching)によるパターニングを行い、Wet処理後に、順次バリアメタル/Cuシードのスパッタ、Cuめっき、CMP(Chemical Mechanical Polishing)を行うことにより、ビア、配線などのメタル配線層が形成される。

【0003】

このようなメタル配線層において、ストレスマイグレーション不良(以下SM不良と記す)が発生し、半導体装置の信頼性、歩留りが低下するという問題がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−294586号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、半導体装置におけるSM不良の発生による信頼性や歩留りの低下を抑えることが可能な半導体装置を提供することである。

【課題を解決するための手段】

【0006】

本発明の実施形態によれば、半導体装置が提供される。この半導体装置においては、第1の配線と、第1の配線と接続され、第1の配線より細幅の第2の配線と、一方の端部が、第1の配線と第2の配線の接続部の近傍で、第1の配線と接続され、他方の端部より局所的に細幅となる中間部を有する犠牲的配線と、を備えることを特徴とする。

【図面の簡単な説明】

【0007】

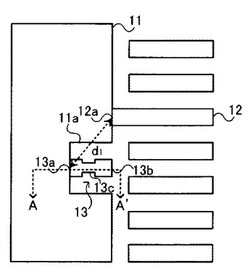

【図1】実施形態1に係る半導体装置における配線パターンの上面図。

【図2】図1のA−A’断面図。

【図3】実施形態1に係る半導体装置における配線パターンの上面図。

【図4】実施形態1に係る半導体装置における配線パターンの上面図。

【図5】実施形態2に係る半導体装置における配線パターンの上面図。

【発明を実施するための形態】

【0008】

以下、実施形態の半導体装置について、図面を参照して説明する。

【0009】

(実施形態1)

図1に、本実施形態の半導体装置における配線パターンの上面図を示す。図1に示すように、例えば幅0.5μm以上の太幅配線11が、例えば幅0.1μm未満の細幅配線12と、切り欠き部11aの近傍で接続部12aにおいて接続されている。太幅配線11には、切り欠き部11aが設けられており、切り欠き部11a内で、太幅配線11と犠牲的配線13が、その端部である接続部13aにおいて接続されている。

【0010】

犠牲的配線13は、他の配線、ビアコンタクトと接続されることなく、細幅配線12と平行に配置されている。そして、接続部13aと太幅配線11と接続されていない方の端部13bとの中間部13cは、端部13bより局所的に細幅となっている。なお、これら太幅配線11、細幅配線12、犠牲的配線13は、例えば、バリアメタル(例えばTa、Tiなど)/Cu層で構成される。

【0011】

図2に図1のA−A’断面図を示す。図2に示すように、太幅配線11、犠牲的配線13は、層間絶縁膜21、22間の層間絶縁膜23に形成されている。配線幅が細くなるほど配線溝が浅く形成されるため、犠牲的配線13は太幅配線11より浅く、犠牲的配線13の局所的に細幅となる中間部13cは、さらに浅くなっている。

【0012】

これまで、SM不良は、下層/上層配線との接続部であるビアチェーンにおいて発生しやすいということは知られていたが、半導体装置の微細化に伴い、太幅配線と細幅配線が接続した配線パターンにおいても発生することが顕在化してきた。そして、SM加速試験後の解析結果より、太幅配線と細幅配線の接続部(細幅配線の根元)にボイドが形成されることがわかった。これは、太幅配線に対し、細幅配線におけるバリアメタル、Cuシードのカバレッジが相対的に弱いことによるものであると考えられる。このようなカバレッジの相対的な劣化は、微細化が進むに伴い、さらに大きくなると考えられる。

【0013】

ビアチェーンにおけるSM不良においては、デザインルールでは、ビア上下の配線幅、フリンジ・エクステンション長さを制限することが一般的である。しかしながら、太幅配線と細幅配線の接続部のSM不良について、同様にデザインルールを適用すると、太幅配線の細幅化が考えられるものの、設計上制約される。また、細幅から太幅に段階的にシフトさせることも考えられるが、同様に、設計上の制約、チップ面積の増大を伴い、現実的とはいえない。

【0014】

そこで、このように、犠牲的配線13を配置することにより、犠牲的配線13内の局所的に細幅の中間部13cが優先的にSM不良サイトとなり、配線本体(太幅配線11、細幅配線12)内におけるSM不良の発生を抑えることができる。そして、SM不良の発生による信頼性や歩留りの低下を抑えることが可能となる。具体的には、メタルに含まれる空孔にCuが移動することでマイグレーションが進行するが、犠牲的配線の中間部13cのBMカバレッジ含むメタルの埋め込み性が相対的に劣化しているため、マイグレーションの起点となり、ボイドが形成されることにより、一定の空孔量を消費するため、配線本体のマイグレーション発生が抑制される。

【0015】

そして、このように、太幅配線11に、切り欠き部11aを設けて犠牲的配線13を配置することにより、太幅配線11と細幅配線12の位置関係を変更することなく、犠牲的配線13を配置することができる。その際、太幅配線11において、メタル面積がわずかに減少するため、わずかに抵抗値Rsが増大するが、それが許容範囲であればよい。

【0016】

なお、犠牲的配線13は、太幅配線11と細幅配線12の接続部12aの近傍に接続されるが、接続部12aと接続部13aのそれぞれ中心距離d1が、例えば太幅配線11が0.5μm、細幅配線12が0.1μmのとき、0.5μm以下(相対的には、太幅配線幅以下、或いは細幅配線の10倍以下)であることが好ましい。上限を超えると、犠牲的配線13内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制することが困難となる。より効果的に、配線本体におけるSM不良の発生を抑制するためには、0.3μm以下(相対的には、太幅配線幅の半分以下、或いは細幅配線の3倍以下)とすることがより好ましい。一方、接続部12aと接続部13aのそれぞれ中心距離d1は、犠牲的配線の形成領域が必要なため、必然的に0.3μm以上であることが好ましい。

【0017】

また、犠牲的配線13の配線幅は、0.1μm以下で、細幅配線12の配線幅以上とする。そして、端部13bより局所的に細幅となる中間部13cの幅は、0.1μm未満、0.07μm以上で、細幅配線12の配線幅未満とする。このような範囲とすることにより、より確実に犠牲的配線13内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制することができる。

【0018】

そして、犠牲的配線13の長さは、より確実に犠牲的配線13内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制するために、0.3μm以上で配線幅の3倍以上、チップ面積の増大を抑えるために、0.5μm以下であることが好ましい。

【0019】

本実施形態において、犠牲的配線13を切り欠き部11a内で細幅配線12と平行に配置しているが、図3に示すように、犠牲的配線33を切り欠き部31a内で細幅配線32と垂直に配置して、太幅配線31と接続してもよい。このように配置することにより、平行に配置したときより、それぞれの接続部を近づけることができ、より効果的にSM不良を抑制することができる。

【0020】

また、図4に示すように、犠牲的配線43が形成される切り欠き部41aは、太幅配線41と細幅配線42との接続部の配置、配置可能なスペースに応じて、太幅配線の端部に形成されていてもよい。

【0021】

(実施形態2)

本実施形態においては、犠牲的配線を、太幅配線に切り欠き部を設けることなく配置している点で、実施形態1と異なっている。

【0022】

図5に、本実施形態の半導体装置における配線パターンの上面図を示す。図5に示すように、幅0.5μm以上の太幅配線51が、例えば幅0.1μm未満の細幅配線52と、接続部52aにおいて接続されている。そして、細幅配線52を挟むように、或いはその一方に、太幅配線51と犠牲的配線53が、その端部である接続部53aにおいて接続されている。

【0023】

犠牲的配線53は、他の配線、ビアコンタクトと接続されることなく、細幅配線52と平行に配置されており、実施形態1と同様に、接続部53aと太幅配線51と接続されていない端部53bとの中間部53cは、端部53bより局所的に細幅となっている。なお、これら太幅配線51、細幅配線52、犠牲的配線53は、実施形態1と同様に、例えば、バリアメタル(例えばTa、Tiなど)/Cu層で構成される。

【0024】

このように、犠牲的配線53を配置することにより、犠牲的配線53が優先的にSM不良サイトとなり、配線本体(太幅配線51、細幅配線52)内におけるSM不良の発生を抑えることができる。そして、SM不良の発生による信頼性や歩留りの低下を抑えることが可能となる。

【0025】

そして、このように、太幅配線51に、切り欠き部を設けることなく犠牲的配線53を配置することにより、メタル面積を減少させることがないため、抵抗値Rsの増大を抑えることができる。なお、この場合、犠牲的配線53と配線54がショートしないように、スペースを設ける必要があるが、配線54側の電気特性への影響はないと考えられる。

【0026】

本実施形態においても、実施形態1と同様に、犠牲的配線53は、太幅配線51と細幅配線52の接続部52aの近傍に接続されるが、接続部52aと接続部53aのそれぞれ中心距離d2が、例えば太幅配線51が0.5μm、細幅配線52が0.1μmのとき、0.5μm以下(相対的には、太幅配線幅以下、或いは細幅配線の10倍以下)であることが好ましい。上限を超えると、犠牲的配線53内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制することが困難となる。より効果的に、配線本体におけるSM不良の発生を抑制するためには、0.2μm以下(相対的には、太幅配線幅の半分以下、或いは細幅配線の2倍以下)とすることがより好ましい。一方、接続部52aと接続部53aのそれぞれ中心距離d2は、犠牲的配線と実配線と分けて形成する都合上、0.2μm以上であることが好ましい。

【0027】

また、犠牲的配線53の配線幅は、0.1μm以下で、細幅配線52の配線幅以上とする。そして、端部53bより局所的に細幅となる中間部53cの幅は、0.1μm未満、0.07μm以上で、細幅配線52の配線幅未満とする。このような範囲とすることにより、より確実に犠牲的配線53内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制することができる。

【0028】

そして、犠牲的配線53の長さは、より確実に犠牲的配線53内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制するために、0.3μm以上で配線幅の3倍以上、チップ面積の増大を抑えるために、0.5μm以下であることが好ましい。

【0029】

以上述べた少なくとも一つの実施形態の半導体装置によれば、犠牲的配線を配置することにより、犠牲的配線が優先的にSM不良サイトとなり、配線本体(太幅配線、細幅配線)内におけるSM不良の発生を抑えることができる。そして、SM不良の発生による信頼性や歩留りの低下を抑えることが可能となる。

【0030】

なお、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。

【0031】

これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。

【0032】

これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0033】

11、31、41、51…太幅配線、11a、31a、41a…切り欠き部、12、32、42、52…細幅配線、12a、13a、52a、53a…接続部、13、33、43、53…犠牲的配線、13b、53b…端部、13c、53c…中間部、21、22、23…層間絶縁膜、54…配線。

【技術分野】

【0001】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0002】

近年、半導体装置の微細化、高機能化に伴い、層間絶縁膜として低誘電率膜(以下Low−k膜と記す)が用いられている。そして、このようなLow−k膜に対し、RIE(Reactive Ion Etching)によるパターニングを行い、Wet処理後に、順次バリアメタル/Cuシードのスパッタ、Cuめっき、CMP(Chemical Mechanical Polishing)を行うことにより、ビア、配線などのメタル配線層が形成される。

【0003】

このようなメタル配線層において、ストレスマイグレーション不良(以下SM不良と記す)が発生し、半導体装置の信頼性、歩留りが低下するという問題がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−294586号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、半導体装置におけるSM不良の発生による信頼性や歩留りの低下を抑えることが可能な半導体装置を提供することである。

【課題を解決するための手段】

【0006】

本発明の実施形態によれば、半導体装置が提供される。この半導体装置においては、第1の配線と、第1の配線と接続され、第1の配線より細幅の第2の配線と、一方の端部が、第1の配線と第2の配線の接続部の近傍で、第1の配線と接続され、他方の端部より局所的に細幅となる中間部を有する犠牲的配線と、を備えることを特徴とする。

【図面の簡単な説明】

【0007】

【図1】実施形態1に係る半導体装置における配線パターンの上面図。

【図2】図1のA−A’断面図。

【図3】実施形態1に係る半導体装置における配線パターンの上面図。

【図4】実施形態1に係る半導体装置における配線パターンの上面図。

【図5】実施形態2に係る半導体装置における配線パターンの上面図。

【発明を実施するための形態】

【0008】

以下、実施形態の半導体装置について、図面を参照して説明する。

【0009】

(実施形態1)

図1に、本実施形態の半導体装置における配線パターンの上面図を示す。図1に示すように、例えば幅0.5μm以上の太幅配線11が、例えば幅0.1μm未満の細幅配線12と、切り欠き部11aの近傍で接続部12aにおいて接続されている。太幅配線11には、切り欠き部11aが設けられており、切り欠き部11a内で、太幅配線11と犠牲的配線13が、その端部である接続部13aにおいて接続されている。

【0010】

犠牲的配線13は、他の配線、ビアコンタクトと接続されることなく、細幅配線12と平行に配置されている。そして、接続部13aと太幅配線11と接続されていない方の端部13bとの中間部13cは、端部13bより局所的に細幅となっている。なお、これら太幅配線11、細幅配線12、犠牲的配線13は、例えば、バリアメタル(例えばTa、Tiなど)/Cu層で構成される。

【0011】

図2に図1のA−A’断面図を示す。図2に示すように、太幅配線11、犠牲的配線13は、層間絶縁膜21、22間の層間絶縁膜23に形成されている。配線幅が細くなるほど配線溝が浅く形成されるため、犠牲的配線13は太幅配線11より浅く、犠牲的配線13の局所的に細幅となる中間部13cは、さらに浅くなっている。

【0012】

これまで、SM不良は、下層/上層配線との接続部であるビアチェーンにおいて発生しやすいということは知られていたが、半導体装置の微細化に伴い、太幅配線と細幅配線が接続した配線パターンにおいても発生することが顕在化してきた。そして、SM加速試験後の解析結果より、太幅配線と細幅配線の接続部(細幅配線の根元)にボイドが形成されることがわかった。これは、太幅配線に対し、細幅配線におけるバリアメタル、Cuシードのカバレッジが相対的に弱いことによるものであると考えられる。このようなカバレッジの相対的な劣化は、微細化が進むに伴い、さらに大きくなると考えられる。

【0013】

ビアチェーンにおけるSM不良においては、デザインルールでは、ビア上下の配線幅、フリンジ・エクステンション長さを制限することが一般的である。しかしながら、太幅配線と細幅配線の接続部のSM不良について、同様にデザインルールを適用すると、太幅配線の細幅化が考えられるものの、設計上制約される。また、細幅から太幅に段階的にシフトさせることも考えられるが、同様に、設計上の制約、チップ面積の増大を伴い、現実的とはいえない。

【0014】

そこで、このように、犠牲的配線13を配置することにより、犠牲的配線13内の局所的に細幅の中間部13cが優先的にSM不良サイトとなり、配線本体(太幅配線11、細幅配線12)内におけるSM不良の発生を抑えることができる。そして、SM不良の発生による信頼性や歩留りの低下を抑えることが可能となる。具体的には、メタルに含まれる空孔にCuが移動することでマイグレーションが進行するが、犠牲的配線の中間部13cのBMカバレッジ含むメタルの埋め込み性が相対的に劣化しているため、マイグレーションの起点となり、ボイドが形成されることにより、一定の空孔量を消費するため、配線本体のマイグレーション発生が抑制される。

【0015】

そして、このように、太幅配線11に、切り欠き部11aを設けて犠牲的配線13を配置することにより、太幅配線11と細幅配線12の位置関係を変更することなく、犠牲的配線13を配置することができる。その際、太幅配線11において、メタル面積がわずかに減少するため、わずかに抵抗値Rsが増大するが、それが許容範囲であればよい。

【0016】

なお、犠牲的配線13は、太幅配線11と細幅配線12の接続部12aの近傍に接続されるが、接続部12aと接続部13aのそれぞれ中心距離d1が、例えば太幅配線11が0.5μm、細幅配線12が0.1μmのとき、0.5μm以下(相対的には、太幅配線幅以下、或いは細幅配線の10倍以下)であることが好ましい。上限を超えると、犠牲的配線13内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制することが困難となる。より効果的に、配線本体におけるSM不良の発生を抑制するためには、0.3μm以下(相対的には、太幅配線幅の半分以下、或いは細幅配線の3倍以下)とすることがより好ましい。一方、接続部12aと接続部13aのそれぞれ中心距離d1は、犠牲的配線の形成領域が必要なため、必然的に0.3μm以上であることが好ましい。

【0017】

また、犠牲的配線13の配線幅は、0.1μm以下で、細幅配線12の配線幅以上とする。そして、端部13bより局所的に細幅となる中間部13cの幅は、0.1μm未満、0.07μm以上で、細幅配線12の配線幅未満とする。このような範囲とすることにより、より確実に犠牲的配線13内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制することができる。

【0018】

そして、犠牲的配線13の長さは、より確実に犠牲的配線13内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制するために、0.3μm以上で配線幅の3倍以上、チップ面積の増大を抑えるために、0.5μm以下であることが好ましい。

【0019】

本実施形態において、犠牲的配線13を切り欠き部11a内で細幅配線12と平行に配置しているが、図3に示すように、犠牲的配線33を切り欠き部31a内で細幅配線32と垂直に配置して、太幅配線31と接続してもよい。このように配置することにより、平行に配置したときより、それぞれの接続部を近づけることができ、より効果的にSM不良を抑制することができる。

【0020】

また、図4に示すように、犠牲的配線43が形成される切り欠き部41aは、太幅配線41と細幅配線42との接続部の配置、配置可能なスペースに応じて、太幅配線の端部に形成されていてもよい。

【0021】

(実施形態2)

本実施形態においては、犠牲的配線を、太幅配線に切り欠き部を設けることなく配置している点で、実施形態1と異なっている。

【0022】

図5に、本実施形態の半導体装置における配線パターンの上面図を示す。図5に示すように、幅0.5μm以上の太幅配線51が、例えば幅0.1μm未満の細幅配線52と、接続部52aにおいて接続されている。そして、細幅配線52を挟むように、或いはその一方に、太幅配線51と犠牲的配線53が、その端部である接続部53aにおいて接続されている。

【0023】

犠牲的配線53は、他の配線、ビアコンタクトと接続されることなく、細幅配線52と平行に配置されており、実施形態1と同様に、接続部53aと太幅配線51と接続されていない端部53bとの中間部53cは、端部53bより局所的に細幅となっている。なお、これら太幅配線51、細幅配線52、犠牲的配線53は、実施形態1と同様に、例えば、バリアメタル(例えばTa、Tiなど)/Cu層で構成される。

【0024】

このように、犠牲的配線53を配置することにより、犠牲的配線53が優先的にSM不良サイトとなり、配線本体(太幅配線51、細幅配線52)内におけるSM不良の発生を抑えることができる。そして、SM不良の発生による信頼性や歩留りの低下を抑えることが可能となる。

【0025】

そして、このように、太幅配線51に、切り欠き部を設けることなく犠牲的配線53を配置することにより、メタル面積を減少させることがないため、抵抗値Rsの増大を抑えることができる。なお、この場合、犠牲的配線53と配線54がショートしないように、スペースを設ける必要があるが、配線54側の電気特性への影響はないと考えられる。

【0026】

本実施形態においても、実施形態1と同様に、犠牲的配線53は、太幅配線51と細幅配線52の接続部52aの近傍に接続されるが、接続部52aと接続部53aのそれぞれ中心距離d2が、例えば太幅配線51が0.5μm、細幅配線52が0.1μmのとき、0.5μm以下(相対的には、太幅配線幅以下、或いは細幅配線の10倍以下)であることが好ましい。上限を超えると、犠牲的配線53内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制することが困難となる。より効果的に、配線本体におけるSM不良の発生を抑制するためには、0.2μm以下(相対的には、太幅配線幅の半分以下、或いは細幅配線の2倍以下)とすることがより好ましい。一方、接続部52aと接続部53aのそれぞれ中心距離d2は、犠牲的配線と実配線と分けて形成する都合上、0.2μm以上であることが好ましい。

【0027】

また、犠牲的配線53の配線幅は、0.1μm以下で、細幅配線52の配線幅以上とする。そして、端部53bより局所的に細幅となる中間部53cの幅は、0.1μm未満、0.07μm以上で、細幅配線52の配線幅未満とする。このような範囲とすることにより、より確実に犠牲的配線53内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制することができる。

【0028】

そして、犠牲的配線53の長さは、より確実に犠牲的配線53内をSM不良サイトとして、配線本体におけるSM不良の発生を抑制するために、0.3μm以上で配線幅の3倍以上、チップ面積の増大を抑えるために、0.5μm以下であることが好ましい。

【0029】

以上述べた少なくとも一つの実施形態の半導体装置によれば、犠牲的配線を配置することにより、犠牲的配線が優先的にSM不良サイトとなり、配線本体(太幅配線、細幅配線)内におけるSM不良の発生を抑えることができる。そして、SM不良の発生による信頼性や歩留りの低下を抑えることが可能となる。

【0030】

なお、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。

【0031】

これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。

【0032】

これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0033】

11、31、41、51…太幅配線、11a、31a、41a…切り欠き部、12、32、42、52…細幅配線、12a、13a、52a、53a…接続部、13、33、43、53…犠牲的配線、13b、53b…端部、13c、53c…中間部、21、22、23…層間絶縁膜、54…配線。

【特許請求の範囲】

【請求項1】

第1の配線と、

前記第1の配線と接続され、前記第1の配線より細幅の第2の配線と、

一方の端部が、前記第1の配線と前記第2の配線の接続部の近傍で、前記第1の配線と接続され、他方の端部より局所的に細幅となる中間部を有する犠牲的配線と、

を備えることを特徴とする半導体装置。

【請求項2】

前記犠牲的配線は、前記第1の配線以外の配線、又はビアコンタクトと直接接続されていないことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記犠牲的配線は、前記非接続の端部の配線幅が、前記第2の配線より太幅で、前記細幅の部分が前記第2の配線の配線幅より細いことを特徴とする請求項1又は請求項2に記載の半導体装置。

【請求項4】

前記第1の配線内に切り欠き部を有し、この切り欠き部内に前記犠牲的配線が配置されることを特徴とする請求項1から請求項3のいずれか1項に記載の半導体装置。

【請求項5】

前記犠牲的配線は、前記第2の配線と間隙を有して平行に配置されることを特徴とする請求項1から請求項4のいずれか1項に記載の半導体装置。

【請求項1】

第1の配線と、

前記第1の配線と接続され、前記第1の配線より細幅の第2の配線と、

一方の端部が、前記第1の配線と前記第2の配線の接続部の近傍で、前記第1の配線と接続され、他方の端部より局所的に細幅となる中間部を有する犠牲的配線と、

を備えることを特徴とする半導体装置。

【請求項2】

前記犠牲的配線は、前記第1の配線以外の配線、又はビアコンタクトと直接接続されていないことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記犠牲的配線は、前記非接続の端部の配線幅が、前記第2の配線より太幅で、前記細幅の部分が前記第2の配線の配線幅より細いことを特徴とする請求項1又は請求項2に記載の半導体装置。

【請求項4】

前記第1の配線内に切り欠き部を有し、この切り欠き部内に前記犠牲的配線が配置されることを特徴とする請求項1から請求項3のいずれか1項に記載の半導体装置。

【請求項5】

前記犠牲的配線は、前記第2の配線と間隙を有して平行に配置されることを特徴とする請求項1から請求項4のいずれか1項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−174773(P2012−174773A)

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願番号】特願2011−33210(P2011−33210)

【出願日】平成23年2月18日(2011.2.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願日】平成23年2月18日(2011.2.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]