半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装

置およびその作製方法に関する。例えば、液晶表示パネルに代表される電気光学装置や有

機発光素子もしくは無機発光素子を有する発光表示装置を部品として搭載した電子機器に

関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装

置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

近年、絶縁表面を有する基板上に形成された半導体薄膜(厚さ数〜数百nm程度)を用

いて薄膜トランジスタ(TFT)を構成する技術が注目されている。薄膜トランジスタは

ICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチ

ング素子として開発が急がれている。

【0004】

また、薄型軽量、高速応答性、直流低電圧駆動などの特徴を有する有機化合物を発光体と

して用いた発光素子は、次世代のフラットパネルディスプレイへの応用が期待されている

。特に、発光素子をマトリクス状に配置した表示装置は、視野角が広く視認性が優れてい

る。

【0005】

絶縁表面を有する基板上に薄膜トランジスタをマトリクス状に配置した発光表示装置は、

配線や電極によって基板表面に凹凸が形成される。その上に塗布法で絶縁膜を形成すると

均一な膜厚を保持することが困難となる。また、塗布法で成膜する際の遠心力によって、

凸部上の膜厚が薄くなる。すると、凸部上において絶縁膜の膜厚が薄くなった部分での耐

圧が低下されるという問題がある。

【0006】

また、絶縁膜の耐圧を高くしようとして単純に膜厚を厚くすると、絶縁膜全体の応力が増

加し、絶縁膜の剥離や、基板の反りが生じる恐れがあった。

【0007】

また、薄膜トランジスタをマトリクス状に配置した発光表示装置は、特許文献1に記載

された構成、具体的には隣接する画素の間に絶縁膜を設ける構造としている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−164181号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ、薄膜ト

ランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の上方に設

けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比べて大き

な段差が形成される。

【0010】

隣接する画素の間に設ける絶縁膜を塗布法で形成した場合においても、この段差の影響を

受けて、部分的に薄くなる箇所が形成され、その箇所の耐圧が低下されるという問題があ

る。

【0011】

本発明は、以上の問題点を鑑みてなされたもので、絶縁膜の膜厚が薄くとも高い絶縁特

性や、高い耐圧を備えた信頼性の高い発光装置を実現することを目的とする。

【課題を解決するための手段】

【0012】

本発明では、段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その

上に形成される絶縁膜の凹凸形状を緩和するものである。

【0013】

また、上方配線の端部と下方配線の端部を一致させると、部分的に薄くなる箇所が形成

される傾向が見られることから、上方配線の端部と下方配線の端部とが一致しないように

、上方配線と下方配線の位置をずらして配置することも本発明の特徴の一つである。また

、上方配線の端部と下方配線の端部とが一致しないように、下方配線の配線幅よりも上方

配線の配線幅を太くして配置することも本発明の特徴の一つである。

【0014】

特に、基板上方から見て上方配線と下方配線とを平行に配置する場合、上方配線の側面

と下方配線の側面とが一致しないようにすることが好ましい。

【0015】

また、下方配線の形成において、テーパー形状を有する断面とし、配線幅を細くするエ

ッチングを行うことが好ましい。即ち、下方配線の形成時にテーパー形状を有する断面と

し、配線幅を細くするエッチングを行うと、設計マスクでは上方配線の端部と下方配線の

端部とが一致していても、実際に形成すると、上方配線の端部と下方配線の端部とが一致

しないようにすることができる。

【0016】

また、塗布時(常温)において、粘度が10cp(センチポイズ)以上60cp(セン

チポイズ)以下を有する絶縁材料液を塗布し、乾燥させることで、段差部でも均一な膜厚

の絶縁膜を得ることもできる。

【0017】

本発明により、絶縁膜を挟む2つの配線(上方配線、下方配線)間の絶縁性及び耐圧を

飛躍的に改善できる。

【0018】

上述したこれらの手段は単なる設計事項ではなく、発光装置を作製し、画像表示させ、

発明者らの深い検討の後、発明された事項である。

【0019】

本明細書で開示する発明の構成は、絶縁表面上に第1の配線、第2の配線、及び金属層

と、前記第1の配線、前記第2の配線、及び前記金属層を覆う第1の絶縁層と、前記第1

の絶縁層上に前記第2の配線と接続する電極と、前記第1の絶縁層、前記電極、前記金属

層、前記第1の配線、及び前記第2の配線を覆う第2の絶縁層とを有し、前記金属層およ

び前記第2の配線は、前記第1の配線と同じ材料であり、前記電極は、前記金属層と前記

第1の配線との間に配置されることを特徴とする半導体装置である。

【0020】

また、本明細書で開示する発明の構成は、絶縁表面上に第1の配線、及び第2の配線と

、前記第1の配線、及び前記第2の配線を覆う第1の絶縁層と、前記第1の絶縁層上に前

記第2の配線と接続する第1の電極、電気的にフローティング状態である金属層と、第2

の電極と、前記第1の絶縁層、前記第1の電極、前記金属層、前記第1の配線、及び前記

第2の配線を覆う第2の絶縁層と、前記第2の電極上に発光層と、前記発光層上に第3の

電極とを有し、前記第2の配線は、前記第1の配線と同じ材料であり、前記金属層は、前

記第1の電極と同じ材料であり、前記第1の電極は、前記金属層と前記第1の配線との間

に配置されることを特徴とする半導体装置である。

上記構成において、前記第2の電極と、前記第3の電極と、前記発光層とが重なる箇所

で発光素子を構成することを特徴の一つとしている。

【0021】

なお、発光素子は、電場を加えることで発生するルミネッセンス(Electro Lu

minescence)が得られる有機化合物を含む層(以下、EL層と記す)と、陽極

と、陰極とを有する。有機化合物におけるルミネッセンスには、一重項励起状態から基底

状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)と

があるが、本発明は、どちらの発光を用いた場合にも適用可能である。

【0022】

また、上記構成において、前記第2の絶縁層は、第2の電極の周縁部を覆う隔壁である

ことを特徴の一つとしている。

【0023】

また、上記構成において、前記金属層は、電気的にフローティング状態の電極であるこ

とを特徴の一つとしている。

【0024】

また、上記構成において、前記半導体装置は、前記第1の配線をゲート電極とする第1

の薄膜トランジスタと前記第2の配線をゲート電極とする第2の薄膜トランジスタとを有

することを特徴とする半導体装置である。

【0025】

また、薄膜トランジスタ(TFTとも呼ぶ)のチャネル形成領域としては、非晶質半導体

膜、結晶構造を含む半導体膜、非晶質構造を含む化合物半導体膜などを適宜用いることが

できる。さらにTFTのチャネル形成領域として、非晶質と結晶構造(単結晶、多結晶を

含む)の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であ

って、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいるセミアモルファス半

導体膜(微結晶半導体膜、マイクロクリスタル半導体膜とも呼ばれる)も用いることがで

きる。

【0026】

また、上記構成において、前記第2の絶縁層は、溶媒を含み、且つ、粘度が10cp以上

60cp以下の材料を用いた塗布法により形成することを特徴の一つとしている。

【0027】

また、本発明の半導体装置において、静電破壊防止のための保護回路(保護ダイオード

など)を設けてもよい。

【0028】

また、本発明の半導体装置において、発光素子をマトリクス状に配置した発光装置を備え

る場合、その発光装置における画面表示の駆動方法は特に限定されず、例えば、点順次駆

動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動

方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、発光装置

のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であっ

てもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

【0029】

さらに、ビデオ信号がデジタルの発光装置において、画素に入力されるビデオ信号が定電

圧(CV)のものと、定電流(CC)のものとがある。ビデオ信号が定電圧のもの(CV

)には、発光素子に印加される信号の電圧が一定のもの(CVCV)と、発光素子に印加

される信号の電流が一定のもの(CVCC)とがある。また、ビデオ信号が定電流のもの

(CC)には、発光素子に印加される信号の電圧が一定のもの(CCCV)と、発光素子

に印加される信号の電流が一定のもの(CCCC)とがある。

【発明の効果】

【0030】

本発明により、塗布法によって得られる絶縁膜を層間に用いた場合において、異なる層

に設けられた配線間の短絡の発生を効果的に防止することができる。従って、半導体装置

の製造における歩留まりが向上する。また、製造後の半導体装置の信頼性を向上すること

もできる。

【図面の簡単な説明】

【0031】

【図1】発光装置の画素の一部を示す上面図及び断面図。(実施の形態1)

【図2】配線付近の断面の写真および模式図。(実施の形態2)

【図3】画素のレイアウトの一例を示す上面図。(実施の形態2)

【図4】画素のレイアウトの一例を示す上面図。(実施の形態3)

【図5】発光装置の作製工程を示す図。(実施の形態4)

【図6】発光装置の作製工程を示す図。(実施の形態4)

【図7】発光装置の作製工程を示す図。(実施の形態4)

【図8】アクティブマトリクス型EL表示装置の構成を示す図。(実施の形態5)

【図9】電子機器の一例を示す図。(実施の形態6)

【図10】電子機器の一例を示す図。(実施の形態6)

【図11】比較例を示す図。

【図12】発光装置の画素の一部を示す上面図及び断面図。(実施の形態1)

【発明を実施するための形態】

【0032】

本発明の実施形態について、以下に説明する。但し、本発明は以下の説明に限定されず

、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得る

ことは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載

内容に限定して解釈されるものではない。

【0033】

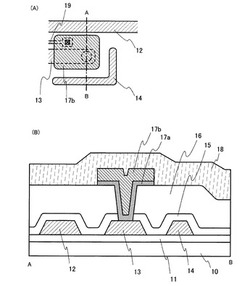

(実施の形態1)

本実施の形態では、ダミー部材を設けることによって、ダミー部材上方に設ける絶縁層

が部分的に薄くなる箇所の形成を防止する例を図1(A)及び図1(B)を用いて説明す

る。

【0034】

図1(A)は、発光装置の画素の一部を示す上面図であり、鎖線A−Bで切断した断面

図が図1(B)である。

【0035】

まず、図1(A)、および図1(B)に示す構造を得る手順を説明する。

【0036】

絶縁表面を有するガラス基板10上に第1の絶縁層11を形成し、その上に第1の配線1

2、第2の配線13、金属層14を形成する。金属層14は導電層でもよい。なお、金属

層14は、ダミー部材として機能させており、電気的に浮遊状態の電極、即ち、フローテ

ィング電極と言える。また、第1の絶縁層は、薄膜トランジスタのゲート絶縁膜としても

機能する。また、第1の配線12、第2の配線13、金属層14と同一工程で、薄膜トラ

ンジスタのゲート電極を形成する。

【0037】

次いで、これらの配線や金属層を覆う第2の絶縁層15、第3の絶縁層16を積層形成

する。

【0038】

次いで、マスクを用いて第2の絶縁層15、及び第3の絶縁層16を選択的にエッチン

グして第2の配線13に達するコンタクトホールを形成する。

【0039】

次いで、金属材料からなる第1の電極を形成する。ここでは、第1の電極をチタン層1

7aとアルミニウム層17bとの積層で構成している。また、この第1の電極と同一工程

で薄膜トランジスタのソース電極やドレイン電極を形成する。

【0040】

次いで、第3の絶縁層16上に第2の電極を形成する。なお、第2の電極は、薄膜トラ

ンジスタのソース電極やドレイン電極と電気的に接続する。

【0041】

次いで、溶媒を含む絶縁材料を用いて塗布法により、第4の絶縁層18を形成する。こ

こまでの段階を終えた時点で図1(A)及び図1(B)の状態が得られる。

【0042】

なお、図1(B)は、発光装置の作製途中の図であり、さらに第4の絶縁層18の上方に

有機化合物または無機化合物を含む発光層72と、第3の電極73とが積層形成される。

また、第3の電極73形成直後の断面図を図12(B)に示す。発光素子は、第2の電極

71と、有機化合物または無機化合物を含む発光層72と、第3の電極73とで構成され

る。特に、アルミニウム層17bの上端部と第3の電極73とで短絡が生じる恐れがある

。本実施の形態では、ダミー部材である金属層14を配置することによって、第4の絶縁

層18の膜厚が部分的に薄くなることを防いでいる。また、図1(A)よりも広範囲に画

素を示した上面図を図12(A)に示す。ソース線75は、第1の半導体層19を活性層

とする薄膜トランジスタに電気的に接続している。第1の半導体層19は、コンタクトホ

ールを介して第1の電極と電気的に接続している。また、第1の電極は、コンタクトホー

ルを介して第2の配線13と電気的に接続している。また、第2の配線13は、第2の絶

縁層15を介して第2の半導体層77と重なるゲート電極として機能する。第2の半導体

層77は、電源線78及び、接続電極76と電気的に接続している。また、接続電極76

は第2の電極71と電気的に接続している。なお、接続電極76とソース線75と電源線

78は第1の電極と同じ材料で形成されている。第4の絶縁層18は、第2の電極71の

端部を覆う隔壁として機能し、第4の絶縁層の周縁を図12(A)中の符号74に示す。

図12(A)に示すように、本発明は、金属層14を第2の配線13と重なっている第1

の電極と、第4の絶縁層の周縁74との間に配置することで、第4の絶縁層の膜厚が部分

的に薄くなることを防いでいる。

【0043】

また、第1の配線12も第4の絶縁層18の凹凸形状を緩和させる機能を有している。本

実施の形態1では、第1の電極を囲むように所定の間隔で第1の配線12及び金属層14

を配置することによって、第4の絶縁層18の凹凸形状を緩和させている。

【0044】

また、金属層14の上面形状をL字形状としているが特に限定されず、複数の矩形形状

としてもよい。

【0045】

(実施の形態2)

本実施の形態では、上方配線の端部と下方配線の端部を一致させないように各配線を設け

る例を図2(A)、図2(B)、及び図3を用いて説明する。

【0046】

実際に、上方配線の端部と下方配線の端部の位置を異ならせたレイアウトで発光装置を

形成し、その一部の断面写真が図2(A)である。なお、図2(A)に対応する模式図を

図2(B)に示す。

【0047】

図2(B)において、ガラス基板20上にゲートメタル層21、第1の絶縁層22、第

1のチタン膜23a、アルミニウム膜23b、第2のチタン膜23c、第2の絶縁層24

が設けられている。第2の絶縁層24上には発光素子を形成する有機化合物を含む層と上

部電極25が形成される。なお、図2(B)において、発光素子の下部電極は図示してい

ない。

【0048】

また、比較例として、上方配線の端部と下方配線の端部を一致させたレイアウトで発光

装置を形成し、その一部の断面写真が図11(A)である。なお、図11(A)に対応す

る模式図を図11(B)に示す。図11(B)において、ガラス基板60上にゲートメタ

ル層61、第1の絶縁層62、第1のチタン膜63a、アルミニウム膜63b、第2のチ

タン膜63c、第2の絶縁層64が設けられている。第2の絶縁層64上には発光素子を

形成する有機化合物を含む層と上部電極65が形成される。なお、図11(B)において

、発光素子の下部電極は図示していない。図11(A)に示したように、上方配線(63

a〜63c)の端部と下方配線(ゲートメタル層61)の端部を一致させた場合、上方配

線の上端部で第2の絶縁層64の膜厚が薄くなり、最も薄い所で約0.1μmの膜厚とな

ってしまう。上方配線が配置されていない領域での第2の絶縁層64の膜厚は、約1μm

であるため、結果として部分的に第2の絶縁層64の膜厚が10倍異なっている。

【0049】

一方、図2(A)に示したように、上方配線(23a〜23c)の端部と下方配線(ゲー

トメタル層21)の端部の位置を異ならせた場合、上方配線の上端部と上部電極25との

間隔を広げることができる。上方配線が配置されていない領域での第2の絶縁層24の膜

厚は、第2の絶縁層64と同じ約1μmであるが、第2の絶縁層24の最も薄い所で約0

.2μm以上の膜厚とすることができている。

【0050】

また、画素のレイアウトの一例を図3に示す。

【0051】

図3において、絶縁表面上には、半導体層(図3中において点線で囲まれた領域)が形

成され、その上にゲート絶縁膜が形成され、さらにその上に第1の配線41、42が同時

に形成されている。そして、第1の配線上に層間絶縁膜が1層または2層形成され、層間

絶縁膜上に第2の配線31、32および電極33、34が同時に形成されている。なお、

電極33は2つのTFTを接続する接続電極である。また、電極34は、発光素子の陰極

または陽極のうち、一方の電極と接続する電極である。

【0052】

図3では2つの配線が交差する部分、重なる部分があるが、配線の端部、即ち配線側面が

、異なる配線の側面と一致しないように配置している。具体的には、第2の配線32に比

べて、第1の配線41、42は配線幅が狭くなっており、且つ、第2の配線32の配線側

面と第1の配線41の配線側面が一致しないように配置され、第2の配線32の配線側面

と第1の配線42の配線側面が一致しないように配置されている。

【0053】

図3に示す配線のレイアウト配置とすることにより、これらの配線上に塗布法で絶縁膜

を形成した場合、絶縁膜の膜厚が部分的に薄くなることを防ぐことができる。従って、こ

の絶縁膜をパターニングして得られる絶縁物(隣り合う発光素子との間に設ける隔壁)は

、電極間の短絡を防止することができる。

【0054】

また、本実施の形態は、実施の形態1と自由に組み合わせることができる。

【0055】

(実施の形態3)

本実施の形態では、実施の形態1と実施の形態2とを組み合わせた画素構成について図4

を用いて説明する。

【0056】

表示装置の画素領域に有する1画素の上面図を図4に示す。図4において、画素は、薄膜

トランジスタ51、薄膜トランジスタ52、第1の電極層50、ゲート配線層53、ソー

ス配線層又はドレイン配線層54、電源線55、導電層56a、導電層56b、導電層5

6c、導電層56dから構成されている。薄膜トランジスタ52の有するソース電極層又

はドレイン電極層58は、ゲート配線層53と同材料、同工程で作製される導電層57を

介して、第1の電極層50と電気的に接続している。

【0057】

導電層56a、導電層56b、導電層56c、導電層56dは、ソース配線層又はドレイ

ン配線層54、及び電源線55と同材料、同工程で形成されており、配線の積層による膜

厚の急激な変化を緩和するために設けられている。この導電層56a、導電層56b、導

電層56c、導電層56dは、他の配線とは電気的に絶縁されている。ゲート配線層53

と、ソース配線層又はドレイン配線層54又は電源線55との交差する領域では配線層が

積層するため、急激に膜厚が大きくなるが、交差する領域の周囲に導電層56a、導電層

56b、導電層56c、導電層56dを設けることで、その上に形成される隔壁として機

能する絶縁層の被覆性が向上し、膜厚の凹凸に起因する形成不良を防ぐことができる。導

電層56aの一部は、ゲート配線層53と重なっている。寄生容量の増大を防ぐため、導

電層56b、導電層56c、及び導電層56dは間隔を空けてゲート配線層53と重ねて

いる。また、隔壁となる絶縁膜は、第1の電極層50の端部を覆うように形成され、隔壁

となる絶縁膜の周縁を図4(A)中の59に示す。図4(B)に図4(A)中の線A−B

で切断した図を示す。図4(B)に示すように導電層56aは、隔壁となる絶縁膜の膜厚

が部分的に薄くなることを防ぐため、隔壁となる絶縁膜の周縁59と薄膜トランジスタ5

2のゲート電極との間に配置されている。

【0058】

また、同材料、同工程で形成されている導電層の端面と、ゲート配線層の端面とが一致

しないように配線を配置することで、隔壁となる絶縁膜の膜厚が部分的に薄くなることを

防ぐことができる。

【0059】

よって、生産性も向上し、信頼性の高い表示装置を歩留まり良く作製することができる。

【0060】

(実施の形態4)

本実施の形態では、アクティブマトリクス型の発光装置の作製方法について、図5、図6

、及び図7を用いて以下に説明する。

【0061】

まず、基板610上に下地絶縁膜611を形成する。基板610側を表示面として発光を

取り出す場合、基板610としては、光透過性を有するガラス基板や石英基板を用いれば

よい。また、処理温度に耐えうる耐熱性を有する光透過性のプラスチック基板を用いても

よい。また、基板610側とは逆の面を表示面として発光を取り出す場合、前述の基板の

他にシリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用い

ても良い。ここでは基板610としてガラス基板を用いる。なお、ガラス基板の屈折率は

1.55前後である。

【0062】

下地絶縁膜611としては、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜

などの絶縁膜から成る下地膜を形成する。ここでは下地膜として単層構造を用いた例を示

すが、前記絶縁膜を2層以上積層させた構造を用いても良い。なお、基板の凹凸や、基板

からの不純物拡散が問題にならないのであれば、特に下地絶縁膜を形成しなくてもよい。

【0063】

次いで、下地絶縁膜上に半導体層612を形成する。半導体層612は、非晶質構造を

有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)

により成膜した後、公知の結晶化処理(レーザー結晶化法、熱結晶化法、またはニッケル

などの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体膜を第1のフォトマス

クを用いて所望の形状にパターニングして、半導体層612を形成する。なお、プラズマ

CVD法を用いれば、下地絶縁膜と、非晶質構造を有する半導体膜とを大気に触れること

なく連続的に積層することができる。この半導体膜の厚さは25〜80nm(好ましくは

30〜70nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくは

シリコンまたはシリコンゲルマニウム(SiGe)合金などで形成すると良い。

【0064】

また、非晶質構造を有する半導体膜の結晶化処理として連続発振のレーザーを用いてもよ

く、非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためには、連続発振が可能な固

体レーザを用い、基本波の第2高調波〜第4高調波を適用するのが好ましい。代表的には

、Nd:YVO4レーザー(基本波1064nm)の第2高調波(532nm)や第3高

調波(355nm)を適用すればよい。連続発振のレーザーを用いる場合には、出力10

Wの連続発振のYVO4レーザから射出されたレーザ光を非線形光学素子により高調波に

変換する。また、共振器の中にYVO4結晶と非線形光学素子を入れて、高調波を射出す

る方法もある。そして、好ましくは光学系により照射面にて矩形状または楕円形状のレー

ザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01〜100M

W/cm2程度(好ましくは0.1〜10MW/cm2)が必要である。そして、10〜

2000cm/s程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射すれ

ばよい。

【0065】

次いで、レジストマスクを除去する。次いで、必要があればTFTのしきい値を制御す

るために、微量な不純物元素(ボロンまたはリン)のドーピングを半導体層に対して行う

。ここでは、ジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法

を用いる。

【0066】

次いで、フッ酸を含むエッチャントで半導体層表面の酸化膜を除去すると同時に半導体

層の表面を洗浄する。

【0067】

そして、半導体層を覆う絶縁膜613を形成する。絶縁膜613はプラズマCVD法また

はスパッタ法を用い、厚さを1〜200nmとする。好ましくは10nm〜50nmと薄

くしてシリコンを含む絶縁膜の単層または積層構造で形成した後にマイクロ波によるプラ

ズマを用いた表面窒化処理を行う。絶縁膜613は、後に形成されるTFTのゲート絶縁

膜として機能する。

【0068】

次いで、絶縁膜613上に膜厚20〜100nmの第1の導電膜と、膜厚100〜400

nmの第2の導電膜とを積層形成する。本実施の形態では、絶縁膜613上に膜厚50n

mの窒化タンタル膜、膜厚370nmのタングステン膜を順次積層し、以下に示す手順で

パターニングを行って各ゲート電極及び各配線を形成する。

【0069】

なお、ここでは導電膜をTaN膜とW膜との積層としたが、特に限定されず、Ta、W、

Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料若し

くは化合物材料の単層、またはこれらの積層で形成してもよい。また、リン等の不純物元

素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。また、2層

構造に限定されず、例えば、膜厚50nmのタングステン膜、膜厚500nmのアルミニ

ウムとシリコンの合金(Al−Si)膜、膜厚30nmの窒化チタン膜を順次積層した3

層構造としてもよい。

【0070】

上記第1の導電膜及び第2の導電膜のエッチング(第1のエッチング処理および第2の

エッチング処理)にはICP(Inductively Coupled Plasma

:誘導結合型プラズマ)エッチング法を用いると良い。ICPエッチング法を用い、エッ

チング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基

板側の電極温度等)を適宜調節することによって所望のテーパー形状に膜をエッチングす

ることができる。

【0071】

ここでは、レジストからなるマスクを形成した後、第1のエッチング条件として1Paの

圧力でコイル型の電極に700WのRF(13.56MHz)電力を投入し、エッチング

用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を25:25:10(s

ccm)とし、基板側(試料ステージ)にも150WのRF(13.56MHz)電力を

投入し、実質的に負の自己バイアス電圧を印加する。なお、基板側の電極面積サイズは、

12.5cm×12.5cmであり、コイル型の電極面積サイズ(ここではコイルの設け

られた石英円板)は、直径25cmの円板である。この第1のエッチング条件によりW膜

をエッチングして端部をテーパー形状とする。この後、レジストからなるマスク616を

除去せずに第2のエッチング条件に変え、エッチング用ガスにCF4とCl2とを用い、

それぞれのガス流量比を30:30(sccm)とし、1Paの圧力でコイル型の電極に

500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度の

エッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電

力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した第2

のエッチング条件ではW膜及びTaN膜とも同程度にエッチングされる。なお、ここでは

、第1のエッチング条件及び第2のエッチング条件を第1のエッチング処理と呼ぶことと

する。

【0072】

第1のエッチング処理が終わった段階での断面図を図5(A)に示す。この段階で第1

の導電層614aを下層とし、第2の導電層614bを上層とするゲート電極および配線

が形成され、また、第1の導電層615aを下層とし、第2の導電層615bを上層とす

る端子電極が形成される。

【0073】

次いで、レジストからなるマスク616を除去せずに第2のエッチング処理を行う。こ

こでは、第3のエッチング条件としてエッチング用ガスにCF4とCl2とを用い、それ

ぞれのガス流量比を30:30(sccm)とし、1Paの圧力でコイル型の電極に50

0WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを60秒

行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、

実質的に負の自己バイアス電圧を印加する。この後、レジストからなるマスクを除去せず

に第4のエッチング条件に変え、エッチング用ガスにCF4とCl2とO2とを用い、そ

れぞれのガス流量比を20:20:20(sccm)とし、1Paの圧力でコイル型の電

極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約20秒程

度のエッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz

)電力を投入し、実質的に負の自己バイアス電圧を印加する。なお、ここでは、第3のエ

ッチング条件及び第4のエッチング条件を第2のエッチング処理と呼ぶこととする。第2

のエッチング処理によって、第3の導電層614c、615cが形成される。次いで、レ

ジストからなるマスクを除去する。

【0074】

上記第2のエッチング処理の際、またはレジストからなるマスクの除去の際、タングス

テン(W)を含む薄い膜(膜厚は約10nm)を形成する。この段階での断面図を図5(

B)に示す。

【0075】

次いで、n型を付与する不純物元素を半導体層に添加するため、ゲート電極をマスクと

して全面にドーピングする第1のドーピング処理を行う。第1のドーピング処理はイオン

ドープ法、もしくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を1.

5×1013atoms/cm2とし、加速電圧を50〜100keVとして行う。n型

を付与する不純物元素として、典型的にはリン(P)または砒素(As)を用いる。この

第1のドーピング工程によって絶縁膜613およびタングステンを含む薄い膜617を介

してドープを行い、自己整合的に第1の不純物領域(n−−領域)618を形成する。こ

の段階での断面図を図5(C)に示す。なお、タングステンを含む薄い膜が設けられてい

るため、第1の導電層614aと重なる部分の半導体層にはn型を付与する不純物元素が

ほとんど添加されない。また、タングステンを含む薄い膜により、n型を付与する不純物

元素が第1の導電層614aの端部を回り込んで添加されることも防ぐことができる。

【0076】

次いで、タングステンを含む薄い膜617を除去する。

【0077】

次いで、レジストからなるマスク619を形成した後、半導体にn型を付与する不純物

元素を高濃度にドープするための第2のドーピング工程を行う。この段階での断面図を図

6(A)に示す。マスク619は、画素部のpチャネル型TFTを形成する半導体層のチ

ャネル形成領域及びその周辺の領域と、画素部のnチャネル型TFTの一部と、駆動回路

部のpチャネル型TFTを形成する半導体層のチャネル形成領域及びその周辺の領域と、

を保護するために設ける。

【0078】

第2のドーピング工程におけるイオンドープ法の条件はドーズ量を1×1013〜5×

1015/cm2とし、加速電圧を60〜100keVとして行う。この第2のドーピン

グ工程によって、絶縁膜613を介してドープされてn型の不純物を高濃度に含む第2の

不純物領域(n+領域)620aと、第1の導電層614a及び絶縁膜613を介してド

ープされて第1の導電層614aと重なる第3の不純物領域(n−領域)620bとを形

成する。なお、画素部のnチャネル型TFTは、一部をマスクで覆ったため、チャネル形

成領域と第2の不純物領域620aとの間に、第1の導電層614aと重ならない第1の

不純物領域(n−−領域)618が形成される。また、駆動回路部のnチャネル型TFT

においては、自己整合的にドープされて、第1の導電層614aと重なる第3の不純物領

域620bと第2の不純物領域620aとの境界が、第1の導電層614aの端部と一致

する。

【0079】

次いで、マスク619を除去した後、新たにレジストからなるマスク621を形成し、半

導体にp型を付与する不純物元素(代表的にはボロン)を高濃度にドープするための第3

のドーピング工程を行う。この段階での断面図を図6(B)に示す。マスク621は、画

素部のnチャネル型TFTを形成する半導体層のチャネル形成領域及びその周辺の領域と

、駆動回路部のnチャネル型TFTを形成する半導体層のチャネル形成領域及びその周辺

の領域と、を保護するために設ける。

【0080】

この第3のドーピング工程によって絶縁膜613を介して半導体層にドープを行い、p

型の不純物を高濃度に含む第4の不純物領域(p+領域)622を形成する。尚、第4の

不純物領域622には先の第1のドーピング工程でリン(P)が添加された領域(n−−

領域)であるが、p型を付与する不純物元素の濃度がリン(P)の1.5〜3倍添加され

ていて導電型はp型となっている。

【0081】

この後、レジストマスクを除去する。以上までの工程でそれぞれの半導体層にn型また

はp型の導電型を有する不純物領域が形成される。この段階での断面図を図6(C)に示

す。

【0082】

次いで、スパッタ法、LPCVD法、またはプラズマCVD法等を用いて、水素を含む

絶縁膜640aを成膜した後、半導体層に添加された不純物元素の活性化および水素化を

行う。水素を含む絶縁膜640aは、PCVD法により得られる窒化酸化珪素膜(SiN

O膜)を用いる。ここでは、水素を含む絶縁膜640aの膜厚は、50nm〜200nm

とする。加えて、結晶化を助長する金属元素、代表的にはニッケルを用いて半導体膜を結

晶化させている場合、活性化と同時にチャネル形成領域におけるニッケルの低減を行うゲ

ッタリングをも行うことができる。なお、水素を含む絶縁膜640aは、層間絶縁膜の1

層目であり、酸化珪素を含んでいる。

【0083】

次いで、スパッタ法、LPCVD法、またはプラズマCVD法等を用いて層間絶縁膜の

2層目となる無機絶縁膜640bを形成する。無機絶縁膜640bとしては、酸化シリコ

ン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜の単層または積層を用いる

。ここでは無機絶縁膜640bの膜厚は600nm〜800nmとする。

【0084】

また、無機絶縁膜640bの一層として、塗布法で得られるシロキサン樹脂を用いてもよ

い。なお、シロキサン樹脂とは、Si−O−Si結合を含む樹脂に相当する。シロキサン

は、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少

なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基

として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基

と、フルオロ基とを用いてもよい。

【0085】

次いで、フォトマスクを用いてレジストからなるマスクを形成し、絶縁膜640a、64

0b及び絶縁膜613を選択的にエッチングしてコンタクトホールを形成する。そして、

レジストからなるマスクを除去する。

【0086】

次いで、スパッタ法により金属膜を積層した後、フォトマスクを用いてレジストからな

るマスクを形成し、選択的に金属積層膜をエッチングして、TFTのソース電極またはド

レイン電極として機能する電極641〜647を形成する。そして、レジストからなるマ

スクを除去する。なお、ここでの金属積層膜は、膜厚100nmのTi膜と、膜厚350

nmのSiを微量に含むAl膜と、膜厚100nmのTi膜との3層積層とする。

【0087】

また、電極641〜647の端面は、下方に配置された第1の導電層と第3の導電層の

端面と重ならないように適宜、それぞれの線幅や位置を設定することが好ましい。

【0088】

以上の工程で、同一基板上にポリシリコン膜を活性層とするトップゲート型のTFT63

6、637、638、639が作製でき、この段階での断面図を図6(D)に示す。

【0089】

なお、駆動回路部に配置されるTFT636はゲート電極と重なる低濃度不純物領域(

LDD領域とも呼ぶ)を備えたnチャネル型TFTであり、TFT637はpチャネル型

TFTである。駆動回路部においては、TFT636とTFT637を相補的に接続する

ことでCMOS回路を構成し、様々な種類の回路を実現することができる。

【0090】

また、画素部に配置されるTFT638は、一つのTFTに複数のチャネル形成領域を

有するnチャネル型TFTである。TFT638は、ゲート電極と重ならない低濃度不純

物領域(LDD領域とも呼ぶ)を備えたマルチゲート型のTFTである。また、画素部に

は、後に形成される発光素子と電気的に接続するTFT639が設けられる。ここでは、

TFT639として、シングルゲート型のpチャネル型TFTを示したが、特に限定され

ず、マルチゲート型のTFTとしてもよい。

【0091】

次いで、第1の電極623、即ち、有機発光素子の陽極(或いは陰極)を形成する。第

1の電極623として、仕事関数の大きい材料、例えば、Ni、W、Cr、Pt、Zn、

Sn、InまたはMoから選ばれた元素、または前記元素を主成分とする合金材料、例え

ばTiN、TiSiXNY、WSiX、WNX、WSiXNY、NbNを用いて、単層膜

またはそれらの積層膜を総膜厚100nm〜800nmの範囲で用いればよい。

【0092】

具体的には第1の電極623として、透光性を有する導電性材料からなる透明導電膜を用

いればよく、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジ

ウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸

化物などを用いることができる。勿論、インジウム錫酸化物(ITO)、インジウム亜鉛

酸化物(IZO)、酸化ケイ素を添加したインジウム錫酸化物(ITSO)なども用いる

ことができる。

【0093】

各透光性を有する導電性材料の、組成比例を述べる。酸化タングステンを含むインジ

ウム酸化物の組成比は、酸化タングステン1.0wt%、インジウム酸化物99.0wt

%とすればよい。酸化タングステンを含むインジウム亜鉛酸化物の組成比は、酸化タング

ステン1.0wt%、酸化亜鉛0.5wt%、インジウム酸化物98.5wt%とすれば

よい。酸化チタンを含むインジウム酸化物は、酸化チタン1.0wt%〜5.0wt%、

インジウム酸化物99.0wt%〜95.0wt%とすればよい。インジウム錫酸化物(

ITO)の組成比は、酸化錫10.0wt%、インジウム酸化物90.0wt%とすれば

よい。インジウム亜鉛酸化物(IZO)の組成比は、酸化亜鉛10.7wt%、インジウ

ム酸化物89.3wt%とすればよい。酸化チタンを含むインジウム錫酸化物の組成比は

、酸化チタン5.0wt%、酸化錫10.0wt%、インジウム酸化物85.0wt%と

すればよい。上記組成比は例であり、適宜その組成比の割合は設定すればよい。

【0094】

次いで、塗布法により得られる絶縁膜(例えば、アルキル基を含むSiOx膜や有機樹脂

膜)をパターニングして、第1の電極623の端部を覆う絶縁物629(バンク、隔壁、

障壁、土手などと呼ばれる)を形成する。

【0095】

次いで、有機化合物を含む層624を、蒸着法または塗布法を用いて形成する。次いで

、第2の電極625、即ち、有機発光素子の陰極(或いは陽極)を形成する。第2の電極

625としては、MgAg、MgIn、AlLiなどの合金、または透明導電膜(ITO

など)を用いる。

【0096】

次いで、蒸着法またはスパッタ法により保護層626を形成する。保護層626は、第2

の電極625を保護する。保護層626を通過させて発光素子の発光を取り出す場合、保

護層626には透明な材料とすることが好ましい。なお、必要でなければ保護層626は

設けなくともよい。

【0097】

次いで、封止基板633をシール材628で貼り合わせて発光素子を封止する。即ち、

発光表示装置は、表示領域の外周をシール材で囲み、一対の基板で封止される。TFTの

層間絶縁膜は、基板全面に設けられているため、シール材のパターンが層間絶縁膜の外周

縁よりも内側に描画された場合、シール材のパターンの外側に位置する層間絶縁膜の一部

から水分や不純物が浸入する恐れがある。従って、TFTの層間絶縁膜として用いる絶縁

膜の外周は、シール材のパターンの内側、好ましくは、シール材パターンと重なるように

して絶縁膜の端部をシール材が覆うようにする。なお、シール材628で囲まれた領域に

は充填材627を充填する。或いは、シール材628で囲まれた領域には乾燥した不活性

ガスを充填する。

【0098】

最後にFPC632を異方性導電膜631により公知の方法で端子電極と貼りつける。

(図7)なお、端子電極は、第1の電極623と同じ工程で得られる透明導電膜を端子電

極の最上層に用いることが好ましく、ゲート配線と同時に形成された端子電極の一層とな

る第3の導電層615c上に形成する。

【0099】

以上の工程によって、画素部と駆動回路と端子部とを同一基板上に形成することができる

。

【0100】

本実施の形態において、電極641〜647の端面が、下方に配置された第1の導電層と

第3の導電層の端面と重ならないように適宜、それぞれの線幅や位置を設定されており、

絶縁物629の膜厚が確保されている。従って、膜厚が部分的に薄くなることが防がれて

、電極641〜647と第2の電極625とが重なる部分での短絡発生の防止ができる。

【0101】

また、発光装置において、発光装置の発光表示面は、一面または両面であってもよい。

第1の電極623と第2の電極625とを透明導電膜で形成した場合、発光素子の光は、

基板610及び封止基板633を通過して両側に取り出される。この場合、封止基板63

3や充填材627は透明な材料を用いることが好ましい。

【0102】

また、第2の電極625を金属膜で形成し、第1の電極623を透明導電膜で形成した

場合、発光素子の光は、基板610のみを通過して一方に取り出される構造、即ちボトム

エミッション型となる。この場合、封止基板633や充填材627は透明な材料を用いな

くともよい。

【0103】

また、第1の電極623を金属膜で形成し、第2の電極625を透明導電膜で形成した

場合、発光素子の光は、封止基板633のみを通過して一方に取り出される構造、即ちト

ップエミッション型となる。この場合、基板610は透明な材料を用いなくともよい。

【0104】

また、第1の電極623及び第2の電極625は仕事関数を考慮して材料を選択する必要

がある。但し第1の電極及び第2の電極は、画素構成によりいずれも陽極、又は陰極とな

りうる。駆動用TFTの極性がpチャネル型である場合、第1の電極を陽極、第2の電極

を陰極とするとよい。また、駆動用TFTの極性がNチャネル型である場合、第1の電極

を陰極、第2の電極を陽極とすると好ましい。

【0105】

また、発光装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方

法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法

とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、発光装置のソ

ース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であっても

よく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

【0106】

さらに、ビデオ信号がデジタルの発光装置において、画素に入力されるビデオ信号が定電

圧(CV)のものと、定電流(CC)のものとがある。ビデオ信号が定電圧のもの(CV

)には、発光素子に印加される信号の電圧が一定のもの(CVCV)と、発光素子に印加

される信号の電流が一定のもの(CVCC)とがある。また、ビデオ信号が定電流のもの

(CC)には、発光素子に印加される信号の電圧が一定のもの(CCCV)と、発光素子

に印加される信号の電流が一定のもの(CCCC)とがある。

【0107】

また、発光装置において、静電破壊防止のための保護回路(保護ダイオードなど)を設

けてもよい。

【0108】

また、本実施の形態は、実施の形態1乃至3のいずれか一と自由に組み合わせることが

できる。

【0109】

(実施の形態5)

ここでは、図8を用いて、発光表示パネルにFPCや、駆動用の駆動ICを実装する例に

ついて説明する。

【0110】

図8(A)に示す図は、FPC1209を4カ所の端子部1208に貼り付けた発光装置

の上面図の一例を示している。基板1210上には発光素子及びTFTを含む画素部12

02と、TFTを含むゲート側駆動回路1203と、TFTを含むソース側駆動回路12

01とが形成されている。TFTの活性層が結晶構造を有する半導体膜で構成されており

、同一基板上にこれらの回路を形成している。従って、システムオンパネル化を実現した

EL表示パネルを作製することができる。

【0111】

なお、基板1210はコンタクト部以外において保護膜で覆われており、保護膜上に光触

媒機能を有する物質を含む下地層が設けられている。

【0112】

また、画素部を挟むように2カ所に設けられた接続領域1207は、発光素子の第2の

電極を下層の配線とコンタクトさせるために設けている。なお、発光素子の第1の電極は

画素部に設けられたTFTと電気的に接続している。

【0113】

また、封止基板1204は、画素部および駆動回路を囲むシール材1205、およびシ

ール材に囲まれた充填材料によって基板1210と固定されている。また、透明な乾燥剤

を含む充填材料を充填する構成としてもよい。また、画素部と重ならない領域に乾燥剤を

配置してもよい。

【0114】

また、図8(A)に示した構造は、XGAクラスの比較的大きなサイズ(例えば対角4

.3インチ)の発光装置で好適な例を示したが、図9(B)は、狭額縁化させた小型サイ

ズ(例えば対角1.5インチ)で好適なCOG方式を採用した例である。

【0115】

図8(B)において、基板1310上に駆動IC1301が実装され、駆動ICの先に配

置された端子部1308にFPC1309を実装している。実装される駆動IC1301

は、生産性を向上させる観点から、一辺が300mmから1000mm以上の矩形状の基

板上に複数個作り込むとよい。つまり、基板上に駆動回路部と入出力端子を一つのユニッ

トとする回路パターンを複数個形成し、最後に分割して駆動ICを個別に取り出せばよい

。駆動ICの長辺の長さは、画素部の一辺の長さや画素ピッチを考慮して、長辺が15〜

80mm、短辺が1〜6mmの矩形状に形成してもよいし、画素領域の一辺、又は画素部

の一辺と各駆動回路の一辺とを足した長さに形成してもよい。

【0116】

駆動ICのICチップに対する外形寸法の優位性は長辺の長さにあり、長辺が15〜8

0mmで形成された駆動ICを用いると、画素部に対応して実装するのに必要な数がIC

チップを用いる場合よりも少なくて済み、製造上の歩留まりを向上させることができる。

また、ガラス基板上に駆動ICを形成すると、母体として用いる基板の形状に限定されな

いので生産性を損なうことがない。これは、円形のシリコンウエハからICチップを取り

出す場合と比較すると、大きな優位点である。

【0117】

また、TAB方式を採用してもよく、その場合は、複数のテープを貼り付けて、該テー

プに駆動ICを実装すればよい。COG方式の場合と同様に、単数のテープに単数の駆動

ICを実装してもよく、この場合には、強度の問題から、駆動ICを固定するための金属

片等を一緒に貼り付けるとよい。

【0118】

また、画素部1302と駆動IC1301の間に設けられた接続領域1307は、発光

素子の第2の電極を下層の配線とコンタクトさせるために設けている。なお、発光素子の

第1の電極は画素部に設けられたTFTと電気的に接続している。

【0119】

また、封止基板1304は、画素部1302を囲むシール材1305、およびシール材

に囲まれた充填材料によって基板1310と固定されている。

【0120】

また、画素部のTFTの活性層として非晶質半導体膜を用いる場合には、駆動回路を同

一基板上に形成することは困難であるため、大きなサイズであっても図8(B)の構成と

なる。

【0121】

また、ここでは表示装置としてアクティブマトリクス型の発光装置の例を示したが、ア

クティブマトリクス型の液晶表示装置にも適用できることはいうまでもない。アクティブ

マトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動する

ことによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画

素電極に対応する対向電極との間に電圧が印加されることによって、素子基板に設けられ

た画素電極と対向基板に設けられた対向電極との間に配置された液晶層の光学変調が行わ

れ、この光学変調が表示パターンとして観察者に認識される。対向基板と素子基板は、等

間隔で配置され、液晶材料が充填されている。液晶材料は、シール材を閉パターンとして

気泡が入らないように減圧下で液晶の滴下を行い、両方の基板を貼り合わせる方法を用い

てもよいし、開口部を有するシールパターンを設け、TFT基板を貼りあわせた後に毛細

管現象を用いて液晶を注入するディップ式(汲み上げ式)を用いてもよい。

【0122】

また、カラーフィルタを用いずに、光シャッタを行い、RGBの3色のバックライト光

源を高速で点滅させるフィールドシーケンシャル方式の駆動方法を用いた液晶表示装置に

も本発明は、適用できる。

【0123】

以上の様に、本発明を実施する、即ち実施の形態1乃至4のいずれか一の作製方法また

は構成を用いて、様々な電子機器を完成させることができる。

【0124】

(実施の形態6)

本発明の半導体装置、及び電子機器として、ビデオカメラ、デジタルカメラ等のカメラ、

ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音

響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ

などのパーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携

帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置(具体的には

Digital Versatile Disc(DVD)等の記録媒体を再生し、その

画像を表示しうるディスプレイを備えた装置)などが挙げられる。それら電子機器の具体

例を図9および図10に示す。

【0125】

図9(A)はデジタルカメラであり、本体2101、表示部2102、撮像部、操作キー

2104、シャッター2106等を含む。なお、図9(A)は表示部2102側からの図

であり、撮像部は示していない。本発明により、信頼性の高いデジタルカメラが実現でき

る。

【0126】

図9(B)はノート型パーソナルコンピュータであり、本体2201、筐体2202、表

示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2

206等を含む。本発明により、信頼性の高いノート型パーソナルコンピュータを実現す

ることができる。

【0127】

図9(C)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であ

り、本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体(D

VD等)読込部2405、操作キー2406、スピーカー部2407等を含む。表示部A

2403は主として画像情報を表示し、表示部B2404は主として文字情報を表示する

。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明に

より、信頼性の高い画像再生装置を実現することができる。

【0128】

また、図9(D)は表示装置であり、筐体1901、支持台1902、表示部1903、

スピーカ1904、ビデオ入力端子1905などを含む。この表示装置は、上述した実施

の形態で示した作製方法により形成した薄膜トランジスタをその表示部1903および駆

動回路に用いることにより作製される。なお、表示装置には液晶表示装置、発光装置など

があり、具体的にはコンピュータ用、テレビ受信用、広告表示用などの全ての情報表示用

表示装置が含まれる。本発明により、信頼性の高い表示装置、特に22インチ〜50イン

チの大画面を有する大型の表示装置を実現することができる。

【0129】

図10で示す携帯電話機は、操作スイッチ類904、マイクロフォン905などが備えら

れた本体(A)901と、表示パネル(A)908、表示パネル(B)909、スピーカ

906などが備えられた本体(B)902とが、蝶番910で開閉可能に連結されている

。表示パネル(A)908と表示パネル(B)909は、回路基板907と共に本体(B

)902の筐体903の中に収納される。表示パネル(A)908及び表示パネル(B)

909の画素部は筐体903に形成された開口窓から視認できるように配置される。

【0130】

表示パネル(A)908と表示パネル(B)909は、その携帯電話機900の機能に

応じて画素数などの仕様を適宜設定することができる。例えば、表示パネル(A)908

を主画面とし、表示パネル(B)909を副画面として組み合わせることができる。

【0131】

本発明により、信頼性の高い携帯情報端末を実現することができる。

【0132】

本実施の形態に係る携帯電話機は、その機能や用途に応じてさまざまな態様に変容し得

る。例えば、蝶番910の部位に撮像素子を組み込んで、カメラ付きの携帯電話機として

も良い。また、操作スイッチ類904、表示パネル(A)908、表示パネル(B)90

9を一つの筐体内に納めた構成としても、上記した作用効果を奏することができる。また

、表示部を複数個そなえた情報表示端末に本実施の形態の構成を適用しても、同様な効果

を得ることができる。

【0133】

以上の様に、本発明を実施する、即ち実施の形態1乃至5のいずれか一の作製方法また

は構成を用いて、様々な電子機器を完成させることができる。

【産業上の利用可能性】

【0134】

本発明は、半導体装置の製造時および製造後の短絡発生を効果的に防止することができ

るため、有用である。

【符号の説明】

【0135】

10 ガラス基板

11 第1の絶縁層

12 第1の配線

13 第2の配線

14 金属層

15 第2の絶縁層

16 第3の絶縁層

17a チタン層

17b アルミニウム層

18 第4の絶縁層

20 ガラス基板

21 ゲートメタル層

22 第1の絶縁層

23a 第1のチタン膜

23b アルミニウム膜

23c 第2のチタン膜

24 第2の絶縁層

25 上部電極

31 第2の配線

32 第2の配線

33 電極

34 電極

41 第1の配線

42 第1の配線

50 第1の電極層

51 薄膜トランジスタ

52 薄膜トランジスタ

53 ゲート配線層

54 ソース配線層又はドレイン配線層

55 電源線

56a 導電層

56b 導電層

56c 導電層

56d 導電層

57 導電層

58 ソース電極層又はドレイン電極層

60 ガラス基板

61 ゲートメタル層

62 第1の絶縁層

63a 第1のチタン膜

63b アルミニウム膜

63c 第2のチタン膜

64 第2の絶縁層

65 上部電極

610 基板

611 下地絶縁膜

612 半導体層

613 絶縁膜

614a 第1の導電層

614b 第2の導電層

614c 第3の導電層

615a 第1の導電層

615b 第2の導電層

615c 第3の導電層

616 マスク

617 タングステンを含む薄い膜

618 第1の不純物領域

619 マスク

620a 第2の不純物領域

620b 第3の不純物領域

621 マスク

622 第4の不純物領域

623 第1の電極

624 有機化合物を含む層

625 第2の電極

626 保護層

627 充填材

628 シール材

629 絶縁物

631 異方性導電膜

632 FPC

636 nチャネル型TFT

637 pチャネル型TFT

638 nチャネル型TFT

639 pチャネル型TFT

640a 水素を含む絶縁膜

640b 無機絶縁膜

641 電極

642 電極

643 電極

644 電極

645 電極

646 電極

647 電極

900 携帯電話機

901 本体(A)

902 本体(B)

903 筐体

904 操作スイッチ類

905 マイクロフォン

906 スピーカ

907 回路基板

908 表示パネル(A)

909 表示パネル(B)

910 蝶番

1201 ソース側駆動回路

1202 画素部

1203 ゲート側駆動回路

1204 封止基板

1205 シール材

1207 接続領域

1208 端子部

1209 FPC

1210 基板

1301 駆動IC

1302 画素部

1304 封止基板

1305 シール材

1307 接続領域

1308 端子部

1309 FPC

1901 筐体

1902 支持台

1903 表示部

1904 スピーカ

1905 ビデオ入力端子

2101 本体

2102 表示部

2104 操作キー

2106 シャッター

2201 本体

2202 筐体

2203 表示部

2204 キーボード

2205 外部接続ポート

2206 ポインティングマウス

2401 本体

2402 筐体

2403 表示部A

2404 表示部B

2405 記録媒体読込部

2406 操作キー

2407 スピーカー部

【技術分野】

【0001】

本発明は薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装

置およびその作製方法に関する。例えば、液晶表示パネルに代表される電気光学装置や有

機発光素子もしくは無機発光素子を有する発光表示装置を部品として搭載した電子機器に

関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装

置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

近年、絶縁表面を有する基板上に形成された半導体薄膜(厚さ数〜数百nm程度)を用

いて薄膜トランジスタ(TFT)を構成する技術が注目されている。薄膜トランジスタは

ICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチ

ング素子として開発が急がれている。

【0004】

また、薄型軽量、高速応答性、直流低電圧駆動などの特徴を有する有機化合物を発光体と

して用いた発光素子は、次世代のフラットパネルディスプレイへの応用が期待されている

。特に、発光素子をマトリクス状に配置した表示装置は、視野角が広く視認性が優れてい

る。

【0005】

絶縁表面を有する基板上に薄膜トランジスタをマトリクス状に配置した発光表示装置は、

配線や電極によって基板表面に凹凸が形成される。その上に塗布法で絶縁膜を形成すると

均一な膜厚を保持することが困難となる。また、塗布法で成膜する際の遠心力によって、

凸部上の膜厚が薄くなる。すると、凸部上において絶縁膜の膜厚が薄くなった部分での耐

圧が低下されるという問題がある。

【0006】

また、絶縁膜の耐圧を高くしようとして単純に膜厚を厚くすると、絶縁膜全体の応力が増

加し、絶縁膜の剥離や、基板の反りが生じる恐れがあった。

【0007】

また、薄膜トランジスタをマトリクス状に配置した発光表示装置は、特許文献1に記載

された構成、具体的には隣接する画素の間に絶縁膜を設ける構造としている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−164181号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ、薄膜ト

ランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の上方に設

けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比べて大き

な段差が形成される。

【0010】

隣接する画素の間に設ける絶縁膜を塗布法で形成した場合においても、この段差の影響を

受けて、部分的に薄くなる箇所が形成され、その箇所の耐圧が低下されるという問題があ

る。

【0011】

本発明は、以上の問題点を鑑みてなされたもので、絶縁膜の膜厚が薄くとも高い絶縁特

性や、高い耐圧を備えた信頼性の高い発光装置を実現することを目的とする。

【課題を解決するための手段】

【0012】

本発明では、段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その

上に形成される絶縁膜の凹凸形状を緩和するものである。

【0013】

また、上方配線の端部と下方配線の端部を一致させると、部分的に薄くなる箇所が形成

される傾向が見られることから、上方配線の端部と下方配線の端部とが一致しないように

、上方配線と下方配線の位置をずらして配置することも本発明の特徴の一つである。また

、上方配線の端部と下方配線の端部とが一致しないように、下方配線の配線幅よりも上方

配線の配線幅を太くして配置することも本発明の特徴の一つである。

【0014】

特に、基板上方から見て上方配線と下方配線とを平行に配置する場合、上方配線の側面

と下方配線の側面とが一致しないようにすることが好ましい。

【0015】

また、下方配線の形成において、テーパー形状を有する断面とし、配線幅を細くするエ

ッチングを行うことが好ましい。即ち、下方配線の形成時にテーパー形状を有する断面と

し、配線幅を細くするエッチングを行うと、設計マスクでは上方配線の端部と下方配線の

端部とが一致していても、実際に形成すると、上方配線の端部と下方配線の端部とが一致

しないようにすることができる。

【0016】

また、塗布時(常温)において、粘度が10cp(センチポイズ)以上60cp(セン

チポイズ)以下を有する絶縁材料液を塗布し、乾燥させることで、段差部でも均一な膜厚

の絶縁膜を得ることもできる。

【0017】

本発明により、絶縁膜を挟む2つの配線(上方配線、下方配線)間の絶縁性及び耐圧を

飛躍的に改善できる。

【0018】

上述したこれらの手段は単なる設計事項ではなく、発光装置を作製し、画像表示させ、

発明者らの深い検討の後、発明された事項である。

【0019】

本明細書で開示する発明の構成は、絶縁表面上に第1の配線、第2の配線、及び金属層

と、前記第1の配線、前記第2の配線、及び前記金属層を覆う第1の絶縁層と、前記第1

の絶縁層上に前記第2の配線と接続する電極と、前記第1の絶縁層、前記電極、前記金属

層、前記第1の配線、及び前記第2の配線を覆う第2の絶縁層とを有し、前記金属層およ

び前記第2の配線は、前記第1の配線と同じ材料であり、前記電極は、前記金属層と前記

第1の配線との間に配置されることを特徴とする半導体装置である。

【0020】

また、本明細書で開示する発明の構成は、絶縁表面上に第1の配線、及び第2の配線と

、前記第1の配線、及び前記第2の配線を覆う第1の絶縁層と、前記第1の絶縁層上に前

記第2の配線と接続する第1の電極、電気的にフローティング状態である金属層と、第2

の電極と、前記第1の絶縁層、前記第1の電極、前記金属層、前記第1の配線、及び前記

第2の配線を覆う第2の絶縁層と、前記第2の電極上に発光層と、前記発光層上に第3の

電極とを有し、前記第2の配線は、前記第1の配線と同じ材料であり、前記金属層は、前

記第1の電極と同じ材料であり、前記第1の電極は、前記金属層と前記第1の配線との間

に配置されることを特徴とする半導体装置である。

上記構成において、前記第2の電極と、前記第3の電極と、前記発光層とが重なる箇所

で発光素子を構成することを特徴の一つとしている。

【0021】

なお、発光素子は、電場を加えることで発生するルミネッセンス(Electro Lu

minescence)が得られる有機化合物を含む層(以下、EL層と記す)と、陽極

と、陰極とを有する。有機化合物におけるルミネッセンスには、一重項励起状態から基底

状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)と

があるが、本発明は、どちらの発光を用いた場合にも適用可能である。

【0022】

また、上記構成において、前記第2の絶縁層は、第2の電極の周縁部を覆う隔壁である

ことを特徴の一つとしている。

【0023】

また、上記構成において、前記金属層は、電気的にフローティング状態の電極であるこ

とを特徴の一つとしている。

【0024】

また、上記構成において、前記半導体装置は、前記第1の配線をゲート電極とする第1

の薄膜トランジスタと前記第2の配線をゲート電極とする第2の薄膜トランジスタとを有

することを特徴とする半導体装置である。

【0025】

また、薄膜トランジスタ(TFTとも呼ぶ)のチャネル形成領域としては、非晶質半導体

膜、結晶構造を含む半導体膜、非晶質構造を含む化合物半導体膜などを適宜用いることが

できる。さらにTFTのチャネル形成領域として、非晶質と結晶構造(単結晶、多結晶を

含む)の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であ

って、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいるセミアモルファス半

導体膜(微結晶半導体膜、マイクロクリスタル半導体膜とも呼ばれる)も用いることがで

きる。

【0026】

また、上記構成において、前記第2の絶縁層は、溶媒を含み、且つ、粘度が10cp以上

60cp以下の材料を用いた塗布法により形成することを特徴の一つとしている。

【0027】

また、本発明の半導体装置において、静電破壊防止のための保護回路(保護ダイオード

など)を設けてもよい。

【0028】

また、本発明の半導体装置において、発光素子をマトリクス状に配置した発光装置を備え

る場合、その発光装置における画面表示の駆動方法は特に限定されず、例えば、点順次駆

動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動

方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、発光装置

のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であっ

てもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

【0029】

さらに、ビデオ信号がデジタルの発光装置において、画素に入力されるビデオ信号が定電

圧(CV)のものと、定電流(CC)のものとがある。ビデオ信号が定電圧のもの(CV

)には、発光素子に印加される信号の電圧が一定のもの(CVCV)と、発光素子に印加

される信号の電流が一定のもの(CVCC)とがある。また、ビデオ信号が定電流のもの

(CC)には、発光素子に印加される信号の電圧が一定のもの(CCCV)と、発光素子

に印加される信号の電流が一定のもの(CCCC)とがある。

【発明の効果】

【0030】

本発明により、塗布法によって得られる絶縁膜を層間に用いた場合において、異なる層

に設けられた配線間の短絡の発生を効果的に防止することができる。従って、半導体装置

の製造における歩留まりが向上する。また、製造後の半導体装置の信頼性を向上すること

もできる。

【図面の簡単な説明】

【0031】

【図1】発光装置の画素の一部を示す上面図及び断面図。(実施の形態1)

【図2】配線付近の断面の写真および模式図。(実施の形態2)

【図3】画素のレイアウトの一例を示す上面図。(実施の形態2)

【図4】画素のレイアウトの一例を示す上面図。(実施の形態3)

【図5】発光装置の作製工程を示す図。(実施の形態4)

【図6】発光装置の作製工程を示す図。(実施の形態4)

【図7】発光装置の作製工程を示す図。(実施の形態4)

【図8】アクティブマトリクス型EL表示装置の構成を示す図。(実施の形態5)

【図9】電子機器の一例を示す図。(実施の形態6)

【図10】電子機器の一例を示す図。(実施の形態6)

【図11】比較例を示す図。

【図12】発光装置の画素の一部を示す上面図及び断面図。(実施の形態1)

【発明を実施するための形態】

【0032】

本発明の実施形態について、以下に説明する。但し、本発明は以下の説明に限定されず

、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得る

ことは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載

内容に限定して解釈されるものではない。

【0033】

(実施の形態1)

本実施の形態では、ダミー部材を設けることによって、ダミー部材上方に設ける絶縁層

が部分的に薄くなる箇所の形成を防止する例を図1(A)及び図1(B)を用いて説明す

る。

【0034】

図1(A)は、発光装置の画素の一部を示す上面図であり、鎖線A−Bで切断した断面

図が図1(B)である。

【0035】

まず、図1(A)、および図1(B)に示す構造を得る手順を説明する。

【0036】

絶縁表面を有するガラス基板10上に第1の絶縁層11を形成し、その上に第1の配線1

2、第2の配線13、金属層14を形成する。金属層14は導電層でもよい。なお、金属

層14は、ダミー部材として機能させており、電気的に浮遊状態の電極、即ち、フローテ

ィング電極と言える。また、第1の絶縁層は、薄膜トランジスタのゲート絶縁膜としても

機能する。また、第1の配線12、第2の配線13、金属層14と同一工程で、薄膜トラ

ンジスタのゲート電極を形成する。

【0037】

次いで、これらの配線や金属層を覆う第2の絶縁層15、第3の絶縁層16を積層形成

する。

【0038】

次いで、マスクを用いて第2の絶縁層15、及び第3の絶縁層16を選択的にエッチン

グして第2の配線13に達するコンタクトホールを形成する。

【0039】

次いで、金属材料からなる第1の電極を形成する。ここでは、第1の電極をチタン層1

7aとアルミニウム層17bとの積層で構成している。また、この第1の電極と同一工程

で薄膜トランジスタのソース電極やドレイン電極を形成する。

【0040】

次いで、第3の絶縁層16上に第2の電極を形成する。なお、第2の電極は、薄膜トラ

ンジスタのソース電極やドレイン電極と電気的に接続する。

【0041】

次いで、溶媒を含む絶縁材料を用いて塗布法により、第4の絶縁層18を形成する。こ

こまでの段階を終えた時点で図1(A)及び図1(B)の状態が得られる。

【0042】

なお、図1(B)は、発光装置の作製途中の図であり、さらに第4の絶縁層18の上方に

有機化合物または無機化合物を含む発光層72と、第3の電極73とが積層形成される。

また、第3の電極73形成直後の断面図を図12(B)に示す。発光素子は、第2の電極

71と、有機化合物または無機化合物を含む発光層72と、第3の電極73とで構成され

る。特に、アルミニウム層17bの上端部と第3の電極73とで短絡が生じる恐れがある

。本実施の形態では、ダミー部材である金属層14を配置することによって、第4の絶縁

層18の膜厚が部分的に薄くなることを防いでいる。また、図1(A)よりも広範囲に画

素を示した上面図を図12(A)に示す。ソース線75は、第1の半導体層19を活性層

とする薄膜トランジスタに電気的に接続している。第1の半導体層19は、コンタクトホ

ールを介して第1の電極と電気的に接続している。また、第1の電極は、コンタクトホー

ルを介して第2の配線13と電気的に接続している。また、第2の配線13は、第2の絶

縁層15を介して第2の半導体層77と重なるゲート電極として機能する。第2の半導体

層77は、電源線78及び、接続電極76と電気的に接続している。また、接続電極76

は第2の電極71と電気的に接続している。なお、接続電極76とソース線75と電源線

78は第1の電極と同じ材料で形成されている。第4の絶縁層18は、第2の電極71の

端部を覆う隔壁として機能し、第4の絶縁層の周縁を図12(A)中の符号74に示す。

図12(A)に示すように、本発明は、金属層14を第2の配線13と重なっている第1

の電極と、第4の絶縁層の周縁74との間に配置することで、第4の絶縁層の膜厚が部分

的に薄くなることを防いでいる。

【0043】

また、第1の配線12も第4の絶縁層18の凹凸形状を緩和させる機能を有している。本

実施の形態1では、第1の電極を囲むように所定の間隔で第1の配線12及び金属層14

を配置することによって、第4の絶縁層18の凹凸形状を緩和させている。

【0044】

また、金属層14の上面形状をL字形状としているが特に限定されず、複数の矩形形状

としてもよい。

【0045】

(実施の形態2)

本実施の形態では、上方配線の端部と下方配線の端部を一致させないように各配線を設け

る例を図2(A)、図2(B)、及び図3を用いて説明する。

【0046】

実際に、上方配線の端部と下方配線の端部の位置を異ならせたレイアウトで発光装置を

形成し、その一部の断面写真が図2(A)である。なお、図2(A)に対応する模式図を

図2(B)に示す。

【0047】

図2(B)において、ガラス基板20上にゲートメタル層21、第1の絶縁層22、第

1のチタン膜23a、アルミニウム膜23b、第2のチタン膜23c、第2の絶縁層24

が設けられている。第2の絶縁層24上には発光素子を形成する有機化合物を含む層と上

部電極25が形成される。なお、図2(B)において、発光素子の下部電極は図示してい

ない。

【0048】

また、比較例として、上方配線の端部と下方配線の端部を一致させたレイアウトで発光

装置を形成し、その一部の断面写真が図11(A)である。なお、図11(A)に対応す

る模式図を図11(B)に示す。図11(B)において、ガラス基板60上にゲートメタ

ル層61、第1の絶縁層62、第1のチタン膜63a、アルミニウム膜63b、第2のチ

タン膜63c、第2の絶縁層64が設けられている。第2の絶縁層64上には発光素子を

形成する有機化合物を含む層と上部電極65が形成される。なお、図11(B)において

、発光素子の下部電極は図示していない。図11(A)に示したように、上方配線(63

a〜63c)の端部と下方配線(ゲートメタル層61)の端部を一致させた場合、上方配

線の上端部で第2の絶縁層64の膜厚が薄くなり、最も薄い所で約0.1μmの膜厚とな

ってしまう。上方配線が配置されていない領域での第2の絶縁層64の膜厚は、約1μm

であるため、結果として部分的に第2の絶縁層64の膜厚が10倍異なっている。

【0049】

一方、図2(A)に示したように、上方配線(23a〜23c)の端部と下方配線(ゲー

トメタル層21)の端部の位置を異ならせた場合、上方配線の上端部と上部電極25との

間隔を広げることができる。上方配線が配置されていない領域での第2の絶縁層24の膜

厚は、第2の絶縁層64と同じ約1μmであるが、第2の絶縁層24の最も薄い所で約0

.2μm以上の膜厚とすることができている。

【0050】

また、画素のレイアウトの一例を図3に示す。

【0051】

図3において、絶縁表面上には、半導体層(図3中において点線で囲まれた領域)が形

成され、その上にゲート絶縁膜が形成され、さらにその上に第1の配線41、42が同時

に形成されている。そして、第1の配線上に層間絶縁膜が1層または2層形成され、層間

絶縁膜上に第2の配線31、32および電極33、34が同時に形成されている。なお、

電極33は2つのTFTを接続する接続電極である。また、電極34は、発光素子の陰極

または陽極のうち、一方の電極と接続する電極である。

【0052】

図3では2つの配線が交差する部分、重なる部分があるが、配線の端部、即ち配線側面が

、異なる配線の側面と一致しないように配置している。具体的には、第2の配線32に比

べて、第1の配線41、42は配線幅が狭くなっており、且つ、第2の配線32の配線側

面と第1の配線41の配線側面が一致しないように配置され、第2の配線32の配線側面

と第1の配線42の配線側面が一致しないように配置されている。

【0053】

図3に示す配線のレイアウト配置とすることにより、これらの配線上に塗布法で絶縁膜

を形成した場合、絶縁膜の膜厚が部分的に薄くなることを防ぐことができる。従って、こ

の絶縁膜をパターニングして得られる絶縁物(隣り合う発光素子との間に設ける隔壁)は

、電極間の短絡を防止することができる。

【0054】

また、本実施の形態は、実施の形態1と自由に組み合わせることができる。

【0055】

(実施の形態3)

本実施の形態では、実施の形態1と実施の形態2とを組み合わせた画素構成について図4

を用いて説明する。

【0056】

表示装置の画素領域に有する1画素の上面図を図4に示す。図4において、画素は、薄膜

トランジスタ51、薄膜トランジスタ52、第1の電極層50、ゲート配線層53、ソー

ス配線層又はドレイン配線層54、電源線55、導電層56a、導電層56b、導電層5

6c、導電層56dから構成されている。薄膜トランジスタ52の有するソース電極層又

はドレイン電極層58は、ゲート配線層53と同材料、同工程で作製される導電層57を

介して、第1の電極層50と電気的に接続している。

【0057】

導電層56a、導電層56b、導電層56c、導電層56dは、ソース配線層又はドレイ

ン配線層54、及び電源線55と同材料、同工程で形成されており、配線の積層による膜

厚の急激な変化を緩和するために設けられている。この導電層56a、導電層56b、導

電層56c、導電層56dは、他の配線とは電気的に絶縁されている。ゲート配線層53

と、ソース配線層又はドレイン配線層54又は電源線55との交差する領域では配線層が

積層するため、急激に膜厚が大きくなるが、交差する領域の周囲に導電層56a、導電層

56b、導電層56c、導電層56dを設けることで、その上に形成される隔壁として機

能する絶縁層の被覆性が向上し、膜厚の凹凸に起因する形成不良を防ぐことができる。導

電層56aの一部は、ゲート配線層53と重なっている。寄生容量の増大を防ぐため、導

電層56b、導電層56c、及び導電層56dは間隔を空けてゲート配線層53と重ねて

いる。また、隔壁となる絶縁膜は、第1の電極層50の端部を覆うように形成され、隔壁

となる絶縁膜の周縁を図4(A)中の59に示す。図4(B)に図4(A)中の線A−B

で切断した図を示す。図4(B)に示すように導電層56aは、隔壁となる絶縁膜の膜厚

が部分的に薄くなることを防ぐため、隔壁となる絶縁膜の周縁59と薄膜トランジスタ5

2のゲート電極との間に配置されている。

【0058】

また、同材料、同工程で形成されている導電層の端面と、ゲート配線層の端面とが一致

しないように配線を配置することで、隔壁となる絶縁膜の膜厚が部分的に薄くなることを

防ぐことができる。

【0059】

よって、生産性も向上し、信頼性の高い表示装置を歩留まり良く作製することができる。

【0060】

(実施の形態4)

本実施の形態では、アクティブマトリクス型の発光装置の作製方法について、図5、図6

、及び図7を用いて以下に説明する。

【0061】

まず、基板610上に下地絶縁膜611を形成する。基板610側を表示面として発光を

取り出す場合、基板610としては、光透過性を有するガラス基板や石英基板を用いれば

よい。また、処理温度に耐えうる耐熱性を有する光透過性のプラスチック基板を用いても

よい。また、基板610側とは逆の面を表示面として発光を取り出す場合、前述の基板の

他にシリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用い

ても良い。ここでは基板610としてガラス基板を用いる。なお、ガラス基板の屈折率は

1.55前後である。

【0062】

下地絶縁膜611としては、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜

などの絶縁膜から成る下地膜を形成する。ここでは下地膜として単層構造を用いた例を示

すが、前記絶縁膜を2層以上積層させた構造を用いても良い。なお、基板の凹凸や、基板

からの不純物拡散が問題にならないのであれば、特に下地絶縁膜を形成しなくてもよい。

【0063】

次いで、下地絶縁膜上に半導体層612を形成する。半導体層612は、非晶質構造を

有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)

により成膜した後、公知の結晶化処理(レーザー結晶化法、熱結晶化法、またはニッケル

などの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体膜を第1のフォトマス

クを用いて所望の形状にパターニングして、半導体層612を形成する。なお、プラズマ

CVD法を用いれば、下地絶縁膜と、非晶質構造を有する半導体膜とを大気に触れること

なく連続的に積層することができる。この半導体膜の厚さは25〜80nm(好ましくは

30〜70nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくは

シリコンまたはシリコンゲルマニウム(SiGe)合金などで形成すると良い。

【0064】

また、非晶質構造を有する半導体膜の結晶化処理として連続発振のレーザーを用いてもよ

く、非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためには、連続発振が可能な固

体レーザを用い、基本波の第2高調波〜第4高調波を適用するのが好ましい。代表的には

、Nd:YVO4レーザー(基本波1064nm)の第2高調波(532nm)や第3高

調波(355nm)を適用すればよい。連続発振のレーザーを用いる場合には、出力10

Wの連続発振のYVO4レーザから射出されたレーザ光を非線形光学素子により高調波に

変換する。また、共振器の中にYVO4結晶と非線形光学素子を入れて、高調波を射出す

る方法もある。そして、好ましくは光学系により照射面にて矩形状または楕円形状のレー

ザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01〜100M

W/cm2程度(好ましくは0.1〜10MW/cm2)が必要である。そして、10〜

2000cm/s程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射すれ

ばよい。

【0065】

次いで、レジストマスクを除去する。次いで、必要があればTFTのしきい値を制御す

るために、微量な不純物元素(ボロンまたはリン)のドーピングを半導体層に対して行う

。ここでは、ジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法

を用いる。

【0066】

次いで、フッ酸を含むエッチャントで半導体層表面の酸化膜を除去すると同時に半導体

層の表面を洗浄する。

【0067】

そして、半導体層を覆う絶縁膜613を形成する。絶縁膜613はプラズマCVD法また

はスパッタ法を用い、厚さを1〜200nmとする。好ましくは10nm〜50nmと薄

くしてシリコンを含む絶縁膜の単層または積層構造で形成した後にマイクロ波によるプラ

ズマを用いた表面窒化処理を行う。絶縁膜613は、後に形成されるTFTのゲート絶縁

膜として機能する。

【0068】

次いで、絶縁膜613上に膜厚20〜100nmの第1の導電膜と、膜厚100〜400

nmの第2の導電膜とを積層形成する。本実施の形態では、絶縁膜613上に膜厚50n

mの窒化タンタル膜、膜厚370nmのタングステン膜を順次積層し、以下に示す手順で

パターニングを行って各ゲート電極及び各配線を形成する。

【0069】

なお、ここでは導電膜をTaN膜とW膜との積層としたが、特に限定されず、Ta、W、

Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料若し

くは化合物材料の単層、またはこれらの積層で形成してもよい。また、リン等の不純物元

素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。また、2層

構造に限定されず、例えば、膜厚50nmのタングステン膜、膜厚500nmのアルミニ

ウムとシリコンの合金(Al−Si)膜、膜厚30nmの窒化チタン膜を順次積層した3

層構造としてもよい。

【0070】

上記第1の導電膜及び第2の導電膜のエッチング(第1のエッチング処理および第2の

エッチング処理)にはICP(Inductively Coupled Plasma

:誘導結合型プラズマ)エッチング法を用いると良い。ICPエッチング法を用い、エッ

チング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基

板側の電極温度等)を適宜調節することによって所望のテーパー形状に膜をエッチングす

ることができる。

【0071】

ここでは、レジストからなるマスクを形成した後、第1のエッチング条件として1Paの

圧力でコイル型の電極に700WのRF(13.56MHz)電力を投入し、エッチング

用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を25:25:10(s

ccm)とし、基板側(試料ステージ)にも150WのRF(13.56MHz)電力を

投入し、実質的に負の自己バイアス電圧を印加する。なお、基板側の電極面積サイズは、

12.5cm×12.5cmであり、コイル型の電極面積サイズ(ここではコイルの設け

られた石英円板)は、直径25cmの円板である。この第1のエッチング条件によりW膜

をエッチングして端部をテーパー形状とする。この後、レジストからなるマスク616を

除去せずに第2のエッチング条件に変え、エッチング用ガスにCF4とCl2とを用い、

それぞれのガス流量比を30:30(sccm)とし、1Paの圧力でコイル型の電極に

500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度の

エッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電

力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した第2

のエッチング条件ではW膜及びTaN膜とも同程度にエッチングされる。なお、ここでは

、第1のエッチング条件及び第2のエッチング条件を第1のエッチング処理と呼ぶことと

する。

【0072】

第1のエッチング処理が終わった段階での断面図を図5(A)に示す。この段階で第1

の導電層614aを下層とし、第2の導電層614bを上層とするゲート電極および配線

が形成され、また、第1の導電層615aを下層とし、第2の導電層615bを上層とす

る端子電極が形成される。

【0073】

次いで、レジストからなるマスク616を除去せずに第2のエッチング処理を行う。こ

こでは、第3のエッチング条件としてエッチング用ガスにCF4とCl2とを用い、それ

ぞれのガス流量比を30:30(sccm)とし、1Paの圧力でコイル型の電極に50

0WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを60秒

行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、

実質的に負の自己バイアス電圧を印加する。この後、レジストからなるマスクを除去せず

に第4のエッチング条件に変え、エッチング用ガスにCF4とCl2とO2とを用い、そ

れぞれのガス流量比を20:20:20(sccm)とし、1Paの圧力でコイル型の電

極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約20秒程

度のエッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz

)電力を投入し、実質的に負の自己バイアス電圧を印加する。なお、ここでは、第3のエ

ッチング条件及び第4のエッチング条件を第2のエッチング処理と呼ぶこととする。第2

のエッチング処理によって、第3の導電層614c、615cが形成される。次いで、レ

ジストからなるマスクを除去する。

【0074】

上記第2のエッチング処理の際、またはレジストからなるマスクの除去の際、タングス

テン(W)を含む薄い膜(膜厚は約10nm)を形成する。この段階での断面図を図5(

B)に示す。

【0075】

次いで、n型を付与する不純物元素を半導体層に添加するため、ゲート電極をマスクと

して全面にドーピングする第1のドーピング処理を行う。第1のドーピング処理はイオン

ドープ法、もしくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を1.

5×1013atoms/cm2とし、加速電圧を50〜100keVとして行う。n型

を付与する不純物元素として、典型的にはリン(P)または砒素(As)を用いる。この

第1のドーピング工程によって絶縁膜613およびタングステンを含む薄い膜617を介

してドープを行い、自己整合的に第1の不純物領域(n−−領域)618を形成する。こ

の段階での断面図を図5(C)に示す。なお、タングステンを含む薄い膜が設けられてい

るため、第1の導電層614aと重なる部分の半導体層にはn型を付与する不純物元素が

ほとんど添加されない。また、タングステンを含む薄い膜により、n型を付与する不純物

元素が第1の導電層614aの端部を回り込んで添加されることも防ぐことができる。

【0076】

次いで、タングステンを含む薄い膜617を除去する。

【0077】

次いで、レジストからなるマスク619を形成した後、半導体にn型を付与する不純物

元素を高濃度にドープするための第2のドーピング工程を行う。この段階での断面図を図

6(A)に示す。マスク619は、画素部のpチャネル型TFTを形成する半導体層のチ

ャネル形成領域及びその周辺の領域と、画素部のnチャネル型TFTの一部と、駆動回路

部のpチャネル型TFTを形成する半導体層のチャネル形成領域及びその周辺の領域と、

を保護するために設ける。

【0078】

第2のドーピング工程におけるイオンドープ法の条件はドーズ量を1×1013〜5×

1015/cm2とし、加速電圧を60〜100keVとして行う。この第2のドーピン

グ工程によって、絶縁膜613を介してドープされてn型の不純物を高濃度に含む第2の

不純物領域(n+領域)620aと、第1の導電層614a及び絶縁膜613を介してド

ープされて第1の導電層614aと重なる第3の不純物領域(n−領域)620bとを形

成する。なお、画素部のnチャネル型TFTは、一部をマスクで覆ったため、チャネル形

成領域と第2の不純物領域620aとの間に、第1の導電層614aと重ならない第1の

不純物領域(n−−領域)618が形成される。また、駆動回路部のnチャネル型TFT

においては、自己整合的にドープされて、第1の導電層614aと重なる第3の不純物領

域620bと第2の不純物領域620aとの境界が、第1の導電層614aの端部と一致

する。

【0079】

次いで、マスク619を除去した後、新たにレジストからなるマスク621を形成し、半

導体にp型を付与する不純物元素(代表的にはボロン)を高濃度にドープするための第3

のドーピング工程を行う。この段階での断面図を図6(B)に示す。マスク621は、画

素部のnチャネル型TFTを形成する半導体層のチャネル形成領域及びその周辺の領域と

、駆動回路部のnチャネル型TFTを形成する半導体層のチャネル形成領域及びその周辺

の領域と、を保護するために設ける。

【0080】

この第3のドーピング工程によって絶縁膜613を介して半導体層にドープを行い、p

型の不純物を高濃度に含む第4の不純物領域(p+領域)622を形成する。尚、第4の

不純物領域622には先の第1のドーピング工程でリン(P)が添加された領域(n−−

領域)であるが、p型を付与する不純物元素の濃度がリン(P)の1.5〜3倍添加され

ていて導電型はp型となっている。

【0081】

この後、レジストマスクを除去する。以上までの工程でそれぞれの半導体層にn型また

はp型の導電型を有する不純物領域が形成される。この段階での断面図を図6(C)に示

す。

【0082】

次いで、スパッタ法、LPCVD法、またはプラズマCVD法等を用いて、水素を含む

絶縁膜640aを成膜した後、半導体層に添加された不純物元素の活性化および水素化を

行う。水素を含む絶縁膜640aは、PCVD法により得られる窒化酸化珪素膜(SiN

O膜)を用いる。ここでは、水素を含む絶縁膜640aの膜厚は、50nm〜200nm

とする。加えて、結晶化を助長する金属元素、代表的にはニッケルを用いて半導体膜を結

晶化させている場合、活性化と同時にチャネル形成領域におけるニッケルの低減を行うゲ

ッタリングをも行うことができる。なお、水素を含む絶縁膜640aは、層間絶縁膜の1

層目であり、酸化珪素を含んでいる。

【0083】

次いで、スパッタ法、LPCVD法、またはプラズマCVD法等を用いて層間絶縁膜の

2層目となる無機絶縁膜640bを形成する。無機絶縁膜640bとしては、酸化シリコ

ン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜の単層または積層を用いる

。ここでは無機絶縁膜640bの膜厚は600nm〜800nmとする。

【0084】

また、無機絶縁膜640bの一層として、塗布法で得られるシロキサン樹脂を用いてもよ

い。なお、シロキサン樹脂とは、Si−O−Si結合を含む樹脂に相当する。シロキサン

は、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少

なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基

として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基

と、フルオロ基とを用いてもよい。

【0085】

次いで、フォトマスクを用いてレジストからなるマスクを形成し、絶縁膜640a、64

0b及び絶縁膜613を選択的にエッチングしてコンタクトホールを形成する。そして、

レジストからなるマスクを除去する。

【0086】

次いで、スパッタ法により金属膜を積層した後、フォトマスクを用いてレジストからな

るマスクを形成し、選択的に金属積層膜をエッチングして、TFTのソース電極またはド

レイン電極として機能する電極641〜647を形成する。そして、レジストからなるマ

スクを除去する。なお、ここでの金属積層膜は、膜厚100nmのTi膜と、膜厚350

nmのSiを微量に含むAl膜と、膜厚100nmのTi膜との3層積層とする。

【0087】

また、電極641〜647の端面は、下方に配置された第1の導電層と第3の導電層の

端面と重ならないように適宜、それぞれの線幅や位置を設定することが好ましい。

【0088】

以上の工程で、同一基板上にポリシリコン膜を活性層とするトップゲート型のTFT63

6、637、638、639が作製でき、この段階での断面図を図6(D)に示す。

【0089】

なお、駆動回路部に配置されるTFT636はゲート電極と重なる低濃度不純物領域(

LDD領域とも呼ぶ)を備えたnチャネル型TFTであり、TFT637はpチャネル型

TFTである。駆動回路部においては、TFT636とTFT637を相補的に接続する

ことでCMOS回路を構成し、様々な種類の回路を実現することができる。

【0090】

また、画素部に配置されるTFT638は、一つのTFTに複数のチャネル形成領域を

有するnチャネル型TFTである。TFT638は、ゲート電極と重ならない低濃度不純

物領域(LDD領域とも呼ぶ)を備えたマルチゲート型のTFTである。また、画素部に

は、後に形成される発光素子と電気的に接続するTFT639が設けられる。ここでは、

TFT639として、シングルゲート型のpチャネル型TFTを示したが、特に限定され

ず、マルチゲート型のTFTとしてもよい。

【0091】

次いで、第1の電極623、即ち、有機発光素子の陽極(或いは陰極)を形成する。第

1の電極623として、仕事関数の大きい材料、例えば、Ni、W、Cr、Pt、Zn、

Sn、InまたはMoから選ばれた元素、または前記元素を主成分とする合金材料、例え

ばTiN、TiSiXNY、WSiX、WNX、WSiXNY、NbNを用いて、単層膜

またはそれらの積層膜を総膜厚100nm〜800nmの範囲で用いればよい。

【0092】

具体的には第1の電極623として、透光性を有する導電性材料からなる透明導電膜を用

いればよく、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジ

ウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸

化物などを用いることができる。勿論、インジウム錫酸化物(ITO)、インジウム亜鉛

酸化物(IZO)、酸化ケイ素を添加したインジウム錫酸化物(ITSO)なども用いる

ことができる。

【0093】

各透光性を有する導電性材料の、組成比例を述べる。酸化タングステンを含むインジ

ウム酸化物の組成比は、酸化タングステン1.0wt%、インジウム酸化物99.0wt

%とすればよい。酸化タングステンを含むインジウム亜鉛酸化物の組成比は、酸化タング

ステン1.0wt%、酸化亜鉛0.5wt%、インジウム酸化物98.5wt%とすれば

よい。酸化チタンを含むインジウム酸化物は、酸化チタン1.0wt%〜5.0wt%、

インジウム酸化物99.0wt%〜95.0wt%とすればよい。インジウム錫酸化物(

ITO)の組成比は、酸化錫10.0wt%、インジウム酸化物90.0wt%とすれば

よい。インジウム亜鉛酸化物(IZO)の組成比は、酸化亜鉛10.7wt%、インジウ

ム酸化物89.3wt%とすればよい。酸化チタンを含むインジウム錫酸化物の組成比は

、酸化チタン5.0wt%、酸化錫10.0wt%、インジウム酸化物85.0wt%と

すればよい。上記組成比は例であり、適宜その組成比の割合は設定すればよい。

【0094】

次いで、塗布法により得られる絶縁膜(例えば、アルキル基を含むSiOx膜や有機樹脂

膜)をパターニングして、第1の電極623の端部を覆う絶縁物629(バンク、隔壁、

障壁、土手などと呼ばれる)を形成する。

【0095】

次いで、有機化合物を含む層624を、蒸着法または塗布法を用いて形成する。次いで

、第2の電極625、即ち、有機発光素子の陰極(或いは陽極)を形成する。第2の電極

625としては、MgAg、MgIn、AlLiなどの合金、または透明導電膜(ITO

など)を用いる。

【0096】

次いで、蒸着法またはスパッタ法により保護層626を形成する。保護層626は、第2

の電極625を保護する。保護層626を通過させて発光素子の発光を取り出す場合、保

護層626には透明な材料とすることが好ましい。なお、必要でなければ保護層626は

設けなくともよい。

【0097】

次いで、封止基板633をシール材628で貼り合わせて発光素子を封止する。即ち、

発光表示装置は、表示領域の外周をシール材で囲み、一対の基板で封止される。TFTの

層間絶縁膜は、基板全面に設けられているため、シール材のパターンが層間絶縁膜の外周

縁よりも内側に描画された場合、シール材のパターンの外側に位置する層間絶縁膜の一部

から水分や不純物が浸入する恐れがある。従って、TFTの層間絶縁膜として用いる絶縁

膜の外周は、シール材のパターンの内側、好ましくは、シール材パターンと重なるように

して絶縁膜の端部をシール材が覆うようにする。なお、シール材628で囲まれた領域に

は充填材627を充填する。或いは、シール材628で囲まれた領域には乾燥した不活性

ガスを充填する。

【0098】

最後にFPC632を異方性導電膜631により公知の方法で端子電極と貼りつける。

(図7)なお、端子電極は、第1の電極623と同じ工程で得られる透明導電膜を端子電

極の最上層に用いることが好ましく、ゲート配線と同時に形成された端子電極の一層とな

る第3の導電層615c上に形成する。

【0099】

以上の工程によって、画素部と駆動回路と端子部とを同一基板上に形成することができる

。

【0100】

本実施の形態において、電極641〜647の端面が、下方に配置された第1の導電層と

第3の導電層の端面と重ならないように適宜、それぞれの線幅や位置を設定されており、

絶縁物629の膜厚が確保されている。従って、膜厚が部分的に薄くなることが防がれて

、電極641〜647と第2の電極625とが重なる部分での短絡発生の防止ができる。

【0101】

また、発光装置において、発光装置の発光表示面は、一面または両面であってもよい。

第1の電極623と第2の電極625とを透明導電膜で形成した場合、発光素子の光は、

基板610及び封止基板633を通過して両側に取り出される。この場合、封止基板63

3や充填材627は透明な材料を用いることが好ましい。

【0102】

また、第2の電極625を金属膜で形成し、第1の電極623を透明導電膜で形成した

場合、発光素子の光は、基板610のみを通過して一方に取り出される構造、即ちボトム

エミッション型となる。この場合、封止基板633や充填材627は透明な材料を用いな

くともよい。

【0103】

また、第1の電極623を金属膜で形成し、第2の電極625を透明導電膜で形成した

場合、発光素子の光は、封止基板633のみを通過して一方に取り出される構造、即ちト

ップエミッション型となる。この場合、基板610は透明な材料を用いなくともよい。

【0104】

また、第1の電極623及び第2の電極625は仕事関数を考慮して材料を選択する必要

がある。但し第1の電極及び第2の電極は、画素構成によりいずれも陽極、又は陰極とな

りうる。駆動用TFTの極性がpチャネル型である場合、第1の電極を陽極、第2の電極

を陰極とするとよい。また、駆動用TFTの極性がNチャネル型である場合、第1の電極

を陰極、第2の電極を陽極とすると好ましい。

【0105】

また、発光装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方

法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法

とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、発光装置のソ

ース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であっても

よく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

【0106】

さらに、ビデオ信号がデジタルの発光装置において、画素に入力されるビデオ信号が定電

圧(CV)のものと、定電流(CC)のものとがある。ビデオ信号が定電圧のもの(CV

)には、発光素子に印加される信号の電圧が一定のもの(CVCV)と、発光素子に印加

される信号の電流が一定のもの(CVCC)とがある。また、ビデオ信号が定電流のもの

(CC)には、発光素子に印加される信号の電圧が一定のもの(CCCV)と、発光素子

に印加される信号の電流が一定のもの(CCCC)とがある。

【0107】

また、発光装置において、静電破壊防止のための保護回路(保護ダイオードなど)を設

けてもよい。

【0108】

また、本実施の形態は、実施の形態1乃至3のいずれか一と自由に組み合わせることが

できる。

【0109】

(実施の形態5)

ここでは、図8を用いて、発光表示パネルにFPCや、駆動用の駆動ICを実装する例に

ついて説明する。

【0110】

図8(A)に示す図は、FPC1209を4カ所の端子部1208に貼り付けた発光装置

の上面図の一例を示している。基板1210上には発光素子及びTFTを含む画素部12

02と、TFTを含むゲート側駆動回路1203と、TFTを含むソース側駆動回路12

01とが形成されている。TFTの活性層が結晶構造を有する半導体膜で構成されており

、同一基板上にこれらの回路を形成している。従って、システムオンパネル化を実現した

EL表示パネルを作製することができる。

【0111】

なお、基板1210はコンタクト部以外において保護膜で覆われており、保護膜上に光触

媒機能を有する物質を含む下地層が設けられている。

【0112】

また、画素部を挟むように2カ所に設けられた接続領域1207は、発光素子の第2の

電極を下層の配線とコンタクトさせるために設けている。なお、発光素子の第1の電極は

画素部に設けられたTFTと電気的に接続している。

【0113】

また、封止基板1204は、画素部および駆動回路を囲むシール材1205、およびシ

ール材に囲まれた充填材料によって基板1210と固定されている。また、透明な乾燥剤

を含む充填材料を充填する構成としてもよい。また、画素部と重ならない領域に乾燥剤を

配置してもよい。

【0114】

また、図8(A)に示した構造は、XGAクラスの比較的大きなサイズ(例えば対角4

.3インチ)の発光装置で好適な例を示したが、図9(B)は、狭額縁化させた小型サイ

ズ(例えば対角1.5インチ)で好適なCOG方式を採用した例である。

【0115】

図8(B)において、基板1310上に駆動IC1301が実装され、駆動ICの先に配

置された端子部1308にFPC1309を実装している。実装される駆動IC1301

は、生産性を向上させる観点から、一辺が300mmから1000mm以上の矩形状の基

板上に複数個作り込むとよい。つまり、基板上に駆動回路部と入出力端子を一つのユニッ

トとする回路パターンを複数個形成し、最後に分割して駆動ICを個別に取り出せばよい

。駆動ICの長辺の長さは、画素部の一辺の長さや画素ピッチを考慮して、長辺が15〜

80mm、短辺が1〜6mmの矩形状に形成してもよいし、画素領域の一辺、又は画素部

の一辺と各駆動回路の一辺とを足した長さに形成してもよい。

【0116】

駆動ICのICチップに対する外形寸法の優位性は長辺の長さにあり、長辺が15〜8

0mmで形成された駆動ICを用いると、画素部に対応して実装するのに必要な数がIC

チップを用いる場合よりも少なくて済み、製造上の歩留まりを向上させることができる。

また、ガラス基板上に駆動ICを形成すると、母体として用いる基板の形状に限定されな

いので生産性を損なうことがない。これは、円形のシリコンウエハからICチップを取り

出す場合と比較すると、大きな優位点である。

【0117】

また、TAB方式を採用してもよく、その場合は、複数のテープを貼り付けて、該テー

プに駆動ICを実装すればよい。COG方式の場合と同様に、単数のテープに単数の駆動

ICを実装してもよく、この場合には、強度の問題から、駆動ICを固定するための金属

片等を一緒に貼り付けるとよい。

【0118】

また、画素部1302と駆動IC1301の間に設けられた接続領域1307は、発光

素子の第2の電極を下層の配線とコンタクトさせるために設けている。なお、発光素子の

第1の電極は画素部に設けられたTFTと電気的に接続している。

【0119】

また、封止基板1304は、画素部1302を囲むシール材1305、およびシール材

に囲まれた充填材料によって基板1310と固定されている。

【0120】

また、画素部のTFTの活性層として非晶質半導体膜を用いる場合には、駆動回路を同

一基板上に形成することは困難であるため、大きなサイズであっても図8(B)の構成と

なる。

【0121】

また、ここでは表示装置としてアクティブマトリクス型の発光装置の例を示したが、ア

クティブマトリクス型の液晶表示装置にも適用できることはいうまでもない。アクティブ

マトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動する

ことによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画

素電極に対応する対向電極との間に電圧が印加されることによって、素子基板に設けられ

た画素電極と対向基板に設けられた対向電極との間に配置された液晶層の光学変調が行わ

れ、この光学変調が表示パターンとして観察者に認識される。対向基板と素子基板は、等

間隔で配置され、液晶材料が充填されている。液晶材料は、シール材を閉パターンとして

気泡が入らないように減圧下で液晶の滴下を行い、両方の基板を貼り合わせる方法を用い

てもよいし、開口部を有するシールパターンを設け、TFT基板を貼りあわせた後に毛細

管現象を用いて液晶を注入するディップ式(汲み上げ式)を用いてもよい。

【0122】

また、カラーフィルタを用いずに、光シャッタを行い、RGBの3色のバックライト光

源を高速で点滅させるフィールドシーケンシャル方式の駆動方法を用いた液晶表示装置に

も本発明は、適用できる。

【0123】

以上の様に、本発明を実施する、即ち実施の形態1乃至4のいずれか一の作製方法また

は構成を用いて、様々な電子機器を完成させることができる。

【0124】

(実施の形態6)

本発明の半導体装置、及び電子機器として、ビデオカメラ、デジタルカメラ等のカメラ、

ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音

響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ

などのパーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携

帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置(具体的には

Digital Versatile Disc(DVD)等の記録媒体を再生し、その

画像を表示しうるディスプレイを備えた装置)などが挙げられる。それら電子機器の具体

例を図9および図10に示す。

【0125】

図9(A)はデジタルカメラであり、本体2101、表示部2102、撮像部、操作キー

2104、シャッター2106等を含む。なお、図9(A)は表示部2102側からの図

であり、撮像部は示していない。本発明により、信頼性の高いデジタルカメラが実現でき

る。

【0126】

図9(B)はノート型パーソナルコンピュータであり、本体2201、筐体2202、表

示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2

206等を含む。本発明により、信頼性の高いノート型パーソナルコンピュータを実現す

ることができる。

【0127】

図9(C)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であ

り、本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体(D

VD等)読込部2405、操作キー2406、スピーカー部2407等を含む。表示部A

2403は主として画像情報を表示し、表示部B2404は主として文字情報を表示する

。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明に

より、信頼性の高い画像再生装置を実現することができる。

【0128】

また、図9(D)は表示装置であり、筐体1901、支持台1902、表示部1903、

スピーカ1904、ビデオ入力端子1905などを含む。この表示装置は、上述した実施

の形態で示した作製方法により形成した薄膜トランジスタをその表示部1903および駆

動回路に用いることにより作製される。なお、表示装置には液晶表示装置、発光装置など

があり、具体的にはコンピュータ用、テレビ受信用、広告表示用などの全ての情報表示用

表示装置が含まれる。本発明により、信頼性の高い表示装置、特に22インチ〜50イン

チの大画面を有する大型の表示装置を実現することができる。

【0129】

図10で示す携帯電話機は、操作スイッチ類904、マイクロフォン905などが備えら

れた本体(A)901と、表示パネル(A)908、表示パネル(B)909、スピーカ

906などが備えられた本体(B)902とが、蝶番910で開閉可能に連結されている

。表示パネル(A)908と表示パネル(B)909は、回路基板907と共に本体(B

)902の筐体903の中に収納される。表示パネル(A)908及び表示パネル(B)

909の画素部は筐体903に形成された開口窓から視認できるように配置される。

【0130】

表示パネル(A)908と表示パネル(B)909は、その携帯電話機900の機能に

応じて画素数などの仕様を適宜設定することができる。例えば、表示パネル(A)908

を主画面とし、表示パネル(B)909を副画面として組み合わせることができる。

【0131】

本発明により、信頼性の高い携帯情報端末を実現することができる。

【0132】

本実施の形態に係る携帯電話機は、その機能や用途に応じてさまざまな態様に変容し得

る。例えば、蝶番910の部位に撮像素子を組み込んで、カメラ付きの携帯電話機として

も良い。また、操作スイッチ類904、表示パネル(A)908、表示パネル(B)90

9を一つの筐体内に納めた構成としても、上記した作用効果を奏することができる。また

、表示部を複数個そなえた情報表示端末に本実施の形態の構成を適用しても、同様な効果

を得ることができる。

【0133】

以上の様に、本発明を実施する、即ち実施の形態1乃至5のいずれか一の作製方法また

は構成を用いて、様々な電子機器を完成させることができる。

【産業上の利用可能性】

【0134】

本発明は、半導体装置の製造時および製造後の短絡発生を効果的に防止することができ

るため、有用である。

【符号の説明】

【0135】

10 ガラス基板

11 第1の絶縁層

12 第1の配線

13 第2の配線

14 金属層

15 第2の絶縁層

16 第3の絶縁層

17a チタン層

17b アルミニウム層

18 第4の絶縁層

20 ガラス基板

21 ゲートメタル層

22 第1の絶縁層

23a 第1のチタン膜

23b アルミニウム膜

23c 第2のチタン膜

24 第2の絶縁層

25 上部電極

31 第2の配線

32 第2の配線

33 電極

34 電極

41 第1の配線

42 第1の配線

50 第1の電極層

51 薄膜トランジスタ

52 薄膜トランジスタ

53 ゲート配線層

54 ソース配線層又はドレイン配線層

55 電源線

56a 導電層

56b 導電層

56c 導電層

56d 導電層

57 導電層

58 ソース電極層又はドレイン電極層

60 ガラス基板

61 ゲートメタル層

62 第1の絶縁層

63a 第1のチタン膜

63b アルミニウム膜

63c 第2のチタン膜

64 第2の絶縁層

65 上部電極

610 基板

611 下地絶縁膜

612 半導体層

613 絶縁膜

614a 第1の導電層

614b 第2の導電層

614c 第3の導電層

615a 第1の導電層

615b 第2の導電層

615c 第3の導電層

616 マスク

617 タングステンを含む薄い膜

618 第1の不純物領域

619 マスク

620a 第2の不純物領域

620b 第3の不純物領域

621 マスク

622 第4の不純物領域

623 第1の電極

624 有機化合物を含む層

625 第2の電極

626 保護層

627 充填材

628 シール材

629 絶縁物

631 異方性導電膜

632 FPC

636 nチャネル型TFT

637 pチャネル型TFT

638 nチャネル型TFT

639 pチャネル型TFT

640a 水素を含む絶縁膜

640b 無機絶縁膜

641 電極

642 電極

643 電極

644 電極

645 電極

646 電極

647 電極

900 携帯電話機

901 本体(A)

902 本体(B)

903 筐体

904 操作スイッチ類

905 マイクロフォン

906 スピーカ

907 回路基板

908 表示パネル(A)

909 表示パネル(B)

910 蝶番

1201 ソース側駆動回路

1202 画素部

1203 ゲート側駆動回路

1204 封止基板

1205 シール材

1207 接続領域

1208 端子部

1209 FPC

1210 基板

1301 駆動IC

1302 画素部

1304 封止基板

1305 シール材

1307 接続領域

1308 端子部

1309 FPC

1901 筐体

1902 支持台

1903 表示部

1904 スピーカ

1905 ビデオ入力端子

2101 本体

2102 表示部

2104 操作キー

2106 シャッター

2201 本体

2202 筐体

2203 表示部

2204 キーボード

2205 外部接続ポート

2206 ポインティングマウス

2401 本体

2402 筐体

2403 表示部A

2404 表示部B

2405 記録媒体読込部

2406 操作キー

2407 スピーカー部

【特許請求の範囲】

【請求項1】

絶縁表面上の第1の配線と、

前記第1の配線上の第1の絶縁層と、

前記第1の絶縁層上の第2の配線と、

前記第2の配線上の第2の絶縁層と、を有し、

前記第1の配線と前記第2の配線とが重なる部分を有し、

前記重なる部分において、前記第1の配線と前記第2の配線とは平行方向に配置されているとともに、前記第1の配線の前記平行方向と垂直な方向の幅と前記第2の配線の前記平行方向と垂直な方向の幅とが異なることを特徴とする半導体装置。

【請求項1】

絶縁表面上の第1の配線と、

前記第1の配線上の第1の絶縁層と、

前記第1の絶縁層上の第2の配線と、

前記第2の配線上の第2の絶縁層と、を有し、

前記第1の配線と前記第2の配線とが重なる部分を有し、

前記重なる部分において、前記第1の配線と前記第2の配線とは平行方向に配置されているとともに、前記第1の配線の前記平行方向と垂直な方向の幅と前記第2の配線の前記平行方向と垂直な方向の幅とが異なることを特徴とする半導体装置。

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図2】

【図11】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図2】

【図11】

【公開番号】特開2012−195592(P2012−195592A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2012−93630(P2012−93630)

【出願日】平成24年4月17日(2012.4.17)

【分割の表示】特願2006−133446(P2006−133446)の分割

【原出願日】平成18年5月12日(2006.5.12)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成24年4月17日(2012.4.17)

【分割の表示】特願2006−133446(P2006−133446)の分割

【原出願日】平成18年5月12日(2006.5.12)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]