半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、DLL(Delay Locked Loop)回路を備える半導体装置に関する。

【背景技術】

【0002】

半導体装置では、例えば、外部クロックに同期した内部クロックを生成するために、DLL回路が用いられている。

【0003】

DLL回路では、入力信号と出力信号の位相を合致させるロック調整動作が行われる。以下では、入力信号と出力信号の位相が合致している状態をロック状態と称す。また、入力信号と出力信号の位相差をロック精度と称す。

【0004】

DLL回路には、縦続接続された複数の遅延素子からなるディレイライン(Delay-Line)が設けられており、これら複数の遅延素子を用いてロック調整動作が行われる。遅延時間は、使用する遅延素子の数に応じて決まり、遅延素子の数が多いほど遅延時間は増加する。

【0005】

DLL回路では、遅延時間は、例えば、カウンタ回路により制御される(特許文献1参照)。遅延時間を増加させたい場合は、カウンタ値を増加させて遅延素子の数を増やし、遅延時間を減少させたい場合は、カウンタ値を減少させて遅延素子の数を減らす。

【0006】

図4Aは、ロック調整動作開始時のDLL回路の入力信号と出力信号の位相関係を示している。

【0007】

DLL回路では、出力信号(調整対象)の位相が入力信号(基準信号)の位相と合致するよう位相調整を行うが、図4Aでは、ロック調整動作開始時に、出力信号の遅延が不足している。そのため、カウンタ値を増加させ、遅延時間を増加させる。

【0008】

図4Bでは、図4Aで遅延時間を増加させた結果、出力信号の遅延が過剰になっている。そのため、カウンタ値を減少させ、遅延時間を減少させる。

【0009】

図4Cでは、図4Bで遅延時間を減少させた結果、再び出力信号の遅延が不足してしまっている。そのため、再びカウンタ値を増加させ、図4Bの状態に戻る。

【0010】

図4Bおよび図4Cでは、出力信号の位相が入力信号の前後を往来する。これにより、入力信号と出力信号の位相合致(つまり、ロック状態)が達成される。

【0011】

なお、DLL回路では、入力信号と出力信号の接近を検知した場合、カウンタ値の更新を停止して固定し、遅延時間の増減を停止させる制御を行うこともある。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2009−177778号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、ロック状態達成後にカウンタ値を固定するDLL回路では、ロック状態達成前に遅延素子を動作させる動作電圧に異常があり、その異常がロック状態達成後に解消した場合、状態達成前後で各遅延素子の遅延時間が異なることに起因して、入力信号と出力信号の位相差が増大してしまうという課題がある。以下、この課題について詳述する。

(A)遅延素子の動作電圧の変化とロック精度の悪化について

遅延素子の遅延時間は、動作電圧に応じて変化する。

【0014】

表1は、遅延素子の動作電圧が標準動作電圧から±100mV変化した場合の遅延時間を示している。なお、表1において、単位はpsである。

【0015】

【表1】

【0016】

表1に示すように、100mVの電圧変化に伴い、遅延素子1個あたり50psの位相差が発生する。

【0017】

そのため、例えば、32個の遅延素子が縦続接続されたディレイラインの場合、ディレイライン全体では、100mVの電圧変化に伴い、1600psもの位相差が発生し、ロック精度が悪化する。

【0018】

以上より、ディレイラインには、常に一定の電圧を供給することができる安定した電源回路が必要と言える。

(B)遅延素子用電源回路の独立化

ディレイラインへの電圧供給の安定化のために、遅延素子用電源回路の独立化が試行されている。

【0019】

遅延素子用電源回路とは、外部電源電圧に依らず一定の電圧を遅延素子に供給し、各遅延素子の遅延時間を一定に保つ機構である。

【0020】

図5は、遅延素子用電源回路の概念図である。

【0021】

図5において、リファレンス電位は、半導体装置の製造時に固有の値になるVtに依存した、バンドギャップ回路などから生成される基準電位である。

【0022】

リファレンス電位は、外部電源電圧の変動の影響を受けないが、上記のバンドギャップ回路などの基準電位生成回路は、大電流を出力可能な構造ではない。

【0023】

そのため、図5のように、リファレンス電位を基準電位とするカレントミラーアンプ31を用いる手法が一般的である。

【0024】

以下、図5に示した遅延素子用電源回路の動作原理について説明する。

【0025】

ステップB1:

遅延素子用電源回路の出力電圧は、NMOSトランジスタVPERDのドレイン端子の電圧VPERDであり、この電圧VPERDが遅延素子に動作電圧として供給される。

【0026】

ステップB2:

電圧VPERDは、カレントミラーアンプ31の入力となり、カレントミラーアンプ31にてリファレンス電位との比較が行われる。

【0027】

ステップB3:

もし、電圧VPERDがリファレンス電位よりも小さい場合、カレントミラーアンプ31の出力電圧(接点Rxの電圧)のレベル、すなわち、NMOSトランジスタVPERDのゲートに入力される入力電圧のレベルが下がる。これにより、NMOSトランジスタVPERDのドレイン端子の電圧VPERDが上がる。

【0028】

したがって、電圧VPERDがリファレンス電位よりも小さい場合、電圧VPERDは上がり続け、リファレンス電位よりも大きくなると、次のステップB4に遷移する。

【0029】

ステップB4:

一方、電圧VPERDがリファレンス電位よりも大きい場合、カレントミラーアンプ31の出力電圧(接点Rxの電圧)のレベル、すなわち、NMOSトランジスタVPERDのゲートに入力される入力電圧のレベルが上がる。これにより、NMOSトランジスタVPERDのドレイン端子の電圧VPERDが下がる。

【0030】

したがって、電圧VPERDがリファレンス電位よりも大きい場合、電圧VPERDは下がり続け、リファレンス電位よりも小さくなると、上記のステップB3に戻る。

【0031】

結局、ステップB3とB4のプロセスが繰り返されることで、電圧VPERDはリファレンス電位付近の一定電位に留まる。

【0032】

ステップB5:

ここで、DLL回路の動作時の電圧VPERDとVSS間の回路抵抗をRdllとすれば、以下の関係式が成立する。

【0033】

VPERD=Rdll*Idll

Idllは、VPERDとRdllにより決定されるDLL回路の消費電流である。

【0034】

以上より、遅延素子に動作電圧として供給される電圧VPERDは、リファレンス電位付近の一定範囲内に調整され、ディレイライン全体の遅延時間も一定範囲内になる。

(C)遅延素子用電源回路の出力電圧の変化に起因するロック精度の悪化

遅延素子用電源回路は、遅延時間の一定化を目的として導入されたものであるが、以下に起因して、出力電圧(電圧VPERD)は変化しうる。

【0035】

・遅延素子用電源回路への入力電圧(=外部電源電圧)が変化

・DLL回路の消費電流が変化

以下、遅延素子用電源回路の出力電圧の変化のロック精度への影響について説明する。

(C−1)遅延素子用電源回路への入力電圧(=外部電源電圧)が変化

ステップC11:

PMOSトランジスタRaおよびNMOSトランジスタRbが飽和領域で動作中に、遅延素子用電源回路への入力電圧である外部電源電圧VDDが変化した場合、PMOSトランジスタRaおよびNMOSトランジスタRbは、ソース−ドレイン間電流はほぼ同一でありながら、ソース−ドレイン間電圧Vds自体は増加するため、接点Rxの電圧が変化してしまう。

【0036】

ステップC12:

接点Rxの電圧は、カレントミラーアンプ31から出力され、NMOSトランジスタVPERDのゲートに入力されるため、接点Rxの電圧の変化に連動して、電圧VPERDが変化する。

【0037】

ステップC13:

電圧VPERDは、カレントミラーアンプ31において、リファレンス電位との比較が行われ、リファレンス電位付近に再調整されるが、調整完了前は、リファレンス電位とは差が生じている。

【0038】

ここで、電圧VPERDの調整を開始してから完了するまでの期間をVPERD調整期間と称す。VPERD調整期間内では、電圧VPERDは、リファレンス電位とは異なる電位にある。

(C−2)DLL回路の消費電流が変化

図6は、DLL回路の消費電流の変化に伴い、電圧VPERDが一時的に変化する様子を説明する図である。

【0039】

ステップC21:

DLL回路の消費電流Idllが増加する(つまり、回路抵抗Rdllが下がる)。以下、増加後の消費電流IdllをIdll_aと称す。

【0040】

ステップC22:

DLL回路の消費電流Idllは、NMOSトランジスタVPERDのソース−ドレイン間電流でもある。

【0041】

消費電流Idllは増加し、Idll_aに変化したが、NMOSトランジスタVPERDの抵抗成分RTrはそのままである。

【0042】

ここで、消費電流Idllの増加前のNMOSトランジスタVPERDにおける電圧降下は以下で表される。

【0043】

RTr×Idll(電圧降下1と称す)

また、消費電流Idll_aへの増加後のNMOSトランジスタVPERDにおける電圧降下は以下で表される。

【0044】

RTr×Idll_a(電圧降下2と称す)

よって、DLL回路の消費電流Idllの増加直後は、電圧VPERDは、(電圧降下2−電圧降下1)分だけ低下する

ステップC23:

電圧VPERDは、カレントミラーアンプ31において、リファレンス電位との比較が行われ、リファレンス電位付近に再調整されるが、調整完了までにはタイムラグが残り、上記の(C−1)と同様にVPERD調整期間が発生する。

【0045】

ここで、消費電流Idllが変化する要因としては、例えば、ロック調整動作中に使用する遅延素子数が変化することなどが挙げられる。

【0046】

つまり、DLL回路のロック調整動作自体が消費電流の変化ひいては電圧VPERDの変化に直結することになる。

【0047】

上記の(C−1)と(C−2)のいずれの場合においても、電圧VPERDは、VPERD調整期間を経て、リファレンス電位付近に調整される。

【0048】

しかし、電圧VPERDがリファレンス電位付近に調整された際、DLL回路が既にロック調整動作を完了していれば、入力信号と出力信号の位相差が増大してしまう。

【課題を解決するための手段】

【0049】

本発明の半導体装置は、

縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、

リファレンス電位を基準として生成した出力電圧を、前記複数の遅延素子に供給する遅延素子用電源回路と、

前記出力電圧が前記リファレンス電位の一定範囲内にあるか否かを検出し、前記出力電圧が前記一定範囲内にない場合、前記ロック調整動作を停止させるDLL動作信号を前記DLL回路に出力する検出回路と、を有する。

【発明の効果】

【0050】

本発明によれば、遅延素子用電源回路の出力電圧がリファレンス電位の一定範囲内にあることを確認した後、DLL回路がロック調整動作を実施する。

【0051】

言い換えれば、外部電源電圧の変化等に起因して、遅延素子用電源回路の出力電圧に異常がある場合には、DLL回路がロック調整動作を停止する。

【0052】

そのため、遅延素子用電源回路の出力電圧(=遅延素子の動作電圧)の異常時に発生していた、入力信号と出力信号の位相差の増大を抑制できるという効果が得られる。

【図面の簡単な説明】

【0053】

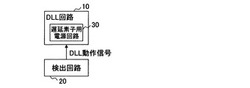

【図1】本発明の一実施形態の半導体装置の構成を示す図である。

【図2】図1に示した検出回路の一構成例を示す図である。

【図3】図2に示した第1段カレントミラーアンプの一構成例を示す図である。

【図4A】ロック調整動作開始時のDLL回路の入力信号と出力信号の位相関係の一例を示す図である。

【図4B】ロック調整動作中のDLL回路の入力信号と出力信号の位相関係の一例を示す図である。

【図4C】ロック調整動作中のDLL回路の入力信号と出力信号の位相関係の一例を示す図である。

【図5】遅延素子用電源回路の一構成例を示す図である。

【図6】DLL回路の消費電流の変化に伴い、電圧VPERDが一時的に変化する様子を説明する図である。

【発明を実施するための形態】

【0054】

以下に、本発明を実施するための形態について図面を参照して説明する。

【0055】

図1は、本発明の一実施形態の半導体装置の構成を示す図である。

【0056】

図1に示すように、本実施形態の半導体装置は、DLL回路10と、検出回路20と、を有している。DLL回路10は、遅延素子用電源回路30を内部に備えている。

【0057】

DLL回路10は、縦続接続された複数の遅延素子(不図示)を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行う。

【0058】

遅延素子用電源回路30は、リファレンス電位を基準として生成した電圧VPERDを、複数の遅延素子に動作電圧として供給する。なお、遅延素子用電源回路30の構成は図5に示したものと同様である。

【0059】

検出回路20は、遅延素子用電源回路30の出力電圧である電圧VPERDがリファレンス電位の一定範囲内にあるか否かを検出し、検出結果に応じてDLL回路10のロック調整動作の可否を示すDLL動作信号をDLL回路10に出力する。

【0060】

具体的には、検出回路20は、電圧VPERDがリファレンス電位の一定範囲内にない場合、ロック調整動作を停止させることを示すDLL動作信号をDLL回路10に出力する。

【0061】

なお、以下では、DLL動作信号は、DLL回路10のカウンタ(不図示)の更新の可否を示す信号であるものとして説明する。

【0062】

図2は、図1に示した検出回路20の一構成例を示す図である。

【0063】

図2に示すように、検出回路20は、第1の比較回路21と、第2の比較回路22と、XOR回路23と、を有している。

【0064】

第1の比較回路21は、電圧VPERDがリファレンス電位の一定範囲の上限値よりも大きい場合にはHを、小さい場合にはLを、それぞれ出力する。

【0065】

第2の比較回路22は、電圧VPERDがリファレンス電位の一定範囲の下限値よりも大きい場合にはHを、小さい場合にはLを、それぞれ出力する。

【0066】

なお、本実施形態では、上記の上限値がリファレンス電位+10mVであり、上記の下限値がリファレンス電位−10mVであるものとして説明する。

【0067】

XOR回路23は、第1の比較回路21の出力と第2の比較回路22の出力とのXORを演算し、演算結果をDLL動作信号としてDLL回路10に出力する。

【0068】

ここで、XOR回路の演算結果がHである場合には、DLL回路10のカウンタの更新機能を有効化(つまり、ロック調整動作を実施)することを示すDLL動作信号が出力され、演算結果がLである場合には、DLL回路10のカウンタの更新機能を無効化(つまり、ロック調整動作を停止)することを示すDLL動作信号が出力されるが、その詳細は後述する。

【0069】

第1の比較回路21は、第1段カレントミラーアンプ21Aと、第2段カレントミラーアンプ21Bと、を有している。

【0070】

また、第2の比較回路22は、第1段カレントミラーアンプ22Aと、第2段カレントミラーアンプ22Bと、を有している。

【0071】

図3は、図2に示した第1段カレントミラーアンプ21A,22Aの一構成例を示す図である。

【0072】

図3に示すように、第1段カレントミラーアンプ21Aは、電圧VPERDとリファレンス電位+10mVとを比較し、比較結果に応じた電圧を出力する。

【0073】

第2段カレントミラーアンプ21Bは、第1段カレントミラーアンプ21Aの後段に縦続接続されており、第1段カレントミラーアンプ21Aからの電圧に応じたディジタル値H/LをXOR回路23に出力する。

【0074】

また、図3に示すように、第1段カレントミラーアンプ22Aは、電圧VPERDとリファレンス電位−10mVとを比較し、比較結果に応じた電圧を出力する。

【0075】

第2段カレントミラーアンプ22Bは、第1段カレントミラーアンプ22Aの後段に縦続接続されており、第1段カレントミラーアンプ22Aからの電圧に応じたディジタル値H/LをXOR回路23に出力する。

【0076】

以下、本発明の特徴部分である検出回路20の動作について説明する。

【0077】

第1の比較回路21および第2の比較回路22に入力される電圧VPERDは、大別して、以下の状態になりうる。

(1)電圧VPERD≒リファレンス電位

本実施形態では、リファレンス電位±10mVを想定している

(2)電圧VPERD<リファレンス電位−10mV

(3)電圧VPERD>リファレンス電位+10mV

以下、電圧VPERDが上記の(1)〜(3)の各々の状態のときのDLL回路10のロック調整動作の可否について説明する。

(1)電圧VPERD≒リファレンス電位

この状態では、第1の比較回路21および第2の比較回路22の出力は、一方がLで他方がHとなる。そのため、XOR回路23の出力(DLL動作信号)はHになる。

【0078】

よって、DLL回路10のカウンタの更新機能が有効化され、ロック調整動作が実施される。

【0079】

このとき、電圧VPERDは、リファレンス電位±10mV以内であるため、ロック調整動作を実施することは妥当と言える。

(2)電圧VPERD<リファレンス電位−10mV

この状態では、第1の比較回路21および第2の比較回路22の出力は共にLとなる。そのため、XOR回路23の出力(DLL動作信号)はLになる。

【0080】

よって、DLL回路10のカウンタの更新機能が無効化され、ロック調整動作が停止される。

【0081】

このとき、電圧VPERDは、リファレンス電位との差が−10mV以上であるため、ロック調整動作を停止することは妥当と言える。

(3)電圧VPERD>リファレンス電位+10mV

この状態では、第1の比較回路21および第2の比較回路22の出力は共にHとなる。そのため、XOR回路23の出力(DLL動作信号)はLになる。

【0082】

よって、DLL回路10のカウンタの更新機能が無効化され、ロック調整動作が停止される。

【0083】

このとき、電圧VPERDは、リファレンス電位との差が+10mV以上であるため、ロック調整動作を停止することは妥当と言える。

【0084】

上述したように本実施形態では、電圧VPERDがリファレンス電位±10mV以内の領域に存在する場合にのみ、DLL回路10のカウンタの更新機能を有効化してロック調整動作を実施させ、これ以外の場合には、DLL回路10のカウンタの更新機能を無効化してロック調整動作を停止させている。

【0085】

このように、電圧VPERDが一定範囲内に到達するのを待って、DLL回路10のロック調整動作を実施させることで、電圧VPERDの異常時に発生していた、入力信号と出力信号の位相差の増大を抑制できるという効果が得られる。

【0086】

なお、本実施形態では、検出回路20をXOR回路23を用いて構成する例を示したが、本発明はこれに限定されず、検出回路20の機能を実現しうる構成であれば、その他の構成でも構わない。

【符号の説明】

【0087】

10 DLL回路

20 検出回路

21 第1の比較回路

21A 第1段カレントミラーアンプ

21B 第2段カレントミラーアンプ

22 第2の比較回路

22A 第1段カレントミラーアンプ

22B 第2段カレントミラーアンプ

23 XOR回路

30 遅延素子用電源回路

31 カレントミラーアンプ

【技術分野】

【0001】

本発明は、DLL(Delay Locked Loop)回路を備える半導体装置に関する。

【背景技術】

【0002】

半導体装置では、例えば、外部クロックに同期した内部クロックを生成するために、DLL回路が用いられている。

【0003】

DLL回路では、入力信号と出力信号の位相を合致させるロック調整動作が行われる。以下では、入力信号と出力信号の位相が合致している状態をロック状態と称す。また、入力信号と出力信号の位相差をロック精度と称す。

【0004】

DLL回路には、縦続接続された複数の遅延素子からなるディレイライン(Delay-Line)が設けられており、これら複数の遅延素子を用いてロック調整動作が行われる。遅延時間は、使用する遅延素子の数に応じて決まり、遅延素子の数が多いほど遅延時間は増加する。

【0005】

DLL回路では、遅延時間は、例えば、カウンタ回路により制御される(特許文献1参照)。遅延時間を増加させたい場合は、カウンタ値を増加させて遅延素子の数を増やし、遅延時間を減少させたい場合は、カウンタ値を減少させて遅延素子の数を減らす。

【0006】

図4Aは、ロック調整動作開始時のDLL回路の入力信号と出力信号の位相関係を示している。

【0007】

DLL回路では、出力信号(調整対象)の位相が入力信号(基準信号)の位相と合致するよう位相調整を行うが、図4Aでは、ロック調整動作開始時に、出力信号の遅延が不足している。そのため、カウンタ値を増加させ、遅延時間を増加させる。

【0008】

図4Bでは、図4Aで遅延時間を増加させた結果、出力信号の遅延が過剰になっている。そのため、カウンタ値を減少させ、遅延時間を減少させる。

【0009】

図4Cでは、図4Bで遅延時間を減少させた結果、再び出力信号の遅延が不足してしまっている。そのため、再びカウンタ値を増加させ、図4Bの状態に戻る。

【0010】

図4Bおよび図4Cでは、出力信号の位相が入力信号の前後を往来する。これにより、入力信号と出力信号の位相合致(つまり、ロック状態)が達成される。

【0011】

なお、DLL回路では、入力信号と出力信号の接近を検知した場合、カウンタ値の更新を停止して固定し、遅延時間の増減を停止させる制御を行うこともある。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2009−177778号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、ロック状態達成後にカウンタ値を固定するDLL回路では、ロック状態達成前に遅延素子を動作させる動作電圧に異常があり、その異常がロック状態達成後に解消した場合、状態達成前後で各遅延素子の遅延時間が異なることに起因して、入力信号と出力信号の位相差が増大してしまうという課題がある。以下、この課題について詳述する。

(A)遅延素子の動作電圧の変化とロック精度の悪化について

遅延素子の遅延時間は、動作電圧に応じて変化する。

【0014】

表1は、遅延素子の動作電圧が標準動作電圧から±100mV変化した場合の遅延時間を示している。なお、表1において、単位はpsである。

【0015】

【表1】

【0016】

表1に示すように、100mVの電圧変化に伴い、遅延素子1個あたり50psの位相差が発生する。

【0017】

そのため、例えば、32個の遅延素子が縦続接続されたディレイラインの場合、ディレイライン全体では、100mVの電圧変化に伴い、1600psもの位相差が発生し、ロック精度が悪化する。

【0018】

以上より、ディレイラインには、常に一定の電圧を供給することができる安定した電源回路が必要と言える。

(B)遅延素子用電源回路の独立化

ディレイラインへの電圧供給の安定化のために、遅延素子用電源回路の独立化が試行されている。

【0019】

遅延素子用電源回路とは、外部電源電圧に依らず一定の電圧を遅延素子に供給し、各遅延素子の遅延時間を一定に保つ機構である。

【0020】

図5は、遅延素子用電源回路の概念図である。

【0021】

図5において、リファレンス電位は、半導体装置の製造時に固有の値になるVtに依存した、バンドギャップ回路などから生成される基準電位である。

【0022】

リファレンス電位は、外部電源電圧の変動の影響を受けないが、上記のバンドギャップ回路などの基準電位生成回路は、大電流を出力可能な構造ではない。

【0023】

そのため、図5のように、リファレンス電位を基準電位とするカレントミラーアンプ31を用いる手法が一般的である。

【0024】

以下、図5に示した遅延素子用電源回路の動作原理について説明する。

【0025】

ステップB1:

遅延素子用電源回路の出力電圧は、NMOSトランジスタVPERDのドレイン端子の電圧VPERDであり、この電圧VPERDが遅延素子に動作電圧として供給される。

【0026】

ステップB2:

電圧VPERDは、カレントミラーアンプ31の入力となり、カレントミラーアンプ31にてリファレンス電位との比較が行われる。

【0027】

ステップB3:

もし、電圧VPERDがリファレンス電位よりも小さい場合、カレントミラーアンプ31の出力電圧(接点Rxの電圧)のレベル、すなわち、NMOSトランジスタVPERDのゲートに入力される入力電圧のレベルが下がる。これにより、NMOSトランジスタVPERDのドレイン端子の電圧VPERDが上がる。

【0028】

したがって、電圧VPERDがリファレンス電位よりも小さい場合、電圧VPERDは上がり続け、リファレンス電位よりも大きくなると、次のステップB4に遷移する。

【0029】

ステップB4:

一方、電圧VPERDがリファレンス電位よりも大きい場合、カレントミラーアンプ31の出力電圧(接点Rxの電圧)のレベル、すなわち、NMOSトランジスタVPERDのゲートに入力される入力電圧のレベルが上がる。これにより、NMOSトランジスタVPERDのドレイン端子の電圧VPERDが下がる。

【0030】

したがって、電圧VPERDがリファレンス電位よりも大きい場合、電圧VPERDは下がり続け、リファレンス電位よりも小さくなると、上記のステップB3に戻る。

【0031】

結局、ステップB3とB4のプロセスが繰り返されることで、電圧VPERDはリファレンス電位付近の一定電位に留まる。

【0032】

ステップB5:

ここで、DLL回路の動作時の電圧VPERDとVSS間の回路抵抗をRdllとすれば、以下の関係式が成立する。

【0033】

VPERD=Rdll*Idll

Idllは、VPERDとRdllにより決定されるDLL回路の消費電流である。

【0034】

以上より、遅延素子に動作電圧として供給される電圧VPERDは、リファレンス電位付近の一定範囲内に調整され、ディレイライン全体の遅延時間も一定範囲内になる。

(C)遅延素子用電源回路の出力電圧の変化に起因するロック精度の悪化

遅延素子用電源回路は、遅延時間の一定化を目的として導入されたものであるが、以下に起因して、出力電圧(電圧VPERD)は変化しうる。

【0035】

・遅延素子用電源回路への入力電圧(=外部電源電圧)が変化

・DLL回路の消費電流が変化

以下、遅延素子用電源回路の出力電圧の変化のロック精度への影響について説明する。

(C−1)遅延素子用電源回路への入力電圧(=外部電源電圧)が変化

ステップC11:

PMOSトランジスタRaおよびNMOSトランジスタRbが飽和領域で動作中に、遅延素子用電源回路への入力電圧である外部電源電圧VDDが変化した場合、PMOSトランジスタRaおよびNMOSトランジスタRbは、ソース−ドレイン間電流はほぼ同一でありながら、ソース−ドレイン間電圧Vds自体は増加するため、接点Rxの電圧が変化してしまう。

【0036】

ステップC12:

接点Rxの電圧は、カレントミラーアンプ31から出力され、NMOSトランジスタVPERDのゲートに入力されるため、接点Rxの電圧の変化に連動して、電圧VPERDが変化する。

【0037】

ステップC13:

電圧VPERDは、カレントミラーアンプ31において、リファレンス電位との比較が行われ、リファレンス電位付近に再調整されるが、調整完了前は、リファレンス電位とは差が生じている。

【0038】

ここで、電圧VPERDの調整を開始してから完了するまでの期間をVPERD調整期間と称す。VPERD調整期間内では、電圧VPERDは、リファレンス電位とは異なる電位にある。

(C−2)DLL回路の消費電流が変化

図6は、DLL回路の消費電流の変化に伴い、電圧VPERDが一時的に変化する様子を説明する図である。

【0039】

ステップC21:

DLL回路の消費電流Idllが増加する(つまり、回路抵抗Rdllが下がる)。以下、増加後の消費電流IdllをIdll_aと称す。

【0040】

ステップC22:

DLL回路の消費電流Idllは、NMOSトランジスタVPERDのソース−ドレイン間電流でもある。

【0041】

消費電流Idllは増加し、Idll_aに変化したが、NMOSトランジスタVPERDの抵抗成分RTrはそのままである。

【0042】

ここで、消費電流Idllの増加前のNMOSトランジスタVPERDにおける電圧降下は以下で表される。

【0043】

RTr×Idll(電圧降下1と称す)

また、消費電流Idll_aへの増加後のNMOSトランジスタVPERDにおける電圧降下は以下で表される。

【0044】

RTr×Idll_a(電圧降下2と称す)

よって、DLL回路の消費電流Idllの増加直後は、電圧VPERDは、(電圧降下2−電圧降下1)分だけ低下する

ステップC23:

電圧VPERDは、カレントミラーアンプ31において、リファレンス電位との比較が行われ、リファレンス電位付近に再調整されるが、調整完了までにはタイムラグが残り、上記の(C−1)と同様にVPERD調整期間が発生する。

【0045】

ここで、消費電流Idllが変化する要因としては、例えば、ロック調整動作中に使用する遅延素子数が変化することなどが挙げられる。

【0046】

つまり、DLL回路のロック調整動作自体が消費電流の変化ひいては電圧VPERDの変化に直結することになる。

【0047】

上記の(C−1)と(C−2)のいずれの場合においても、電圧VPERDは、VPERD調整期間を経て、リファレンス電位付近に調整される。

【0048】

しかし、電圧VPERDがリファレンス電位付近に調整された際、DLL回路が既にロック調整動作を完了していれば、入力信号と出力信号の位相差が増大してしまう。

【課題を解決するための手段】

【0049】

本発明の半導体装置は、

縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、

リファレンス電位を基準として生成した出力電圧を、前記複数の遅延素子に供給する遅延素子用電源回路と、

前記出力電圧が前記リファレンス電位の一定範囲内にあるか否かを検出し、前記出力電圧が前記一定範囲内にない場合、前記ロック調整動作を停止させるDLL動作信号を前記DLL回路に出力する検出回路と、を有する。

【発明の効果】

【0050】

本発明によれば、遅延素子用電源回路の出力電圧がリファレンス電位の一定範囲内にあることを確認した後、DLL回路がロック調整動作を実施する。

【0051】

言い換えれば、外部電源電圧の変化等に起因して、遅延素子用電源回路の出力電圧に異常がある場合には、DLL回路がロック調整動作を停止する。

【0052】

そのため、遅延素子用電源回路の出力電圧(=遅延素子の動作電圧)の異常時に発生していた、入力信号と出力信号の位相差の増大を抑制できるという効果が得られる。

【図面の簡単な説明】

【0053】

【図1】本発明の一実施形態の半導体装置の構成を示す図である。

【図2】図1に示した検出回路の一構成例を示す図である。

【図3】図2に示した第1段カレントミラーアンプの一構成例を示す図である。

【図4A】ロック調整動作開始時のDLL回路の入力信号と出力信号の位相関係の一例を示す図である。

【図4B】ロック調整動作中のDLL回路の入力信号と出力信号の位相関係の一例を示す図である。

【図4C】ロック調整動作中のDLL回路の入力信号と出力信号の位相関係の一例を示す図である。

【図5】遅延素子用電源回路の一構成例を示す図である。

【図6】DLL回路の消費電流の変化に伴い、電圧VPERDが一時的に変化する様子を説明する図である。

【発明を実施するための形態】

【0054】

以下に、本発明を実施するための形態について図面を参照して説明する。

【0055】

図1は、本発明の一実施形態の半導体装置の構成を示す図である。

【0056】

図1に示すように、本実施形態の半導体装置は、DLL回路10と、検出回路20と、を有している。DLL回路10は、遅延素子用電源回路30を内部に備えている。

【0057】

DLL回路10は、縦続接続された複数の遅延素子(不図示)を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行う。

【0058】

遅延素子用電源回路30は、リファレンス電位を基準として生成した電圧VPERDを、複数の遅延素子に動作電圧として供給する。なお、遅延素子用電源回路30の構成は図5に示したものと同様である。

【0059】

検出回路20は、遅延素子用電源回路30の出力電圧である電圧VPERDがリファレンス電位の一定範囲内にあるか否かを検出し、検出結果に応じてDLL回路10のロック調整動作の可否を示すDLL動作信号をDLL回路10に出力する。

【0060】

具体的には、検出回路20は、電圧VPERDがリファレンス電位の一定範囲内にない場合、ロック調整動作を停止させることを示すDLL動作信号をDLL回路10に出力する。

【0061】

なお、以下では、DLL動作信号は、DLL回路10のカウンタ(不図示)の更新の可否を示す信号であるものとして説明する。

【0062】

図2は、図1に示した検出回路20の一構成例を示す図である。

【0063】

図2に示すように、検出回路20は、第1の比較回路21と、第2の比較回路22と、XOR回路23と、を有している。

【0064】

第1の比較回路21は、電圧VPERDがリファレンス電位の一定範囲の上限値よりも大きい場合にはHを、小さい場合にはLを、それぞれ出力する。

【0065】

第2の比較回路22は、電圧VPERDがリファレンス電位の一定範囲の下限値よりも大きい場合にはHを、小さい場合にはLを、それぞれ出力する。

【0066】

なお、本実施形態では、上記の上限値がリファレンス電位+10mVであり、上記の下限値がリファレンス電位−10mVであるものとして説明する。

【0067】

XOR回路23は、第1の比較回路21の出力と第2の比較回路22の出力とのXORを演算し、演算結果をDLL動作信号としてDLL回路10に出力する。

【0068】

ここで、XOR回路の演算結果がHである場合には、DLL回路10のカウンタの更新機能を有効化(つまり、ロック調整動作を実施)することを示すDLL動作信号が出力され、演算結果がLである場合には、DLL回路10のカウンタの更新機能を無効化(つまり、ロック調整動作を停止)することを示すDLL動作信号が出力されるが、その詳細は後述する。

【0069】

第1の比較回路21は、第1段カレントミラーアンプ21Aと、第2段カレントミラーアンプ21Bと、を有している。

【0070】

また、第2の比較回路22は、第1段カレントミラーアンプ22Aと、第2段カレントミラーアンプ22Bと、を有している。

【0071】

図3は、図2に示した第1段カレントミラーアンプ21A,22Aの一構成例を示す図である。

【0072】

図3に示すように、第1段カレントミラーアンプ21Aは、電圧VPERDとリファレンス電位+10mVとを比較し、比較結果に応じた電圧を出力する。

【0073】

第2段カレントミラーアンプ21Bは、第1段カレントミラーアンプ21Aの後段に縦続接続されており、第1段カレントミラーアンプ21Aからの電圧に応じたディジタル値H/LをXOR回路23に出力する。

【0074】

また、図3に示すように、第1段カレントミラーアンプ22Aは、電圧VPERDとリファレンス電位−10mVとを比較し、比較結果に応じた電圧を出力する。

【0075】

第2段カレントミラーアンプ22Bは、第1段カレントミラーアンプ22Aの後段に縦続接続されており、第1段カレントミラーアンプ22Aからの電圧に応じたディジタル値H/LをXOR回路23に出力する。

【0076】

以下、本発明の特徴部分である検出回路20の動作について説明する。

【0077】

第1の比較回路21および第2の比較回路22に入力される電圧VPERDは、大別して、以下の状態になりうる。

(1)電圧VPERD≒リファレンス電位

本実施形態では、リファレンス電位±10mVを想定している

(2)電圧VPERD<リファレンス電位−10mV

(3)電圧VPERD>リファレンス電位+10mV

以下、電圧VPERDが上記の(1)〜(3)の各々の状態のときのDLL回路10のロック調整動作の可否について説明する。

(1)電圧VPERD≒リファレンス電位

この状態では、第1の比較回路21および第2の比較回路22の出力は、一方がLで他方がHとなる。そのため、XOR回路23の出力(DLL動作信号)はHになる。

【0078】

よって、DLL回路10のカウンタの更新機能が有効化され、ロック調整動作が実施される。

【0079】

このとき、電圧VPERDは、リファレンス電位±10mV以内であるため、ロック調整動作を実施することは妥当と言える。

(2)電圧VPERD<リファレンス電位−10mV

この状態では、第1の比較回路21および第2の比較回路22の出力は共にLとなる。そのため、XOR回路23の出力(DLL動作信号)はLになる。

【0080】

よって、DLL回路10のカウンタの更新機能が無効化され、ロック調整動作が停止される。

【0081】

このとき、電圧VPERDは、リファレンス電位との差が−10mV以上であるため、ロック調整動作を停止することは妥当と言える。

(3)電圧VPERD>リファレンス電位+10mV

この状態では、第1の比較回路21および第2の比較回路22の出力は共にHとなる。そのため、XOR回路23の出力(DLL動作信号)はLになる。

【0082】

よって、DLL回路10のカウンタの更新機能が無効化され、ロック調整動作が停止される。

【0083】

このとき、電圧VPERDは、リファレンス電位との差が+10mV以上であるため、ロック調整動作を停止することは妥当と言える。

【0084】

上述したように本実施形態では、電圧VPERDがリファレンス電位±10mV以内の領域に存在する場合にのみ、DLL回路10のカウンタの更新機能を有効化してロック調整動作を実施させ、これ以外の場合には、DLL回路10のカウンタの更新機能を無効化してロック調整動作を停止させている。

【0085】

このように、電圧VPERDが一定範囲内に到達するのを待って、DLL回路10のロック調整動作を実施させることで、電圧VPERDの異常時に発生していた、入力信号と出力信号の位相差の増大を抑制できるという効果が得られる。

【0086】

なお、本実施形態では、検出回路20をXOR回路23を用いて構成する例を示したが、本発明はこれに限定されず、検出回路20の機能を実現しうる構成であれば、その他の構成でも構わない。

【符号の説明】

【0087】

10 DLL回路

20 検出回路

21 第1の比較回路

21A 第1段カレントミラーアンプ

21B 第2段カレントミラーアンプ

22 第2の比較回路

22A 第1段カレントミラーアンプ

22B 第2段カレントミラーアンプ

23 XOR回路

30 遅延素子用電源回路

31 カレントミラーアンプ

【特許請求の範囲】

【請求項1】

縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、

リファレンス電位を基準として生成した出力電圧を、前記複数の遅延素子に供給する遅延素子用電源回路と、

前記出力電圧が前記リファレンス電位の一定範囲内にあるか否かを検出し、前記出力電圧が前記一定範囲内にない場合、前記ロック調整動作を停止させるDLL動作信号を前記DLL回路に出力する検出回路と、を有する半導体回路。

【請求項2】

前記検出回路は、

前記出力電圧が前記一定範囲の上限値よりも大きい場合にはHを、小さい場合にはLを、それぞれ出力する第1の比較回路と、

前記出力電圧が前記一定範囲の下限値よりも大きい場合にはHを、小さい場合にはLを、それぞれ出力する第2の比較回路と、

前記第1の比較回路の出力と前記第2の比較回路の出力とのXORを演算するXOR回路と、を有し、

前記XOR回路の演算結果Hが、前記DLL回路の前記ロック調整動作を停止させる前記DLL動作信号となる、請求項1に記載の半導体装置。

【請求項1】

縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、

リファレンス電位を基準として生成した出力電圧を、前記複数の遅延素子に供給する遅延素子用電源回路と、

前記出力電圧が前記リファレンス電位の一定範囲内にあるか否かを検出し、前記出力電圧が前記一定範囲内にない場合、前記ロック調整動作を停止させるDLL動作信号を前記DLL回路に出力する検出回路と、を有する半導体回路。

【請求項2】

前記検出回路は、

前記出力電圧が前記一定範囲の上限値よりも大きい場合にはHを、小さい場合にはLを、それぞれ出力する第1の比較回路と、

前記出力電圧が前記一定範囲の下限値よりも大きい場合にはHを、小さい場合にはLを、それぞれ出力する第2の比較回路と、

前記第1の比較回路の出力と前記第2の比較回路の出力とのXORを演算するXOR回路と、を有し、

前記XOR回路の演算結果Hが、前記DLL回路の前記ロック調整動作を停止させる前記DLL動作信号となる、請求項1に記載の半導体装置。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図5】

【図6】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図5】

【図6】

【公開番号】特開2012−195834(P2012−195834A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2011−59378(P2011−59378)

【出願日】平成23年3月17日(2011.3.17)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成23年3月17日(2011.3.17)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]