半導体装置

【課題】とりわけ表面マークの下部に配線タングステンパッドがある場合でも、表面マークのコントラスト低下を抑制する。

【解決手段】メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多層配線構造を備える。各配線層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。第1のダミーパターンDP1は、第1アルミニウム配線階層1AlLに形成され、第2層間絶縁膜316に覆われている。第2のダミーパターンDP2は、第2アルミニウム配線階層2AlLに形成され、第3層間絶縁膜317に覆われている。第2ダミーパターンDP2は、第1ダミーパターンDP1よりも幅が長い。

【解決手段】メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多層配線構造を備える。各配線層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。第1のダミーパターンDP1は、第1アルミニウム配線階層1AlLに形成され、第2層間絶縁膜316に覆われている。第2のダミーパターンDP2は、第2アルミニウム配線階層2AlLに形成され、第3層間絶縁膜317に覆われている。第2ダミーパターンDP2は、第1ダミーパターンDP1よりも幅が長い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関するものである。

【背景技術】

【0002】

図20は、従来における半導体装置の概略構成を示す断面図である。同図に示された半導体装置1pは、CoC(Chip on Chip)型の積層型半導体装置である。

【0003】

半導体装置1pは、配線基板2と、この配線基板2の一面に搭載されたチップ積層体3pとを備えている。このチップ積層体3pは、複数のメモリチップ31pa〜31pdとインターフェースチップ32pを有している。メモリチップ31pa〜31pd、インターフェースチップ32pのそれぞれは、表面バンプ電極311とこれに対応する裏面バンプ電極312とを備え、さらに、表面バンプ電極311と裏面バンプ電極312とは貫通電極4により電気的に接続されている。また、複数のメモリチップ31pa〜31pd、インターフェースチップ32pは、表面バンプ電極311、裏面バンプ電極312、及び、貫通電極4を介して互いに電気的に接続されている。

【0004】

更に、インターフェースチップ32p、の一面(図20における下側の面)の表面バンプ電極311は、配線基板2の電極パッド23に接続されている。

【0005】

次に、図20に示した半導体装置1pの組み立て工程について説明する。図21は、組み立て工程を説明するための図である。

【0006】

ステージ99上に保持されたメモリチップ31pa上に、図21に示すように、メモリチップ(2段目の半導体チップ)31pbを積層搭載する。

【0007】

ここで、メモリチップ31pa〜31pd、インターフェースチップ32pのそれぞれは、チップ表面側と裏面側とにそれぞれ表面マークと裏面マークとを有している。これら表面マークと裏面マークとは、半導体チップを積層する際の位置合わせに用いられる。具体的には、メモリチップ31paの表面マークを、フリップチップボンダーの基板側認識カメラで撮影し、半導体チップ31paのステージ上での座標を認識する。フリップチップボンダーのツールBTでピックアップされたメモリチップ31pbの裏面マークを、フリップチップボンダーの部品側認識カメラで撮影し、メモリチップ31pbのツール上での座標を認識する。得られた位置情報に応じて、メモリチップ31paの表面バンプ電極311とメモリチップ31pbの裏面バンプ電極312が正確に重なるように、ステージに対するツールの位置を調整して積層搭載する。

【0008】

同様に、メモリチップ(3段目及び4断面の半導体チップ)31pc及び31pd、インターフェースチップ(5段目の半導体チップ)32pが積層搭載される。

【0009】

上述のように、半導体チップ間の正確な位置合わせを行うために、表面マーク及び裏面マークが採用されている。

【0010】

図22は、メモリチップ31pのマーク部分の断面図である。

図22の断面図に示すように、メモリチップ31pは、配線タングステンWT、第1、第2、第3アルミニウム配線1ALp,2ALp,3ALを備える多層配線構造を備える。

【0011】

更に、図22に示すように、メモリチップ31pの表面側には第3アルミニウム配線3ALからなる表面マーク313が形成され、また、その下部には、裏面マーク用貫通電極TSV(Through−Silicon Via)に接続された配線タングステンWTが形成されている。裏面マーク用貫通電極TSVには、更に裏面バンプ電極312が接続されており、裏面マーク用貫通電極TSVと裏面バンプ電極312とで、裏面マーク314を形成している。裏面マーク用貫通電極TSVは、半導体基板319を貫通している。また、多層配線構造の上には、ポリイミド(PI)膜が形成されている。このポリイミド膜PIは、表面マーク313の上部を含む領域に形成されたPI開口部PIOを有している。

【0012】

ここで、最近の半導体プロセスでは、平坦化するために化学機械的研磨(CMP:Chemical Mechanical Polishing)技術が使用される。このCMP工程では、パターンが密な部分と疎な部分との研磨状態の差を補正する目的で、疎な部分にはダミーパターンを配置するのが一般的である。PI開口部の左右にある第1及び第2アルミニウム配線、配線タングステン、ゲート、シャロウ・トレンチ・アイソレーションSTI(Shallow Trench Isolation)の微小パターンが、そのCMPダミーパターンである。

【0013】

しかしながら、従来は、主に以下の2つの理由により、PI開口部PIOの下部へのダミーパターンの配置を禁止していた。第一には、第1及び第2アルミニウム配線の配線層の微小なダミーパターンが、第3アルミニウム配線3ALの表面マーク313の認識の障害になる場合があるからである。第二には、配線タングステンパッドWTの下には、裏面マーク用貫通電極TSVがあるので、ここにゲートなどの微小パターンが存在すると、裏面マーク用貫通電極TSVのドライエッチング工程で微小パターンのゲートがハードマスクとなってパーティクル(塵)の発生原因となる場合があるからである。

【0014】

従って、ここでの説明の表面マークの部分においても、禁止領域PAを設けている。なお、図22において、そのCMPダミーパターン禁止領域PAは、PI開口部PIOとほぼ一致(詳細は後述)させている。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2006−140300号公報

【特許文献2】特開2007−088124号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

しかしながら、上述の組み立て工程において、自チップを積層半導体装置に組み込む際の認識カメラでの表面マーク313の認識において、表面マーク313のコントラストが著しく低下することがあることが、発明者の研究で明らかとなった。

【0017】

図23は、照明の入射光(実線)及び反射光(破線)を記したPI開口部PIOを示す断面図である。配線タングステンWTのパット上部のPI開口部PIOでは、酸化ケイ素(SiO2)などの誘電体のみしか存在しないため、可視光の減衰は非常に小さい。このため、表面マーク313の背景となる配線タングステンパッド(WTP)からの反射が大きく、表面マーク313のコントラストが著しく低下するという問題があった。

【0018】

その結果、TSV積層工程で表面マーク313の認識エラーが発生し、前述の組み立て工程のスループットが著しく劣化するという問題があった。

【0019】

かかる技術的内容に関連する文献として特許文献1及び2がある。

特許文献1においては、半導体基板上に多層の回路パターンを形成する際に、露光によって形成されたレジストパターンが正確に下層の回路パターンに対して重ね合わせられているかを検査するために精度測定マークについて、下層に形成された主尺パターンがCMP時のディッシングの影響を受けないようにするために、主尺パターンが形成された配線層の下層の配線層のマーク形成領域にダミーパターンを形成することが開示されている。

【0020】

また、特許文献2には、実装基板のアライメントマークについて記載されている。

しかしながら、特許文献1には、あくまで、デバイス形成層形成時のレジストパターンの位置合わせに使用する精度測定マークについて開示しているのみである。従って、特許文献1には、半導体チップ形成後のアライメントマークの認識については何ら記載されておらず、さらに、精度測定マークに対して対称に配置されたマーク等の記載がなく、積層半導体装置の半導体チップに関するものではない。

【0021】

また、特許文献2は、あくまで、フレキシブル基板にデバイスを実装する場合のアラインメントマークについて開示されているだけであり、積層半導体装置の半導体チップに関するものではない。

【課題を解決するための手段】

【0022】

本発明の半導体装置は、第1の配線階層と、当該第1の配線階層の上方に形成された第2の配線階層と、当該第2の配線階層の上方に形成された第3の配線階層とを含む多階層配線構造であって、第1の配線階層として形成された第1の配線層と、前記第1の配線層の上部に位置する領域に前記第2の配線階層として形成された複数の第1のパターンと、前記第1の配線層の上部に位置する領域に前記第3の配線階層として形成された第1のマークとを含む、前記多階層配線構造を備えることを特徴とする。

【発明の効果】

【0023】

本発明の半導体装置によれば、とりわけ第1のマークの下部に複数の第1のパターンがある場合でも、第1のマークのコントラスト低下を抑制することにより、自半導体チップの積層工程で、マーク認識エラーを回避でき、スループットが向上する。

【図面の簡単な説明】

【0024】

【図1】本発明における半導体装置の概略構成を示す断面図である。

【図2A】本発明の第一実施形態のメモリチップの回路形成面(表面)から見た平面模式図である。

【図2B】本発明の第一実施形態のメモリチップの半導体基板側(裏面)から見た平面模式図である。

【図3A】本発明の第一実施形態のメモリチップの配線貫通電極部分の断面図である。

【図3B】本発明の第一実施形態のメモリチップのマーク部分の断面図である。

【図4A】本発明の第一実施形態のメモリチップの回路形成面(表面)側から見た表面マーク部分の概略平面図である。

【図4B】本発明の第一実施形態のメモリチップの回路形成面(表面)側から見た表面マーク部分の出来上がり状態を示した概略平面図である。

【図4C】本発明の第一実施形態のメモリチップの半導体基板側(裏面)から見た裏面マーク部分の概略平面図である。

【図4D】表面側から見た配線貫通電極の第2アルミニウム配線階層より下の階層の平面概略図である。

【図4E】第2アルミニウム配線階層以上の階層の平面概略図である。

【図4F】裏面から見た裏面バンプの平面概略図である。

【図5】本発明における照明の入射光(実線)及び反射光(破線)を記したPI開口部を示す断面図である。

【図6A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図6B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図6C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図7A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図7B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図7C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図8A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図8B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図8C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図8D】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図9A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図9B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図9C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図10A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図10B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図11A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図11B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図11C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図12A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図12B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図13A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図13B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図13C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図14】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図15A】組み立て工程を説明するための図である。

【図15B】組み立て工程を説明するための図である。

【図15C】組み立て工程を説明するための図である。

【図16】本発明の第二実施形態のメモリチップにおけるダミーパターンを説明するための図である。

【図17】本発明の第三実施形態のメモリチップにおけるダミーパターンを説明するための図である。

【図18】本発明のメモリチップの変形例を説明するための図である。

【図19A】マークの形状の他の例を示す図である。

【図19B】マークの形状の他の例を示す図である。

【図19C】マークの形状の他の例を示す図である。

【図19D】マークの形状の他の例を示す図である。

【図20】従来の半導体装置の概略構成を示す断面図である。

【図21】組み立て工程を説明するための図である。

【図22】従来のメモリチップのマーク部分の断面図である。

【図23】従来における照明の入射光(実線)及び反射光(破線)を記したPI開口部を示す断面図である。

【発明を実施するための形態】

【0025】

以下、図面を参照して、本発明の実施の形態について詳細に説明する。

<第一実施形態>

図1は、本発明における半導体装置の概略構成を示す断面図である。同図に示された半導体装置1は、CoC型の積層型半導体装置である。

【0026】

具体的には、半導体装置1は、略四角形で所定の配線が形成された配線基板2を有している。この配線基板2は、例えば0.2mm厚のガラスエポキシ基板であり、絶縁基材21の両面に所定の配線が形成され、その配線は部分的に絶縁膜22、例えばソルダーレジスト、で覆われている。また、配線基板2の一面の中央領域には開口部が形成されており、絶縁膜(ソルダーレジスト)22の開口部から露出された部位には、複数の接続パッド23が形成されている。一方、配線基板2の他面の配線の絶縁膜22から露出された部位には、複数のランド24が形成されている。ここで、接続パッド23と、これに対応するランド24とは、配線基板2の配線によりそれぞれ電気的に接続されている。

【0027】

また、配線基板2の一面には、チップ積層体3が搭載されている。チップ積層体3は、例えば略四角形の板状で、一面に所定の回路が形成された半導体チップが、複数個、積層された構成となっている。図1に示した半導体装置においては、例えばメモリ回路が形成された4つのメモリチップ31a〜31dと、メモリチップ31と配線基板2とのインターフェースを取るためのインターフェースチップ32を5段積層したものである。それぞれの半導体チップは、例えば50μm厚で構成されており、一面の中央領域に複数の表面バンプ電極311と、他面側の中央領域に複数の裏面バンプ電極312が形成されている。表面バンプ電極311とこれに対応する裏面バンプ電極312とは貫通配線4により電気的に接続されている。

【0028】

また、チップ積層体3には、例えばアンダーフィル材からなる第1の封止樹脂部5が形成されている。この封止樹脂部5は、それぞれの半導体チップの間の隙間を充填するように形成されている。

【0029】

更に、チップ積層体3の最下の半導体チップの一面(図1における下側の面)の表面バンプ電極311は、ワイヤバンプ25を介して、配線基板2の接続パッド23に接続されている。

【0030】

また、チップ積層体3と配線基板2との電気的接続部の周囲には、NCP(Non Conductive Paste)6が配置されており、電気的接合部の保護と、チップ積層体3と配線基板2との接着固定するように構成されている。更に、配線基板2の一面上には、チップ積層体3を覆うように第2の封止樹脂層7が形成されている。

【0031】

また、配線基板2の他面の複数のランド24には、半導体装置1の外部端子となる半田ボール8がそれぞれ搭載されており、外部端子は所定の間隔で格子状に配置されている。

【0032】

次に、本発明の第一実施形態のメモリチップ31について説明する。図2A及び図2Bは、メモリチップ31の平面模式図であり、図2Aはその回路形成面(表面)から見た図であり、図2Bはその半導体基板側(裏面)から見た図である。

【0033】

図2Aに示されるように、メモリチップ31の回路形成面には、y方向中央部に、配線貫通電極41がx方向に沿って配置されている。また、メモリチップ31の回路形成面の2つの長辺(図中x方向に延伸する辺)のそれぞれに沿って、複数のダミーバンプ貫通電極42が配置されている。このダミーバンプ貫通電極42は、応力によってメモリチップ31が破損することを防ぐために設けられている。さらに、互いに対角に位置する1組の角部に、その回路形成面側から見えるように、表面マーク313が配置されている。好ましくは、表面マーク313は、複数のダミーバンプ貫通電極42が配置される領域内、つまり、複数のダミーバンプ貫通電極42を通過する直線上に配置される。

【0034】

また、図2Bに示されるように、メモリチップ31の半導体基板側には、y方向中央部に、配線貫通電極41がx方向に沿って配置されている。また、メモリチップ31の半導体基板側の2つの長辺(図中x方向に延伸する辺)のそれぞれに沿って、複数のダミーバンプ貫通電極42が配置されている。さらに、互いに対角に位置する1組の角部に、その半導体基板側から見えるように、裏面マーク314が配置されている。各組の表面マーク313及び裏面マーク314は、互いに半導体基板を挟んで対向する位置に設けられる。好ましくは、表面マーク313は、複数のダミーバンプ貫通電極42が配置される領域内、つまり、複数のダミーバンプ貫通電極42を通過する直線上に配置される。

【0035】

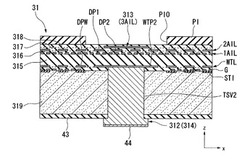

図3A及び図3Bは、メモリチップ31の配線貫通電極41の周辺部分(ダミーバンプ用貫通電極部分も実質的に同一)及び表面マーク313並びに裏面マーク314の周辺部分(以下単にマーク部分と記載する場合もある)の断面図である。

【0036】

図3Aに、配線貫通電極41部分の周辺の断面図を、図3Bには、マーク部分の断面図をそれぞれ示す。図3A及び図3Bに示すように、メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多階層配線構造を備える。各配線階層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。また、半導体基板319を貫通して貫通電極TSV1又はマーク用貫通電極TSV2が形成されている。

【0037】

図3Aに示すように、配線貫通電極41部分の回路形成面(表面)側においては、ポリイミド膜PIに形成された開口部PIOに表面バンプ26と銅ピラー27からなる表面バンプ電極311が形成され、この表面バンプ電極311がカバー開口28を介して第3アルミニウム配線階層3AlLとして形成された配線パッドMWLPに電気的に接続される。

【0038】

さらに、配線パッドMWLPは第3層間絶縁膜317中に形成された第3スルーホールTH3を介して第2アルミニウム配線階層2AlLとして形成された第2金属配線MWL2に接続され、第2金属配線MWLは、第2絶縁膜316中に形成された第2スルーホールTH2を介して第1アルミニウム配線階層1AlLとして形成された第1金属配線MWL1に接続される。第1金属配線MWL1は、第1層間絶縁膜315中に形成された第1スルーホールTH1を介して配線タングステン階層WTLとして形成された配線タングステンパッドWTP1に接続され、配線タングステンパッドWTP1が配線貫通電極TSV1に接続される。また、配線貫通電極41部分では、半導体基板319中に配線貫通電極TSV1を囲むように絶縁トレンチ29が形成されている。

【0039】

配線貫通電極部分の半導体基板側の面(裏面)には、裏面絶縁膜43及び裏面バンプ44が形成されており、裏面バンプ44は、配線貫通電極TSV1と接続されている。

【0040】

図3Aに示すように、配線貫通電極部分では、配線タングステン階層WTL、第1、第2アルミニウム配線階層1AlL、2AlLのそれぞれの配線階層として、実質的な機能配線(配線タングステンパッドWTP1、第1、第2金属配線MWL1,2)のほかに、複数のダミー配線(ダミーパターン)DPW、DP1、DP2が形成されている。

【0041】

ここで、実質的な機能配線とは、それぞれ電源電位や信号レベル等を伝播するための配線であり、それぞれ対応する電源レベルや信号レベルに応じた所望の電位が供給される配線である。

【0042】

これに対して、ダミー配線(ダミーパターン)DPW、DP1、DP2は、CMP(Chemical Mechanical Polishing)法により層間絶縁膜を平坦化する際に機能配線が存在しない領域において「ディッシング」が生じることを防止するために配置されるものであり、そのため、電源電位や信号レベル等に応じた所望の電位は供給されず、フローティング状態とされている配線である。

【0043】

尚、図3Aにおいては、機能配線として、配線貫通電極TSV1に接続されたものだけを示したが、これに限定されるものではない。例えば、図3Aに示す複数のダミー配線(ダミーパターン)DPW,DP1,DP2に混じって、機能配線が配置されていてもよい。

【0044】

一方、図3Bに示すように、マーク部分の表面側においては、ポリイミド膜PIに形成された開口部PIOの下部に位置する第3アルミニウム配線階層3AlLとして表面マーク313が形成され、さらに、開口部PIOの下部に位置する配線タングステン階層WTLとしては、配線タングステンパッドWTP2が形成されおり、配線タングステンパッドWTLP2がマーク用貫通電極TSV2に接続されている。また、マーク部分の裏面側においては、裏面マークが形成された裏面バンプ44がマーク用貫通電極TSV2の下部に形成されている。

【0045】

また、マーク部分においては、第1のダミーパターン(下層のダミーパターン)DP1が、第1アルミニウム配線階層1AlLとして、第2層間絶縁膜316に覆われて(つまり、第2層間絶縁膜316を貫通していない)形成され、第2のダミーパターン(上層のダミーパターン)DP2が、第2アルミニウム配線階層2AlLとして、第3層間絶縁膜317に覆われて(つまり、第3層間絶縁膜317を貫通していない)形成されている。第2ダミーパターンは、第1ダミーパターンよりも幅(図面x方向の長さ)が長い。好ましくは、配線タングステンパッドWTP2の上部の領域の第1及び第2アルミニウム配線階層1AlL、2AlLには、機能配線が配置されない。

【0046】

ここで、発明者は、マークのコントラストについて調べる過程で、マークを認識するためのカメラの画像を調査したところ、当該カメラの解像度(約1μm程度)では、CMPダミーパターンに非常に微小なために全く認識されず、開口部PIOのエッジ部分から露出しているCMPダミーパターン部分は、他の背景よりも暗く認識されることを見出した。つまり、カメラの分解能よりも小さい微小パターンは、マークに近接して配置してもマークの認識の障害にはならず、むしろコントラストの改善に役立つことを見出した。

【0047】

図4Aは、メモリチップの回路形成面(表面)側から見た表面マーク313部分のポリイミド膜PIを除いた場合の概略平面図であり、図4Bは、ポリイミド膜PIを含む概略平面図である。また、図4Cは、メモリチップの半導体基板側(裏面)から見た裏面マーク314部分の概略平面図である。

【0048】

表面マーク313は、図4Aに示すように、第3アルミニウム配線階層3AlLとして形成されたL字型のマークであり、図3Bに示すように、その領域に対応するポリイミド膜PIは、表面マーク313が露出するように開口されている。また、図3Bに示すように、下部には、配線タングステン階層WTLとして形成されマーク用貫通電極TSV2に接続された配線タングステンパッドWTP2が形成されている。マーク用貫通電極TSV2には、更に裏面バンプ電極312が接続されており、図4Cに示すように、マーク用貫通電極TSV2と裏面バンプ電極312とで、L字型の裏面マーク314を形成している。マーク用貫通電極TSV2は、半導体基板319を貫通している。

【0049】

ここで、本発明の半導体装置の第一実施形態におけるチップにおいては、図3B、図4A及び図4Bに示すように、ポリイミド膜PIに形成された開口部PIOの下部(表面マークの下部を含む)領域(即ち、配線タングステン階層WTLとして形成された配線タングステンパッドWTP2の上部の領域)にも、第1及び第2のダミー配線(ダミーパターン)DP1,DP2が、それぞれ第1及び第2アルミニウム配線階層1AlL及び2AlLとして形成されている。なお、このポリイミド膜PIに形成された開口部PIOの下部領域(配線タングステンパッドWTP2の上部の領域を含む)のうちでダミー配線(ダミーパターン)DP1,DP2が形成される配線階層は、配線タングステン階層WTLより上部、即ち、第1及び第2アルミニウム配線階層1AlL及び2AlLのみであり、配線タングステン階層WTL、ゲートG、及びSTIについては、ダミーパターンを排除する。

【0050】

ここで、それぞれ、配線タングステン配線階層WTLが第1の配線階層に、第1アルミニウム配線階層1AlLが第2の配線階層に、第3アルミニウム配線階層3AlLが第3の配線階層に対応している。また、表面マーク313及び裏面マーク314が、それぞれ、第1のマーク及び第2のマークに対応している。

【0051】

図5は、本発明における照明の入射光(実線)及び反射光(破線)を記した断面図である。同図においては、外部からの照明光は、第2アルミニウム配線階層2AlLとしての複数のダミーパターンDP2の間を透過した光は、第1アルミニウム配線階層1AlLとしての複数のダミーパターンDP1で散乱されるものと、第1アルミニウム配線階層1AlLとしての複数のダミーパターンDP1の間を透過するものに分かれる。第1アルミニウム配線階層1AlLとしての複数のダミーパターンDP1の間を透過したものは、配線タングステン階層WTLとしての配線タングステンパッドWTP2で反射されるが、第1アルミニウム配線階層1AlL、第2アルミニウム配線階層2AlLとしての複数のダミーパターンDP1,DP2で散乱される。このため、外部から見たときの反射率が大幅に低下する。ダミーパターン自体は一種の回折格子を形成することになるので、複数のダミーパターンDP1,DP2間の間隔(ピッチ)を第1アルミニウム配線階層1AlLと第2アルミニウム配線階層2AlLとで互いに異ならせることは、マーク背景の反射率低下により効果的である。

【0052】

また、図4D〜図4Fに、マーク部分との比較として、配線貫通電極42の部分の表面側及び裏面側から見た平面図を示す。図4Dは、表面側から見た配線貫通電極42の第2アルミニウム配線階層2AlLより下の階層の平面概略図であり、図4Eは、第2アルミニウム配線階層2AlL以上の階層の平面概略図であり、図4Fは、裏面から見た裏面バンプ44の平面概略図である。

【0053】

図4A及び図4Bと、図4C及び図4Dとを比べると、図4A及び図4Bはマーク部分の配線タングステンパッドWTP2が矩形をしているのに対し、図4C及び図4Dは配線貫通電極部分の配線タングステンパッドWTP1は円形をしている。

【0054】

また、図3A及び図3Bに示すように、好ましくは、マーク部分の配線タングステンパッドWTP2の大きさは、配線貫通電極部分の配線タングステンパッドWTP1の大きさよりも大きいほうがよい。これは、カメラ等で認識するために充分な大きさの裏面マーク314を形成するためには、図4Cに示すマーク用貫通電極TSV2を配線貫通電極TSV1よりも大きなサイズにする必要があるためである。

【0055】

次に、本発明の第一実施形態のメモリチップ31の製造方法について説明する。図6〜図14は、メモリチップ31の製造方法を順に説明するための図である。

【0056】

まず、図6Aに示された製造ステップは、半導体基板319の一面(表面、回路形成面側)に、多階層配線構造の一部である配線タングステン階層WTL(配線タングステンパッドWTP2を含む)、アクティブ素子、キャパシタを形成する工程が完了した状態で、これら配線タングステン階層WTL、アクティブ素子、キャパシタを覆うように第1層間絶縁膜315を形成した状態を示している。これ以降、多層配線構造の形成を行っていく。この図では、図示していない第1スルーホールのビアが形成される。

【0057】

図6Bは、図6Aを表面側から見た平面概略図である。尚、以降、本実施例の製造方法の説明中の平面概略図においては、図4A〜図4Cに示したポリイミド膜PIに形成された開口部PIOの下部に対応する領域について記載するものとする。また、本実施例の製造方法の説明中の平面概略図においては、配線階層の形状を見やすくするために層間絶縁膜の記載を省略している。

【0058】

図6Cに示された製造ステップは、第1アルミニウム配線階層1AlLの成長過程を示しており、第1層間絶縁膜315上に、バリアメタル、アルミニウム、反射防止膜などの積層メタル層をスパッタなどで成長させる。

【0059】

図7Aの製造ステップにおいては、積層メタル層上にフォトレジストPRを塗布し、レチクルなどを用いてパターン形成する。次に、図7Bの製造ステップにおいては、フォトレジストPRをマスクとして積層メタル層をドライエッチすることで第1アルミニウム配線階層1AlLを形成する。この際、表面マーク313が形成される領域の下部を含む領域(図7Bの配線タングステンパッドWTP2上の領域)に、第1ダミーパターンDP1が形成される。その上に、第1ダミーパターンDP1を含む第1アルミニウム配線階層1AlLを覆うように第2層間絶縁膜316を形成する。絶縁膜はSiO2などの酸化膜である。この図では図示していない第2スルーホールのビアが形成される。

【0060】

図7Cは、図7Bを表面側から見た平面概略図である。配線タングステン階層WTLに形成された配線タングステンパッドWTP2の上部を含む領域に、第1アルミニウム配線階層1AlLに形成された複数の第1ダミーパターンDP1が形成される。

【0061】

次に、図8Aの製造ステップにおいては、第2アルミニウム配線階層2AlLのパターンを形成して第3層間絶縁膜317を形成する。この工程は第1アルミニウム配線階層1AlLの形成の場合と同様である。第2層間絶縁膜316上の表面マーク313が形成される領域の下部を含む領域には、複数の第2ダミーパターンDP2が形成される。絶縁膜はSiO2などの酸化膜である。複数の第2ダミーパターンDP2を含む第2アルミニウム配線階層2AlLを覆うように第3層間絶縁膜317が形成される。この図では図示していない第3スルーホールのビアが形成される。

【0062】

図8Bは、図8Aを表面側から見た平面概略図である。配線タングステン階層WTLに形成された配線タングステンパッドWTP2の上部を含む領域に、第2アルミニウム配線階層2AlLに形成された複数の第2ダミーパターンDP2が形成される。

【0063】

次に、図8Cの製造ステップにおいては、第3層間絶縁膜317上に、表面マーク313を含む第3アルミニウム配線階層3AlLが形成される。更に、第3アルミニウム配線3ALを覆う第4層間絶縁膜318を形成する。なお、第4層間絶縁膜318は、パッシベーション膜とも呼ばれ、水分の浸入などを防止するため、緻密なSi3O4などのナイトライド膜や、SiONなどの酸窒化膜である。

【0064】

図8Dは、図8Cを表面側から見た平面概略図である。配線タングステン階層WTLに形成された配線タングステンパッドWTP2の上部を含む領域に、第3アルミニウム配線階層3AlLに形成されたL字状の表面マーク313が形成される。尚、図7C、図8Aに示したように、本実施形態においては、表面マーク313の下部にも第1及び第2のダミーパターンDP1,DP2が形成されている。

【0065】

次に、図9Aの製造ステップにおいては、第4層間絶縁膜318上に樹脂層であるポリイミド(PI)層PIを形成し、更に、形成したポリイミド層PIに、表面マーク313と第4層間絶縁膜318のうちの表面マーク313を覆う部分を露出させる開口部PIOを形成する。

【0066】

図9Bは、図9Aを表面側から見た平面概略図である。ポリイミド膜PIに形成された開口部PIOは、表面マーク313、複数の第2のダミーパターンDP2の一部、複数の第1のダミーパターンDP1の一部、及び、配線タングステンパッドWTP2が形成された上部領域に形成される。

【0067】

次に、図9Cの製造ステップにおいては、表面バンプ形成までの配線工程が完了したウエハ表面に、SiO2などで形成された支持体(Wafer Support System; WSS)321を接着剤320で貼り付ける。この接着剤320としては、紫外線などでウエハから剥離可能なものを用いる。

【0068】

次に、図10Aの製造ステップにおいては、ウエハ裏面を研削して50〜20um程度まで薄くする。裏面には金属汚染防止のため、Si3N4などのナイトライドの絶縁膜322を形成する。なお、このステップから裏面側の加工のため、説明の便宜上、同図から以降、上下反転している。

【0069】

次に、図10Bの製造ステップにおいては、マーク用貫通電極TSV2を形成するため、フォトレジストPRを塗布して開口パターン330形成する。

【0070】

次に、図11Aの製造ステップにおいては、フォトレジストPRをマスクとして、ドライエッチで配線タングステンパッドWTP2までマーク用貫通電極TSV2の開口部331を形成する。

【0071】

図11Bは、図11Aを裏面側から見た平面概略図であり、ドライエッチにより矩形の開口部331a、331bが形成されている。

【0072】

次に、図11Cの製造ステップにおいては、フォトレジストPRの除去後に、開口部33(331a、331b)の側壁及びマーク用貫通電極TSV2底部の配線タングステンパッドWTP2上を含めて、ウエハ裏面全面にTi/Cuなどのシード膜323をスパッタなどで形成する。

【0073】

次に、図12Aの製造ステップにおいては、裏面マーク314を含む裏面バンプ電極312を形成するため、フォトレジストPRを塗布して開口パターン332を形成する。

【0074】

次に、図12Bの製造ステップにおいては、シード膜323を電極として、Cuめっき324を成長させてマーク用貫通電極TSV2のビアの充填と裏面バンプ電極312のピラーを形成する。

【0075】

次に、図13Aの製造ステップにおいては、裏面バンプ44を含む裏面バンプ電極312として、SnAgはんだをめっきで形成する。

【0076】

次に、図13Bの製造ステップにおいては、フォトレジストPRを除去し、更にシード膜323をウェットエッチ等で除去する。

【0077】

図13Cは、図13Bを裏面側から見た平面概略図である。L字型の裏面マーク314が形成されている。次に、図14の製造ステップにおいては、支持体321から紫外線等でデマウントする。

【0078】

次に、図1に示した半導体装置1の組み立て工程について説明する。図15A〜図15Cは、組み立て工程を説明するための図である。

【0079】

図15Aに示すように、吸着ステージ99には凹部991が形成されており、メモリチップ(1段目の半導体チップ)31paが、回路形成面を上方に向けて当該凹部991内に載置される。そして、図示しない真空装置により真空吸引することで、吸着ステージ99上に載置されたメモリチップ31aが保持固定される。

【0080】

次に、このように吸着ステージ99上に保持されたメモリチップ31a上に、図15Bに示すように、ボンディングツールBTにより高温、例えば300℃程度、で荷重を印加することで、メモリチップ(2段目の半導体チップ)31bを積層搭載する。

【0081】

この際、各メモリチップ31a、31bの積層位置を合わせるために、吸着ステージ99上に配置されたメモリチップ31aの表面マーク313を、フリップチップボンダーの基板側認識カメラで撮影し、半導体チップ31aのステージ上での座標を認識する。フリップチップボンダーのツールでピックアップされたメモリチップ31bの裏面マーク314を、フリップチップボンダーの部品側認識カメラで撮影し、メモリチップ31bのツール上での座標を認識する。得られた位置情報に応じて、メモリチップ31aの表面バンプ電極311とメモリチップ31bの裏面バンプ電極312が正確に重なるように、ステージに対するツールの位置を調整して積層搭載する。

【0082】

メモリチップ31bは、メモリチップ31aと同様なメモリチップであり、メモリチップ31aの一面の表面バンプ電極311と、メモリチップ31bの他面の対応する裏面バンプ電極312とを、熱圧着により電気的に接続することで、メモリチップ31aの一面側にメモリチップ31bが積層搭載される。このように、それぞれのメモリチップをバンプ電極で接続することで、メモリチップ間に隙間が形成される。

【0083】

同様に、メモリチップ(3段目及び4断面の半導体チップ)31c及び31d、インターフェースチップ(5段目の半導体チップ)32が積層搭載され、図15Cに示すような、例えば4つのメモリチップ31a〜31dとインターフェースチップ32が積層されたチップ積層体3が形成される。

【0084】

なお、インターフェースチップ32においては、他面側の裏面バンプ電極312はメモリチップ31dの表面バンプ電極311に対応して配置され、表面側の表面バンプ電極311は、配線基板2の接続パッド23に搭載するため、60〜200μm程度の広いピッチで、表面バンプ電極311が配置されている。

【0085】

その後、各チップ間へのアンダーフィルの挿入形成を経て、更に、組み立て工程にて配線基板2に搭載され、半田ボール8が取り付けられることで、図1に示した半導体装置1となる。

【0086】

本発明における半導体装置においては、前述のように、メモリチップ31(31a〜31d)の表面マーク313の下側に位置する第1アルミニウム配線階層1AlL及び第2アルミニウム配線階層2AlLは、ともに認識カメラの解像度よりも小さい大きさ、つまり、認識カメラには認識されないサイズのダミーパターンDP1,DP2を形成しているため、組み立て工程においては、従来よりも表面マーク313を高いコントラストで識別することが可能となっている。ここで、特に、新たな工程を追加することなしに、表面マーク313のコントラスト低下を抑制することができることが顕著な特徴である。

【0087】

以上のように表面マーク313のコントラスト低下を抑制して、識別が容易になれば、図15A〜図15Cに示した組み立て工程において、各チップ間の位置合わせが容易となる。

特に、TSV積層用チップのように、表面マーク313の下部に配線タングステンパッドWTPを配置する必要がある場合に有効である。

【0088】

<第二実施形態>

次に、本発明の第二実施形態のメモリチップについて説明する。

半導体装置の全体構成としては、図1に示した半導体装置1の全体構成と同じである。第一実施形態と異なる点は、図4Bに示す第一実施形態においては、CMPダミーパターンDP1,DP2を採用しているが、本第二実施形態においては、その代わりに、図16に示すように、ストライプ状のパターンDP21,DP22を配置していることにある。なお、ストライプ状のダミーパターンDP21,DP22のピッチを各配線層で異ならせている点は、第一実施形態と同様である。

【0089】

<第三実施形態>

次に、本発明の半導体装置の第二実施形態について説明する。

半導体装置の全体構成としては、図1に示した半導体装置1の全体構成と同じである。第一実施形態と異なる点は、図4Bに示す第一実施形態においては、CMPダミーパターンDP1,DP2を採用しているが、本第三実施形態においては、その代わりに、図17に示すように、ストライプ状のパターンDP31とドットパターンのダミーパターンDP32との組み合わせを配置していることにある。

【0090】

<各種変形例>

上述の第一乃至第三実施形態においては、禁止領域PAの表面マーク313の直下にもパターンを配置させているが、図18に示すように、表面マーク313の直下は排除してもよい。

【0091】

また、上述の第一乃至第三実施形態においては、表面マーク313及び裏面マーク314の形状をL字型としたが、これに限られることはない。図19A〜図19Dは、マークの形状の他の例を示す図である。マークの形状としては、図19A〜図19Dにそれぞれ示すように、十字(313a)、四角(313b)、円形(313c)、直角三角形(313d)であってもよいし、他の多様な形状であってもよい。

【符号の説明】

【0092】

1・・・半導体装置

2・・・配線基板

21・・・絶縁基材

22・・・絶縁膜

23・・・接続パッド

24・・・ランド

25・・・ワイヤバンプ

26・・・表面バンプ

27・・・Cuピラー

28・・・カバー開口

29・・・絶縁トレンチ

3・・・チップ積層体

31(31a,31b,31c,31d)・・・メモリチップ

32・・・インターフェースチップ

311・・・表面バンプ電極

312・・・裏面バンプ電極

313・・・表面マーク

314・・・裏面マーク

315・・・第1層間絶縁膜

316・・・第2層間絶縁膜

317・・・第3層間絶縁膜

318・・・第4層間絶縁膜

319・・・半導体基板

320・・・接着剤

321・・・支持体

322・・・絶縁膜

323・・・シード膜

324・・・Cuめっき

32・・・インターフェースチップ

4・・・貫通配線

41・・・配線貫通電極

42・・・ダミーバンプ貫通電極

43・・・裏面絶縁膜

44・・・裏面バンプ

5・・・第1の封止樹脂部

6・・・NCP

7・・・第2の封止樹脂部

8・・・半田ボール

99・・・吸着ステージ

991・・・凹部

1〜3AlL・・・第1〜3アルミニウム配線階層

MWLP・・・配線パッド

PIO・・・ポリイミド(PI)開口部

PR・・・フォトレジスト

TH1〜3・・・第1〜第3スルーホール

TSV1・・・配線貫通電極

TSV2・・・マーク用貫通電極

WTL・・・配線タングステン階層

WTP1,WTP2・・・配線タングステンパッド

【技術分野】

【0001】

本発明は、半導体装置に関するものである。

【背景技術】

【0002】

図20は、従来における半導体装置の概略構成を示す断面図である。同図に示された半導体装置1pは、CoC(Chip on Chip)型の積層型半導体装置である。

【0003】

半導体装置1pは、配線基板2と、この配線基板2の一面に搭載されたチップ積層体3pとを備えている。このチップ積層体3pは、複数のメモリチップ31pa〜31pdとインターフェースチップ32pを有している。メモリチップ31pa〜31pd、インターフェースチップ32pのそれぞれは、表面バンプ電極311とこれに対応する裏面バンプ電極312とを備え、さらに、表面バンプ電極311と裏面バンプ電極312とは貫通電極4により電気的に接続されている。また、複数のメモリチップ31pa〜31pd、インターフェースチップ32pは、表面バンプ電極311、裏面バンプ電極312、及び、貫通電極4を介して互いに電気的に接続されている。

【0004】

更に、インターフェースチップ32p、の一面(図20における下側の面)の表面バンプ電極311は、配線基板2の電極パッド23に接続されている。

【0005】

次に、図20に示した半導体装置1pの組み立て工程について説明する。図21は、組み立て工程を説明するための図である。

【0006】

ステージ99上に保持されたメモリチップ31pa上に、図21に示すように、メモリチップ(2段目の半導体チップ)31pbを積層搭載する。

【0007】

ここで、メモリチップ31pa〜31pd、インターフェースチップ32pのそれぞれは、チップ表面側と裏面側とにそれぞれ表面マークと裏面マークとを有している。これら表面マークと裏面マークとは、半導体チップを積層する際の位置合わせに用いられる。具体的には、メモリチップ31paの表面マークを、フリップチップボンダーの基板側認識カメラで撮影し、半導体チップ31paのステージ上での座標を認識する。フリップチップボンダーのツールBTでピックアップされたメモリチップ31pbの裏面マークを、フリップチップボンダーの部品側認識カメラで撮影し、メモリチップ31pbのツール上での座標を認識する。得られた位置情報に応じて、メモリチップ31paの表面バンプ電極311とメモリチップ31pbの裏面バンプ電極312が正確に重なるように、ステージに対するツールの位置を調整して積層搭載する。

【0008】

同様に、メモリチップ(3段目及び4断面の半導体チップ)31pc及び31pd、インターフェースチップ(5段目の半導体チップ)32pが積層搭載される。

【0009】

上述のように、半導体チップ間の正確な位置合わせを行うために、表面マーク及び裏面マークが採用されている。

【0010】

図22は、メモリチップ31pのマーク部分の断面図である。

図22の断面図に示すように、メモリチップ31pは、配線タングステンWT、第1、第2、第3アルミニウム配線1ALp,2ALp,3ALを備える多層配線構造を備える。

【0011】

更に、図22に示すように、メモリチップ31pの表面側には第3アルミニウム配線3ALからなる表面マーク313が形成され、また、その下部には、裏面マーク用貫通電極TSV(Through−Silicon Via)に接続された配線タングステンWTが形成されている。裏面マーク用貫通電極TSVには、更に裏面バンプ電極312が接続されており、裏面マーク用貫通電極TSVと裏面バンプ電極312とで、裏面マーク314を形成している。裏面マーク用貫通電極TSVは、半導体基板319を貫通している。また、多層配線構造の上には、ポリイミド(PI)膜が形成されている。このポリイミド膜PIは、表面マーク313の上部を含む領域に形成されたPI開口部PIOを有している。

【0012】

ここで、最近の半導体プロセスでは、平坦化するために化学機械的研磨(CMP:Chemical Mechanical Polishing)技術が使用される。このCMP工程では、パターンが密な部分と疎な部分との研磨状態の差を補正する目的で、疎な部分にはダミーパターンを配置するのが一般的である。PI開口部の左右にある第1及び第2アルミニウム配線、配線タングステン、ゲート、シャロウ・トレンチ・アイソレーションSTI(Shallow Trench Isolation)の微小パターンが、そのCMPダミーパターンである。

【0013】

しかしながら、従来は、主に以下の2つの理由により、PI開口部PIOの下部へのダミーパターンの配置を禁止していた。第一には、第1及び第2アルミニウム配線の配線層の微小なダミーパターンが、第3アルミニウム配線3ALの表面マーク313の認識の障害になる場合があるからである。第二には、配線タングステンパッドWTの下には、裏面マーク用貫通電極TSVがあるので、ここにゲートなどの微小パターンが存在すると、裏面マーク用貫通電極TSVのドライエッチング工程で微小パターンのゲートがハードマスクとなってパーティクル(塵)の発生原因となる場合があるからである。

【0014】

従って、ここでの説明の表面マークの部分においても、禁止領域PAを設けている。なお、図22において、そのCMPダミーパターン禁止領域PAは、PI開口部PIOとほぼ一致(詳細は後述)させている。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2006−140300号公報

【特許文献2】特開2007−088124号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

しかしながら、上述の組み立て工程において、自チップを積層半導体装置に組み込む際の認識カメラでの表面マーク313の認識において、表面マーク313のコントラストが著しく低下することがあることが、発明者の研究で明らかとなった。

【0017】

図23は、照明の入射光(実線)及び反射光(破線)を記したPI開口部PIOを示す断面図である。配線タングステンWTのパット上部のPI開口部PIOでは、酸化ケイ素(SiO2)などの誘電体のみしか存在しないため、可視光の減衰は非常に小さい。このため、表面マーク313の背景となる配線タングステンパッド(WTP)からの反射が大きく、表面マーク313のコントラストが著しく低下するという問題があった。

【0018】

その結果、TSV積層工程で表面マーク313の認識エラーが発生し、前述の組み立て工程のスループットが著しく劣化するという問題があった。

【0019】

かかる技術的内容に関連する文献として特許文献1及び2がある。

特許文献1においては、半導体基板上に多層の回路パターンを形成する際に、露光によって形成されたレジストパターンが正確に下層の回路パターンに対して重ね合わせられているかを検査するために精度測定マークについて、下層に形成された主尺パターンがCMP時のディッシングの影響を受けないようにするために、主尺パターンが形成された配線層の下層の配線層のマーク形成領域にダミーパターンを形成することが開示されている。

【0020】

また、特許文献2には、実装基板のアライメントマークについて記載されている。

しかしながら、特許文献1には、あくまで、デバイス形成層形成時のレジストパターンの位置合わせに使用する精度測定マークについて開示しているのみである。従って、特許文献1には、半導体チップ形成後のアライメントマークの認識については何ら記載されておらず、さらに、精度測定マークに対して対称に配置されたマーク等の記載がなく、積層半導体装置の半導体チップに関するものではない。

【0021】

また、特許文献2は、あくまで、フレキシブル基板にデバイスを実装する場合のアラインメントマークについて開示されているだけであり、積層半導体装置の半導体チップに関するものではない。

【課題を解決するための手段】

【0022】

本発明の半導体装置は、第1の配線階層と、当該第1の配線階層の上方に形成された第2の配線階層と、当該第2の配線階層の上方に形成された第3の配線階層とを含む多階層配線構造であって、第1の配線階層として形成された第1の配線層と、前記第1の配線層の上部に位置する領域に前記第2の配線階層として形成された複数の第1のパターンと、前記第1の配線層の上部に位置する領域に前記第3の配線階層として形成された第1のマークとを含む、前記多階層配線構造を備えることを特徴とする。

【発明の効果】

【0023】

本発明の半導体装置によれば、とりわけ第1のマークの下部に複数の第1のパターンがある場合でも、第1のマークのコントラスト低下を抑制することにより、自半導体チップの積層工程で、マーク認識エラーを回避でき、スループットが向上する。

【図面の簡単な説明】

【0024】

【図1】本発明における半導体装置の概略構成を示す断面図である。

【図2A】本発明の第一実施形態のメモリチップの回路形成面(表面)から見た平面模式図である。

【図2B】本発明の第一実施形態のメモリチップの半導体基板側(裏面)から見た平面模式図である。

【図3A】本発明の第一実施形態のメモリチップの配線貫通電極部分の断面図である。

【図3B】本発明の第一実施形態のメモリチップのマーク部分の断面図である。

【図4A】本発明の第一実施形態のメモリチップの回路形成面(表面)側から見た表面マーク部分の概略平面図である。

【図4B】本発明の第一実施形態のメモリチップの回路形成面(表面)側から見た表面マーク部分の出来上がり状態を示した概略平面図である。

【図4C】本発明の第一実施形態のメモリチップの半導体基板側(裏面)から見た裏面マーク部分の概略平面図である。

【図4D】表面側から見た配線貫通電極の第2アルミニウム配線階層より下の階層の平面概略図である。

【図4E】第2アルミニウム配線階層以上の階層の平面概略図である。

【図4F】裏面から見た裏面バンプの平面概略図である。

【図5】本発明における照明の入射光(実線)及び反射光(破線)を記したPI開口部を示す断面図である。

【図6A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図6B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図6C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図7A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図7B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図7C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図8A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図8B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図8C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図8D】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図9A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図9B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図9C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図10A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図10B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図11A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図11B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図11C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図12A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図12B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図13A】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図13B】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図13C】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図14】本発明の第一実施形態のメモリチップの製造方法を説明するための図である。

【図15A】組み立て工程を説明するための図である。

【図15B】組み立て工程を説明するための図である。

【図15C】組み立て工程を説明するための図である。

【図16】本発明の第二実施形態のメモリチップにおけるダミーパターンを説明するための図である。

【図17】本発明の第三実施形態のメモリチップにおけるダミーパターンを説明するための図である。

【図18】本発明のメモリチップの変形例を説明するための図である。

【図19A】マークの形状の他の例を示す図である。

【図19B】マークの形状の他の例を示す図である。

【図19C】マークの形状の他の例を示す図である。

【図19D】マークの形状の他の例を示す図である。

【図20】従来の半導体装置の概略構成を示す断面図である。

【図21】組み立て工程を説明するための図である。

【図22】従来のメモリチップのマーク部分の断面図である。

【図23】従来における照明の入射光(実線)及び反射光(破線)を記したPI開口部を示す断面図である。

【発明を実施するための形態】

【0025】

以下、図面を参照して、本発明の実施の形態について詳細に説明する。

<第一実施形態>

図1は、本発明における半導体装置の概略構成を示す断面図である。同図に示された半導体装置1は、CoC型の積層型半導体装置である。

【0026】

具体的には、半導体装置1は、略四角形で所定の配線が形成された配線基板2を有している。この配線基板2は、例えば0.2mm厚のガラスエポキシ基板であり、絶縁基材21の両面に所定の配線が形成され、その配線は部分的に絶縁膜22、例えばソルダーレジスト、で覆われている。また、配線基板2の一面の中央領域には開口部が形成されており、絶縁膜(ソルダーレジスト)22の開口部から露出された部位には、複数の接続パッド23が形成されている。一方、配線基板2の他面の配線の絶縁膜22から露出された部位には、複数のランド24が形成されている。ここで、接続パッド23と、これに対応するランド24とは、配線基板2の配線によりそれぞれ電気的に接続されている。

【0027】

また、配線基板2の一面には、チップ積層体3が搭載されている。チップ積層体3は、例えば略四角形の板状で、一面に所定の回路が形成された半導体チップが、複数個、積層された構成となっている。図1に示した半導体装置においては、例えばメモリ回路が形成された4つのメモリチップ31a〜31dと、メモリチップ31と配線基板2とのインターフェースを取るためのインターフェースチップ32を5段積層したものである。それぞれの半導体チップは、例えば50μm厚で構成されており、一面の中央領域に複数の表面バンプ電極311と、他面側の中央領域に複数の裏面バンプ電極312が形成されている。表面バンプ電極311とこれに対応する裏面バンプ電極312とは貫通配線4により電気的に接続されている。

【0028】

また、チップ積層体3には、例えばアンダーフィル材からなる第1の封止樹脂部5が形成されている。この封止樹脂部5は、それぞれの半導体チップの間の隙間を充填するように形成されている。

【0029】

更に、チップ積層体3の最下の半導体チップの一面(図1における下側の面)の表面バンプ電極311は、ワイヤバンプ25を介して、配線基板2の接続パッド23に接続されている。

【0030】

また、チップ積層体3と配線基板2との電気的接続部の周囲には、NCP(Non Conductive Paste)6が配置されており、電気的接合部の保護と、チップ積層体3と配線基板2との接着固定するように構成されている。更に、配線基板2の一面上には、チップ積層体3を覆うように第2の封止樹脂層7が形成されている。

【0031】

また、配線基板2の他面の複数のランド24には、半導体装置1の外部端子となる半田ボール8がそれぞれ搭載されており、外部端子は所定の間隔で格子状に配置されている。

【0032】

次に、本発明の第一実施形態のメモリチップ31について説明する。図2A及び図2Bは、メモリチップ31の平面模式図であり、図2Aはその回路形成面(表面)から見た図であり、図2Bはその半導体基板側(裏面)から見た図である。

【0033】

図2Aに示されるように、メモリチップ31の回路形成面には、y方向中央部に、配線貫通電極41がx方向に沿って配置されている。また、メモリチップ31の回路形成面の2つの長辺(図中x方向に延伸する辺)のそれぞれに沿って、複数のダミーバンプ貫通電極42が配置されている。このダミーバンプ貫通電極42は、応力によってメモリチップ31が破損することを防ぐために設けられている。さらに、互いに対角に位置する1組の角部に、その回路形成面側から見えるように、表面マーク313が配置されている。好ましくは、表面マーク313は、複数のダミーバンプ貫通電極42が配置される領域内、つまり、複数のダミーバンプ貫通電極42を通過する直線上に配置される。

【0034】

また、図2Bに示されるように、メモリチップ31の半導体基板側には、y方向中央部に、配線貫通電極41がx方向に沿って配置されている。また、メモリチップ31の半導体基板側の2つの長辺(図中x方向に延伸する辺)のそれぞれに沿って、複数のダミーバンプ貫通電極42が配置されている。さらに、互いに対角に位置する1組の角部に、その半導体基板側から見えるように、裏面マーク314が配置されている。各組の表面マーク313及び裏面マーク314は、互いに半導体基板を挟んで対向する位置に設けられる。好ましくは、表面マーク313は、複数のダミーバンプ貫通電極42が配置される領域内、つまり、複数のダミーバンプ貫通電極42を通過する直線上に配置される。

【0035】

図3A及び図3Bは、メモリチップ31の配線貫通電極41の周辺部分(ダミーバンプ用貫通電極部分も実質的に同一)及び表面マーク313並びに裏面マーク314の周辺部分(以下単にマーク部分と記載する場合もある)の断面図である。

【0036】

図3Aに、配線貫通電極41部分の周辺の断面図を、図3Bには、マーク部分の断面図をそれぞれ示す。図3A及び図3Bに示すように、メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多階層配線構造を備える。各配線階層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。また、半導体基板319を貫通して貫通電極TSV1又はマーク用貫通電極TSV2が形成されている。

【0037】

図3Aに示すように、配線貫通電極41部分の回路形成面(表面)側においては、ポリイミド膜PIに形成された開口部PIOに表面バンプ26と銅ピラー27からなる表面バンプ電極311が形成され、この表面バンプ電極311がカバー開口28を介して第3アルミニウム配線階層3AlLとして形成された配線パッドMWLPに電気的に接続される。

【0038】

さらに、配線パッドMWLPは第3層間絶縁膜317中に形成された第3スルーホールTH3を介して第2アルミニウム配線階層2AlLとして形成された第2金属配線MWL2に接続され、第2金属配線MWLは、第2絶縁膜316中に形成された第2スルーホールTH2を介して第1アルミニウム配線階層1AlLとして形成された第1金属配線MWL1に接続される。第1金属配線MWL1は、第1層間絶縁膜315中に形成された第1スルーホールTH1を介して配線タングステン階層WTLとして形成された配線タングステンパッドWTP1に接続され、配線タングステンパッドWTP1が配線貫通電極TSV1に接続される。また、配線貫通電極41部分では、半導体基板319中に配線貫通電極TSV1を囲むように絶縁トレンチ29が形成されている。

【0039】

配線貫通電極部分の半導体基板側の面(裏面)には、裏面絶縁膜43及び裏面バンプ44が形成されており、裏面バンプ44は、配線貫通電極TSV1と接続されている。

【0040】

図3Aに示すように、配線貫通電極部分では、配線タングステン階層WTL、第1、第2アルミニウム配線階層1AlL、2AlLのそれぞれの配線階層として、実質的な機能配線(配線タングステンパッドWTP1、第1、第2金属配線MWL1,2)のほかに、複数のダミー配線(ダミーパターン)DPW、DP1、DP2が形成されている。

【0041】

ここで、実質的な機能配線とは、それぞれ電源電位や信号レベル等を伝播するための配線であり、それぞれ対応する電源レベルや信号レベルに応じた所望の電位が供給される配線である。

【0042】

これに対して、ダミー配線(ダミーパターン)DPW、DP1、DP2は、CMP(Chemical Mechanical Polishing)法により層間絶縁膜を平坦化する際に機能配線が存在しない領域において「ディッシング」が生じることを防止するために配置されるものであり、そのため、電源電位や信号レベル等に応じた所望の電位は供給されず、フローティング状態とされている配線である。

【0043】

尚、図3Aにおいては、機能配線として、配線貫通電極TSV1に接続されたものだけを示したが、これに限定されるものではない。例えば、図3Aに示す複数のダミー配線(ダミーパターン)DPW,DP1,DP2に混じって、機能配線が配置されていてもよい。

【0044】

一方、図3Bに示すように、マーク部分の表面側においては、ポリイミド膜PIに形成された開口部PIOの下部に位置する第3アルミニウム配線階層3AlLとして表面マーク313が形成され、さらに、開口部PIOの下部に位置する配線タングステン階層WTLとしては、配線タングステンパッドWTP2が形成されおり、配線タングステンパッドWTLP2がマーク用貫通電極TSV2に接続されている。また、マーク部分の裏面側においては、裏面マークが形成された裏面バンプ44がマーク用貫通電極TSV2の下部に形成されている。

【0045】

また、マーク部分においては、第1のダミーパターン(下層のダミーパターン)DP1が、第1アルミニウム配線階層1AlLとして、第2層間絶縁膜316に覆われて(つまり、第2層間絶縁膜316を貫通していない)形成され、第2のダミーパターン(上層のダミーパターン)DP2が、第2アルミニウム配線階層2AlLとして、第3層間絶縁膜317に覆われて(つまり、第3層間絶縁膜317を貫通していない)形成されている。第2ダミーパターンは、第1ダミーパターンよりも幅(図面x方向の長さ)が長い。好ましくは、配線タングステンパッドWTP2の上部の領域の第1及び第2アルミニウム配線階層1AlL、2AlLには、機能配線が配置されない。

【0046】

ここで、発明者は、マークのコントラストについて調べる過程で、マークを認識するためのカメラの画像を調査したところ、当該カメラの解像度(約1μm程度)では、CMPダミーパターンに非常に微小なために全く認識されず、開口部PIOのエッジ部分から露出しているCMPダミーパターン部分は、他の背景よりも暗く認識されることを見出した。つまり、カメラの分解能よりも小さい微小パターンは、マークに近接して配置してもマークの認識の障害にはならず、むしろコントラストの改善に役立つことを見出した。

【0047】

図4Aは、メモリチップの回路形成面(表面)側から見た表面マーク313部分のポリイミド膜PIを除いた場合の概略平面図であり、図4Bは、ポリイミド膜PIを含む概略平面図である。また、図4Cは、メモリチップの半導体基板側(裏面)から見た裏面マーク314部分の概略平面図である。

【0048】

表面マーク313は、図4Aに示すように、第3アルミニウム配線階層3AlLとして形成されたL字型のマークであり、図3Bに示すように、その領域に対応するポリイミド膜PIは、表面マーク313が露出するように開口されている。また、図3Bに示すように、下部には、配線タングステン階層WTLとして形成されマーク用貫通電極TSV2に接続された配線タングステンパッドWTP2が形成されている。マーク用貫通電極TSV2には、更に裏面バンプ電極312が接続されており、図4Cに示すように、マーク用貫通電極TSV2と裏面バンプ電極312とで、L字型の裏面マーク314を形成している。マーク用貫通電極TSV2は、半導体基板319を貫通している。

【0049】

ここで、本発明の半導体装置の第一実施形態におけるチップにおいては、図3B、図4A及び図4Bに示すように、ポリイミド膜PIに形成された開口部PIOの下部(表面マークの下部を含む)領域(即ち、配線タングステン階層WTLとして形成された配線タングステンパッドWTP2の上部の領域)にも、第1及び第2のダミー配線(ダミーパターン)DP1,DP2が、それぞれ第1及び第2アルミニウム配線階層1AlL及び2AlLとして形成されている。なお、このポリイミド膜PIに形成された開口部PIOの下部領域(配線タングステンパッドWTP2の上部の領域を含む)のうちでダミー配線(ダミーパターン)DP1,DP2が形成される配線階層は、配線タングステン階層WTLより上部、即ち、第1及び第2アルミニウム配線階層1AlL及び2AlLのみであり、配線タングステン階層WTL、ゲートG、及びSTIについては、ダミーパターンを排除する。

【0050】

ここで、それぞれ、配線タングステン配線階層WTLが第1の配線階層に、第1アルミニウム配線階層1AlLが第2の配線階層に、第3アルミニウム配線階層3AlLが第3の配線階層に対応している。また、表面マーク313及び裏面マーク314が、それぞれ、第1のマーク及び第2のマークに対応している。

【0051】

図5は、本発明における照明の入射光(実線)及び反射光(破線)を記した断面図である。同図においては、外部からの照明光は、第2アルミニウム配線階層2AlLとしての複数のダミーパターンDP2の間を透過した光は、第1アルミニウム配線階層1AlLとしての複数のダミーパターンDP1で散乱されるものと、第1アルミニウム配線階層1AlLとしての複数のダミーパターンDP1の間を透過するものに分かれる。第1アルミニウム配線階層1AlLとしての複数のダミーパターンDP1の間を透過したものは、配線タングステン階層WTLとしての配線タングステンパッドWTP2で反射されるが、第1アルミニウム配線階層1AlL、第2アルミニウム配線階層2AlLとしての複数のダミーパターンDP1,DP2で散乱される。このため、外部から見たときの反射率が大幅に低下する。ダミーパターン自体は一種の回折格子を形成することになるので、複数のダミーパターンDP1,DP2間の間隔(ピッチ)を第1アルミニウム配線階層1AlLと第2アルミニウム配線階層2AlLとで互いに異ならせることは、マーク背景の反射率低下により効果的である。

【0052】

また、図4D〜図4Fに、マーク部分との比較として、配線貫通電極42の部分の表面側及び裏面側から見た平面図を示す。図4Dは、表面側から見た配線貫通電極42の第2アルミニウム配線階層2AlLより下の階層の平面概略図であり、図4Eは、第2アルミニウム配線階層2AlL以上の階層の平面概略図であり、図4Fは、裏面から見た裏面バンプ44の平面概略図である。

【0053】

図4A及び図4Bと、図4C及び図4Dとを比べると、図4A及び図4Bはマーク部分の配線タングステンパッドWTP2が矩形をしているのに対し、図4C及び図4Dは配線貫通電極部分の配線タングステンパッドWTP1は円形をしている。

【0054】

また、図3A及び図3Bに示すように、好ましくは、マーク部分の配線タングステンパッドWTP2の大きさは、配線貫通電極部分の配線タングステンパッドWTP1の大きさよりも大きいほうがよい。これは、カメラ等で認識するために充分な大きさの裏面マーク314を形成するためには、図4Cに示すマーク用貫通電極TSV2を配線貫通電極TSV1よりも大きなサイズにする必要があるためである。

【0055】

次に、本発明の第一実施形態のメモリチップ31の製造方法について説明する。図6〜図14は、メモリチップ31の製造方法を順に説明するための図である。

【0056】

まず、図6Aに示された製造ステップは、半導体基板319の一面(表面、回路形成面側)に、多階層配線構造の一部である配線タングステン階層WTL(配線タングステンパッドWTP2を含む)、アクティブ素子、キャパシタを形成する工程が完了した状態で、これら配線タングステン階層WTL、アクティブ素子、キャパシタを覆うように第1層間絶縁膜315を形成した状態を示している。これ以降、多層配線構造の形成を行っていく。この図では、図示していない第1スルーホールのビアが形成される。

【0057】

図6Bは、図6Aを表面側から見た平面概略図である。尚、以降、本実施例の製造方法の説明中の平面概略図においては、図4A〜図4Cに示したポリイミド膜PIに形成された開口部PIOの下部に対応する領域について記載するものとする。また、本実施例の製造方法の説明中の平面概略図においては、配線階層の形状を見やすくするために層間絶縁膜の記載を省略している。

【0058】

図6Cに示された製造ステップは、第1アルミニウム配線階層1AlLの成長過程を示しており、第1層間絶縁膜315上に、バリアメタル、アルミニウム、反射防止膜などの積層メタル層をスパッタなどで成長させる。

【0059】

図7Aの製造ステップにおいては、積層メタル層上にフォトレジストPRを塗布し、レチクルなどを用いてパターン形成する。次に、図7Bの製造ステップにおいては、フォトレジストPRをマスクとして積層メタル層をドライエッチすることで第1アルミニウム配線階層1AlLを形成する。この際、表面マーク313が形成される領域の下部を含む領域(図7Bの配線タングステンパッドWTP2上の領域)に、第1ダミーパターンDP1が形成される。その上に、第1ダミーパターンDP1を含む第1アルミニウム配線階層1AlLを覆うように第2層間絶縁膜316を形成する。絶縁膜はSiO2などの酸化膜である。この図では図示していない第2スルーホールのビアが形成される。

【0060】

図7Cは、図7Bを表面側から見た平面概略図である。配線タングステン階層WTLに形成された配線タングステンパッドWTP2の上部を含む領域に、第1アルミニウム配線階層1AlLに形成された複数の第1ダミーパターンDP1が形成される。

【0061】

次に、図8Aの製造ステップにおいては、第2アルミニウム配線階層2AlLのパターンを形成して第3層間絶縁膜317を形成する。この工程は第1アルミニウム配線階層1AlLの形成の場合と同様である。第2層間絶縁膜316上の表面マーク313が形成される領域の下部を含む領域には、複数の第2ダミーパターンDP2が形成される。絶縁膜はSiO2などの酸化膜である。複数の第2ダミーパターンDP2を含む第2アルミニウム配線階層2AlLを覆うように第3層間絶縁膜317が形成される。この図では図示していない第3スルーホールのビアが形成される。

【0062】

図8Bは、図8Aを表面側から見た平面概略図である。配線タングステン階層WTLに形成された配線タングステンパッドWTP2の上部を含む領域に、第2アルミニウム配線階層2AlLに形成された複数の第2ダミーパターンDP2が形成される。

【0063】

次に、図8Cの製造ステップにおいては、第3層間絶縁膜317上に、表面マーク313を含む第3アルミニウム配線階層3AlLが形成される。更に、第3アルミニウム配線3ALを覆う第4層間絶縁膜318を形成する。なお、第4層間絶縁膜318は、パッシベーション膜とも呼ばれ、水分の浸入などを防止するため、緻密なSi3O4などのナイトライド膜や、SiONなどの酸窒化膜である。

【0064】

図8Dは、図8Cを表面側から見た平面概略図である。配線タングステン階層WTLに形成された配線タングステンパッドWTP2の上部を含む領域に、第3アルミニウム配線階層3AlLに形成されたL字状の表面マーク313が形成される。尚、図7C、図8Aに示したように、本実施形態においては、表面マーク313の下部にも第1及び第2のダミーパターンDP1,DP2が形成されている。

【0065】

次に、図9Aの製造ステップにおいては、第4層間絶縁膜318上に樹脂層であるポリイミド(PI)層PIを形成し、更に、形成したポリイミド層PIに、表面マーク313と第4層間絶縁膜318のうちの表面マーク313を覆う部分を露出させる開口部PIOを形成する。

【0066】

図9Bは、図9Aを表面側から見た平面概略図である。ポリイミド膜PIに形成された開口部PIOは、表面マーク313、複数の第2のダミーパターンDP2の一部、複数の第1のダミーパターンDP1の一部、及び、配線タングステンパッドWTP2が形成された上部領域に形成される。

【0067】

次に、図9Cの製造ステップにおいては、表面バンプ形成までの配線工程が完了したウエハ表面に、SiO2などで形成された支持体(Wafer Support System; WSS)321を接着剤320で貼り付ける。この接着剤320としては、紫外線などでウエハから剥離可能なものを用いる。

【0068】

次に、図10Aの製造ステップにおいては、ウエハ裏面を研削して50〜20um程度まで薄くする。裏面には金属汚染防止のため、Si3N4などのナイトライドの絶縁膜322を形成する。なお、このステップから裏面側の加工のため、説明の便宜上、同図から以降、上下反転している。

【0069】

次に、図10Bの製造ステップにおいては、マーク用貫通電極TSV2を形成するため、フォトレジストPRを塗布して開口パターン330形成する。

【0070】

次に、図11Aの製造ステップにおいては、フォトレジストPRをマスクとして、ドライエッチで配線タングステンパッドWTP2までマーク用貫通電極TSV2の開口部331を形成する。

【0071】

図11Bは、図11Aを裏面側から見た平面概略図であり、ドライエッチにより矩形の開口部331a、331bが形成されている。

【0072】

次に、図11Cの製造ステップにおいては、フォトレジストPRの除去後に、開口部33(331a、331b)の側壁及びマーク用貫通電極TSV2底部の配線タングステンパッドWTP2上を含めて、ウエハ裏面全面にTi/Cuなどのシード膜323をスパッタなどで形成する。

【0073】

次に、図12Aの製造ステップにおいては、裏面マーク314を含む裏面バンプ電極312を形成するため、フォトレジストPRを塗布して開口パターン332を形成する。

【0074】

次に、図12Bの製造ステップにおいては、シード膜323を電極として、Cuめっき324を成長させてマーク用貫通電極TSV2のビアの充填と裏面バンプ電極312のピラーを形成する。

【0075】

次に、図13Aの製造ステップにおいては、裏面バンプ44を含む裏面バンプ電極312として、SnAgはんだをめっきで形成する。

【0076】

次に、図13Bの製造ステップにおいては、フォトレジストPRを除去し、更にシード膜323をウェットエッチ等で除去する。

【0077】

図13Cは、図13Bを裏面側から見た平面概略図である。L字型の裏面マーク314が形成されている。次に、図14の製造ステップにおいては、支持体321から紫外線等でデマウントする。

【0078】

次に、図1に示した半導体装置1の組み立て工程について説明する。図15A〜図15Cは、組み立て工程を説明するための図である。

【0079】

図15Aに示すように、吸着ステージ99には凹部991が形成されており、メモリチップ(1段目の半導体チップ)31paが、回路形成面を上方に向けて当該凹部991内に載置される。そして、図示しない真空装置により真空吸引することで、吸着ステージ99上に載置されたメモリチップ31aが保持固定される。

【0080】

次に、このように吸着ステージ99上に保持されたメモリチップ31a上に、図15Bに示すように、ボンディングツールBTにより高温、例えば300℃程度、で荷重を印加することで、メモリチップ(2段目の半導体チップ)31bを積層搭載する。

【0081】

この際、各メモリチップ31a、31bの積層位置を合わせるために、吸着ステージ99上に配置されたメモリチップ31aの表面マーク313を、フリップチップボンダーの基板側認識カメラで撮影し、半導体チップ31aのステージ上での座標を認識する。フリップチップボンダーのツールでピックアップされたメモリチップ31bの裏面マーク314を、フリップチップボンダーの部品側認識カメラで撮影し、メモリチップ31bのツール上での座標を認識する。得られた位置情報に応じて、メモリチップ31aの表面バンプ電極311とメモリチップ31bの裏面バンプ電極312が正確に重なるように、ステージに対するツールの位置を調整して積層搭載する。

【0082】

メモリチップ31bは、メモリチップ31aと同様なメモリチップであり、メモリチップ31aの一面の表面バンプ電極311と、メモリチップ31bの他面の対応する裏面バンプ電極312とを、熱圧着により電気的に接続することで、メモリチップ31aの一面側にメモリチップ31bが積層搭載される。このように、それぞれのメモリチップをバンプ電極で接続することで、メモリチップ間に隙間が形成される。

【0083】

同様に、メモリチップ(3段目及び4断面の半導体チップ)31c及び31d、インターフェースチップ(5段目の半導体チップ)32が積層搭載され、図15Cに示すような、例えば4つのメモリチップ31a〜31dとインターフェースチップ32が積層されたチップ積層体3が形成される。

【0084】

なお、インターフェースチップ32においては、他面側の裏面バンプ電極312はメモリチップ31dの表面バンプ電極311に対応して配置され、表面側の表面バンプ電極311は、配線基板2の接続パッド23に搭載するため、60〜200μm程度の広いピッチで、表面バンプ電極311が配置されている。

【0085】

その後、各チップ間へのアンダーフィルの挿入形成を経て、更に、組み立て工程にて配線基板2に搭載され、半田ボール8が取り付けられることで、図1に示した半導体装置1となる。

【0086】

本発明における半導体装置においては、前述のように、メモリチップ31(31a〜31d)の表面マーク313の下側に位置する第1アルミニウム配線階層1AlL及び第2アルミニウム配線階層2AlLは、ともに認識カメラの解像度よりも小さい大きさ、つまり、認識カメラには認識されないサイズのダミーパターンDP1,DP2を形成しているため、組み立て工程においては、従来よりも表面マーク313を高いコントラストで識別することが可能となっている。ここで、特に、新たな工程を追加することなしに、表面マーク313のコントラスト低下を抑制することができることが顕著な特徴である。

【0087】

以上のように表面マーク313のコントラスト低下を抑制して、識別が容易になれば、図15A〜図15Cに示した組み立て工程において、各チップ間の位置合わせが容易となる。

特に、TSV積層用チップのように、表面マーク313の下部に配線タングステンパッドWTPを配置する必要がある場合に有効である。

【0088】

<第二実施形態>

次に、本発明の第二実施形態のメモリチップについて説明する。

半導体装置の全体構成としては、図1に示した半導体装置1の全体構成と同じである。第一実施形態と異なる点は、図4Bに示す第一実施形態においては、CMPダミーパターンDP1,DP2を採用しているが、本第二実施形態においては、その代わりに、図16に示すように、ストライプ状のパターンDP21,DP22を配置していることにある。なお、ストライプ状のダミーパターンDP21,DP22のピッチを各配線層で異ならせている点は、第一実施形態と同様である。

【0089】

<第三実施形態>

次に、本発明の半導体装置の第二実施形態について説明する。

半導体装置の全体構成としては、図1に示した半導体装置1の全体構成と同じである。第一実施形態と異なる点は、図4Bに示す第一実施形態においては、CMPダミーパターンDP1,DP2を採用しているが、本第三実施形態においては、その代わりに、図17に示すように、ストライプ状のパターンDP31とドットパターンのダミーパターンDP32との組み合わせを配置していることにある。

【0090】

<各種変形例>

上述の第一乃至第三実施形態においては、禁止領域PAの表面マーク313の直下にもパターンを配置させているが、図18に示すように、表面マーク313の直下は排除してもよい。

【0091】

また、上述の第一乃至第三実施形態においては、表面マーク313及び裏面マーク314の形状をL字型としたが、これに限られることはない。図19A〜図19Dは、マークの形状の他の例を示す図である。マークの形状としては、図19A〜図19Dにそれぞれ示すように、十字(313a)、四角(313b)、円形(313c)、直角三角形(313d)であってもよいし、他の多様な形状であってもよい。

【符号の説明】

【0092】

1・・・半導体装置

2・・・配線基板

21・・・絶縁基材

22・・・絶縁膜

23・・・接続パッド

24・・・ランド

25・・・ワイヤバンプ

26・・・表面バンプ

27・・・Cuピラー

28・・・カバー開口

29・・・絶縁トレンチ

3・・・チップ積層体

31(31a,31b,31c,31d)・・・メモリチップ

32・・・インターフェースチップ

311・・・表面バンプ電極

312・・・裏面バンプ電極

313・・・表面マーク

314・・・裏面マーク

315・・・第1層間絶縁膜

316・・・第2層間絶縁膜

317・・・第3層間絶縁膜

318・・・第4層間絶縁膜

319・・・半導体基板

320・・・接着剤

321・・・支持体

322・・・絶縁膜

323・・・シード膜

324・・・Cuめっき

32・・・インターフェースチップ

4・・・貫通配線

41・・・配線貫通電極

42・・・ダミーバンプ貫通電極

43・・・裏面絶縁膜

44・・・裏面バンプ

5・・・第1の封止樹脂部

6・・・NCP

7・・・第2の封止樹脂部

8・・・半田ボール

99・・・吸着ステージ

991・・・凹部

1〜3AlL・・・第1〜3アルミニウム配線階層

MWLP・・・配線パッド

PIO・・・ポリイミド(PI)開口部

PR・・・フォトレジスト

TH1〜3・・・第1〜第3スルーホール

TSV1・・・配線貫通電極

TSV2・・・マーク用貫通電極

WTL・・・配線タングステン階層

WTP1,WTP2・・・配線タングステンパッド

【特許請求の範囲】

【請求項1】

第1の配線階層と、当該第1の配線階層の上方に形成された第2の配線階層と、当該第2の配線階層の上方に形成された第3の配線階層とを含む多階層配線構造であって、

第1の配線階層として形成された第1の配線層と、前記第1の配線層の上部に位置する領域に前記第2の配線階層として形成された複数の第1のパターンと、前記第1の配線層の上部に位置する領域に前記第3の配線階層として形成された第1のマークとを含む、前記多階層配線構造を備えることを特徴とする半導体装置。

【請求項2】

第1の面に前記多階層配線構造が形成された半導体基板と、

前記半導体基板を、前記第1の面から当該第1の面と対向する第2の面まで貫通する貫通電極と、

前記貫通電極に接続された第2のマークと、を更に備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記貫通電極は、前記半導体基板の前記第2の面において前記多階層配線層の前記第1の配線階層の前記第1の配線層の下部に位置する領域に配置されることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記複数の第1のパターンは、電気的にフローティング状態であることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記複数の第1のパターンは、前記第2の配線階層における前記第1のマークの下部の領域に形成されることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記多階層配線構造は、更に、前記第1の配線階層と前記第3の配線階層との間に形成された第4の配線階層と、前記第1の配線層の上部に位置する領域に前記第4の配線階層として形成された複数の第2のパターンとを含むことを特徴とする請求項1に記載の半導体装置。

【請求項7】

前記複数の第2のパターンの各々は、前記複数の第1のパターンの各々よりも大きいことを特徴とする請求項6に記載の半導体装置。

【請求項8】

第1の配線階層と当該第1の配線階層の上方に形成された第2の配線階層とを含む多階層配線構造であって、

前記第2の配線階層として形成された第1のマークと、前記第1の配線階層として形成された複数のパターンとを含む、前記多階層配線構造と、

前記多層配線構造上に形成された樹脂層であって、当該樹脂層は、前記第1のマークと前記複数のパターンのうちの1又は複数との上部に位置する開口部を含む、前記樹脂層と、

を備えることを特徴とする半導体装置。

【請求項9】

第1の面に前記多階層配線層が形成された半導体基板と、

前記半導体基板の前記第1の面から前記半導体基板の前記第1の面に対向する第2の面まで貫通する貫通電極と、

前記貫通電極に接続された第2のマークと、

を更に備えることを特徴とする請求項8に記載の半導体装置。

【請求項10】

前記多階層配線構造は、さらに、前記第1の配線階層の下方に形成された第3の配線階層を含み、前記貫通電極の一端は、前記第3の配線階層まで延伸することを特徴とする請求項9に記載の半導体装置。

【請求項11】

前記複数のパターンは、電気的にフローティング状態であることを特徴とする請求項8に記載の半導体装置。

【請求項12】

互いに積層された第1及び第2の半導体チップであって、

各々が、第1の配線階層と、当該第1の配線階層の上方に形成された第2の配線階層と、当該第2の配線階層の上方に形成された第3の配線階層とを含む多階層配線構造であって、第1の配線階層として形成された第1の配線層と、前記第1の配線層の上部に位置する領域に前記第2の配線層として形成された複数の第1のパターンと、前記第1の配線層の上部に位置する領域に前記第3の配線層として形成された第1のマークとを含む、前記多階層配線構造を含む、前記第1及び第2の半導体チップと、

を備えることを特徴とする半導体装置。

【請求項13】

前記第1及び第2の半導体チップの各々が、

第1の面に前記多階層配線構造が形成された半導体基板と、

前記半導体基板を、前記第1の面から当該第1の面と対向する第2の面まで貫通する貫通電極と、

前記貫通電極に接続された第2のマークと、

を更に含むことを特徴とする請求項12に記載の半導体装置。

【請求項14】

前記第1及び第2の半導体チップの各々の前記貫通電極は、自身が形成された前記半導体基板の前記第2の面において前記自身が形成半導体基板の前記第1の面に形成された前記多階層配線層の前記第1の配線階層の前記第1の配線層の下部に位置する領域に配置されることを特徴とする請求項13に記載の半導体装置。

【請求項15】

前記第1及び第2の半導体チップの各々の前記複数の第1のパターンは、電気的にフローティング状態であることを特徴とする請求項12に記載の半導体装置。

【請求項16】

前記第1及び第2の半導体チップの各々の前記複数の第1のパターンは、自身が形成された前記多階層配線層中の前記第2の配線階層における前記第1のマークの下部の領域に形成されることを特徴とする請求項12に記載の半導体装置。

【請求項17】

前記第1及び第2の半導体チップの各々の前記多階層配線構造は、更に、前記第1の配線階層と前記第3の配線階層との間に形成された第4の配線階層と、前記第1の配線層の上部に位置する領域に前記第4の配線階層として形成された複数の第2のパターンとを含むことを特徴とする請求項12に記載の半導体装置。

【請求項18】

前記第1及び第2の半導体チップの各々の前記複数の第2のパターンの各々は、自身が形成された前記多階層配線構造中の前記複数の第1のパターンの各々よりも大きいことを特徴とする請求項17に記載の半導体装置。

【請求項1】

第1の配線階層と、当該第1の配線階層の上方に形成された第2の配線階層と、当該第2の配線階層の上方に形成された第3の配線階層とを含む多階層配線構造であって、

第1の配線階層として形成された第1の配線層と、前記第1の配線層の上部に位置する領域に前記第2の配線階層として形成された複数の第1のパターンと、前記第1の配線層の上部に位置する領域に前記第3の配線階層として形成された第1のマークとを含む、前記多階層配線構造を備えることを特徴とする半導体装置。

【請求項2】

第1の面に前記多階層配線構造が形成された半導体基板と、

前記半導体基板を、前記第1の面から当該第1の面と対向する第2の面まで貫通する貫通電極と、

前記貫通電極に接続された第2のマークと、を更に備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記貫通電極は、前記半導体基板の前記第2の面において前記多階層配線層の前記第1の配線階層の前記第1の配線層の下部に位置する領域に配置されることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記複数の第1のパターンは、電気的にフローティング状態であることを特徴とする請求項1に記載の半導体装置。

【請求項5】

前記複数の第1のパターンは、前記第2の配線階層における前記第1のマークの下部の領域に形成されることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記多階層配線構造は、更に、前記第1の配線階層と前記第3の配線階層との間に形成された第4の配線階層と、前記第1の配線層の上部に位置する領域に前記第4の配線階層として形成された複数の第2のパターンとを含むことを特徴とする請求項1に記載の半導体装置。

【請求項7】

前記複数の第2のパターンの各々は、前記複数の第1のパターンの各々よりも大きいことを特徴とする請求項6に記載の半導体装置。

【請求項8】

第1の配線階層と当該第1の配線階層の上方に形成された第2の配線階層とを含む多階層配線構造であって、

前記第2の配線階層として形成された第1のマークと、前記第1の配線階層として形成された複数のパターンとを含む、前記多階層配線構造と、

前記多層配線構造上に形成された樹脂層であって、当該樹脂層は、前記第1のマークと前記複数のパターンのうちの1又は複数との上部に位置する開口部を含む、前記樹脂層と、

を備えることを特徴とする半導体装置。

【請求項9】

第1の面に前記多階層配線層が形成された半導体基板と、

前記半導体基板の前記第1の面から前記半導体基板の前記第1の面に対向する第2の面まで貫通する貫通電極と、

前記貫通電極に接続された第2のマークと、

を更に備えることを特徴とする請求項8に記載の半導体装置。

【請求項10】

前記多階層配線構造は、さらに、前記第1の配線階層の下方に形成された第3の配線階層を含み、前記貫通電極の一端は、前記第3の配線階層まで延伸することを特徴とする請求項9に記載の半導体装置。

【請求項11】

前記複数のパターンは、電気的にフローティング状態であることを特徴とする請求項8に記載の半導体装置。

【請求項12】

互いに積層された第1及び第2の半導体チップであって、

各々が、第1の配線階層と、当該第1の配線階層の上方に形成された第2の配線階層と、当該第2の配線階層の上方に形成された第3の配線階層とを含む多階層配線構造であって、第1の配線階層として形成された第1の配線層と、前記第1の配線層の上部に位置する領域に前記第2の配線層として形成された複数の第1のパターンと、前記第1の配線層の上部に位置する領域に前記第3の配線層として形成された第1のマークとを含む、前記多階層配線構造を含む、前記第1及び第2の半導体チップと、

を備えることを特徴とする半導体装置。

【請求項13】

前記第1及び第2の半導体チップの各々が、

第1の面に前記多階層配線構造が形成された半導体基板と、

前記半導体基板を、前記第1の面から当該第1の面と対向する第2の面まで貫通する貫通電極と、

前記貫通電極に接続された第2のマークと、

を更に含むことを特徴とする請求項12に記載の半導体装置。

【請求項14】

前記第1及び第2の半導体チップの各々の前記貫通電極は、自身が形成された前記半導体基板の前記第2の面において前記自身が形成半導体基板の前記第1の面に形成された前記多階層配線層の前記第1の配線階層の前記第1の配線層の下部に位置する領域に配置されることを特徴とする請求項13に記載の半導体装置。

【請求項15】

前記第1及び第2の半導体チップの各々の前記複数の第1のパターンは、電気的にフローティング状態であることを特徴とする請求項12に記載の半導体装置。

【請求項16】

前記第1及び第2の半導体チップの各々の前記複数の第1のパターンは、自身が形成された前記多階層配線層中の前記第2の配線階層における前記第1のマークの下部の領域に形成されることを特徴とする請求項12に記載の半導体装置。

【請求項17】

前記第1及び第2の半導体チップの各々の前記多階層配線構造は、更に、前記第1の配線階層と前記第3の配線階層との間に形成された第4の配線階層と、前記第1の配線層の上部に位置する領域に前記第4の配線階層として形成された複数の第2のパターンとを含むことを特徴とする請求項12に記載の半導体装置。

【請求項18】

前記第1及び第2の半導体チップの各々の前記複数の第2のパターンの各々は、自身が形成された前記多階層配線構造中の前記複数の第1のパターンの各々よりも大きいことを特徴とする請求項17に記載の半導体装置。

【図1】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図5】

【図6A】

【図6B】

【図6C】

【図7A】

【図7B】

【図7C】

【図8A】

【図8B】

【図8C】

【図8D】

【図9A】

【図9B】

【図9C】

【図10A】

【図10B】

【図11A】

【図11B】

【図11C】

【図12A】

【図12B】

【図13A】

【図13B】

【図13C】

【図14】

【図15A】

【図15B】

【図15C】

【図16】

【図17】

【図18】

【図19A】

【図19B】

【図19C】

【図19D】

【図20】

【図21】

【図22】

【図23】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図5】

【図6A】

【図6B】

【図6C】

【図7A】

【図7B】

【図7C】

【図8A】

【図8B】

【図8C】

【図8D】

【図9A】

【図9B】

【図9C】

【図10A】

【図10B】

【図11A】

【図11B】

【図11C】

【図12A】

【図12B】

【図13A】

【図13B】

【図13C】

【図14】

【図15A】

【図15B】

【図15C】

【図16】

【図17】

【図18】

【図19A】

【図19B】

【図19C】

【図19D】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2012−222161(P2012−222161A)

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願番号】特願2011−86715(P2011−86715)

【出願日】平成23年4月8日(2011.4.8)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願日】平成23年4月8日(2011.4.8)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]