半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法、特にSRAM(static random access memory )、システムLSI に搭載されるオンチップメモリ、マイクロプロセッサ、あるいは、システムLSIなどに関する。

【背景技術】

【0002】

ゲートトンネルリーク電流を低減する公知技術として、特願平9-536055が知られている。この公知例においては、ゲートトンネルリーク電流が大きいときにゲート酸化膜の厚いゲートトンネルリーク電流の小さいスイッチMOSで電源を遮断することにより、リーク電流を削減する回路が示されている。また、GIDL(Gate Induced Drain Leakage)電流を低減する技術として、特願2000−357962号が知られている。この公知例においては、MOSトランジスタのしきい値が比較的低いことを前提として、まずサブスレッショルドリーク電流を削減するためにPチャネル型MOSトランジスタの基板電極を電源電圧以上、Nチャネル型MOSトランジスタの基板電極を接地電位以下に制御する。その結果GIDLが顕在化するため、電源電圧を低減してGIDL電流を削減する技術が開示されている。また、特開平9−135029号公報には、GIDL電流対策としてnチャネルMISトランジスタのゲート電極とソース・ドレイン領域に燐イオンを注入している技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特願平9−536055号

【特許文献2】特願2000−357962号

【特許文献3】特開平9−135029号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年プロセスの微細化に伴い、MOSトランジスタのゲート酸化膜厚が4nm以下になってきている。しかしながら、ゲート酸化膜が4nm以下になるとゲートトンネルリーク電流が増大し、ゲート電極とソース電極間に動作時の電圧が印加されると、ゲートトンネルリーク電流がティピカルプロセスで10-12 A/μm2 以上となる。

【0005】

携帯電話に使用されるLSIにおいては、低リーク電流での待機が要求される。特にSRAMは、ボタン電池でデータを一週間以上保持する必要があり、プロセスがワーストになり、酸化膜が薄くなった場合、ゲートトンネルリーク電流が増大し一週間以上のデータ保持が不可能となる問題がある。また、ドレインから基板へ流れるリーク電流であるGIDL電流の増加も同様に問題となっている。

【0006】

しかし、ゲートトンネルリーク電流を低減する従来の公知例(特願平9-536055)ではMOSで電源を遮断するため、SRAMセルやレジスタファイルおよびラッチ回路等の保持データが破壊されてしまうという問題があった。また、GIDL電流を低減する従来の公知例(特願平11-255317 )においては、比較的高いしきい値たとえば0.7VのMOSトランジスタを使用する場合には、サブスレッショルドリーク電流が顕著でないため、Nャネル型MOSトランジスタの基板電極を接地電位以下の電位に、Pチャネル型MOSトランジスタの基板電極を電源電位以上の電位にしてもオフ電流は低減せず、かえって接合リーク電流が増大するという問題があった。

【課題を解決するための手段】

【0007】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。半導体集積回路装置は、そのソース電極が電源線に接続される第1の負荷型Pチャネル型MOSトランジスタと、そのソース電極がソース線に接続され、そのドレイン電極が前記第1の負荷型Pチャネル型MOSトランジスタのドレイン電極に接続され、そのゲート電極が前記第1の負荷型Pチャネル型MOSトランジスタのゲート電極に接続される第1の駆動型Nチャネル型MOSトランジスタと、そのソース電極が前記電源線に接続される第2の負荷型Pチャネル型MOSトランジスタと、そのソース電極が前記ソース線に接続され、そのドレイン電極が前記第2の負荷型Pチャネル型MOSトランジスタのドレイン電極に接続されると共に前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのゲート電極に接続され、そのゲート電極が前記第2の負荷型Pチャネル型MOSトランジスタのゲート電極に接続されると共に前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのドレイン電極に接続される第2の駆動型Nチャネル型MOSトランジスタとを夫々が有する複数のスタティック型メモリセルを含む。前記電源線と前記ソース線との電位差である前記複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路とを具備する。前記第1及び第2の負荷型Pチャネル型MOSトランジスタ及び前記第1及び第2の駆動型Nチャネル型MOSトランジスタのゲート絶縁膜厚は、4nm以下である。前記電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御し、前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第2の駆動型Nチャネル型MOSトランジスタがオン状態である場合に、前記第1の負荷型Pチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、前記第2の駆動型Nチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を前記動作状態に対し前記待機状態の方を小さくする。

【0008】

前記Nチャネル型MOSトランジスタの基板電極は接地電位あるいは前記ソース線に接続される。

【0009】

待機時には、オン状態のMOSトランジスタのゲート−ソース電極間に印加される電圧が電源電圧より小さくなる為ゲートトンネルリーク電流を低減でき、なおかつラッチ等の保持データが破壊されない。

【0010】

また、サブスレッショルド電流がGIDLより小さい、しきい値の高いMOSトランジスタでは、オフ状態でのゲート−ドレイン電極間に印加される電圧が電源電圧より小さいため、GIDLが低減されオフ電流が低減される。しかし、Nチャネル型MOSトランジスタの基板電極には、接地電位あるいは接地電位より高い電圧が、Pチャネル型MOSトランジスタの基板電極には電源電位が印加されるため接合リーク電流は増大しない。

【0011】

図13にしきい値電圧が0.7V程度と比較的高くサブスレッショルド電流がGIDL電流より小さいNチャネル型MOSトランジスタのドレイン−ソース間電流Idsのゲート電圧依存性を示した。Idsはログスケールで表示されている。ドレイン電圧を電源電位(1.5V)にした場合と本発明である電源電位より低い電位にした場合(1.0V)について示している。ソース電極および基板電極は接地電位に接続され、基板電位にバイアスがかけられていない。オフ状態では、ゲート−ドレイン間に印加される電位差が下がりGIDL電流が小さくなるため、リーク電流が低減する低減できる。

【0012】

また、本願発明の半導体装置は、少なくとも1個のNチャネル型MOSトランジスタを有する第1の電流路と、少なくとも1個のPチャネル型MOSトランジスタを有する第2の電流路からなる少なくとも1個の論理回路からなり、前記論理回路の双方の電流路の一方の端子が相互に接続されており、一方の電流路が導通状態のとき他方の電流路が非導通状態となる。前記少なくとも1個の論理回路は、前記第1の電流路の他方の端子がソース線によって接続されており、当該ソース線にスイッチ回路が接続されており、当該スイッチ回路は、前記少なくとも1個の論理回路が動作するように選択された場合にはソース線を接地電位に保ち、かつ、そのように選択されない待機時にはソース線を接地電位より高い電圧に保つことを特徴とする。

【発明の効果】

【0013】

本発明によれば、データを破壊することなくリーク電流を低減することができる。

【図面の簡単な説明】

【0014】

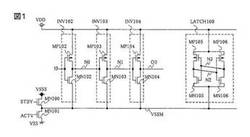

【図1】実施例1に係わる半導体装置集積回路の回路図。

【図2】実施例1に係わる半導体装置集積回路の動作波形。

【図3】実施例2に係わる半導体装置集積回路の回路図。

【図4】実施例2係わる半導体装置集積回路の動作波形。

【図5】実施例3に係わる半導体記憶装置の回路図。

【図6】実施例3に係わる待機時および読み出し時の動作波形。

【図7】実施例3に係わる待機時および書き込み時の動作波形。

【図8】実施例4に係わる半導体集積回路の回路図。

【図9】実施例5に係わる半導体集積回路の回路図。

【図10】実施例6に係わる半導体集積回路の回路図。

【図11】実施例7に係わる半導体集積回路の回路図。

【図12】実施例7に係わる半導体集積回路の動作波形。

【図13】本方式におけるMOSトランジスタ電流低減効果。

【図14】実施例3に係わるリーク電流低減効果。

【図15】実施例3に係わる半導体記憶装置の概略回路図。

【図16】実施例3に係わる降圧回路の特性図。

【図17】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図18】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図19】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図20】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図21】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図22】本発明の製造方法を適用した場合の特性図。

【発明を実施するための形態】

【0015】

以下、本発明に係わる半導体記憶装置の好適ないくつかの事例につき、図面を用いて説明する。

【実施例】

【0016】

〈実施例1〉

図1は、本発明に係わる半導体装置の一実施例を示す回路図である。本回路は、Pチャネル型MOSトランジスタMPおよびNチャネル型MOSトランジスタMNより構成される半導体集積回路の一部を示しており、MOSトランジスタのゲートに使用される絶縁膜が4nm以下か、ゲートトンネルリーク電流が電源電圧1.5Vで、10-12 A/μm

2 以上である半導体集積回路製造技術を用いて単結晶シリコンのような半導体基板に形成される。

【0017】

図1には半導体集積回路装置の一部として、インバータ回路INVおよびデータを保持するラッチ回路LATCHが示されている。

【0018】

インバータ回路INV102は、Pチャネル型MOSトランジスタMP102およびNチャネル型MOSトランジスタMN102より構成される。Pチャネル型MOSトランジスタMP102のゲート電極には入力信号I0が、ドレイン電極には接続ノードN0が、ソース電極には電源電位VDDがそれぞれ接続される。

【0019】

またPチャネル型MOSトランジスタMP102の基板電極は、電源電位VDDに接続される。Nチャネル型MOSトランジスタMN102のゲート電極には入力信号I0が、ドレイン電極には接続ノードN0が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN102の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。

【0020】

インバータ回路INV103は、Pチャネル型MOSトランジスタMP103およびNチャネル型MOSトランジスタMN103より構成される。Pチャネル型MOSトランジスタMP103のゲート電極には接続ノードN0が、ドレイン電極には接続ノードN1が、ソース電極には電源電位VDDがそれぞれ接続される。またPチャネル型MOSトランジスタMP103の基板電極は、電源電位VDDに接続される。Nチャネル型MOSトランジスタMN103のゲート電極には接続ノードN0が、ドレイン電極には接続ノードN1が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN103の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。

【0021】

インバータ回路INV104は、Pチャネル型MOSトランジスタMP104およびNチャネル型MOSトランジスタMN104より構成される。Pチャネル型MOSトランジスタMP104のゲート電極には接続ノードN1が、ドレイン電極には出力ノードO0が、ソース電極には電源電位VDDがそれぞれ接続される。またPチャネル型MOSトランジスタMP104の基板電極は、電源電位VDDに接続される。Nチャネル型MOSトランジスタMN104のゲート電極には接続ノードN1が、ドレイン電極には出力ノードO0が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN104の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。

【0022】

ラッチ回路LATCHは、CMOSインバータの入力と出力が互いに接続されて構成されるフリップ・フロップ(Pチャネル型MOSトランジスタ(MP105、MP06)、Nチャネル型トランジスタ(MN105、MN106)で構成される)で、記憶ノードN2と記憶ノードN3に情報が記憶される。

【0023】

Pチャネル型MOSトランジスタMP105のゲート電極には記憶ノードN3が、ドレイン電極には記憶ノードN2が、ソース電極には電源電位VDDがそれぞれ接続される。またPチャネル型MOSトランジスタMP105の基板電極は、電源電位VDDに接続される。

【0024】

Pチャネル型MOSトランジスタMP106のゲート電極には記憶ノードN2が、ドレイン電極には記憶ノードN3が、ソース電極には電源電位VDDがそれぞれ接続される。またPチャネル型MOSトランジスタMP106の基板電極は、電源電位VDDに接続される。

【0025】

Nチャネル型MOSトランジスタMP105のゲート電極には記憶ノードN3が、ドレイン電極には記憶ノードN2が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN105の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。Nチャネル型MOSトランジスタMP106のゲート電極には記憶ノードN2が、ドレイン電極には記憶ノードN3が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN106の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。

【0026】

また、接地ソース電極線VSSMを接地電位VSSと接続するNチャネル型MOSトランジスタMN101および接地ソース電極線VSSMを接地電位より高い電位VSSSたとえば0.5Vに接続するNチャネル型MOSトランジスタMN100が配置される。

【0027】

次に動作状態および待機状態について図2の動作波形を用いて説明する。ここでは、電源電圧VDDを1.5V、接地電位VSSを0V、接地電位より高い電位VSSSを0.5Vとする。この電圧はデバイスの特性等により変更される。

【0028】

動作時では、Nチャネル型MOSトランジスタMN101がオンしており、VSSMは接地電位VSS、たとえば0Vとなっている。I0、N1、N3の電位が1.5V、N0、N2の電位が0Vとなっている。このときPチャネル型MOSトランジスタ(MP103、MP106)およびNチャネル型MOSトランジスタ(MN102、MN104、MN105)がオン、Pチャネル型MOSトランジスタ(MP102、MP104、MP105)およびNチャネル型MOSトランジスタ(MN103、MN106)がオフしている。

【0029】

Pチャネル型MOSトランジスタMP103のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がソース電極からゲート電極に流れる。この電流は、接続ノードN0、オン状態のNチャネル型MOSトランジスタMN102を通って接地電位VSSへ流れる。

【0030】

同様に、Nチャネル型MOSトランジスタMP104のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がゲート電極からソース電極に流れる。この電流は、接続ノードN1、オン状態のPチャネル型MOSトランジスタMP103を通って電源電位VDDから流れる。

【0031】

同様に、Pチャネル型MOSトランジスタMP106のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がソース電極からゲート電極に流れる。この電流は、接続ノードN2、オン状態のNチャネル型MOSトランジスタMN105を通って接地電位VSSへ流れる。

【0032】

同様に、Nチャネル型MOSトランジスタMN105のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がゲート電極からソース電極に流れる。この電流は、接続ノードN2、オン状態のPチャネル型MOSトランジスタMP106を通って電源電位VDDから流れる。以上のようなパスにより動作時にはゲートトンネルリーク電流が流れる。

【0033】

一方待機時には、Nチャネル型MOSトランジスタMN100がオンしており、VSSMは接地電位より高い電位VSSSたとえば0.5Vとなっている。I0、N1、N3の電位が1.5V、N0、N2の電位が0.5Vとなっている。このときPチャネル型MOSトランジスタ(MP103、MP106)およびNチャネル型MOSトランジスタ(MN102、MN104、MN105)がオン、Pチャネル型MOSトランジスタ(MP102、MP104、MP105)およびNチャネル型MOSトランジスタ(MN103、MN106)がオフしている。

【0034】

Pチャネル型MOSトランジスタMP103のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0035】

同様に、Nチャネル型MOSトランジスタMN104のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0036】

同様に、Pチャネル型MOSトランジスタMP106のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0037】

同様に、Nチャネル型MOSトランジスタMN105のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が印加されている場合に比べ、約1桁低減される。

【0038】

以上のようにゲート−ソース間に印加される電圧が下がるためゲートトンネルリーク電流が減少する。一方、保持データは破壊されない。また、オフ状態でゲート−ドレイン間に印可される電圧が下がるためGIDL電流も減少する。

【0039】

本実施例では、インバータ回路およびラッチ回路の場合について述べたが、その他の半導体集積回路たとえば、ナンド回路、ノア回路等でも同様の効果が得られる。

【0040】

〈実施例2〉

図3は、本発明に係わる半導体装置の一実施例を示す回路図である。本回路は、Pチャネル型MOSトランジスタMPおよびNチャネル型MOSトランジスタMNより構成される半導体集積回路の一部を示しており、MOSトランジスタのゲートに使用される絶縁膜が4nm以下か、トンネルリーク電流が電源電圧1.5Vで、10-12 A/μm2 以上

である半導体集積回路製造技術を用いて単結晶シリコンのような半導体基板に形成される。

【0041】

図3には半導体集積回路装置の一部として、インバータ回路INVおよびデータを保持するラッチ回路LATCHが示されている。

【0042】

インバータ回路INV112は、Pチャネル型MOSトランジスタMP112およびNチャネル型MOSトランジスタMN112より構成される。Pチャネル型MOSトランジスタMP112のゲート電極には入力信号I1が、ドレイン電極には接続ノードN4が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP112の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。Nチャネル型MOSトランジスタMN112のゲート電極には入力信号I1が、ドレイン電極には接続ノードN4が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN112の基板電極は、接地電位VSSに接続される。

【0043】

インバータ回路INV113は、Pチャネル型MOSトランジスタMP113およびNチャネル型MOSトランジスタMN113より構成される。Pチャネル型MOSトランジスタMP113のゲート電極には接続ノードN4が、ドレイン電極には接続ノードN5が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP113の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。Nチャネル型MOSトランジスタMN113のゲート電極には接続ノードN4が、ドレイン電極には接続ノードN5が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN114の基板電極は、接地電位VSSに接続される。

【0044】

インバータ回路INV114は、Pチャネル型MOSトランジスタMP114およびNチャネル型MOSトランジスタMN114より構成される。Pチャネル型MOSトランジスタMP114のゲート電極には接続ノードN5が、ドレイン電極には出力信号O1が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP114の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。Nチャネル型MOSトランジスタMN114のゲート電極には接続ノードN5が、ドレイン電極には出力信号O1が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN114の基板電極は、接地電位VSSに接続される。

【0045】

ラッチ回路LATCHは、CMOSインバータの入力と出力が互いに接続されて構成されるフリップ・フロップ(Pチャネル型MOSトランジスタ(MP115、MP116)、Nチャネル型トランジスタ(MN115、MN116)で構成される)で、記憶ノードN6と記憶ノードN7に情報が記憶される。

【0046】

Pチャネル型MOSトランジスタMP115のゲート電極には記憶ノードN7が、ドレイン電極には記憶ノードN6が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP105の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。

【0047】

Pチャネル型MOSトランジスタMP116のゲート電極には記憶ノードN6が、ドレイン電極には記憶ノードN7が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP116の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。

【0048】

Nチャネル型MOSトランジスタMP115のゲート電極には記憶ノードN7が、ドレイン電極には記憶ノードN6が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN115の基板電極は、接地電位VSSに接続される。

【0049】

Nチャネル型MOSトランジスタMP116のゲート電極には記憶ノードN6が、ドレイン電極には記憶ノードN7が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN116の基板電極は、接地電位VSSに接続される。

【0050】

また、電源ソース電極線VDDMを電源電位VDDと接続するPチャネル型MOSトランジスタMP101および電源ソース電極線VDDMを電源電位より低い電位VDDDたとえば1.0Vに接続するPチャネル型MOSトランジスタMP100が配置される。

【0051】

次に動作状態および待機状態について図4の動作波形を用いて説明する。ここでは、電源電圧VDDを1.5V、接地電位VSSを0V、電源電位より低い電位VDDDを1.0Vとする。この電圧はデバイスの特性等により変更される。

【0052】

動作時では、Nチャネル型MOSトランジスタMP100がオンしており、VDDMは電源電位VDD、たとえば1.5Vとなっている。N4、N7の電位が1.5V、I1、N5、N6の電位が0Vとなっている。このときPチャネル型MOSトランジスタ(MP112、MP114、MP116)およびNチャネル型MOSトランジスタ(MN113、MN11 5)がオン、Pチャネル型MOSトランジスタ(MP113、MP11 5)およびNチャネル型MOSトランジスタ(MN112、MP114、MN116)がオフしている。

【0053】

Nチャネル型MOSトランジスタMN113のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がゲート電極からソース電極に流れる。この電流は、接続ノードN4、オン状態のPチャネル型MOSトランジスタMP112を通って電源電位VDDから流れる。

【0054】

同様に、Pチャネル型MOSトランジスタMP114のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がソース電極からゲート電極に流れる。この電流は、接続ノードN5、オン状態のNチャネル型MOSトランジスタMN113を通って接地電位VSSへ流れる。

【0055】

同様に、Pチャネル型MOSトランジスタMP116のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がソース電極からゲート電極に流れる。この電流は、接続ノードN6、オン状態のNチャネル型MOSトランジスタMN115を通って接地電位VSSへ流れる。

【0056】

同様に、Nチャネル型MOSトランジスタMN115のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がゲート電極からソース電極に流れる。この電流は、接続ノードN6、オン状態のPチャネル型MOSトランジスタMP116を通って電源電位VDDから流れる。以上のようなパスにより動作時にはゲートトンネルリーク電流が流れる。

【0057】

一方待機時には、Pチャネル型MOSトランジスタMP101がオンしており、VDDMは電源電位より低い電位VVDDたとえば1.0Vとなっている。N4、N7の電位が1.0V、I1、N5、N6の電位が0Vとなっている。このときPチャネル型MOSトランジスタ(MP112、MP114、MP116)およびNチャネル型MOSトランジスタ(MN113、MN115)がオン、Pチャネル型MOSトランジスタ(MP113、MP115)およびNチャネル型MOSトランジスタ(MN112、MN114、MN116)がオフしている。

【0058】

Nチャネル型MOSトランジスタMN113のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0059】

同様に、Pチャネル型MOSトランジスタMP114のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0060】

同様に、Pチャネル型MOSトランジスタMP116のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0061】

同様に、Nチャネル型MOSトランジスタMN115のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0062】

以上のようにゲート−ソース間に印加される電圧が下がるためゲートトンネルリーク電流が減少する。一方、保持データは破壊されない。また、オフ状態でゲート−ドレイン間に印可される電圧が下がるためGIDL電流も減少する。

【0063】

本実施例では、インバータ回路およびラッチ回路の場合について述べたが、その他の半導体集積回路たとえば、ナンド回路、ノア回路等でも同様の効果が得られる

【0064】

〈実施例3〉

図15は、本発明をSRAMに適用した場合の一実施例を示す回路図である。本半導体製造装置98は、Pチャネル型MOSトランジスタおよびNチャネル型MOSトランジスタより構成され、MOSトランジスタのゲートに使用される絶縁膜が4nm 以下か、トンネルリーク電流が電源電圧1.5Vで、10-12 A/μm2 以上である半導体集積回路製

造技術を用いて単結晶シリコンのような半導体基板に形成される。

【0065】

半導体装置であるSRAM98は、複数のマットMEMBLKに分割されている。マットの詳細は図5に示した。マット単位は例えば2M ビット毎で、16M のSRAMでは8マットに分割される。降圧回路PWRは、外部パッドより印加される電源電位VCCを基に、内部電源(VDD、VSSS、VDDD)を生成し各マットへ分配する。インプットバッファINBUFからのデータ116は、プリデコーダ115および制御回路117を通してデコード信号および制御信号となり、各マットに分配される。各マット108は、複数の基本ユニット106より構成される。基本ユニットは2カラムのメモリCELLで構成される。

【0066】

CELL0は、1対のCMOSインバータの入力と出力が互いに接続されて構成されるフリップ・フロップ(負荷型Pチャネル型MOSトランジスタ(MP00、MP01)、駆動型Nチャネル型トランジスタ(MN00、MN01)で構成される)と、前記フリップ・フロップの記憶ノードNL0と記憶ノードNR0とをデータ線(DT0、DB0)に選択的に接続する転送型Nチャネル型MOSトランジスタ(MN02、MN03)とで構成される。Nチャネル型MOSトランジスタ(MN02、MN03)のゲート電極には、サブワード線SWL0が接続される。

【0067】

メモリセルCELL1は、1対のCMOSインバータの入力と出力が互いに接続されて構成されるフリップ・フロップ(Pチャネル型MOSトランジスタ(MP10、MP11)、Nチャネル型トランジスタ(MN10、MN11)で構成される)と、前記フリップ・フロップの記憶ノードNL1と記憶ノードNR1とをデータ線(DT1、DB1)に選択的に接続するNチャネル型MOSトランジスタ(MN12、MN13)とで構成される。Nチャネル型MOSトランジスタ(MN12、MN13)のゲート電極には、サブワード線SWL0が接続される。

【0068】

また、基本ユニットには、センスアンプ回路(103)とリードデータドライブ回路(104)とライトアンプ回路(105)とイコライズ・プリチャージ回路(99、100)およびYスイッチ回路(101、102)が含まれている。センスアンプ回路(103)は、Pチャネル型MOSトランジスタ(MP20、MP21)とNチャネル型MOSトランジスタ(MN20、MN21)からなるフリップ・フロップとセンスアンプを活性にするNチャネル型MOSトランジスタMN22からなるラッチ型センスアンプ回路とスイッチ回路(MP22、MP23)から構成される。MOSトランジスタ(MN22、MP22、MP23)のゲート電極には、活性化信号SAが接続されている。

【0069】

Yスイッチ回路101はデータ線(DT0、DB0)とセンスアンプ回路103をつなぐPチャネル型MOSトランジスタ(MP05、MP06)とNチャネル型MOSトランジスタ(MN04、MN05)からなる。

【0070】

Yスイッチ回路102はデータ線(DT1、DB1)とセンスアンプ回路103をつなぐPチャネル型MOSトランジスタ(MP15、MP16)とNチャネル型MOSトランジスタ(MN14、MN15)からなる。

【0071】

制御信号(YSW、YSWB)は、センスアンプ回路103をデータ線(DT0、DB0)に接続するかデータ線(DT1、DB1)に接続するか選択する信号である。

【0072】

ライトアンプ回路105は、2つのクロックドインバータ(CINV2、CINV3)およびインバータINV0より構成される。制御信号(WBC、WBCB)によってデータバス111の信号がデータ線に伝播される。

【0073】

リードデータドライブ回路104は、2つのクロックドインバータ(CINV2、CINV3)より構成される。制御信号(RBC、RBCB)によってデータバス111に読み出しデータが伝播される。

【0074】

イコライズ・プリチャージ回路99は、電源電位VDDとデータ線DT0をつなぐPチャネル型MOSトランジスタMP02と電源電位VDDとデータ線DB0をつなぐPチャネル型MOSトランジスタMP03およびデータ線DT0とデータ線DB0をつなぐPチャネル型MOSトランジスタMP04より構成される。

【0075】

Pチャネル型MOSトランジスタ(MP02、MP03、MP04)のゲート電極には制御信号EQが接続される。

【0076】

イコライズ・プリチャージ回路99は、電源電位VDDとデータ線DT0をつなぐPチャネル型MOSトランジスタMP02と電源電位VDDとデータ線DB0をつなぐPチャネル型MOSトランジスタMP03およびデータ線DT0とデータ線DB0をつなぐPチャネル型MOSトランジスタMP04より構成される。Pチャネル型MOSトランジスタ(MP02、MP03、MP04)のゲート電極には制御信号EQが接続される。

【0077】

イコライズ・プリチャージ回路100は、電源電位VDDとデータ線DT1をつなぐPチャネル型MOSトランジスタMP12と電源電位VDDとデータ線DB1をつなぐPチャネル型MOSトランジスタMP13およびデータ線DT1とデータ線DB1をつなぐPチャネル型MOSトランジスタMP14より構成される。Pチャネル型MOSトランジスタ(MP12、MP13、MP14)のゲート電極には制御信号EQが接続される。

【0078】

各カラムには待機時にデータ線(DT、DB)に電源電圧より低い電圧、たとえば1.0Vを供給するためのスイッチ回路(109、110)が配置される。スイッチ回路109は、電源電圧より低い電圧VDDDとデータ線DT0を接続するPチャネル型MOSトランジスタMP07と電源電圧より低い電圧VDDDとデータ線DB0を接続するPチャネル型MOSトランジスタMP08より構成される。Pチャネル型MOSトランジスタ(MP07、MP08)のゲート電極には制御信号CVDDDが接続される。

【0079】

スイッチ回路110は、電源電圧より低い電圧VDDDとデータ線DT1を接続するPチャネル型MOSトランジスタMP17と電源電圧より低い電圧VDDDとデータ線DB1を接続するPチャネル型MOSトランジスタMP18より構成される。Pチャネル型MOSトランジスタ(MP17、MP18)のゲート電極には制御信号CVDDDが接続される。

【0080】

メモリマット108内の全てのメモリセル接地ソース電極線VSSMは、金属層によって接続されており、Nチャネル型MOSトランジスタ(MN6、MN7)によって電源に接続される。Nチャネル型MOSトランジスタMN6は接地電位VSSより高い電圧を供給する電源VSSSと接地ソース電極線VSSMを接続するトランジスタであり、ゲート電極には制御信号STVSSMが接続されている。Nチャネル型MOSトランジスタMN7は接地電位VSSと接地ソース電極線VSSMを接続するトランジスタであり、ゲート電極には制御信号ACVSSMが接続されている。

【0081】

制御信号STVSSMは、チップ選択信号CSおよびマット選択信号MATを使ってアンド回路AND0およびインバータ回路INV1によって生成される。制御信号ACVSSMは、チップ選択信号CSおよびマット選択信号MATを使ってアンド回路AND0によって生成される。

【0082】

制御信号CVDDDは、チップ選択信号CSおよびマット選択信号MATを使ってアンド回路AND0によって生成される。

【0083】

サブワード線SWLは入力されたアドレスおよび制御信号116をプリデコーダ115でプリデコードし、ワードデコーダおよびワードドライバ114により生成される。

【0084】

制御信号EQは、チップ選択信号CS、マット選択信号MATおよびリセットパルスATDを使ってナンド回路NAND0によって生成される。

【0085】

制御信号(YSWB、YSW)は、YアドレスAYを使って、インバータ回路INV2によって生成される。

【0086】

制御信号SAは、チップ選択信号CS、マット選択信号MAT、書き込み選択信号WEおよびFSENを使ってアンド回路AND2およびインバータ回路(INV3、INV4)によって生成される。FSENはATDより生成されるタイミングパルスである。

【0087】

制御信号(RBC、RBCB)は、制御信号SAを使ってインバータ回路INV5によって生成される。

【0088】

制御信号(WBC、WBCB)は、チップ選択信号CS、マット選択信号MATおよび書き込み選択信号WEを使ってアンド回路AND3およびインバータ回路INV6によって生成される。

【0089】

制御信号(CS、WE、YA、MAT、ATD)は、入力されたアドレスおよび制御信号よりコントロール回路117を用いて生成される。マット選択信号MATは、図15に示したように、別のコントロール回路118を用いて、速いマット選択信号FMATが用意される場合もある。ワード線の選択は誤動作防止のためプロセスばらつき・タイミングを十分に考慮するのに対し、メモリセルに対し読み出し・書き込みをするために駆動される回路( 動作電位を選択状態に制御する回路、イコライズ・プリチャージ回路等) はワード線の選択よりも早ければ、タイミングの制御精度は落としてもよい。

【0090】

そこで、ワード線を選択するもととなるコントロール回路117には高いしきい値のMOSFET( Pチャネル型とNチャネル型いずれも含む) を用い、メモリセルに対し読み出し・書き込みをするために駆動される回路を活性化する信号を出力するコントロール回路118には前記高いしきい値及び低いしきい値の2種類のしきい値のMOSFET( Pチャネル型とNチャネル型いずれも含む) を用いる。しきい値の低いMOSFETを含めると、プロセスばらつきに対して弱くなり、出力タイミングの精度をとることが難しくなるが、(コントロール回路117よりコントロール回路118は早くマット選択信号を出力することができる。同じ回路構成を用いて設計を簡易にすることもできる。ワード線を選択するもととなるコントロール回路よりも低いしきい値のMOSFETを含めてしきい値の種類を増やしてメモリセルに対し読み出し・書き込みをするために駆動される回路を制御する回路を構成する。これにより、ワード線を選択するもととなるマット選択信号MATのタイミングの精度を上げるとともに、メモリセルに対し読み出し・書き込みをするために駆動される回路を選択するもととなるマット選択信号FMATのタイミングをマット選択信号MATよりも早く確実に出力させることができる。

【0091】

本構成は非同期式で選択タイミングの精度が厳しいメモリ装置の設計に特に有効である。速いマット選択信号FMATは、例えばメモリセル接地ソース電極線VSSMを制御する回路のアンド回路AND0、VDDD供給を制御する回路のアンド回路AND1、イコライズ・プリチャージを制御する回路のナンド回路NAND0に、マット信号MATの代わりに使用される。

【0092】

次に待機状態から読み出し動作を行う場合について図6の動作波形を用いて説明する。チップ選択信号CSが“L”(“LOW”レベル)のときあるいはマットが選択されてない時には、メモリマットは待機状態となる。このときメモリセル接地ソース電極線VSSMには接地電位より高い電圧VSSSたとえば0.5Vが供給される。またデータ線(DT、DB)には、電源電圧VDDより低い電圧VDDDたとえば1.0Vが供給される。このときメモリセルCELL0の蓄積ノードNL0は、0.5Vに、NR0は電源電位VDDたとえば1.5Vとなる。オン状態であるPチャネル型MOSトランジスタMP01のゲート−ソース電極間には電源電圧1.5Vより低い1.0Vの電圧が印加され、ゲートトンネルリーク電流が低減される。またオン状態であるNチャネル型MOSトランジスタMN00のゲート−ソース電極間には電源電圧1.5Vより低い1.0Vの電圧が印加され、ゲートトンネルリーク電流が低減される。また、オフ状態のトランスファーNチャネル型MOSトランジスタ(MN02、MN03)のゲート−ソース電極間には電源電圧1.5Vより低い1.0Vの電圧が印加され、GIDL電流が低減される。

【0093】

チップ選択信号CSが“H”になるかアドレスが変わると、ATDパルスが生成され読み出し動作が開始される。マット選択信号MATとチップ選択信号CSにより、選択されたマット108のメモリセル接地ソース電極線VSSMが接地電位0Vとなる。また、データ線(DT、DB)に電圧VDDDを供給していたPチャネル型MOSトランジスタ(MP07、MP08、MP17、MP18)がオフする。

【0094】

ATDパルスから生成された制御信号EQによりデータ線(DT、DB)が、電源電圧VDDにプリチャージされる。

【0095】

この結果メモリセルCELL0の蓄積ノードNL0は、0Vに、NR0は電源電位VDDたとえば1.5Vとなる。オン状態であるPチャネル型MOSトランジスタMP01のゲート−ソース電極間には電源電圧1.5Vが印加され、ゲートトンネルリーク電流が増大する。またオン状態であるNチャネル型MOSトランジスタMN00のゲート−ソース電極間には電源電圧1.5Vが印加され、ゲートトンネルリーク電流が増大する。また、オフ状態のトランスファーNチャネル型MOSトランジスタ(MN02、MN03)のゲート−ソース電極間には電源電圧1.5Vが印加され、GIDL電流が増加する。

【0096】

その後ワード線SWL0が選択され、データ線(DT、DB)に微小電位差が生じ、制御信号SAでセンスアンプ103を活性化することにより微小電位差を増幅してデータをデータバス111に出力する。

【0097】

次に待機状態から書き込み動作を行う場合について図7の動作波形を用いて説明する。待機状態は読み出し動作の時と同様である。

【0098】

チップ選択信号CSが“H”になるかアドレスが変わると、ATDパルスが生成され書き込み動作が開始される。マット選択信号MATとチップ選択信号CSにより、選択されたマット108のメモリセル接地ソース電極線VSSMが接地電位0Vとなる。また、データ線(DT、DB)に電圧VDDDを供給していたPチャネル型MOSトランジスタ(MP07、MP08、MP17、MP18)がオフする。

【0099】

ATDパルスから生成された制御信号EQによりデータ線(DT、DB)が、電源電圧VDDにプリチャージされる。

【0100】

この結果メモリセルCELL0の蓄積ノードNL0は、0Vに、NR0は電源電位VDDたとえば1.5Vとなる。オン状態であるPチャネル型MOSトランジスタMP01のゲート−ソース電極間には電源電圧1.5Vが印加され、ゲートトンネルリーク電流が増大する。またオン状態であるNチャネル型MOSトランジスタMN00のゲート−ソース電極間には電源電圧1.5Vが印加され、ゲートトンネルリーク電流が増大する。また、オフ状態のトランスファーNチャネル型MOSトランジスタ(MN02、MN03)のゲート−ソース電極間には電源電圧1.5Vが印加され、GIDL電流が増加する。

【0101】

その後ワード線SWL0が選択される。データ線(DT、DB)には、データバス111の信号が入力され、この信号によりメモリセルCELLにデータが書き込まれる。

【0102】

本実施例ではメモリセルのソース電圧を待機時に0.5Vに上げたが、メモリセルの電源を1.0Vに下げてもいい。ただし、待機状態から動作状態に変わるときは、動作状態から待機状態に変わるときより高速に移行することが要求される。このため、待機時にソース電圧を0.5Vに上げるほうが、メモリセルの電源を1.0Vにさげるより、電源回路の負担が小さくなるため、ソースを0.5Vに上げるほうが有利である。また、図13の特性を見ても分るとおり、同じ0.5Vであっても、低電位側のソース電圧を高くすることが電流を下げる上で有利であるといえる。

【0103】

図14に待機時と動作時の1SRAMセルのリーク電流を示した。GIDL電流、サブスレッショルドリーク電流、GIDL全てが待機時で小さくなっている。

【0104】

図16に降圧回路PWRの特性の一例を示す。ビット線等に供給する電位VDDD及び、メモリセルに供給する動作電位( 高電位VDD、低電位VSSS) を生成するに際し、外部パッドより供給される電位VCCがある所定値以上となるときに外部パッドより供給される電位を制御して出力する構成をとっている。例えば、外部パッドより供給される電位VCCが1.5V以下では、メモリセルに供給する高電位VDDは、外部パッドより供給される電源電位VCCと同一であり、VCCが1.5V以上では、VDDは1.5Vで一定となるように制御する。また、電源電位より低い電位VDDDは、VCCが1.0V以下では、外部パッドより供給される電位VCCと同一であり、VCCが1.0V以上では、1.0Vで一定となるように制御する。接地電位より高い電位VSSSは、電位VCCが1.0V以下の時は0Vであり、外部電源パッドより供給される電位VCCが1.0V以上の時は、メモリセルに供給する高電位側の電位VDDに基づいてそれよりより1.0V低い値になるように制御される。これにより、半導体チップの外より入力される電源電位VCCが変動してもメモリセルに印加される電圧が常に1.0Vとなりデータ破壊が生じないようにすることが可能となる。尚、別の外部パッドから供給される低電位側の電位VSSは接地電位であることから変動しないものと考えることができる。帰還回路により制御が可能となる動作電位生成回路の適用は、メモリを具備する半導体集積回路に限られず、前の実施例においても有効である。

【0105】

本実施例においては、GIDL電流の低減のために半導体装置において、ソース・ドレイン領域のうち、コンタクトをとる領域に砒素を、エクステンション領域に燐を用いたNチャネル型MOSトランジスタを具備させる。SRAMを有する半導体装置において、前記Nチャネル型MOSトランジスタをSRAMのメモリセル内のNチャネル型MOSトランジスタに用い、メモリセルを制御する周辺回路のNチャネル型MOSトランジスタにはコンタクトをとる領域とエクステンション領域いずれにも砒素を用いたNチャネル型MOSトランジスタを用いる。

【0106】

図26において、Nチャネル型MOSトランジスタのソース・ドレイン領域のうち、コンタクトをとる領域に砒素をいずれにも用い、エクステンション領域に砒素を用いたときのゲート電圧Vgsとソース・ドレイン間の電流の特性Idsを( a) に、燐を用いたときのゲート電圧Vgsとソース・ドレイン間の電流Idsの特性を( b) に示す。座標は( a) ( b) で同じである。この波形を見て明らかなように、ゲート電圧が0.0Vにおけるオフ電流は燐を用いた方( b) が明らかに低下しており、さらに今回の発明の方式( スタンバイ時にメモリセルの動作電位Vssmを0.0Vから0.5Vにあげる方式) とした場合に燐をエクステンション領域に用いることがオフ電流を低減するに対し有効であることがわかる。ここには示していないが、高温動作領域での効果が顕著であることがわかっている。

【0107】

As(砒素)よりP (リン)は、Vth −Lowering特性などのデバイス特性への変動が大きく、電流駆動力はAsより低下するため、イオン打込み濃度やエネルギーの調整が難しいため、一般にはコンタクトを取る領域及びエクステンション領域には砒素が用いられていた。特開平9-135029号においてはコンタクトを取る領域及びエクステンション領域いずれにも燐をデバイス構造が開示されているが、本発明者らによりGIDL電流低減にはエクステンション領域に燐を注入することが有効であり、コンタクトを取る領域にはデバイスの性能面( 電流駆動力、短チャネル特性) から砒素を用いることが有効であることが示された。

【0108】

本効果が得られる理由は、ゲート電極下にオーバーラップしているエクステンション領域での燐注入により、ゲート電極からの縦方向電界によるバンド曲がりが緩和されるためである。また、インプラプロファイルのブロード化により、チャネル領域とエクテンション領域との縦方向の接合電界強度が緩和され、PN接合リークが低減した効果も寄与している。

【0109】

図17〜図25は、本実施例の半導体装置の製造方法の一例を工程順に示した断面図である。それぞれの図はメモリセル部MCを構成するNチャネル型MOSトランジスタQmnとPチャネル型MOSトランジスタQmpと、周辺回路部PERIを構成するNチャネル型MOSトランジスタQpnとPチャネル型MOSトランジスタQppと、高耐圧部HVを構成するNチャネル型MOSトランジスタQhnとPチャネル型MOSトランジスタQhpとに分けて記載している。メモリセル部MCを構成するNチャネル型MOSトランジスタQmnは図5の各メモリセルCELLの駆動と転送MOSトランジスタに用いられる。メモリセル部MCを構成するPチャネル型MOSトランジスタQmpは図5の各メモリセルCELLの負荷MOSトランジスタに用いられる。周辺回路部PERIを構成するNチャネル型MOSトランジスタQpnとPチャネル型MOSトランジスタQppは図5のメモリセル部以外のPとNチャネル型MOSトランジスタに用いられる。つまり、センスアンプ回路(103)、リードデータドライブ回路(104)、ライトアンプ回路(105)、イコライズ・プリチャージ回路(99、100)とYスイッチ回路(101、102)、ワードデコーダおよびワードドライバ( 114) 、プリデコーダ( 115) 、制御回路(117)に用いられるMOSトランジスタを含む。高耐圧部HVを構成するNチャネル型MOSトランジスタQhnとPチャネル型MOSトランジスタQhpは入力と出力の動作電圧が異なる回路、つまり図15の入力バッファ( INBUF)、降圧回路( PWR) 、入出力回路IOを構成するNとPチャネル型MOSトランジスタに用いられる。

【0110】

以下、図面を用いて工程順に説明する。まず、図17( a) に示すように、たとえばp- 型の単結晶シリコンからなる半導体基板200を用意し、半導体基板200の主面に素子分離領域201を形成する。素子分離領域201は、たとえば以下のようにして形成できる。まず、半導体基板200の主面上にシリコン酸化膜(SiO2 )およびシリコン窒化膜(Si3 N4 )を順次形成し、このシリコン窒化膜をパターニングされたフォトレジスト膜を用いてエッチングし、このエッチングされたシリコン窒化膜をマスクとして半導体基板200に溝型の分離領域を形成する。その後、溝型の分離領域を埋め込む絶縁膜、たとえばシリコン酸化膜を堆積し、CMP法等を用いて溝型分離領域以外の領域のシリコン酸化膜を除去し、さらにウエットエッチング法等によりシリコン窒化膜を除去する。これにより素子分離領域(トレンチアイソレーション)201が形成される。素子分離領域は、溝型の分離領域に限定されるものではなく、例えばLOCOS(Local Oxidization of Silicon)法によって形成されたフィールド絶縁膜で形成しても良い。次のイオン注入工程による半導体基板表面のダメージを緩和するために、薄いシリコン酸化膜を堆積させる。

【0111】

その後パターニングされたフォトレジスト膜をマスクとして不純物をイオン注入し、図17( b) に示すように、pウエル210、212およびnウエル211、213を形成する。pウエルにはp型の導電型を示す不純物たとえばボロンB又はフッ化ボロンBF2をイオン注入し、nウエルにはn型の導電型を示す不純物たとえばリンP、砒素Asをイオン注入する。この後、各ウエル領域にMOSFETのしきい値を制御するための不純物( Nチャネル型MOSトランジスタではn型の導電型を示す不純物( P) 、Pチャネル型MOSトランジスタではp型の導電型を示す不純物( BF2))をイオン注入する。

【0112】

次に図17( b) に示すように、ゲート絶縁膜となるシリコン酸化膜221を形成する。この際に、高耐圧部には厚膜ゲート酸化膜、周辺回路部とメモリセル部には薄膜ゲート酸化膜をホトリソグラフィー、エッチング技術を用いて形成した。

【0113】

本実施例では、厚膜ゲート酸化膜の膜厚は外部入出力で3.3V に対応するため8.0nm、薄膜ゲート酸化膜は待機時におけるゲートリーク電流が問題となる3.0nmとした。高耐圧部以外の酸化膜をホトリソグラフィー・ウエットエッチング技術により除去した後に、再度、熱酸化して熱酸化することにより2種類の膜厚の酸化膜が形成される。その後、ゲート電極用の多結晶シリコン膜222を堆積し、レジストマスク223を用いてNとPチャネル型MOSの電極領域にそれぞれn型/p型の不純物( 燐、ボロン) をイオン注入する。

【0114】

図18( a) に示すように、ホトリソグラフィー・ドライエッチングを用いて加工することによりゲート電極230、231、232、233、234、235が形成される。次に図18( b) に示すようにエクステンション領域となる半導体領域及びそれとパンチスルーを抑制するための反対の導電型( ウエルと同導電型でウエル領域よりも高濃度)の半導体領域をイオン注入法で形成する。N チャネル型MOS トランジスタにおいてはメモリセル部MCと周辺回路部PERIと高耐圧部HVとでそれぞれマスク( 工程) を変えてイオン注入を行う。メモリセル部MCにおいてはスタンバイ時のGIDL電流を低減するためにn型の不純物である燐、p型の不純物( ボロン) を注入することによりn型半導体領域241、242とp型半導体領域243、244を形成する。その際には他の領域(Pチャネル型MOS トランジスタ領域、周辺回路部・高耐圧部領域) はレジストでマスクされる。周辺回路部PERIにおいては高速動作を実現するためにn型の不純物である砒素、p型の不純物( ボロン) を注入することによりn型半導体領域245、246とp型半導体領域247、248を形成する。その際には他の領域(Pチャネル型MOS トランジスタ領域、メモリセル部・高耐圧部領域) はレジストでマスクされる。

【0115】

次に図18( c) で示すように、Pチャネル型MOSトランジスタとなるn型ウエル領域211にはp型の不純物( ボロン) 、n型の不純物( As) を注入することにより、エクステンション領域となる半導体領域251、254、255、256、パンチスルーを抑制するための、ウエルと同導電型でウエル領域よりも高濃度の半導体領域253、254、257、258を形成する。Pチャネル型MOSトランジスタはメモリセル部MC、周辺回路部PERIで不純物の種類・イオン注入の条件( エネルギー) を変えないため、同じマスク( 工程) で行い、イオンを注入する際にはN チャネル型MOS トランジスタとなる領域及び高耐圧部HVのPチャネル型MOS トランジスタとなる領域はレジストでマスクする。高耐圧部のN チャネル型MOS トランジスタはエッジ端の縦方向電界を緩和するようにn型の不純物である砒素及び燐、p型の不純物( ボロン) を注入することによりn型半導体領域259、260、261、262とp型半導体領域263、264を形成する。分布係数の違いにより半導体表面に近いn型半導体領域259、260は砒素により主に構成され、より深く注入されるn型半導体領域261、262は燐が主成分となる。

【0116】

次に図19( a) に示すように、高耐圧部HVのPチャネル型MOSトランジスタとなるn型ウエル領域213にはp型の不純物( ボロン) 、n型の不純物( As) を注入することにより、エクステンション領域となるp型半導体領域266、パンチスルーを抑制するための、ウエルと同導電型でウエル領域よりも高濃度の半導体領域267を形成する。本実施例では、高耐圧部HVとメモリセル部MC、周辺回路部PERIでマスク( 工程、イオン打ち込み条件) を変えたが、耐圧が製品の特性を満たすことが可能であれば、Pチャネル型MOSトランジスタをメモリセル部MC、周辺回路部PERI、高耐圧部HVで不純物の種類・イオン注入の条件( エネルギー) を変えずに一つのマスク( 工程) で行うことが可能となる。

【0117】

尚、エクステンション領域及びウエルと反導電型で高濃度の半導体領域のイオン注入の順序は問わない。つまり、N チャネル型MOS トランジスタ領域へのイオン注入より先にP チャネル型MOS トランジスタとなる領域のイオン注入を行ってもよく。また、図18( b)(c) によれば、N チャネル型MOS トランジスタの内、メモリセル部、周辺回路部、高耐圧部の順にイオン注入を行っているが、順番は問わない。高耐圧部のイオン注入をするに当たって不純物量によっては、メモリセル部、周辺回路部のイオン注入の際にマスクで覆わず、高耐圧部のためにマスクを用意しないことも可能ではあるが、不純物量に違いがあれば、図18( c) のように別のマスクを用意する必要がある。

【0118】

図19( a) で示すように、半導体基板200上に、たとえばCVD法でシリコン酸化膜を堆積した後、このシリコン酸化膜を異方性エッチングすることにより、ゲート電極230、231、232、233、234、235の側壁にサイドウォールスペーサ( ゲート側壁膜) 265をそれぞれ形成する。次に図19( b) に示すように、フォトレジスト膜270をマスクとして、ウエルnウエル210、212にp型不純物(ボロン)をイオン注入し、nウエル上のゲート電極231、232、235の両側にp型半導体領域271を形成する。p型半導体領域271は、ゲート電極231、232、235およびサイドウォールスペーサ265に対して自己整合的に形成され、pチャネルMISFETのソース、ドレイン領域として機能する。

【0119】

同様に、フォトレジスト膜をマスクとしてpウエル211、213にn型不純物(As)をイオン注入し、電極とコンタクトを取ることになるn型半導体領域280を形成する。n型半導体領域280は、ゲート電極230、233、234およびサイドウォールスペーサ265に対して自己整合的に形成される。また、n型半導体領域280は、nチャネルMISFETのソース、ドレイン領域として機能する。その結果、サイドウォールスペーサ265の形成前に低濃度の不純物半導体領域を形成し、サイドウォールスペーサ265の形成後に高濃度の不純物半導体領域を形成するLDD(Lightly Doped Drain )構造のトランジスタがそれぞれの領域で形成される(図19( c) )。尚、本実施例ではNチャネル型MOSトランジスタのソース・ドレイン領域を先に形成したが、Pチャネル型MOSトランジスタを先に形成してもよい。

【0120】

次に図20( a) に示すように、シリコン酸化膜をエッチングし、ソース・ドレイン半導体領域の表面を露出し、高融点金属膜( Co、Ti、W、Mo、Ta) を堆積させ、アニールし、未反応の高融点金属膜を除去することによりゲート電極230、231、232、233、234、235及びソース・ドレインを形成する半導体領域の表面の一部をシリサイド化( 290、291) させる。その後、シリコン窒化膜292を堆積させる。

【0121】

図19( b) に示すように、半導体基板200上にCVD法またはスパッタ法でシリコン酸化膜を堆積した後、そのシリコン酸化膜を、たとえばCMP法で研磨することにより、表面が平坦化された第1層間絶縁膜300を形成する。次に、フォトリソグラフィ技術を用いて第1層間絶縁膜300に接続孔を形成する。この接続孔は、n型半導体領域あるいはp型半導体領域上の必要部分に形成する。

【0122】

接続孔内にプラグを、たとえば以下のようにして形成する。まず、接続孔の内部を含む半導体基板200の全面に窒化チタン膜301を形成する。窒化チタン膜は、たとえばCVD法により形成できる。CVD法は被膜の段差被覆性に優れるため、微細な接続孔内にも均一な膜厚で窒化チタン膜を形成できる。次に、接続孔を埋め込む金属( リチウム) 膜302を形成する。金属膜は、たとえばCVD法で形成できる。次に、接続孔以外の領域の金属膜および窒化チタン膜を、たとえばCMP法により除去してプラグを形成できる。

【0123】

このようなシリサイド層を形成することにより、接続孔12底部でのコンタクト抵抗を低減できる。同様にして第2層間絶縁膜310に接続孔を形成する。接続孔は窒化チタン膜311と金属( タングステン) 膜312により形成される。これらのプラグはローカル配線の接続に用いられる。次に、半導体基板200の全面に、CVD法またはスパッタ法によりたとえば窒化チタン膜321とアルミニウム膜322を形成し、堆積された膜をフォトリソグラフィ技術によりパターニングし、第1配線層の配線を形成する。第1 層の配線はメモリ部ではビット線等に用いられる。配線を覆う絶縁膜、たとえばシリコン酸化膜を形成し、この絶縁膜をCMP法により平坦化して第2層間絶縁膜330を形成する。第2層間絶縁膜330上に接続孔が形成される領域に開孔を有するフォトレジスト膜を形成し、このフォトレジスト膜をマスクとしてエッチングを施す。これにより第2層間絶縁膜330の所定の領域に接続孔を形成する。接続孔内にプラグを形成する。

【0124】

プラグは以下のようにして形成できる。まず、接続孔の内部を含む半導体基板200の全面にバリアメタル層340 を形成し、さらに接続孔を埋め込む金属( タングステン) 膜341を形成する。その後、接続孔以外の領域の金属膜およびバリアメタル層をCMP法により除去してプラグを形成する。バリアメタル層は第2層間絶縁膜330 等周辺へのタングステンの拡散を防止する機能を有し、たとえば窒化チタン膜を例示できる。なお、窒化チタン膜には限られず、タングステンの拡散防止機能を有する限り他の金属膜であってもよい。たとえば、窒化チタンに代えてタンタル(Ta)、窒化タンタル(TaN)を用いることもできる。第1 配線層と同様に、第2配線層の配線( 351、352) を形成する。配線を覆う絶縁膜を形成し、この絶縁膜をCMP法により平坦化して第3層間絶縁膜360を形成する。第3層間絶縁膜360上に第2 層間絶縁膜330で設けたと同様に接続孔を形成し、接続孔内にプラグ( 361、362) を形成する。第2配線層と同様に、第3配線層の配線( 363、364) を形成する。配線を覆う絶縁膜370を形成し、この絶縁膜の上に窒化シリコン膜をパッシベーション膜371として形成する。製品として出荷する前には検査工程、樹脂封止工程等がある。

【0125】

砒素をエクステンション領域とコンタクトをとる領域に注入した場合と燐をエクステンション領域に適用した本デバイス構造を用いたメモリセルを試作した結果、スタンバイ電流は25℃、90℃において約50%低減できることがわかった。つまり、通常動作の温度だけでなく、高温においても半導体装置のスタンバイ電流を抑制することができ、本構造をとることにより製品の動作保証温度( 例えば70度C以下) を高く設定することができるという効果を有する。

【0126】

薄膜NMOSに本デバイス構造を採る事により、半導体装置のスタンバイ電流が従来As構造での2.5uAから1.0uA程度と低減することができる。この効果は、スタンバイ電流の主成分がNMOSのGIDL電流(約70% 程度)であることに起因する。

【0127】

尚、メモリセル部のNチャネル型MOSトランジスタのエクステンション領域には燐のみを用いたが、高速動作のために燐及び砒素を注入することもある。この場合には、イオン源が2種類必要となるが駆動電流が増えるという効果がでる。構造は高耐圧部のNチャネル型MOSトランジスタと類似する。高耐圧MOSよりも低いエネルギーでイオン注入を行う必要があるため、高耐圧部のエクステンション領域のイオン打ちこみをするときとマスクを変える必要があり、その結果半導体領域の広がりは高耐圧部のそのものより狭くなる。

【0128】

〈実施例4〉

図8は、本発明をマイクロプロセッサに適用した実施例を示している。MOSトランジスタのゲートに使用される絶縁膜が4nm 以下か、トンネルリーク電流が電源電圧1.5Vで、10-12 A/μm2 以上である半導体集積回路製造技術を用いて単結晶シリコンの

ような半導体基板に形成される。

【0129】

マイクロプロセッサ130は、IP回路133、キャッシュメモリ131およびCPU132より構成されている。また、動作および待機状態をコントロールするコントロール回路134もマイクロプロセッサ130に搭載されている。

【0130】

キャッシュメモリ131の接地ソース電極線VSSMは、Nチャネル型MOSトランジスタMN200を介して接地電位より高い電位VSSSに接続され、またNチャネル型MOSトランジスタMN201を介して接地電位VSSに接続されている。Nチャネル型MOSトランジスタMN200のゲート電極には制御信号STBY0が接続されている。Nチャネル型MOSトランジスタMN201のゲート電極には制御信号ACTV0が接続されている。

【0131】

CPU回路132の接地ソース電極線VSSMは、Nチャネル型MOSトランジスタMN202を介して接地電位より高い電位VSSSに接続され、またNチャネル型MOSトランジスタMN203を介して接地電位VSSに接続されている。Nチャネル型MOSトランジスタMN202のゲート電極には制御信号STBY1が接続されている。Nチャネル型MOSトランジスタMN203のゲート電極には制御信号ACTV1が接続されている。

【0132】

IP回路133の接地ソース電極線VSSMは、Nチャネル型MOSトランジスタMN204を介して接地電位より高い電位VSSSに接続され、またNチャネル型MOSトランジスタMN205を介して接地電位VSSに接続されている。Nチャネル型MOSトランジスタMN204のゲート電極には制御信号STBY2が接続されている。Nチャネル型MOSトランジスタMN205のゲート電極には制御信号ACTV2が接続されている。

【0133】

制御信号STBY0が“H”、ACTV0が“L”となると、キャッシュメモリ131は、待機状態となり、VSSMの電位が接地電位より高い電圧VSSSたとえば0.5Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。ただし、キャッシュメモリ内のデータは破壊されず保持される。

【0134】

制御信号STBY0が“L”、ACTV0が“H”となると、キャッシュメモリ131は、動作状態となり、VSSMの電位が接地電位VSSとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0135】

制御信号STBY1が“H”、ACTV1が“L”となると、CPU回路132は、待機状態となり、VSSMの電位が接地電位より高い電圧VSSSたとえば0.5Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。ただし、レジスターファイルおよびラッチ内のデータは破壊されず保持される。

【0136】

制御信号STBY1が“L”、ACTV1が“H”となると、CPU回路132は、動作状態となり、VSSMの電位が接地電位VSSとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0137】

制御信号STBY2が“H”、ACTV2が“L”となると、IP138は、待機状態となり、VSSMの電位が接地電位より高い電圧VSSSたとえば0.5Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。

【0138】

制御信号STBY2が“L”、ACTV2が“H”となると、IP138は、動作状態となり、VSSMの電位が接地電位VSSとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0139】

〈実施例5〉

図9は、本発明をマイクロプロセッサに適用した実施例を示している。MOSトランジスタのゲートに使用される絶縁膜が4nm 以下か、トンネルリーク電流が電源電圧1.5Vで、10-12 A/μm2 以上である半導体集積回路製造技術を用いて単結晶シリコンの

ような半導体基板に形成される。

【0140】

マイクロプロセッサ135は、IP回路138、キャッシュメモリ136およびCPU137より構成されている。また、動作および待機状態をコントロールするコントロール回路139もマイクロプロセッサ135に搭載されている。

【0141】

キャッシュメモリ136の電源ソース電極線VDDMは、Pチャネル型MOSトランジスタMP200を介して電源電位より低い電位VDDDに接続され、またPチャネル型MOSトランジスタMP201を介して電源電位VDDに接続されている。Pチャネル型MOSトランジスタMP200のゲート電極には制御信号STBYB0が接続されている。Pチャネル型MOSトランジスタMP201のゲート電極には制御信号ACTVB0が接続されている。

【0142】

CPU回路137の電源ソース電極線VDDMは、Pチャネル型MOSトランジスタMP202を介して電源電位より低い電位VDDDに接続され、またPチャネル型MOSトランジスタMP203を介して電源電位VDDに接続されている。Pチャネル型MOSトランジスタMP202のゲート電極には制御信号STBYB1が接続されている。Pチャネル型MOSトランジスタMP203のゲート電極には制御信号ACTVB1が接続されている。

【0143】

IP回路138の電源ソース電極線VDDMは、Pチャネル型MOSトランジスタMP204を介して電源電位より低い電位VDDDに接続され、またPチャネル型MOSトランジスタMP205を介して電源電位VDDに接続されている。Pチャネル型MOSトランジスタMP204のゲート電極には制御信号STBYB2が接続されている。Pチャネル型MOSトランジスタMP205のゲート電極には制御信号ACTVB2が接続されている。

【0144】

制御信号STBYB0が“L”、ACTVB0が“H”となると、キャッシュメモリ136は、待機状態となり、VDDMの電位が電源電位より低い電圧VDDDたとえば1.0Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。ただし、キャッシュメモリ内のデータは破壊されず保持される。

【0145】

制御信号STBYB0が“H”、ACTVB0が“L”となると、キャッシュメモリ136は、動作状態となり、VDDMの電位が電源電位VDDとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。制御信号STBYB1が“L”、ACTVB1が“H”となると、CPU回路137は、待機状態となり、VDDMの電位が電源電位より低い電圧VDDDたとえば1.0Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。ただし、レジスタファイルおよびラッチ内のデータは破壊されず保持される。

【0146】

制御信号STBYB1が“H”、ACTVB1が“L”となると、CPU回路137は、動作状態となり、VDDMの電位が電源電位VDDとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0147】

制御信号STBYB2が“L”、ACTVB2が“H”となると、IP回路138は、待機状態となり、VDDMの電位が電源電位より低い電圧VDDDたとえば1.0Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。

【0148】

制御信号STBYB2が“H”、ACTVB2が“L”となると、IP回路138は、動作状態となり、VDDMの電位が電源電位VDDとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0149】

〈実施例6〉

図10は、本発明を使ったSRAMあるいはマイクロプロセッサを携帯電話などの電池で動作するシステムに応用した実施例を示している。携帯電話140には、電池141と実施例3で述べたSRAM、実施例4で述べたマイクロプロセッサ130が搭載されている。電池駆動するための端子とSRAMとマイクロプロセッサが単一の半導体基板に搭載されている半導体装置からなる。また接地電位より高い電圧VSSSたとえば0.5Vを電源電位VDDから生成する回路143も搭載されている。

【0150】

SRAM98はCSが“L”のときに待機状態となり接地電極が0.5Vとなりゲートトンネルリーク電流が低減される。

【0151】

マイクロプロセッサ130はSTBYが“H”でACTVが“L”のとき待機状態となり接地電極が0.5Vとなりゲートトンネルリーク電流が低減される。この結果電池の寿命を延ばすことが可能となる。

【0152】

〈実施例7〉

図11は、本発明を使ったSRAMあるいはマイクロプロセッサを携帯電話などの電池で動作するシステムに応用した実施例を示している。携帯電話144には、電池141とSRAM146、マイクロプロセッサ147が搭載されている。SRAM146とマイクロプロセッサ147の電源VDDIを供給する電源チップ145も搭載されている。

【0153】

図12に動作波形を示す。動作時にはスタンバイ信号STBYが“L”となりSRAM146とマイクロプロセッサ147に電源電位VDDが与えられる。待機時にはスタンバイ信号STBYが“H”となりSRAM146とマイクロプロセッサ147に電源電位VDDより低い電位が与えられる。このときゲートトンネルリーク電流およびGIDL電流が低減される。この結果電池の寿命を延ばすことが可能となる。

【0154】

尚、本文中のMOSトランジスタのゲート酸化膜を絶縁膜としたMISトランジスタに適用してもよい。本発明によれば、データを破壊することなくリーク電流を低減することができる。

【産業上の利用可能性】

【0155】

この発明は、半導体装置に広く利用することができる。

【符号の説明】

【0156】

CELL……SRAMメモリセル

MN……Nチャネル型MOSトランジスタ

MP……Pチャネル型MOSトランジスタ

INV ……インバータ回路

CINV ……クロックドインバータ回路

LATCH……ラッチ回路

NAND……NAND回路

AND……NAND回路

N……接続ノード

I……入力信号

O……出力信号

NL、NR……SRAMメモリセル内部ノード

VDD……電源電位

VDDD……電源電位より低い電位

VCC……外部パッドより供給される高電位側の電源電位

VDDM……電源ソース電極線

VSS……接地電位

VSSS……接地電位より高い電位

VSSM……接地ソース電極線

DT、DB……データ線

SWL……サブワード線

STBY……待機選択信号

ACTV……動作選択信号

ACVSSM……制御信号

STVSSM……制御信号

CVDDD……制御信号

EQ……イコライズ・プリチャージ回路制御信号

YSW、YSWB……Yスイッチ制御信号

SA……センスアンプ制御信号

RBC、RBCB……読み出しデータ出力制御信号

WBC、WBCB……書き込みデータ入力制御信号

CS……チップ選択信号

WE……書き込み選択信号

AY……Yアドレス

MAT……マット選択信号

ATD……ATDパルス

98、146……SRAM

99、100……イコライズ、プリチャージ回路

101、102……Yスイッチ回路

103……センスアンプ回路

104……リードデータドライブ回路

105……ライトアンプ回路

106……基本ユニット

108、MEMBLK……メモリセルマット

109、110……スイッチ回路

111……データバス

114……ワードデコーダおよびワードドライバ

115……プリデコーダ

116……アドレスおよび制御信号

117、118……制御回路

130、135、147……マイクロプロセッサ

131、136……キャッシュメモリ

132、137……CPU回路

133、138……IP回路

134、139……コントロール回路

140、144……携帯電話システム

141……電池

143、145……電源回路。

FMAT……速いマット選択信号

PWR……降圧回路

INBUF……インプットバッファ

Qmn、Qmp……メモリセル部のNとPチャネル型MISFET

Qpn、Qpp……周辺回路部のNとPチャネル型MISFET

Qhn、Qhp……高耐圧部のNとPチャネル型MISFET

200……半導体基板

201……素子分離領域

210、211、212、213……ウエル

221……絶縁膜

222……多結晶シリコン膜

223、270……レジストマスク

230、231、232、233、234、235……ゲート電極

241、242、245、246、253、254、257、258、259、

260、261、262、267、280……n型半導体領域

243、244、247、248、251、254、255、256、263、

264、266、271……p型半導体領域

265……サイドウォールスペーサ

290、291……シリサイド膜

292……シリコン窒化

300、310、330、360、370……層間絶縁膜

301、311、321……窒化チタン膜

302、312、322、341、352、364……金属膜

340、351、364……バリアメタル層

371……パッシベーション膜。

【技術分野】

【0001】

本発明は、半導体装置の製造方法、特にSRAM(static random access memory )、システムLSI に搭載されるオンチップメモリ、マイクロプロセッサ、あるいは、システムLSIなどに関する。

【背景技術】

【0002】

ゲートトンネルリーク電流を低減する公知技術として、特願平9-536055が知られている。この公知例においては、ゲートトンネルリーク電流が大きいときにゲート酸化膜の厚いゲートトンネルリーク電流の小さいスイッチMOSで電源を遮断することにより、リーク電流を削減する回路が示されている。また、GIDL(Gate Induced Drain Leakage)電流を低減する技術として、特願2000−357962号が知られている。この公知例においては、MOSトランジスタのしきい値が比較的低いことを前提として、まずサブスレッショルドリーク電流を削減するためにPチャネル型MOSトランジスタの基板電極を電源電圧以上、Nチャネル型MOSトランジスタの基板電極を接地電位以下に制御する。その結果GIDLが顕在化するため、電源電圧を低減してGIDL電流を削減する技術が開示されている。また、特開平9−135029号公報には、GIDL電流対策としてnチャネルMISトランジスタのゲート電極とソース・ドレイン領域に燐イオンを注入している技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特願平9−536055号

【特許文献2】特願2000−357962号

【特許文献3】特開平9−135029号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年プロセスの微細化に伴い、MOSトランジスタのゲート酸化膜厚が4nm以下になってきている。しかしながら、ゲート酸化膜が4nm以下になるとゲートトンネルリーク電流が増大し、ゲート電極とソース電極間に動作時の電圧が印加されると、ゲートトンネルリーク電流がティピカルプロセスで10-12 A/μm2 以上となる。

【0005】

携帯電話に使用されるLSIにおいては、低リーク電流での待機が要求される。特にSRAMは、ボタン電池でデータを一週間以上保持する必要があり、プロセスがワーストになり、酸化膜が薄くなった場合、ゲートトンネルリーク電流が増大し一週間以上のデータ保持が不可能となる問題がある。また、ドレインから基板へ流れるリーク電流であるGIDL電流の増加も同様に問題となっている。

【0006】

しかし、ゲートトンネルリーク電流を低減する従来の公知例(特願平9-536055)ではMOSで電源を遮断するため、SRAMセルやレジスタファイルおよびラッチ回路等の保持データが破壊されてしまうという問題があった。また、GIDL電流を低減する従来の公知例(特願平11-255317 )においては、比較的高いしきい値たとえば0.7VのMOSトランジスタを使用する場合には、サブスレッショルドリーク電流が顕著でないため、Nャネル型MOSトランジスタの基板電極を接地電位以下の電位に、Pチャネル型MOSトランジスタの基板電極を電源電位以上の電位にしてもオフ電流は低減せず、かえって接合リーク電流が増大するという問題があった。

【課題を解決するための手段】

【0007】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。半導体集積回路装置は、そのソース電極が電源線に接続される第1の負荷型Pチャネル型MOSトランジスタと、そのソース電極がソース線に接続され、そのドレイン電極が前記第1の負荷型Pチャネル型MOSトランジスタのドレイン電極に接続され、そのゲート電極が前記第1の負荷型Pチャネル型MOSトランジスタのゲート電極に接続される第1の駆動型Nチャネル型MOSトランジスタと、そのソース電極が前記電源線に接続される第2の負荷型Pチャネル型MOSトランジスタと、そのソース電極が前記ソース線に接続され、そのドレイン電極が前記第2の負荷型Pチャネル型MOSトランジスタのドレイン電極に接続されると共に前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのゲート電極に接続され、そのゲート電極が前記第2の負荷型Pチャネル型MOSトランジスタのゲート電極に接続されると共に前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのドレイン電極に接続される第2の駆動型Nチャネル型MOSトランジスタとを夫々が有する複数のスタティック型メモリセルを含む。前記電源線と前記ソース線との電位差である前記複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路とを具備する。前記第1及び第2の負荷型Pチャネル型MOSトランジスタ及び前記第1及び第2の駆動型Nチャネル型MOSトランジスタのゲート絶縁膜厚は、4nm以下である。前記電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御し、前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第2の駆動型Nチャネル型MOSトランジスタがオン状態である場合に、前記第1の負荷型Pチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、前記第2の駆動型Nチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を前記動作状態に対し前記待機状態の方を小さくする。

【0008】

前記Nチャネル型MOSトランジスタの基板電極は接地電位あるいは前記ソース線に接続される。

【0009】

待機時には、オン状態のMOSトランジスタのゲート−ソース電極間に印加される電圧が電源電圧より小さくなる為ゲートトンネルリーク電流を低減でき、なおかつラッチ等の保持データが破壊されない。

【0010】

また、サブスレッショルド電流がGIDLより小さい、しきい値の高いMOSトランジスタでは、オフ状態でのゲート−ドレイン電極間に印加される電圧が電源電圧より小さいため、GIDLが低減されオフ電流が低減される。しかし、Nチャネル型MOSトランジスタの基板電極には、接地電位あるいは接地電位より高い電圧が、Pチャネル型MOSトランジスタの基板電極には電源電位が印加されるため接合リーク電流は増大しない。

【0011】

図13にしきい値電圧が0.7V程度と比較的高くサブスレッショルド電流がGIDL電流より小さいNチャネル型MOSトランジスタのドレイン−ソース間電流Idsのゲート電圧依存性を示した。Idsはログスケールで表示されている。ドレイン電圧を電源電位(1.5V)にした場合と本発明である電源電位より低い電位にした場合(1.0V)について示している。ソース電極および基板電極は接地電位に接続され、基板電位にバイアスがかけられていない。オフ状態では、ゲート−ドレイン間に印加される電位差が下がりGIDL電流が小さくなるため、リーク電流が低減する低減できる。

【0012】

また、本願発明の半導体装置は、少なくとも1個のNチャネル型MOSトランジスタを有する第1の電流路と、少なくとも1個のPチャネル型MOSトランジスタを有する第2の電流路からなる少なくとも1個の論理回路からなり、前記論理回路の双方の電流路の一方の端子が相互に接続されており、一方の電流路が導通状態のとき他方の電流路が非導通状態となる。前記少なくとも1個の論理回路は、前記第1の電流路の他方の端子がソース線によって接続されており、当該ソース線にスイッチ回路が接続されており、当該スイッチ回路は、前記少なくとも1個の論理回路が動作するように選択された場合にはソース線を接地電位に保ち、かつ、そのように選択されない待機時にはソース線を接地電位より高い電圧に保つことを特徴とする。

【発明の効果】

【0013】

本発明によれば、データを破壊することなくリーク電流を低減することができる。

【図面の簡単な説明】

【0014】

【図1】実施例1に係わる半導体装置集積回路の回路図。

【図2】実施例1に係わる半導体装置集積回路の動作波形。

【図3】実施例2に係わる半導体装置集積回路の回路図。

【図4】実施例2係わる半導体装置集積回路の動作波形。

【図5】実施例3に係わる半導体記憶装置の回路図。

【図6】実施例3に係わる待機時および読み出し時の動作波形。

【図7】実施例3に係わる待機時および書き込み時の動作波形。

【図8】実施例4に係わる半導体集積回路の回路図。

【図9】実施例5に係わる半導体集積回路の回路図。

【図10】実施例6に係わる半導体集積回路の回路図。

【図11】実施例7に係わる半導体集積回路の回路図。

【図12】実施例7に係わる半導体集積回路の動作波形。

【図13】本方式におけるMOSトランジスタ電流低減効果。

【図14】実施例3に係わるリーク電流低減効果。

【図15】実施例3に係わる半導体記憶装置の概略回路図。

【図16】実施例3に係わる降圧回路の特性図。

【図17】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図18】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図19】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図20】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図21】本発明の半導体集積回路の製造方法を示す半導体基板の要部断面図。

【図22】本発明の製造方法を適用した場合の特性図。

【発明を実施するための形態】

【0015】

以下、本発明に係わる半導体記憶装置の好適ないくつかの事例につき、図面を用いて説明する。

【実施例】

【0016】

〈実施例1〉

図1は、本発明に係わる半導体装置の一実施例を示す回路図である。本回路は、Pチャネル型MOSトランジスタMPおよびNチャネル型MOSトランジスタMNより構成される半導体集積回路の一部を示しており、MOSトランジスタのゲートに使用される絶縁膜が4nm以下か、ゲートトンネルリーク電流が電源電圧1.5Vで、10-12 A/μm

2 以上である半導体集積回路製造技術を用いて単結晶シリコンのような半導体基板に形成される。

【0017】

図1には半導体集積回路装置の一部として、インバータ回路INVおよびデータを保持するラッチ回路LATCHが示されている。

【0018】

インバータ回路INV102は、Pチャネル型MOSトランジスタMP102およびNチャネル型MOSトランジスタMN102より構成される。Pチャネル型MOSトランジスタMP102のゲート電極には入力信号I0が、ドレイン電極には接続ノードN0が、ソース電極には電源電位VDDがそれぞれ接続される。

【0019】

またPチャネル型MOSトランジスタMP102の基板電極は、電源電位VDDに接続される。Nチャネル型MOSトランジスタMN102のゲート電極には入力信号I0が、ドレイン電極には接続ノードN0が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN102の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。

【0020】

インバータ回路INV103は、Pチャネル型MOSトランジスタMP103およびNチャネル型MOSトランジスタMN103より構成される。Pチャネル型MOSトランジスタMP103のゲート電極には接続ノードN0が、ドレイン電極には接続ノードN1が、ソース電極には電源電位VDDがそれぞれ接続される。またPチャネル型MOSトランジスタMP103の基板電極は、電源電位VDDに接続される。Nチャネル型MOSトランジスタMN103のゲート電極には接続ノードN0が、ドレイン電極には接続ノードN1が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN103の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。

【0021】

インバータ回路INV104は、Pチャネル型MOSトランジスタMP104およびNチャネル型MOSトランジスタMN104より構成される。Pチャネル型MOSトランジスタMP104のゲート電極には接続ノードN1が、ドレイン電極には出力ノードO0が、ソース電極には電源電位VDDがそれぞれ接続される。またPチャネル型MOSトランジスタMP104の基板電極は、電源電位VDDに接続される。Nチャネル型MOSトランジスタMN104のゲート電極には接続ノードN1が、ドレイン電極には出力ノードO0が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN104の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。

【0022】

ラッチ回路LATCHは、CMOSインバータの入力と出力が互いに接続されて構成されるフリップ・フロップ(Pチャネル型MOSトランジスタ(MP105、MP06)、Nチャネル型トランジスタ(MN105、MN106)で構成される)で、記憶ノードN2と記憶ノードN3に情報が記憶される。

【0023】

Pチャネル型MOSトランジスタMP105のゲート電極には記憶ノードN3が、ドレイン電極には記憶ノードN2が、ソース電極には電源電位VDDがそれぞれ接続される。またPチャネル型MOSトランジスタMP105の基板電極は、電源電位VDDに接続される。

【0024】

Pチャネル型MOSトランジスタMP106のゲート電極には記憶ノードN2が、ドレイン電極には記憶ノードN3が、ソース電極には電源電位VDDがそれぞれ接続される。またPチャネル型MOSトランジスタMP106の基板電極は、電源電位VDDに接続される。

【0025】

Nチャネル型MOSトランジスタMP105のゲート電極には記憶ノードN3が、ドレイン電極には記憶ノードN2が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN105の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。Nチャネル型MOSトランジスタMP106のゲート電極には記憶ノードN2が、ドレイン電極には記憶ノードN3が、ソース電極には接地ソース電極線VSSMがそれぞれ接続される。またNチャネル型MOSトランジスタMN106の基板電極は、接地ソース電極線VSSMあるいは接地電位VSSに接続される。

【0026】

また、接地ソース電極線VSSMを接地電位VSSと接続するNチャネル型MOSトランジスタMN101および接地ソース電極線VSSMを接地電位より高い電位VSSSたとえば0.5Vに接続するNチャネル型MOSトランジスタMN100が配置される。

【0027】

次に動作状態および待機状態について図2の動作波形を用いて説明する。ここでは、電源電圧VDDを1.5V、接地電位VSSを0V、接地電位より高い電位VSSSを0.5Vとする。この電圧はデバイスの特性等により変更される。

【0028】

動作時では、Nチャネル型MOSトランジスタMN101がオンしており、VSSMは接地電位VSS、たとえば0Vとなっている。I0、N1、N3の電位が1.5V、N0、N2の電位が0Vとなっている。このときPチャネル型MOSトランジスタ(MP103、MP106)およびNチャネル型MOSトランジスタ(MN102、MN104、MN105)がオン、Pチャネル型MOSトランジスタ(MP102、MP104、MP105)およびNチャネル型MOSトランジスタ(MN103、MN106)がオフしている。

【0029】

Pチャネル型MOSトランジスタMP103のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がソース電極からゲート電極に流れる。この電流は、接続ノードN0、オン状態のNチャネル型MOSトランジスタMN102を通って接地電位VSSへ流れる。

【0030】

同様に、Nチャネル型MOSトランジスタMP104のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がゲート電極からソース電極に流れる。この電流は、接続ノードN1、オン状態のPチャネル型MOSトランジスタMP103を通って電源電位VDDから流れる。

【0031】

同様に、Pチャネル型MOSトランジスタMP106のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がソース電極からゲート電極に流れる。この電流は、接続ノードN2、オン状態のNチャネル型MOSトランジスタMN105を通って接地電位VSSへ流れる。

【0032】

同様に、Nチャネル型MOSトランジスタMN105のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がゲート電極からソース電極に流れる。この電流は、接続ノードN2、オン状態のPチャネル型MOSトランジスタMP106を通って電源電位VDDから流れる。以上のようなパスにより動作時にはゲートトンネルリーク電流が流れる。

【0033】

一方待機時には、Nチャネル型MOSトランジスタMN100がオンしており、VSSMは接地電位より高い電位VSSSたとえば0.5Vとなっている。I0、N1、N3の電位が1.5V、N0、N2の電位が0.5Vとなっている。このときPチャネル型MOSトランジスタ(MP103、MP106)およびNチャネル型MOSトランジスタ(MN102、MN104、MN105)がオン、Pチャネル型MOSトランジスタ(MP102、MP104、MP105)およびNチャネル型MOSトランジスタ(MN103、MN106)がオフしている。

【0034】

Pチャネル型MOSトランジスタMP103のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0035】

同様に、Nチャネル型MOSトランジスタMN104のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0036】

同様に、Pチャネル型MOSトランジスタMP106のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0037】

同様に、Nチャネル型MOSトランジスタMN105のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が印加されている場合に比べ、約1桁低減される。

【0038】

以上のようにゲート−ソース間に印加される電圧が下がるためゲートトンネルリーク電流が減少する。一方、保持データは破壊されない。また、オフ状態でゲート−ドレイン間に印可される電圧が下がるためGIDL電流も減少する。

【0039】

本実施例では、インバータ回路およびラッチ回路の場合について述べたが、その他の半導体集積回路たとえば、ナンド回路、ノア回路等でも同様の効果が得られる。

【0040】

〈実施例2〉

図3は、本発明に係わる半導体装置の一実施例を示す回路図である。本回路は、Pチャネル型MOSトランジスタMPおよびNチャネル型MOSトランジスタMNより構成される半導体集積回路の一部を示しており、MOSトランジスタのゲートに使用される絶縁膜が4nm以下か、トンネルリーク電流が電源電圧1.5Vで、10-12 A/μm2 以上

である半導体集積回路製造技術を用いて単結晶シリコンのような半導体基板に形成される。

【0041】

図3には半導体集積回路装置の一部として、インバータ回路INVおよびデータを保持するラッチ回路LATCHが示されている。

【0042】

インバータ回路INV112は、Pチャネル型MOSトランジスタMP112およびNチャネル型MOSトランジスタMN112より構成される。Pチャネル型MOSトランジスタMP112のゲート電極には入力信号I1が、ドレイン電極には接続ノードN4が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP112の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。Nチャネル型MOSトランジスタMN112のゲート電極には入力信号I1が、ドレイン電極には接続ノードN4が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN112の基板電極は、接地電位VSSに接続される。

【0043】

インバータ回路INV113は、Pチャネル型MOSトランジスタMP113およびNチャネル型MOSトランジスタMN113より構成される。Pチャネル型MOSトランジスタMP113のゲート電極には接続ノードN4が、ドレイン電極には接続ノードN5が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP113の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。Nチャネル型MOSトランジスタMN113のゲート電極には接続ノードN4が、ドレイン電極には接続ノードN5が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN114の基板電極は、接地電位VSSに接続される。

【0044】

インバータ回路INV114は、Pチャネル型MOSトランジスタMP114およびNチャネル型MOSトランジスタMN114より構成される。Pチャネル型MOSトランジスタMP114のゲート電極には接続ノードN5が、ドレイン電極には出力信号O1が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP114の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。Nチャネル型MOSトランジスタMN114のゲート電極には接続ノードN5が、ドレイン電極には出力信号O1が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN114の基板電極は、接地電位VSSに接続される。

【0045】

ラッチ回路LATCHは、CMOSインバータの入力と出力が互いに接続されて構成されるフリップ・フロップ(Pチャネル型MOSトランジスタ(MP115、MP116)、Nチャネル型トランジスタ(MN115、MN116)で構成される)で、記憶ノードN6と記憶ノードN7に情報が記憶される。

【0046】

Pチャネル型MOSトランジスタMP115のゲート電極には記憶ノードN7が、ドレイン電極には記憶ノードN6が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP105の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。

【0047】

Pチャネル型MOSトランジスタMP116のゲート電極には記憶ノードN6が、ドレイン電極には記憶ノードN7が、ソース電極には電源ソース電極線VDDMがそれぞれ接続される。またPチャネル型MOSトランジスタMP116の基板電極は、電源ソース電極線VDDMあるいは電源電位VDDに接続される。

【0048】

Nチャネル型MOSトランジスタMP115のゲート電極には記憶ノードN7が、ドレイン電極には記憶ノードN6が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN115の基板電極は、接地電位VSSに接続される。

【0049】

Nチャネル型MOSトランジスタMP116のゲート電極には記憶ノードN6が、ドレイン電極には記憶ノードN7が、ソース電極には接地電位VSSがそれぞれ接続される。またNチャネル型MOSトランジスタMN116の基板電極は、接地電位VSSに接続される。

【0050】

また、電源ソース電極線VDDMを電源電位VDDと接続するPチャネル型MOSトランジスタMP101および電源ソース電極線VDDMを電源電位より低い電位VDDDたとえば1.0Vに接続するPチャネル型MOSトランジスタMP100が配置される。

【0051】

次に動作状態および待機状態について図4の動作波形を用いて説明する。ここでは、電源電圧VDDを1.5V、接地電位VSSを0V、電源電位より低い電位VDDDを1.0Vとする。この電圧はデバイスの特性等により変更される。

【0052】

動作時では、Nチャネル型MOSトランジスタMP100がオンしており、VDDMは電源電位VDD、たとえば1.5Vとなっている。N4、N7の電位が1.5V、I1、N5、N6の電位が0Vとなっている。このときPチャネル型MOSトランジスタ(MP112、MP114、MP116)およびNチャネル型MOSトランジスタ(MN113、MN11 5)がオン、Pチャネル型MOSトランジスタ(MP113、MP11 5)およびNチャネル型MOSトランジスタ(MN112、MP114、MN116)がオフしている。

【0053】

Nチャネル型MOSトランジスタMN113のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がゲート電極からソース電極に流れる。この電流は、接続ノードN4、オン状態のPチャネル型MOSトランジスタMP112を通って電源電位VDDから流れる。

【0054】

同様に、Pチャネル型MOSトランジスタMP114のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がソース電極からゲート電極に流れる。この電流は、接続ノードN5、オン状態のNチャネル型MOSトランジスタMN113を通って接地電位VSSへ流れる。

【0055】

同様に、Pチャネル型MOSトランジスタMP116のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がソース電極からゲート電極に流れる。この電流は、接続ノードN6、オン状態のNチャネル型MOSトランジスタMN115を通って接地電位VSSへ流れる。

【0056】

同様に、Nチャネル型MOSトランジスタMN115のゲート−ソース電極間には1.5Vが印加されゲートトンネルリーク電流がゲート電極からソース電極に流れる。この電流は、接続ノードN6、オン状態のPチャネル型MOSトランジスタMP116を通って電源電位VDDから流れる。以上のようなパスにより動作時にはゲートトンネルリーク電流が流れる。

【0057】

一方待機時には、Pチャネル型MOSトランジスタMP101がオンしており、VDDMは電源電位より低い電位VVDDたとえば1.0Vとなっている。N4、N7の電位が1.0V、I1、N5、N6の電位が0Vとなっている。このときPチャネル型MOSトランジスタ(MP112、MP114、MP116)およびNチャネル型MOSトランジスタ(MN113、MN115)がオン、Pチャネル型MOSトランジスタ(MP113、MP115)およびNチャネル型MOSトランジスタ(MN112、MN114、MN116)がオフしている。

【0058】

Nチャネル型MOSトランジスタMN113のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0059】

同様に、Pチャネル型MOSトランジスタMP114のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0060】

同様に、Pチャネル型MOSトランジスタMP116のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0061】

同様に、Nチャネル型MOSトランジスタMN115のゲート−ソース電極間には1.0Vが印加されゲートトンネルリーク電流が1.5Vの電位差が引加されている場合に比べ、約1桁低減される。

【0062】

以上のようにゲート−ソース間に印加される電圧が下がるためゲートトンネルリーク電流が減少する。一方、保持データは破壊されない。また、オフ状態でゲート−ドレイン間に印可される電圧が下がるためGIDL電流も減少する。

【0063】

本実施例では、インバータ回路およびラッチ回路の場合について述べたが、その他の半導体集積回路たとえば、ナンド回路、ノア回路等でも同様の効果が得られる

【0064】

〈実施例3〉

図15は、本発明をSRAMに適用した場合の一実施例を示す回路図である。本半導体製造装置98は、Pチャネル型MOSトランジスタおよびNチャネル型MOSトランジスタより構成され、MOSトランジスタのゲートに使用される絶縁膜が4nm 以下か、トンネルリーク電流が電源電圧1.5Vで、10-12 A/μm2 以上である半導体集積回路製

造技術を用いて単結晶シリコンのような半導体基板に形成される。

【0065】

半導体装置であるSRAM98は、複数のマットMEMBLKに分割されている。マットの詳細は図5に示した。マット単位は例えば2M ビット毎で、16M のSRAMでは8マットに分割される。降圧回路PWRは、外部パッドより印加される電源電位VCCを基に、内部電源(VDD、VSSS、VDDD)を生成し各マットへ分配する。インプットバッファINBUFからのデータ116は、プリデコーダ115および制御回路117を通してデコード信号および制御信号となり、各マットに分配される。各マット108は、複数の基本ユニット106より構成される。基本ユニットは2カラムのメモリCELLで構成される。

【0066】

CELL0は、1対のCMOSインバータの入力と出力が互いに接続されて構成されるフリップ・フロップ(負荷型Pチャネル型MOSトランジスタ(MP00、MP01)、駆動型Nチャネル型トランジスタ(MN00、MN01)で構成される)と、前記フリップ・フロップの記憶ノードNL0と記憶ノードNR0とをデータ線(DT0、DB0)に選択的に接続する転送型Nチャネル型MOSトランジスタ(MN02、MN03)とで構成される。Nチャネル型MOSトランジスタ(MN02、MN03)のゲート電極には、サブワード線SWL0が接続される。

【0067】

メモリセルCELL1は、1対のCMOSインバータの入力と出力が互いに接続されて構成されるフリップ・フロップ(Pチャネル型MOSトランジスタ(MP10、MP11)、Nチャネル型トランジスタ(MN10、MN11)で構成される)と、前記フリップ・フロップの記憶ノードNL1と記憶ノードNR1とをデータ線(DT1、DB1)に選択的に接続するNチャネル型MOSトランジスタ(MN12、MN13)とで構成される。Nチャネル型MOSトランジスタ(MN12、MN13)のゲート電極には、サブワード線SWL0が接続される。

【0068】

また、基本ユニットには、センスアンプ回路(103)とリードデータドライブ回路(104)とライトアンプ回路(105)とイコライズ・プリチャージ回路(99、100)およびYスイッチ回路(101、102)が含まれている。センスアンプ回路(103)は、Pチャネル型MOSトランジスタ(MP20、MP21)とNチャネル型MOSトランジスタ(MN20、MN21)からなるフリップ・フロップとセンスアンプを活性にするNチャネル型MOSトランジスタMN22からなるラッチ型センスアンプ回路とスイッチ回路(MP22、MP23)から構成される。MOSトランジスタ(MN22、MP22、MP23)のゲート電極には、活性化信号SAが接続されている。

【0069】

Yスイッチ回路101はデータ線(DT0、DB0)とセンスアンプ回路103をつなぐPチャネル型MOSトランジスタ(MP05、MP06)とNチャネル型MOSトランジスタ(MN04、MN05)からなる。

【0070】

Yスイッチ回路102はデータ線(DT1、DB1)とセンスアンプ回路103をつなぐPチャネル型MOSトランジスタ(MP15、MP16)とNチャネル型MOSトランジスタ(MN14、MN15)からなる。

【0071】

制御信号(YSW、YSWB)は、センスアンプ回路103をデータ線(DT0、DB0)に接続するかデータ線(DT1、DB1)に接続するか選択する信号である。

【0072】

ライトアンプ回路105は、2つのクロックドインバータ(CINV2、CINV3)およびインバータINV0より構成される。制御信号(WBC、WBCB)によってデータバス111の信号がデータ線に伝播される。

【0073】

リードデータドライブ回路104は、2つのクロックドインバータ(CINV2、CINV3)より構成される。制御信号(RBC、RBCB)によってデータバス111に読み出しデータが伝播される。

【0074】

イコライズ・プリチャージ回路99は、電源電位VDDとデータ線DT0をつなぐPチャネル型MOSトランジスタMP02と電源電位VDDとデータ線DB0をつなぐPチャネル型MOSトランジスタMP03およびデータ線DT0とデータ線DB0をつなぐPチャネル型MOSトランジスタMP04より構成される。

【0075】

Pチャネル型MOSトランジスタ(MP02、MP03、MP04)のゲート電極には制御信号EQが接続される。

【0076】

イコライズ・プリチャージ回路99は、電源電位VDDとデータ線DT0をつなぐPチャネル型MOSトランジスタMP02と電源電位VDDとデータ線DB0をつなぐPチャネル型MOSトランジスタMP03およびデータ線DT0とデータ線DB0をつなぐPチャネル型MOSトランジスタMP04より構成される。Pチャネル型MOSトランジスタ(MP02、MP03、MP04)のゲート電極には制御信号EQが接続される。

【0077】

イコライズ・プリチャージ回路100は、電源電位VDDとデータ線DT1をつなぐPチャネル型MOSトランジスタMP12と電源電位VDDとデータ線DB1をつなぐPチャネル型MOSトランジスタMP13およびデータ線DT1とデータ線DB1をつなぐPチャネル型MOSトランジスタMP14より構成される。Pチャネル型MOSトランジスタ(MP12、MP13、MP14)のゲート電極には制御信号EQが接続される。

【0078】

各カラムには待機時にデータ線(DT、DB)に電源電圧より低い電圧、たとえば1.0Vを供給するためのスイッチ回路(109、110)が配置される。スイッチ回路109は、電源電圧より低い電圧VDDDとデータ線DT0を接続するPチャネル型MOSトランジスタMP07と電源電圧より低い電圧VDDDとデータ線DB0を接続するPチャネル型MOSトランジスタMP08より構成される。Pチャネル型MOSトランジスタ(MP07、MP08)のゲート電極には制御信号CVDDDが接続される。

【0079】

スイッチ回路110は、電源電圧より低い電圧VDDDとデータ線DT1を接続するPチャネル型MOSトランジスタMP17と電源電圧より低い電圧VDDDとデータ線DB1を接続するPチャネル型MOSトランジスタMP18より構成される。Pチャネル型MOSトランジスタ(MP17、MP18)のゲート電極には制御信号CVDDDが接続される。

【0080】

メモリマット108内の全てのメモリセル接地ソース電極線VSSMは、金属層によって接続されており、Nチャネル型MOSトランジスタ(MN6、MN7)によって電源に接続される。Nチャネル型MOSトランジスタMN6は接地電位VSSより高い電圧を供給する電源VSSSと接地ソース電極線VSSMを接続するトランジスタであり、ゲート電極には制御信号STVSSMが接続されている。Nチャネル型MOSトランジスタMN7は接地電位VSSと接地ソース電極線VSSMを接続するトランジスタであり、ゲート電極には制御信号ACVSSMが接続されている。

【0081】

制御信号STVSSMは、チップ選択信号CSおよびマット選択信号MATを使ってアンド回路AND0およびインバータ回路INV1によって生成される。制御信号ACVSSMは、チップ選択信号CSおよびマット選択信号MATを使ってアンド回路AND0によって生成される。

【0082】

制御信号CVDDDは、チップ選択信号CSおよびマット選択信号MATを使ってアンド回路AND0によって生成される。

【0083】

サブワード線SWLは入力されたアドレスおよび制御信号116をプリデコーダ115でプリデコードし、ワードデコーダおよびワードドライバ114により生成される。

【0084】

制御信号EQは、チップ選択信号CS、マット選択信号MATおよびリセットパルスATDを使ってナンド回路NAND0によって生成される。

【0085】

制御信号(YSWB、YSW)は、YアドレスAYを使って、インバータ回路INV2によって生成される。

【0086】

制御信号SAは、チップ選択信号CS、マット選択信号MAT、書き込み選択信号WEおよびFSENを使ってアンド回路AND2およびインバータ回路(INV3、INV4)によって生成される。FSENはATDより生成されるタイミングパルスである。

【0087】

制御信号(RBC、RBCB)は、制御信号SAを使ってインバータ回路INV5によって生成される。

【0088】

制御信号(WBC、WBCB)は、チップ選択信号CS、マット選択信号MATおよび書き込み選択信号WEを使ってアンド回路AND3およびインバータ回路INV6によって生成される。

【0089】

制御信号(CS、WE、YA、MAT、ATD)は、入力されたアドレスおよび制御信号よりコントロール回路117を用いて生成される。マット選択信号MATは、図15に示したように、別のコントロール回路118を用いて、速いマット選択信号FMATが用意される場合もある。ワード線の選択は誤動作防止のためプロセスばらつき・タイミングを十分に考慮するのに対し、メモリセルに対し読み出し・書き込みをするために駆動される回路( 動作電位を選択状態に制御する回路、イコライズ・プリチャージ回路等) はワード線の選択よりも早ければ、タイミングの制御精度は落としてもよい。

【0090】

そこで、ワード線を選択するもととなるコントロール回路117には高いしきい値のMOSFET( Pチャネル型とNチャネル型いずれも含む) を用い、メモリセルに対し読み出し・書き込みをするために駆動される回路を活性化する信号を出力するコントロール回路118には前記高いしきい値及び低いしきい値の2種類のしきい値のMOSFET( Pチャネル型とNチャネル型いずれも含む) を用いる。しきい値の低いMOSFETを含めると、プロセスばらつきに対して弱くなり、出力タイミングの精度をとることが難しくなるが、(コントロール回路117よりコントロール回路118は早くマット選択信号を出力することができる。同じ回路構成を用いて設計を簡易にすることもできる。ワード線を選択するもととなるコントロール回路よりも低いしきい値のMOSFETを含めてしきい値の種類を増やしてメモリセルに対し読み出し・書き込みをするために駆動される回路を制御する回路を構成する。これにより、ワード線を選択するもととなるマット選択信号MATのタイミングの精度を上げるとともに、メモリセルに対し読み出し・書き込みをするために駆動される回路を選択するもととなるマット選択信号FMATのタイミングをマット選択信号MATよりも早く確実に出力させることができる。

【0091】

本構成は非同期式で選択タイミングの精度が厳しいメモリ装置の設計に特に有効である。速いマット選択信号FMATは、例えばメモリセル接地ソース電極線VSSMを制御する回路のアンド回路AND0、VDDD供給を制御する回路のアンド回路AND1、イコライズ・プリチャージを制御する回路のナンド回路NAND0に、マット信号MATの代わりに使用される。

【0092】

次に待機状態から読み出し動作を行う場合について図6の動作波形を用いて説明する。チップ選択信号CSが“L”(“LOW”レベル)のときあるいはマットが選択されてない時には、メモリマットは待機状態となる。このときメモリセル接地ソース電極線VSSMには接地電位より高い電圧VSSSたとえば0.5Vが供給される。またデータ線(DT、DB)には、電源電圧VDDより低い電圧VDDDたとえば1.0Vが供給される。このときメモリセルCELL0の蓄積ノードNL0は、0.5Vに、NR0は電源電位VDDたとえば1.5Vとなる。オン状態であるPチャネル型MOSトランジスタMP01のゲート−ソース電極間には電源電圧1.5Vより低い1.0Vの電圧が印加され、ゲートトンネルリーク電流が低減される。またオン状態であるNチャネル型MOSトランジスタMN00のゲート−ソース電極間には電源電圧1.5Vより低い1.0Vの電圧が印加され、ゲートトンネルリーク電流が低減される。また、オフ状態のトランスファーNチャネル型MOSトランジスタ(MN02、MN03)のゲート−ソース電極間には電源電圧1.5Vより低い1.0Vの電圧が印加され、GIDL電流が低減される。

【0093】

チップ選択信号CSが“H”になるかアドレスが変わると、ATDパルスが生成され読み出し動作が開始される。マット選択信号MATとチップ選択信号CSにより、選択されたマット108のメモリセル接地ソース電極線VSSMが接地電位0Vとなる。また、データ線(DT、DB)に電圧VDDDを供給していたPチャネル型MOSトランジスタ(MP07、MP08、MP17、MP18)がオフする。

【0094】

ATDパルスから生成された制御信号EQによりデータ線(DT、DB)が、電源電圧VDDにプリチャージされる。

【0095】

この結果メモリセルCELL0の蓄積ノードNL0は、0Vに、NR0は電源電位VDDたとえば1.5Vとなる。オン状態であるPチャネル型MOSトランジスタMP01のゲート−ソース電極間には電源電圧1.5Vが印加され、ゲートトンネルリーク電流が増大する。またオン状態であるNチャネル型MOSトランジスタMN00のゲート−ソース電極間には電源電圧1.5Vが印加され、ゲートトンネルリーク電流が増大する。また、オフ状態のトランスファーNチャネル型MOSトランジスタ(MN02、MN03)のゲート−ソース電極間には電源電圧1.5Vが印加され、GIDL電流が増加する。

【0096】

その後ワード線SWL0が選択され、データ線(DT、DB)に微小電位差が生じ、制御信号SAでセンスアンプ103を活性化することにより微小電位差を増幅してデータをデータバス111に出力する。

【0097】

次に待機状態から書き込み動作を行う場合について図7の動作波形を用いて説明する。待機状態は読み出し動作の時と同様である。

【0098】

チップ選択信号CSが“H”になるかアドレスが変わると、ATDパルスが生成され書き込み動作が開始される。マット選択信号MATとチップ選択信号CSにより、選択されたマット108のメモリセル接地ソース電極線VSSMが接地電位0Vとなる。また、データ線(DT、DB)に電圧VDDDを供給していたPチャネル型MOSトランジスタ(MP07、MP08、MP17、MP18)がオフする。

【0099】

ATDパルスから生成された制御信号EQによりデータ線(DT、DB)が、電源電圧VDDにプリチャージされる。

【0100】

この結果メモリセルCELL0の蓄積ノードNL0は、0Vに、NR0は電源電位VDDたとえば1.5Vとなる。オン状態であるPチャネル型MOSトランジスタMP01のゲート−ソース電極間には電源電圧1.5Vが印加され、ゲートトンネルリーク電流が増大する。またオン状態であるNチャネル型MOSトランジスタMN00のゲート−ソース電極間には電源電圧1.5Vが印加され、ゲートトンネルリーク電流が増大する。また、オフ状態のトランスファーNチャネル型MOSトランジスタ(MN02、MN03)のゲート−ソース電極間には電源電圧1.5Vが印加され、GIDL電流が増加する。

【0101】

その後ワード線SWL0が選択される。データ線(DT、DB)には、データバス111の信号が入力され、この信号によりメモリセルCELLにデータが書き込まれる。

【0102】

本実施例ではメモリセルのソース電圧を待機時に0.5Vに上げたが、メモリセルの電源を1.0Vに下げてもいい。ただし、待機状態から動作状態に変わるときは、動作状態から待機状態に変わるときより高速に移行することが要求される。このため、待機時にソース電圧を0.5Vに上げるほうが、メモリセルの電源を1.0Vにさげるより、電源回路の負担が小さくなるため、ソースを0.5Vに上げるほうが有利である。また、図13の特性を見ても分るとおり、同じ0.5Vであっても、低電位側のソース電圧を高くすることが電流を下げる上で有利であるといえる。

【0103】

図14に待機時と動作時の1SRAMセルのリーク電流を示した。GIDL電流、サブスレッショルドリーク電流、GIDL全てが待機時で小さくなっている。

【0104】

図16に降圧回路PWRの特性の一例を示す。ビット線等に供給する電位VDDD及び、メモリセルに供給する動作電位( 高電位VDD、低電位VSSS) を生成するに際し、外部パッドより供給される電位VCCがある所定値以上となるときに外部パッドより供給される電位を制御して出力する構成をとっている。例えば、外部パッドより供給される電位VCCが1.5V以下では、メモリセルに供給する高電位VDDは、外部パッドより供給される電源電位VCCと同一であり、VCCが1.5V以上では、VDDは1.5Vで一定となるように制御する。また、電源電位より低い電位VDDDは、VCCが1.0V以下では、外部パッドより供給される電位VCCと同一であり、VCCが1.0V以上では、1.0Vで一定となるように制御する。接地電位より高い電位VSSSは、電位VCCが1.0V以下の時は0Vであり、外部電源パッドより供給される電位VCCが1.0V以上の時は、メモリセルに供給する高電位側の電位VDDに基づいてそれよりより1.0V低い値になるように制御される。これにより、半導体チップの外より入力される電源電位VCCが変動してもメモリセルに印加される電圧が常に1.0Vとなりデータ破壊が生じないようにすることが可能となる。尚、別の外部パッドから供給される低電位側の電位VSSは接地電位であることから変動しないものと考えることができる。帰還回路により制御が可能となる動作電位生成回路の適用は、メモリを具備する半導体集積回路に限られず、前の実施例においても有効である。

【0105】

本実施例においては、GIDL電流の低減のために半導体装置において、ソース・ドレイン領域のうち、コンタクトをとる領域に砒素を、エクステンション領域に燐を用いたNチャネル型MOSトランジスタを具備させる。SRAMを有する半導体装置において、前記Nチャネル型MOSトランジスタをSRAMのメモリセル内のNチャネル型MOSトランジスタに用い、メモリセルを制御する周辺回路のNチャネル型MOSトランジスタにはコンタクトをとる領域とエクステンション領域いずれにも砒素を用いたNチャネル型MOSトランジスタを用いる。

【0106】

図26において、Nチャネル型MOSトランジスタのソース・ドレイン領域のうち、コンタクトをとる領域に砒素をいずれにも用い、エクステンション領域に砒素を用いたときのゲート電圧Vgsとソース・ドレイン間の電流の特性Idsを( a) に、燐を用いたときのゲート電圧Vgsとソース・ドレイン間の電流Idsの特性を( b) に示す。座標は( a) ( b) で同じである。この波形を見て明らかなように、ゲート電圧が0.0Vにおけるオフ電流は燐を用いた方( b) が明らかに低下しており、さらに今回の発明の方式( スタンバイ時にメモリセルの動作電位Vssmを0.0Vから0.5Vにあげる方式) とした場合に燐をエクステンション領域に用いることがオフ電流を低減するに対し有効であることがわかる。ここには示していないが、高温動作領域での効果が顕著であることがわかっている。

【0107】

As(砒素)よりP (リン)は、Vth −Lowering特性などのデバイス特性への変動が大きく、電流駆動力はAsより低下するため、イオン打込み濃度やエネルギーの調整が難しいため、一般にはコンタクトを取る領域及びエクステンション領域には砒素が用いられていた。特開平9-135029号においてはコンタクトを取る領域及びエクステンション領域いずれにも燐をデバイス構造が開示されているが、本発明者らによりGIDL電流低減にはエクステンション領域に燐を注入することが有効であり、コンタクトを取る領域にはデバイスの性能面( 電流駆動力、短チャネル特性) から砒素を用いることが有効であることが示された。

【0108】

本効果が得られる理由は、ゲート電極下にオーバーラップしているエクステンション領域での燐注入により、ゲート電極からの縦方向電界によるバンド曲がりが緩和されるためである。また、インプラプロファイルのブロード化により、チャネル領域とエクテンション領域との縦方向の接合電界強度が緩和され、PN接合リークが低減した効果も寄与している。

【0109】

図17〜図25は、本実施例の半導体装置の製造方法の一例を工程順に示した断面図である。それぞれの図はメモリセル部MCを構成するNチャネル型MOSトランジスタQmnとPチャネル型MOSトランジスタQmpと、周辺回路部PERIを構成するNチャネル型MOSトランジスタQpnとPチャネル型MOSトランジスタQppと、高耐圧部HVを構成するNチャネル型MOSトランジスタQhnとPチャネル型MOSトランジスタQhpとに分けて記載している。メモリセル部MCを構成するNチャネル型MOSトランジスタQmnは図5の各メモリセルCELLの駆動と転送MOSトランジスタに用いられる。メモリセル部MCを構成するPチャネル型MOSトランジスタQmpは図5の各メモリセルCELLの負荷MOSトランジスタに用いられる。周辺回路部PERIを構成するNチャネル型MOSトランジスタQpnとPチャネル型MOSトランジスタQppは図5のメモリセル部以外のPとNチャネル型MOSトランジスタに用いられる。つまり、センスアンプ回路(103)、リードデータドライブ回路(104)、ライトアンプ回路(105)、イコライズ・プリチャージ回路(99、100)とYスイッチ回路(101、102)、ワードデコーダおよびワードドライバ( 114) 、プリデコーダ( 115) 、制御回路(117)に用いられるMOSトランジスタを含む。高耐圧部HVを構成するNチャネル型MOSトランジスタQhnとPチャネル型MOSトランジスタQhpは入力と出力の動作電圧が異なる回路、つまり図15の入力バッファ( INBUF)、降圧回路( PWR) 、入出力回路IOを構成するNとPチャネル型MOSトランジスタに用いられる。

【0110】

以下、図面を用いて工程順に説明する。まず、図17( a) に示すように、たとえばp- 型の単結晶シリコンからなる半導体基板200を用意し、半導体基板200の主面に素子分離領域201を形成する。素子分離領域201は、たとえば以下のようにして形成できる。まず、半導体基板200の主面上にシリコン酸化膜(SiO2 )およびシリコン窒化膜(Si3 N4 )を順次形成し、このシリコン窒化膜をパターニングされたフォトレジスト膜を用いてエッチングし、このエッチングされたシリコン窒化膜をマスクとして半導体基板200に溝型の分離領域を形成する。その後、溝型の分離領域を埋め込む絶縁膜、たとえばシリコン酸化膜を堆積し、CMP法等を用いて溝型分離領域以外の領域のシリコン酸化膜を除去し、さらにウエットエッチング法等によりシリコン窒化膜を除去する。これにより素子分離領域(トレンチアイソレーション)201が形成される。素子分離領域は、溝型の分離領域に限定されるものではなく、例えばLOCOS(Local Oxidization of Silicon)法によって形成されたフィールド絶縁膜で形成しても良い。次のイオン注入工程による半導体基板表面のダメージを緩和するために、薄いシリコン酸化膜を堆積させる。

【0111】

その後パターニングされたフォトレジスト膜をマスクとして不純物をイオン注入し、図17( b) に示すように、pウエル210、212およびnウエル211、213を形成する。pウエルにはp型の導電型を示す不純物たとえばボロンB又はフッ化ボロンBF2をイオン注入し、nウエルにはn型の導電型を示す不純物たとえばリンP、砒素Asをイオン注入する。この後、各ウエル領域にMOSFETのしきい値を制御するための不純物( Nチャネル型MOSトランジスタではn型の導電型を示す不純物( P) 、Pチャネル型MOSトランジスタではp型の導電型を示す不純物( BF2))をイオン注入する。

【0112】

次に図17( b) に示すように、ゲート絶縁膜となるシリコン酸化膜221を形成する。この際に、高耐圧部には厚膜ゲート酸化膜、周辺回路部とメモリセル部には薄膜ゲート酸化膜をホトリソグラフィー、エッチング技術を用いて形成した。

【0113】

本実施例では、厚膜ゲート酸化膜の膜厚は外部入出力で3.3V に対応するため8.0nm、薄膜ゲート酸化膜は待機時におけるゲートリーク電流が問題となる3.0nmとした。高耐圧部以外の酸化膜をホトリソグラフィー・ウエットエッチング技術により除去した後に、再度、熱酸化して熱酸化することにより2種類の膜厚の酸化膜が形成される。その後、ゲート電極用の多結晶シリコン膜222を堆積し、レジストマスク223を用いてNとPチャネル型MOSの電極領域にそれぞれn型/p型の不純物( 燐、ボロン) をイオン注入する。

【0114】

図18( a) に示すように、ホトリソグラフィー・ドライエッチングを用いて加工することによりゲート電極230、231、232、233、234、235が形成される。次に図18( b) に示すようにエクステンション領域となる半導体領域及びそれとパンチスルーを抑制するための反対の導電型( ウエルと同導電型でウエル領域よりも高濃度)の半導体領域をイオン注入法で形成する。N チャネル型MOS トランジスタにおいてはメモリセル部MCと周辺回路部PERIと高耐圧部HVとでそれぞれマスク( 工程) を変えてイオン注入を行う。メモリセル部MCにおいてはスタンバイ時のGIDL電流を低減するためにn型の不純物である燐、p型の不純物( ボロン) を注入することによりn型半導体領域241、242とp型半導体領域243、244を形成する。その際には他の領域(Pチャネル型MOS トランジスタ領域、周辺回路部・高耐圧部領域) はレジストでマスクされる。周辺回路部PERIにおいては高速動作を実現するためにn型の不純物である砒素、p型の不純物( ボロン) を注入することによりn型半導体領域245、246とp型半導体領域247、248を形成する。その際には他の領域(Pチャネル型MOS トランジスタ領域、メモリセル部・高耐圧部領域) はレジストでマスクされる。

【0115】

次に図18( c) で示すように、Pチャネル型MOSトランジスタとなるn型ウエル領域211にはp型の不純物( ボロン) 、n型の不純物( As) を注入することにより、エクステンション領域となる半導体領域251、254、255、256、パンチスルーを抑制するための、ウエルと同導電型でウエル領域よりも高濃度の半導体領域253、254、257、258を形成する。Pチャネル型MOSトランジスタはメモリセル部MC、周辺回路部PERIで不純物の種類・イオン注入の条件( エネルギー) を変えないため、同じマスク( 工程) で行い、イオンを注入する際にはN チャネル型MOS トランジスタとなる領域及び高耐圧部HVのPチャネル型MOS トランジスタとなる領域はレジストでマスクする。高耐圧部のN チャネル型MOS トランジスタはエッジ端の縦方向電界を緩和するようにn型の不純物である砒素及び燐、p型の不純物( ボロン) を注入することによりn型半導体領域259、260、261、262とp型半導体領域263、264を形成する。分布係数の違いにより半導体表面に近いn型半導体領域259、260は砒素により主に構成され、より深く注入されるn型半導体領域261、262は燐が主成分となる。

【0116】

次に図19( a) に示すように、高耐圧部HVのPチャネル型MOSトランジスタとなるn型ウエル領域213にはp型の不純物( ボロン) 、n型の不純物( As) を注入することにより、エクステンション領域となるp型半導体領域266、パンチスルーを抑制するための、ウエルと同導電型でウエル領域よりも高濃度の半導体領域267を形成する。本実施例では、高耐圧部HVとメモリセル部MC、周辺回路部PERIでマスク( 工程、イオン打ち込み条件) を変えたが、耐圧が製品の特性を満たすことが可能であれば、Pチャネル型MOSトランジスタをメモリセル部MC、周辺回路部PERI、高耐圧部HVで不純物の種類・イオン注入の条件( エネルギー) を変えずに一つのマスク( 工程) で行うことが可能となる。

【0117】

尚、エクステンション領域及びウエルと反導電型で高濃度の半導体領域のイオン注入の順序は問わない。つまり、N チャネル型MOS トランジスタ領域へのイオン注入より先にP チャネル型MOS トランジスタとなる領域のイオン注入を行ってもよく。また、図18( b)(c) によれば、N チャネル型MOS トランジスタの内、メモリセル部、周辺回路部、高耐圧部の順にイオン注入を行っているが、順番は問わない。高耐圧部のイオン注入をするに当たって不純物量によっては、メモリセル部、周辺回路部のイオン注入の際にマスクで覆わず、高耐圧部のためにマスクを用意しないことも可能ではあるが、不純物量に違いがあれば、図18( c) のように別のマスクを用意する必要がある。

【0118】

図19( a) で示すように、半導体基板200上に、たとえばCVD法でシリコン酸化膜を堆積した後、このシリコン酸化膜を異方性エッチングすることにより、ゲート電極230、231、232、233、234、235の側壁にサイドウォールスペーサ( ゲート側壁膜) 265をそれぞれ形成する。次に図19( b) に示すように、フォトレジスト膜270をマスクとして、ウエルnウエル210、212にp型不純物(ボロン)をイオン注入し、nウエル上のゲート電極231、232、235の両側にp型半導体領域271を形成する。p型半導体領域271は、ゲート電極231、232、235およびサイドウォールスペーサ265に対して自己整合的に形成され、pチャネルMISFETのソース、ドレイン領域として機能する。

【0119】

同様に、フォトレジスト膜をマスクとしてpウエル211、213にn型不純物(As)をイオン注入し、電極とコンタクトを取ることになるn型半導体領域280を形成する。n型半導体領域280は、ゲート電極230、233、234およびサイドウォールスペーサ265に対して自己整合的に形成される。また、n型半導体領域280は、nチャネルMISFETのソース、ドレイン領域として機能する。その結果、サイドウォールスペーサ265の形成前に低濃度の不純物半導体領域を形成し、サイドウォールスペーサ265の形成後に高濃度の不純物半導体領域を形成するLDD(Lightly Doped Drain )構造のトランジスタがそれぞれの領域で形成される(図19( c) )。尚、本実施例ではNチャネル型MOSトランジスタのソース・ドレイン領域を先に形成したが、Pチャネル型MOSトランジスタを先に形成してもよい。

【0120】

次に図20( a) に示すように、シリコン酸化膜をエッチングし、ソース・ドレイン半導体領域の表面を露出し、高融点金属膜( Co、Ti、W、Mo、Ta) を堆積させ、アニールし、未反応の高融点金属膜を除去することによりゲート電極230、231、232、233、234、235及びソース・ドレインを形成する半導体領域の表面の一部をシリサイド化( 290、291) させる。その後、シリコン窒化膜292を堆積させる。

【0121】

図19( b) に示すように、半導体基板200上にCVD法またはスパッタ法でシリコン酸化膜を堆積した後、そのシリコン酸化膜を、たとえばCMP法で研磨することにより、表面が平坦化された第1層間絶縁膜300を形成する。次に、フォトリソグラフィ技術を用いて第1層間絶縁膜300に接続孔を形成する。この接続孔は、n型半導体領域あるいはp型半導体領域上の必要部分に形成する。

【0122】

接続孔内にプラグを、たとえば以下のようにして形成する。まず、接続孔の内部を含む半導体基板200の全面に窒化チタン膜301を形成する。窒化チタン膜は、たとえばCVD法により形成できる。CVD法は被膜の段差被覆性に優れるため、微細な接続孔内にも均一な膜厚で窒化チタン膜を形成できる。次に、接続孔を埋め込む金属( リチウム) 膜302を形成する。金属膜は、たとえばCVD法で形成できる。次に、接続孔以外の領域の金属膜および窒化チタン膜を、たとえばCMP法により除去してプラグを形成できる。

【0123】

このようなシリサイド層を形成することにより、接続孔12底部でのコンタクト抵抗を低減できる。同様にして第2層間絶縁膜310に接続孔を形成する。接続孔は窒化チタン膜311と金属( タングステン) 膜312により形成される。これらのプラグはローカル配線の接続に用いられる。次に、半導体基板200の全面に、CVD法またはスパッタ法によりたとえば窒化チタン膜321とアルミニウム膜322を形成し、堆積された膜をフォトリソグラフィ技術によりパターニングし、第1配線層の配線を形成する。第1 層の配線はメモリ部ではビット線等に用いられる。配線を覆う絶縁膜、たとえばシリコン酸化膜を形成し、この絶縁膜をCMP法により平坦化して第2層間絶縁膜330を形成する。第2層間絶縁膜330上に接続孔が形成される領域に開孔を有するフォトレジスト膜を形成し、このフォトレジスト膜をマスクとしてエッチングを施す。これにより第2層間絶縁膜330の所定の領域に接続孔を形成する。接続孔内にプラグを形成する。

【0124】

プラグは以下のようにして形成できる。まず、接続孔の内部を含む半導体基板200の全面にバリアメタル層340 を形成し、さらに接続孔を埋め込む金属( タングステン) 膜341を形成する。その後、接続孔以外の領域の金属膜およびバリアメタル層をCMP法により除去してプラグを形成する。バリアメタル層は第2層間絶縁膜330 等周辺へのタングステンの拡散を防止する機能を有し、たとえば窒化チタン膜を例示できる。なお、窒化チタン膜には限られず、タングステンの拡散防止機能を有する限り他の金属膜であってもよい。たとえば、窒化チタンに代えてタンタル(Ta)、窒化タンタル(TaN)を用いることもできる。第1 配線層と同様に、第2配線層の配線( 351、352) を形成する。配線を覆う絶縁膜を形成し、この絶縁膜をCMP法により平坦化して第3層間絶縁膜360を形成する。第3層間絶縁膜360上に第2 層間絶縁膜330で設けたと同様に接続孔を形成し、接続孔内にプラグ( 361、362) を形成する。第2配線層と同様に、第3配線層の配線( 363、364) を形成する。配線を覆う絶縁膜370を形成し、この絶縁膜の上に窒化シリコン膜をパッシベーション膜371として形成する。製品として出荷する前には検査工程、樹脂封止工程等がある。

【0125】

砒素をエクステンション領域とコンタクトをとる領域に注入した場合と燐をエクステンション領域に適用した本デバイス構造を用いたメモリセルを試作した結果、スタンバイ電流は25℃、90℃において約50%低減できることがわかった。つまり、通常動作の温度だけでなく、高温においても半導体装置のスタンバイ電流を抑制することができ、本構造をとることにより製品の動作保証温度( 例えば70度C以下) を高く設定することができるという効果を有する。

【0126】

薄膜NMOSに本デバイス構造を採る事により、半導体装置のスタンバイ電流が従来As構造での2.5uAから1.0uA程度と低減することができる。この効果は、スタンバイ電流の主成分がNMOSのGIDL電流(約70% 程度)であることに起因する。

【0127】

尚、メモリセル部のNチャネル型MOSトランジスタのエクステンション領域には燐のみを用いたが、高速動作のために燐及び砒素を注入することもある。この場合には、イオン源が2種類必要となるが駆動電流が増えるという効果がでる。構造は高耐圧部のNチャネル型MOSトランジスタと類似する。高耐圧MOSよりも低いエネルギーでイオン注入を行う必要があるため、高耐圧部のエクステンション領域のイオン打ちこみをするときとマスクを変える必要があり、その結果半導体領域の広がりは高耐圧部のそのものより狭くなる。

【0128】

〈実施例4〉

図8は、本発明をマイクロプロセッサに適用した実施例を示している。MOSトランジスタのゲートに使用される絶縁膜が4nm 以下か、トンネルリーク電流が電源電圧1.5Vで、10-12 A/μm2 以上である半導体集積回路製造技術を用いて単結晶シリコンの

ような半導体基板に形成される。

【0129】

マイクロプロセッサ130は、IP回路133、キャッシュメモリ131およびCPU132より構成されている。また、動作および待機状態をコントロールするコントロール回路134もマイクロプロセッサ130に搭載されている。

【0130】

キャッシュメモリ131の接地ソース電極線VSSMは、Nチャネル型MOSトランジスタMN200を介して接地電位より高い電位VSSSに接続され、またNチャネル型MOSトランジスタMN201を介して接地電位VSSに接続されている。Nチャネル型MOSトランジスタMN200のゲート電極には制御信号STBY0が接続されている。Nチャネル型MOSトランジスタMN201のゲート電極には制御信号ACTV0が接続されている。

【0131】

CPU回路132の接地ソース電極線VSSMは、Nチャネル型MOSトランジスタMN202を介して接地電位より高い電位VSSSに接続され、またNチャネル型MOSトランジスタMN203を介して接地電位VSSに接続されている。Nチャネル型MOSトランジスタMN202のゲート電極には制御信号STBY1が接続されている。Nチャネル型MOSトランジスタMN203のゲート電極には制御信号ACTV1が接続されている。

【0132】

IP回路133の接地ソース電極線VSSMは、Nチャネル型MOSトランジスタMN204を介して接地電位より高い電位VSSSに接続され、またNチャネル型MOSトランジスタMN205を介して接地電位VSSに接続されている。Nチャネル型MOSトランジスタMN204のゲート電極には制御信号STBY2が接続されている。Nチャネル型MOSトランジスタMN205のゲート電極には制御信号ACTV2が接続されている。

【0133】

制御信号STBY0が“H”、ACTV0が“L”となると、キャッシュメモリ131は、待機状態となり、VSSMの電位が接地電位より高い電圧VSSSたとえば0.5Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。ただし、キャッシュメモリ内のデータは破壊されず保持される。

【0134】

制御信号STBY0が“L”、ACTV0が“H”となると、キャッシュメモリ131は、動作状態となり、VSSMの電位が接地電位VSSとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0135】

制御信号STBY1が“H”、ACTV1が“L”となると、CPU回路132は、待機状態となり、VSSMの電位が接地電位より高い電圧VSSSたとえば0.5Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。ただし、レジスターファイルおよびラッチ内のデータは破壊されず保持される。

【0136】

制御信号STBY1が“L”、ACTV1が“H”となると、CPU回路132は、動作状態となり、VSSMの電位が接地電位VSSとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0137】

制御信号STBY2が“H”、ACTV2が“L”となると、IP138は、待機状態となり、VSSMの電位が接地電位より高い電圧VSSSたとえば0.5Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。

【0138】

制御信号STBY2が“L”、ACTV2が“H”となると、IP138は、動作状態となり、VSSMの電位が接地電位VSSとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0139】

〈実施例5〉

図9は、本発明をマイクロプロセッサに適用した実施例を示している。MOSトランジスタのゲートに使用される絶縁膜が4nm 以下か、トンネルリーク電流が電源電圧1.5Vで、10-12 A/μm2 以上である半導体集積回路製造技術を用いて単結晶シリコンの

ような半導体基板に形成される。

【0140】

マイクロプロセッサ135は、IP回路138、キャッシュメモリ136およびCPU137より構成されている。また、動作および待機状態をコントロールするコントロール回路139もマイクロプロセッサ135に搭載されている。

【0141】

キャッシュメモリ136の電源ソース電極線VDDMは、Pチャネル型MOSトランジスタMP200を介して電源電位より低い電位VDDDに接続され、またPチャネル型MOSトランジスタMP201を介して電源電位VDDに接続されている。Pチャネル型MOSトランジスタMP200のゲート電極には制御信号STBYB0が接続されている。Pチャネル型MOSトランジスタMP201のゲート電極には制御信号ACTVB0が接続されている。

【0142】

CPU回路137の電源ソース電極線VDDMは、Pチャネル型MOSトランジスタMP202を介して電源電位より低い電位VDDDに接続され、またPチャネル型MOSトランジスタMP203を介して電源電位VDDに接続されている。Pチャネル型MOSトランジスタMP202のゲート電極には制御信号STBYB1が接続されている。Pチャネル型MOSトランジスタMP203のゲート電極には制御信号ACTVB1が接続されている。

【0143】

IP回路138の電源ソース電極線VDDMは、Pチャネル型MOSトランジスタMP204を介して電源電位より低い電位VDDDに接続され、またPチャネル型MOSトランジスタMP205を介して電源電位VDDに接続されている。Pチャネル型MOSトランジスタMP204のゲート電極には制御信号STBYB2が接続されている。Pチャネル型MOSトランジスタMP205のゲート電極には制御信号ACTVB2が接続されている。

【0144】

制御信号STBYB0が“L”、ACTVB0が“H”となると、キャッシュメモリ136は、待機状態となり、VDDMの電位が電源電位より低い電圧VDDDたとえば1.0Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。ただし、キャッシュメモリ内のデータは破壊されず保持される。

【0145】

制御信号STBYB0が“H”、ACTVB0が“L”となると、キャッシュメモリ136は、動作状態となり、VDDMの電位が電源電位VDDとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。制御信号STBYB1が“L”、ACTVB1が“H”となると、CPU回路137は、待機状態となり、VDDMの電位が電源電位より低い電圧VDDDたとえば1.0Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。ただし、レジスタファイルおよびラッチ内のデータは破壊されず保持される。

【0146】

制御信号STBYB1が“H”、ACTVB1が“L”となると、CPU回路137は、動作状態となり、VDDMの電位が電源電位VDDとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0147】

制御信号STBYB2が“L”、ACTVB2が“H”となると、IP回路138は、待機状態となり、VDDMの電位が電源電位より低い電圧VDDDたとえば1.0Vとなる。この時MOSトランジスタのゲート−ソース間に印加される電圧が下がり、ゲートトンネルリーク電流が低減される。

【0148】

制御信号STBYB2が“H”、ACTVB2が“L”となると、IP回路138は、動作状態となり、VDDMの電位が電源電位VDDとなる。この場合MOSトランジスタのゲートトンネルリーク電流は待機時に比べ増加する。

【0149】

〈実施例6〉

図10は、本発明を使ったSRAMあるいはマイクロプロセッサを携帯電話などの電池で動作するシステムに応用した実施例を示している。携帯電話140には、電池141と実施例3で述べたSRAM、実施例4で述べたマイクロプロセッサ130が搭載されている。電池駆動するための端子とSRAMとマイクロプロセッサが単一の半導体基板に搭載されている半導体装置からなる。また接地電位より高い電圧VSSSたとえば0.5Vを電源電位VDDから生成する回路143も搭載されている。

【0150】

SRAM98はCSが“L”のときに待機状態となり接地電極が0.5Vとなりゲートトンネルリーク電流が低減される。

【0151】

マイクロプロセッサ130はSTBYが“H”でACTVが“L”のとき待機状態となり接地電極が0.5Vとなりゲートトンネルリーク電流が低減される。この結果電池の寿命を延ばすことが可能となる。

【0152】

〈実施例7〉

図11は、本発明を使ったSRAMあるいはマイクロプロセッサを携帯電話などの電池で動作するシステムに応用した実施例を示している。携帯電話144には、電池141とSRAM146、マイクロプロセッサ147が搭載されている。SRAM146とマイクロプロセッサ147の電源VDDIを供給する電源チップ145も搭載されている。

【0153】

図12に動作波形を示す。動作時にはスタンバイ信号STBYが“L”となりSRAM146とマイクロプロセッサ147に電源電位VDDが与えられる。待機時にはスタンバイ信号STBYが“H”となりSRAM146とマイクロプロセッサ147に電源電位VDDより低い電位が与えられる。このときゲートトンネルリーク電流およびGIDL電流が低減される。この結果電池の寿命を延ばすことが可能となる。

【0154】

尚、本文中のMOSトランジスタのゲート酸化膜を絶縁膜としたMISトランジスタに適用してもよい。本発明によれば、データを破壊することなくリーク電流を低減することができる。

【産業上の利用可能性】

【0155】

この発明は、半導体装置に広く利用することができる。

【符号の説明】

【0156】

CELL……SRAMメモリセル

MN……Nチャネル型MOSトランジスタ

MP……Pチャネル型MOSトランジスタ

INV ……インバータ回路

CINV ……クロックドインバータ回路

LATCH……ラッチ回路

NAND……NAND回路

AND……NAND回路

N……接続ノード

I……入力信号

O……出力信号

NL、NR……SRAMメモリセル内部ノード

VDD……電源電位

VDDD……電源電位より低い電位

VCC……外部パッドより供給される高電位側の電源電位

VDDM……電源ソース電極線

VSS……接地電位

VSSS……接地電位より高い電位

VSSM……接地ソース電極線

DT、DB……データ線

SWL……サブワード線

STBY……待機選択信号

ACTV……動作選択信号

ACVSSM……制御信号

STVSSM……制御信号

CVDDD……制御信号

EQ……イコライズ・プリチャージ回路制御信号

YSW、YSWB……Yスイッチ制御信号

SA……センスアンプ制御信号

RBC、RBCB……読み出しデータ出力制御信号

WBC、WBCB……書き込みデータ入力制御信号

CS……チップ選択信号

WE……書き込み選択信号

AY……Yアドレス

MAT……マット選択信号

ATD……ATDパルス

98、146……SRAM

99、100……イコライズ、プリチャージ回路

101、102……Yスイッチ回路

103……センスアンプ回路

104……リードデータドライブ回路

105……ライトアンプ回路

106……基本ユニット

108、MEMBLK……メモリセルマット

109、110……スイッチ回路

111……データバス

114……ワードデコーダおよびワードドライバ

115……プリデコーダ

116……アドレスおよび制御信号

117、118……制御回路

130、135、147……マイクロプロセッサ

131、136……キャッシュメモリ

132、137……CPU回路

133、138……IP回路

134、139……コントロール回路

140、144……携帯電話システム

141……電池

143、145……電源回路。

FMAT……速いマット選択信号

PWR……降圧回路

INBUF……インプットバッファ

Qmn、Qmp……メモリセル部のNとPチャネル型MISFET

Qpn、Qpp……周辺回路部のNとPチャネル型MISFET

Qhn、Qhp……高耐圧部のNとPチャネル型MISFET

200……半導体基板

201……素子分離領域

210、211、212、213……ウエル

221……絶縁膜

222……多結晶シリコン膜

223、270……レジストマスク

230、231、232、233、234、235……ゲート電極

241、242、245、246、253、254、257、258、259、

260、261、262、267、280……n型半導体領域

243、244、247、248、251、254、255、256、263、

264、266、271……p型半導体領域

265……サイドウォールスペーサ

290、291……シリサイド膜

292……シリコン窒化

300、310、330、360、370……層間絶縁膜

301、311、321……窒化チタン膜

302、312、322、341、352、364……金属膜

340、351、364……バリアメタル層

371……パッシベーション膜。

【特許請求の範囲】

【請求項1】

そのソース電極が電源線に接続される第1の負荷型Pチャネル型MOSトランジスタと、そのソース電極がソース線に接続され、そのドレイン電極が前記第1の負荷型Pチャネル型MOSトランジスタのドレイン電極に接続され、そのゲート電極が前記第1の負荷型Pチャネル型MOSトランジスタのゲート電極に接続される第1の駆動型Nチャネル型MOSトランジスタと、そのソース電極が前記電源線に接続される第2の負荷型Pチャネル型MOSトランジスタと、そのソース電極が前記ソース線に接続され、そのドレイン電極が前記第2の負荷型Pチャネル型MOSトランジスタのドレイン電極に接続されると共に前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのゲート電極に接続され、そのゲート電極が前記第2の負荷型Pチャネル型MOSトランジスタのゲート電極に接続されると共に前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのドレイン電極に接続される第2の駆動型Nチャネル型MOSトランジスタとを夫々が有する複数のスタティック型メモリセルを含む半導体集積回路装置であって、

前記電源線と前記ソース線との電位差である前記複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路とを具備し、

前記第1及び第2の負荷型Pチャネル型MOSトランジスタ及び前記第1及び第2の駆動型Nチャネル型MOSトランジスタのゲート絶縁膜厚は、4nm以下であり、

前記電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御し、前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第2の駆動型Nチャネル型MOSトランジスタがオン状態である場合に、前記第1の負荷型Pチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、前記第2の駆動型Nチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を前記動作状態に対し前記待機状態の方を小さくすることを特徴とする半導体集積回路装置。

【請求項2】

請求項1において、

前記電源線の電位は、前記動作状態及び前記待機状態において第1電位とされ、

前記ソース線の電位は、前記動作状態では第2電位とされ、前記待機状態では前記第2電位よりも高い第3電位とされるとともに、前記第1及び第2の駆動型Nチャネル型MOSトランジスタの基板電位は前記動作状態及び前記待機状態において第2電位とされる半導体集積回路装置。

【請求項3】

請求項1において、

前記ソース線の電位は、前記動作状態及び前記待機状態において第1電位とされ、

前記電源線の電位は、前記動作状態では前記第1電位より大きい第2電位とされ、

前記待機状態では前記第1電位と第2電位の間の第3電位とされるとともに、前記第1及び第2の負荷型Pチャネル型MOSトランジスタの基板電位は前記動作状態及び前記待機状態において前記第2電位とされる半導体集積回路装置。

【請求項4】

請求項1乃至3の何れか1項において、

前記動作状態では前記複数のスタティック型メモリセルに対する読み出し又は書き込み動作が行われ、

前記待機状態は前記複数のスタティック型メモリセルが選択されていないことを特徴とする半導体集積回路装置。

【請求項5】

請求項1乃至4の何れか1項において

前記半導体集積回路装置は、前記複数のスタティック型メモリセルを夫々が有する複数のメモリマットを有し、

前記動作状態と前記待機状態の切り替えは、マット選択信号に基づいていることを特徴とする半導体集積回路装置。

【請求項6】

請求項1乃至5の何れか1項において、

前記複数のスタティック型メモリセルの夫々は、データ線対の一方と前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのドレイン電極との間に設けられた第1のトランスファーNチャネル型MOSトランジスタと、前記データ線対の他方と前記第2の負荷型Pチャネル型MOSトランジスタ及び前記第2の駆動型Nチャネル型MOSトランジスタのドレイン電極との間に設けられた第2のトランスファーNチャネル型MOSトランジスタとを更に有し、

前記データ線対は、前記待機状態において、前記動作状態におけるプリチャージ電位より低い電位に設定され、

前記第1及び第2のトランスファーNチャネル型MOSトランジスタがオフ状態の際に、前記第1及び第2のトランスファーNチャネル型MOSトランジスタに流れるGIDL電流が前記動作状態に対して前記待機状態の方が小さくされることを特徴とする半導体集積回路装置。

【請求項7】

そのソース電極が電源線に接続される第1Pチャネル型MOSトランジスタと、そのソース電極がソース線に接続され、そのドレイン電極が前記第1Pチャネル型MOSトランジスタのドレイン電極に接続され、そのゲート電極が前記第1Pチャネル型MOSトランジスタのゲート電極に接続される第1Nチャネル型MOSトランジスタと、そのソース電極が前記電源線に接続される第2Pチャネル型MOSトランジスタと、そのソース電極が前記ソース線に接続され、そのドレイン電極が前記第2Pチャネル型MOSトランジスタのドレイン電極に接続されると共に前記第1Pチャネル型MOSトランジスタ及び前記第1Nチャネル型MOSトランジスタのゲート電極に接続され、そのゲート電極が前記第2Pチャネル型MOSトランジスタのゲート電極に接続されると共に前記第1Pチャネル型MOSトランジスタ及び前記第1Nチャネル型MOSトランジスタのドレイン電極に接続される第2Nチャネル型MOSトランジスタとを有するラッチ回路を含む半導体集積回路装置であって、

前記電源線と前記ソース線との電位差である前記ラッチ回路の電源電圧を制御する電源電圧制御回路とを具備し、

前記第1及び第2Pチャネル型MOSトランジスタ及び前記第1及び第2Nチャネル型MOSトランジスタのゲート絶縁膜厚は、4nm以下であり、

前記電源電圧制御回路は、第1状態では前記電源電圧を第1電圧とし、第2状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御し、前記第1Pチャネル型MOSトランジスタ及び前記第2Nチャネル型MOSトランジスタがオン状態である場合に、前記第1Pチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、前記第2Nチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を前記第1状態に対し前記第2状態の方を小さくすることを特徴とする半導体集積回路装置。

【請求項8】

請求項7において、

前記電源線の電位は、前記第1及び第2状態において第1電位とされ、

前記ソース線の電位は、前記第1状態では第2電位とされ、前記第2状態では前記第2電位よりも高い第3電位とされるとともに、前記第1及び第2Nチャネル型MOSトランジスタの基板電位は前記第1及び第2状態において第2電位とされる半導体集積回路装置。

【請求項9】

請求項7において、

前記ラッチ回路は、データ線対の一方と前記第1Pチャネル型MOSトランジスタ及び前記第1Nチャネル型MOSトランジスタのドレイン電極との間に設けられた第3Nチャネル型MOSトランジスタと、前記データ線対の他方と前記第2Pチャネル型MOSトランジスタ及び前記第2Nチャネル型MOSトランジスタのドレイン電極との間に設けられた第4Nチャネル型MOSトランジスタとを有し、前記第3Nチャネル型MOSトランジスタ及び前記第4Nチャネル型MOSトランジスタのそれぞれゲート電極に共通のワード線が接続されたスタティック型メモリセルであることを特徴とする半導体集積回路装置。

【請求項10】

請求項9において、

前記第3Nチャネル型MOSトランジスタ及び前記第4Nチャネル型MOSトランジスタのそれぞれのゲート絶縁膜厚は、4nm以下であることを特徴とする半導体集積回路装置。

【請求項1】

そのソース電極が電源線に接続される第1の負荷型Pチャネル型MOSトランジスタと、そのソース電極がソース線に接続され、そのドレイン電極が前記第1の負荷型Pチャネル型MOSトランジスタのドレイン電極に接続され、そのゲート電極が前記第1の負荷型Pチャネル型MOSトランジスタのゲート電極に接続される第1の駆動型Nチャネル型MOSトランジスタと、そのソース電極が前記電源線に接続される第2の負荷型Pチャネル型MOSトランジスタと、そのソース電極が前記ソース線に接続され、そのドレイン電極が前記第2の負荷型Pチャネル型MOSトランジスタのドレイン電極に接続されると共に前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのゲート電極に接続され、そのゲート電極が前記第2の負荷型Pチャネル型MOSトランジスタのゲート電極に接続されると共に前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのドレイン電極に接続される第2の駆動型Nチャネル型MOSトランジスタとを夫々が有する複数のスタティック型メモリセルを含む半導体集積回路装置であって、

前記電源線と前記ソース線との電位差である前記複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路とを具備し、

前記第1及び第2の負荷型Pチャネル型MOSトランジスタ及び前記第1及び第2の駆動型Nチャネル型MOSトランジスタのゲート絶縁膜厚は、4nm以下であり、

前記電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御し、前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第2の駆動型Nチャネル型MOSトランジスタがオン状態である場合に、前記第1の負荷型Pチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、前記第2の駆動型Nチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を前記動作状態に対し前記待機状態の方を小さくすることを特徴とする半導体集積回路装置。

【請求項2】

請求項1において、

前記電源線の電位は、前記動作状態及び前記待機状態において第1電位とされ、

前記ソース線の電位は、前記動作状態では第2電位とされ、前記待機状態では前記第2電位よりも高い第3電位とされるとともに、前記第1及び第2の駆動型Nチャネル型MOSトランジスタの基板電位は前記動作状態及び前記待機状態において第2電位とされる半導体集積回路装置。

【請求項3】

請求項1において、

前記ソース線の電位は、前記動作状態及び前記待機状態において第1電位とされ、

前記電源線の電位は、前記動作状態では前記第1電位より大きい第2電位とされ、

前記待機状態では前記第1電位と第2電位の間の第3電位とされるとともに、前記第1及び第2の負荷型Pチャネル型MOSトランジスタの基板電位は前記動作状態及び前記待機状態において前記第2電位とされる半導体集積回路装置。

【請求項4】

請求項1乃至3の何れか1項において、

前記動作状態では前記複数のスタティック型メモリセルに対する読み出し又は書き込み動作が行われ、

前記待機状態は前記複数のスタティック型メモリセルが選択されていないことを特徴とする半導体集積回路装置。

【請求項5】

請求項1乃至4の何れか1項において

前記半導体集積回路装置は、前記複数のスタティック型メモリセルを夫々が有する複数のメモリマットを有し、

前記動作状態と前記待機状態の切り替えは、マット選択信号に基づいていることを特徴とする半導体集積回路装置。

【請求項6】

請求項1乃至5の何れか1項において、

前記複数のスタティック型メモリセルの夫々は、データ線対の一方と前記第1の負荷型Pチャネル型MOSトランジスタ及び前記第1の駆動型Nチャネル型MOSトランジスタのドレイン電極との間に設けられた第1のトランスファーNチャネル型MOSトランジスタと、前記データ線対の他方と前記第2の負荷型Pチャネル型MOSトランジスタ及び前記第2の駆動型Nチャネル型MOSトランジスタのドレイン電極との間に設けられた第2のトランスファーNチャネル型MOSトランジスタとを更に有し、

前記データ線対は、前記待機状態において、前記動作状態におけるプリチャージ電位より低い電位に設定され、

前記第1及び第2のトランスファーNチャネル型MOSトランジスタがオフ状態の際に、前記第1及び第2のトランスファーNチャネル型MOSトランジスタに流れるGIDL電流が前記動作状態に対して前記待機状態の方が小さくされることを特徴とする半導体集積回路装置。

【請求項7】

そのソース電極が電源線に接続される第1Pチャネル型MOSトランジスタと、そのソース電極がソース線に接続され、そのドレイン電極が前記第1Pチャネル型MOSトランジスタのドレイン電極に接続され、そのゲート電極が前記第1Pチャネル型MOSトランジスタのゲート電極に接続される第1Nチャネル型MOSトランジスタと、そのソース電極が前記電源線に接続される第2Pチャネル型MOSトランジスタと、そのソース電極が前記ソース線に接続され、そのドレイン電極が前記第2Pチャネル型MOSトランジスタのドレイン電極に接続されると共に前記第1Pチャネル型MOSトランジスタ及び前記第1Nチャネル型MOSトランジスタのゲート電極に接続され、そのゲート電極が前記第2Pチャネル型MOSトランジスタのゲート電極に接続されると共に前記第1Pチャネル型MOSトランジスタ及び前記第1Nチャネル型MOSトランジスタのドレイン電極に接続される第2Nチャネル型MOSトランジスタとを有するラッチ回路を含む半導体集積回路装置であって、

前記電源線と前記ソース線との電位差である前記ラッチ回路の電源電圧を制御する電源電圧制御回路とを具備し、

前記第1及び第2Pチャネル型MOSトランジスタ及び前記第1及び第2Nチャネル型MOSトランジスタのゲート絶縁膜厚は、4nm以下であり、

前記電源電圧制御回路は、第1状態では前記電源電圧を第1電圧とし、第2状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御し、前記第1Pチャネル型MOSトランジスタ及び前記第2Nチャネル型MOSトランジスタがオン状態である場合に、前記第1Pチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、前記第2Nチャネル型MOSトランジスタのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を前記第1状態に対し前記第2状態の方を小さくすることを特徴とする半導体集積回路装置。

【請求項8】

請求項7において、

前記電源線の電位は、前記第1及び第2状態において第1電位とされ、

前記ソース線の電位は、前記第1状態では第2電位とされ、前記第2状態では前記第2電位よりも高い第3電位とされるとともに、前記第1及び第2Nチャネル型MOSトランジスタの基板電位は前記第1及び第2状態において第2電位とされる半導体集積回路装置。

【請求項9】

請求項7において、

前記ラッチ回路は、データ線対の一方と前記第1Pチャネル型MOSトランジスタ及び前記第1Nチャネル型MOSトランジスタのドレイン電極との間に設けられた第3Nチャネル型MOSトランジスタと、前記データ線対の他方と前記第2Pチャネル型MOSトランジスタ及び前記第2Nチャネル型MOSトランジスタのドレイン電極との間に設けられた第4Nチャネル型MOSトランジスタとを有し、前記第3Nチャネル型MOSトランジスタ及び前記第4Nチャネル型MOSトランジスタのそれぞれゲート電極に共通のワード線が接続されたスタティック型メモリセルであることを特徴とする半導体集積回路装置。

【請求項10】

請求項9において、

前記第3Nチャネル型MOSトランジスタ及び前記第4Nチャネル型MOSトランジスタのそれぞれのゲート絶縁膜厚は、4nm以下であることを特徴とする半導体集積回路装置。

【図1】

【図2】

【図3】

【図4】

【図5】