半導体装置

【課題】コイル状のアンテナ部の内部に、占有面積が大きい導電層が設けられていると、電源を安定して供給することが困難になっていた。

【解決手段】記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電力化を図ることができる。また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、スペースを有効に利用することができる。従って、半導体装置の小型化を実現することができる。

【解決手段】記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電力化を図ることができる。また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、スペースを有効に利用することができる。従って、半導体装置の小型化を実現することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、無線通信によりデータの交信を行う半導体装置に関する。特に、電磁誘導方

式を用いて、無線通信によりデータの交信を行う半導体装置に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装

置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

近年、無線通信によりデータの交信を行う半導体装置を利用した個体識別技術が注目を

集めている。半導体装置を利用した個体識別技術は、個々の対象物の生産、管理等に役立

てられ始めており、個人認証への応用も開始している。このような半導体装置は、RFI

D(Radio Frequency Identification)タグ、IC(I

ntegrated Circuit)タグ、ICチップ、RFタグ、無線タグ、電子タ

グとも呼ばれる。

【0004】

電磁誘導方式によりデータの交信を行う半導体装置(特許文献1参照)について、図1

0を用いて説明する。半導体装置301は、コイル状のアンテナ部302と半導体回路部

303を有する。半導体回路部303の端子304は、コイル状のアンテナ部302の一

端305に電気的に接続されている。半導体回路部303の端子306は、コイル状のア

ンテナ部302の他端307に電気的に接続されている。

【0005】

コイル状のアンテナ部を含むリーダライターを、半導体装置301に近づけると、リー

ダライターが含むコイル状のアンテナ部から交流磁界が発生する。交流磁界は、半導体装

置301内のコイル状のアンテナ部302を貫き、電磁誘導により半導体装置301内の

コイル状のアンテナ部302の端子間(一端305と他端307の間)に起電力が発生す

る。電磁誘導により発生した起電力により半導体装置301内の半導体回路部303が動

作する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平11−11058号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

電磁誘導方式によりデータの交信を行う半導体装置は、上述の通り、アンテナを用いて電

源が供給されるため、電源の安定的な供給が困難であった。そのため、消費電力を極力抑

制することが必要であった。

【0008】

コイル状のアンテナ部の内部に、占有面積の大きい導電層があると、電磁誘導の影響を

うけて、当該導電層にも電流が流れてしまうことがあった。つまり、コイル状のアンテナ

部の内部に、占有面積が大きい導電層が設けられていると、電源を安定して供給すること

が困難になっていた。

【0009】

そこで、本発明は、コイル状のアンテナ部と、占有面積の大きい導電層の配置を工夫す

ることにより、当該導電層に対する電磁誘導の影響を防止し、また、電源の安定化を実現

した半導体装置の提供を課題とする。

【課題を解決するための手段】

【0010】

本発明は、アンテナを有する一つの半導体デバイスに対して占有面積の大きい導電層を一

対の電極の一方として用いる素子(例えば、メモリ素子、発光素子、センサ素子など)に

おいて、アンテナと占有面積の大きい導電層とを少なくとも一部重ねることを特徴とする

。

【0011】

本明細書で開示する発明の構成は、絶縁表面を有する基板上に、少なくとも複数の集積回

路と、渦巻き状(一つの平面内で渦巻き状、またはコイル状と呼ぶ)を主たる構成とする

アンテナと、第1の電極と、第2の電極と、前記第1の電極と前記第2の電極の間に有機

化合物を含む層とを有し、前記アンテナは、少なくとも前記複数の集積回路うちの一つと

電気的に接続し、前記第1の電極または前記第2の電極は、少なくとも前記複数の集積回

路のうちの一つと電気的に接続し、前記アンテナは、前記第2の電極と重なることを特徴

とする半導体装置である。

【0012】

また、アンテナはトランジスタとも重なるように配置してもよく、本発明の他の構成は、

絶縁表面を有する基板上に、少なくとも複数の集積回路と、トランジスタと、渦巻き状(

一つの平面内で渦巻き状、またはコイル状と呼ぶ)を主たる構成とするアンテナと、第1

の電極と、第2の電極と、前記第1の電極と前記第2の電極の間に有機化合物を含む層と

を有し、前記アンテナは、少なくとも前記複数の集積回路うちの一つと電気的に接続し、

前記第1の電極または前記第2の電極は、少なくとも前記複数の集積回路のうちの一つと

電気的に接続し、前記トランジスタは、前記第1の電極と電気的に接続し、前記アンテナ

は、前記第2の電極及び前記トランジスタと重なることを特徴とする半導体装置である。

なお、第2の電極だけでなく、集積回路のトランジスタもアンテナと重ねる場合には、そ

の集積回路は、アンテナで囲まれる領域の外側にも一部が配置される。

【0013】

なお、第1の電極と、第2の電極と、これらの電極間に有機化合物を含む層とで、メモリ

素子、発光素子、センサ素子などを構成する。これらの素子は、一方または両方の電極面

積が比較的広く、アンテナと少なくとも一部が重なるように配置することが好ましい。

【0014】

中でも有機材料を用いたメモリ素子の利点としては、他者が偽造しようとして分解した場

合、大気などに触れた有機材料は変質しやすく、使用している材料を特定しにくいため、

偽造を非常に困難なものとすることができる。

【0015】

また、情報の改ざんや不正使用を防止するため、メモリ素子の有機化合物を含む層を可

逆的に相変化しない有機材料または無機材料とした場合には、メモリへの書き込みは1回

とする。

【0016】

また、繰り返し使用するため、メモリ素子の有機化合物を含む層を可逆的に相変化する有

機材料(例えば、バソフェナントロリン(略称:BPhen))、または無機材料とした

場合には、メモリへのデータの書き換えが複数回可能となる。また、リーダライタによっ

て、有機材料を用いたメモリ素子への書き込みと読み取りの両方が可能であってもよい。

【0017】

また、上記各構成において、前記アンテナは給電部及び線状または帯状の複数のアンテナ

導体からなり、該アンテナ導体は給電部の周囲から給電部に向かって渦巻き状に設けられ

ていることを特徴の一つとしている。また、アンテナ導体は、楕円形または円形であって

もよい。

【0018】

また、上記各構成において、前記集積回路は、例えば、書き込み回路、読み出し回路、セ

ンスアンプ、出力回路、バッファ等である。

【0019】

上述したこれらの手段は単なる設計事項ではなく、メモリやアンテナや配線を配置し、そ

の配置を用いた記憶回路を含む半導体装置を作製し、書き込み動作や読み込み動作をさせ

、発明者らの深い検討の後、発明された事項である。

【発明の効果】

【0020】

本発明により、アンテナと重なる領域に対して占有面積の大きい導電層を配置することが

できるため、アンテナと重なる領域に何も配置しないものに比べ、スペースを有効に利用

することができる。従って、半導体装置の小型化を実現することができる。

【0021】

また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路

部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電

力化を図ることができる。

【図面の簡単な説明】

【0022】

【図1】(A)本発明の半導体装置の構成を説明する図。(B)本発明の半導体装置の構成を説明する図。(C)比較例を説明する図。

【図2】本発明の半導体装置の構成を説明する図。

【図3】本発明の半導体装置の構成を説明する図。

【図4】本発明の半導体装置の構成を説明する図。

【図5】本発明の半導体装置の構成を説明する図。

【図6】本発明の半導体装置の構成を説明する図。

【図7】本発明の半導体装置の構成を説明する図。

【図8】本発明の半導体装置の構成を説明する断面図。

【図9】本発明の半導体装置の構成を説明する回路図。

【図10】半導体装置の構成を説明する図。

【発明を実施するための形態】

【0023】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明

に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々

に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施

の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構

成において、同じものを指す符号は異なる図面間で共通して用いる。

(実施の形態1)

【0024】

本発明の半導体装置は、半導体回路部11、記憶回路部12、コイル状のアンテナ部1

3を有する。記憶回路部12は、複数の記憶素子を有する。複数の記憶素子の各々は、一

対の電極間に有機化合物を含む層が挟まれた構造を有する。複数の記憶素子が含む一対の

電極のうちの一方または両方は、複数の記憶素子で共通して用いられている。そのため、

複数の記憶素子が含む一対の電極のうちの一方は、占有面積が大きい導電層となってしま

う。そこで本発明は、記憶回路部12が含む占有面積の大きい導電層に、電磁誘導の影響

により電流が流れてしまうことを防止するため、記憶回路部12とコイル状のアンテナ部

13とを重なるように配置する。

【0025】

本発明の半導体装置の上面構造について説明する。以下の説明では、半導体回路部、記

憶回路部、コイル状のアンテナ部を有し、記憶回路部と、コイル状のアンテナ部が重なら

ない半導体装置(図1(C)参照)と比較して説明する。なお、図1(C)は比較例であ

って本発明ではない。図1(C)に示す半導体装置は、半導体回路部1201と記憶回路

部1202とアンテナ部1203とを有している。なお、半導体回路部1201の第1の

端子は、コイル状のアンテナ部1203の一方の端に電気的に接続されて、半導体回路部

1201の第2の端子は、コイル状のアンテナ部1203の他方の端に電気的に接続され

ている。また、半導体回路部1201と記憶回路部1202は電気的に接続されている。

【0026】

図1(C)の構成と比較して記憶回路部12の占有面積が同じであり、記憶回路部12

とコイル状のアンテナ部13とが重なるように配置する場合(図1(A)参照)、半導体

回路部11の占有面積を拡大することができる。半導体回路部11の占有面積を拡大する

ことができると、より複数の素子を設けることができるため、高機能な回路を提供するこ

とができる。なお、図1(A)に示すコイル状のアンテナ部13は、巻き数が5巻を越え

る例を示したが特に限定されず、2巻以上であればよい。なお、半導体回路部11の第1

の端子は、コイル状のアンテナ部13の一方の端に電気的に接続されて、半導体回路部1

1の第2の端子は、コイル状のアンテナ部13の他方の端に電気的に接続されている。ま

た、半導体回路部11と記憶回路部12は電気的に接続されている。

【0027】

図1(C)の構成と比較して半導体回路部11の面積が同じであり、記憶回路部12と

コイル状のアンテナ部13とが重なるように配置する場合(図1(B)参照)、記憶回路

部12の占有面積を拡大することができる。記憶回路部12の占有面積を拡大することが

できると、より複数の素子を設けることができるため、記憶容量が大きい回路を提供する

ことができる。図1(B)においても、半導体回路部11の第1の端子は、コイル状のア

ンテナ部13の一方の端に電気的に接続されて、半導体回路部11の第2の端子は、コイ

ル状のアンテナ部13の他方の端に電気的に接続されている。また、半導体回路部11と

記憶回路部12は電気的に接続されている。

【0028】

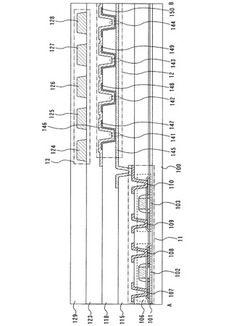

次に、上記構成を有する半導体装置の断面構造について説明する(図2参照)。図2に

示す断面構造は、図1(A)の半導体装置の上面構造の点Aから点Bの断面構造を示す図

である。

【0029】

本発明の半導体装置は、絶縁表面を有する基板100上に、下地用の絶縁層101と、

絶縁層101上に設けられた薄膜トランジスタ102〜105と、薄膜トランジスタ10

2〜105を覆う絶縁層106と、絶縁層106に設けられた開口部を介して、薄膜トラ

ンジスタ102〜105のソース又はドレインに接続された配線107〜114とを有す

る。

【0030】

また、配線107〜114を覆う絶縁層115と、絶縁層115に設けられた開口部を

介して、配線112、114に接続された導電層116、117と、導電層116、11

7を覆う絶縁層118と、絶縁層118に設けられた開口部を介して、導電層116、1

17に接続された有機化合物を含む層119、120と、有機化合物を含む層119、1

20に接続された導電層121を有する。また、導電層121を覆う絶縁層123と、絶

縁層123上に設けられた導電層124〜128、導電層124〜128を覆う絶縁層1

29を有する。

【0031】

上記の断面構造において、薄膜トランジスタ102、103を含む部分が、半導体回路

部11に相当する。また、導電層116、有機化合物を含む層119及び導電層121の

積層体が、記憶素子130に相当する。また、導電層117、有機化合物を含む層120

及び導電層121の積層体が、記憶素子131に相当する。記憶素子130、131を含

む回路が、記憶回路部12に相当する。また、導電層124〜128が、コイル状のアン

テナ部13に相当する。

【0032】

上記の構造のように、記憶回路部12が含む占有面積の大きい導電層121と、コイル

状のアンテナ部13が含む導電層124〜128とを重ねて配置することにより、電磁誘

導の影響により導電層121に電流が流れてしまうことを防止することができる。また、

記憶回路部12とコイル状のアンテナ部13とを積層して配置することにより、小型化を

実現することができる。

【0033】

次に、上記とは異なる構成の半導体装置の断面構造について説明する(図3参照)。半

導体装置は、絶縁表面を有する基板100上に、下地用の絶縁層101と、絶縁層101

上に設けられた薄膜トランジスタ102、103と、薄膜トランジスタ102、103を

覆う絶縁層106と、絶縁層106に設けられた開口部を介して、薄膜トランジスタ10

2、103のソース又はドレインに接続された配線107〜110とを有する。

【0034】

また、配線107〜110を覆う絶縁層115と、絶縁層115に設けられた開口部を

介して、配線110に接続された導電層145と、導電層145を覆う絶縁層118と、

絶縁層118に設けられた開口部を介して、導電層145に接続された有機化合物を含む

層147〜150と、有機化合物を含む層147〜150に接続された導電層146を有

する。また、導電層146を覆う絶縁層123と、絶縁層123上に設けられた導電層1

24〜128、導電層124〜128を覆う絶縁層129を有する。導電層145と、有

機化合物を含む層147〜150のいずれか一つと、導電層146の積層体が、記憶素子

141〜144に相当する。

【0035】

上記の構造のように、記憶回路部12が含む占有面積の大きい導電層145、146と

、コイル状のアンテナ部13が含む導電層124〜128とを重ねて配置することにより

、電磁誘導の影響により導電層121に電流が流れてしまうことを防止することができる

。また、記憶回路部12とコイル状のアンテナ部13とを積層して配置することにより、

小型化を実現することができる。

【0036】

(実施の形態2)

本実施の形態では、上記実施の形態1で示す記憶装置を有する半導体装置の一例に関して

さらなる詳細な図面を用いて説明する。本実施の形態の半導体装置の上面図を図8(A)

に示し、図8(A)における線X−Yの断面図を図8(B)に示す。

【0037】

図8(A)に示すように、基板400上に記憶素子を有する記憶装置である記憶素子部4

04、集積回路部421、アンテナ431が形成されている。図8(A)及び(B)は、

作製工程途中であり、作製条件に耐えうる基板400上に記憶素子部、回路部、及びアン

テナを形成した状態である。記憶装置に用いる材料及び作製工程は公知のものを用いれば

よい。

【0038】

基板400上に剥離層452、絶縁層453を介して記憶素子部404にはトランジス

タ441、集積回路部421にはトランジスタ442が設けられている。剥離層452と

しては、50nm〜200nmのタングステン膜を用い、絶縁層453としては酸化珪素

膜を用いる。ただし、剥離層はタングステン膜に限定されず、Mo膜やアモルファスシリ

コン膜などを用いてもよい。トランジスタ441及びトランジスタ442上に絶縁層45

1、絶縁層454、絶縁層455が形成されており、絶縁層455上に第1の導電層45

7d、有機化合物層458及び第2の導電層459の積層から構成される記憶素子443

が形成されている。隔壁として機能する絶縁層460bにより有機化合物層458は個々

に隔てられている。第1の導電層457dはトランジスタ441の配線層と接続しており

、記憶素子443は、トランジスタ441と電気的に接続している。

【0039】

第1の導電層457d及びトランジスタ441と、導電層457c及び配線層456a

と、導電層457e及び配線層456bとがそれぞれ接続するために絶縁層455に開口

(コンタクトホールとも言う)を形成する。開口を大きくし、導電層同士の接触面積を増

加した方がより低抵抗となるため、本実施の形態では、第1の導電層457dとトランジ

スタ441とが接続する開口が一番小さく、その次が導電層457cと配線層456aと

が接続する開口、導電層457eと配線層456bとが接続する開口が一番大きいという

ように順に開口を大きく設定している。本実施の形態では、第1の導電層457dとトラ

ンジスタ441とが接続する開口を5μm×5μm、導電層457cと配線層456aと

が接続する開口を50μm×50μm、導電層457eと配線層456bとが接続する開

口を500μm×500μmとしている。

【0040】

図8(B)における半導体装置では、第2の導電層459は、配線層456a、導電層

457cと積層して電気的に接続している。第2の導電層459は、第1の導電層457

dよりも電極面積が大きく、本発明では、この第2の導電層459とアンテナ431が重

なるように配置する。

【0041】

絶縁層455上に絶縁層461が形成されている。絶縁層461上には、導電層457a

とアンテナ431a、導電層457bとアンテナ431b、導電層457eとアンテナ4

31c、及び導電層457fとアンテナ431dとがそれぞれ積層して形成されている。

導電層457eは絶縁層461に形成された配線層462に達する開口を介して配線層4

62と接して形成されている。また、配線層462は、絶縁層455に形成された配線層

456bに達する開口を介して配線層456bと接して形成されている。なお、本明細書

では、このアンテナと、アンテナの下方の配線層との接続部分をアンテナの給電部と呼ぶ

。ここでは、配線層462と配線層456bを用いてアンテナと記憶素子部404及び集

積回路部421とを電気的に接続しているが、特にこの接続に限定されず、アンテナ43

1cと456bとが電気的に接続するような構造とすればよい。

【0042】

アンテナ431a、アンテナ431b、アンテナ431c、及び431d下の導電層45

7a、導電層457b、導電層457e、導電層457fは、絶縁層455とアンテナ4

31a、アンテナ431b、アンテナ431c、及び431dとの密着性を向上させる効

果もある。本実施の形態では、絶縁層455、及び絶縁層461にポリイミド膜を用い、

導電層457a、導電層457b、導電層457e、及び導電層457fにチタン膜を用

い、アンテナ431a、アンテナ431b、アンテナ431c、及び431dにアルミニ

ウム膜をそれぞれ用いている。

【0043】

集積回路部421は部分的に絶縁層460cが形成されており、トランジスタ442も

絶縁層460cに覆われていない領域と覆われている領域がある。

【0044】

ここで、本実施の形態における半導体装置の回路に関するブロック図を図9示す。図9

(A)における半導体装置のブロック図は、RF入力部401、ロジック回路部402、

外部入力部403、記憶素子部404、調整回路部405、ダイオード406、抵抗40

7を有している。なお、図8(A)に示した集積回路部421は、図9(A)のRF入力

部401、ロジック回路部402、外部入力部403、調整回路部405、ダイオード4

06、または抵抗407に相当する。

【0045】

外部入力端子から入力された電圧及び信号は、記憶素子部404に入力され、記憶素子

部404にデータ(情報)が書き込まれる。RF入力部401において、アンテナによっ

て交流信号を受信し信号及び電圧をロジック回路部402に入力する。ロジック回路部4

02を介して信号は制御信号となり、制御信号が記憶素子部404に入力されることで記

憶素子部404より書き込まれたデータが再び読み出される。

【0046】

図9(B)は、図9(A)の半導体装置と調整回路部405の構造が異なる例であり、

調整回路部405は抵抗で、調整回路部415はスイッチで構成されている。図9(B)

におけるブロック図は、RF入力部411、ロジック回路部412、外部入力部413、

記憶素子部414、調整回路部415、ダイオード416、抵抗417を有している。な

お、図8(A)に示した集積回路部421は、図9(B)のRF入力部411、ロジック

回路部412、外部入力部413、調整回路部415、ダイオード416、または抵抗4

17に相当する。

【0047】

また、抵抗407及び抵抗417はプルアップ回路であり、調整回路部として機能する。

調整回路部405は、記憶素子部404にデータを書き込み時に、ロジック回路部402

より不要な制御信号が記憶素子部404に入力されないように調整するものである。同様

に、抵抗407も、記憶素子部404にデータを書き込む時に、ロジック回路部402よ

り記憶素子部404に信号が入力されないように調整するものである。記憶素子部404

にデータを書き込む時は、ダイオード406により外部入力部403からの信号は遮断さ

れるが、記憶素子部404よりデータを読み取る時は、記憶素子部404のVDDHをR

F入力部401より印加されるVDDに固定し、安定させる。図9(A)のブロック図に

基づいて説明したが、図9(B)においても同様である。

【0048】

また、RF入力部401、411に電気的に接続されるアンテナは、記憶素子部を有す

る記憶装置に対して、重ねて設ける。また記憶装置の電極全面が重なってもよいし、一部

が重なっている構造でもよい。アンテナ部と記憶装置が重なる構造であると、アンテナが

交信する際に信号に載っているノイズ等や、電磁誘導により発生する起電力の変動等の影

響による、半導体装置の動作不良を減らすことが可能であり、信頼性が向上する。また、

半導体装置の省電力化が実現できる。また、半導体装置を小型化することもできる。

【0049】

本実施の形態で示す第1の導電層457d、有機化合物層458、及び第2の導電層4

59を有する記憶素子443は密着性が良いので、第1の基板(ガラス基板)である基板

400に形成された後に、第2の基板に転写される工程でかかる力によって、層界面で膜

剥がれなどの不良が生じない。よって良好な形状で記憶素子を剥離した後、紙やプラスチ

ック基板上に転写し、軽量、且つ、フレキシブルな記憶装置、または軽量、且つ、フレキ

シブルな半導体装置を作製することができる。

【0050】

本実施の形態で作製される記憶素子を有する記憶装置は密着性が良好なため、剥離工程

、及び転写工程を良好な状態で行うことができる。よって、自由に様々な基板に転写する

ことができるため、基板の材料の選択性の幅が広がる。また安価な材料を基板として選択

することもでき、用途に合わせて広い機能を持たせることができるだけでなく、低コスト

で記憶装置、半導体装置を作製することができる。

【0051】

本発明により、良好な状態で転写工程を行えるような密着性のよい記憶素子を有する記

憶装置を作製できる。よって、より高信頼性の記憶装置、及びその記憶装置を備えた半導

体装置を装置や工程を複雑化することなく、歩留まりよく作製することができる。

【0052】

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行う

こととする。

【実施例1】

【0053】

本発明の半導体装置が含む記憶回路部の構成について説明する(図4、5参照)。

【0054】

記憶回路部は、複数のビット線B1〜Bm(mは自然数)と、複数のワード線W1〜W

n(nは自然数)と、複数のメモリセル201とを含むメモリセルアレイ202を有する

。また、複数のビット線B1〜Bmを制御するデコーダ203と、複数のワード線W1〜

Wnを制御するデコーダ204と、セレクタ205と、読み出し書き込み回路206とを

有する。

【0055】

メモリセルアレイ202の構成には、アクティブマトリクス型とパッシブマトリクス型

とがある。メモリセルアレイ202がアクティブマトリクス型の場合、メモリセル201

は、トランジスタ215と、記憶素子207を含む(図4参照)。トランジスタ215の

ゲートはワード線Wb(1≦b≦n)に電気的に接続され、トランジスタ215のソース

又はドレインの一方はビット線Ba(1≦a≦m)に電気的に接続され、トランジスタ2

15のソース又はドレインの他方は記憶素子207が含む一対の電極の一方に電気的に接

続されている。

【0056】

また、メモリセルアレイ202がパッシブマトリクス型の場合、メモリセル201は、

ビット線Baとワード線Wbが交差する箇所に設けられた記憶素子207を含む(図5参

照)。

【0057】

次に、記憶回路部にデータの書き込みを行うときの動作について説明する。

【0058】

まず、電気的作用により、記憶回路部にデータの書き込みを行う場合について説明する

。最初に、デコーダ203、デコーダ204、セレクタ205により、メモリセル201

が選択される。次に、読み出し書き込み回路206により、選択されたメモリセル201

にデータが書き込まれる。具体的には、読み出し書き込み回路206により、選択された

メモリセル201が含む記憶素子に所定の電圧が印加されることにより、データが書き込

まれる。所定の電圧が印加されると、記憶素子の抵抗値は変化する。記憶素子の抵抗値の

変化には、抵抗値が大きくなる場合と、抵抗値が小さくなる場合があるが、データの書き

込みには、そのどちらの現象を用いてもよい。抵抗値が大きくなる現象は、記憶素子に所

定の電圧を印加して、一対の電極の間の有機化合物を含む層が高抵抗化する現象を利用し

たものである。また、抵抗値が小さくなる現象は、記憶素子に所定の電圧を印加して、一

対の電極間の距離を短くする現象を利用したものである。このように、記憶回路部は、電

気的作用により、記憶素子の抵抗値が変化することを利用して、データの書き込みを行う

。例えば、初期状態の記憶素子を「0」のデータとすると、「1」のデータを書き込む記

憶素子には電気的作用を印加する。

【0059】

次に、光学的作用によりデータの書き込みを行う場合について説明する。この場合、透

光性を有する導電層側から、光学照射装置(例えば、レーザ照射装置)により、有機化合

物を含む層に光を照射する。そうすると、光が照射された記憶素子にデータが書き込まれ

る。光が照射されることにより、記憶素子の抵抗値は変化する。記憶素子の抵抗値の変化

には、抵抗値が大きくなる場合と、抵抗値が小さくなる場合とがあるが、データの書き込

みには、そのどちらの現象を用いてもよい。このように、記憶回路部は、光学的作用によ

り、記憶素子の抵抗値が変化することを利用して、データの書き込みを行う。例えば、初

期状態の記憶素子を「0」のデータとすると、「1」のデータを書き込む記憶素子には、

光学的作用を印加する。

【0060】

次に、記憶回路部にデータの読み出しを行うときの動作について説明する。

【0061】

データの読み出しは、データの書き込みの方法にかかわらず、電気的作用により行われ

る。データの読み出しは、デコーダ203、204、セレクタ205、読み出し書き込み

回路206により、記憶素子の抵抗値の相違を読み出すことにより行われる。

【0062】

なお、記憶素子が含む一対の導電層の一方と、有機化合物を含む層との間に、整流性を

有する素子を設けてもよい。整流性を有する素子とは、ゲートとドレインを互いに電気的

に接続させたトランジスタ、ダイオード等である。整流性を有する素子を設けると、電流

の流れる方向を限定することができるため、データの読み出しの正確性を向上させること

ができる。

【0063】

次に、記憶素子が含む有機化合物を含む層に用いる材料について説明する。

【0064】

記憶素子に対するデータの書き込みを電気的作用により行う場合、有機化合物を含む層

には、低分子系材料、高分子系材料、シングレット材料、トリプレット材料などを用いる

とよい。また、有機化合物を含む層には、有機化合物材料のみからなるものだけでなく、

無機化合物を一部に含む材料を用いるとよい。また、有機化合物を含む層には、正孔注入

層、正孔輸送層、正孔阻止層、発光層、電子輸送層、電子注入層等が用いられるが、単層

で用いてもよいし、複数の層を積層させてもよい。なお、有機化合物を含む層は、インク

ジェット法に代表される液滴吐出法により形成するとよい。液滴吐出法を用いることによ

り、材料の利用効率の向上、作製工程の簡略化による作製時間の短縮、作製費用の低減を

実現することができる。

【0065】

また、記憶回路部に対するデータの書き込みを光学的作用により行う場合、有機化合物

を含む層には、光学的作用により性質が変化する材料を用いるとよい。例えば、光を吸収

することによって酸を発生する化合物(光酸発生剤)をドープした共役高分子を用いると

よい。共役高分子とは、ポリアセチレン類、ポリフェニレンビニレン類、ポリチオフェン

類、ポリアニリン類、ポリフェニレンエチニレン類等を用いるとよい。また、光酸発生剤

としては、アリールスルホニウム塩、アリールヨードニウム塩、o−ニトロベンジルトシ

レート、アリールスルホン酸p−ニトロベンジルエステル、スルホニルアセトフェノン類

、Fe−アレン錯体PF6塩等を用いるとよい。

【0066】

また、本発明の半導体装置が有する記憶装置は、不揮発性であってもよく、データの追

記を可能としてもよい。また、本発明の半導体装置が有する記憶装置は、外部からの電気

的作用によりデータの書き換えが可能なものとしてもよい。

【0067】

本実施例では、アンテナの面積サイズを約9mm×11mmとし、アンテナの巻き数を

9巻とし、アンテナ自体の線幅を150μmとし、10μmの間隔でアンテナの配線を巻

いている。このようにコイル状に巻かれたアンテナと重なるように記憶回路部の一方の電

極、即ち上部電極を配置する。この上部電極は、有機化合物を含む層の上方に設けられて

おり、複数の記憶素子に共通の電極となっている。1キロビットの情報量を有する記憶回

路を構成する場合、この上部電極の面積サイズは、1.5mm×3mm程度とすればよい

。なお、上部電極の面積サイズは特に限定されず、4.5mm2のサイズよりも小さくす

ることは可能である。

【0068】

アンテナと、占有面積の大きい導電層(上部電極:4.5mm2)とを重ねて配置するこ

とによって、アンテナと重なる領域に何も配置しないものに比べ、スペースを有効に利用

することができる。従って、半導体装置の小型化を実現することができる。

【0069】

また、占有面積の大きい上部電極とコイル状のアンテナ部とを積層して配置することに

より、記憶回路部が含む上部電極に電流が流れてしまうことを防止することができ、省電

力化を図ることができる。

【0070】

本実施例は、実施の形態1、または実施の形態2と自由に組み合わせることができる。

【実施例2】

【0071】

本発明の半導体装置が含む半導体回路部の構成について説明する(図6参照)。

【0072】

半導体回路部は、アナログ回路551とデジタル回路552とを有する。アナログ回路

551は、共振容量501、帯域フィルタ502、整流回路と保持容量を含む電源回路5

03、復調回路504、変調回路505等を有する。デジタル回路552は、コード抽出

回路506、クロック生成回路507、巡回冗長検査回路508、制御回路509、記憶

回路510等を有する。

【0073】

半導体装置がデータを受信する際の動作について説明する。コイル状のアンテナから入

力された無線信号(変調された搬送波)は、端子221aからアナログ回路551に入力

される。入力された無線信号は、帯域フィルタ502によって所望の周波数成分が取り出

され、電源回路503及び復調回路504に入力される。帯域フィルタ502を介して入

力された変調された搬送波は、電源回路503が含む整流回路によって整流され、更に、

電源回路503が含む保持容量によって平滑化される。こうして、電源回路503は直流

電圧を生成する。電源回路503において生成された直流電圧は電源電圧として、各回路

に供給される。

【0074】

また、帯域フィルタ502を介して入力された変調された搬送波は、デジタル回路55

2内のクロック生成回路507に入力される。クロック生成回路507で生成されたクロ

ックは各回路に供給される。帯域フィルタ502を介して入力された変調された搬送波は

、復調回路504によって復調され、復調された信号はデジタル回路552に入力される

。変調された搬送波を復調回路504によって復調した信号は、コード抽出回路506に

入力され、信号の有するコードが抽出される。コード抽出回路506の出力は、制御回路

509に入力され、コードが抽出される。抽出されたコードは、巡回冗長検査回路508

に入力され、送信エラーを識別するための演算処理が行われる。こうして、巡回冗長検査

回路508は受信データに誤りがあるか否かを制御回路509に出力する。

【0075】

次いで、半導体装置がデータを送信する際の動作について説明する。記憶回路510は

、制御回路509から入力される信号に応じて、記憶された固有識別子(UID)を制御

回路509に出力する。巡回冗長検査回路508は、送信データに対応するCRC符号を

計算し、制御回路509に出力する。制御回路509は送信データにCRC符号を付加す

る。また、制御回路509は、送信データにCRC符号が付加されたデータを符号化する

。更に、制御回路509は、符号化された情報を、所定の変調方式に対応して搬送波を変

調するための信号に変換する。制御回路509の出力は、アナログ回路551の変調回路

505に入力される。変調回路505は、入力された信号に応じて搬送波を負荷変調し、

コイル状のアンテナ部に出力する。

【0076】

本実施例は、実施の形態1、実施の形態2、または実施例1と自由に組み合わせること

ができる。

【実施例3】

【0077】

本実施例では、本発明の半導体装置の用途について説明する。本発明の半導体装置は、例

えば、紙幣、硬貨、有価証券、無記名債券類、証書類(運転免許証や住民票等)、包装用

容器類(包装紙やボトル等)、DVD(Digital Versatile Disc

)、ビデオテープ等の記録媒体、車、自転車等の乗物類、鞄や眼鏡等の身の回り品、食品

類、衣類、生活用品類、電子機器等に設けて使用することができる。電子機器とは、液晶

表示装置、EL(エレクトロルミネッセンス)表示装置、テレビジョン装置および携帯電

話機等を指す。

【0078】

本発明の半導体装置は、物品の表面に貼り付けたり、物品に埋め込んだりして物品に固

定することができる。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケージな

ら当該有機樹脂に埋め込んだりするとよい。紙幣、硬貨、有価証券類、無記名債券類、証

書類等に半導体装置を設けることにより、偽造を防止することができる。また、包装用容

器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に半導体装置を設

けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる

。また乗物類に半導体装置を設けることにより、偽造や盗難を防止することができる。ま

た、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことがで

きる。例えば、家畜等の生き物に半導体装置を埋め込むことによって、生まれた年や性別

または種類等を容易に識別することが可能となる。以上のように、本発明の半導体装置は

物品(生き物を含む)であればどのようなものにでも設けて使用することができる。

【0079】

次に、半導体装置を用いたシステムの一形態について、図7を用いて説明する。表示部

9521を含む端末9520には、アンテナ及び当該アンテナに接続されたリーダライタ

ーが設けられている。物品9532には本発明の半導体装置9531が設けられ、物品9

522には本発明の半導体装置9523が設けられている。物品9532が含む半導体装

置9531に端末9520のアンテナをかざすと、表示部9521に物品9532の原材

料や原産地、生産工程ごとの検査結果や流通過程の履歴、商品の説明等の商品に関する情

報が表示される。物品9522が含む半導体装置9523に端末9520のアンテナをか

ざすと、表示部9521に物品9522の原材料や原産地、生産工程ごとの検査結果や流

通過程の履歴、商品の説明等の商品に関する情報が表示される。

【0080】

本実施例は、実施の形態1、実施の形態2、実施例1、または実施例2と自由に組み合

わせることができる。

【符号の説明】

【0081】

11 半導体回路部

12 記憶回路部

13 コイル状のアンテナ部

100 基板

101 絶縁層

102〜105 薄膜トランジスタ

106 絶縁層

107〜114 配線

115 絶縁層

116 導電層

117 導電層

118 絶縁層

119 有機化合物を含む層

120 有機化合物を含む層

121 導電層

123 絶縁層

124〜128 導電層

129 絶縁層

130 記憶素子

131 記憶素子

141〜144 記憶素子

145 導電層

146 導電層

147〜149 有機化合物を含む層

150 有機化合物を含む層

201 メモリセル

202 メモリセルアレイ

203 デコーダ

204 デコーダ

205 セレクタ

206 読み出し書き込み回路

207 記憶素子

210 有機化合物を含む層

215 トランジスタ

221a 端子

301 半導体装置

302 コイル状のアンテナ部

303 半導体回路部

304 端子

305 一端

306 端子

307 他端

400 基板

401 RF入力部

402 ロジック回路部

403 外部入力部

404 記憶素子部

405 調整回路部

406 ダイオード

407 抵抗

411 RF入力部

412 ロジック回路部

413 外部入力部

414 記憶素子部

415 調整回路部

416 ダイオード

417 抵抗

421 集積回路部

431 アンテナ

431a アンテナ

431b アンテナ

431c アンテナ

431d アンテナ

441 トランジスタ

442 トランジスタ

443 記憶素子

451 絶縁層

452 剥離層

453 絶縁層

454 絶縁層

455 絶縁層

456a 配線層

456b 配線層

457a 導電層

457b 導電層

457c 導電層

457d 第1の導電層

457e 導電層

457f 導電層

458 有機化合物層

459 第2の導電層

460a 絶縁層

460b 絶縁層

460c 絶縁層

461 絶縁層

462 配線層

501 共振容量

502 フィルタ

503 電源回路

504 復調回路

505 変調回路

506 抽出回路

507 生成回路

508 巡回冗長検査回路

509 制御回路

510 記憶回路

551 アナログ回路

552 デジタル回路

1201 半導体回路部

1202 記憶回路部

1203 アンテナ部

9520 端末

9521 表示部

9522 物品

9523 半導体装置

9531 半導体装置

9532 物品

【技術分野】

【0001】

本発明は、無線通信によりデータの交信を行う半導体装置に関する。特に、電磁誘導方

式を用いて、無線通信によりデータの交信を行う半導体装置に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装

置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

近年、無線通信によりデータの交信を行う半導体装置を利用した個体識別技術が注目を

集めている。半導体装置を利用した個体識別技術は、個々の対象物の生産、管理等に役立

てられ始めており、個人認証への応用も開始している。このような半導体装置は、RFI

D(Radio Frequency Identification)タグ、IC(I

ntegrated Circuit)タグ、ICチップ、RFタグ、無線タグ、電子タ

グとも呼ばれる。

【0004】

電磁誘導方式によりデータの交信を行う半導体装置(特許文献1参照)について、図1

0を用いて説明する。半導体装置301は、コイル状のアンテナ部302と半導体回路部

303を有する。半導体回路部303の端子304は、コイル状のアンテナ部302の一

端305に電気的に接続されている。半導体回路部303の端子306は、コイル状のア

ンテナ部302の他端307に電気的に接続されている。

【0005】

コイル状のアンテナ部を含むリーダライターを、半導体装置301に近づけると、リー

ダライターが含むコイル状のアンテナ部から交流磁界が発生する。交流磁界は、半導体装

置301内のコイル状のアンテナ部302を貫き、電磁誘導により半導体装置301内の

コイル状のアンテナ部302の端子間(一端305と他端307の間)に起電力が発生す

る。電磁誘導により発生した起電力により半導体装置301内の半導体回路部303が動

作する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平11−11058号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

電磁誘導方式によりデータの交信を行う半導体装置は、上述の通り、アンテナを用いて電

源が供給されるため、電源の安定的な供給が困難であった。そのため、消費電力を極力抑

制することが必要であった。

【0008】

コイル状のアンテナ部の内部に、占有面積の大きい導電層があると、電磁誘導の影響を

うけて、当該導電層にも電流が流れてしまうことがあった。つまり、コイル状のアンテナ

部の内部に、占有面積が大きい導電層が設けられていると、電源を安定して供給すること

が困難になっていた。

【0009】

そこで、本発明は、コイル状のアンテナ部と、占有面積の大きい導電層の配置を工夫す

ることにより、当該導電層に対する電磁誘導の影響を防止し、また、電源の安定化を実現

した半導体装置の提供を課題とする。

【課題を解決するための手段】

【0010】

本発明は、アンテナを有する一つの半導体デバイスに対して占有面積の大きい導電層を一

対の電極の一方として用いる素子(例えば、メモリ素子、発光素子、センサ素子など)に

おいて、アンテナと占有面積の大きい導電層とを少なくとも一部重ねることを特徴とする

。

【0011】

本明細書で開示する発明の構成は、絶縁表面を有する基板上に、少なくとも複数の集積回

路と、渦巻き状(一つの平面内で渦巻き状、またはコイル状と呼ぶ)を主たる構成とする

アンテナと、第1の電極と、第2の電極と、前記第1の電極と前記第2の電極の間に有機

化合物を含む層とを有し、前記アンテナは、少なくとも前記複数の集積回路うちの一つと

電気的に接続し、前記第1の電極または前記第2の電極は、少なくとも前記複数の集積回

路のうちの一つと電気的に接続し、前記アンテナは、前記第2の電極と重なることを特徴

とする半導体装置である。

【0012】

また、アンテナはトランジスタとも重なるように配置してもよく、本発明の他の構成は、

絶縁表面を有する基板上に、少なくとも複数の集積回路と、トランジスタと、渦巻き状(

一つの平面内で渦巻き状、またはコイル状と呼ぶ)を主たる構成とするアンテナと、第1

の電極と、第2の電極と、前記第1の電極と前記第2の電極の間に有機化合物を含む層と

を有し、前記アンテナは、少なくとも前記複数の集積回路うちの一つと電気的に接続し、

前記第1の電極または前記第2の電極は、少なくとも前記複数の集積回路のうちの一つと

電気的に接続し、前記トランジスタは、前記第1の電極と電気的に接続し、前記アンテナ

は、前記第2の電極及び前記トランジスタと重なることを特徴とする半導体装置である。

なお、第2の電極だけでなく、集積回路のトランジスタもアンテナと重ねる場合には、そ

の集積回路は、アンテナで囲まれる領域の外側にも一部が配置される。

【0013】

なお、第1の電極と、第2の電極と、これらの電極間に有機化合物を含む層とで、メモリ

素子、発光素子、センサ素子などを構成する。これらの素子は、一方または両方の電極面

積が比較的広く、アンテナと少なくとも一部が重なるように配置することが好ましい。

【0014】

中でも有機材料を用いたメモリ素子の利点としては、他者が偽造しようとして分解した場

合、大気などに触れた有機材料は変質しやすく、使用している材料を特定しにくいため、

偽造を非常に困難なものとすることができる。

【0015】

また、情報の改ざんや不正使用を防止するため、メモリ素子の有機化合物を含む層を可

逆的に相変化しない有機材料または無機材料とした場合には、メモリへの書き込みは1回

とする。

【0016】

また、繰り返し使用するため、メモリ素子の有機化合物を含む層を可逆的に相変化する有

機材料(例えば、バソフェナントロリン(略称:BPhen))、または無機材料とした

場合には、メモリへのデータの書き換えが複数回可能となる。また、リーダライタによっ

て、有機材料を用いたメモリ素子への書き込みと読み取りの両方が可能であってもよい。

【0017】

また、上記各構成において、前記アンテナは給電部及び線状または帯状の複数のアンテナ

導体からなり、該アンテナ導体は給電部の周囲から給電部に向かって渦巻き状に設けられ

ていることを特徴の一つとしている。また、アンテナ導体は、楕円形または円形であって

もよい。

【0018】

また、上記各構成において、前記集積回路は、例えば、書き込み回路、読み出し回路、セ

ンスアンプ、出力回路、バッファ等である。

【0019】

上述したこれらの手段は単なる設計事項ではなく、メモリやアンテナや配線を配置し、そ

の配置を用いた記憶回路を含む半導体装置を作製し、書き込み動作や読み込み動作をさせ

、発明者らの深い検討の後、発明された事項である。

【発明の効果】

【0020】

本発明により、アンテナと重なる領域に対して占有面積の大きい導電層を配置することが

できるため、アンテナと重なる領域に何も配置しないものに比べ、スペースを有効に利用

することができる。従って、半導体装置の小型化を実現することができる。

【0021】

また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路

部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電

力化を図ることができる。

【図面の簡単な説明】

【0022】

【図1】(A)本発明の半導体装置の構成を説明する図。(B)本発明の半導体装置の構成を説明する図。(C)比較例を説明する図。

【図2】本発明の半導体装置の構成を説明する図。

【図3】本発明の半導体装置の構成を説明する図。

【図4】本発明の半導体装置の構成を説明する図。

【図5】本発明の半導体装置の構成を説明する図。

【図6】本発明の半導体装置の構成を説明する図。

【図7】本発明の半導体装置の構成を説明する図。

【図8】本発明の半導体装置の構成を説明する断面図。

【図9】本発明の半導体装置の構成を説明する回路図。

【図10】半導体装置の構成を説明する図。

【発明を実施するための形態】

【0023】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明

に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々

に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施

の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構

成において、同じものを指す符号は異なる図面間で共通して用いる。

(実施の形態1)

【0024】

本発明の半導体装置は、半導体回路部11、記憶回路部12、コイル状のアンテナ部1

3を有する。記憶回路部12は、複数の記憶素子を有する。複数の記憶素子の各々は、一

対の電極間に有機化合物を含む層が挟まれた構造を有する。複数の記憶素子が含む一対の

電極のうちの一方または両方は、複数の記憶素子で共通して用いられている。そのため、

複数の記憶素子が含む一対の電極のうちの一方は、占有面積が大きい導電層となってしま

う。そこで本発明は、記憶回路部12が含む占有面積の大きい導電層に、電磁誘導の影響

により電流が流れてしまうことを防止するため、記憶回路部12とコイル状のアンテナ部

13とを重なるように配置する。

【0025】

本発明の半導体装置の上面構造について説明する。以下の説明では、半導体回路部、記

憶回路部、コイル状のアンテナ部を有し、記憶回路部と、コイル状のアンテナ部が重なら

ない半導体装置(図1(C)参照)と比較して説明する。なお、図1(C)は比較例であ

って本発明ではない。図1(C)に示す半導体装置は、半導体回路部1201と記憶回路

部1202とアンテナ部1203とを有している。なお、半導体回路部1201の第1の

端子は、コイル状のアンテナ部1203の一方の端に電気的に接続されて、半導体回路部

1201の第2の端子は、コイル状のアンテナ部1203の他方の端に電気的に接続され

ている。また、半導体回路部1201と記憶回路部1202は電気的に接続されている。

【0026】

図1(C)の構成と比較して記憶回路部12の占有面積が同じであり、記憶回路部12

とコイル状のアンテナ部13とが重なるように配置する場合(図1(A)参照)、半導体

回路部11の占有面積を拡大することができる。半導体回路部11の占有面積を拡大する

ことができると、より複数の素子を設けることができるため、高機能な回路を提供するこ

とができる。なお、図1(A)に示すコイル状のアンテナ部13は、巻き数が5巻を越え

る例を示したが特に限定されず、2巻以上であればよい。なお、半導体回路部11の第1

の端子は、コイル状のアンテナ部13の一方の端に電気的に接続されて、半導体回路部1

1の第2の端子は、コイル状のアンテナ部13の他方の端に電気的に接続されている。ま

た、半導体回路部11と記憶回路部12は電気的に接続されている。

【0027】

図1(C)の構成と比較して半導体回路部11の面積が同じであり、記憶回路部12と

コイル状のアンテナ部13とが重なるように配置する場合(図1(B)参照)、記憶回路

部12の占有面積を拡大することができる。記憶回路部12の占有面積を拡大することが

できると、より複数の素子を設けることができるため、記憶容量が大きい回路を提供する

ことができる。図1(B)においても、半導体回路部11の第1の端子は、コイル状のア

ンテナ部13の一方の端に電気的に接続されて、半導体回路部11の第2の端子は、コイ

ル状のアンテナ部13の他方の端に電気的に接続されている。また、半導体回路部11と

記憶回路部12は電気的に接続されている。

【0028】

次に、上記構成を有する半導体装置の断面構造について説明する(図2参照)。図2に

示す断面構造は、図1(A)の半導体装置の上面構造の点Aから点Bの断面構造を示す図

である。

【0029】

本発明の半導体装置は、絶縁表面を有する基板100上に、下地用の絶縁層101と、

絶縁層101上に設けられた薄膜トランジスタ102〜105と、薄膜トランジスタ10

2〜105を覆う絶縁層106と、絶縁層106に設けられた開口部を介して、薄膜トラ

ンジスタ102〜105のソース又はドレインに接続された配線107〜114とを有す

る。

【0030】

また、配線107〜114を覆う絶縁層115と、絶縁層115に設けられた開口部を

介して、配線112、114に接続された導電層116、117と、導電層116、11

7を覆う絶縁層118と、絶縁層118に設けられた開口部を介して、導電層116、1

17に接続された有機化合物を含む層119、120と、有機化合物を含む層119、1

20に接続された導電層121を有する。また、導電層121を覆う絶縁層123と、絶

縁層123上に設けられた導電層124〜128、導電層124〜128を覆う絶縁層1

29を有する。

【0031】

上記の断面構造において、薄膜トランジスタ102、103を含む部分が、半導体回路

部11に相当する。また、導電層116、有機化合物を含む層119及び導電層121の

積層体が、記憶素子130に相当する。また、導電層117、有機化合物を含む層120

及び導電層121の積層体が、記憶素子131に相当する。記憶素子130、131を含

む回路が、記憶回路部12に相当する。また、導電層124〜128が、コイル状のアン

テナ部13に相当する。

【0032】

上記の構造のように、記憶回路部12が含む占有面積の大きい導電層121と、コイル

状のアンテナ部13が含む導電層124〜128とを重ねて配置することにより、電磁誘

導の影響により導電層121に電流が流れてしまうことを防止することができる。また、

記憶回路部12とコイル状のアンテナ部13とを積層して配置することにより、小型化を

実現することができる。

【0033】

次に、上記とは異なる構成の半導体装置の断面構造について説明する(図3参照)。半

導体装置は、絶縁表面を有する基板100上に、下地用の絶縁層101と、絶縁層101

上に設けられた薄膜トランジスタ102、103と、薄膜トランジスタ102、103を

覆う絶縁層106と、絶縁層106に設けられた開口部を介して、薄膜トランジスタ10

2、103のソース又はドレインに接続された配線107〜110とを有する。

【0034】

また、配線107〜110を覆う絶縁層115と、絶縁層115に設けられた開口部を

介して、配線110に接続された導電層145と、導電層145を覆う絶縁層118と、

絶縁層118に設けられた開口部を介して、導電層145に接続された有機化合物を含む

層147〜150と、有機化合物を含む層147〜150に接続された導電層146を有

する。また、導電層146を覆う絶縁層123と、絶縁層123上に設けられた導電層1

24〜128、導電層124〜128を覆う絶縁層129を有する。導電層145と、有

機化合物を含む層147〜150のいずれか一つと、導電層146の積層体が、記憶素子

141〜144に相当する。

【0035】

上記の構造のように、記憶回路部12が含む占有面積の大きい導電層145、146と

、コイル状のアンテナ部13が含む導電層124〜128とを重ねて配置することにより

、電磁誘導の影響により導電層121に電流が流れてしまうことを防止することができる

。また、記憶回路部12とコイル状のアンテナ部13とを積層して配置することにより、

小型化を実現することができる。

【0036】

(実施の形態2)

本実施の形態では、上記実施の形態1で示す記憶装置を有する半導体装置の一例に関して

さらなる詳細な図面を用いて説明する。本実施の形態の半導体装置の上面図を図8(A)

に示し、図8(A)における線X−Yの断面図を図8(B)に示す。

【0037】

図8(A)に示すように、基板400上に記憶素子を有する記憶装置である記憶素子部4

04、集積回路部421、アンテナ431が形成されている。図8(A)及び(B)は、

作製工程途中であり、作製条件に耐えうる基板400上に記憶素子部、回路部、及びアン

テナを形成した状態である。記憶装置に用いる材料及び作製工程は公知のものを用いれば

よい。

【0038】

基板400上に剥離層452、絶縁層453を介して記憶素子部404にはトランジス

タ441、集積回路部421にはトランジスタ442が設けられている。剥離層452と

しては、50nm〜200nmのタングステン膜を用い、絶縁層453としては酸化珪素

膜を用いる。ただし、剥離層はタングステン膜に限定されず、Mo膜やアモルファスシリ

コン膜などを用いてもよい。トランジスタ441及びトランジスタ442上に絶縁層45

1、絶縁層454、絶縁層455が形成されており、絶縁層455上に第1の導電層45

7d、有機化合物層458及び第2の導電層459の積層から構成される記憶素子443

が形成されている。隔壁として機能する絶縁層460bにより有機化合物層458は個々

に隔てられている。第1の導電層457dはトランジスタ441の配線層と接続しており

、記憶素子443は、トランジスタ441と電気的に接続している。

【0039】

第1の導電層457d及びトランジスタ441と、導電層457c及び配線層456a

と、導電層457e及び配線層456bとがそれぞれ接続するために絶縁層455に開口

(コンタクトホールとも言う)を形成する。開口を大きくし、導電層同士の接触面積を増

加した方がより低抵抗となるため、本実施の形態では、第1の導電層457dとトランジ

スタ441とが接続する開口が一番小さく、その次が導電層457cと配線層456aと

が接続する開口、導電層457eと配線層456bとが接続する開口が一番大きいという

ように順に開口を大きく設定している。本実施の形態では、第1の導電層457dとトラ

ンジスタ441とが接続する開口を5μm×5μm、導電層457cと配線層456aと

が接続する開口を50μm×50μm、導電層457eと配線層456bとが接続する開

口を500μm×500μmとしている。

【0040】

図8(B)における半導体装置では、第2の導電層459は、配線層456a、導電層

457cと積層して電気的に接続している。第2の導電層459は、第1の導電層457

dよりも電極面積が大きく、本発明では、この第2の導電層459とアンテナ431が重

なるように配置する。

【0041】

絶縁層455上に絶縁層461が形成されている。絶縁層461上には、導電層457a

とアンテナ431a、導電層457bとアンテナ431b、導電層457eとアンテナ4

31c、及び導電層457fとアンテナ431dとがそれぞれ積層して形成されている。

導電層457eは絶縁層461に形成された配線層462に達する開口を介して配線層4

62と接して形成されている。また、配線層462は、絶縁層455に形成された配線層

456bに達する開口を介して配線層456bと接して形成されている。なお、本明細書

では、このアンテナと、アンテナの下方の配線層との接続部分をアンテナの給電部と呼ぶ

。ここでは、配線層462と配線層456bを用いてアンテナと記憶素子部404及び集

積回路部421とを電気的に接続しているが、特にこの接続に限定されず、アンテナ43

1cと456bとが電気的に接続するような構造とすればよい。

【0042】

アンテナ431a、アンテナ431b、アンテナ431c、及び431d下の導電層45

7a、導電層457b、導電層457e、導電層457fは、絶縁層455とアンテナ4

31a、アンテナ431b、アンテナ431c、及び431dとの密着性を向上させる効

果もある。本実施の形態では、絶縁層455、及び絶縁層461にポリイミド膜を用い、

導電層457a、導電層457b、導電層457e、及び導電層457fにチタン膜を用

い、アンテナ431a、アンテナ431b、アンテナ431c、及び431dにアルミニ

ウム膜をそれぞれ用いている。

【0043】

集積回路部421は部分的に絶縁層460cが形成されており、トランジスタ442も

絶縁層460cに覆われていない領域と覆われている領域がある。

【0044】

ここで、本実施の形態における半導体装置の回路に関するブロック図を図9示す。図9

(A)における半導体装置のブロック図は、RF入力部401、ロジック回路部402、

外部入力部403、記憶素子部404、調整回路部405、ダイオード406、抵抗40

7を有している。なお、図8(A)に示した集積回路部421は、図9(A)のRF入力

部401、ロジック回路部402、外部入力部403、調整回路部405、ダイオード4

06、または抵抗407に相当する。

【0045】

外部入力端子から入力された電圧及び信号は、記憶素子部404に入力され、記憶素子

部404にデータ(情報)が書き込まれる。RF入力部401において、アンテナによっ

て交流信号を受信し信号及び電圧をロジック回路部402に入力する。ロジック回路部4

02を介して信号は制御信号となり、制御信号が記憶素子部404に入力されることで記

憶素子部404より書き込まれたデータが再び読み出される。

【0046】

図9(B)は、図9(A)の半導体装置と調整回路部405の構造が異なる例であり、

調整回路部405は抵抗で、調整回路部415はスイッチで構成されている。図9(B)

におけるブロック図は、RF入力部411、ロジック回路部412、外部入力部413、

記憶素子部414、調整回路部415、ダイオード416、抵抗417を有している。な

お、図8(A)に示した集積回路部421は、図9(B)のRF入力部411、ロジック

回路部412、外部入力部413、調整回路部415、ダイオード416、または抵抗4

17に相当する。

【0047】

また、抵抗407及び抵抗417はプルアップ回路であり、調整回路部として機能する。

調整回路部405は、記憶素子部404にデータを書き込み時に、ロジック回路部402

より不要な制御信号が記憶素子部404に入力されないように調整するものである。同様

に、抵抗407も、記憶素子部404にデータを書き込む時に、ロジック回路部402よ

り記憶素子部404に信号が入力されないように調整するものである。記憶素子部404

にデータを書き込む時は、ダイオード406により外部入力部403からの信号は遮断さ

れるが、記憶素子部404よりデータを読み取る時は、記憶素子部404のVDDHをR

F入力部401より印加されるVDDに固定し、安定させる。図9(A)のブロック図に

基づいて説明したが、図9(B)においても同様である。

【0048】

また、RF入力部401、411に電気的に接続されるアンテナは、記憶素子部を有す

る記憶装置に対して、重ねて設ける。また記憶装置の電極全面が重なってもよいし、一部

が重なっている構造でもよい。アンテナ部と記憶装置が重なる構造であると、アンテナが

交信する際に信号に載っているノイズ等や、電磁誘導により発生する起電力の変動等の影

響による、半導体装置の動作不良を減らすことが可能であり、信頼性が向上する。また、

半導体装置の省電力化が実現できる。また、半導体装置を小型化することもできる。

【0049】

本実施の形態で示す第1の導電層457d、有機化合物層458、及び第2の導電層4

59を有する記憶素子443は密着性が良いので、第1の基板(ガラス基板)である基板

400に形成された後に、第2の基板に転写される工程でかかる力によって、層界面で膜

剥がれなどの不良が生じない。よって良好な形状で記憶素子を剥離した後、紙やプラスチ

ック基板上に転写し、軽量、且つ、フレキシブルな記憶装置、または軽量、且つ、フレキ

シブルな半導体装置を作製することができる。

【0050】

本実施の形態で作製される記憶素子を有する記憶装置は密着性が良好なため、剥離工程

、及び転写工程を良好な状態で行うことができる。よって、自由に様々な基板に転写する

ことができるため、基板の材料の選択性の幅が広がる。また安価な材料を基板として選択

することもでき、用途に合わせて広い機能を持たせることができるだけでなく、低コスト

で記憶装置、半導体装置を作製することができる。

【0051】

本発明により、良好な状態で転写工程を行えるような密着性のよい記憶素子を有する記

憶装置を作製できる。よって、より高信頼性の記憶装置、及びその記憶装置を備えた半導

体装置を装置や工程を複雑化することなく、歩留まりよく作製することができる。

【0052】

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行う

こととする。

【実施例1】

【0053】

本発明の半導体装置が含む記憶回路部の構成について説明する(図4、5参照)。

【0054】

記憶回路部は、複数のビット線B1〜Bm(mは自然数)と、複数のワード線W1〜W

n(nは自然数)と、複数のメモリセル201とを含むメモリセルアレイ202を有する

。また、複数のビット線B1〜Bmを制御するデコーダ203と、複数のワード線W1〜

Wnを制御するデコーダ204と、セレクタ205と、読み出し書き込み回路206とを

有する。

【0055】

メモリセルアレイ202の構成には、アクティブマトリクス型とパッシブマトリクス型

とがある。メモリセルアレイ202がアクティブマトリクス型の場合、メモリセル201

は、トランジスタ215と、記憶素子207を含む(図4参照)。トランジスタ215の

ゲートはワード線Wb(1≦b≦n)に電気的に接続され、トランジスタ215のソース

又はドレインの一方はビット線Ba(1≦a≦m)に電気的に接続され、トランジスタ2

15のソース又はドレインの他方は記憶素子207が含む一対の電極の一方に電気的に接

続されている。

【0056】

また、メモリセルアレイ202がパッシブマトリクス型の場合、メモリセル201は、

ビット線Baとワード線Wbが交差する箇所に設けられた記憶素子207を含む(図5参

照)。

【0057】

次に、記憶回路部にデータの書き込みを行うときの動作について説明する。

【0058】

まず、電気的作用により、記憶回路部にデータの書き込みを行う場合について説明する

。最初に、デコーダ203、デコーダ204、セレクタ205により、メモリセル201

が選択される。次に、読み出し書き込み回路206により、選択されたメモリセル201

にデータが書き込まれる。具体的には、読み出し書き込み回路206により、選択された

メモリセル201が含む記憶素子に所定の電圧が印加されることにより、データが書き込

まれる。所定の電圧が印加されると、記憶素子の抵抗値は変化する。記憶素子の抵抗値の

変化には、抵抗値が大きくなる場合と、抵抗値が小さくなる場合があるが、データの書き

込みには、そのどちらの現象を用いてもよい。抵抗値が大きくなる現象は、記憶素子に所

定の電圧を印加して、一対の電極の間の有機化合物を含む層が高抵抗化する現象を利用し

たものである。また、抵抗値が小さくなる現象は、記憶素子に所定の電圧を印加して、一

対の電極間の距離を短くする現象を利用したものである。このように、記憶回路部は、電

気的作用により、記憶素子の抵抗値が変化することを利用して、データの書き込みを行う

。例えば、初期状態の記憶素子を「0」のデータとすると、「1」のデータを書き込む記

憶素子には電気的作用を印加する。

【0059】

次に、光学的作用によりデータの書き込みを行う場合について説明する。この場合、透

光性を有する導電層側から、光学照射装置(例えば、レーザ照射装置)により、有機化合

物を含む層に光を照射する。そうすると、光が照射された記憶素子にデータが書き込まれ

る。光が照射されることにより、記憶素子の抵抗値は変化する。記憶素子の抵抗値の変化

には、抵抗値が大きくなる場合と、抵抗値が小さくなる場合とがあるが、データの書き込

みには、そのどちらの現象を用いてもよい。このように、記憶回路部は、光学的作用によ

り、記憶素子の抵抗値が変化することを利用して、データの書き込みを行う。例えば、初

期状態の記憶素子を「0」のデータとすると、「1」のデータを書き込む記憶素子には、

光学的作用を印加する。

【0060】

次に、記憶回路部にデータの読み出しを行うときの動作について説明する。

【0061】

データの読み出しは、データの書き込みの方法にかかわらず、電気的作用により行われ

る。データの読み出しは、デコーダ203、204、セレクタ205、読み出し書き込み

回路206により、記憶素子の抵抗値の相違を読み出すことにより行われる。

【0062】

なお、記憶素子が含む一対の導電層の一方と、有機化合物を含む層との間に、整流性を

有する素子を設けてもよい。整流性を有する素子とは、ゲートとドレインを互いに電気的

に接続させたトランジスタ、ダイオード等である。整流性を有する素子を設けると、電流

の流れる方向を限定することができるため、データの読み出しの正確性を向上させること

ができる。

【0063】

次に、記憶素子が含む有機化合物を含む層に用いる材料について説明する。

【0064】

記憶素子に対するデータの書き込みを電気的作用により行う場合、有機化合物を含む層

には、低分子系材料、高分子系材料、シングレット材料、トリプレット材料などを用いる

とよい。また、有機化合物を含む層には、有機化合物材料のみからなるものだけでなく、

無機化合物を一部に含む材料を用いるとよい。また、有機化合物を含む層には、正孔注入

層、正孔輸送層、正孔阻止層、発光層、電子輸送層、電子注入層等が用いられるが、単層

で用いてもよいし、複数の層を積層させてもよい。なお、有機化合物を含む層は、インク

ジェット法に代表される液滴吐出法により形成するとよい。液滴吐出法を用いることによ

り、材料の利用効率の向上、作製工程の簡略化による作製時間の短縮、作製費用の低減を

実現することができる。

【0065】

また、記憶回路部に対するデータの書き込みを光学的作用により行う場合、有機化合物

を含む層には、光学的作用により性質が変化する材料を用いるとよい。例えば、光を吸収

することによって酸を発生する化合物(光酸発生剤)をドープした共役高分子を用いると

よい。共役高分子とは、ポリアセチレン類、ポリフェニレンビニレン類、ポリチオフェン

類、ポリアニリン類、ポリフェニレンエチニレン類等を用いるとよい。また、光酸発生剤

としては、アリールスルホニウム塩、アリールヨードニウム塩、o−ニトロベンジルトシ

レート、アリールスルホン酸p−ニトロベンジルエステル、スルホニルアセトフェノン類

、Fe−アレン錯体PF6塩等を用いるとよい。

【0066】

また、本発明の半導体装置が有する記憶装置は、不揮発性であってもよく、データの追

記を可能としてもよい。また、本発明の半導体装置が有する記憶装置は、外部からの電気

的作用によりデータの書き換えが可能なものとしてもよい。

【0067】

本実施例では、アンテナの面積サイズを約9mm×11mmとし、アンテナの巻き数を

9巻とし、アンテナ自体の線幅を150μmとし、10μmの間隔でアンテナの配線を巻

いている。このようにコイル状に巻かれたアンテナと重なるように記憶回路部の一方の電

極、即ち上部電極を配置する。この上部電極は、有機化合物を含む層の上方に設けられて

おり、複数の記憶素子に共通の電極となっている。1キロビットの情報量を有する記憶回

路を構成する場合、この上部電極の面積サイズは、1.5mm×3mm程度とすればよい

。なお、上部電極の面積サイズは特に限定されず、4.5mm2のサイズよりも小さくす

ることは可能である。

【0068】

アンテナと、占有面積の大きい導電層(上部電極:4.5mm2)とを重ねて配置するこ

とによって、アンテナと重なる領域に何も配置しないものに比べ、スペースを有効に利用

することができる。従って、半導体装置の小型化を実現することができる。

【0069】

また、占有面積の大きい上部電極とコイル状のアンテナ部とを積層して配置することに

より、記憶回路部が含む上部電極に電流が流れてしまうことを防止することができ、省電

力化を図ることができる。

【0070】

本実施例は、実施の形態1、または実施の形態2と自由に組み合わせることができる。

【実施例2】

【0071】

本発明の半導体装置が含む半導体回路部の構成について説明する(図6参照)。

【0072】

半導体回路部は、アナログ回路551とデジタル回路552とを有する。アナログ回路

551は、共振容量501、帯域フィルタ502、整流回路と保持容量を含む電源回路5

03、復調回路504、変調回路505等を有する。デジタル回路552は、コード抽出

回路506、クロック生成回路507、巡回冗長検査回路508、制御回路509、記憶

回路510等を有する。

【0073】

半導体装置がデータを受信する際の動作について説明する。コイル状のアンテナから入

力された無線信号(変調された搬送波)は、端子221aからアナログ回路551に入力

される。入力された無線信号は、帯域フィルタ502によって所望の周波数成分が取り出

され、電源回路503及び復調回路504に入力される。帯域フィルタ502を介して入

力された変調された搬送波は、電源回路503が含む整流回路によって整流され、更に、

電源回路503が含む保持容量によって平滑化される。こうして、電源回路503は直流

電圧を生成する。電源回路503において生成された直流電圧は電源電圧として、各回路

に供給される。

【0074】

また、帯域フィルタ502を介して入力された変調された搬送波は、デジタル回路55

2内のクロック生成回路507に入力される。クロック生成回路507で生成されたクロ

ックは各回路に供給される。帯域フィルタ502を介して入力された変調された搬送波は

、復調回路504によって復調され、復調された信号はデジタル回路552に入力される

。変調された搬送波を復調回路504によって復調した信号は、コード抽出回路506に

入力され、信号の有するコードが抽出される。コード抽出回路506の出力は、制御回路

509に入力され、コードが抽出される。抽出されたコードは、巡回冗長検査回路508

に入力され、送信エラーを識別するための演算処理が行われる。こうして、巡回冗長検査

回路508は受信データに誤りがあるか否かを制御回路509に出力する。

【0075】

次いで、半導体装置がデータを送信する際の動作について説明する。記憶回路510は

、制御回路509から入力される信号に応じて、記憶された固有識別子(UID)を制御

回路509に出力する。巡回冗長検査回路508は、送信データに対応するCRC符号を

計算し、制御回路509に出力する。制御回路509は送信データにCRC符号を付加す

る。また、制御回路509は、送信データにCRC符号が付加されたデータを符号化する

。更に、制御回路509は、符号化された情報を、所定の変調方式に対応して搬送波を変

調するための信号に変換する。制御回路509の出力は、アナログ回路551の変調回路

505に入力される。変調回路505は、入力された信号に応じて搬送波を負荷変調し、

コイル状のアンテナ部に出力する。

【0076】

本実施例は、実施の形態1、実施の形態2、または実施例1と自由に組み合わせること

ができる。

【実施例3】

【0077】

本実施例では、本発明の半導体装置の用途について説明する。本発明の半導体装置は、例

えば、紙幣、硬貨、有価証券、無記名債券類、証書類(運転免許証や住民票等)、包装用

容器類(包装紙やボトル等)、DVD(Digital Versatile Disc

)、ビデオテープ等の記録媒体、車、自転車等の乗物類、鞄や眼鏡等の身の回り品、食品

類、衣類、生活用品類、電子機器等に設けて使用することができる。電子機器とは、液晶

表示装置、EL(エレクトロルミネッセンス)表示装置、テレビジョン装置および携帯電

話機等を指す。

【0078】

本発明の半導体装置は、物品の表面に貼り付けたり、物品に埋め込んだりして物品に固

定することができる。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケージな

ら当該有機樹脂に埋め込んだりするとよい。紙幣、硬貨、有価証券類、無記名債券類、証

書類等に半導体装置を設けることにより、偽造を防止することができる。また、包装用容

器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に半導体装置を設

けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる

。また乗物類に半導体装置を設けることにより、偽造や盗難を防止することができる。ま

た、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことがで

きる。例えば、家畜等の生き物に半導体装置を埋め込むことによって、生まれた年や性別

または種類等を容易に識別することが可能となる。以上のように、本発明の半導体装置は

物品(生き物を含む)であればどのようなものにでも設けて使用することができる。

【0079】

次に、半導体装置を用いたシステムの一形態について、図7を用いて説明する。表示部

9521を含む端末9520には、アンテナ及び当該アンテナに接続されたリーダライタ

ーが設けられている。物品9532には本発明の半導体装置9531が設けられ、物品9

522には本発明の半導体装置9523が設けられている。物品9532が含む半導体装

置9531に端末9520のアンテナをかざすと、表示部9521に物品9532の原材

料や原産地、生産工程ごとの検査結果や流通過程の履歴、商品の説明等の商品に関する情

報が表示される。物品9522が含む半導体装置9523に端末9520のアンテナをか

ざすと、表示部9521に物品9522の原材料や原産地、生産工程ごとの検査結果や流

通過程の履歴、商品の説明等の商品に関する情報が表示される。

【0080】

本実施例は、実施の形態1、実施の形態2、実施例1、または実施例2と自由に組み合

わせることができる。

【符号の説明】

【0081】

11 半導体回路部

12 記憶回路部

13 コイル状のアンテナ部

100 基板

101 絶縁層

102〜105 薄膜トランジスタ

106 絶縁層

107〜114 配線

115 絶縁層

116 導電層

117 導電層

118 絶縁層

119 有機化合物を含む層

120 有機化合物を含む層

121 導電層

123 絶縁層

124〜128 導電層

129 絶縁層

130 記憶素子

131 記憶素子

141〜144 記憶素子

145 導電層

146 導電層

147〜149 有機化合物を含む層

150 有機化合物を含む層

201 メモリセル

202 メモリセルアレイ

203 デコーダ

204 デコーダ

205 セレクタ

206 読み出し書き込み回路

207 記憶素子

210 有機化合物を含む層

215 トランジスタ

221a 端子

301 半導体装置

302 コイル状のアンテナ部

303 半導体回路部

304 端子

305 一端

306 端子

307 他端

400 基板

401 RF入力部

402 ロジック回路部

403 外部入力部

404 記憶素子部

405 調整回路部

406 ダイオード

407 抵抗

411 RF入力部

412 ロジック回路部

413 外部入力部

414 記憶素子部

415 調整回路部

416 ダイオード

417 抵抗

421 集積回路部

431 アンテナ

431a アンテナ

431b アンテナ

431c アンテナ

431d アンテナ

441 トランジスタ

442 トランジスタ

443 記憶素子

451 絶縁層

452 剥離層

453 絶縁層

454 絶縁層

455 絶縁層

456a 配線層

456b 配線層

457a 導電層

457b 導電層

457c 導電層

457d 第1の導電層

457e 導電層

457f 導電層

458 有機化合物層

459 第2の導電層

460a 絶縁層

460b 絶縁層

460c 絶縁層

461 絶縁層

462 配線層

501 共振容量

502 フィルタ

503 電源回路

504 復調回路

505 変調回路

506 抽出回路

507 生成回路

508 巡回冗長検査回路

509 制御回路

510 記憶回路

551 アナログ回路

552 デジタル回路

1201 半導体回路部

1202 記憶回路部

1203 アンテナ部

9520 端末

9521 表示部

9522 物品

9523 半導体装置

9531 半導体装置

9532 物品

【特許請求の範囲】

【請求項1】

絶縁表面を有する基板上に、集積回路と、渦巻き状を主たる構成とするアンテナと、素子とを有し、

前記素子は、第1の電極と、第2の電極と、前記第1の電極と前記第2の電極の間に有機化合物を含む層とを有し、

前記アンテナは、前記集積回路と電気的に接続し、

前記第1の電極または前記第2の電極は、前記集積回路と電気的に接続し、

前記アンテナは、前記第2の電極と重なることを特徴とする半導体装置。

【請求項1】

絶縁表面を有する基板上に、集積回路と、渦巻き状を主たる構成とするアンテナと、素子とを有し、

前記素子は、第1の電極と、第2の電極と、前記第1の電極と前記第2の電極の間に有機化合物を含む層とを有し、

前記アンテナは、前記集積回路と電気的に接続し、

前記第1の電極または前記第2の電極は、前記集積回路と電気的に接続し、

前記アンテナは、前記第2の電極と重なることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−253370(P2012−253370A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2012−167872(P2012−167872)

【出願日】平成24年7月30日(2012.7.30)

【分割の表示】特願2007−17453(P2007−17453)の分割

【原出願日】平成19年1月29日(2007.1.29)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成24年7月30日(2012.7.30)

【分割の表示】特願2007−17453(P2007−17453)の分割

【原出願日】平成19年1月29日(2007.1.29)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]