半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路の微細化技術に関する。本明細書で開示する発明の中には、半導体集積回路を構成する要素としてシリコン半導体の他に化合物半導体によって構成される素子が含まれ、その一例として酸化物半導体を適用したものが開示される。

【背景技術】

【0002】

半導体記憶装置としてダイナミックRAM(DRAM)は良く知られた製品であり、今日においても各種電子機器の中で使われている。DRAMの中核部を構成するメモリセルは書き込み及び読み出し用のトランジスタとキャパシタによって構成されている。

【0003】

DRAMは、他の半導体集積回路と同様にスケーリング則に従って回路パターンの微細化が進められてきたが、デザインルールを100nm以下にすることは難しいと考えられていた時期もあった。その理由の一つとして、トランジスタのチャネル長が100nm以下となると、短チャネル効果によりパンチスルー電流が流れやすくなり、トランジスタがスイッチング素子として機能しなくなることが問題視されていた。もっとも、パンチスルー電流を防ぐにはシリコン基板に高濃度の不純物をドーピングすれば良いが、そうするとソースと基板間又はドレインと基板間に接合リーク電流が流れやすくなり、結局はメモリの保持特性を低下させてしまう原因となってしまい、この問題の解決策としては適切ではなかった。

【0004】

このような問題に対して、メモリセルを構成するトランジスタを3次元に形成し、一つのメモリセルが占める面積を縮小しつつトランジスタの実効的なチャネル長を短チャネル効果が生じない程度に維持する方法が考えられてきた。例えば、トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、その溝の壁面に沿ってゲート絶縁膜を形成し、さらにその溝にゲート電極を埋め込んだ構造である(非特許文献1参照)。

【0005】

このような構造をチャネル部に有するトランジスタは、ソース領域とドレイン領域の間を流れる電流が溝部分を回り込む形で流れるため実効的なチャネル長が長くなっている。このため、メモリセルに占めるトランジスタの占有面積を縮小しつつ、短チャネル効果を抑制できるといったメリットが得られていた。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】Kinam Kim、「Technology for sub−50nm DRAM and NAND Flash Manufacturing」、International Electron Devices Meeting, 2005. IEDM Technical Digest、2005年12月、p. 333 − 336

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【0008】

また、もう一つの課題として、記憶装置のメモリ容量を増加させる要求は強く、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【0009】

そこで本発明は、半導体記憶装置におけるデータ保持特性の改善を図ることのできる技術を提供することを目的の一とする。また、半導体記憶装置におけるデータ保持特性の改善を図りつつ、消費電力の低減を図ることのできる技術を提供することを目的の一とする。また、半導体装置におけるデータの保持特性の改善、及び消費電力の低減を図りつつ、半導体装置の面積縮小を図ることのできる技術を提供することを目的の一とする。

【課題を解決するための手段】

【0010】

上記課題を解決するために、酸化物半導体(OS:オキサイドセミコンダクター)を有するトランジスタ、特に、酸化物半導体を有するMOSトランジスタを用いて、回路、具体的には半導体記憶装置を構成する。その酸化物半導体は、実質的に真性な半導体である。そのため、オフ電流が非常に低いメリットを有する。

【0011】

従って、酸化物半導体を有するトランジスタを用いることによって、従来のDRAMよりも長い間隔でリフレッシュを行うことができ、消費電力の低減を実現できる。また、単位時間あたりのトランジスタのオン状態とオフ状態の切り換え回数が低減されるため、従来のDRAMよりもトランジスタの寿命を長くすることができる。

【0012】

また、酸化物半導体層を用いたトランジスタにおいても、トランジスタの微細化が進むと、短チャネル効果が発現する恐れがある。そこで、酸化物半導体層を用いた新規のトランジスタ構造を提案する。また、酸化物半導体層を用いた新規のトランジスタにより半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。より詳細には以下の通りである。

【0013】

本発明の一態様は、酸化物半導体以外の材料により形成された第1のトランジスタと、第1のトランジスタを含む周辺回路と、酸化物半導体により形成された第2のトランジスタと、第2のトランジスタと電気的に接続された容量素子と、第2のトランジスタと容量素子により形成された記憶素子と、を有し、第2のトランジスタは、絶縁層に第1のトレンチ及び第2のトレンチと、第1のトレンチの底面及び内壁面に接する酸化物半導体層と、酸化物半導体層上にゲート絶縁層と、ゲート絶縁層上にゲート電極と、第2のトレンチの底面及び内壁面上にゲート絶縁層と、第2のトレンチ内を充填する絶縁層と、酸化物半導体層に接するソース電極またはドレイン電極と、を有し、周辺回路の上に、記憶素子が積層されることを特徴とする半導体装置である。第1のトレンチは、ゲート電極用のトレンチであり、第2のトレンチは素子分離用のトレンチである。なお、第1のトレンチの上面形状は、ストライプ形状または棒状であり、第2のトレンチの上面形状は格子形状またはストライプ形状または棒状である。

【0014】

上記構成において、ゲート絶縁層は、酸化物半導体層の側面に接して覆っていてもよい。また、酸化物半導体層は、酸化物半導体層の表面に概略垂直なc軸を有している結晶を含んでいてもよい。また、酸化物半導体以外の材料は、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素を含んでいてもよい。

【0015】

また、上記酸化物半導体層の厚さは、1nm以上100nm以下が好ましく、上記酸化物半導体層は、結晶性酸化物半導体層としてもよい。結晶性酸化物半導体層とすることで、可視光や紫外光の照射よるトランジスタの電気的特性変化を抑制し、信頼性の高い半導体装置とすることができる。さらに、該結晶性酸化物半導体層は、単結晶構造ではなく、非晶質構造でもない構造であり、c軸配向を有した結晶(C Axis Aligned Crystal; CAACとも呼ぶ)を含む酸化物を有する。

【発明の効果】

【0016】

半導体記憶装置におけるデータ保持特性の改善を図ることのできる技術を提供することができる。

【0017】

また、半導体記憶装置におけるデータ保持特性の改善を図りつつ、消費電力の低減を図ることのできる技術を提供することができる。

【0018】

また、半導体装置におけるデータの保持特性の改善、及び消費電力の低減を図りつつ、半導体装置の面積縮小を図ることのできる技術を提供することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の一態様を示す断面図及び上面図である。

【図2】本発明の一態様を示す断面模式図である。

【図3】本発明の一態様を示す断面図および回路図である。

【図4】本発明の一態様を示す半導体装置の断面図である。

【図5】本発明の一態様を示す半導体装置の回路図、及び概念図である。

【図6】本発明の一態様を示す半導体装置の断面図である。

【図7】計算に用いた構造断面図と計算結果である。

【図8】計算に用いた構造断面図と計算結果である。

【図9】計算に用いた構造断面図と計算結果である。

【図10】半導体装置の回路図である。

【図11】半導体装置を用いた携帯機器を説明するための図である。

【図12】半導体装置を用いた携帯機器を説明するための図である。

【図13】半導体装置を用いた携帯機器を説明するための図である。

【図14】本発明の一態様に係る酸化物材料の構造を説明する図。

【図15】本発明の一態様に係る酸化物材料の構造を説明する図。

【図16】本発明の一態様に係る酸化物材料の構造を説明する図。

【図17】本発明の一態様を示す断面図である。

【発明を実施するための形態】

【0020】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0021】

(実施の形態1)

本実施の形態では、本発明の一態様であるトランジスタの構造および作製方法について、図1及び図2を用いて説明する。図1(A)はトランジスタ162のチャネル長方向の断面図の一例を示している。また、図1(B)はトランジスタ162とトランジスタ163の素子分離領域165に垂直な断面図の一例を示している。また、図1(C)はトランジスタ162とトランジスタ163の上面図の一例を示している。なお、図1(B)はトランジスタ162のチャネル幅方向の断面図の一部であり、図1(C)中の鎖線D1−D2で切断した断面に相当する。また、図1(A)は、図1(C)中の鎖線A1−A2で切断した断面に相当する。

【0022】

まず、半導体基板上に酸化膜からなる絶縁層130を形成する。そして絶縁層130に複数のトレンチ(溝とも呼ぶ)を形成する。そしてトレンチを覆うように酸化物半導体層144を形成する。トレンチの形成方法は公知の技術を用いればよく、本実施の形態では約0.4μmの深さのトレンチを形成する。また、本実施の形態では、ゲート電極用のトレンチを一回のエッチングまたは複数回のエッチングによって形成する。

【0023】

半導体基板としては、SOI基板、MOSFET構造のトランジスタを含む駆動回路が形成された半導体基板、容量が形成された半導体基板などを用いる。

【0024】

絶縁層130は、酸化物半導体層144と接するため、膜中(バルク中)に少なくとも化学量論的組成比を超える量の酸素が存在することが好ましい。例えば、絶縁層130として、酸化シリコン膜を用いる場合には、SiO2+α(ただし、α>0)とする。このような絶縁層130を用いることで、酸化物半導体層144に酸素を供給することができ、特性を良好にすることができる。

【0025】

酸化物半導体層144としては、膜厚は、1nm以上100nm以下とし、少なくともIn、Ga、Sn及びZnから選ばれた一種以上の元素を含有する。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0026】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0027】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属の酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する)、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0028】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0029】

また、In−Sn−Zn系酸化物は、用いるターゲットの組成比として、In:Sn:Znが原子数比で、1:2:2、2:1:3、1:1:1、または20:45:35などとなる酸化物ターゲットを用いる。

【0030】

また、酸化物半導体として、InMO3(ZnO)m(m>0、且つ、mは整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In3SnO5(ZnO)n(n>0、且つ、nは整数)で表記される材料を用いてもよい。

【0031】

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)、またはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子数比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。または、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)、またはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子数比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

【0032】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0033】

例えば、In−Sn−Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In−Ga−Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

【0034】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物の組成の近傍であるとは、a、b、cが、

(a―A)2+(b―B)2+(c―C)2≦r2

を満たすことをいい、rは、例えば、0.05とすればよい。他の酸化物でも同様である。

【0035】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0036】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0037】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0038】

なお、Raは、JIS B0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

【0039】

【数1】

【0040】

なお、上記において、S0は、測定面(座標(x1,y1)(x1,y2)(x2,y1)(x2,y2)で表される4点によって囲まれる長方形の領域)の面積を指し、Z0は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて評価可能である。

【0041】

酸化物半導体層144の材料として、Inを含み、c軸配向を有した結晶性酸化物半導体を用いることが好ましい。

【0042】

本実施の形態では、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる(c軸を中心に回転した)結晶(CAAC:C Axis Aligned Crystalともいう。)を含む酸化物について説明する。

【0043】

CAACを含む酸化物とは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物をいう。

【0044】

CAACは単結晶ではないが、非晶質のみから形成されているものでもない。また、CAACは結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

【0045】

CAACに酸素が含まれる場合、酸素の一部は窒素で置換されてもよい。また、CAACを構成する個々の結晶部分のc軸は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)に揃っていてもよい。または、CAACを構成する個々の結晶部分のab面の法線は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)を向いていてもよい。

【0046】

CAACは、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

【0047】

このようなCAACの例として、膜状に形成され、膜表面または支持する基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子(または窒素原子)の層状配列が認められる結晶を挙げることもできる。

【0048】

CAACに含まれる結晶構造の一例について図14乃至図16を用いて詳細に説明する。なお、特に断りがない限り、図14乃至図16は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図14において丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

【0049】

図14(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図14(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図14(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図14(A)に示す小グループは電荷が0である。

【0050】

図14(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図14(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図14(B)に示す構造をとりうる。図14(B)に示す小グループは電荷が0である。

【0051】

図14(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図14(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図14(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあってもよい。図14(C)に示す小グループは電荷が0である。

【0052】

図14(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図14(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図14(D)に示す小グループは電荷が+1となる。

【0053】

図14(E)に、2個のZnを含む小グループを示す。図14(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図14(E)に示す小グループは電荷が−1となる。

【0054】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

【0055】

ここで、これらの小グループ同士が結合する規則について説明する。図14(A)に示す6配位のInの上半分の3個のOは、下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Inを有する。図14(B)に示す5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。図14(C)に示す4配位のZnの上半分の1個のOは、下方向に1個の近接Znを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)、4配位の金属原子(Zn)のいずれかと結合することになる。

【0056】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0057】

図15(A)に、In−Sn−Zn−O系の層構造を構成する中グループのモデル図を示す。図15(B)に、3つの中グループで構成される大グループを示す。なお、図15(C)は、図15(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0058】

図15(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図15(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図15(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0059】

図15(A)において、In−Sn−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0060】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ−0.667、−0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷−1が必要となる。電荷−1をとる構造として、図14(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0061】

具体的には、図15(B)に示した大グループが繰り返されることで、In−Sn−Zn−O系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn−O系の層構造は、In2SnZn2O7(ZnO)m(mは0または自然数。)とする組成式で表すことができる。

【0062】

また、このほかにも、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物や、三元系金属の酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する。)、In−Al−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物や、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物や、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物や、In−Ga系酸化物などを用いた場合も同様である。

【0063】

例えば、図16(A)に、In−Ga−Zn−O系の層構造を構成する中グループのモデル図を示す。

【0064】

図16(A)において、In−Ga−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

【0065】

図16(B)に3つの中グループで構成される大グループを示す。なお、図16(C)は、図16(B)の層構造をc軸方向から観察した場合の原子配列を示している。

【0066】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0067】

また、In−Ga−Zn−O系の層構造を構成する中グループは、図16(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

【0068】

c軸配向を有した結晶性酸化物半導体を得る方法としては、三つ挙げられる。一つ目は、成膜温度を400℃以上450℃以下として酸化物半導体層144の成膜を行い、図2(A)に示す矢印の方向にc軸配向させる方法である。二つ目は、膜厚を薄く成膜した後、200℃以上700℃以下の加熱処理を行い、図2(B)に示す矢印の方向にc軸配向させる方法である。三つ目は、一層目の膜厚を薄く成膜した後、200℃以上700℃以下の加熱処理を行い、2層目の成膜を行い、図2(C)に示す矢印の方向にc軸配向させる方法である。

【0069】

図2(A)、図2(B)、及び図2(C)に示すように、いずれの方法であっても、酸化物半導体層144の表面の凹凸に対して垂直な方向に結晶成長が行われ、c軸配向した結晶性酸化物半導体を得ることができる。

【0070】

次いで、酸化物半導体層144に接し、ソース電極またはドレイン電極として機能する電極142a、142bを形成する。電極142a、電極142bは、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。

【0071】

また、電極142a、142bを保護するため、絶縁層143a、143bを形成する。次いで、CMP(化学的機械的研磨)などを用いて平坦化処理を行う。この平坦化処理の際、絶縁層143a、143bは、電極142a、142bを削らないためのバッファ層として機能する。

【0072】

次いで、チャネル長方向の素子分離用のトレンチと、チャネル幅方向の素子分離用のトレンチを形成する。これらの素子分離用のトレンチは、繋がった上面パターン形状としてもよいし、独立した上面パターン形状としてもよい。本実施の形態では、トレンチの形成によって酸化物半導体層の分離を行うため、図1(C)において、これらのトレンチのパターンは、繋がった上面パターン形状(格子状)としている。チャネル幅方向の素子分離用のトレンチの形成の際に、電極142aと電極142bの分離も行うことができる。なお、素子分離用のトレンチの形成のタイミングは、特に限定されない。また、素子分離用のトレンチの深さは、素子分離が十分行えるのであれば、ゲート電極用のトレンチと同じ底面の水平位置となる深さに限定されない。ゲート電極用トレンチよりも素子分離用のトレンチの底面の水平位置を深くすることで確実に素子分離を行うことができる。

【0073】

次いで、酸化物半導体層144の一部、ソース電極またはドレイン電極として機能する電極142a、142b、及び絶縁層143a、143bを覆うゲート絶縁層146を形成する。また、チャネル長方向の素子分離用のトレンチの内壁及び底面と、チャネル幅方向のトレンチの内壁及び底面にもゲート絶縁層146を成膜する。

【0074】

ゲート絶縁層146としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。ゲート絶縁層146は、酸化物半導体層144と接する部分において酸素を含むことが好ましい。特に、ゲート絶縁層146は、膜中(バルク中)に少なくとも化学量論的組成比を超える量の酸素が存在することが好ましく、例えば、ゲート絶縁層146として、酸化シリコン膜を用いる場合には、SiO2+α(ただし、α>0)とする。本実施の形態では、ゲート絶縁層146として、SiO2+α(ただし、α>0)である酸化シリコン膜を用いる。この酸化シリコン膜をゲート絶縁層146として用いることで、酸化物半導体層144に酸素を供給することができ、特性を良好にすることができる。さらに、ゲート絶縁層146は、作製するトランジスタのサイズやゲート絶縁層146の段差被覆性を考慮して形成することが好ましい。

【0075】

また、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSixOyNz(x>0、y>0、z>0))、ハフニウムアルミネート(HfAlxOy(x>0、y>0))、などのhigh−k材料を用いることでゲートリーク電流を低減できる。さらに、ゲート絶縁層146は、単層構造としても良いし、積層構造としても良い。なお、ゲート絶縁層の膜厚は、1nm以上100nm以下とする。

【0076】

そして、ゲート電極用のトレンチ内に充填されるように、ゲート電極148aをゲート絶縁層146上に形成する。ゲート電極148aの材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。ゲート電極148aは、単層構造としてもよいし、積層構造としてもよい。

【0077】

ゲート絶縁層146と接するゲート電極148aの一層として、窒素を含む金属酸化物、具体的には、窒素を含むIn−Ga−Zn−O膜や、窒素を含むIn−Sn−O膜や、窒素を含むIn−Ga−O膜や、窒素を含むIn−Zn−O膜や、窒素を含むSn−O膜や、窒素を含むIn−O膜や、金属窒化膜(InN、SnNなど)を用いる。これらの膜は5電子ボルト、好ましくは5.5電子ボルト以上の仕事関数を有し、ゲート電極として用いた場合、トランジスタの電気特性の一であるしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。

【0078】

ゲート電極用のトレンチ内にゲート電極148aを形成した段階で、トレンチ構造のトランジスタ162が形成される。

【0079】

次いで、ゲート電極148a、148bを覆う絶縁層149を形成する。絶縁層149は段差被覆性のよい絶縁膜を用いることが好ましい。絶縁層149の材料としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。本実施の形態では、絶縁層149の材料として酸化アルミニウム膜を用いる。図1(A)及び図1(B)においては、酸化物半導体層144の側面に接してゲート絶縁層146が形成され、さらに絶縁層149が形成される。なお、本実施の形態では、ゲート絶縁層146として、SiO2+α(ただし、α>0)である酸化シリコン膜を用い、絶縁層149として、酸化アルミニウム膜を用いる。従って、酸化アルミニウム膜が酸化シリコン膜を覆うことによって酸化シリコン膜中の酸素が拡散し、酸素が絶縁層149を通過しないようにブロックしている。

【0080】

絶縁層149を形成した後、素子分離用のトレンチを充填するための絶縁層150をCVD法などにより形成する。素子分離用のトレンチに絶縁層150を充填することによって素子分離領域161、165が形成される。なお、絶縁層150の形成前に、素子分離用のトレンチにはゲート絶縁層146、絶縁層149を積層させておくことで、絶縁層150を充填する領域を小さくし、絶縁層150の充填をスムーズに行うことができる。その後、CMPなどを用いて平坦化処理を行い、図1(A)及び図1(B)に示す構造を得ることができる。

【0081】

また、図1(B)に示すように、トランジスタ162のゲート電極148aと、隣り合うトランジスタ163のゲート電極148bとの間にも絶縁層150が充填され、ゲート電極同士の短絡防止が図られている。また、図1(A)に示すように、トランジスタ162のソース電極またはドレイン電極として機能する電極と、チャネル長方向に隣り合うトランジスタのソース電極またはドレイン電極として機能する電極との間にも絶縁層150が充填され、ソース電極またはドレイン電極の短絡防止も図られている。

【0082】

トランジスタのチャネルがトレンチの内壁に沿って形成され、チャネル形成領域が平坦でなくともキャリアの流れがCAACの酸化物半導体のIn−O−In−Oとスムーズに流れる。本実施の形態では、深さ0.4μmのトレンチ内壁に接して酸化物半導体層144を形成するため、チャネル長は約0.8μm以上となる。0.8μm以上のチャネル長とすることで、ノーマリーオフのトランジスタとすることができ、ショートチャネル効果も生じないようにすることができる。また、トレンチ構造を採用することで、トランジスタの平面面積を縮小できるため、高集積化が可能である。

【0083】

(実施の形態2)

図1に示すトランジスタ162を使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置の一例を図3、及び図17に示す。

【0084】

トランジスタ162は、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。

【0085】

図3(A)は、半導体装置の断面の一例を示している。

【0086】

図3(A)に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ160を有し、上部に第2の半導体材料を用いたトランジスタ162を有するものである。なお、トランジスタ162は、実施の形態1と同一であるため、図3(A)、(B)において図1(A)と同じ箇所は、同じ符号を用いて説明する。

【0087】

ここで、第1の半導体材料と第2の半導体材料とは異なる材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。また、本実施の形態においては、第1の半導体材料を用いたトランジスタを第1のトランジスタとし、第2の半導体材料を用いたトランジスタを第2のトランジスタとする。

【0088】

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、pチャネル型トランジスタを用いることができるのはいうまでもない。また、開示する発明の技術的な本質は、情報を保持するために酸化物半導体をトランジスタ162に用いる点にあるから、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

【0089】

図3(A)におけるトランジスタ160は、半導体材料(例えば、シリコンなど)を含む基板100に設けられたチャネル形成領域116と、チャネル形成領域116を挟むように設けられた不純物領域120と、不純物領域120に接する金属化合物領域124と、チャネル形成領域116上に設けられたゲート絶縁層108と、ゲート絶縁層108上に設けられたゲート電極110と、を有する。

【0090】

トランジスタ160の金属化合物領域124の一部には、電極126が接続されている。ここで、電極126は、トランジスタ160のソース電極やドレイン電極として機能する。また、基板100上にはトランジスタ160を囲むように素子分離絶縁層(図示しない)が設けられており、トランジスタ160を覆うように絶縁層130が設けられている。なお、高集積化を実現するためには、図3(A)に示すようにトランジスタ160がサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ160の特性を重視する場合には、ゲート電極110の側面にサイドウォール絶縁層を設け、不純物濃度が異なる領域を含む不純物領域120を設けても良い。

【0091】

図3(A)に示すようにトランジスタ162は、酸化物半導体層144を有するトレンチ構造のトランジスタである。

【0092】

ここで、酸化物半導体層144は水素などの不純物が十分に除去されることにより、または、十分な酸素が供給されることにより、高純度化されたものであることが望ましい。具体的には、例えば、酸化物半導体層144の水素濃度は5×1019atoms/cm3以下、望ましくは5×1018atoms/cm3以下、より望ましくは5×1017atoms/cm3以下とする。なお、上述の酸化物半導体層144中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectroscopy)で測定されるものである。このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠乏に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体層144では、キャリア濃度が1×1012/cm3未満、望ましくは、1×1011/cm3未満、より望ましくは1.45×1010/cm3未満となる。例えば、室温(25℃)でのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値)は100zA(1zA(ゼプトアンペア)は1×10−21A)以下、望ましくは10zA以下となる。このように、i型化(真性化)または実質的にi型化された酸化物半導体を用いることで、極めて優れたオフ電流特性のトランジスタ162を得ることができる。

【0093】

なお、図3(A)のトランジスタ162では、微細化に起因して素子間に生じるリークを抑制するために、素子分離領域161を設けている。さらに素子分離領域161に囲まれた領域よりも小さく島状に加工された酸化物半導体層144を用いているが、実施の形態1に示したように、素子分離用のトレンチを形成するまで島状に加工されていない構成を採用しても良い。酸化物半導体層144を島状に加工しない場合には、加工の際のエッチングによる酸化物半導体層144の汚染を防止できる。勿論、酸化物半導体層144を島状に加工しない場合には、工程数の削減も図ることができる。また、素子分離領域161に囲まれた領域よりも小さく島状に加工された酸化物半導体層144を用いる場合、素子分離用のトレンチの形成によって酸化物半導体層を分断する必要がないため、素子分離用のトレンチの底面の水平位置はゲート電極用のトレンチよりも浅くできる、または素子分離用のトレンチ形成のトータル面積を減らすことができる。

【0094】

トランジスタ162上には、絶縁層151が設けられており、絶縁層151上にはゲート電極148aと電気的に接続する電極153が設けられている。そして、電極153上には絶縁層152が設けられている。そして、ゲート絶縁層146、絶縁層150、絶縁層151、絶縁層152などに形成された開口には、電極154が設けられ、絶縁層152上には電極154と接続する配線156が形成される。なお、図3(A)では電極126および電極154を用いて、金属化合物領域124、電極142b、および配線156を接続しているが、開示する発明はこれに限定されない。例えば、電極142bを直接、金属化合物領域124に接触させても良い。または、配線156を直接、電極142bに接触させても良い。

【0095】

次に、図3(A)に対応する回路構成の一例を図3(B)に示す。なお、回路図においては、酸化物半導体を用いたトランジスタであることを示すために、OSの符号を併せて付す場合がある。

【0096】

図3(B)において、第1の配線(1st Line)とトランジスタ160のソース電極層とは、電気的に接続され、第2の配線(2nd Line)とトランジスタ160のドレイン電極層とは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ162のソース電極またはドレイン電極層の一方とは、電気的に接続され、第4の配線(4th Line)と、トランジスタ162のゲート電極層とは、電気的に接続されている。そして、トランジスタ160のゲート電極層と、トランジスタ162のソース電極層またはドレイン電極層の他方は、容量素子164の電極の一方と電気的に接続され、第5の配線(5th Line)と、容量素子164の電極の他方は電気的に接続されている。

【0097】

容量素子164は、トランジスタ160やトランジスタ162の作製プロセスと同じ工程で一対の電極と、その間に挟まれる誘電体となる絶縁層で形成することができる。トランジスタ162の作製プロセスと同じ工程で容量素子164を形成する一例を、図17に示す。図17に示す構成は、図3(A)に示す構成に容量素子164が追加されている。トランジスタ162を形成後、トランジスタ162の電極142aに達する開口部を形成し、その後、開口部を覆うように絶縁膜502を形成する。そして、絶縁膜502と接し、当該開口部を充填するように電極504形成することで、電極142aと、絶縁膜502と、電極504により容量素子164が形成される。なお、トランジスタ160やトランジスタ162の作製プロセスと同じ工程で形成することに限定されず、容量素子164の層を別途、トランジスタ162の上方に設けてもよい。例えば、トレンチ型の容量素子やスタック型の容量素子を別途、トランジスタの162の上方、または、トランジスタ160の下方に形成し、3次元的に積み重ねることで高集積化を図ってもよい。

【0098】

図3(B)に示す半導体装置の回路構成では、トランジスタ160のゲート電極層の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

【0099】

情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電位が、トランジスタ160のゲート電極層、および容量素子164に与えられる。すなわち、トランジスタ160のゲート電極層には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下Lowレベル電荷、Highレベル電荷という)のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位にして、トランジスタ162をオフ状態とすることにより、トランジスタ160のゲート電極層に与えられた電荷が保持される(保持)。次に情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、トランジスタ160のゲート電極層に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ160をnチャネル型とすると、トランジスタ160のゲート電極層にHighレベル電荷が与えられている場合の見かけのしきい値Vth_Hは、トランジスタ160のゲート電極層にLowレベル電荷が与えられている場合の見かけのしきい値Vth_Lより低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ160を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位をVth_HとVth_Lの中間の電位V0とすることにより、トランジスタ160のゲート電極層に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位がV0(>Vth_H)となれば、トランジスタ160は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位がV0(<Vth_L)となっても、トランジスタ160は「オフ状態」のままである。このため、第2の配線の電位を見ることで、保持されている情報を読み出すことができる。

【0100】

また、バックゲート電極をトランジスタ162に設けてもよく、バックゲート電極に電圧を印加することによってトランジスタ162のノーマリーオフ化を確実なものとすることが好ましい。

【0101】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0102】

(実施の形態3)

本実施の形態においては、図1に示すトランジスタ162を使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置について、実施の形態2に示した構成と異なる構成について図4を用いて説明を行う。

【0103】

図4に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ350を有し、上部に第2の半導体材料を用いたトランジスタ162を有するものである。なお、本実施の形態においては、下部に形成されたトランジスタ350は、第1のトランジスタとし、上部に形成されたトランジスタ162は、第2のトランジスタとする。また、上部、及び下部には、複数のトランジスタが形成されているが、代表的にトランジスタ350、及びトランジスタ162について、説明を行う。また、下部に形成されたトランジスタ350を含む複数のトランジスタは、半導体装置の周辺回路として機能し、上部に形成されたトランジスタ162を含む複数のトランジスタは、記憶素子として機能する。なお、線B1−B2で切断された図4は、トランジスタのチャネル長方向に垂直な断面図に相当する。

【0104】

ここで、第1の半導体材料と第2の半導体材料とは異なる材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

【0105】

なお、図4に示すように上部に第2の半導体材料を用いたトランジスタ162は、酸化物半導体層を有するトレンチ構造のトランジスタである。トランジスタ162は、先の実施の形態1、および実施の形態2に記載したトランジスタ162と同一であるため、図4において図1(A)と同じ箇所は、同じ符号を用いており、詳細な説明は省略する。

【0106】

ここでは、下部の第1の半導体材料を用いたトランジスタ350について、以下説明を行う。

【0107】

トランジスタ350は、半導体基板310、ゲート絶縁層314、半導体層316、導電層318、保護絶縁層320、サイドウォール絶縁層322、不純物領域324、及び絶縁層326により構成されている。なお、半導体層316、及び導電層318はゲート電極として機能し、不純物領域324は、ソース領域またはドレイン領域として機能する。

【0108】

また、トランジスタ350は、STI(Shallow Trench Isolation)領域312と隣接している。

【0109】

STI領域312としては、まず、半導体基板310の上の所望の領域に保護絶縁膜を形成し、エッチングを行うことでトレンチ(溝ともいう)が形成される。トレンチを形成した後、絶縁誘電体膜をトレンチに埋め込むことでSTI領域312を形成することができる。絶縁誘電体膜としては、酸化シリコン膜、窒化シリコン膜などを用いることができる。

【0110】

次に、トランジスタ350の詳細な説明を行う。トランジスタ350のゲート絶縁層314としては、STI領域312が形成された半導体基板310に、絶縁膜を形成した後、所望の位置にパターニング、エッチングを行い、半導体基板310にSTI領域312とは異なる深さのトレンチを形成する。その後、酸素雰囲気内にて加熱処理を行うことで、トレンチ内の半導体基板310が酸化され、ゲート絶縁層314を形成することができる。

【0111】

ゲート絶縁層314形成後に、LPCVD法などを用いて、シリコン膜を形成する。なお、該シリコン膜にn+、p+のドーピング処理、または加熱処理等を行い、所謂ポリシリコンとして導電性の高い半導体層を形成する。その後、該半導体層の上にスパッタリング法などにより、金属膜を成膜する。金属膜としては、タングステン、チタン、コバルト、ニッケル、または、タングステン、チタン、コバルト、ニッケルを含む合金膜、金属窒化膜、シリサイド膜などを適宜用いることができる。該金属膜上の所望の領域にパターニングを行い、エッチングすることで、導電層318が形成される。また、導電層318をマスクとして半導体層をエッチングすることで、半導体層316を形成することができる。なお、導電層318と半導体層316はトランジスタ350のゲート電極として機能する。

【0112】

次に、導電層318の上に、保護絶縁層320を形成する。保護絶縁層320としては、プラズマCVD法などを用い、酸化シリコン膜、窒化シリコン膜などを成膜し、所望の領域にパターニング、エッチング処理を行うことで形成することができる。

【0113】

次に、半導体基板310、および保護絶縁層320を覆うようにプラズマCVD法などにより、窒化シリコン膜を成膜し、エッチバックを行うことで、サイドウォール絶縁層322を形成することができる。

【0114】

次に、保護絶縁層320、及びサイドウォール絶縁層322をマスクとして、ドーピング処理を行うことで、不純物領域324を形成する。なお、ドーパントとしては、ボロンやリンなどを用いればよく、不純物領域324として用いるドーパントによりn+領域、p+領域など適宜形成することができる。なお、不純物領域324は、トランジスタ350のソース領域またはドレイン領域として機能する。

【0115】

次に、不純物領域324、保護絶縁層320、及びサイドウォール絶縁層322を覆うように絶縁層326を形成する。絶縁層326としては、プラズマCVD法などにより酸化シリコン膜などを用いて形成することができる。

【0116】

次に、絶縁層326の所望の領域に開口部を設け、不純物領域324と電気的に接続する接続電極325、及び接続電極331を形成する。なお、接続電極325、及び接続電極331形成後に、絶縁層326、接続電極325、および接続電極331の表面を平坦化させるCMP処理などを行ってもよい。

【0117】

次に、絶縁層326、接続電極325、及び接続電極331の上に、スパッタリング法などを用いて導電膜を成膜し、所望の領域にパターニングを行い、エッチングすることで、電極328、及び電極332を形成する。電極328、及び電極332に使用できる材料としては、タングステン、銅、チタンなど適宜用いることができる。

【0118】

次に、絶縁層326、電極328、及び電極332上に絶縁層329を形成する。絶縁層329としては、絶縁層326と同様の材料、及び手法により形成することができる。

【0119】

以上の工程により、第1の半導体材料を用いたトランジスタ350が形成された半導体基板310を形成することができる。

【0120】

次に、下部の第1の半導体材料を用いたトランジスタ350と、上部の第2の半導体材料を用いたトランジスタ162の接続関係について以下説明を行う。

【0121】

トランジスタ350は、不純物領域324と、接続電極325と、電極328と、接続電極330とにより、トランジスタ162と電気的に接続されている。また、他方では、不純物領域324と、接続電極331と、電極332と、接続電極334と、電極336と、接続電極338により、配線156と電気的に接続されている。

【0122】

また、トランジスタ350のゲート電極(すなわち、半導体層316、及び導電層318)は、トランジスタ162のソース電極と電気的に接続している。ただし、図4においては、トランジスタ350のゲート電極と、トランジスタ162のソース電極の接続は示されておらず、3次元方向で接続を行っている。

【0123】

以上のように、上部に形成された記憶素子は、酸化物半導体を用いたトランジスタにより形成されている。酸化物半導体を用いたトランジスタは、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、一方で周辺回路では、酸化物半導体以外の半導体材料が用いられている。酸化物半導体以外の半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、酸化物半導体以外の材料を用いたトランジスタにより、高速動作が要求される各種回路(論理回路、駆動回路など)を好適に実現することが可能である。

【0124】

このように、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた周辺回路と、酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路とを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。また、周辺回路と記憶回路を積層構造とすることにより、半導体装置の集積化を図ることができる。

【0125】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0126】

(実施の形態4)

本実施の形態においては、図1に示すトランジスタ162を使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置について、実施の形態2、及び実施の形態3に示した構成と異なる構成について、図5、及び図6を用いて説明を行う。

【0127】

図5(A)は、半導体装置の回路構成の一例を示し、図5(B)は半導体装置の一例を示す概念図である。まず、図5(A)に示す半導体装置について説明を行い、続けて図5(B)に示す半導体装置について、以下説明を行う。

【0128】

図5(A)に示す半導体装置において、ビット線BLとトランジスタ162のソース電極又はドレイン電極とは電気的に接続され、ワード線WLとトランジスタ162のゲート電極とは電気的に接続され、トランジスタ162のソース電極又はドレイン電極と容量素子254の第1の端子とは電気的に接続されている。

【0129】

酸化物半導体を用いたトランジスタ162は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ162をオフ状態とすることで、容量素子254の第1の端子の電位(あるいは、容量素子254に蓄積された電荷)を極めて長時間にわたって保持することが可能である。また、酸化物半導体を用いたトランジスタ162では、短チャネル効果が現れにくいというメリットもある。

【0130】

次に、図5(A)に示す半導体装置(メモリセル250)に、情報の書き込みおよび保持を行う場合について説明する。

【0131】

まず、ワード線WLの電位を、トランジスタ162がオン状態となる電位として、トランジスタ162をオン状態とする。これにより、ビット線BLの電位が、容量素子254の第1の端子に与えられる(書き込み)。その後、ワード線WLの電位を、トランジスタ162がオフ状態となる電位として、トランジスタ162をオフ状態とすることにより、容量素子254の第1の端子の電位が保持される(保持)。

【0132】

トランジスタ162のオフ電流は極めて小さいから、容量素子254の第1の端子の電位(あるいは容量素子に蓄積された電荷)は長時間にわたって保持することができる。

【0133】

次に、情報の読み出しについて説明する。トランジスタ162がオン状態となると、浮遊状態であるビット線BLと容量素子254とが導通し、ビット線BLと容量素子254の間で電荷が再分配される。その結果、ビット線BLの電位が変化する。ビット線BLの電位の変化量は、容量素子254の第1の端子の電位(あるいは容量素子254に蓄積された電荷)によって、異なる値をとる。

【0134】

例えば、容量素子254の第1の端子の電位をV、容量素子254の容量をC、ビット線BLが有する容量成分(以下、ビット線容量とも呼ぶ)をCB、電荷が再分配される前のビット線BLの電位をVB0とすると、電荷が再分配された後のビット線BLの電位は、(CB*VB0+C*V)/(CB+C)となる。従って、メモリセル250の状態として、容量素子254の第1の端子の電位がV1とV0(V1>V0)の2状態をとるとすると、電位V1を保持している場合のビット線BLの電位(=(CB*VB0+C*V1)/(CB+C))は、電位V0を保持している場合のビット線BLの電位(=(CB*VB0+C*V0)/(CB+C))よりも高くなることがわかる。

【0135】

そして、ビット線BLの電位を所定の電位と比較することで、情報を読み出すことができる。

【0136】

このように、図5(A)に示す半導体装置は、トランジスタ162のオフ電流が極めて小さいという特徴から、容量素子254に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。

【0137】

次に、図5(B)に示す半導体装置について、説明を行う。

【0138】

図5(B)に示す半導体装置は、上部に記憶素子として図5(A)に示したメモリセル250を複数有するメモリセルアレイ251、及び図5(A)に示したメモリセル250を複数有するメモリセルアレイ252を有し、下部に、メモリセルアレイ251、及びメモリセルアレイ252を動作させるために必要な周辺回路253を有する。なお、本実施の形態においてメモリセルアレイ252は、メモリセルアレイ251と周辺回路253の中部に位置しているが、周辺回路253に対しては、上部に位置しているため、メモリセルアレイ251、メモリセルアレイ252は、上部に位置しているとする。

【0139】

図5(B)に示した構成とすることにより、周辺回路253をメモリセルアレイ251、及びメモリセルアレイ252の直下に設けることができるため、且つ、メモリセルアレイ251とメモリセルアレイ252も積層構造とすることにより、半導体装置の小型化を図ることができる。

【0140】

次に、図5(B)に示した半導体装置の具体的な構成について図6を用いて説明を行う。

【0141】

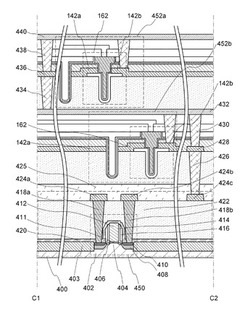

図6に示す半導体装置は、上部に多層に形成された記憶素子として、複数のメモリセル(メモリセル452a、及びメモリセル452b)を有し、下部に周辺回路400を有する。下部の周辺回路400は、第1の半導体材料を用いたトランジスタ450を有し、上部に多層に形成された複数のメモリセル(メモリセル452a、及びメモリセル452b)は、第2の半導体材料を用いたトランジスタ162を有するものである。また、トランジスタ162は、容量素子に接続されているが、3次元方向に接続されているために、図6には示されていない。なお、線C1−C2で切断された図6は、トランジスタのチャネル長方向に垂直な断面図に相当する。

【0142】

ここで、第1の半導体材料と第2の半導体材料とは異なる材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

【0143】

また、上部の第2の半導体材料を用いたトランジスタ162は、先の実施の形態1乃至実施の形態3に記載したトランジスタ162と同一であるため、図6において図1(A)と同じ箇所は、同じ符号を用いており、詳細な説明は省略する。ここでは、下部の第1の半導体材料を用いたトランジスタ450について、以下説明を行う。

【0144】

図6におけるトランジスタ450は、半導体材料(例えば、シリコンなど)を含む基板402に設けられたチャネル形成領域404と、チャネル形成領域404を挟むように設けられた不純物領域406および高濃度不純物領域408(これらをあわせて単に不純物領域とも呼ぶ)と、高濃度不純物領域408に接する金属化合物領域410と、チャネル形成領域404の上に設けられたゲート絶縁層411と、ゲート絶縁層411に接して設けられたゲート電極層412と、不純物領域と電気的に接続するソース電極またはドレイン電極418a、およびソース電極またはドレイン電極418bを有する。

【0145】

ここで、ゲート電極層412の側面にはサイドウォール絶縁層414が設けられている。また、基板402上にはトランジスタ450を囲むように素子分離絶縁層403が設けられており、トランジスタ450を覆うように、層間絶縁層420および層間絶縁層422が設けられている。ソース電極またはドレイン電極418a、およびソース電極またはドレイン電極418bは、層間絶縁層420および層間絶縁層422に形成された開口を通じて、金属化合物領域410と電気的に接続されている。つまり、ソース電極またはドレイン電極418a、およびソース電極またはドレイン電極418bは、金属化合物領域410を介して高濃度不純物領域408および不純物領域406と電気的に接続されている。なお、トランジスタ450の集積化などのため、サイドウォール絶縁層414が形成されない場合もある。また、層間絶縁層422の上に、トランジスタ450のソース電極またはドレイン電極418a、およびソース電極またはドレイン電極418bと、電気的に接続する電極424a、電極424b、及び電極424cを有し、層間絶縁層422、電極424a、電極424b、及び電極424cを覆う、絶縁層425により平坦化されている。

【0146】

電極424cは、接続電極426によって、電極428と電気的に接続されている。なお、電極428は、トランジスタ162のソース電極層及びドレイン電極層と同じ層にて形成されている。

【0147】

また、配線432は、接続電極430によって、電極428と電気的に接続されており、接続電極434によって、トランジスタ162のソース電極層及びドレイン電極層と同じ層で形成された電極436と電気的に接続されている。また、電極436は、接続電極438によって、配線440と電気的に接続されている。

【0148】

電極424c、配線432、及び配線440によって、メモリセル間の電気的接続や、周辺回路400とメモリセル(メモリセル452aと、メモリセル452b)との電気的接続等を行うことができる。

【0149】

なお、図6に示した半導体装置では、2つのメモリセル(メモリセル452aと、メモリセル452b)が積層された構成を例示したが、積層するメモリセルの数はこれに限定されない。3つ以上のメモリセルを積層する構成としても良い。

【0150】

また、図6に示した半導体装置では、メモリセル452aと、メモリセル452bと、周辺回路400との接続には、電極424c、電極428、配線432、電極436、及び配線440によって、接続する構成について例示したがこれに限定されない。メモリセル452a、メモリセル452b、及び周辺回路400との間には、二つ以上の配線層、及び電極が設けられる構成としてもよい。

【0151】

以上のように、上部に多層に形成された複数のメモリセルは、酸化物半導体を用いたトランジスタにより形成されている。酸化物半導体を用いたトランジスタは、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、一方で周辺回路では、酸化物半導体以外の半導体材料が用いられている。酸化物半導体以外の半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、酸化物半導体以外の材料を用いたトランジスタにより、高速動作が要求される各種回路(論理回路、駆動回路など)を好適に実現することが可能である。

【0152】

このように、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた周辺回路と、酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路とを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。また、周辺回路と記憶回路を積層構造とすることにより、半導体装置の集積化を図ることができる。

【0153】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0154】

(実施の形態5)

本実施の形態では、先の実施の形態で説明した半導体装置を携帯電話、スマートフォン、電子書籍などの携帯機器に応用した場合の例を図10乃至図13を用いて説明する。

【0155】

携帯電話、スマートフォン、電子書籍などの携帯機器においては、画像データの一時記憶などにSRAMまたはDRAMが使用されている。SRAMまたはDRAMは使用される理由としてはフラッシュメモリでは応答が遅く、画像処理では不向きであるためである。一方で、SRAMまたはDRAMを画像データの一時記憶に用いた場合以下の特徴がある。

【0156】

通常のSRAMは、図10(A)に示すように1つのメモリセルがトランジスタ801〜806の6個のトランジスタで構成されており、それをXデコーダー807、Yデコーダー808にて駆動している。トランジスタ803とトランジスタ805、トランジスタ804とトランジスタ806はインバータを構成し、高速駆動を可能としている。しかし1つのメモリセルが6トランジスタで構成されているため、セル面積が大きいという欠点がある。デザインルールの最小寸法をFとしたときにSRAMのメモリセル面積は通常100〜150F2である。このためSRAMはビットあたりの単価が各種メモリの中で最も高い。

【0157】

それに対して、DRAMはメモリセルが図10(B)に示すようにトランジスタ811、保持容量812によって構成され、それをXデコーダー813、Yデコーダー814にて駆動している。1つのセルが1トランジスタ1容量の構成になっており、面積が小さい。DRAMのメモリセル面積は通常10F2以下である。ただし、DRAMは常にリフレッシュが必要であり、書き換えをおこなわない場合でも電力を消費する。

【0158】

しかし、先の実施の形態で説明した半導体装置のメモリセル面積は、10F2前後であり、且つ頻繁なリフレッシュは不要である。したがって、メモリセル面積が縮小され、且つ消費電力が低減することができる。

【0159】

次に、図11は携帯機器のブロック図である。図11に示す携帯機器はRF回路901、アナログベースバンド回路902、デジタルベースバンド回路903、バッテリー904、電源回路905、アプリケーションプロセッサ906、フラッシュメモリ910、ディスプレイコントローラ911、メモリ回路912、ディスプレイ913、タッチセンサ919、音声回路917、キーボード918などより構成されている。ディスプレイ913は表示部914、ソースドライバ915、ゲートドライバ916によって構成されている。アプリケーションプロセッサ906はCPU907、DSP908、インターフェイス909(IF909)を有している。一般にメモリ回路912はSRAMまたはDRAMで構成されており、この部分に先の実施の形態で説明した半導体装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

【0160】

次に、図12はディスプレイのメモリ回路950に先の実施の形態で説明した半導体装置を使用した例である。図12に示すメモリ回路950は、メモリ952、メモリ953、スイッチ954、スイッチ955およびメモリコントローラ951により構成されている。また、メモリ回路950は、信号線から入力された画像データ(入力画像データ)、メモリ952、及びメモリ953に記憶されたデータ(記憶画像データ)を読み出し、及び制御を行うディスプレイコントローラ956と、ディスプレイコントローラ956からの信号により表示するディスプレイ957が接続されている。

【0161】

まず、ある画像データがアプリケーションプロセッサ(図示しない)によって、形成される(入力画像データA)。入力画像データAは、スイッチ954を介してメモリ952に記憶される。そしてメモリ952に記憶された画像データ(記憶画像データA)は、スイッチ955、及びディスプレイコントローラ956を介してディスプレイ957に送られ、表示される。

【0162】

入力画像データAに変更が無い場合、記憶画像データAは、通常30〜60Hz程度の周期でメモリ952からスイッチ955を介して、ディスプレイコントローラ956により読み出される。

【0163】

次に、例えばユーザーが画面を書き換える操作をしたとき(すなわち、入力画像データAに変更が有る場合)、アプリケーションプロセッサは新たな画像データ(入力画像データB)を形成する。入力画像データBはスイッチ954を介してメモリ953に記憶される。この間も定期的にメモリ952からスイッチ955を介して記憶画像データAは読み出されている。メモリ953に新たな画像データ(記憶画像データB)が記憶し終わると、ディスプレイ957の次のフレームより、記憶画像データBは読み出され、スイッチ955、及びディスプレイコントローラ956を介して、ディスプレイ957に記憶画像データBが送られ、表示がおこなわれる。この読み出しはさらに次に新たな画像データがメモリ952に記憶されるまで継続される。

【0164】

このようにメモリ952、及びメモリ953は交互に画像データの書き込みと、画像データの読み出しを行うことによって、ディスプレイ957の表示をおこなう。なお、メモリ952、及びメモリ953はそれぞれ別のメモリには限定されず、1つのメモリを分割して使用してもよい。先の実施の形態で説明した半導体装置をメモリ952、及びメモリ953に採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

【0165】

次に、図13は電子書籍のブロック図である。図13はバッテリー1001、電源回路1002、マイクロプロセッサ1003、フラッシュメモリ1004、音声回路1005、キーボード1006、メモリ回路1007、タッチパネル1008、ディスプレイ1009、ディスプレイコントローラ1010によって構成される。

【0166】

ここでは、図13のメモリ回路1007に先の実施の形態で説明した半導体装置を使用することができる。メモリ回路1007は書籍の内容を一時的に保持する機能を持つ。機能の例としては、ユーザーがハイライト機能を使用する場合などがある。ユーザーが電子書籍を読んでいるときに、特定の箇所にマーキングをしたい場合がある。このマーキング機能をハイライト機能と言い、表示の色を変える、アンダーラインを引く、文字を太くする、文字の書体を変えるなどによって、周囲との違いを示すことである。ユーザーが指定した箇所の情報を記憶し、保持する機能である。この情報を長期に保存する場合にはフラッシュメモリ1004にコピーしても良い。このような場合においても、先の実施の形態で説明した半導体装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

【0167】

以上のように、本実施の形態に示す携帯機器には、先の実施の形態に係る半導体装置が搭載されている。このため、読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力を低減した携帯機器が実現される。

【0168】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【実施例1】

【0169】

本実施例では、実施の形態1に示すトレンチ構造のトランジスタに短チャネル効果が発現するかを確認するため、計算を行った。図7乃至図9に計算に用いた構造、及び計算結果を示す。なお、図7乃至図9において、ゲート絶縁層がSiOx、酸化物半導体層がOS、ゲート電極がGate、ソース電極、及びドレイン電極がS/D、とそれぞれ付記してある。

【0170】

なお、計算にはシノプシス社製デバイスシミュレーションソフトSentaurus Deviceを使用した。

【0171】

図7(A)に計算に用いた構造および個々のサイズを示す。ゲート絶縁層の膜厚を5nm、酸化物半導体層の膜厚を5nmとし、ゲート電極用のトレンチの深さを0.4μmと設定する。図7(A)は、トレンチの底部の長さ(チャネル長方向の長さ)が90nm、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)が110nmであるトレンチ構造のトランジスタである。酸化物半導体層の材料は、In−Ga−Zn−O系酸化物半導体(バンドギャップ3.15eV、電子親和力4.6eV、電子移動度10cm2/Vs)を用い、酸化物半導体層に接する電極(ソース電極とドレイン電極)の仕事関数を4.6eV、ゲート電極の仕事関数を5.5eVとする。このトレンチ構造のトランジスタのVg−Id特性(Vds=1V、温度27℃)を計算した結果が図7(B)である。

【0172】

また、図8(A)は、トレンチの底部の長さ(チャネル長方向の長さ)が60nm、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)が80nmであるトレンチ構造のトランジスタである。トレンチの底部の長さとソース電極とドレイン電極の間隔以外は図7(B)と同じ条件で計算した結果が図8(B)である。

【0173】

また、図9(A)は、トレンチの底部の長さ(チャネル長方向の長さ)が30nm、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)が50nmであるトレンチ構造のトランジスタである。トレンチの底部の長さとソース電極とドレイン電極の間隔以外は図7(B)と同じ条件で計算した結果が図9(B)である。

【0174】

計算の結果、図7(A)、図8(A)、及び図9(A)の構造全てのトランジスタ特性は、ほぼ同等であった。それぞれのトランジスタのしきい値(Vth)は、0.8V、S値は60mV/decと良好な値を示した。

【0175】

これらの計算結果から、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)を30nmまで狭めても、しきい値のマイナスシフトやS値の増大といった短チャネル効果は発現せず、良好なトランジスタ特性を示している。

【0176】

比較のため、トレンチ構造ではなく、プレナー型のトランジスタの構造を用いて同様の計算を行ったところ、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)を狭めると、チャネル長も狭くなり、しきい値のマイナスシフトやS値の増大といった短チャネル効果が発現し、さらにはゲートに負のバイアスを印加したときのリーク電流(オフ電流)の増大も確認された。

【0177】

この比較のための計算結果と比べ、図7(B)、図8(B)、及び図9(B)の計算結果は、良好であり、実施の形態1に示すトランジスタ構造とすることでソース電極とドレイン電極の間隔(チャネル長方向の長さ)を狭めても実効的なチャネル長の変化は少ないため、短チャネル効果は発現せず、オフ電流を低く抑えることができる。その結果、保持特性が良好なメモリセルを作ることが可能になる。

【符号の説明】

【0178】

100 基板

108 ゲート絶縁層

110 ゲート電極

116 チャネル形成領域

120 不純物領域

124 金属化合物領域

126 電極

130 絶縁層

142a 電極

142b 電極

143a 絶縁層

143b 絶縁層

144 酸化物半導体層

146 ゲート絶縁層

148a ゲート電極

148b ゲート電極

149 絶縁層

150 絶縁層

151 絶縁層

152 絶縁層

153 電極

154 電極

156 配線

160 トランジスタ

161 素子分離領域

162 トランジスタ

163 トランジスタ

164 容量素子

165 素子分離領域

250 メモリセル

251 メモリセルアレイ

252 メモリセルアレイ

253 周辺回路

254 容量素子

310 半導体基板

312 STI領域

314 ゲート絶縁層

316 半導体層

318 導電層

320 保護絶縁層

322 サイドウォール絶縁層

324 不純物領域

325 接続電極

326 絶縁層

328 電極

329 絶縁層

330 接続電極

331 接続電極

332 電極

334 接続電極

336 電極

338 接続電極

350 トランジスタ

400 周辺回路

402 基板

403 素子分離絶縁層

404 チャネル形成領域

406 不純物領域

408 高濃度不純物領域

410 金属化合物領域

411 ゲート絶縁層

412 ゲート電極層

414 サイドウォール絶縁層

418a ドレイン電極

418b ドレイン電極

420 層間絶縁層

422 層間絶縁層

424a 電極

424b 電極

424c 電極

425 絶縁層

426 接続電極

428 電極

430 接続電極

432 配線

434 接続電極

436 電極

438 接続電極

440 配線

450 トランジスタ

452a メモリセル

452b メモリセル

502 絶縁膜

504 電極

801 トランジスタ

803 トランジスタ

804 トランジスタ

805 トランジスタ

806 トランジスタ

807 Xデコーダー

808 Yデコーダー

811 トランジスタ

812 保持容量

813 Xデコーダー

814 Yデコーダー

901 RF回路

902 アナログベースバンド回路

903 デジタルベースバンド回路

904 バッテリー

905 電源回路

906 アプリケーションプロセッサ

907 CPU

908 DSP

909 インターフェイス

910 フラッシュメモリ

911 ディスプレイコントローラ

912 メモリ回路

913 ディスプレイ

914 表示部

915 ソースドライバ

916 ゲートドライバ

917 音声回路

918 キーボード

919 タッチセンサ

950 メモリ回路

951 メモリコントローラ

952 メモリ

953 メモリ

954 スイッチ

955 スイッチ

956 ディスプレイコントローラ

957 ディスプレイ

1001 バッテリー

1002 電源回路

1003 マイクロプロセッサ

1004 フラッシュメモリ

1005 音声回路

1006 キーボード

1007 メモリ回路

1008 タッチパネル

1009 ディスプレイ

1010 ディスプレイコントローラ

【技術分野】

【0001】

本発明は、半導体集積回路の微細化技術に関する。本明細書で開示する発明の中には、半導体集積回路を構成する要素としてシリコン半導体の他に化合物半導体によって構成される素子が含まれ、その一例として酸化物半導体を適用したものが開示される。

【背景技術】

【0002】

半導体記憶装置としてダイナミックRAM(DRAM)は良く知られた製品であり、今日においても各種電子機器の中で使われている。DRAMの中核部を構成するメモリセルは書き込み及び読み出し用のトランジスタとキャパシタによって構成されている。

【0003】

DRAMは、他の半導体集積回路と同様にスケーリング則に従って回路パターンの微細化が進められてきたが、デザインルールを100nm以下にすることは難しいと考えられていた時期もあった。その理由の一つとして、トランジスタのチャネル長が100nm以下となると、短チャネル効果によりパンチスルー電流が流れやすくなり、トランジスタがスイッチング素子として機能しなくなることが問題視されていた。もっとも、パンチスルー電流を防ぐにはシリコン基板に高濃度の不純物をドーピングすれば良いが、そうするとソースと基板間又はドレインと基板間に接合リーク電流が流れやすくなり、結局はメモリの保持特性を低下させてしまう原因となってしまい、この問題の解決策としては適切ではなかった。

【0004】

このような問題に対して、メモリセルを構成するトランジスタを3次元に形成し、一つのメモリセルが占める面積を縮小しつつトランジスタの実効的なチャネル長を短チャネル効果が生じない程度に維持する方法が考えられてきた。例えば、トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、その溝の壁面に沿ってゲート絶縁膜を形成し、さらにその溝にゲート電極を埋め込んだ構造である(非特許文献1参照)。

【0005】

このような構造をチャネル部に有するトランジスタは、ソース領域とドレイン領域の間を流れる電流が溝部分を回り込む形で流れるため実効的なチャネル長が長くなっている。このため、メモリセルに占めるトランジスタの占有面積を縮小しつつ、短チャネル効果を抑制できるといったメリットが得られていた。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】Kinam Kim、「Technology for sub−50nm DRAM and NAND Flash Manufacturing」、International Electron Devices Meeting, 2005. IEDM Technical Digest、2005年12月、p. 333 − 336

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【0008】

また、もう一つの課題として、記憶装置のメモリ容量を増加させる要求は強く、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【0009】

そこで本発明は、半導体記憶装置におけるデータ保持特性の改善を図ることのできる技術を提供することを目的の一とする。また、半導体記憶装置におけるデータ保持特性の改善を図りつつ、消費電力の低減を図ることのできる技術を提供することを目的の一とする。また、半導体装置におけるデータの保持特性の改善、及び消費電力の低減を図りつつ、半導体装置の面積縮小を図ることのできる技術を提供することを目的の一とする。

【課題を解決するための手段】

【0010】

上記課題を解決するために、酸化物半導体(OS:オキサイドセミコンダクター)を有するトランジスタ、特に、酸化物半導体を有するMOSトランジスタを用いて、回路、具体的には半導体記憶装置を構成する。その酸化物半導体は、実質的に真性な半導体である。そのため、オフ電流が非常に低いメリットを有する。

【0011】

従って、酸化物半導体を有するトランジスタを用いることによって、従来のDRAMよりも長い間隔でリフレッシュを行うことができ、消費電力の低減を実現できる。また、単位時間あたりのトランジスタのオン状態とオフ状態の切り換え回数が低減されるため、従来のDRAMよりもトランジスタの寿命を長くすることができる。

【0012】

また、酸化物半導体層を用いたトランジスタにおいても、トランジスタの微細化が進むと、短チャネル効果が発現する恐れがある。そこで、酸化物半導体層を用いた新規のトランジスタ構造を提案する。また、酸化物半導体層を用いた新規のトランジスタにより半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。より詳細には以下の通りである。

【0013】

本発明の一態様は、酸化物半導体以外の材料により形成された第1のトランジスタと、第1のトランジスタを含む周辺回路と、酸化物半導体により形成された第2のトランジスタと、第2のトランジスタと電気的に接続された容量素子と、第2のトランジスタと容量素子により形成された記憶素子と、を有し、第2のトランジスタは、絶縁層に第1のトレンチ及び第2のトレンチと、第1のトレンチの底面及び内壁面に接する酸化物半導体層と、酸化物半導体層上にゲート絶縁層と、ゲート絶縁層上にゲート電極と、第2のトレンチの底面及び内壁面上にゲート絶縁層と、第2のトレンチ内を充填する絶縁層と、酸化物半導体層に接するソース電極またはドレイン電極と、を有し、周辺回路の上に、記憶素子が積層されることを特徴とする半導体装置である。第1のトレンチは、ゲート電極用のトレンチであり、第2のトレンチは素子分離用のトレンチである。なお、第1のトレンチの上面形状は、ストライプ形状または棒状であり、第2のトレンチの上面形状は格子形状またはストライプ形状または棒状である。

【0014】

上記構成において、ゲート絶縁層は、酸化物半導体層の側面に接して覆っていてもよい。また、酸化物半導体層は、酸化物半導体層の表面に概略垂直なc軸を有している結晶を含んでいてもよい。また、酸化物半導体以外の材料は、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素を含んでいてもよい。

【0015】

また、上記酸化物半導体層の厚さは、1nm以上100nm以下が好ましく、上記酸化物半導体層は、結晶性酸化物半導体層としてもよい。結晶性酸化物半導体層とすることで、可視光や紫外光の照射よるトランジスタの電気的特性変化を抑制し、信頼性の高い半導体装置とすることができる。さらに、該結晶性酸化物半導体層は、単結晶構造ではなく、非晶質構造でもない構造であり、c軸配向を有した結晶(C Axis Aligned Crystal; CAACとも呼ぶ)を含む酸化物を有する。

【発明の効果】

【0016】

半導体記憶装置におけるデータ保持特性の改善を図ることのできる技術を提供することができる。

【0017】

また、半導体記憶装置におけるデータ保持特性の改善を図りつつ、消費電力の低減を図ることのできる技術を提供することができる。

【0018】

また、半導体装置におけるデータの保持特性の改善、及び消費電力の低減を図りつつ、半導体装置の面積縮小を図ることのできる技術を提供することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の一態様を示す断面図及び上面図である。

【図2】本発明の一態様を示す断面模式図である。

【図3】本発明の一態様を示す断面図および回路図である。

【図4】本発明の一態様を示す半導体装置の断面図である。

【図5】本発明の一態様を示す半導体装置の回路図、及び概念図である。

【図6】本発明の一態様を示す半導体装置の断面図である。

【図7】計算に用いた構造断面図と計算結果である。

【図8】計算に用いた構造断面図と計算結果である。

【図9】計算に用いた構造断面図と計算結果である。

【図10】半導体装置の回路図である。

【図11】半導体装置を用いた携帯機器を説明するための図である。

【図12】半導体装置を用いた携帯機器を説明するための図である。

【図13】半導体装置を用いた携帯機器を説明するための図である。

【図14】本発明の一態様に係る酸化物材料の構造を説明する図。

【図15】本発明の一態様に係る酸化物材料の構造を説明する図。

【図16】本発明の一態様に係る酸化物材料の構造を説明する図。

【図17】本発明の一態様を示す断面図である。

【発明を実施するための形態】

【0020】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0021】

(実施の形態1)

本実施の形態では、本発明の一態様であるトランジスタの構造および作製方法について、図1及び図2を用いて説明する。図1(A)はトランジスタ162のチャネル長方向の断面図の一例を示している。また、図1(B)はトランジスタ162とトランジスタ163の素子分離領域165に垂直な断面図の一例を示している。また、図1(C)はトランジスタ162とトランジスタ163の上面図の一例を示している。なお、図1(B)はトランジスタ162のチャネル幅方向の断面図の一部であり、図1(C)中の鎖線D1−D2で切断した断面に相当する。また、図1(A)は、図1(C)中の鎖線A1−A2で切断した断面に相当する。

【0022】

まず、半導体基板上に酸化膜からなる絶縁層130を形成する。そして絶縁層130に複数のトレンチ(溝とも呼ぶ)を形成する。そしてトレンチを覆うように酸化物半導体層144を形成する。トレンチの形成方法は公知の技術を用いればよく、本実施の形態では約0.4μmの深さのトレンチを形成する。また、本実施の形態では、ゲート電極用のトレンチを一回のエッチングまたは複数回のエッチングによって形成する。

【0023】

半導体基板としては、SOI基板、MOSFET構造のトランジスタを含む駆動回路が形成された半導体基板、容量が形成された半導体基板などを用いる。

【0024】

絶縁層130は、酸化物半導体層144と接するため、膜中(バルク中)に少なくとも化学量論的組成比を超える量の酸素が存在することが好ましい。例えば、絶縁層130として、酸化シリコン膜を用いる場合には、SiO2+α(ただし、α>0)とする。このような絶縁層130を用いることで、酸化物半導体層144に酸素を供給することができ、特性を良好にすることができる。

【0025】

酸化物半導体層144としては、膜厚は、1nm以上100nm以下とし、少なくともIn、Ga、Sn及びZnから選ばれた一種以上の元素を含有する。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0026】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0027】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属の酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する)、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0028】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0029】

また、In−Sn−Zn系酸化物は、用いるターゲットの組成比として、In:Sn:Znが原子数比で、1:2:2、2:1:3、1:1:1、または20:45:35などとなる酸化物ターゲットを用いる。

【0030】

また、酸化物半導体として、InMO3(ZnO)m(m>0、且つ、mは整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In3SnO5(ZnO)n(n>0、且つ、nは整数)で表記される材料を用いてもよい。

【0031】

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)、またはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子数比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。または、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)、またはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子数比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

【0032】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0033】

例えば、In−Sn−Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In−Ga−Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

【0034】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物の組成の近傍であるとは、a、b、cが、

(a―A)2+(b―B)2+(c―C)2≦r2

を満たすことをいい、rは、例えば、0.05とすればよい。他の酸化物でも同様である。

【0035】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0036】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0037】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0038】

なお、Raは、JIS B0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

【0039】

【数1】

【0040】

なお、上記において、S0は、測定面(座標(x1,y1)(x1,y2)(x2,y1)(x2,y2)で表される4点によって囲まれる長方形の領域)の面積を指し、Z0は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて評価可能である。

【0041】

酸化物半導体層144の材料として、Inを含み、c軸配向を有した結晶性酸化物半導体を用いることが好ましい。

【0042】

本実施の形態では、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる(c軸を中心に回転した)結晶(CAAC:C Axis Aligned Crystalともいう。)を含む酸化物について説明する。

【0043】

CAACを含む酸化物とは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物をいう。

【0044】

CAACは単結晶ではないが、非晶質のみから形成されているものでもない。また、CAACは結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

【0045】

CAACに酸素が含まれる場合、酸素の一部は窒素で置換されてもよい。また、CAACを構成する個々の結晶部分のc軸は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)に揃っていてもよい。または、CAACを構成する個々の結晶部分のab面の法線は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)を向いていてもよい。

【0046】

CAACは、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

【0047】

このようなCAACの例として、膜状に形成され、膜表面または支持する基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子(または窒素原子)の層状配列が認められる結晶を挙げることもできる。

【0048】

CAACに含まれる結晶構造の一例について図14乃至図16を用いて詳細に説明する。なお、特に断りがない限り、図14乃至図16は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図14において丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

【0049】

図14(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図14(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図14(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図14(A)に示す小グループは電荷が0である。

【0050】

図14(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図14(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図14(B)に示す構造をとりうる。図14(B)に示す小グループは電荷が0である。

【0051】

図14(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図14(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図14(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあってもよい。図14(C)に示す小グループは電荷が0である。

【0052】

図14(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図14(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図14(D)に示す小グループは電荷が+1となる。

【0053】

図14(E)に、2個のZnを含む小グループを示す。図14(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図14(E)に示す小グループは電荷が−1となる。

【0054】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

【0055】

ここで、これらの小グループ同士が結合する規則について説明する。図14(A)に示す6配位のInの上半分の3個のOは、下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Inを有する。図14(B)に示す5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。図14(C)に示す4配位のZnの上半分の1個のOは、下方向に1個の近接Znを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)、4配位の金属原子(Zn)のいずれかと結合することになる。

【0056】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0057】

図15(A)に、In−Sn−Zn−O系の層構造を構成する中グループのモデル図を示す。図15(B)に、3つの中グループで構成される大グループを示す。なお、図15(C)は、図15(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0058】

図15(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図15(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図15(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0059】

図15(A)において、In−Sn−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0060】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ−0.667、−0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷−1が必要となる。電荷−1をとる構造として、図14(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0061】

具体的には、図15(B)に示した大グループが繰り返されることで、In−Sn−Zn−O系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn−O系の層構造は、In2SnZn2O7(ZnO)m(mは0または自然数。)とする組成式で表すことができる。

【0062】

また、このほかにも、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物や、三元系金属の酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する。)、In−Al−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物や、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物や、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物や、In−Ga系酸化物などを用いた場合も同様である。

【0063】

例えば、図16(A)に、In−Ga−Zn−O系の層構造を構成する中グループのモデル図を示す。

【0064】

図16(A)において、In−Ga−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

【0065】

図16(B)に3つの中グループで構成される大グループを示す。なお、図16(C)は、図16(B)の層構造をc軸方向から観察した場合の原子配列を示している。

【0066】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0067】

また、In−Ga−Zn−O系の層構造を構成する中グループは、図16(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

【0068】

c軸配向を有した結晶性酸化物半導体を得る方法としては、三つ挙げられる。一つ目は、成膜温度を400℃以上450℃以下として酸化物半導体層144の成膜を行い、図2(A)に示す矢印の方向にc軸配向させる方法である。二つ目は、膜厚を薄く成膜した後、200℃以上700℃以下の加熱処理を行い、図2(B)に示す矢印の方向にc軸配向させる方法である。三つ目は、一層目の膜厚を薄く成膜した後、200℃以上700℃以下の加熱処理を行い、2層目の成膜を行い、図2(C)に示す矢印の方向にc軸配向させる方法である。

【0069】

図2(A)、図2(B)、及び図2(C)に示すように、いずれの方法であっても、酸化物半導体層144の表面の凹凸に対して垂直な方向に結晶成長が行われ、c軸配向した結晶性酸化物半導体を得ることができる。

【0070】

次いで、酸化物半導体層144に接し、ソース電極またはドレイン電極として機能する電極142a、142bを形成する。電極142a、電極142bは、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。

【0071】

また、電極142a、142bを保護するため、絶縁層143a、143bを形成する。次いで、CMP(化学的機械的研磨)などを用いて平坦化処理を行う。この平坦化処理の際、絶縁層143a、143bは、電極142a、142bを削らないためのバッファ層として機能する。

【0072】

次いで、チャネル長方向の素子分離用のトレンチと、チャネル幅方向の素子分離用のトレンチを形成する。これらの素子分離用のトレンチは、繋がった上面パターン形状としてもよいし、独立した上面パターン形状としてもよい。本実施の形態では、トレンチの形成によって酸化物半導体層の分離を行うため、図1(C)において、これらのトレンチのパターンは、繋がった上面パターン形状(格子状)としている。チャネル幅方向の素子分離用のトレンチの形成の際に、電極142aと電極142bの分離も行うことができる。なお、素子分離用のトレンチの形成のタイミングは、特に限定されない。また、素子分離用のトレンチの深さは、素子分離が十分行えるのであれば、ゲート電極用のトレンチと同じ底面の水平位置となる深さに限定されない。ゲート電極用トレンチよりも素子分離用のトレンチの底面の水平位置を深くすることで確実に素子分離を行うことができる。

【0073】

次いで、酸化物半導体層144の一部、ソース電極またはドレイン電極として機能する電極142a、142b、及び絶縁層143a、143bを覆うゲート絶縁層146を形成する。また、チャネル長方向の素子分離用のトレンチの内壁及び底面と、チャネル幅方向のトレンチの内壁及び底面にもゲート絶縁層146を成膜する。

【0074】

ゲート絶縁層146としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。ゲート絶縁層146は、酸化物半導体層144と接する部分において酸素を含むことが好ましい。特に、ゲート絶縁層146は、膜中(バルク中)に少なくとも化学量論的組成比を超える量の酸素が存在することが好ましく、例えば、ゲート絶縁層146として、酸化シリコン膜を用いる場合には、SiO2+α(ただし、α>0)とする。本実施の形態では、ゲート絶縁層146として、SiO2+α(ただし、α>0)である酸化シリコン膜を用いる。この酸化シリコン膜をゲート絶縁層146として用いることで、酸化物半導体層144に酸素を供給することができ、特性を良好にすることができる。さらに、ゲート絶縁層146は、作製するトランジスタのサイズやゲート絶縁層146の段差被覆性を考慮して形成することが好ましい。

【0075】

また、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSixOyNz(x>0、y>0、z>0))、ハフニウムアルミネート(HfAlxOy(x>0、y>0))、などのhigh−k材料を用いることでゲートリーク電流を低減できる。さらに、ゲート絶縁層146は、単層構造としても良いし、積層構造としても良い。なお、ゲート絶縁層の膜厚は、1nm以上100nm以下とする。

【0076】

そして、ゲート電極用のトレンチ内に充填されるように、ゲート電極148aをゲート絶縁層146上に形成する。ゲート電極148aの材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。ゲート電極148aは、単層構造としてもよいし、積層構造としてもよい。

【0077】

ゲート絶縁層146と接するゲート電極148aの一層として、窒素を含む金属酸化物、具体的には、窒素を含むIn−Ga−Zn−O膜や、窒素を含むIn−Sn−O膜や、窒素を含むIn−Ga−O膜や、窒素を含むIn−Zn−O膜や、窒素を含むSn−O膜や、窒素を含むIn−O膜や、金属窒化膜(InN、SnNなど)を用いる。これらの膜は5電子ボルト、好ましくは5.5電子ボルト以上の仕事関数を有し、ゲート電極として用いた場合、トランジスタの電気特性の一であるしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。

【0078】

ゲート電極用のトレンチ内にゲート電極148aを形成した段階で、トレンチ構造のトランジスタ162が形成される。

【0079】

次いで、ゲート電極148a、148bを覆う絶縁層149を形成する。絶縁層149は段差被覆性のよい絶縁膜を用いることが好ましい。絶縁層149の材料としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。本実施の形態では、絶縁層149の材料として酸化アルミニウム膜を用いる。図1(A)及び図1(B)においては、酸化物半導体層144の側面に接してゲート絶縁層146が形成され、さらに絶縁層149が形成される。なお、本実施の形態では、ゲート絶縁層146として、SiO2+α(ただし、α>0)である酸化シリコン膜を用い、絶縁層149として、酸化アルミニウム膜を用いる。従って、酸化アルミニウム膜が酸化シリコン膜を覆うことによって酸化シリコン膜中の酸素が拡散し、酸素が絶縁層149を通過しないようにブロックしている。

【0080】

絶縁層149を形成した後、素子分離用のトレンチを充填するための絶縁層150をCVD法などにより形成する。素子分離用のトレンチに絶縁層150を充填することによって素子分離領域161、165が形成される。なお、絶縁層150の形成前に、素子分離用のトレンチにはゲート絶縁層146、絶縁層149を積層させておくことで、絶縁層150を充填する領域を小さくし、絶縁層150の充填をスムーズに行うことができる。その後、CMPなどを用いて平坦化処理を行い、図1(A)及び図1(B)に示す構造を得ることができる。

【0081】

また、図1(B)に示すように、トランジスタ162のゲート電極148aと、隣り合うトランジスタ163のゲート電極148bとの間にも絶縁層150が充填され、ゲート電極同士の短絡防止が図られている。また、図1(A)に示すように、トランジスタ162のソース電極またはドレイン電極として機能する電極と、チャネル長方向に隣り合うトランジスタのソース電極またはドレイン電極として機能する電極との間にも絶縁層150が充填され、ソース電極またはドレイン電極の短絡防止も図られている。

【0082】

トランジスタのチャネルがトレンチの内壁に沿って形成され、チャネル形成領域が平坦でなくともキャリアの流れがCAACの酸化物半導体のIn−O−In−Oとスムーズに流れる。本実施の形態では、深さ0.4μmのトレンチ内壁に接して酸化物半導体層144を形成するため、チャネル長は約0.8μm以上となる。0.8μm以上のチャネル長とすることで、ノーマリーオフのトランジスタとすることができ、ショートチャネル効果も生じないようにすることができる。また、トレンチ構造を採用することで、トランジスタの平面面積を縮小できるため、高集積化が可能である。

【0083】

(実施の形態2)

図1に示すトランジスタ162を使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置の一例を図3、及び図17に示す。

【0084】

トランジスタ162は、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。

【0085】

図3(A)は、半導体装置の断面の一例を示している。

【0086】

図3(A)に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ160を有し、上部に第2の半導体材料を用いたトランジスタ162を有するものである。なお、トランジスタ162は、実施の形態1と同一であるため、図3(A)、(B)において図1(A)と同じ箇所は、同じ符号を用いて説明する。

【0087】

ここで、第1の半導体材料と第2の半導体材料とは異なる材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。また、本実施の形態においては、第1の半導体材料を用いたトランジスタを第1のトランジスタとし、第2の半導体材料を用いたトランジスタを第2のトランジスタとする。

【0088】

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、pチャネル型トランジスタを用いることができるのはいうまでもない。また、開示する発明の技術的な本質は、情報を保持するために酸化物半導体をトランジスタ162に用いる点にあるから、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

【0089】

図3(A)におけるトランジスタ160は、半導体材料(例えば、シリコンなど)を含む基板100に設けられたチャネル形成領域116と、チャネル形成領域116を挟むように設けられた不純物領域120と、不純物領域120に接する金属化合物領域124と、チャネル形成領域116上に設けられたゲート絶縁層108と、ゲート絶縁層108上に設けられたゲート電極110と、を有する。

【0090】

トランジスタ160の金属化合物領域124の一部には、電極126が接続されている。ここで、電極126は、トランジスタ160のソース電極やドレイン電極として機能する。また、基板100上にはトランジスタ160を囲むように素子分離絶縁層(図示しない)が設けられており、トランジスタ160を覆うように絶縁層130が設けられている。なお、高集積化を実現するためには、図3(A)に示すようにトランジスタ160がサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ160の特性を重視する場合には、ゲート電極110の側面にサイドウォール絶縁層を設け、不純物濃度が異なる領域を含む不純物領域120を設けても良い。

【0091】

図3(A)に示すようにトランジスタ162は、酸化物半導体層144を有するトレンチ構造のトランジスタである。

【0092】

ここで、酸化物半導体層144は水素などの不純物が十分に除去されることにより、または、十分な酸素が供給されることにより、高純度化されたものであることが望ましい。具体的には、例えば、酸化物半導体層144の水素濃度は5×1019atoms/cm3以下、望ましくは5×1018atoms/cm3以下、より望ましくは5×1017atoms/cm3以下とする。なお、上述の酸化物半導体層144中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectroscopy)で測定されるものである。このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠乏に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体層144では、キャリア濃度が1×1012/cm3未満、望ましくは、1×1011/cm3未満、より望ましくは1.45×1010/cm3未満となる。例えば、室温(25℃)でのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値)は100zA(1zA(ゼプトアンペア)は1×10−21A)以下、望ましくは10zA以下となる。このように、i型化(真性化)または実質的にi型化された酸化物半導体を用いることで、極めて優れたオフ電流特性のトランジスタ162を得ることができる。

【0093】

なお、図3(A)のトランジスタ162では、微細化に起因して素子間に生じるリークを抑制するために、素子分離領域161を設けている。さらに素子分離領域161に囲まれた領域よりも小さく島状に加工された酸化物半導体層144を用いているが、実施の形態1に示したように、素子分離用のトレンチを形成するまで島状に加工されていない構成を採用しても良い。酸化物半導体層144を島状に加工しない場合には、加工の際のエッチングによる酸化物半導体層144の汚染を防止できる。勿論、酸化物半導体層144を島状に加工しない場合には、工程数の削減も図ることができる。また、素子分離領域161に囲まれた領域よりも小さく島状に加工された酸化物半導体層144を用いる場合、素子分離用のトレンチの形成によって酸化物半導体層を分断する必要がないため、素子分離用のトレンチの底面の水平位置はゲート電極用のトレンチよりも浅くできる、または素子分離用のトレンチ形成のトータル面積を減らすことができる。

【0094】

トランジスタ162上には、絶縁層151が設けられており、絶縁層151上にはゲート電極148aと電気的に接続する電極153が設けられている。そして、電極153上には絶縁層152が設けられている。そして、ゲート絶縁層146、絶縁層150、絶縁層151、絶縁層152などに形成された開口には、電極154が設けられ、絶縁層152上には電極154と接続する配線156が形成される。なお、図3(A)では電極126および電極154を用いて、金属化合物領域124、電極142b、および配線156を接続しているが、開示する発明はこれに限定されない。例えば、電極142bを直接、金属化合物領域124に接触させても良い。または、配線156を直接、電極142bに接触させても良い。

【0095】

次に、図3(A)に対応する回路構成の一例を図3(B)に示す。なお、回路図においては、酸化物半導体を用いたトランジスタであることを示すために、OSの符号を併せて付す場合がある。

【0096】

図3(B)において、第1の配線(1st Line)とトランジスタ160のソース電極層とは、電気的に接続され、第2の配線(2nd Line)とトランジスタ160のドレイン電極層とは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ162のソース電極またはドレイン電極層の一方とは、電気的に接続され、第4の配線(4th Line)と、トランジスタ162のゲート電極層とは、電気的に接続されている。そして、トランジスタ160のゲート電極層と、トランジスタ162のソース電極層またはドレイン電極層の他方は、容量素子164の電極の一方と電気的に接続され、第5の配線(5th Line)と、容量素子164の電極の他方は電気的に接続されている。

【0097】

容量素子164は、トランジスタ160やトランジスタ162の作製プロセスと同じ工程で一対の電極と、その間に挟まれる誘電体となる絶縁層で形成することができる。トランジスタ162の作製プロセスと同じ工程で容量素子164を形成する一例を、図17に示す。図17に示す構成は、図3(A)に示す構成に容量素子164が追加されている。トランジスタ162を形成後、トランジスタ162の電極142aに達する開口部を形成し、その後、開口部を覆うように絶縁膜502を形成する。そして、絶縁膜502と接し、当該開口部を充填するように電極504形成することで、電極142aと、絶縁膜502と、電極504により容量素子164が形成される。なお、トランジスタ160やトランジスタ162の作製プロセスと同じ工程で形成することに限定されず、容量素子164の層を別途、トランジスタ162の上方に設けてもよい。例えば、トレンチ型の容量素子やスタック型の容量素子を別途、トランジスタの162の上方、または、トランジスタ160の下方に形成し、3次元的に積み重ねることで高集積化を図ってもよい。

【0098】

図3(B)に示す半導体装置の回路構成では、トランジスタ160のゲート電極層の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

【0099】

情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電位が、トランジスタ160のゲート電極層、および容量素子164に与えられる。すなわち、トランジスタ160のゲート電極層には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下Lowレベル電荷、Highレベル電荷という)のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位にして、トランジスタ162をオフ状態とすることにより、トランジスタ160のゲート電極層に与えられた電荷が保持される(保持)。次に情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、トランジスタ160のゲート電極層に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ160をnチャネル型とすると、トランジスタ160のゲート電極層にHighレベル電荷が与えられている場合の見かけのしきい値Vth_Hは、トランジスタ160のゲート電極層にLowレベル電荷が与えられている場合の見かけのしきい値Vth_Lより低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ160を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位をVth_HとVth_Lの中間の電位V0とすることにより、トランジスタ160のゲート電極層に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位がV0(>Vth_H)となれば、トランジスタ160は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位がV0(<Vth_L)となっても、トランジスタ160は「オフ状態」のままである。このため、第2の配線の電位を見ることで、保持されている情報を読み出すことができる。

【0100】

また、バックゲート電極をトランジスタ162に設けてもよく、バックゲート電極に電圧を印加することによってトランジスタ162のノーマリーオフ化を確実なものとすることが好ましい。

【0101】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0102】

(実施の形態3)

本実施の形態においては、図1に示すトランジスタ162を使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置について、実施の形態2に示した構成と異なる構成について図4を用いて説明を行う。

【0103】

図4に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ350を有し、上部に第2の半導体材料を用いたトランジスタ162を有するものである。なお、本実施の形態においては、下部に形成されたトランジスタ350は、第1のトランジスタとし、上部に形成されたトランジスタ162は、第2のトランジスタとする。また、上部、及び下部には、複数のトランジスタが形成されているが、代表的にトランジスタ350、及びトランジスタ162について、説明を行う。また、下部に形成されたトランジスタ350を含む複数のトランジスタは、半導体装置の周辺回路として機能し、上部に形成されたトランジスタ162を含む複数のトランジスタは、記憶素子として機能する。なお、線B1−B2で切断された図4は、トランジスタのチャネル長方向に垂直な断面図に相当する。

【0104】

ここで、第1の半導体材料と第2の半導体材料とは異なる材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

【0105】

なお、図4に示すように上部に第2の半導体材料を用いたトランジスタ162は、酸化物半導体層を有するトレンチ構造のトランジスタである。トランジスタ162は、先の実施の形態1、および実施の形態2に記載したトランジスタ162と同一であるため、図4において図1(A)と同じ箇所は、同じ符号を用いており、詳細な説明は省略する。

【0106】

ここでは、下部の第1の半導体材料を用いたトランジスタ350について、以下説明を行う。

【0107】

トランジスタ350は、半導体基板310、ゲート絶縁層314、半導体層316、導電層318、保護絶縁層320、サイドウォール絶縁層322、不純物領域324、及び絶縁層326により構成されている。なお、半導体層316、及び導電層318はゲート電極として機能し、不純物領域324は、ソース領域またはドレイン領域として機能する。

【0108】

また、トランジスタ350は、STI(Shallow Trench Isolation)領域312と隣接している。

【0109】

STI領域312としては、まず、半導体基板310の上の所望の領域に保護絶縁膜を形成し、エッチングを行うことでトレンチ(溝ともいう)が形成される。トレンチを形成した後、絶縁誘電体膜をトレンチに埋め込むことでSTI領域312を形成することができる。絶縁誘電体膜としては、酸化シリコン膜、窒化シリコン膜などを用いることができる。

【0110】

次に、トランジスタ350の詳細な説明を行う。トランジスタ350のゲート絶縁層314としては、STI領域312が形成された半導体基板310に、絶縁膜を形成した後、所望の位置にパターニング、エッチングを行い、半導体基板310にSTI領域312とは異なる深さのトレンチを形成する。その後、酸素雰囲気内にて加熱処理を行うことで、トレンチ内の半導体基板310が酸化され、ゲート絶縁層314を形成することができる。

【0111】

ゲート絶縁層314形成後に、LPCVD法などを用いて、シリコン膜を形成する。なお、該シリコン膜にn+、p+のドーピング処理、または加熱処理等を行い、所謂ポリシリコンとして導電性の高い半導体層を形成する。その後、該半導体層の上にスパッタリング法などにより、金属膜を成膜する。金属膜としては、タングステン、チタン、コバルト、ニッケル、または、タングステン、チタン、コバルト、ニッケルを含む合金膜、金属窒化膜、シリサイド膜などを適宜用いることができる。該金属膜上の所望の領域にパターニングを行い、エッチングすることで、導電層318が形成される。また、導電層318をマスクとして半導体層をエッチングすることで、半導体層316を形成することができる。なお、導電層318と半導体層316はトランジスタ350のゲート電極として機能する。

【0112】

次に、導電層318の上に、保護絶縁層320を形成する。保護絶縁層320としては、プラズマCVD法などを用い、酸化シリコン膜、窒化シリコン膜などを成膜し、所望の領域にパターニング、エッチング処理を行うことで形成することができる。

【0113】

次に、半導体基板310、および保護絶縁層320を覆うようにプラズマCVD法などにより、窒化シリコン膜を成膜し、エッチバックを行うことで、サイドウォール絶縁層322を形成することができる。

【0114】

次に、保護絶縁層320、及びサイドウォール絶縁層322をマスクとして、ドーピング処理を行うことで、不純物領域324を形成する。なお、ドーパントとしては、ボロンやリンなどを用いればよく、不純物領域324として用いるドーパントによりn+領域、p+領域など適宜形成することができる。なお、不純物領域324は、トランジスタ350のソース領域またはドレイン領域として機能する。

【0115】

次に、不純物領域324、保護絶縁層320、及びサイドウォール絶縁層322を覆うように絶縁層326を形成する。絶縁層326としては、プラズマCVD法などにより酸化シリコン膜などを用いて形成することができる。

【0116】

次に、絶縁層326の所望の領域に開口部を設け、不純物領域324と電気的に接続する接続電極325、及び接続電極331を形成する。なお、接続電極325、及び接続電極331形成後に、絶縁層326、接続電極325、および接続電極331の表面を平坦化させるCMP処理などを行ってもよい。

【0117】

次に、絶縁層326、接続電極325、及び接続電極331の上に、スパッタリング法などを用いて導電膜を成膜し、所望の領域にパターニングを行い、エッチングすることで、電極328、及び電極332を形成する。電極328、及び電極332に使用できる材料としては、タングステン、銅、チタンなど適宜用いることができる。

【0118】

次に、絶縁層326、電極328、及び電極332上に絶縁層329を形成する。絶縁層329としては、絶縁層326と同様の材料、及び手法により形成することができる。

【0119】

以上の工程により、第1の半導体材料を用いたトランジスタ350が形成された半導体基板310を形成することができる。

【0120】

次に、下部の第1の半導体材料を用いたトランジスタ350と、上部の第2の半導体材料を用いたトランジスタ162の接続関係について以下説明を行う。

【0121】

トランジスタ350は、不純物領域324と、接続電極325と、電極328と、接続電極330とにより、トランジスタ162と電気的に接続されている。また、他方では、不純物領域324と、接続電極331と、電極332と、接続電極334と、電極336と、接続電極338により、配線156と電気的に接続されている。

【0122】

また、トランジスタ350のゲート電極(すなわち、半導体層316、及び導電層318)は、トランジスタ162のソース電極と電気的に接続している。ただし、図4においては、トランジスタ350のゲート電極と、トランジスタ162のソース電極の接続は示されておらず、3次元方向で接続を行っている。

【0123】

以上のように、上部に形成された記憶素子は、酸化物半導体を用いたトランジスタにより形成されている。酸化物半導体を用いたトランジスタは、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、一方で周辺回路では、酸化物半導体以外の半導体材料が用いられている。酸化物半導体以外の半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、酸化物半導体以外の材料を用いたトランジスタにより、高速動作が要求される各種回路(論理回路、駆動回路など)を好適に実現することが可能である。

【0124】

このように、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた周辺回路と、酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路とを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。また、周辺回路と記憶回路を積層構造とすることにより、半導体装置の集積化を図ることができる。

【0125】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0126】

(実施の形態4)

本実施の形態においては、図1に示すトランジスタ162を使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置について、実施の形態2、及び実施の形態3に示した構成と異なる構成について、図5、及び図6を用いて説明を行う。

【0127】

図5(A)は、半導体装置の回路構成の一例を示し、図5(B)は半導体装置の一例を示す概念図である。まず、図5(A)に示す半導体装置について説明を行い、続けて図5(B)に示す半導体装置について、以下説明を行う。

【0128】

図5(A)に示す半導体装置において、ビット線BLとトランジスタ162のソース電極又はドレイン電極とは電気的に接続され、ワード線WLとトランジスタ162のゲート電極とは電気的に接続され、トランジスタ162のソース電極又はドレイン電極と容量素子254の第1の端子とは電気的に接続されている。

【0129】

酸化物半導体を用いたトランジスタ162は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ162をオフ状態とすることで、容量素子254の第1の端子の電位(あるいは、容量素子254に蓄積された電荷)を極めて長時間にわたって保持することが可能である。また、酸化物半導体を用いたトランジスタ162では、短チャネル効果が現れにくいというメリットもある。

【0130】

次に、図5(A)に示す半導体装置(メモリセル250)に、情報の書き込みおよび保持を行う場合について説明する。

【0131】

まず、ワード線WLの電位を、トランジスタ162がオン状態となる電位として、トランジスタ162をオン状態とする。これにより、ビット線BLの電位が、容量素子254の第1の端子に与えられる(書き込み)。その後、ワード線WLの電位を、トランジスタ162がオフ状態となる電位として、トランジスタ162をオフ状態とすることにより、容量素子254の第1の端子の電位が保持される(保持)。

【0132】

トランジスタ162のオフ電流は極めて小さいから、容量素子254の第1の端子の電位(あるいは容量素子に蓄積された電荷)は長時間にわたって保持することができる。

【0133】

次に、情報の読み出しについて説明する。トランジスタ162がオン状態となると、浮遊状態であるビット線BLと容量素子254とが導通し、ビット線BLと容量素子254の間で電荷が再分配される。その結果、ビット線BLの電位が変化する。ビット線BLの電位の変化量は、容量素子254の第1の端子の電位(あるいは容量素子254に蓄積された電荷)によって、異なる値をとる。

【0134】

例えば、容量素子254の第1の端子の電位をV、容量素子254の容量をC、ビット線BLが有する容量成分(以下、ビット線容量とも呼ぶ)をCB、電荷が再分配される前のビット線BLの電位をVB0とすると、電荷が再分配された後のビット線BLの電位は、(CB*VB0+C*V)/(CB+C)となる。従って、メモリセル250の状態として、容量素子254の第1の端子の電位がV1とV0(V1>V0)の2状態をとるとすると、電位V1を保持している場合のビット線BLの電位(=(CB*VB0+C*V1)/(CB+C))は、電位V0を保持している場合のビット線BLの電位(=(CB*VB0+C*V0)/(CB+C))よりも高くなることがわかる。

【0135】

そして、ビット線BLの電位を所定の電位と比較することで、情報を読み出すことができる。

【0136】

このように、図5(A)に示す半導体装置は、トランジスタ162のオフ電流が極めて小さいという特徴から、容量素子254に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。

【0137】

次に、図5(B)に示す半導体装置について、説明を行う。

【0138】

図5(B)に示す半導体装置は、上部に記憶素子として図5(A)に示したメモリセル250を複数有するメモリセルアレイ251、及び図5(A)に示したメモリセル250を複数有するメモリセルアレイ252を有し、下部に、メモリセルアレイ251、及びメモリセルアレイ252を動作させるために必要な周辺回路253を有する。なお、本実施の形態においてメモリセルアレイ252は、メモリセルアレイ251と周辺回路253の中部に位置しているが、周辺回路253に対しては、上部に位置しているため、メモリセルアレイ251、メモリセルアレイ252は、上部に位置しているとする。

【0139】

図5(B)に示した構成とすることにより、周辺回路253をメモリセルアレイ251、及びメモリセルアレイ252の直下に設けることができるため、且つ、メモリセルアレイ251とメモリセルアレイ252も積層構造とすることにより、半導体装置の小型化を図ることができる。

【0140】

次に、図5(B)に示した半導体装置の具体的な構成について図6を用いて説明を行う。

【0141】

図6に示す半導体装置は、上部に多層に形成された記憶素子として、複数のメモリセル(メモリセル452a、及びメモリセル452b)を有し、下部に周辺回路400を有する。下部の周辺回路400は、第1の半導体材料を用いたトランジスタ450を有し、上部に多層に形成された複数のメモリセル(メモリセル452a、及びメモリセル452b)は、第2の半導体材料を用いたトランジスタ162を有するものである。また、トランジスタ162は、容量素子に接続されているが、3次元方向に接続されているために、図6には示されていない。なお、線C1−C2で切断された図6は、トランジスタのチャネル長方向に垂直な断面図に相当する。

【0142】

ここで、第1の半導体材料と第2の半導体材料とは異なる材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

【0143】

また、上部の第2の半導体材料を用いたトランジスタ162は、先の実施の形態1乃至実施の形態3に記載したトランジスタ162と同一であるため、図6において図1(A)と同じ箇所は、同じ符号を用いており、詳細な説明は省略する。ここでは、下部の第1の半導体材料を用いたトランジスタ450について、以下説明を行う。

【0144】

図6におけるトランジスタ450は、半導体材料(例えば、シリコンなど)を含む基板402に設けられたチャネル形成領域404と、チャネル形成領域404を挟むように設けられた不純物領域406および高濃度不純物領域408(これらをあわせて単に不純物領域とも呼ぶ)と、高濃度不純物領域408に接する金属化合物領域410と、チャネル形成領域404の上に設けられたゲート絶縁層411と、ゲート絶縁層411に接して設けられたゲート電極層412と、不純物領域と電気的に接続するソース電極またはドレイン電極418a、およびソース電極またはドレイン電極418bを有する。

【0145】

ここで、ゲート電極層412の側面にはサイドウォール絶縁層414が設けられている。また、基板402上にはトランジスタ450を囲むように素子分離絶縁層403が設けられており、トランジスタ450を覆うように、層間絶縁層420および層間絶縁層422が設けられている。ソース電極またはドレイン電極418a、およびソース電極またはドレイン電極418bは、層間絶縁層420および層間絶縁層422に形成された開口を通じて、金属化合物領域410と電気的に接続されている。つまり、ソース電極またはドレイン電極418a、およびソース電極またはドレイン電極418bは、金属化合物領域410を介して高濃度不純物領域408および不純物領域406と電気的に接続されている。なお、トランジスタ450の集積化などのため、サイドウォール絶縁層414が形成されない場合もある。また、層間絶縁層422の上に、トランジスタ450のソース電極またはドレイン電極418a、およびソース電極またはドレイン電極418bと、電気的に接続する電極424a、電極424b、及び電極424cを有し、層間絶縁層422、電極424a、電極424b、及び電極424cを覆う、絶縁層425により平坦化されている。

【0146】

電極424cは、接続電極426によって、電極428と電気的に接続されている。なお、電極428は、トランジスタ162のソース電極層及びドレイン電極層と同じ層にて形成されている。

【0147】

また、配線432は、接続電極430によって、電極428と電気的に接続されており、接続電極434によって、トランジスタ162のソース電極層及びドレイン電極層と同じ層で形成された電極436と電気的に接続されている。また、電極436は、接続電極438によって、配線440と電気的に接続されている。

【0148】

電極424c、配線432、及び配線440によって、メモリセル間の電気的接続や、周辺回路400とメモリセル(メモリセル452aと、メモリセル452b)との電気的接続等を行うことができる。

【0149】

なお、図6に示した半導体装置では、2つのメモリセル(メモリセル452aと、メモリセル452b)が積層された構成を例示したが、積層するメモリセルの数はこれに限定されない。3つ以上のメモリセルを積層する構成としても良い。

【0150】

また、図6に示した半導体装置では、メモリセル452aと、メモリセル452bと、周辺回路400との接続には、電極424c、電極428、配線432、電極436、及び配線440によって、接続する構成について例示したがこれに限定されない。メモリセル452a、メモリセル452b、及び周辺回路400との間には、二つ以上の配線層、及び電極が設けられる構成としてもよい。

【0151】

以上のように、上部に多層に形成された複数のメモリセルは、酸化物半導体を用いたトランジスタにより形成されている。酸化物半導体を用いたトランジスタは、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、一方で周辺回路では、酸化物半導体以外の半導体材料が用いられている。酸化物半導体以外の半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、酸化物半導体以外の材料を用いたトランジスタにより、高速動作が要求される各種回路(論理回路、駆動回路など)を好適に実現することが可能である。

【0152】

このように、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた周辺回路と、酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路とを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。また、周辺回路と記憶回路を積層構造とすることにより、半導体装置の集積化を図ることができる。

【0153】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0154】

(実施の形態5)

本実施の形態では、先の実施の形態で説明した半導体装置を携帯電話、スマートフォン、電子書籍などの携帯機器に応用した場合の例を図10乃至図13を用いて説明する。

【0155】

携帯電話、スマートフォン、電子書籍などの携帯機器においては、画像データの一時記憶などにSRAMまたはDRAMが使用されている。SRAMまたはDRAMは使用される理由としてはフラッシュメモリでは応答が遅く、画像処理では不向きであるためである。一方で、SRAMまたはDRAMを画像データの一時記憶に用いた場合以下の特徴がある。

【0156】

通常のSRAMは、図10(A)に示すように1つのメモリセルがトランジスタ801〜806の6個のトランジスタで構成されており、それをXデコーダー807、Yデコーダー808にて駆動している。トランジスタ803とトランジスタ805、トランジスタ804とトランジスタ806はインバータを構成し、高速駆動を可能としている。しかし1つのメモリセルが6トランジスタで構成されているため、セル面積が大きいという欠点がある。デザインルールの最小寸法をFとしたときにSRAMのメモリセル面積は通常100〜150F2である。このためSRAMはビットあたりの単価が各種メモリの中で最も高い。

【0157】

それに対して、DRAMはメモリセルが図10(B)に示すようにトランジスタ811、保持容量812によって構成され、それをXデコーダー813、Yデコーダー814にて駆動している。1つのセルが1トランジスタ1容量の構成になっており、面積が小さい。DRAMのメモリセル面積は通常10F2以下である。ただし、DRAMは常にリフレッシュが必要であり、書き換えをおこなわない場合でも電力を消費する。

【0158】

しかし、先の実施の形態で説明した半導体装置のメモリセル面積は、10F2前後であり、且つ頻繁なリフレッシュは不要である。したがって、メモリセル面積が縮小され、且つ消費電力が低減することができる。

【0159】

次に、図11は携帯機器のブロック図である。図11に示す携帯機器はRF回路901、アナログベースバンド回路902、デジタルベースバンド回路903、バッテリー904、電源回路905、アプリケーションプロセッサ906、フラッシュメモリ910、ディスプレイコントローラ911、メモリ回路912、ディスプレイ913、タッチセンサ919、音声回路917、キーボード918などより構成されている。ディスプレイ913は表示部914、ソースドライバ915、ゲートドライバ916によって構成されている。アプリケーションプロセッサ906はCPU907、DSP908、インターフェイス909(IF909)を有している。一般にメモリ回路912はSRAMまたはDRAMで構成されており、この部分に先の実施の形態で説明した半導体装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

【0160】

次に、図12はディスプレイのメモリ回路950に先の実施の形態で説明した半導体装置を使用した例である。図12に示すメモリ回路950は、メモリ952、メモリ953、スイッチ954、スイッチ955およびメモリコントローラ951により構成されている。また、メモリ回路950は、信号線から入力された画像データ(入力画像データ)、メモリ952、及びメモリ953に記憶されたデータ(記憶画像データ)を読み出し、及び制御を行うディスプレイコントローラ956と、ディスプレイコントローラ956からの信号により表示するディスプレイ957が接続されている。

【0161】

まず、ある画像データがアプリケーションプロセッサ(図示しない)によって、形成される(入力画像データA)。入力画像データAは、スイッチ954を介してメモリ952に記憶される。そしてメモリ952に記憶された画像データ(記憶画像データA)は、スイッチ955、及びディスプレイコントローラ956を介してディスプレイ957に送られ、表示される。

【0162】

入力画像データAに変更が無い場合、記憶画像データAは、通常30〜60Hz程度の周期でメモリ952からスイッチ955を介して、ディスプレイコントローラ956により読み出される。

【0163】

次に、例えばユーザーが画面を書き換える操作をしたとき(すなわち、入力画像データAに変更が有る場合)、アプリケーションプロセッサは新たな画像データ(入力画像データB)を形成する。入力画像データBはスイッチ954を介してメモリ953に記憶される。この間も定期的にメモリ952からスイッチ955を介して記憶画像データAは読み出されている。メモリ953に新たな画像データ(記憶画像データB)が記憶し終わると、ディスプレイ957の次のフレームより、記憶画像データBは読み出され、スイッチ955、及びディスプレイコントローラ956を介して、ディスプレイ957に記憶画像データBが送られ、表示がおこなわれる。この読み出しはさらに次に新たな画像データがメモリ952に記憶されるまで継続される。

【0164】

このようにメモリ952、及びメモリ953は交互に画像データの書き込みと、画像データの読み出しを行うことによって、ディスプレイ957の表示をおこなう。なお、メモリ952、及びメモリ953はそれぞれ別のメモリには限定されず、1つのメモリを分割して使用してもよい。先の実施の形態で説明した半導体装置をメモリ952、及びメモリ953に採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

【0165】

次に、図13は電子書籍のブロック図である。図13はバッテリー1001、電源回路1002、マイクロプロセッサ1003、フラッシュメモリ1004、音声回路1005、キーボード1006、メモリ回路1007、タッチパネル1008、ディスプレイ1009、ディスプレイコントローラ1010によって構成される。

【0166】

ここでは、図13のメモリ回路1007に先の実施の形態で説明した半導体装置を使用することができる。メモリ回路1007は書籍の内容を一時的に保持する機能を持つ。機能の例としては、ユーザーがハイライト機能を使用する場合などがある。ユーザーが電子書籍を読んでいるときに、特定の箇所にマーキングをしたい場合がある。このマーキング機能をハイライト機能と言い、表示の色を変える、アンダーラインを引く、文字を太くする、文字の書体を変えるなどによって、周囲との違いを示すことである。ユーザーが指定した箇所の情報を記憶し、保持する機能である。この情報を長期に保存する場合にはフラッシュメモリ1004にコピーしても良い。このような場合においても、先の実施の形態で説明した半導体装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

【0167】

以上のように、本実施の形態に示す携帯機器には、先の実施の形態に係る半導体装置が搭載されている。このため、読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力を低減した携帯機器が実現される。

【0168】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【実施例1】

【0169】

本実施例では、実施の形態1に示すトレンチ構造のトランジスタに短チャネル効果が発現するかを確認するため、計算を行った。図7乃至図9に計算に用いた構造、及び計算結果を示す。なお、図7乃至図9において、ゲート絶縁層がSiOx、酸化物半導体層がOS、ゲート電極がGate、ソース電極、及びドレイン電極がS/D、とそれぞれ付記してある。

【0170】

なお、計算にはシノプシス社製デバイスシミュレーションソフトSentaurus Deviceを使用した。

【0171】

図7(A)に計算に用いた構造および個々のサイズを示す。ゲート絶縁層の膜厚を5nm、酸化物半導体層の膜厚を5nmとし、ゲート電極用のトレンチの深さを0.4μmと設定する。図7(A)は、トレンチの底部の長さ(チャネル長方向の長さ)が90nm、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)が110nmであるトレンチ構造のトランジスタである。酸化物半導体層の材料は、In−Ga−Zn−O系酸化物半導体(バンドギャップ3.15eV、電子親和力4.6eV、電子移動度10cm2/Vs)を用い、酸化物半導体層に接する電極(ソース電極とドレイン電極)の仕事関数を4.6eV、ゲート電極の仕事関数を5.5eVとする。このトレンチ構造のトランジスタのVg−Id特性(Vds=1V、温度27℃)を計算した結果が図7(B)である。

【0172】

また、図8(A)は、トレンチの底部の長さ(チャネル長方向の長さ)が60nm、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)が80nmであるトレンチ構造のトランジスタである。トレンチの底部の長さとソース電極とドレイン電極の間隔以外は図7(B)と同じ条件で計算した結果が図8(B)である。

【0173】

また、図9(A)は、トレンチの底部の長さ(チャネル長方向の長さ)が30nm、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)が50nmであるトレンチ構造のトランジスタである。トレンチの底部の長さとソース電極とドレイン電極の間隔以外は図7(B)と同じ条件で計算した結果が図9(B)である。

【0174】

計算の結果、図7(A)、図8(A)、及び図9(A)の構造全てのトランジスタ特性は、ほぼ同等であった。それぞれのトランジスタのしきい値(Vth)は、0.8V、S値は60mV/decと良好な値を示した。

【0175】

これらの計算結果から、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)を30nmまで狭めても、しきい値のマイナスシフトやS値の増大といった短チャネル効果は発現せず、良好なトランジスタ特性を示している。

【0176】

比較のため、トレンチ構造ではなく、プレナー型のトランジスタの構造を用いて同様の計算を行ったところ、ソース電極とドレイン電極の間隔(チャネル長方向の長さ)を狭めると、チャネル長も狭くなり、しきい値のマイナスシフトやS値の増大といった短チャネル効果が発現し、さらにはゲートに負のバイアスを印加したときのリーク電流(オフ電流)の増大も確認された。

【0177】

この比較のための計算結果と比べ、図7(B)、図8(B)、及び図9(B)の計算結果は、良好であり、実施の形態1に示すトランジスタ構造とすることでソース電極とドレイン電極の間隔(チャネル長方向の長さ)を狭めても実効的なチャネル長の変化は少ないため、短チャネル効果は発現せず、オフ電流を低く抑えることができる。その結果、保持特性が良好なメモリセルを作ることが可能になる。

【符号の説明】

【0178】

100 基板

108 ゲート絶縁層

110 ゲート電極

116 チャネル形成領域

120 不純物領域

124 金属化合物領域

126 電極

130 絶縁層

142a 電極

142b 電極

143a 絶縁層

143b 絶縁層

144 酸化物半導体層

146 ゲート絶縁層

148a ゲート電極

148b ゲート電極

149 絶縁層

150 絶縁層

151 絶縁層

152 絶縁層

153 電極

154 電極

156 配線

160 トランジスタ

161 素子分離領域

162 トランジスタ

163 トランジスタ

164 容量素子

165 素子分離領域

250 メモリセル

251 メモリセルアレイ

252 メモリセルアレイ

253 周辺回路

254 容量素子

310 半導体基板

312 STI領域

314 ゲート絶縁層

316 半導体層

318 導電層

320 保護絶縁層

322 サイドウォール絶縁層

324 不純物領域

325 接続電極

326 絶縁層

328 電極

329 絶縁層

330 接続電極

331 接続電極

332 電極

334 接続電極

336 電極

338 接続電極

350 トランジスタ

400 周辺回路

402 基板

403 素子分離絶縁層

404 チャネル形成領域

406 不純物領域

408 高濃度不純物領域

410 金属化合物領域

411 ゲート絶縁層

412 ゲート電極層

414 サイドウォール絶縁層

418a ドレイン電極

418b ドレイン電極

420 層間絶縁層

422 層間絶縁層

424a 電極

424b 電極

424c 電極

425 絶縁層

426 接続電極

428 電極

430 接続電極

432 配線

434 接続電極

436 電極

438 接続電極

440 配線

450 トランジスタ

452a メモリセル

452b メモリセル

502 絶縁膜

504 電極

801 トランジスタ

803 トランジスタ

804 トランジスタ

805 トランジスタ

806 トランジスタ

807 Xデコーダー

808 Yデコーダー

811 トランジスタ

812 保持容量

813 Xデコーダー

814 Yデコーダー

901 RF回路

902 アナログベースバンド回路

903 デジタルベースバンド回路

904 バッテリー

905 電源回路

906 アプリケーションプロセッサ

907 CPU

908 DSP

909 インターフェイス

910 フラッシュメモリ

911 ディスプレイコントローラ

912 メモリ回路

913 ディスプレイ

914 表示部

915 ソースドライバ

916 ゲートドライバ

917 音声回路

918 キーボード

919 タッチセンサ

950 メモリ回路

951 メモリコントローラ

952 メモリ

953 メモリ

954 スイッチ

955 スイッチ

956 ディスプレイコントローラ

957 ディスプレイ

1001 バッテリー

1002 電源回路

1003 マイクロプロセッサ

1004 フラッシュメモリ

1005 音声回路

1006 キーボード

1007 メモリ回路

1008 タッチパネル

1009 ディスプレイ

1010 ディスプレイコントローラ

【特許請求の範囲】

【請求項1】

酸化物半導体以外の材料により形成された第1のトランジスタと、

前記第1のトランジスタを含む周辺回路と、

酸化物半導体により形成された第2のトランジスタと、

前記第2のトランジスタと電気的に接続された容量素子と、

前記第2のトランジスタと前記容量素子により形成された記憶素子と、を有し、

前記第2のトランジスタは、

絶縁層に第1のトレンチ及び第2のトレンチと、

前記第1のトレンチの底面及び内壁面に接する酸化物半導体層と、

前記酸化物半導体層上にゲート絶縁層と、

前記ゲート絶縁層上にゲート電極と、

前記第2のトレンチの底面及び内壁面上に前記ゲート絶縁層と、

前記第2のトレンチ内を充填する絶縁層と、

前記酸化物半導体層に接するソース電極またはドレイン電極と、を有し、

前記周辺回路の上に、前記記憶素子が積層されることを特徴とする半導体装置。

【請求項2】

請求項1において、

前記ゲート絶縁層は、前記酸化物半導体層の側面に接して覆っていることを特徴とする半導体装置。

【請求項3】

請求項1または請求項2において、

前記酸化物半導体層は、前記酸化物半導体層の表面に概略垂直なc軸を有している結晶を含むことを特徴とする半導体装置。

【請求項4】

請求項1乃至請求項3のいずれか一において、

前記酸化物半導体以外の材料は、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素を含むことを特徴とする半導体装置。

【請求項1】

酸化物半導体以外の材料により形成された第1のトランジスタと、

前記第1のトランジスタを含む周辺回路と、

酸化物半導体により形成された第2のトランジスタと、

前記第2のトランジスタと電気的に接続された容量素子と、

前記第2のトランジスタと前記容量素子により形成された記憶素子と、を有し、

前記第2のトランジスタは、

絶縁層に第1のトレンチ及び第2のトレンチと、

前記第1のトレンチの底面及び内壁面に接する酸化物半導体層と、

前記酸化物半導体層上にゲート絶縁層と、

前記ゲート絶縁層上にゲート電極と、

前記第2のトレンチの底面及び内壁面上に前記ゲート絶縁層と、

前記第2のトレンチ内を充填する絶縁層と、

前記酸化物半導体層に接するソース電極またはドレイン電極と、を有し、

前記周辺回路の上に、前記記憶素子が積層されることを特徴とする半導体装置。

【請求項2】

請求項1において、

前記ゲート絶縁層は、前記酸化物半導体層の側面に接して覆っていることを特徴とする半導体装置。

【請求項3】

請求項1または請求項2において、

前記酸化物半導体層は、前記酸化物半導体層の表面に概略垂直なc軸を有している結晶を含むことを特徴とする半導体装置。

【請求項4】

請求項1乃至請求項3のいずれか一において、

前記酸化物半導体以外の材料は、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素を含むことを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図17】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図17】

【図15】

【図16】

【公開番号】特開2012−256835(P2012−256835A)

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願番号】特願2012−11677(P2012−11677)

【出願日】平成24年1月24日(2012.1.24)