半導体装置

【課題】占有面積が小さく、冗長性があり、かつリーク電流の小さい保護回路を提供する。

【解決手段】保護回路は、複数の非線形素子が重畳するように積層され、かつ該非線形素子が電気的に直列接続されている構成であり、該保護回路に含まれる少なくとも一つの非線形素子は、チャネル形成領域に酸化物半導体を用いたトランジスタをダイオード接続した素子であり、他の非線形素子は、チャネル形成領域にシリコンを用いたトランジスタをダイオード接続した素子、または、接合領域にシリコンを用いたダイオードとする。

【解決手段】保護回路は、複数の非線形素子が重畳するように積層され、かつ該非線形素子が電気的に直列接続されている構成であり、該保護回路に含まれる少なくとも一つの非線形素子は、チャネル形成領域に酸化物半導体を用いたトランジスタをダイオード接続した素子であり、他の非線形素子は、チャネル形成領域にシリコンを用いたトランジスタをダイオード接続した素子、または、接合領域にシリコンを用いたダイオードとする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、静電気放電などの予期しない高電圧の印加に対して回路の破壊を防ぐ手段を備えた半導体装置に関する。なお、本明細書において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。例えば、表示装置、撮像装置、記憶装置及び演算装置、並びにそれらを用いた電子機器は全て半導体装置である。

【背景技術】

【0002】

半導体装置に用いられる半導体回路は、静電気放電(Electro Static Discharge、以下、「ESD」と呼ぶ。)によって半導体素子や電極などが破壊されることがある。このESDによる半導体回路の破壊防止対策として、多くの半導体回路には、保護回路が接続されている。保護回路は、端子や配線などに印加された過剰な電圧が半導体回路に供給されることを防ぐための回路である。保護回路に用いられる代表的な素子には、抵抗素子、ダイオード、トランジスタ、容量素子などがある。

【0003】

また、保護回路を設けることで、信号や電源電圧と共にノイズが配線等に入力された場合であっても、該ノイズによる後段の半導体回路の誤動作の防止が可能であり、また該ノイズによる半導体素子の劣化又は破壊を防ぐこともできる。

【0004】

例えば、特許文献1では、半導体回路と接続端子との間に、抵抗素子及びダイオードを含む保護回路を接続することで、ESDにより発生したサージ電流の平滑化及び放電経路の確保を行い、サージ電流の半導体回路への流入を防止する技術が開示されている。

【0005】

また、特許文献2では、表示装置の走査電極と表示部の外周に配置した導電線との間に、ソースとゲートを短絡させたMOS型トランジスタと、ゲートとドレインを短絡させたMOS型トランジスタとを直列に接続した保護回路を接続する技術が開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−58762号公報

【特許文献2】特開平7−92448号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

半導体装置の小型化、高集積化に伴い、保護回路の占有面積を小さくすることが望まれている。しかしながら、保護回路に用いる素子を小型化するとサージ耐性が低下してしまい、保護回路そのものが破壊されてしまうことがある。

【0008】

また、代表的な半導体材料であるシリコンを用いた素子(ダイオード、トランジスタなど)では、オフ状態でのリーク電流が比較的大きい。そのため、半導体回路に接続される配線(信号線など)と電源線との間に該素子で形成した保護回路を接続した場合、該配線間にリーク電流が流れ、該配線の電位や電源電位が変化し、半導体装置の動作を不安定にさせることがある。

【0009】

したがって、本発明の一態様では、占有面積が小さく、冗長性のある保護回路を提供することを目的の一つとする。また、リーク電流の小さい保護回路を提供することを目的の一つとする。

【課題を解決するための手段】

【0010】

本明細書に開示する本発明の一態様は、シリコンを用いた半導体素子、及び酸化物半導体を用いた半導体素子で構成された保護回路を有する半導体装置に関する。

【0011】

本明細書に開示する本発明の一態様は、基板上に、第1の配線と、第2の配線と、第3の配線と、第1の非線形素子及び第3の非線形素子を含む第1の保護回路と、第2の非線形素子及び第4の非線形素子を含む第2の保護回路と、を有し、第1の保護回路は、基板側から順に第1の非線形素子及び第3の非線形素子が重畳するように積層され、かつ該二つの非線形素子が電気的に直列接続されている構成であり、第2の保護回路は、基板側から順に第2の非線形素子及び第4の非線形素子が重畳するように積層され、かつ該二つの非線形素子が電気的に直列接続されている構成であり、第1の保護回路は、該保護回路を構成する第1の非線形素子及び第3の非線形素子が、第1の配線の電位が第2の配線の電位よりも高いときに順方向バイアスとなるように、第1の配線と第2の配線との間に電気的に接続され、第2の保護回路は、該保護回路を構成する第2の非線形素子及び第4の非線形素子が、第1の配線の電位が第3の配線の電位よりも低いときに順方向バイアスとなるように、第1の配線と第3の配線との間に電気的に接続されていることを特徴とする半導体装置である。

【0012】

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0013】

上記第1の配線は半導体回路に信号を入力するための信号線、第2の配線は高電位電源線、第3の配線は低電位電源線または接地電位線とすることができる。

【0014】

また、第1の非線形素子及び第2の非線形素子には、チャネル形成領域をシリコンで形成したトランジスタ、第3の非線形素子及び第4の非線形素子には、チャネル形成領域を化合物半導体で形成したトランジスタを用いることができる。特に、該化合物半導体として酸化物半導体を用いると、トランジスタのオフ電流は極めて小さくなる。したがって、配線間に接続される保護回路に該トランジスタを用いると、該配線間のリーク電流を低減することができる。

【0015】

また、該シリコンを用いたトランジスタには、オフ電流の低いpチャネル型トランジスタを用いることが好ましい。なお、第1乃至第4の非線形素子は、ドレインまたはソースの一方とゲート電極を短絡させて一方の端子とし、ドレインまたはソースの他方を他方の端子とする二端子素子として用いる。

【0016】

また、第1の非線形素子及び第2の非線形素子には、シリコンを用いて形成したダイオードを用いても良い。

【発明の効果】

【0017】

本発明の一態様である保護回路は、複数の非線形素子が積層された構成であるため、保護回路の占有面積を小さくすることができる。また、該複数の非線形素子は電気的に直列接続されているため、短絡不良に対して冗長性を有する。また、保護回路に用いる非線形素子のうちの少なくとも一つに、酸化物半導体を用いて形成したトランジスタを用いることで、保護回路が接続された配線間でのリーク電流を低減し、電源電位または信号の電位を安定にすることができる。

【図面の簡単な説明】

【0018】

【図1】半導体装置に用いる保護回路、及び該保護回路と配線との接続形態を説明する図。

【図2】半導体装置に用いる保護回路を説明する回路図。

【図3】半導体装置に用いる保護回路を説明する回路図。

【図4】半導体装置に用いる保護回路を説明する回路図。

【図5】半導体装置に用いる保護回路の作製方法を説明する工程断面図。

【図6】半導体装置に用いる保護回路の作製方法を説明する工程断面図。

【図7】半導体装置に用いる保護回路の作製方法を説明する工程断面図。

【図8】トランジスタの構造を説明する図。

【図9】メモリセルを説明する図。

【図10】電子機器を説明する図。

【図11】半導体装置に用いる保護回路を説明する断面図。

【図12】酸化物材料の結晶構造を説明する図。

【図13】酸化物材料の結晶構造を説明する図。

【図14】酸化物材料の結晶構造を説明する図。

【図15】計算によって得られた移動度のゲート電圧依存性を説明する図。

【図16】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

【図17】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

【図18】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

【図19】計算に用いたトランジスタの断面構造を説明する図。

【図20】酸化物半導体層を用いたトランジスタ特性のグラフ。

【図21】試料1のトランジスタのBT試験後のVg−Id特性を示す図。

【図22】試料2であるトランジスタのBT試験後のVg−Id特性を示す図。

【図23】試料Aおよび試料BのXRDスペクトルを示す図。

【図24】トランジスタのオフ電流と測定時基板温度との関係を示す図。

【図25】Idおよび電界効果移動度のVg依存性を示す図。

【図26】基板温度としきい値電圧の関係および基板温度と電界効果移動度の関係を示す図。

【図27】半導体装置の上面図及び断面図。

【図28】半導体装置の上面図及び断面図。

【発明を実施するための形態】

【0019】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。

【0020】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0021】

(実施の形態1)

本実施の形態では、本発明の一態様における半導体装置に用いる保護回路の構成及び動作方法について説明する。

【0022】

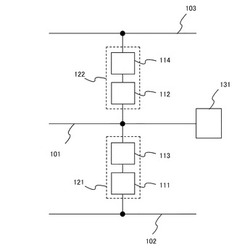

図1は、本発明の一態様における半導体装置に用いる保護回路、及び該保護回路と配線との接続形態を示すものである。第1の保護回路121は、第1の非線形素子111及び第3の非線形素子113を有する。また、第2の保護回路122は、第2の非線形素子112及び第4の非線形素子114を有する。本発明の一態様における半導体装置は、半導体回路131に接続される第1の配線101、並びに第2の配線102及び第3の配線103を有し、第1の保護回路121は、第1の配線101と第2の配線102との間に電気的に接続され、第2の保護回路122は、第1の配線101と第3の配線103との間に電気的に接続される。

【0023】

第1の配線101は、半導体回路131に信号を入力するための信号線、第2の配線102は高電位電源線(VDD)、第3の配線103は低電位電源線(VSS)または接地電位線(GND)とすることができる。

【0024】

なお、上記非線形素子とは、印加電圧に対して電流が比例しない素子のことをいう。例えば、ダイオードではアノードの電位をカソードの電位よりも高くすることで順方向バイアスとなり、電流を流すことが容易になる。一方、カソードの電位をアノードの電位よりも高くすることで逆方向バイアスとなり、順方向バイアスと比べると電流を流すことがほとんどできなくなる。

【0025】

第1の保護回路121は、直列に接続された第1の非線形素子111及び第3の非線形素子113を有し、第1の配線101の電位が第2の配線102の電位よりも高いときに該二つの非線形素子が順方向バイアスとなるように第1の配線101と第2の配線102との間に接続される。

【0026】

第2の保護回路122は、直列に接続された第2の非線形素子112及び第4の非線形素子114を有し、第1の配線101の電位が第3の配線103の電位よりも低いときに該二つの非線形素子が順方向バイアスとなるように第1の配線101と第3の配線103との間に接続される。

【0027】

このような形態で第1の保護回路121及び第2の保護回路122を第1の配線101に接続することで、ESDなどの高いサージ電圧が第1の配線101に印加された場合でも、該保護回路が放電経路となり、サージ電流が半導体回路131に流れることを防ぐことができる。

【0028】

例えば、正のサージ電圧が第1の配線101に印加された場合、第1の保護回路121が順方向バイアスとなるため、第1の配線101から第2の配線102へ電流が流れる。また、負のサージ電圧が第1の配線101に印加された場合、第2の保護回路122が順方向バイアスとなるため、第3の配線103から第1の配線101へ電流が流れる。このようにしてESD等で第1の配線101に供給された電荷を打ち消し、半導体回路131への不要な電荷の流入を防ぐことができる。

【0029】

次に、保護回路の具体例を説明する。図2は、第1の保護回路121及び第2の保護回路122に用いる非線形素子として、ドレイン電極またはソース電極の一方とゲート電極を短絡し、ダイオード接続としたトランジスタを用いる場合の例である。図2においては、第1の非線形素子201及び第2の非線形素子202にpチャネル型のトランジスタ、第3の非線形素子203及び第4の非線形素子204にnチャネル型のトランジスタを用いる例を示している。本発明の一態様では、第1の非線形素子201及び第2の非線形素子202にチャネル形成領域にシリコンを用いたトランジスタを適用するため、第1の非線形素子201及び第2の非線形素子202には、nチャネル型トランジスタよりもオフ電流が低いpチャネル型トランジスタを用いることが好ましい。ただし、図3に示すように、第1の非線形素子301及び第2の非線形素子302をnチャネル型のトランジスタで構成しても良い。

【0030】

また、図4のように、第1の非線形素子401及び第2の非線形素子402を接合領域にシリコンを用いたダイオードとしても良い。なお、図2乃至図4の構成は自由に組み合わせることができる。例えば、第1の保護回路121をnチャネル型のトランジスタ及びpチャネル型のトランジスタで構成し、第2の保護回路122を二つのnチャネル型トランジスタで構成しても良い。

【0031】

また、該保護回路を構成する非線形素子の素子数は二つ以上であり、それらが電気的に直列接続されていれば良い。非線形素子の素子数を複数とすることで、一つの非線形素子が製造工程における工程不良、またはESDなどによる破壊などにより短絡した場合でも保護回路として機能させることができる。すなわち、冗長性を持たせることができる。なお、該非線形素子のうち、一つ以上は、後述するオフ電流の極めて小さいトランジスタで構成することが好ましい。また、該保護回路は直列接続された複数の非線形素子を一単位として、複数の単位を並列接続する構成であっても良い。非線形素子を並列接続することで保護回路全体に流せる電流が多くなり、非線形素子の破壊を抑えることができる。

【0032】

また、該保護回路に用いる複数の非線形素子は、できるだけ最小面積となるように、それぞれが重畳するように形成する。このように複数の非線形素子を重畳させることで保護回路の占有面積を小さくすることができる。

【0033】

なお、通常動作時においては、該保護回路に用いられる非線形素子が逆バイアス、または配線間の電位差が非線形素子の動作電圧を超えない状態であるため、該保護回路は基本的には動作しない。しかしながら、逆方向バイアスでも僅かな電流が流れるため、各配線間でリーク電流が流れ、電源線の電位または信号線の電位に変化が生じてしまうことがある。

【0034】

特に、シリコンを用いたダイオードやトランジスタでは、その逆方向電流やオフ電流が比較的大きく、上述の配線の電位変化が起きやすい。そのため、本発明の一態様では、保護回路に用いる非線形素子の一つ以上にオフ電流の極めて小さいトランジスタを用いる。

【0035】

オフ電流が極めて小さいトランジスタとしては、シリコンよりも広いバンドギャップを有する半導体をチャネル形成領域に用いたトランジスタが挙げられる。シリコンよりも広いバンドギャップを有する半導体としては化合物半導体があり、例えば、酸化物半導体、窒化物半導体などが知られている。

【0036】

具体的には、非常に高いオフ抵抗を得るためには、シリコン(バンドギャップ1.1eV)では不十分であり、バンドギャップが2.5eV以上4eV以下、好ましくは3eV以上3.8eV以下のワイドバンドギャップ半導体を使用すると良い。例えば、チャネルが形成される半導体層に酸化インジウム、酸化亜鉛等を含む酸化物半導体、窒化ガリウム等を含む窒化物半導体、硫化亜鉛等を含む硫化物半導体等を用いることができる。

【0037】

トランジスタのオフ抵抗は、チャネルが形成される半導体層において、熱的に励起されるキャリアの濃度に反比例する。ドナーやアクセプタによるキャリアが全く存在しない状態(真性半導体)であっても、シリコンの場合にはバンドギャップが1.1eVなので、室温(300K)での熱励起キャリアの濃度は1×1011cm−3程度である。

【0038】

一方、バンドギャップ3.2eVの半導体では熱励起キャリアの濃度は1×10−7cm−3程度となる。電子移動度が同じ場合、抵抗率は、キャリア濃度に反比例するので、バンドギャップ3.2eVの半導体の抵抗率は、シリコンより18桁も大きくなる。このような化合物半導体としては、例えばIn−Ga−Zn−O系やIn−Sn−Zn−O系の酸化物半導体が知られている。

【0039】

したがって、保護回路を構成する非線形素子の一つに上述したような化合物半導体で形成したトランジスタを用いれば、直列に接続される他の非線形素子がシリコンで形成されていてもリーク電流は小さくすることができ、保護回路が接続される配線の電位変化を抑制することができる。つまり、図2乃至図4の構成の保護回路においては、第3の非線形素子203及び第4の非線形素子204に化合物半導体で形成したトランジスタを用いることが好ましい。

【0040】

なお、本発明の一態様における半導体装置は、シリコンで形成された素子上に化合物半導体(例えば、酸化物半導体)で形成された素子が設けられている構成であることが好ましい。このような構成においては、保護回路を形成するための特別な工程を必要とせず、他の素子と同一工程で保護回路を形成することができる。もちろん、保護回路のみに化合物半導体を用いる構成であっても良い。

【0041】

該半導体装置としては、駆動回路部がシリコンを用いた素子で形成され、画素回路部が化合物半導体を用いた素子で形成された表示装置または撮像装置、記憶回路部がシリコンを用いた素子及び化合物半導体を用いた素子で形成された記憶装置、駆動回路部または演算回路部がシリコンを用いた素子で形成され、記憶回路部が化合物半導体を用いた素子で形成された記憶装置または演算装置などがある。該半導体装置は、化合物半導体を用いた素子の極めて小さいオフ電流特性を利用して、電位保持部の保持特性を向上させたものである。

【0042】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0043】

(実施の形態2)

本実施の形態では、実施の形態1に示した保護回路の作製方法の一例について説明する。なお、本実施の形態では、酸化物半導体を用いるトランジスタをノンセルフアラインのトップゲート型で作製する方法を一例として説明するが、トランジスタの構造はこれに限るものではなく、セルフアラインのトップゲート型、またはボトムゲート型の構造であっても良い。

【0044】

まず、単結晶シリコン基板500に絶縁層540(フィールド酸化膜とも言う)で分離した素子形成領域を形成する。素子分離領域の形成は、LOCOS法(Local Oxidation of Silicon)法)やSTI法(Shallow Trench Isolation)等を用いることができる。

【0045】

ここで基板は単結晶シリコン基板に限らず、SOI(Silicon on Insulator)基板等を用いることもできる。

【0046】

次に、素子形成領域を覆うようにゲート絶縁層となる第1の絶縁層536を形成する。例えば、熱処理を行い単結晶シリコン基板500に設けられた素子形成領域の表面を酸化させることにより酸化シリコン膜を形成することができる。また、熱酸化法により酸化シリコン膜を形成した後に、窒化処理を行うことによって酸化シリコン膜の表面を窒化させることにより、酸化シリコン膜と酸素と窒素を有する膜(酸窒化シリコン膜)との積層構造で形成してもよい。

【0047】

他の方法としては、例えば、単結晶シリコン基板500に設けられた素子形成領域の表面に高密度プラズマ処理により酸化処理または窒化処理を行うことにより、第1の絶縁層536として酸化シリコン膜または窒化シリコン膜を形成することができる。また、高密度プラズマ処理により素子形成領域の表面に酸化処理を行った後に、再度高密度プラズマ処理を行うことによって窒化処理を行ってもよい。この場合、素子形成領域の表面に接して酸化シリコン膜が形成され、当該酸化シリコン膜上に酸窒化シリコン膜が形成され、第1の絶縁層536は酸化シリコン膜と酸窒化シリコン膜とが積層された膜となる。

【0048】

次に、第1の絶縁層536を覆うように導電層を形成する。ここでは、導電層538aと導電層538bを順に積層して形成する。ここで、導電層は二層に限らず、単層または三層以上の積層構造としても良い。

【0049】

導電層538a、538bとしては、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素またはこれらの元素を主成分とする合金材料若しくは化合物材料を用いることができる。また、これらの元素を窒化した金属窒化膜を用いることもできる。他にも、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体材料を用いることもできる。

【0050】

ここでは、導電層538aとして窒化タンタルを形成し、その上に導電層538bとしてタングステンを形成して積層構造を設ける。なお、導電層538aとしては、窒化タングステン、窒化モリブデン、窒化チタンから選ばれた単層または積層膜を用いることができる。また、導電層538bとしては、タンタル、モリブデン、チタンから選ばれた単層または積層膜を用いることができる。

【0051】

次に、積層して設けられた導電層538a、538bを選択的にエッチングして、第1の絶縁層536上にゲート電極538、558を形成する。

【0052】

次に、素子形成領域以外を覆うようにレジストマスクを選択的に形成し、該レジストマスク及びゲート電極538、558をマスクとして不純物元素を導入することによってp+領域532a、532b、552a、552bを形成する。ここでは、pチャネル型のバルクトランジスタを形成するため、不純物元素としては、p型を付与する不純物元素であるホウ素(B)等を用いることができる。

【0053】

そして、層間絶縁層及び保護層として機能する第2の絶縁層539を成膜する。第2の絶縁層539としては、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、または窒化酸化シリコン膜などを用いることができる。

【0054】

この段階で、図5(A)に示すように、チャネル形成領域にシリコンを用いたトランジスタである第1の非線形素子201及び第2の非線形素子202の構造が完成する。

【0055】

次に、第1の非線形素子201及び第2の非線形素子202のソース領域またはドレイン領域の一方、ソース領域またはドレイン領域の他方、及びゲート電極538、558のそれぞれに通じるコンタクトホールを第2の絶縁層539に形成する。該コンタクトホールは、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。

【0056】

そして、接続配線541a、541b、561a、561bを形成する。このとき、接続配線541aによって、第1の非線形素子201のソース領域またはドレイン領域の一方とゲート電極538を短絡させ、接続配線561aによって、第2の非線形素子202のソース領域またはドレイン領域の一方とゲート電極558を短絡させる。

【0057】

該接続配線は、スパッタ法などの成膜方法により導電膜を形成した後、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。該導電膜に用いられる材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステン等から選ばれた元素、または上述した元素を成分とする合金、または上述した元素を組み合わせた合金などが上げられる。また、該導電膜は単層でも2層以上の積層としてもよい。例えば、アルミニウムや銅などの金属膜の下側、または上側、若しくはその両方にクロム、タンタル、チタン、モリブデン、タングステン等の高融点金属膜を積層する構成とすることもできる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

【0058】

次に、該接続配線及び第2の絶縁層539上に、層間絶縁層及び平坦化層として機能する第3の絶縁層544を形成する(図5(B)参照)。第3の絶縁層544は、プラズマCVD法やスパッタ法で酸化シリコン膜などを形成した後、CMP(Chemical Mechanical Polishing)法等によって平坦化処理を行うことで形成することができる。

【0059】

また、第3の絶縁層544としては、ポリイミド系樹脂、アクリル系樹脂、ベンゾシクロブテン系樹脂、ポリアミド系樹脂、エポキシ系樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low−k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁層を複数積層させることで、第3の絶縁層544を形成してもよい。

【0060】

なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi−O−Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基(例えばアルキル基やアリール基)やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。

【0061】

これらの材料を用いた第3の絶縁層544の形成法は、特に限定されず、その材料に応じて、SOG法、スピンコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法等)、スクリーン印刷法、オフセット印刷法、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコーター等を用いることができる。

【0062】

次に、第1の非線形素子201及び第2の非線形素子202上に形成する酸化物半導体層を用いたトランジスタの作製方法について説明する。

【0063】

まず、第3の絶縁層544上に第4の絶縁層521を形成する。第4の絶縁層521は、下層からの不純物の拡散を抑制する機能を有する。

【0064】

また、第4の絶縁層521には、酸素を含む絶縁層を用いることが好ましい。例えば、酸化シリコン、酸化ガリウム、酸化ガリウムアルミニウム、酸化ガリウム亜鉛、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、酸化ハフニウム、またはこれらの混合材料を用いて単層で、または積層して形成する。第4の絶縁層521に酸素を含む絶縁層を用いることで、後述する酸化物半導体層の酸素欠損に対して酸素の補填を容易に行うことができる。これらの絶縁層は、プラズマCVD法やスパッタ法などの各種成膜方法で形成することができる。

【0065】

次に、第4の絶縁層521上に半導体層502、522を形成する。本実施の形態では、In−Ga−Zn−O系酸化物ターゲットを用いて、In−Ga−Zn−O系酸化物半導体層をスパッタ法により成膜し、公知のフォトリソグラフィ法及びエッチング法を用いて、島状の半導体層502、522を形成する(図5(C)参照)。

【0066】

用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0067】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0068】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属の酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する)、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0069】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0070】

また、酸化物半導体として、InMO3(ZnO)m(m>0、且つ、mは整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In3SnO5(ZnO)n(n>0、且つ、nは整数)で表記される材料を用いてもよい。

【0071】

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)あるいはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子数比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子数比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

【0072】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0073】

例えば、In−Sn−Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In−Ga−Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

【0074】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物の組成の近傍であるとは、a、b、cが、

(a―A)2+(b―B)2+(c―C)2≦r2

を満たすことをいい、rは、例えば、0.05とすればよい。他の酸化物でも同様である。

【0075】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0076】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0077】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0078】

なお、Raは、JIS B0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

【0079】

【数1】

【0080】

なお、上記において、S0は、測定面(座標(x1,y1)(x1,y2)(x2,y1)(x2,y2)で表される4点によって囲まれる長方形の領域)の面積を指し、Z0は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて評価可能である。

【0081】

In−Ga−Zn−O系酸化物半導体層をスパッタ法で成膜する際に用いる成膜用ターゲットには、例えば、組成比として、In2O3:Ga2O3:ZnO=1:1:1[mol数比]の金属酸化物を用いることができる。また、In2O3:Ga2O3:ZnO=1:1:2[mol数比]の金属酸化物を用いてもよい。

【0082】

また、酸化物半導体としてIn−Zn−O系の材料を用いる場合、用いるターゲットの組成比は、原子数比で、In:Zn=50:1〜1:2(mol数比に換算するとIn2O3:ZnO=25:1〜1:4)、好ましくはIn:Zn=20:1〜1:1(mol数比に換算するとIn2O3:ZnO=10:1〜1:2)、さらに好ましくはIn:Zn=15:1〜1.5:1(mol数比に換算するとIn2O3:ZnO=15:2〜3:4)とする。例えば、In−Zn−O系酸化物半導体の形成に用いるターゲットは、原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとする。

【0083】

また、In−Sn−Zn−O系の材料膜の形成に用いる酸化物半導体のターゲットの組成比は、In:Sn:Znが原子数比で、1:2:2、2:1:3、1:1:1、或いは20:45:35などを用いることができる。

【0084】

ここで、酸化物半導体層にはアルカリ金属、水素原子、水素分子、水、水酸基、または水素化合物などの不純物ができるだけ混入しないように形成することが好ましい。例えば、スパッタ成膜用ターゲットや成膜に用いるガスに上記不純物が混入しないようにする。スパッタガスにアルゴン及び酸素を用いる場合は、純度9Nのアルゴン(露点−121℃、H2O;0.1ppb、H2;0.5ppb)及び純度8Nの酸素(露点−112℃、H2O;1ppb、H2;1ppb)を用いることが好ましい。

【0085】

また、成膜の際、成膜装置内を十分排気し、成膜時に基板を加熱しながら成膜することにより、成膜された酸化物半導体層に含まれる不純物濃度を低減することができる。また、酸化物半導体層に加熱処理をして酸化物半導体層中の水分及び水素を脱離しても良い。なお、該加熱処理は、酸化物半導体層の成膜後であれば、どの時点で行っても良い。なお、該加熱処理後の酸化物半導体層中の水素濃度を5×1019/cm3以下、好ましくは5×1018/cm3以下とすることで、電気特性及び動作の信頼性の高いトランジスタ等の素子を作製することができる。

【0086】

酸化物半導体層としては、結晶性部分と非結晶性部分とを有し、結晶性部分の配向がc軸配向に揃っている酸化物半導体であるCAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜を用いてもよい。

【0087】

CAAC−OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC−OS膜は、非晶質相に結晶部を有する結晶−非晶質混相構造の酸化物半導体層である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0088】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0089】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体層の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0090】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に熱処理などの結晶化処理を行うことにより形成される。

【0091】

CAAC−OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

【0092】

なお、酸化物半導体層を構成する酸素の一部は窒素で置換されてもよい。

【0093】

また、CAAC−OS膜のように結晶部を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0094】

CAAC−OS膜の結晶構造の一例について図12乃至図14を用いて詳細に説明する。なお、特に断りがない限り、図12乃至図14は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図12において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

【0095】

図12(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図12(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図12(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図12(A)に示す小グループは電荷が0である。

【0096】

図12(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図12(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図12(B)に示す構造をとりうる。図12(B)に示す小グループは電荷が0である。

【0097】

図12(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図12(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図12(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあってもよい。図12(C)に示す小グループは電荷が0である。

【0098】

図12(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図12(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図12(D)に示す小グループは電荷が+1となる。

【0099】

図12(E)に、2個のZnを含む小グループを示す。図12(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図12(E)に示す小グループは電荷が−1となる。

【0100】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

【0101】

ここで、これらの小グループ同士が結合する規則について説明する。図12(A)に示す6配位のInの上半分の3個のOは、下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Inを有する。図12(B)に示す5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。図12(C)に示す4配位のZnの上半分の1個のOは、下方向に1個の近接Znを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。したがって、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)、または4配位の金属原子(Zn)のいずれかと結合することになる。

【0102】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0103】

図13(A)に、In−Sn−Zn−O系の層構造を構成する中グループのモデル図を示す。図13(B)に、3つの中グループで構成される大グループを示す。なお、図13(C)は、図13(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0104】

図13(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図13(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図13(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0105】

図13(A)において、In−Sn−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0106】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ−0.667、−0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。したがって、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷−1が必要となる。電荷−1をとる構造として、図12(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0107】

具体的には、図13(B)に示した大グループが繰り返されることで、In−Sn−Zn−O系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn−O系の層構造は、In2SnZn2O7(ZnO)m(mは0または自然数。)とする組成式で表すことができる。

【0108】

また、このほかにも、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物や、三元系金属の酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する。)、In−Al−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物や、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物や、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物や、In−Ga系酸化物などを用いた場合も同様である。

【0109】

例えば、図14(A)に、In−Ga−Zn−O系の層構造を構成する中グループのモデル図を示す。

【0110】

図14(A)において、In−Ga−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

【0111】

図14(B)に3つの中グループで構成される大グループを示す。なお、図14(C)は、図14(B)の層構造をc軸方向から観察した場合の原子配列を示している。

【0112】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0113】

また、In−Ga−Zn−O系の層構造を構成する中グループは、図14(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

【0114】

また、成膜時においては、スパッタガス中の酸素比率を高めて成膜することが好ましい。例えば、スパッタガスにアルゴンと酸素を用いる場合は、酸素の流量比率を30%以上とすることでCAAC−OS膜を構成する結晶の結晶性を高めることができ、かつ膜中の酸素欠損への酸素の補填を行うことができる。また、150℃以上の高温で成膜することで、CAAC−OS膜を構成する結晶の結晶性を更に高めることができる。

【0115】

また、膜形成後の加熱処理においては、窒素雰囲気または減圧下で加熱処理した後、酸素雰囲気または窒素と酸素の混合雰囲気で加熱処理することによりCAAC−OS膜中の酸素を過剰とし、効果的に酸素欠損を補填することができる。なお、該加熱処理の温度は、450℃程度であることが好ましい。

【0116】

上述したCAAC−OS膜を用いたトランジスタ等の素子は電気特性が向上し、更に動作の信頼性を高めることができる。

【0117】

次に、接続配線541b、561bのそれぞれに通じるコンタクトホールを第4の絶縁層521及び第3の絶縁層544に形成する。該コンタクトホールは、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。

【0118】

そして、トランジスタのソースまたはドレインの一方の電極504、524、及びソースまたはドレインの他方の電極506、526を形成する。このとき、ソースまたはドレインの他方の電極506は、コンタクトホールを通じて接続配線541bと電気的に接続され、ソースまたはドレインの他方の電極526は、コンタクトホールを通じて接続配線561bと電気的に接続される。

【0119】

該ソースまたはドレインの電極は、スパッタ法などの成膜方法により導電膜を形成した後、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。なお、該ソースまたはドレインの電極は、接続配線541a、541b、561a、561bと同様の材料を用いることができる。

【0120】

次に、該ソースまたはドレインの電極及び半導体層502、522を覆うようにゲート絶縁層として第5の絶縁層の518を形成する(図6(A)参照)。第5の絶縁層518には、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ガリウム、酸化ガリウムアルミニウム、酸化ガリウム亜鉛、酸化窒化アルミニウム、窒化酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化イットリウム、酸化ランタン、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSixOyNz(x>0、y>0、z>0))、窒素が添加されたハフニウムアルミネート(HfAlxOyNz(x>0、y>0、z>0))等の絶縁層を単層または積層で用いることができる。これらの絶縁層は、スパッタ法等で形成することができる。

【0121】

次に、第5の絶縁層518を介して半導体層502、522と重なるようにゲート電極508、528を形成する。該ゲート電極は、スパッタ法などの成膜方法により導電層を形成した後、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。なお、該導電層には、接続配線541a、541b、561a、561bと同様の材料を用いることができる。

【0122】

次に、第5の絶縁層518及びゲート電極508、528上に第6の絶縁層542を形成する(図6(B)参照)。第6の絶縁層542は、保護層として機能するものであり、第4の絶縁層521と同様の材料を用いることができる。特に、酸化アルミニウムを用いると半導体層中の酸素が放出されにくくなり、酸素欠損の生成を抑制することできる。

【0123】

この段階で、チャネル形成領域に酸化物半導体を用いたトランジスタである第3の非線形素子203及び第4の非線形素子204の構造が完成する。

【0124】

次に、第6の絶縁層542の表面から、第3の非線形素子203及び第4の非線形素子204のソースまたはドレインの一方の電極504、524、並びにゲート電極508、528のそれぞれに通じるコンタクトホールを形成する。該コンタクトホールは、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。

【0125】

そして、接続配線509、529を形成する。このとき、接続配線509によって、第3の非線形素子203のソースまたはドレインの一方の電極504とゲート電極508を短絡させ、接続配線529によって、第4の非線形素子204のソースまたはドレインの一方の電極524とゲート電極528を短絡させる。

【0126】

該接続配線は、スパッタ法などの成膜方法により導電膜を形成した後、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。該導電膜に用いられる材料としては、接続配線541a、541b、561a、561bと同様の材料を用いることができる。

【0127】

次に、接続配線509、529、及び第6の絶縁層542を覆うように第7の絶縁層546を形成する(図7(A)参照)。第7の絶縁層546は、第3の絶縁層544と同様の材料及び手段で形成することができる。なお、図7(A)では、第7の絶縁層546の表面を平坦化させた状態を例示しているが、平坦化させなくても良い。

【0128】

次に、第7の絶縁層546の表面から接続配線541a、561a、509、529に通じる複数のコンタクトホールを形成する。該コンタクトホールは、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。

【0129】

そして、該コンタクトホールの一つを通じて接続配線541aと電気的に接続する第2の配線102、該コンタクトホールの二つを通じて接続配線561a及び接続配線509と電気的に接続する第1の配線101、該コンタクトホールの一つを通じて接続配線529と電気的に接続する第3の配線103を形成する(図7(B)参照)。なお、第1の配線101、第2の配線102、第3の配線103を別途形成し、それらと接続する接続配線を設ける構成であっても良い。

【0130】

以上により、図2に示す構成の保護回路を作製することができる。

【0131】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0132】

(実施の形態3)

本実施の形態では、実施の形態2の酸化物半導体のトランジスタの作製方法で説明したトランジスタの形態とは異なる構造のトランジスタであり、実施の形態1及び2に示す、第3の非線形素子203及び第4の非線形素子204に適用可能なトランジスタの構造について説明する。

【0133】

図8(A)に示すトランジスタ901は、絶縁層902上に、活性層として機能する酸化物半導体層903、酸化物半導体層903上に形成されたソース電極904及びドレイン電極905、酸化物半導体層903、ソース電極904及びドレイン電極905上のゲート絶縁層906、並びにゲート絶縁層906上において酸化物半導体層903と重なる位置に設けられたゲート電極907を有する。

【0134】

図8(A)に示すトランジスタ901は、ゲート電極907が酸化物半導体層903の上に形成されているトップゲート型であり、かつ、ソース電極904及びドレイン電極905が酸化物半導体層903の上に形成されているトップコンタクト型である。そして、トランジスタ901は、ソース電極904及びドレイン電極905と、ゲート電極907とは重ならず、ソース電極904及びドレイン電極905とゲート電極907との間には、ゲート絶縁層906の膜厚よりも大きい間隔が設けられている。よって、トランジスタ901は、ソース電極904及びドレイン電極905とゲート電極907との間に形成される寄生容量を小さく抑えることができ、高速動作を実現することができる。

【0135】

また、酸化物半導体層903は、ゲート電極907が形成された後に酸化物半導体層903にn型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域908を有する。また、酸化物半導体層903のうち、ゲート絶縁層906を間に挟んでゲート電極907と重なる領域がチャネル形成領域909である。酸化物半導体層903では、一対の高濃度領域908の間にチャネル形成領域909が設けられている。高濃度領域908を形成するためのドーパントの添加は、イオン注入法を用いることができる。ドーパントは、例えばヘリウム、アルゴン、キセノンなどの希ガスや、窒素、リン、ヒ素、アンチモンなどの15族原子などを用いることができる。

【0136】

例えば、窒素をドーパントとして用いた場合、高濃度領域908中の窒素原子の濃度は、5×1019/cm3以上1×1022/cm3以下であることが望ましい。

【0137】

n型の導電性を付与するドーパントが添加されている高濃度領域908は、酸化物半導体層903中の他の領域に比べて導電率が高くなる。よって、高濃度領域908を酸化物半導体層903に設けることで、ソース電極904とドレイン電極905の間の抵抗を下げることができる。

【0138】

また、In−Ga−Zn−O系酸化物半導体を酸化物半導体層903に用いた場合、窒素を添加した後、300℃以上600℃以下で1時間程度加熱処理を施すことにより、高濃度領域908中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。高濃度領域908中の酸化物半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域908の導電性を高め、ソース電極904とドレイン電極905の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極904とドレイン電極905の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域908中の窒素原子の濃度は、1×1020/cm3以上であって、7atoms%以下とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。

【0139】

また、酸化物半導体層903は、CAAC−OS膜で構成されていても良い。酸化物半導体層903がCAAC−OS膜で構成されている場合、非晶質の場合に比べて酸化物半導体層903の導電率を高めることができるため、ソース電極904とドレイン電極905の間の抵抗を下げることができる。

【0140】

そして、ソース電極904とドレイン電極905の間の抵抗を下げることで、トランジスタ901の微細化を進めても、高いオン電流と、高速動作を確保することができる。また、トランジスタ901の微細化により、当該トランジスタを用いた素子の占める面積を縮小化し、半導体装置の集積密度を高めることができる。

【0141】

図11は、図2の構成の保護回路の第3の非線形素子203及び第4の非線形素子204に図8(A)のトランジスタ901を適用した場合の断面図である。以降に説明する図8(B)、(C)、(D)のトランジスタについても、図11に示す図8(A)のトランジスタと同様に第3の非線形素子203及び第4の非線形素子204に適用することができる。

【0142】

図8(B)に示すトランジスタ911は、絶縁層912上に形成されたソース電極914及びドレイン電極915、ソース電極914及びドレイン電極915上に形成された活性層として機能する酸化物半導体層913、酸化物半導体層913、ソース電極914及びドレイン電極915上のゲート絶縁層916、並びにゲート絶縁層916上において酸化物半導体層913と重なる位置に設けられたゲート電極917を有する。

【0143】

図8(B)に示すトランジスタ911は、ゲート電極917が酸化物半導体層913の上に形成されているトップゲート型であり、かつ、ソース電極914及びドレイン電極915が酸化物半導体層913の下に形成されているボトムコンタクト型である。そして、トランジスタ911は、トランジスタ901と同様に、ソース電極914及びドレイン電極915と、ゲート電極917とが重なっていないため、ソース電極914及びドレイン電極915とゲート電極917との間に形成される寄生容量を小さく抑えることができ、高速動作を実現することができる。

【0144】

また、酸化物半導体層913は、ゲート電極917が形成された後に酸化物半導体層913にn型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域918を有する。また、酸化物半導体層913のうち、ゲート絶縁層916を間に挟んでゲート電極917と重なる領域がチャネル形成領域919である。酸化物半導体層913では、一対の高濃度領域918の間にチャネル形成領域919が設けられている。

【0145】

高濃度領域918は、上述した、トランジスタ901が有する高濃度領域908と同様に、イオン注入法を用いて形成することができる。そして、高濃度領域918を形成するためのドーパントの種類については、高濃度領域908の場合を参照することができる。

【0146】

例えば、窒素をドーパントとして用いた場合、高濃度領域918中の窒素原子の濃度は、5×1019/cm3以上1×1022/cm3以下であることが望ましい。

【0147】

n型の導電性を付与するドーパントが添加されている高濃度領域918は、酸化物半導体層913中の他の領域に比べて導電率が高くなる。よって、高濃度領域918を酸化物半導体層913に設けることで、ソース電極914とドレイン電極915の間の抵抗を下げることができる。

【0148】

また、In−Ga−Zn−O系酸化物半導体を酸化物半導体層913に用いた場合、窒素を添加した後、300℃以上600℃以下程度で加熱処理を施すことにより、高濃度領域918中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。高濃度領域918中の酸化物半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域918の導電性を高め、ソース電極914とドレイン電極915の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極914とドレイン電極915の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域918中の窒素原子の濃度は、1×1020/cm3以上であって、7atoms%以下とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。

【0149】

また、酸化物半導体層913は、CAAC−OS膜で構成されていても良い。酸化物半導体層913がCAAC−OS膜で構成されている場合、非晶質の場合に比べて酸化物半導体層913の導電率を高めることができるので、ソース電極914とドレイン電極915の間の抵抗を下げることができる。

【0150】

そして、ソース電極914とドレイン電極915の間の抵抗を下げることで、トランジスタ911の微細化を進めても、高いオン電流と、高速動作を確保することができる。また、トランジスタ911の微細化により、当該トランジスタを用いた素子の占める面積を縮小化し、半導体装置の集積密度を高めることができる。

【0151】

図8(C)に示すトランジスタ921は、絶縁層922上に、活性層として機能する酸化物半導体層923、酸化物半導体層923上に形成されたソース電極924及びドレイン電極925、酸化物半導体層923、ソース電極924及びドレイン電極925上のゲート絶縁層926、並びにゲート絶縁層926上において酸化物半導体層923と重なる位置に設けられたゲート電極927を有する。更に、トランジスタ921は、ゲート電極927の側部に設けられた、絶縁層で形成されたサイドウォール930を有する。

【0152】

図8(C)に示すトランジスタ921は、ゲート電極927が酸化物半導体層923の上に形成されているトップゲート型であり、かつ、ソース電極924及びドレイン電極925が酸化物半導体層923の上に形成されているトップコンタクト型である。そして、トランジスタ921は、トランジスタ901と同様に、ソース電極924及びドレイン電極925と、ゲート電極927とが重なっていないため、ソース電極924及びドレイン電極925とゲート電極927との間に形成される寄生容量を小さく抑えることができ、高速動作を実現することができる。

【0153】

また、酸化物半導体層923は、ゲート電極927が形成された後に酸化物半導体層923にn型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域928と、一対の低濃度領域929とを有する。また、酸化物半導体層923のうち、ゲート絶縁層926を間に挟んでゲート電極927と重なる領域がチャネル形成領域931である。酸化物半導体層923では、一対の高濃度領域928の間に一対の低濃度領域929が設けられ、一対の低濃度領域929の間にチャネル形成領域931が設けられている。そして、一対の低濃度領域929は、酸化物半導体層923中の、ゲート絶縁層926を間に挟んでサイドウォール930と重なる領域に設けられている。

【0154】

高濃度領域928及び低濃度領域929は、上述した、トランジスタ901が有する高濃度領域908の場合と同様に、イオン注入法を用いて形成することができる。そして、高濃度領域928を形成するためのドーパントの種類については、高濃度領域908の場合を参照することができる。

【0155】

例えば、窒素をドーパントとして用いた場合、高濃度領域928中の窒素原子の濃度は、5×1019/cm3以上1×1022/cm3以下、低濃度領域929中の窒素原子の濃度は、5×1018/cm3以上5×1019/cm3未満であることが望ましい。

【0156】

n型の導電性を付与するドーパントが添加されている高濃度領域928は、酸化物半導体層923中の他の領域に比べて導電率が高くなる。よって、高濃度領域928を酸化物半導体層923に設けることで、ソース電極924とドレイン電極925の間の抵抗を下げることができる。また、低濃度領域929をチャネル形成領域931と高濃度領域928の間に設けることで、短チャネル効果による閾値電圧のマイナスシフトを軽減することができる。

【0157】

また、In−Ga−Zn−O系酸化物半導体を酸化物半導体層923に用いた場合、窒素を添加した後、300℃以上600℃以下程度で加熱処理を施すことにより、高濃度領域928中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。さらに、低濃度領域929も、窒素の濃度によっては、上記加熱処理によりウルツ鉱型の結晶構造を有する場合もある。高濃度領域928中の酸化物半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域928の導電性を高め、ソース電極924とドレイン電極925の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極924とドレイン電極925の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域928中の窒素原子の濃度は、1×1020/cm3以上であって、7atoms%以下とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。

【0158】

また、酸化物半導体層923は、CAAC−OS膜で構成されていても良い。酸化物半導体層923がCAAC−OS膜で構成されている場合、非晶質の場合に比べて酸化物半導体層923の導電率を高めることができるので、ソース電極924とドレイン電極925の間の抵抗を下げることができる。

【0159】

そして、ソース電極924とドレイン電極925の間の抵抗を下げることで、トランジスタ921の微細化を進めても、高いオン電流と、高速動作を確保することができる。また、トランジスタ921の微細化により、当該トランジスタを用いた素子の占める面積を縮小化し、半導体装置の集積密度を高めることができる。

【0160】

図8(D)に示すトランジスタ941は、絶縁層942上に形成されたソース電極944及びドレイン電極945、ソース電極944及びドレイン電極945上に形成された活性層として機能する酸化物半導体層943、酸化物半導体層943、ソース電極944及びドレイン電極945上のゲート絶縁層946、並びにゲート絶縁層946上において酸化物半導体層943と重なる位置に設けられたゲート電極947を有する。更に、トランジスタ941は、ゲート電極947の側部に設けられた、絶縁層で形成されたサイドウォール950を有する。

【0161】

図8(D)に示すトランジスタ941は、ゲート電極947が酸化物半導体層943の上に形成されているトップゲート型であり、かつ、ソース電極944及びドレイン電極945が酸化物半導体層943の下に形成されているボトムコンタクト型である。そして、トランジスタ941は、トランジスタ901と同様に、ソース電極944及びドレイン電極945と、ゲート電極947とが重なっていないため、ソース電極944及びドレイン電極945とゲート電極947との間に形成される寄生容量を小さく抑えることができ、高速動作を実現することができる。

【0162】

また、酸化物半導体層943は、ゲート電極947が形成された後に酸化物半導体層943にn型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域948と、一対の低濃度領域949とを有する。また、酸化物半導体層943のうち、ゲート絶縁層946を間に挟んでゲート電極947と重なる領域がチャネル形成領域951である。酸化物半導体層943では、一対の高濃度領域948の間に一対の低濃度領域949が設けられ、一対の低濃度領域949の間にチャネル形成領域951が設けられている。そして、一対の低濃度領域949は、酸化物半導体層943中の、ゲート絶縁層946を間に挟んでサイドウォール950と重なる領域に設けられている。

【0163】

高濃度領域948及び低濃度領域949は、上述した、トランジスタ901が有する高濃度領域908の場合と同様に、イオン注入法を用いて形成することができる。そして、高濃度領域948を形成するためのドーパントの種類については、高濃度領域908の場合を参照することができる。

【0164】

例えば、窒素をドーパントとして用いた場合、高濃度領域948中の窒素原子の濃度は、5×1019/cm3以上1×1022/cm3以下、低濃度領域949中の窒素原子の濃度は、5×1018/cm3以上5×1019/cm3未満であることが望ましい。

【0165】

n型の導電性を付与するドーパントが添加されている高濃度領域948は、酸化物半導体層943中の他の領域に比べて導電率が高くなる。よって、高濃度領域948を酸化物半導体層943に設けることで、ソース電極944とドレイン電極945の間の抵抗を下げることができる。また、低濃度領域949をチャネル形成領域951と高濃度領域948の間に設けることで、短チャネル効果による閾値電圧のマイナスシフトを軽減することができる。

【0166】

また、In−Ga−Zn−O系酸化物半導体を酸化物半導体層943に用いた場合、窒素を添加した後、300℃以上600℃以下程度で加熱処理を施すことにより、高濃度領域948中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。さらに、低濃度領域949も、窒素の濃度によっては、上記加熱処理によりウルツ鉱型の結晶構造を有する場合もある。高濃度領域948中の酸化物半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域948の導電性を高め、ソース電極944とドレイン電極945の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極944とドレイン電極945の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域948中の窒素原子の濃度は、1×1020/cm3以上であって、7atoms%以下とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。

【0167】

また、酸化物半導体層943は、CAAC−OS膜で構成されていても良い。酸化物半導体層943がCAAC−OS膜で構成されている場合、非晶質の場合に比べて酸化物半導体層943の導電率を高めることができるので、ソース電極944とドレイン電極945の間の抵抗を下げることができる。

【0168】

そして、ソース電極944とドレイン電極945の間の抵抗を下げることで、トランジスタ941の微細化を進めても、高いオン電流と、高速動作を確保することができる。また、トランジスタ941の微細化により、当該トランジスタを用いた素子の占める面積を縮小化し、半導体装置の集積密度を高めることができる。

【0169】

なお、酸化物半導体を用いたトランジスタにおいて、ソース領域またはドレイン領域として機能する高濃度領域をセルフアラインプロセスにて作製する方法の一つとして、酸化物半導体層の表面を露出させて、アルゴンプラズマ処理をおこない、酸化物半導体層のプラズマにさらされた領域の抵抗率を低下させる方法が開示されている(S. Jeon et al. ”180nm Gate Length Amorphous InGaZnO Thin Film Transistor for High Density Image Sensor Applications”, IEDM Tech. Dig., pp.504−507, 2010.)。

【0170】

しかしながら、上記作製方法では、ゲート絶縁層を形成した後に、ソース領域またはドレイン領域となるべき部分を露出するべく、ゲート絶縁層を部分的に除去する必要がある。よって、ゲート絶縁層が除去される際に、下層の酸化物半導体層も部分的にオーバーエッチングされ、ソース領域またはドレイン領域となるべき部分の膜厚が小さくなってしまう。その結果、ソース領域またはドレイン領域の抵抗が増加し、また、オーバーエッチングによるトランジスタの特性不良が起こりやすくなる。

【0171】

トランジスタの微細化を進めるには、加工精度の高いドライエッチング法を採用する必要がある。しかし、上記オーバーエッチングは、酸化物半導体層とゲート絶縁層の選択比が十分に確保できないドライエッチング法を採用する場合に、顕著に起こりやすい。

【0172】

例えば、酸化物半導体層が十分な厚さであればオーバーエッチングも問題にはならないが、チャネル長を200nm以下とする場合には、短チャネル効果を防止する上で、チャネル形成領域となる部分の酸化物半導体層の厚さは20nm以下、好ましくは10nm以下であることが求められる。そのような薄い酸化物半導体層を扱う場合には、酸化物半導体層のオーバーエッチングは、上述したような、ソース領域またはドレイン領域の抵抗が増加、トランジスタの特性不良を生じさせるため、好ましくない。

【0173】

しかし、開示される発明の一態様のように、酸化物半導体層へのドーパントの添加を、酸化物半導体層を露出させず、ゲート絶縁層を残したまま行うことで、酸化物半導体層のオーバーエッチングを防ぎ、酸化物半導体層への過剰なダメージを軽減することができる。また、加えて、酸化物半導体層とゲート絶縁層の界面も清浄に保たれる。したがって、トランジスタの特性及び信頼性を高めることができる。

【0174】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0175】

(実施の形態4)

本実施の形態では、実施の形態1で説明した保護回路を用いることができる半導体装置の一例として、記憶装置の回路構成及びその動作について説明を行う。なお、本実施の形態の記憶装置は、シリコンを用いる素子と酸化物半導体を用いる素子から形成されるため、該保護回路を形成するための特別な工程を必要とせず、他の素子と同一工程で該保護回路を形成することができる。

【0176】

図9は記憶装置のメモリセルの回路図である。ここでは、第1のトランジスタ860をシリコンを用いて形成したpチャネル型トランジスタ、第2のトランジスタ862を酸化物半導体を用いて形成したnチャネル型トランジスタとする。

【0177】

図9(A)に示すメモリセルにおいて、第1の配線(L1)と第1のトランジスタ860のソース電極またはドレイン電極の一方、及び第2の配線(L2)と第1のトランジスタ860のソース電極またはドレイン電極の他方は、電気的に接続されている。また、第3の配線(L3)と第2のトランジスタ862のソース電極またはドレイン電極の一方は、電気的に接続され、第4の配線(L4)と第2のトランジスタ862のゲート電極は、電気的に接続されている。そして、第1のトランジスタ860のゲート電極、及び第2のトランジスタ862のソース電極またはドレイン電極の他方は、容量素子864の電極の一方と電気的に接続され、第5の配線(L5)と容量素子864の電極の他方は電気的に接続されている。

【0178】

図9(A)に示すメモリセルでは、第1のトランジスタ860のゲート電極の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しをすることができる。

【0179】

はじめに、情報の書き込み及び保持について説明する。まず、第4の配線の電位を、第2のトランジスタ862がオン状態となる電位にして、第2のトランジスタ862をオン状態とする。これにより、第3の配線の電位が、第1のトランジスタ860のゲート電極、及び容量素子864に与えられる。すなわち、第1のトランジスタ860のゲート電極には、所定の電荷が与えられる。ここでは、異なる二つの電位を与える電荷(以下、低電位を与える電荷を電荷QL、高電位を与える電荷を電荷QHという)のいずれかが与えられるものとする。なお、異なる三つまたはそれ以上の電位を与える電荷を適用して、記憶容量を向上させても良い。その後、第4の配線の電位を、第2のトランジスタ862がオフ状態となる電位にして、第2のトランジスタ862をオフ状態とすることにより、第1のトランジスタ860のゲート電極に与えられた電荷が保持される。

【0180】

酸化物半導体を用いて形成された第2のトランジスタ862のオフ電流は極めて小さいから、第1のトランジスタ860のゲート電極の電荷は長時間にわたって保持される。

【0181】

次に、情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、第1のトランジスタ860のゲート電極に保持された電荷量に応じて、第2の配線は異なる電位をとる。第1のトランジスタ860がpチャネル型である場合、第1のトランジスタ860のゲート電極にQHが与えられている場合の見かけのしきい値Vth_Hは、第1のトランジスタ860のゲート電極にQLが与えられている場合の見かけのしきい値Vth_Lより低くなるためである。ここで、見かけのしきい値とは、第1のトランジスタ860を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位をVth_LとVth_Hの間の電位V0とすることにより、第1のトランジスタ860のゲート電極に与えられた電荷を判別できる。例えば、書き込みにおいてQHが与えられた場合には、第5の配線の電位がV0(>Vth_H)となっても、第1のトランジスタ860は「オフ状態」のままである。QLが与えられた場合には、第5の配線の電位がV0(<Vth_L)となれば、第1のトランジスタ860は「オン状態」となる。このため、第2の配線の電位を見ることで、保持されている情報を読み出すことができる。

【0182】

なお、メモリセルをアレイ状に配置して用いる場合には、所望のメモリセルの情報のみを読み出せることが必要になる。このように、所定のメモリセルの情報を読み出し、それ以外のメモリセルの情報を読み出さない場合には、読み出しの対象ではないメモリセルの第5の配線に対して、ゲート電極の状態にかかわらず第1のトランジスタ860が「オフ状態」となるような電位、つまり、Vth_Lより大きい電位を与えればよい。または、ゲート電極の状態にかかわらず第1のトランジスタ860が「オン状態」となるような電位、つまり、Vth_Hより小さい電位を第5の配線に与えればよい。

【0183】

次に、情報の書き換えについて説明する。情報の書き換えは、上記情報の書き込み及び保持と同様に行われる。つまり、第4の配線の電位を、第2のトランジスタ862がオン状態となる電位にして、第2のトランジスタ862をオン状態とする。これにより、第3の配線の電位(新たな情報に係る電位)が、第1のトランジスタ860のゲート電極及び容量素子864に与えられる。その後、第4の配線の電位を、第2のトランジスタ862がオフ状態となる電位にして、第2のトランジスタ862をオフ状態とすることにより、第1のトランジスタ860のゲート電極は、新たな情報に係る電荷が与えられた状態となる。

【0184】

このように、開示する発明に係る記憶装置は、再度の情報の書き込みによって直接的に情報を書き換えることが可能である。このためフラッシュメモリなどにおいて必要とされる高電圧を用いてのフローティングゲートからの電荷の引き抜きが不要であり、消去動作に起因する動作速度の低下を抑制することができる。つまり、記憶装置の高速動作が実現される。

【0185】

なお、第2のトランジスタ862のソース電極またはドレイン電極の他方は、第1のトランジスタ860のゲート電極と電気的に接続されることにより、不揮発性メモリ素子として用いられるフローティングゲート型トランジスタのフローティングゲートと同等の作用を奏する。以下において、第2のトランジスタ862のソース電極またはドレイン電極の一方と第1のトランジスタ860のゲート電極が電気的に接続される部位をノードFGと呼ぶ場合がある。第2のトランジスタ862がオフの場合、当該ノードFGは絶縁体中に埋設されたと見ることができ、ノードFGには電荷が保持される。酸化物半導体を用いた第2のトランジスタ862のオフ電流は、シリコン半導体で形成されるトランジスタの10万分の1以下であるため、第2のトランジスタ862のリークによるノードFGに蓄積された電荷の消失を無視することができる。つまり、酸化物半導体を用いた第2のトランジスタ862により、電力の供給が無くても情報の保持が可能な不揮発性の記憶装置を実現することが可能である。

【0186】

例えば、第2のトランジスタ862の室温(25℃)でのオフ電流が10zA(1zA(ゼプトアンペア)は1×10−21A)以下であり、容量素子864の容量値が10fF程度である場合には、少なくとも104秒以上のデータ保持が可能である。なお、当該保持時間が、トランジスタ特性や容量値によって変動することはいうまでもない。

【0187】

また、図9(A)に示すメモリセルでは、従来のフローティングゲート型トランジスタにおいて指摘されているゲート絶縁層(トンネル絶縁層)の劣化という問題が存在しない。つまり、従来問題とされていた、電子をフローティングゲートに注入する際のゲート絶縁層の劣化という問題を解消することができる。これは、原理的な書き込み回数の制限が存在しないことを意味するものである。また、従来のフローティングゲート型トランジスタにおいて書き込みや消去の際に必要であった高電圧も不要である。

【0188】

図9(A)に示すメモリセルは、該メモリセルを構成するトランジスタなどの要素が抵抗及び容量を含むものとして、図9(B)のように考えることが可能である。つまり、図9(A)では、第1のトランジスタ860及び容量素子864が、それぞれ、抵抗及び容量を含んで構成されると考えていることになる。R1及びC1は、それぞれ、容量素子864の抵抗値及び容量値であり、抵抗値R1は、容量素子864を構成する絶縁層の抵抗値に相当する。また、R2及びC2は、それぞれ、第1のトランジスタ860の抵抗値及び容量値であり、抵抗値R2は第1のトランジスタ860がオン状態の時のゲート絶縁層による抵抗値に相当し、容量値C2はいわゆるゲート容量(ゲート電極と、ソース電極またはドレイン電極との間に形成される容量、及び、ゲート電極とチャネル形成領域との間に形成される容量)の容量値に相当する。

【0189】

第2のトランジスタ862がオフ状態にある場合のソース電極とドレイン電極の間の抵抗値(実効抵抗とも呼ぶ)をROSとすると、第2のトランジスタ862のゲートリーク電流が十分に小さい条件において、R1及びR2が、R1≧ROS(R1はROS以上)、R2≧ROS(R2はROS以上)を満たす場合には、電荷の保持期間(情報の保持期間ということもできる)は、主として第2のトランジスタ862のオフ電流によって決定されることになる。

【0190】

逆に、当該条件を満たさない場合には、第2のトランジスタ862のオフ電流が十分に小さくとも、保持期間を十分に確保することが困難になる。第2のトランジスタ862のオフ電流以外のリーク電流(例えば、第1のトランジスタ860におけるソース電極とゲート電極の間において生じるリーク電流等)が大きいためである。このことから、本実施の形態において開示するメモリセルは、R1≧ROS(R1はROS以上)、及びR2≧ROS(R2はROS以上)の関係を満たすものであることが望ましいといえる。

【0191】

一方で、C1とC2は、C1≧C2(C1はC2以上)の関係を満たすことが望ましい。C1を大きくすることで、第5の配線によってノードFGの電位を制御する際に、第5の配線の電位を効率よくノードFGに与えることができるようになり、第5の配線に与える電位(例えば、読み出しの電位と、非読み出しの電位)間の電位差を低く抑えることができるためである。

【0192】

このように、上述の関係を満たすことで、より好適なメモリセルを実現することが可能である。なお、R1及びR2は、第1のトランジスタ860のゲート絶縁層や容量素子864の絶縁層によって制御できる。C1及びC2についても同様である。よって、ゲート絶縁層の材料や厚さなどを適宜設定し、上述の関係を満たすようにすることが望ましい。

【0193】

本実施の形態で示すメモリセルにおいては、ノードFGが、フラッシュメモリ等のフローティングゲート型トランジスタのフローティングゲートと同等の作用をするが、本実施の形態のノードFGは、本質的に異なる特徴を有している。

【0194】

フラッシュメモリでは、コントロールゲートに印加される電位が高いため、その電位が、隣接するセルのフローティングゲートに影響を与えないように、セルとセルとの間隔をある程度保つ必要が生じる。このことは、記憶装置の高集積化を阻害する要因の一つである。そして、当該要因は、高電界をかけてトンネル電流を発生させるというフラッシュメモリの根本的な原理に起因するものである。

【0195】

一方、本実施の形態におけるメモリセルは、酸化物半導体を用いたトランジスタのスイッチングによって動作し、上述のようなトンネル電流による電荷注入の原理を用いない。すなわち、フラッシュメモリのような、電荷を注入するための高電界が不要である。これにより、隣接セルに対する、コントロールゲートによる高電界の影響を考慮する必要がないため、高集積化が容易になる。

【0196】

したがって、本実施の形態における記憶装置には、大型の昇圧回路などが不要である点も、フラッシュメモリに対する利点である。例えば、メモリセルに印加される電圧(メモリセルの各電極に同時に印加される最大電位と最小電位の差)の最大値は、2段階(1ビット)の情報を書き込む場合、一つのメモリセルにおいて、5V以下、好ましくは3V以下とすることができる。

【0197】

更に、容量素子864を構成する絶縁層の比誘電率εr1と、第1のトランジスタ860を構成する絶縁層の比誘電率εr2とを異ならせる場合には、容量素子864を構成する絶縁層の面積S1と、第1のトランジスタ860においてゲート容量を構成する絶縁層の面積S2とが、2・S2≧S1(2・S2はS1以上)、望ましくはS2≧S1(S2はS1以上)を満たしつつ、C1≧C2(C1はC2以上)を実現することが容易である。すなわち、容量素子864を構成する絶縁層の面積を小さくしつつ、C1≧C2を実現することが容易である。具体的には、例えば、容量素子864を構成する絶縁層においては、酸化ハフニウムなどのhigh−k材料でなる層、または酸化ハフニウムなどのhigh−k材料でなる層と酸化物半導体でなる層との積層構造を採用してεr1を10以上、好ましくは15以上とし、ゲート容量を構成する絶縁層においては、酸化シリコンなどを採用して、εr2=3〜4とすることができる。

【0198】

このような構成を併せて用いることで、記憶装置の更なる高集積化が可能となる。

【0199】

なお、記憶装置の記憶容量を大きくするためには、高集積化以外に、多値化の手法を採ることもできる。例えば、メモリセルの一つに3段階以上の情報を書き込む構成とすることで、2段階(1ビット)の情報を書き込む場合と比較して記憶容量を増大させることができる。例えば、上述のような、低電位を与える電荷QL、高電位を与える電荷QHに加え、他の電位を与える電荷Qを第1のトランジスタのゲート電極に与えることで、多値化を実現することができる。

【0200】

以上のように、シリコンを用いたトランジスタ及び酸化物半導体を用いたトランジスタを用いて回路を構成することで保持特性に優れた記憶装置を形成することができる。また、該記憶装置には、実施の形態1で説明した保護回路を特別な工程を用いずに設けることができる。

【0201】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0202】

(実施の形態5)

酸化物半導体に限らず、実際に測定される絶縁ゲート型トランジスタの電界効果移動度は、さまざまな理由によって本来の移動度よりも低くなる。移動度を低下させる要因としては半導体内部の欠陥や半導体と絶縁膜との界面の欠陥があるが、Levinsonモデルを用いると、半導体内部に欠陥がないと仮定した場合の電界効果移動度を理論的に導き出せる。

【0203】

半導体本来の移動度をμ0、測定される電界効果移動度をμとし、半導体中に何らかのポテンシャル障壁(粒界等)が存在すると仮定すると、以下の式で表現できる。

【0204】

【数2】

【0205】

ここで、Eはポテンシャル障壁の高さであり、kがボルツマン定数、Tは絶対温度である。また、ポテンシャル障壁が欠陥に由来すると仮定すると、Levinsonモデルでは、以下の式で表される。

【0206】

【数3】

【0207】

ここで、eは電気素量、Nはチャネル内の単位面積当たりの平均欠陥密度、εは半導体の誘電率、nは単位面積当たりのチャネルに含まれるキャリア数、Coxは単位面積当たりの容量、Vgはゲート電圧、tはチャネルの厚さである。なお、厚さ30nm以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。

線形領域におけるドレイン電流Idは、以下の式となる。

【0208】

【数4】

【0209】

ここで、Lはチャネル長、Wはチャネル幅であり、ここでは、L=W=10μmである。また、Vdはドレイン電圧である。

上式の両辺をVgで割り、更に両辺の対数を取ると、以下のようになる。

【0210】

【数5】

【0211】

数5の右辺はVgの関数である。この式からわかるように、縦軸をln(Id/Vg)、横軸を1/Vgとして実測値をプロットして得られるグラフの直線の傾きから欠陥密度Nが求められる。すなわち、トランジスタのId―Vg特性から、欠陥密度を評価できる。酸化物半導体としては、インジウム(In)、スズ(Sn)、亜鉛(Zn)の比率が、In:Sn:Zn=1:1:1のものでは欠陥密度Nは1×1012/cm2程度である。

【0212】

このようにして求めた欠陥密度等をもとに数2および数3よりμ0=120cm2/Vsが導出される。欠陥のあるIn−Sn−Zn酸化物で測定される移動度は35cm2/Vs程度である。しかし、半導体内部および半導体と絶縁膜との界面の欠陥が無い酸化物半導体の移動度μ0は120cm2/Vsとなると予想できる。

【0213】

ただし、半導体内部に欠陥がなくても、チャネルとゲート絶縁層との界面での散乱によってトランジスタの輸送特性は影響を受ける。すなわち、ゲート絶縁層界面からxだけ離れた場所における移動度μ1は、以下の式で表される。

【0214】

【数6】

【0215】

ここで、Dはゲート方向の電界、B、Gは定数である。BおよびGは、実際の測定結果より求めることができ、上記の測定結果からは、B=4.75×107cm/s、G=10nm(界面散乱が及ぶ深さ)である。Dが増加する(すなわち、ゲート電圧が高くなる)と数6の第2項が増加するため、移動度μ1は低下することがわかる。

【0216】

半導体内部の欠陥が無い理想的な酸化物半導体をチャネルに用いたトランジスタの移動度μ2の計算結果を図15に示す。なお、計算にはシノプシス社製デバイスシミュレーションソフト、Sentaurus Deviceを使用し、酸化物半導体のバンドギャップ、電子親和力、比誘電率、厚さをそれぞれ、2.8電子ボルト、4.7電子ボルト、15、15nmとした。これらの値は、スパッタ法により形成された薄膜を測定して得られたものである。

【0217】

さらに、ゲート、ソース、ドレインの仕事関数をそれぞれ、5.5電子ボルト、4.6電子ボルト、4.6電子ボルトとした。また、ゲート絶縁層の厚さは100nm、比誘電率は4.1とした。チャネル長およびチャネル幅はともに10μm、ドレイン電圧Vdは0.1Vである。

【0218】

図15で示されるように、ゲート電圧1V強で移動度100cm2/Vs以上のピークをつけるが、ゲート電圧がさらに高くなると、界面散乱が大きくなり、移動度が低下する。なお、界面散乱を低減するためには、半導体層表面を原子レベルで平坦にすること(Atomic Layer Flatness)が望ましい。

【0219】

このような移動度を有する酸化物半導体を用いて微細なトランジスタを作製した場合の特性の計算結果を図16乃至図18に示す。なお、計算に用いたトランジスタの断面構造を図19に示す。図19に示すトランジスタは酸化物半導体層にn+の導電型を呈する半導体領域2103aおよび半導体領域2103cを有する。半導体領域2103aおよび半導体領域2103cの抵抗率は2×10−3Ωcmとする。

【0220】

図19(A)に示すトランジスタは、下地絶縁層2101と、下地絶縁層2101に埋め込まれるように形成された酸化アルミニウムよりなる埋め込み絶縁物2102の上に形成される。トランジスタは半導体領域2103a、半導体領域2103cと、それらに挟まれ、チャネル形成領域となる真性の半導体領域2103bと、ゲート2105を有する。ゲート2105の幅を33nmとする。

【0221】

ゲート2105と半導体領域2103bの間には、ゲート絶縁層2104を有し、また、ゲート2105の両側面には側壁絶縁物2106aおよび側壁絶縁物2106b、ゲート2105の上部には、ゲート2105と他の配線との短絡を防止するための絶縁物2107を有する。側壁絶縁物の幅は5nmとする。また、半導体領域2103aおよび半導体領域2103cに接して、ソース2108aおよびドレイン2108bを有する。なお、このトランジスタにおけるチャネル幅を40nmとする。

【0222】

図19(B)に示すトランジスタは、下地絶縁層2101と、酸化アルミニウムよりなる埋め込み絶縁物2102の上に形成され、半導体領域2103a、半導体領域2103cと、それらに挟まれた真性の半導体領域2103bと、幅33nmのゲート2105とゲート絶縁層2104と側壁絶縁物2106aおよび側壁絶縁物2106bと絶縁物2107とソース2108aおよびドレイン2108bを有する点で図19(A)に示すトランジスタと同じである。

【0223】

図19(A)に示すトランジスタと図19(B)に示すトランジスタの相違点は、側壁絶縁物2106aおよび側壁絶縁物2106bの下の半導体領域の導電型である。図19(A)に示すトランジスタでは、側壁絶縁物2106aおよび側壁絶縁物2106bの下の半導体領域はn+の導電型を呈する半導体領域2103aおよび半導体領域2103cであるが、図19(B)に示すトランジスタでは、真性の半導体領域2103bである。すなわち、図19(B)に示す半導体層において、半導体領域2103a(半導体領域2103c)とゲート2105がLoffだけ重ならない領域ができている。この領域をオフセット領域といい、その幅Loffをオフセット長という。図から明らかなように、オフセット長は、側壁絶縁物2106a(側壁絶縁物2106b)の幅と同じである。

【0224】

その他の計算に使用するパラメータは上述の通りである。計算にはシノプシス社製デバイスシミュレーションソフト、Sentaurus Deviceを使用した。図16は、図19(A)に示される構造のトランジスタのドレイン電流(Id、実線)および移動度(μ、点線)のゲート電圧(Vg、ゲートとソースの電位差)依存性を示す。ドレイン電流Idは、ドレイン電圧(ドレインとソースの電位差)を+1Vとし、移動度μはドレイン電圧を+0.1Vとして計算したものである。

【0225】

図16(A)はゲート絶縁層の厚さを15nmとしたものであり、図16(B)は10nmとしたものであり、図16(C)は5nmとしたものである。ゲート絶縁層が薄くなるほど、特にオフ状態でのドレイン電流Id(オフ電流)が顕著に低下する。一方、移動度μのピーク値やオン状態でのドレイン電流Id(オン電流)には目立った変化が無い。ゲート電圧1V前後で、ドレイン電流はメモリ素子等で必要とされる10μAを超えることが示された。

【0226】

図17は、図19(B)に示される構造のトランジスタで、オフセット長Loffを5nmとしたもののドレイン電流Id(実線)および移動度μ(点線)のゲート電圧Vg依存性を示す。ドレイン電流Idは、ドレイン電圧を+1Vとし、移動度μはドレイン電圧を+0.1Vとして計算したものである。図17(A)はゲート絶縁層の厚さを15nmとしたものであり、図17(B)は10nmとしたものであり、図17(C)は5nmとしたものである。

【0227】

また、図18は、図19(B)に示される構造のトランジスタで、オフセット長Loffを15nmとしたもののドレイン電流Id(実線)および移動度μ(点線)のゲート電圧依存性を示す。ドレイン電流Idは、ドレイン電圧を+1Vとし、移動度μはドレイン電圧を+0.1Vとして計算したものである。図18(A)はゲート絶縁層の厚さを15nmとしたものであり、図18(B)は10nmとしたものであり、図18(C)は5nmとしたものである。

【0228】

いずれもゲート絶縁層が薄くなるほど、オフ電流が顕著に低下する一方、移動度μのピーク値やオン電流には目立った変化が無い。

【0229】

なお、移動度μのピークは、図16では80cm2/Vs程度であるが、図17では60cm2/Vs程度、図18では40cm2/Vs程度と、オフセット長Loffが増加するほど低下する。また、オフ電流も同様な傾向がある。一方、オン電流もオフセット長Loffの増加にともなって減少するが、オフ電流の低下に比べるとはるかに緩やかである。また、いずれもゲート電圧1V前後で、ドレイン電流はメモリ素子等で必要とされる10μAを超えることが示された。

【0230】

(実施の形態6)

本実施の形態では、上述の実施の形態で説明した半導体装置を電子機器に適用する場合について、図10を用いて説明する。本実施の形態では、コンピュータ、携帯電話機、携帯情報端末(携帯型ゲーム機、音響再生装置なども含む)、デジタルカメラ、デジタルビデオカメラ、電子ペーパー、テレビジョン装置などの電子機器に、本発明の一態様における半導体装置を適用する場合について説明する。

【0231】

図10(A)は、ノート型のパーソナルコンピュータであり、筐体701、筐体702、表示部703、キーボード704などによって構成されている。筐体701と筐体702の少なくとも一つには、先の実施の形態に示す半導体装置が設けられている。したがって、小型化かつ信頼性の高いノート型のパーソナルコンピュータを実現することができる。

【0232】

図10(B)は、携帯情報端末(PDA)であり、本体711には、表示部713と、外部インターフェイス715と、操作ボタン714等が設けられている。また、携帯情報端末はスタイラス712などを用いて操作することもできる。本体711内には、先の実施の形態に示す半導体装置が設けられている。したがって、小型化かつ信頼性の高い携帯情報端末を実現することができる。

【0233】

図10(C)は、電子ペーパーを実装した電子書籍であり、電子書籍720は、筐体721と筐体723の二つの筐体で構成されている。筐体721及び筐体723には、それぞれ表示部725及び表示部727が設けられている。筐体721と筐体723は、軸部737により接続されており、該軸部737を軸として開閉動作を行うことができる。また、筐体721は、電源731、操作キー733、スピーカー735などを備えている。筐体721、筐体723の少なくとも一つには、先の実施の形態に示す半導体装置が設けられている。したがって、小型化かつ信頼性の高い電子書籍を実現することができる。

【0234】

図10(D)は、携帯電話機であり、筐体740と筐体741の二つの筐体で構成されている。さらに、筐体740と筐体741は、スライドし、図10(D)のように展開している状態から重なり合った状態とすることができ、携帯に適した小型化が可能である。また、筐体741は、表示パネル742、スピーカー743、マイクロフォン744、操作キー745、ポインティングデバイス746、カメラ747、外部接続電極748などを備えている。また、筐体740は、携帯電話機の充電を行う太陽電池749、外部メモリスロット750などを備えている。また、アンテナは、筐体741に内蔵されている。筐体740と筐体741の少なくとも一つには、先の実施の形態に示す半導体装置が設けられている。したがって、小型化かつ信頼性の高い携帯電話機を実現することができる。

【0235】

図10(E)は、デジタルカメラであり、本体761、表示部767、接眼部763、操作スイッチ764、表示部765、バッテリー766などによって構成されている。本体761内には、先の実施の形態に示す半導体装置が設けられている。したがって、小型化かつ信頼性の高いデジタルカメラを実現することができる。

【0236】

図10(F)は、テレビジョン装置であり、筐体771、表示部773、スタンド775などで構成されている。テレビジョン装置770の操作は、筐体771が備えるスイッチや、リモートコントローラ780により行うことができる。筐体771及びリモートコントローラ780には、先の実施の形態に示す半導体装置が搭載されている。そのため、したがって、小型化かつ信頼性の高いテレビジョン装置を実現することができる。

【0237】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置が搭載されている。したがって、小型化かつ信頼性の高い電子機器が実現される。

【0238】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【実施例1】

【0239】

In、Sn、Znを主成分とする酸化物半導体をチャネル形成領域とするトランジスタは、該酸化物半導体を形成する際に基板を加熱して成膜すること、或いは酸化物半導体層を形成した後に熱処理を行うことで良好な特性を得ることができる。なお、主成分とは組成比で5atomic%以上含まれる元素をいう。

【0240】

In、Sn、Znを主成分とする酸化物半導体層の成膜後に基板を意図的に加熱することで、トランジスタの電界効果移動度を向上させることが可能となる。また、トランジスタのしきい値電圧をプラスシフトさせ、ノーマリ・オフ化させることが可能となる。

【0241】

例えば、図20(A)〜(C)は、In、Sn、Znを主成分とし、チャネル長Lが3μm、チャネル幅Wが10μmである酸化物半導体層と、厚さ100nmのゲート絶縁層を用いたトランジスタの特性である。なお、Vdは10Vとした。

【0242】

図20(A)は基板を意図的に加熱せずにスパッタ法でIn、Sn、Znを主成分とする酸化物半導体層を形成したときのトランジスタ特性である。このとき電界効果移動度は18.8cm2/Vsecが得られている。一方、基板を意図的に加熱してIn、Sn、Znを主成分とする酸化物半導体層を形成すると電界効果移動度を向上させることが可能となる。図20(B)は基板を200℃に加熱してIn、Sn、Znを主成分とする酸化物半導体層を形成したときのトランジスタ特性を示すが、電界効果移動度は32.2cm2/Vsecが得られている。

【0243】

電界効果移動度は、In、Sn、Znを主成分とする酸化物半導体層を形成した後に熱処理をすることによって、さらに高めることができる。図20(C)は、In、Sn、Znを主成分とする酸化物半導体層を200℃で成膜した後、650℃で熱処理をしたときのトランジスタ特性を示す。このとき電界効果移動度は34.5cm2/Vsecが得られている。

【0244】

基板を意図的に加熱することで、成膜中に酸化物半導体層中に取り込まれる水分を低減することができる。また、成膜後に熱処理をすることによっても、酸化物半導体層から水素や水酸基若しくは水分を放出させ除去することができ、上記のように電界効果移動度を向上させることができる。このような電界効果移動度の向上は、脱水化・脱水素化による不純物の除去のみならず、高密度化により原子間距離が短くなるためとも推定される。また、酸化物半導体から不純物を除去して高純度化することで結晶化を図ることができる。このように高純度化された非単結晶酸化物半導体は、理想的には100cm2/Vsecを超える電界効果移動度を実現することも可能になると推定される。

【0245】

In、Sn、Znを主成分とする酸化物半導体に酸素イオンを注入し、熱処理により該酸化物半導体に含まれる水素や水酸基若しくは水分を放出させ、その熱処理と同時に又はその後の熱処理により酸化物半導体を結晶化させても良い。このような結晶化若しくは再結晶化の処理により結晶性の良い非単結晶酸化物半導体を得ることができる。

【0246】

基板を意図的に加熱して成膜すること及び/又は成膜後に熱処理することの効果は、電界効果移動度の向上のみならず、トランジスタのノーマリ・オフ化を図ることにも寄与している。基板を意図的に加熱しないで形成されたIn、Sn、Znを主成分とする酸化物半導体層をチャネル形成領域としたトランジスタは、しきい値電圧がマイナスシフトしてしまう傾向がある。しかし、基板を意図的に加熱して形成された酸化物半導体層を用いた場合、このしきい値電圧のマイナスシフト化は解消される。つまり、しきい値電圧はトランジスタがノーマリ・オフとなる方向に動き、このような傾向は図20(A)と図20(B)の対比からも確認することができる。

【0247】

なお、しきい値電圧はIn、Sn及びZnの比率を変えることによっても制御することが可能であり、組成比としてIn:Sn:Zn=2:1:3とすることでトランジスタをノーマリ・オフ化することができる。また、ターゲットの組成比をIn:Sn:Zn=2:1:3とすることで結晶性の高い酸化物半導体層を得ることができる。

【0248】

意図的な基板加熱温度若しくは熱処理温度は、150℃以上、好ましくは200℃以上、より好ましくは400℃以上であり、より高温で成膜し或いは熱処理することでトランジスタのノーマリ・オフ化を図ることが可能となる。

【0249】

また、意図的に基板を加熱した成膜及び/又は成膜後に熱処理をすることで、ゲートバイアス・ストレスに対する安定性を高めることができる。例えば、2MV/cm、150℃、1時間印加の条件において、ドリフトがそれぞれ±1.5V未満、好ましくは1.0V未満を得ることができる。

【0250】

実際に、酸化物半導体層成膜後に加熱処理を行っていない試料1と、650℃の加熱処理を行った試料2のトランジスタに対してBT試験を行った。

【0251】

まず基板温度を25℃とし、Vdを10Vとし、トランジスタのVg−Id特性の測定を行った。なお、Vdはドレイン電圧(ドレインとソースの電位差)を示す。次に、基板温度を150℃とし、Vdを0.1Vとした。次に、ゲート絶縁層に印加される電界強度が2MV/cmとなるようにVgに20Vを印加し、そのまま1時間保持した。次に、Vgを0Vとした。次に、基板温度25℃とし、Vdを10Vとし、トランジスタのVg−Id測定を行った。これをプラスBT試験と呼ぶ。

【0252】

同様に、まず基板温度を25℃とし、Vdを10Vとし、トランジスタのVg−Id特性の測定を行った。次に、基板温度を150℃とし、Vdを0.1Vとした。次に、ゲート絶縁層に印加される電界強度が−2MV/cmとなるようにVgに−20Vを印加し、そのまま1時間保持した。次に、Vgを0Vとした。次に、基板温度25℃とし、Vdを10Vとし、トランジスタのVg−Id測定を行った。これをマイナスBT試験と呼ぶ。

【0253】

試料1のプラスBT試験の結果を図21(A)に、マイナスBT試験の結果を図21(B)に示す。また、試料2のプラスBT試験の結果を図22(A)に、マイナスBT試験の結果を図22(B)に示す。

【0254】

試料1のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ1.80Vおよび−0.42Vであった。また、試料2のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ0.79Vおよび0.76Vであった。

試料1および試料2のいずれも、BT試験前後におけるしきい値電圧の変動が小さく、信頼性が高いことがわかる。

【0255】

熱処理は酸素雰囲気中で行うことができるが、まず窒素若しくは不活性ガス、または減圧下で熱処理を行ってから酸素を含む雰囲気中で熱処理を行っても良い。最初に脱水化・脱水素化を行ってから酸素を酸化物半導体に加えることで、熱処理の効果をより高めることができる。また、後から酸素を加えるには、酸素イオンを電界で加速して酸化物半導体層に注入する方法を適用しても良い。

【0256】

酸化物半導体中及び該酸化物半導体と接する膜との界面には、酸素欠損による欠陥が生成されやすいが、かかる熱処理により酸化物半導体中に酸素を過剰に含ませることにより、定常的に生成される酸素欠損を過剰な酸素によって補償することが可能となる。過剰酸素は主に格子間に存在する酸素であり、その酸素濃度を1×1016/cm3以上2×1020/cm3以下とすれば、結晶に歪み等を与えることなく酸化物半導体中に含ませることができる。

【0257】

また、熱処理によって酸化物半導体に結晶が少なくとも一部に含まれるようにすることで、より安定な酸化物半導体層を得ることができる。例えば、組成比In:Sn:Zn=1:1:1のターゲットを用いて、基板を意図的に加熱せずにスパッタ成膜した酸化物半導体層は、X線回折(XRD:X−Ray Diffraction)でハローパタンが観測される。この成膜された酸化物半導体層を熱処理することによって結晶化させることができる。熱処理温度は任意であるが、例えば650℃の熱処理を行うことで、X線回折により明確な回折ピークを観測することができる。

【0258】

実際に、In−Sn−Zn−O膜のXRD分析を行った。XRD分析には、Bruker AXS社製X線回折装置D8 ADVANCEを用い、Out−of−Plane法で測定した。

【0259】

XRD分析を行った試料として、試料Aおよび試料Bを用意した。以下に試料Aおよび試料Bの作製方法を説明する。

【0260】

脱水素化処理済みの石英基板上にIn−Sn−Zn−O膜を100nmの厚さで成膜した。

【0261】

In−Sn−Zn−O膜は、スパッタ装置を用い、酸素雰囲気で電力を100W(DC)として成膜した。ターゲットは、原子数比でIn:Sn:Zn=1:1:1のIn−Sn−Zn−Oターゲットを用いた。なお、成膜時の基板加熱温度は200℃とした。このようにして作製した試料を試料Aとした。

【0262】

次に、試料Aと同様の方法で作製した試料に対し加熱処理を650℃の温度で行った。加熱処理は、はじめに窒素雰囲気で1時間の加熱処理を行い、温度を下げずに酸素雰囲気でさらに1時間の加熱処理を行っている。このようにして作製した試料を試料Bとした。

【0263】

図23に試料Aおよび試料BのXRDスペクトルを示す。試料Aでは、結晶由来のピークが観測されなかったが、試料Bでは、2θが35deg近傍および37deg〜38degに結晶由来のピークが観測された。

【0264】

このように、In、Sn、Znを主成分とする酸化物半導体は成膜時に意図的に加熱すること及び/又は成膜後に熱処理することによりトランジスタの特性を向上させることができる。

【0265】

この基板加熱や熱処理は、酸化物半導体にとって悪性の不純物である水素や水酸基を膜中に含ませないようにすること、或いは膜中から除去する作用がある。すなわち、酸化物半導体中でドナー不純物となる水素を除去することで高純度化を図ることができ、それによってトランジスタのノーマリ・オフ化を図ることができ、酸化物半導体が高純度化されることによりオフ電流を1aA/μm以下にすることができる。ここで、上記オフ電流値の単位は、チャネル幅1μmあたりの電流値を示す。

【0266】

図24に、トランジスタのオフ電流と測定時の基板温度(絶対温度)の逆数との関係を示す。ここでは、簡単のため測定時の基板温度の逆数に1000を掛けた数値(1000/T)を横軸としている。

【0267】

具体的には、図24に示すように、基板温度が125℃の場合には1aA/μm(1×10−18A/μm)以下、85℃の場合には100zA/μm(1×10−19A/μm)以下、室温(27℃)の場合には1zA/μm(1×10−21A/μm)以下にすることができる。好ましくは、125℃において0.1aA/μm(1×10−19A/μm)以下に、85℃において10zA/μm(1×10−20A/μm)以下に、室温において0.1zA/μm(1×10−22A/μm)以下にすることができる。これらのオフ電流値は、Siを半導体膜として用いたトランジスタに比べて、極めて低いものであることは明らかである。

【0268】

もっとも、酸化物半導体層の成膜時に水素や水分が膜中に混入しないように、成膜室外部からのリークや成膜室内の内壁からの脱ガスを十分抑え、スパッタガスの高純度化を図ることが好ましい。例えば、スパッタガスは水分が膜中に含まれないように露点−70℃以下であるガスを用いることが好ましい。また、ターゲットそのものに水素や水分などの不純物が含まれていていないように、高純度化されたターゲットを用いることが好ましい。In、Sn、Znを主成分とする酸化物半導体は熱処理によって膜中の水分を除去することができるが、In、Ga、Znを主成分とする酸化物半導体と比べて水分の放出温度が高いため、好ましくは最初から水分の含まれない膜を形成しておくことが好ましい。

【0269】

また、酸化物半導体層成膜後に650℃の加熱処理を行った試料Bを用いたトランジスタにおいて、基板温度と電気的特性の関係について評価した。

【0270】

測定に用いたトランジスタは、チャネル長Lが3μm、チャネル幅Wが10μm、Lovが0μm、dWが0μmである。なお、Vdは10Vとした。なお、基板温度は−40℃、−25℃、25℃、75℃、125℃および150℃で行った。ここで、トランジスタにおいて、ゲート電極と一対の電極との重畳する幅をLovと呼び、酸化物半導体層に対する一対の電極のはみ出しをdWと呼ぶ。

【0271】

図25に、Id(実線)および電界効果移動度(点線)のVg依存性を示す。また、図26(A)に基板温度としきい値電圧の関係を、図26(B)に基板温度と電界効果移動度の関係を示す。

【0272】

図26(A)より、基板温度が高いほどしきい値電圧は低くなることがわかる。なお、その範囲は−40℃〜150℃で1.09V〜−0.23Vであった。

【0273】

また、図26(B)より、基板温度が高いほど電界効果移動度が低くなることがわかる。なお、その範囲は−40℃〜150℃で36cm2/Vs〜32cm2/Vsであった。したがって、上述の温度範囲において電気的特性の変動が小さいことがわかる。

【0274】

上記のようなIn、Sn、Znを主成分とする酸化物半導体をチャネル形成領域とするトランジスタによれば、オフ電流を1aA/μm以下に保ちつつ、電界効果移動度を30cm2/Vsec以上、好ましくは40cm2/Vsec以上、より好ましくは60cm2/Vsec以上とし、LSIで要求されるオン電流の値を満たすことができる。例えば、L/W=33nm/40nmのFETで、ゲート電圧2.7V、ドレイン電圧1.0Vのとき12μA以上のオン電流を流すことができる。またトランジスタの動作に求められる温度範囲においても、十分な電気的特性を確保することができる。このような特性であれば、Si半導体で作られる集積回路の中に酸化物半導体で形成されるトランジスタを混載しても、動作速度を犠牲にすることなく新たな機能を有する集積回路を実現することができる。

【実施例2】

【0275】

本実施例では、In−Sn−Zn−O膜を酸化物半導体層に用いたトランジスタの一例について、図27などを用いて説明する。

【0276】

図27は、コプラナー型であるトップゲート・トップコンタクト構造のトランジスタの上面図および断面図である。図27(A)にトランジスタの上面図を示す。また、図27(B)に図27(A)の一点鎖線A1−A2に対応する断面A1−A2を示す。

【0277】

図27(B)に示すトランジスタは、基板3100と、基板3100上に設けられた下地絶縁層3102と、下地絶縁層3102の周辺に設けられた保護絶縁膜3104と、下地絶縁層3102および保護絶縁膜3104上に設けられた高抵抗領域3106aおよび低抵抗領域3106bを有する酸化物半導体層3106と、酸化物半導体層3106上に設けられたゲート絶縁層3108と、ゲート絶縁層3108を介して酸化物半導体層3106と重畳して設けられたゲート電極3110と、ゲート電極3110の側面と接して設けられた側壁絶縁膜3112と、少なくとも低抵抗領域3106bと接して設けられた一対の電極3114と、少なくとも酸化物半導体層3106、ゲート電極3110および一対の電極3114を覆って設けられた層間絶縁膜3116と、層間絶縁膜3116に設けられた開口部を介して少なくとも一対の電極3114の一方と接続して設けられた配線3118と、を有する。

【0278】

なお、図示しないが、層間絶縁膜3116および配線3118を覆って設けられた保護膜を有していても構わない。該保護膜を設けることで、層間絶縁膜3116の表面伝導に起因して生じる微小リーク電流を低減することができ、トランジスタのオフ電流を低減することができる。

【実施例3】

【0279】

本実施例では、上記とは異なるIn−Sn−Zn−O膜を酸化物半導体層に用いたトランジスタの他の一例について示す。

【0280】

図28は、本実施例で作製したトランジスタの構造を示す上面図および断面図である。図28(A)はトランジスタの上面図である。また、図28(B)は図28(A)の一点鎖線B1−B2に対応する断面図である。

【0281】

図28(B)に示すトランジスタは、基板3600と、基板3600上に設けられた下地絶縁層3602と、下地絶縁層3602上に設けられた酸化物半導体層3606と、酸化物半導体層3606と接する一対の電極3614と、酸化物半導体層3606および一対の電極3614上に設けられたゲート絶縁層3608と、ゲート絶縁層3608を介して酸化物半導体層3606と重畳して設けられたゲート電極3610と、ゲート絶縁層3608およびゲート電極3610を覆って設けられた層間絶縁膜3616と、層間絶縁膜3616に設けられた開口部を介して一対の電極3614と接続する配線3618と、層間絶縁膜3616および配線3618を覆って設けられた保護膜3620と、を有する。

【0282】

基板3600としてはガラス基板を、下地絶縁層3602としては酸化シリコン膜を、酸化物半導体層3606としてはIn−Sn−Zn−O膜を、一対の電極3614としてはタングステン膜を、ゲート絶縁層3608としては酸化シリコン膜を、ゲート電極3610としては窒化タンタル膜とタングステン膜との積層構造を、層間絶縁膜3616としては酸化窒化シリコン膜とポリイミド膜との積層構造を、配線3618としてはチタン膜、アルミニウム膜、チタン膜がこの順で形成された積層構造を、保護膜3620としてはポリイミド膜を、それぞれ用いた。

【0283】

なお、図28(A)に示す構造のトランジスタにおいて、ゲート電極3610と一対の電極3614との重畳する幅をLovと呼ぶ。同様に、酸化物半導体層3606に対する一対の電極3614のはみ出しをdWと呼ぶ。

【符号の説明】

【0284】

101 第1の配線

102 第2の配線

103 第3の配線

111 第1の非線形素子

112 第2の非線形素子

113 第3の非線形素子

114 第4の非線形素子

121 第1の保護回路

122 第2の保護回路

131 半導体回路

201 第1の非線形素子

202 第2の非線形素子

203 第3の非線形素子

204 第4の非線形素子

301 第1の非線形素子

302 第2の非線形素子

401 第1の非線形素子

402 第2の非線形素子

500 単結晶シリコン基板

502 半導体層

504 電極

506 電極

508 ゲート電極

509 接続配線

518 第5の絶縁層

521 第4の絶縁層

522 半導体層

524 電極

526 電極

528 ゲート電極

529 接続配線

532a p+領域

536 第1の絶縁層

538 ゲート電極

538a 導電層

538b 導電層

539 第2の絶縁層

540 絶縁層

541a 接続配線

541b 接続配線

542 第6の絶縁層

544 第3の絶縁層

546 第7の絶縁層

558 ゲート電極

561a 接続配線

561b 接続配線

701 筐体

702 筐体

703 表示部

704 キーボード

711 本体

712 スタイラス

713 表示部

714 操作ボタン

715 外部インターフェイス

720 電子書籍

721 筐体

723 筐体

725 表示部

727 表示部

731 電源

733 操作キー

735 スピーカー

737 軸部

740 筐体

741 筐体

742 表示パネル

743 スピーカー

744 マイクロフォン

745 操作キー

746 ポインティングデバイス

747 カメラ

748 外部接続電極

749 太陽電池

750 外部メモリスロット

761 本体

763 接眼部

764 操作スイッチ

765 表示部

766 バッテリー

767 表示部

770 テレビジョン装置

771 筐体

773 表示部

775 スタンド

780 リモートコントローラ

860 第1のトランジスタ

862 第2のトランジスタ

864 容量素子

901 トランジスタ

902 絶縁層

903 酸化物半導体層

904 ソース電極

905 ドレイン電極

906 ゲート絶縁層

907 ゲート電極

908 高濃度領域

909 チャネル形成領域

911 トランジスタ

912 絶縁層

913 酸化物半導体層

914 ソース電極

915 ドレイン電極

916 ゲート絶縁層

917 ゲート電極

918 高濃度領域

919 チャネル形成領域

921 トランジスタ

922 絶縁層

923 酸化物半導体層

924 ソース電極

925 ドレイン電極

926 ゲート絶縁層

927 ゲート電極

928 高濃度領域

929 低濃度領域

930 サイドウォール

931 チャネル形成領域

941 トランジスタ

942 絶縁層

943 酸化物半導体層

944 ソース電極

945 ドレイン電極

946 ゲート絶縁層

947 ゲート電極

948 高濃度領域

949 低濃度領域

950 サイドウォール

951 チャネル形成領域

2101 下地絶縁層

2102 埋め込み絶縁物

2103a 半導体領域

2103b 半導体領域

2103c 半導体領域

2104 ゲート絶縁層

2105 ゲート

2106a 側壁絶縁物

2106b 側壁絶縁物

2107 絶縁物

2108a ソース

2108b ドレイン

3100 基板

3102 下地絶縁層

3104 保護絶縁膜

3106 酸化物半導体層

3106a 高抵抗領域

3106b 低抵抗領域

3108 ゲート絶縁層

3110 ゲート電極

3112 側壁絶縁膜

3114 電極

3116 層間絶縁膜

3118 配線

3600 基板

3602 下地絶縁層

3606 酸化物半導体層

3608 ゲート絶縁層

3610 ゲート電極

3614 電極

3616 層間絶縁膜

3618 配線

3620 保護膜

【技術分野】

【0001】

本発明は、静電気放電などの予期しない高電圧の印加に対して回路の破壊を防ぐ手段を備えた半導体装置に関する。なお、本明細書において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。例えば、表示装置、撮像装置、記憶装置及び演算装置、並びにそれらを用いた電子機器は全て半導体装置である。

【背景技術】

【0002】

半導体装置に用いられる半導体回路は、静電気放電(Electro Static Discharge、以下、「ESD」と呼ぶ。)によって半導体素子や電極などが破壊されることがある。このESDによる半導体回路の破壊防止対策として、多くの半導体回路には、保護回路が接続されている。保護回路は、端子や配線などに印加された過剰な電圧が半導体回路に供給されることを防ぐための回路である。保護回路に用いられる代表的な素子には、抵抗素子、ダイオード、トランジスタ、容量素子などがある。

【0003】

また、保護回路を設けることで、信号や電源電圧と共にノイズが配線等に入力された場合であっても、該ノイズによる後段の半導体回路の誤動作の防止が可能であり、また該ノイズによる半導体素子の劣化又は破壊を防ぐこともできる。

【0004】

例えば、特許文献1では、半導体回路と接続端子との間に、抵抗素子及びダイオードを含む保護回路を接続することで、ESDにより発生したサージ電流の平滑化及び放電経路の確保を行い、サージ電流の半導体回路への流入を防止する技術が開示されている。

【0005】

また、特許文献2では、表示装置の走査電極と表示部の外周に配置した導電線との間に、ソースとゲートを短絡させたMOS型トランジスタと、ゲートとドレインを短絡させたMOS型トランジスタとを直列に接続した保護回路を接続する技術が開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−58762号公報

【特許文献2】特開平7−92448号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

半導体装置の小型化、高集積化に伴い、保護回路の占有面積を小さくすることが望まれている。しかしながら、保護回路に用いる素子を小型化するとサージ耐性が低下してしまい、保護回路そのものが破壊されてしまうことがある。

【0008】

また、代表的な半導体材料であるシリコンを用いた素子(ダイオード、トランジスタなど)では、オフ状態でのリーク電流が比較的大きい。そのため、半導体回路に接続される配線(信号線など)と電源線との間に該素子で形成した保護回路を接続した場合、該配線間にリーク電流が流れ、該配線の電位や電源電位が変化し、半導体装置の動作を不安定にさせることがある。

【0009】

したがって、本発明の一態様では、占有面積が小さく、冗長性のある保護回路を提供することを目的の一つとする。また、リーク電流の小さい保護回路を提供することを目的の一つとする。

【課題を解決するための手段】

【0010】

本明細書に開示する本発明の一態様は、シリコンを用いた半導体素子、及び酸化物半導体を用いた半導体素子で構成された保護回路を有する半導体装置に関する。

【0011】

本明細書に開示する本発明の一態様は、基板上に、第1の配線と、第2の配線と、第3の配線と、第1の非線形素子及び第3の非線形素子を含む第1の保護回路と、第2の非線形素子及び第4の非線形素子を含む第2の保護回路と、を有し、第1の保護回路は、基板側から順に第1の非線形素子及び第3の非線形素子が重畳するように積層され、かつ該二つの非線形素子が電気的に直列接続されている構成であり、第2の保護回路は、基板側から順に第2の非線形素子及び第4の非線形素子が重畳するように積層され、かつ該二つの非線形素子が電気的に直列接続されている構成であり、第1の保護回路は、該保護回路を構成する第1の非線形素子及び第3の非線形素子が、第1の配線の電位が第2の配線の電位よりも高いときに順方向バイアスとなるように、第1の配線と第2の配線との間に電気的に接続され、第2の保護回路は、該保護回路を構成する第2の非線形素子及び第4の非線形素子が、第1の配線の電位が第3の配線の電位よりも低いときに順方向バイアスとなるように、第1の配線と第3の配線との間に電気的に接続されていることを特徴とする半導体装置である。

【0012】

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0013】

上記第1の配線は半導体回路に信号を入力するための信号線、第2の配線は高電位電源線、第3の配線は低電位電源線または接地電位線とすることができる。

【0014】

また、第1の非線形素子及び第2の非線形素子には、チャネル形成領域をシリコンで形成したトランジスタ、第3の非線形素子及び第4の非線形素子には、チャネル形成領域を化合物半導体で形成したトランジスタを用いることができる。特に、該化合物半導体として酸化物半導体を用いると、トランジスタのオフ電流は極めて小さくなる。したがって、配線間に接続される保護回路に該トランジスタを用いると、該配線間のリーク電流を低減することができる。

【0015】

また、該シリコンを用いたトランジスタには、オフ電流の低いpチャネル型トランジスタを用いることが好ましい。なお、第1乃至第4の非線形素子は、ドレインまたはソースの一方とゲート電極を短絡させて一方の端子とし、ドレインまたはソースの他方を他方の端子とする二端子素子として用いる。

【0016】

また、第1の非線形素子及び第2の非線形素子には、シリコンを用いて形成したダイオードを用いても良い。

【発明の効果】

【0017】

本発明の一態様である保護回路は、複数の非線形素子が積層された構成であるため、保護回路の占有面積を小さくすることができる。また、該複数の非線形素子は電気的に直列接続されているため、短絡不良に対して冗長性を有する。また、保護回路に用いる非線形素子のうちの少なくとも一つに、酸化物半導体を用いて形成したトランジスタを用いることで、保護回路が接続された配線間でのリーク電流を低減し、電源電位または信号の電位を安定にすることができる。

【図面の簡単な説明】

【0018】

【図1】半導体装置に用いる保護回路、及び該保護回路と配線との接続形態を説明する図。

【図2】半導体装置に用いる保護回路を説明する回路図。

【図3】半導体装置に用いる保護回路を説明する回路図。

【図4】半導体装置に用いる保護回路を説明する回路図。

【図5】半導体装置に用いる保護回路の作製方法を説明する工程断面図。

【図6】半導体装置に用いる保護回路の作製方法を説明する工程断面図。

【図7】半導体装置に用いる保護回路の作製方法を説明する工程断面図。

【図8】トランジスタの構造を説明する図。

【図9】メモリセルを説明する図。

【図10】電子機器を説明する図。

【図11】半導体装置に用いる保護回路を説明する断面図。

【図12】酸化物材料の結晶構造を説明する図。

【図13】酸化物材料の結晶構造を説明する図。

【図14】酸化物材料の結晶構造を説明する図。

【図15】計算によって得られた移動度のゲート電圧依存性を説明する図。

【図16】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

【図17】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

【図18】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

【図19】計算に用いたトランジスタの断面構造を説明する図。

【図20】酸化物半導体層を用いたトランジスタ特性のグラフ。

【図21】試料1のトランジスタのBT試験後のVg−Id特性を示す図。

【図22】試料2であるトランジスタのBT試験後のVg−Id特性を示す図。

【図23】試料Aおよび試料BのXRDスペクトルを示す図。

【図24】トランジスタのオフ電流と測定時基板温度との関係を示す図。

【図25】Idおよび電界効果移動度のVg依存性を示す図。

【図26】基板温度としきい値電圧の関係および基板温度と電界効果移動度の関係を示す図。

【図27】半導体装置の上面図及び断面図。

【図28】半導体装置の上面図及び断面図。

【発明を実施するための形態】

【0019】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。

【0020】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0021】

(実施の形態1)

本実施の形態では、本発明の一態様における半導体装置に用いる保護回路の構成及び動作方法について説明する。

【0022】

図1は、本発明の一態様における半導体装置に用いる保護回路、及び該保護回路と配線との接続形態を示すものである。第1の保護回路121は、第1の非線形素子111及び第3の非線形素子113を有する。また、第2の保護回路122は、第2の非線形素子112及び第4の非線形素子114を有する。本発明の一態様における半導体装置は、半導体回路131に接続される第1の配線101、並びに第2の配線102及び第3の配線103を有し、第1の保護回路121は、第1の配線101と第2の配線102との間に電気的に接続され、第2の保護回路122は、第1の配線101と第3の配線103との間に電気的に接続される。

【0023】

第1の配線101は、半導体回路131に信号を入力するための信号線、第2の配線102は高電位電源線(VDD)、第3の配線103は低電位電源線(VSS)または接地電位線(GND)とすることができる。

【0024】

なお、上記非線形素子とは、印加電圧に対して電流が比例しない素子のことをいう。例えば、ダイオードではアノードの電位をカソードの電位よりも高くすることで順方向バイアスとなり、電流を流すことが容易になる。一方、カソードの電位をアノードの電位よりも高くすることで逆方向バイアスとなり、順方向バイアスと比べると電流を流すことがほとんどできなくなる。

【0025】

第1の保護回路121は、直列に接続された第1の非線形素子111及び第3の非線形素子113を有し、第1の配線101の電位が第2の配線102の電位よりも高いときに該二つの非線形素子が順方向バイアスとなるように第1の配線101と第2の配線102との間に接続される。

【0026】

第2の保護回路122は、直列に接続された第2の非線形素子112及び第4の非線形素子114を有し、第1の配線101の電位が第3の配線103の電位よりも低いときに該二つの非線形素子が順方向バイアスとなるように第1の配線101と第3の配線103との間に接続される。

【0027】

このような形態で第1の保護回路121及び第2の保護回路122を第1の配線101に接続することで、ESDなどの高いサージ電圧が第1の配線101に印加された場合でも、該保護回路が放電経路となり、サージ電流が半導体回路131に流れることを防ぐことができる。

【0028】

例えば、正のサージ電圧が第1の配線101に印加された場合、第1の保護回路121が順方向バイアスとなるため、第1の配線101から第2の配線102へ電流が流れる。また、負のサージ電圧が第1の配線101に印加された場合、第2の保護回路122が順方向バイアスとなるため、第3の配線103から第1の配線101へ電流が流れる。このようにしてESD等で第1の配線101に供給された電荷を打ち消し、半導体回路131への不要な電荷の流入を防ぐことができる。

【0029】

次に、保護回路の具体例を説明する。図2は、第1の保護回路121及び第2の保護回路122に用いる非線形素子として、ドレイン電極またはソース電極の一方とゲート電極を短絡し、ダイオード接続としたトランジスタを用いる場合の例である。図2においては、第1の非線形素子201及び第2の非線形素子202にpチャネル型のトランジスタ、第3の非線形素子203及び第4の非線形素子204にnチャネル型のトランジスタを用いる例を示している。本発明の一態様では、第1の非線形素子201及び第2の非線形素子202にチャネル形成領域にシリコンを用いたトランジスタを適用するため、第1の非線形素子201及び第2の非線形素子202には、nチャネル型トランジスタよりもオフ電流が低いpチャネル型トランジスタを用いることが好ましい。ただし、図3に示すように、第1の非線形素子301及び第2の非線形素子302をnチャネル型のトランジスタで構成しても良い。

【0030】

また、図4のように、第1の非線形素子401及び第2の非線形素子402を接合領域にシリコンを用いたダイオードとしても良い。なお、図2乃至図4の構成は自由に組み合わせることができる。例えば、第1の保護回路121をnチャネル型のトランジスタ及びpチャネル型のトランジスタで構成し、第2の保護回路122を二つのnチャネル型トランジスタで構成しても良い。

【0031】

また、該保護回路を構成する非線形素子の素子数は二つ以上であり、それらが電気的に直列接続されていれば良い。非線形素子の素子数を複数とすることで、一つの非線形素子が製造工程における工程不良、またはESDなどによる破壊などにより短絡した場合でも保護回路として機能させることができる。すなわち、冗長性を持たせることができる。なお、該非線形素子のうち、一つ以上は、後述するオフ電流の極めて小さいトランジスタで構成することが好ましい。また、該保護回路は直列接続された複数の非線形素子を一単位として、複数の単位を並列接続する構成であっても良い。非線形素子を並列接続することで保護回路全体に流せる電流が多くなり、非線形素子の破壊を抑えることができる。

【0032】

また、該保護回路に用いる複数の非線形素子は、できるだけ最小面積となるように、それぞれが重畳するように形成する。このように複数の非線形素子を重畳させることで保護回路の占有面積を小さくすることができる。

【0033】

なお、通常動作時においては、該保護回路に用いられる非線形素子が逆バイアス、または配線間の電位差が非線形素子の動作電圧を超えない状態であるため、該保護回路は基本的には動作しない。しかしながら、逆方向バイアスでも僅かな電流が流れるため、各配線間でリーク電流が流れ、電源線の電位または信号線の電位に変化が生じてしまうことがある。

【0034】

特に、シリコンを用いたダイオードやトランジスタでは、その逆方向電流やオフ電流が比較的大きく、上述の配線の電位変化が起きやすい。そのため、本発明の一態様では、保護回路に用いる非線形素子の一つ以上にオフ電流の極めて小さいトランジスタを用いる。

【0035】

オフ電流が極めて小さいトランジスタとしては、シリコンよりも広いバンドギャップを有する半導体をチャネル形成領域に用いたトランジスタが挙げられる。シリコンよりも広いバンドギャップを有する半導体としては化合物半導体があり、例えば、酸化物半導体、窒化物半導体などが知られている。

【0036】

具体的には、非常に高いオフ抵抗を得るためには、シリコン(バンドギャップ1.1eV)では不十分であり、バンドギャップが2.5eV以上4eV以下、好ましくは3eV以上3.8eV以下のワイドバンドギャップ半導体を使用すると良い。例えば、チャネルが形成される半導体層に酸化インジウム、酸化亜鉛等を含む酸化物半導体、窒化ガリウム等を含む窒化物半導体、硫化亜鉛等を含む硫化物半導体等を用いることができる。

【0037】

トランジスタのオフ抵抗は、チャネルが形成される半導体層において、熱的に励起されるキャリアの濃度に反比例する。ドナーやアクセプタによるキャリアが全く存在しない状態(真性半導体)であっても、シリコンの場合にはバンドギャップが1.1eVなので、室温(300K)での熱励起キャリアの濃度は1×1011cm−3程度である。

【0038】

一方、バンドギャップ3.2eVの半導体では熱励起キャリアの濃度は1×10−7cm−3程度となる。電子移動度が同じ場合、抵抗率は、キャリア濃度に反比例するので、バンドギャップ3.2eVの半導体の抵抗率は、シリコンより18桁も大きくなる。このような化合物半導体としては、例えばIn−Ga−Zn−O系やIn−Sn−Zn−O系の酸化物半導体が知られている。

【0039】

したがって、保護回路を構成する非線形素子の一つに上述したような化合物半導体で形成したトランジスタを用いれば、直列に接続される他の非線形素子がシリコンで形成されていてもリーク電流は小さくすることができ、保護回路が接続される配線の電位変化を抑制することができる。つまり、図2乃至図4の構成の保護回路においては、第3の非線形素子203及び第4の非線形素子204に化合物半導体で形成したトランジスタを用いることが好ましい。

【0040】

なお、本発明の一態様における半導体装置は、シリコンで形成された素子上に化合物半導体(例えば、酸化物半導体)で形成された素子が設けられている構成であることが好ましい。このような構成においては、保護回路を形成するための特別な工程を必要とせず、他の素子と同一工程で保護回路を形成することができる。もちろん、保護回路のみに化合物半導体を用いる構成であっても良い。

【0041】

該半導体装置としては、駆動回路部がシリコンを用いた素子で形成され、画素回路部が化合物半導体を用いた素子で形成された表示装置または撮像装置、記憶回路部がシリコンを用いた素子及び化合物半導体を用いた素子で形成された記憶装置、駆動回路部または演算回路部がシリコンを用いた素子で形成され、記憶回路部が化合物半導体を用いた素子で形成された記憶装置または演算装置などがある。該半導体装置は、化合物半導体を用いた素子の極めて小さいオフ電流特性を利用して、電位保持部の保持特性を向上させたものである。

【0042】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0043】

(実施の形態2)

本実施の形態では、実施の形態1に示した保護回路の作製方法の一例について説明する。なお、本実施の形態では、酸化物半導体を用いるトランジスタをノンセルフアラインのトップゲート型で作製する方法を一例として説明するが、トランジスタの構造はこれに限るものではなく、セルフアラインのトップゲート型、またはボトムゲート型の構造であっても良い。

【0044】

まず、単結晶シリコン基板500に絶縁層540(フィールド酸化膜とも言う)で分離した素子形成領域を形成する。素子分離領域の形成は、LOCOS法(Local Oxidation of Silicon)法)やSTI法(Shallow Trench Isolation)等を用いることができる。

【0045】

ここで基板は単結晶シリコン基板に限らず、SOI(Silicon on Insulator)基板等を用いることもできる。

【0046】

次に、素子形成領域を覆うようにゲート絶縁層となる第1の絶縁層536を形成する。例えば、熱処理を行い単結晶シリコン基板500に設けられた素子形成領域の表面を酸化させることにより酸化シリコン膜を形成することができる。また、熱酸化法により酸化シリコン膜を形成した後に、窒化処理を行うことによって酸化シリコン膜の表面を窒化させることにより、酸化シリコン膜と酸素と窒素を有する膜(酸窒化シリコン膜)との積層構造で形成してもよい。

【0047】

他の方法としては、例えば、単結晶シリコン基板500に設けられた素子形成領域の表面に高密度プラズマ処理により酸化処理または窒化処理を行うことにより、第1の絶縁層536として酸化シリコン膜または窒化シリコン膜を形成することができる。また、高密度プラズマ処理により素子形成領域の表面に酸化処理を行った後に、再度高密度プラズマ処理を行うことによって窒化処理を行ってもよい。この場合、素子形成領域の表面に接して酸化シリコン膜が形成され、当該酸化シリコン膜上に酸窒化シリコン膜が形成され、第1の絶縁層536は酸化シリコン膜と酸窒化シリコン膜とが積層された膜となる。

【0048】

次に、第1の絶縁層536を覆うように導電層を形成する。ここでは、導電層538aと導電層538bを順に積層して形成する。ここで、導電層は二層に限らず、単層または三層以上の積層構造としても良い。

【0049】

導電層538a、538bとしては、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素またはこれらの元素を主成分とする合金材料若しくは化合物材料を用いることができる。また、これらの元素を窒化した金属窒化膜を用いることもできる。他にも、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体材料を用いることもできる。

【0050】

ここでは、導電層538aとして窒化タンタルを形成し、その上に導電層538bとしてタングステンを形成して積層構造を設ける。なお、導電層538aとしては、窒化タングステン、窒化モリブデン、窒化チタンから選ばれた単層または積層膜を用いることができる。また、導電層538bとしては、タンタル、モリブデン、チタンから選ばれた単層または積層膜を用いることができる。

【0051】

次に、積層して設けられた導電層538a、538bを選択的にエッチングして、第1の絶縁層536上にゲート電極538、558を形成する。

【0052】

次に、素子形成領域以外を覆うようにレジストマスクを選択的に形成し、該レジストマスク及びゲート電極538、558をマスクとして不純物元素を導入することによってp+領域532a、532b、552a、552bを形成する。ここでは、pチャネル型のバルクトランジスタを形成するため、不純物元素としては、p型を付与する不純物元素であるホウ素(B)等を用いることができる。

【0053】

そして、層間絶縁層及び保護層として機能する第2の絶縁層539を成膜する。第2の絶縁層539としては、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、または窒化酸化シリコン膜などを用いることができる。

【0054】

この段階で、図5(A)に示すように、チャネル形成領域にシリコンを用いたトランジスタである第1の非線形素子201及び第2の非線形素子202の構造が完成する。

【0055】

次に、第1の非線形素子201及び第2の非線形素子202のソース領域またはドレイン領域の一方、ソース領域またはドレイン領域の他方、及びゲート電極538、558のそれぞれに通じるコンタクトホールを第2の絶縁層539に形成する。該コンタクトホールは、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。

【0056】

そして、接続配線541a、541b、561a、561bを形成する。このとき、接続配線541aによって、第1の非線形素子201のソース領域またはドレイン領域の一方とゲート電極538を短絡させ、接続配線561aによって、第2の非線形素子202のソース領域またはドレイン領域の一方とゲート電極558を短絡させる。

【0057】

該接続配線は、スパッタ法などの成膜方法により導電膜を形成した後、公知のフォトリソグラフィ法及びエッチング法を用いて形成することができる。該導電膜に用いられる材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステン等から選ばれた元素、または上述した元素を成分とする合金、または上述した元素を組み合わせた合金などが上げられる。また、該導電膜は単層でも2層以上の積層としてもよい。例えば、アルミニウムや銅などの金属膜の下側、または上側、若しくはその両方にクロム、タンタル、チタン、モリブデン、タングステン等の高融点金属膜を積層する構成とすることもできる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

【0058】

次に、該接続配線及び第2の絶縁層539上に、層間絶縁層及び平坦化層として機能する第3の絶縁層544を形成する(図5(B)参照)。第3の絶縁層544は、プラズマCVD法やスパッタ法で酸化シリコン膜などを形成した後、CMP(Chemical Mechanical Polishing)法等によって平坦化処理を行うことで形成することができる。

【0059】

また、第3の絶縁層544としては、ポリイミド系樹脂、アクリル系樹脂、ベンゾシクロブテン系樹脂、ポリアミド系樹脂、エポキシ系樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low−k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁層を複数積層させることで、第3の絶縁層544を形成してもよい。

【0060】

なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi−O−Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基(例えばアルキル基やアリール基)やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。

【0061】

これらの材料を用いた第3の絶縁層544の形成法は、特に限定されず、その材料に応じて、SOG法、スピンコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法等)、スクリーン印刷法、オフセット印刷法、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコーター等を用いることができる。

【0062】

次に、第1の非線形素子201及び第2の非線形素子202上に形成する酸化物半導体層を用いたトランジスタの作製方法について説明する。

【0063】

まず、第3の絶縁層544上に第4の絶縁層521を形成する。第4の絶縁層521は、下層からの不純物の拡散を抑制する機能を有する。

【0064】

また、第4の絶縁層521には、酸素を含む絶縁層を用いることが好ましい。例えば、酸化シリコン、酸化ガリウム、酸化ガリウムアルミニウム、酸化ガリウム亜鉛、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、酸化ハフニウム、またはこれらの混合材料を用いて単層で、または積層して形成する。第4の絶縁層521に酸素を含む絶縁層を用いることで、後述する酸化物半導体層の酸素欠損に対して酸素の補填を容易に行うことができる。これらの絶縁層は、プラズマCVD法やスパッタ法などの各種成膜方法で形成することができる。

【0065】

次に、第4の絶縁層521上に半導体層502、522を形成する。本実施の形態では、In−Ga−Zn−O系酸化物ターゲットを用いて、In−Ga−Zn−O系酸化物半導体層をスパッタ法により成膜し、公知のフォトリソグラフィ法及びエッチング法を用いて、島状の半導体層502、522を形成する(図5(C)参照)。

【0066】

用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0067】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0068】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属の酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する)、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0069】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0070】

また、酸化物半導体として、InMO3(ZnO)m(m>0、且つ、mは整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In3SnO5(ZnO)n(n>0、且つ、nは整数)で表記される材料を用いてもよい。

【0071】

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)あるいはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子数比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子数比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

【0072】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0073】

例えば、In−Sn−Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In−Ga−Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

【0074】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物の組成の近傍であるとは、a、b、cが、

(a―A)2+(b―B)2+(c―C)2≦r2

を満たすことをいい、rは、例えば、0.05とすればよい。他の酸化物でも同様である。

【0075】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0076】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0077】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0078】

なお、Raは、JIS B0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

【0079】

【数1】

【0080】

なお、上記において、S0は、測定面(座標(x1,y1)(x1,y2)(x2,y1)(x2,y2)で表される4点によって囲まれる長方形の領域)の面積を指し、Z0は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて評価可能である。

【0081】

In−Ga−Zn−O系酸化物半導体層をスパッタ法で成膜する際に用いる成膜用ターゲットには、例えば、組成比として、In2O3:Ga2O3:ZnO=1:1:1[mol数比]の金属酸化物を用いることができる。また、In2O3:Ga2O3:ZnO=1:1:2[mol数比]の金属酸化物を用いてもよい。

【0082】

また、酸化物半導体としてIn−Zn−O系の材料を用いる場合、用いるターゲットの組成比は、原子数比で、In:Zn=50:1〜1:2(mol数比に換算するとIn2O3:ZnO=25:1〜1:4)、好ましくはIn:Zn=20:1〜1:1(mol数比に換算するとIn2O3:ZnO=10:1〜1:2)、さらに好ましくはIn:Zn=15:1〜1.5:1(mol数比に換算するとIn2O3:ZnO=15:2〜3:4)とする。例えば、In−Zn−O系酸化物半導体の形成に用いるターゲットは、原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとする。

【0083】

また、In−Sn−Zn−O系の材料膜の形成に用いる酸化物半導体のターゲットの組成比は、In:Sn:Znが原子数比で、1:2:2、2:1:3、1:1:1、或いは20:45:35などを用いることができる。

【0084】

ここで、酸化物半導体層にはアルカリ金属、水素原子、水素分子、水、水酸基、または水素化合物などの不純物ができるだけ混入しないように形成することが好ましい。例えば、スパッタ成膜用ターゲットや成膜に用いるガスに上記不純物が混入しないようにする。スパッタガスにアルゴン及び酸素を用いる場合は、純度9Nのアルゴン(露点−121℃、H2O;0.1ppb、H2;0.5ppb)及び純度8Nの酸素(露点−112℃、H2O;1ppb、H2;1ppb)を用いることが好ましい。

【0085】

また、成膜の際、成膜装置内を十分排気し、成膜時に基板を加熱しながら成膜することにより、成膜された酸化物半導体層に含まれる不純物濃度を低減することができる。また、酸化物半導体層に加熱処理をして酸化物半導体層中の水分及び水素を脱離しても良い。なお、該加熱処理は、酸化物半導体層の成膜後であれば、どの時点で行っても良い。なお、該加熱処理後の酸化物半導体層中の水素濃度を5×1019/cm3以下、好ましくは5×1018/cm3以下とすることで、電気特性及び動作の信頼性の高いトランジスタ等の素子を作製することができる。

【0086】

酸化物半導体層としては、結晶性部分と非結晶性部分とを有し、結晶性部分の配向がc軸配向に揃っている酸化物半導体であるCAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜を用いてもよい。

【0087】

CAAC−OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC−OS膜は、非晶質相に結晶部を有する結晶−非晶質混相構造の酸化物半導体層である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0088】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0089】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体層の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0090】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に熱処理などの結晶化処理を行うことにより形成される。

【0091】

CAAC−OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

【0092】

なお、酸化物半導体層を構成する酸素の一部は窒素で置換されてもよい。

【0093】

また、CAAC−OS膜のように結晶部を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0094】

CAAC−OS膜の結晶構造の一例について図12乃至図14を用いて詳細に説明する。なお、特に断りがない限り、図12乃至図14は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図12において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

【0095】

図12(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図12(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図12(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図12(A)に示す小グループは電荷が0である。

【0096】

図12(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図12(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図12(B)に示す構造をとりうる。図12(B)に示す小グループは電荷が0である。

【0097】

図12(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図12(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図12(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあってもよい。図12(C)に示す小グループは電荷が0である。

【0098】

図12(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図12(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図12(D)に示す小グループは電荷が+1となる。

【0099】

図12(E)に、2個のZnを含む小グループを示す。図12(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図12(E)に示す小グループは電荷が−1となる。

【0100】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

【0101】

ここで、これらの小グループ同士が結合する規則について説明する。図12(A)に示す6配位のInの上半分の3個のOは、下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Inを有する。図12(B)に示す5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。図12(C)に示す4配位のZnの上半分の1個のOは、下方向に1個の近接Znを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。したがって、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)、または4配位の金属原子(Zn)のいずれかと結合することになる。

【0102】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0103】

図13(A)に、In−Sn−Zn−O系の層構造を構成する中グループのモデル図を示す。図13(B)に、3つの中グループで構成される大グループを示す。なお、図13(C)は、図13(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0104】

図13(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図13(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図13(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0105】

図13(A)において、In−Sn−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0106】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ−0.667、−0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。したがって、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷−1が必要となる。電荷−1をとる構造として、図12(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0107】

具体的には、図13(B)に示した大グループが繰り返されることで、In−Sn−Zn−O系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn−O系の層構造は、In2SnZn2O7(ZnO)m(mは0または自然数。)とする組成式で表すことができる。