半導体装置

【課題】回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供する。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、例えば2逓倍クロック信号を入力するコンパレータに適用して好適な構成の半導体装置に関する。

【背景技術】

【0002】

クロック信号(CLK)の周波数を2逓倍した2逓倍クロック信号(CLKX2)に基づき比較動作を行うコンパレータが用いられている(図11(B)参照)。このコンパレータは、例えばアナログ信号をデジタル信号に変換するアナログデジタル変換器(ADC)において2つの信号の電圧レベルを比較するコンパレータとして用いられる(図11(A)参照)。

【0003】

図12は、コンパレータに2逓倍クロック信号を供給する2逓倍器(Frequecny Doubler)として、PLL(Phase Locked Loop:位相同期ループ)を用いた典型的な回路構成の一例を示す図である。2逓倍PLL30は、発振回路(図11(B)の4)等のクロック生成回路から供給されるクロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成し、コンパレータ10に供給する。特に制限されないが、コンパレータ10は、第1、第2の入力信号INP、INNを入力し、2逓倍クロック信号CLKX2がHigh(例えば電源電位)のとき、第1、第2の入力信号INP、INNの電圧を比較し、第1、第2の出力COP、CONに比較結果を出力し、2逓倍クロック信号CLKX2がLow(例えばグランド電位)のとき、第1、第2の出力COP、CONはともにHighレベル(電源電圧)にリセットされる。

【0004】

図12の例では、SRラッチ(SR Latch)11は、コンパレータ10の第1、第2の出力COP、CONをセット入力端子 ̄S、リセット入力端子 ̄Rに受けて、相補の出力Q、QBを出力する。SRラッチ11は、( ̄S、 ̄R)=(Low、High)のとき、(Q、QB)=(High、Low)にセットされ、( ̄S、 ̄R)=(High、Low)のとき、(Q、QB)=(Low、High)にリセットされ、( ̄S、 ̄R)=(High、High)のとき、(Q、QB)は前の状態を保持する。なお、図12において、端子S、Rの上のバー( ̄)は該端子に入力される信号がLowレベルでアクティブであることを表している。コンパレータ10の出力(COP、CON)=(Low、High)に応答して、SRラッチ11の出力は(Q、QB)=(High、Low)にセットされ、(COP、CON)=(High、Low)に応答して、(Q、QB)=(Low、High)にリセットされ、(COP、CON)=(High、High)のときは、(Q、QB)は前の状態を保持する。以下、他の図面のSRラッチ11も、図12のSRラッチ11と同様の構成とされる。

【0005】

なお、図12では、2逓倍PLL30の内部構成は図示されていないが、PLLは、よく知られているように、例えば制御電圧で発振周波数を可変させるVCO(Voltage Controlled Oscillator:電圧制御発振器)と、VCOの発振信号を分周する分周器(Divider)と、分周器の出力と入力クロック信号の位相差を検出する位相比較器(PD:Phase Detector又はPFD:Phase Frequency Detector)と、位相比較器の出力を受け容量を充電、放電するチャージポンプ(CP:Charge Pump)と、チャージポンプの電圧を平滑化するループフィルタ(LPF: Loop Filter)を備え、ループフィルタの出力電圧が制御電圧としてVCOに供給される。2逓倍PLL30では、VCOの発振信号を分周する分周器として、例えば第1の分周器で2逓倍クロック信号CLKX2を生成し、2逓倍クロック信号CLKX2をさらに2分周してクロック信号CLKと同一周波数のクロック信号を生成し位相比較器に入力する。2逓倍PLL30は、入力クロック信号CLKに位相同期した逓倍クロック信号CLKX2を生成する。なお、PLLは、完全デジタルPLL(ADPLL:All Digital PLL)であってもよい。

【0006】

2逓倍器としてPLLを用いた図12の構成の場合、回路面積が増大し電力が増加する。

【0007】

より簡素な回路構成として、時間遅延技術(Time−Delay Technique)を用いた2逓倍器が知られている。図13は、時間遅延技術(Time−Delay Technique)を用いた2逓倍器の典型的な回路構成を示す図である。Time−Delay Techniqueの詳細は、例えば非特許文献1が参照される。

【0008】

図13を参照すると、2逓倍器20’は、遅延τがT/4(ただし、TはCLKの周期)の遅延回路19(Delay)と、位相比較器として機能する排他的論理和(Exclusive OR)回路18とを備えている。なお、図13の2逓倍器20’は、非特許文献1のFigure.1に基づき、本願で新たに作成したものである。図13において、コンパレータ10、SRラッチ11は、図12と同一であるため、説明は省略する。

【0009】

2逓倍器20’において、遅延回路19は、入力クロック信号CLK(デューティ=50%とする)をτ=T/4遅延させたクロック信号(遅延クロック信号)CLKDを生成する。遅延クロック信号CLKDと入力クロック信号CLKは排他的論理和回路18に入力され、排他的論理和回路18から2逓倍クロック信号CLKX2が出力される。すなわち、排他的論理和回路18は、入力クロック信号CLKと遅延クロック信号CLKDが同一論理レベル(ともにHighレベルであるか、又はともにLowレベル)のとき、Lowを出力し、入力クロック信号CLKと遅延クロック信号CLKDが互いに異なる論理レベルのとき、Highを出力する。なお、非特許文献1のFigure.1では、遅延回路は、積分器とコンパレータを備え、積分器は、矩形波である入力クロック信号CLKを積分して三角波を出力し、コンパレータは、積分器からの三角波を基準電圧と比較しCLKからT/4遅延させた矩形波を出力する構成とされている。図13において、遅延回路19は、積分器とコンパレータの構成に制限されるものでなく、例えばCMOSインバータを偶数段接続した構成としてもよい。

【0010】

図14は、図13の回路において、入力クロック信号CLKと、遅延回路10の出力信号(遅延クロック信号)CLKDと、排他的論理和回路18の出力信号である2逓倍クロック信号CLKX2のそれぞれのタイミング波形を示す図である。ここでは、クロック信号CLKの周期をTとし、そのデューティ=50%であるものとし、遅延回路19の遅延τ=T/4とする。入力クロック信号CLKを遅延回路19でτ=T/4遅延させた遅延クロック信号CLKDと、入力クロック信号CLKとを排他的論理和回路18で比較することで、遅延クロック信号CLKDと入力クロック信号CLKの論理レベルの異なるときに、Highとなる2逓倍クロック信号CLKX2が生成される。図14に示すように、入力クロック信号CLKの立ち上がりエッジと立ち下がりエッジにそれぞれ応答してHighに立ち上がるパルス(パルス幅=T/4)、周期=T/2の2逓倍クロック信号CLKX2が生成される。図14では、2逓倍クロック信号CLKX2のデューティは50%である。

【0011】

図13の2逓倍器20’は、遅延回路19と1つの論理ゲート(Exclusive OR)で構成され、回路構成が簡素化されており、図12の2逓倍PLL30を備えた構成と比較して、回路面積の削減、消費電力の低減が可能である。

【先行技術文献】

【非特許文献】

【0012】

【非特許文献1】Brad R. Jackson and Carlos E. Saavedra, "An L-Band CMOS Frequency Doubler using a Time-Delay Technique" Silicon Monolithic Integrated Circuits in RF Systems, Jan. 2006

【発明の概要】

【発明が解決しようとする課題】

【0013】

以下に、本発明者によって為された関連技術の分析を示す。

【0014】

前述したように、2逓倍器として、図12に示した2逓倍PLLを備えた構成は、入力クロック信号CLKに位相同期した2逓倍クロック信号CLKX2を生成することができるが、PLL自体の構成が、コンパレータ等と比べて大きく且つ複雑であることから、面積及び電力がともに増加する、という問題点を有している。

【0015】

一方、図13の2逓倍器20’の場合、遅延回路19の遅延時間τは、製造プロセスや、電源電圧変動、温度等によってばらつく。

【0016】

図15は、図13の構成のタイミング動作上の問題点を説明するための図である。図15(A)、図15(B)には、図13の入力クロック信号CLK、遅延クロック信号CLKD、2逓倍クロック信号CLKX2のタイミング波形が示されており、図15(A)では、さらに、コンパレータ10の状態(CMP状態)が示されている。コンパレータ10の状態(CMP状態)の「動作」は、コンパレータ10がINPとINNの電圧を比較する動作状態にあることを表しており、CMP状態の「停止」は、コンパレータ10がINPとINNの電圧比較動作を停止している状態を表している。コンパレータ10は、2逓倍クロック信号CLKX2がHighとなってから、第1、第2の出力COP、CONの値(比較結果)を確定するまでに時間CMP_Delayを要する。

【0017】

図15(A)は、図13の構成の第1の問題点を説明する図である。第1の問題点は、遅延回路19の遅延τがコンパレータ10の判定動作時間よりも小さくなる場合に生じる。図15(A)の場合、遅延回路19の遅延τ’はτ=T/4(Tはクロック信号CLKの1周期)よりも短く、コンパレータ10の比較動作の確定に必要な時間区間(CMP_Delay)よりも短い。すなわち、遅延クロック信号CLKDは、入力クロック信号CLKのLowからHighへの立ち上がりから遅延τ’で、LowからHighに立ち上がる。入力クロック信号CLKの立ち上がりでHighとなった2逓倍クロック信号CLKX2は、遅延クロック信号CLKDのLowからHighへの立ち上がりエッジに応答して、図15(A)の破線のタイミングでHighからLowに立ち下がる。2逓倍クロック信号CLKX2のHighパルス期間(コンパレータの動作期間)は、コンパレータ10の比較動作の確定に必要な時間区間(=CMP_Delay)よりも短い。この結果、図15(A)の「CMP状態」に示すように、コンパレータ10の比較結果が確定する前に、CLKDがHighとなり、CLKX2がLowとなるため、コンパレータ10は比較動作を停止してしまう。この結果、コンパレータ10の第1、第2の出力COP、CONには正しい比較結果が出力されない。

【0018】

図15(B)は、図13の構成の第2の問題点を説明する図である。図13の遅延回路19の遅延τ’が、入力クロック信号CLKの半周期(=T/2)よりも大きくなると、2逓倍クロック信号CLKX2は、コンパレータ10が正しく動作するために必要な2逓倍波形とはならない。図15(B)では、遅延クロック信号CLKDは入力クロック信号CLKがLowからHighに立ち上がり、その後、HighからLowに立ち下ったのちに、LowからHighに立ち上がっている(τ’>T/2)。このため、2逓倍クロック信号CLKX2は、入力クロック信号CLKの立ち上がりでHighとなり、T/2後の入力クロック信号CLKの立ち下がりでLowとなり、時間区間(τ’−T/2)ののち、遅延クロック信号CLKDの立ち上がりでHighとなり、次サイクルの入力クロック信号CLKがLowからHighに立ち上がるまでの期間Highとなる。このCLKX2の波形は、入力クロック信号CLKの1周期(=T)内において、連続する2つのHighパルスのうち1発目のHighパルスのパルス幅がT/2となり、時間(τ’−T/2)の間Lowとなり、次のHighパルスは、次サイクルの入力クロック信号CLKの立ち上がりまでの時間区間(T−τ’)Highとなる。図15(B)のCLKX2の波形では、連続する2つのHighパルスの間のLow期間が短いため、コンパレータ10のリセット動作に必要な時間が確保できない場合がある。

【0019】

したがって、本発明は、遅延回路の遅延時間のばらつき等に起因して生じる上記問題点に鑑みて創案されたものであって、その目的は、回路構成の簡素化を図るとともに、上記問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供することにある。

【課題を解決するための手段】

【0020】

上記課題を解決するため、概略以下の構成の半導体装置が提供される(ただし、以下に制限されるものでない)。

【0021】

本発明によれば、入力クロック信号を第1の遅延回路で遅延させた遅延クロック信号と、前記入力クロック信号とを位相比較器に入力し、前記入力クロック信号の周波数を2逓倍した2逓倍クロック信号を生成する2逓倍回路と、

前記2逓倍回路からの前記2逓倍クロック信号を受け、前記2逓倍クロック信号が第1の論理レベルのとき、第1、第2の入力信号の大小の比較動作を行い、前記2逓倍クロック信号が第2の論理レベルのとき、比較動作を停止するコンパレータと、

前記コンパレータの出力をモニタし、前記コンパレータが比較動作を完了したことを検出した時点でトリガ信号を出力する第1の回路と、を備え、前記第1の遅延回路は、前記入力クロック信号を、少なくとも前記第1の回路から前記トリガ信号が出力される時点まで遅延させ、前記遅延クロック信号として出力する可変遅延器を備えた半導体装置が提供される。

【発明の効果】

【0022】

本発明によれば、回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる上記問題点を解消し、コンパレータの動作を保証することができる。

【図面の簡単な説明】

【0023】

【図1】本発明の一実施形態の構成を示す図である。

【図2】本発明の一実施形態の動作を説明するためのタイミング図である。

【図3】本発明の実施例1の構成を示す図である。

【図4】本発明の実施例1の動作を説明するためのタイミング図である。

【図5】本発明の実施例2の構成を示す図である。

【図6】実施例1(2)において、クロック信号CLKにDuty誤差が生じたときのCLKX2の波形を示す図である。

【図7】本発明の実施例3の構成を示す図である。

【図8】本発明の実施例4の構成を示す図である。

【図9】コンパレータの構成例を示す図である。

【図10】周波数2逓倍器を搭載する半導体チップの一例を示す図である。

【図11】(A)はADCのコンパレータクロックに周波数2逓倍器を使用した回路を示す図である。(B)はコンパレータ単体のクロックに周波数2逓倍器を使用した回路を示す。

【図12】コンパレータクロックに2逓倍器としてPLL2逓倍器を使用した関連技術を示す図である。

【図13】コンパレータクロックに2逓倍器としてTime−Delay Techniqueの2逓倍器を使用した関連技術を示す図である。

【図14】図13の2逓倍器の動作を説明するためのタイミング図である。

【図15】(A)、(B)は図13の2逓倍器の問題点を説明するためのタイミング図である。

【発明を実施するための形態】

【0024】

本発明の好ましい形態の1つによれば、入力クロック信号(CLK)を第1の遅延回路(例えば図1の可変遅延器16)で遅延させた遅延クロック信号(CLKD)と、入力クロック信号(CLK)の位相を位相比較器(例えば図1の18)で比較することにより、入力クロック信号(CLK)の周波数を2逓倍した2逓倍クロック信号(CLKX2)を生成する2逓倍回路(例えば図1の2逓倍器20)と、2逓倍回路(図1の20)からの2逓倍クロック信号(CLKX2)を受け、2逓倍クロック信号(CLKX2)が第1の論理レベル(例えばHighレベル)のとき、比較動作を行い、2逓倍クロック信号(CLKX2)が第2の論理レベル(例えばLowレベル)のとき、比較動作を停止するコンパレータ(10)と、前記コンパレータ(10)の出力をモニタし、前記コンパレータ(10)の比較結果を出力したことが確認された時点で、トリガ信号(DLCLK)を生成する回路(例えば図1の12、14、あるいは図3の13)を備えている。第1の遅延回路(図1の16)は、少なくとも、第1の回路(図1の12、14、あるいは図3の13)からトリガ信号(DLCLK)が出力される時点まで、前記入力クロック信号(CLK)を可変に遅延させた信号を前記遅延クロック信号(CLKD)として出力する。位相比較器(図1の18)は、遅延クロック信号(CLKD)と入力クロック信号(CLK)が互いに異なる論理レベルのとき、第1の論理レベル(例えばHighレベル)を出力し、遅延クロック信号(CLKD)と入力クロック信号(CLK)が同一の論理レベルのとき、第2の論理レベル(例えばLowレベル)を出力する。

【0025】

2逓倍クロック信号(CLLX2)は、入力クロック信号(CLK)の第2の論理レベル(Lowレベル)から第1の論理レベル(Highレベル)への遷移に応答して第1の論理レベル(Highレベル)となり、入力クロック信号(CLK)を、トリガ信号(DLCLK)が出力される時点まで遅延させた遅延クロック信号(CLKD)の第1の論理レベル(Highレベル)への遷移に応答して、第2の論理レベル(Lowレベル)となる。このため、コンパレータ(10)は、比較動作が確定(完了)したのちに、比較動作を停止する。このため、製造プロセスによるばらつき、電源電圧変動、温度変化等による遅延回路の遅延変動により、逓倍クロック信号の第1の論理レベルの期間が狭まり、コンパレータ(10)が比較動作を確定する前に停止してしまうという、図13の回路に関する第1の問題点を解消している。

【0026】

また、2逓倍クロック信号(CLLX2)は入力クロック信号(CLK)の第2の論理レベルから第1の論理レベルへの遷移で第1の論理レベルに遷移し、コンパレータ(10)での比較動作が確定した時点で第2の論理レベルに遷移させるように制御するため、図13の回路に関する上記第2の問題点を解消している。図13の回路では、2逓倍クロック信号(CLLX2)は、入力クロック信号(CLK)の第2の論理レベル(例えばLow)から第1の論理レベル(例えばHigh)への遷移で第1の論理レベルに遷移し、遅延回路(19)の遅延τの後に第2の論理レベルとなる。一方、図13の回路では、2逓倍クロック信号(CLLX2)の第1の論理レベル(Highレベル)から第2の論理レベル(Lowレベル)への遷移はコンパレータ(10)での比較動作が確定する時点とは無関係とされる。以下実施形態に即して説明する。

【0027】

<実施形態>

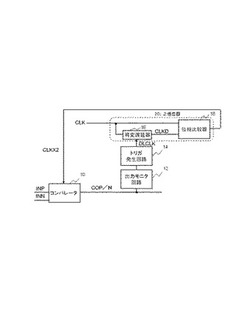

図1は、本発明の一実施形態の構成を示す図である。図1を参照すると、本実施形態においては、コンパレータ10と、出力モニタ回路12と、トリガ発生回路14と、可変遅延器16と、位相比較器18を備えている。可変遅延器16と、位相比較器18は2逓倍器20を構成している。コンパレータ10は、図12、図13を参照して説明したものと同一の構成とされ、2逓倍クロック信号CLKX2がHighのとき、入力信号INP、INNの電圧比較を行い、2逓倍クロック信号CLKX2がHighからLowになると、比較動作を停止する。特に制限されないが、2逓倍クロック信号CLKX2がLowの期間、出力COP/NともHighレベルにプリチャージされる。

【0028】

出力モニタ回路12と、トリガ発生回路14は、コンパレータ10の出力COP/Nをモニタリングし、コンパレータ10が比較結果を出したことを検出すると、トリガ信号DLCLKを出力する。出力モニタ回路12とトリガ発生回路14を1つの回路ブロック又は論理ゲートで構成するようにしてもよいことは勿論である。

【0029】

可変遅延器16は、入力クロック信号CLKを入力し、入力クロック信号CLKの立ち上がりエッジをトリガ信号DLCLKの出力タイミング(DLCLKのLowからHighへの立ち上がりのタイミング)まで遅延させた遅延クロック信号CLKDを出力する。

【0030】

位相比較器18は、入力クロック信号CLKと遅延クロック信号CLKDの位相を比較し、位相差(一方がHigh、他方がLowのとき、その位相差)に応じたパルス幅のHighパルスを出力する。

【0031】

図2は、図1の回路の動作を説明するタイミング図である。図2は、図1の入力クロック信号CLK、2逓倍クロック信号CLKX2、コンパレータ出力COP/Nの一方COP、トリガ信号DLCLK、遅延クロック信号CLKDのタイミング波形の一例が示されている。COPの波形において、枠で囲んだ区間は、コンパレータの判定区間を模式的に表している。図1、図2を参照して、本実施形態の動作を説明する。

【0032】

まず、入力クロック信号CLKがLowからHighに立ち上がった時、遅延クロック信号CLKDがLowの場合、位相誤差があるため、位相比較器18の出力である2逓倍クロック信号CLKX2はHighとなる。

【0033】

2逓倍クロック信号CLKX2のHighを受け、コンパレータ10はINPとINNの電圧の比較動作を開始する。

【0034】

コンパレータ10の出力をモニタする出力モニタ回路12とトリガ発生回路14は、コンパレータ10の比較結果の出力を検出すると、トリガ信号DLCLKを活性状態(例えばHIghレベル)とする。

【0035】

可変遅延器16は、トリガ信号DLCLKのLowからHighへの立ち上がりを受けて、入力クロック信号CLKのエッジ(例えば立ち上がりエッジ)をトリガ信号DLCLKの立ち上がりエッジまで遅延させる。トリガ信号DLCLKの立ち上がりエッジに応答して、可変遅延器16から出力される遅延クロック信号CLKDはHighとなる。

【0036】

遅延クロック信号CLKDがLowからHighになると、入力ロック信号CLKと遅延クロック信号CLKDがともにHighであることから、これらの信号に位相差はなくなり、位相比較器18はその出力である2逓倍クロック信号CLKX2をLowとする。

【0037】

つづいて、入力ロック信号CLKがHighからLowに立ち下がると、遅延クロック信号CLKDはHighであるため、位相比較器18から出力される2逓倍クロック信号CLKX2はHighとなる。2逓倍クロック信号CLKX2のHighを受け、コンパレータ10はINPとINNの電圧の比較動作を開始する。この後の動作は、前述の動作を繰り返す。

【0038】

本実施形態によれば、コンパレータ10での比較動作の終了(比較結果の確定)の検出結果に基づき、トリガ信号DLCLKを活性化し、トリガ信号DLCLKの活性化のタイミングに対応して、遅延クロック信号CLKDの立ち上がりエッジを生成し、位相比較器18で遅延クロック信号CLKDと入力クロック信号CLKと位相比較して2逓倍クロック信号CLKX2を生成している。このため、図15(A)、(B)で説明した問題点を解消し、コンパレータ10の動作を保証している。

【0039】

<実施例1>

図3は、実施例1として、図1の具体的な構成例を示す図である。図3を参照すると、コンパレータ10と、SRラッチ11と、NAND回路(否定論理積回路)からなる出力モニタ&トリガ発生回路13と、可変遅延器(D Latch)16と、位相比較器(排他的論理和回路)18とからなる。実施例1の出力モニタ&トリガ発生回路(NAND回路)13は、図1の出力モニタ回路12とトリガ発生回路14に対応し、図1の出力モニタ回路12とトリガ発生回路14を1つの回路にまとめたものである。図1の可変遅延器16は、入力クロック信号CLKをデータ端子に入力し、トリガ信号をクロック端子に入力し、クロック端子の立ち上がりエッジでデータ端子の信号値をキャプチャ出力するエッジトリガ型のD型ラッチ(D Latch)で構成される。D型ラッチは、エッジトリガ型のD型フリップフロップで構成してもよい。位相比較器18は、図13と同様、排他的論理和回路(EXOR)で構成される。以下では、説明の簡単のため、可変遅延器を構成するD型ラッチを参照符号16、位相比較器を構成する排他的論理和回路を参照符号18で参照する場合もある。図4は、図3の動作例を説明するタイミング波形図である。

【0040】

図3と図4を参照して、コンパレータ10に入力される第1、第2の入力信号INP、INNの電圧レベルがINP<INNの場合の動作を説明する。

【0041】

コンパレータ10は、2逓倍クロック信号CLKX2がLowの期間でリセットがかかり、第1、第2の出力COP、CONをともにHighとする。

【0042】

遅延クロック信号CLKDがLowレベルのときに、入力クロック信号CLKがLowからHighに立ち上がると、位相比較器18の出力である2逓倍クロック信号CLKX2は、入力クロック信号CLKのHighへの立ち上がりに応答してHighに立ち上がる。

【0043】

2逓倍クロック信号CLKX2がHighとなると、コンパレータ10は第1、第2の入力信号INP、INNの電圧レベルを比較する比較動作を行う。

【0044】

コンパレータ10の比較判定に要する時間(図15(A)のCMP_Delay)に従い、2逓倍クロック信号CLKX2がLowからHighに立ち上がってからしばらくして、INP<INNに対応して、第1の出力COPがHighからLowとなる。第2の出力CONはHighのまま変化せず比較動作が終了する。なお、INP>INNの場合、2逓倍クロック信号CLKX2がLowからHighに立ち上がってからしばらくして、第2の出力CONがHighからLowとなり、第1の出力COPはHighのまま変化せず比較動作が終了する。

【0045】

INP<INNに対応して、コンパレータ10の第1の出力COPがHighからLowとなり、第2の出力CONはHighのままであるため、第1、第2の出力COP、CONを入力するNAND回路13の出力信号であるトリガ信号DLCLKは、LowからHighとなる。D型ラッチ16は、トリガ信号DLCLKのLowからHighへの立ち上がりエッジに応答して、入力クロック信号CLK(その時点でHighレベル)をキャプチャし、Highを出力する。すなわち、D型ラッチ16の出力信号である遅延クロック信号CLKDはHighとなる。

【0046】

遅延クロック信号CLKDがLowからHighに変化した時点で、入力クロック信号CLKはHighであるため、位相比較器18の入力はともにHighとなり、位相比較器18から出力される2逓倍クロック信号CLKX2はHighからLowに変化する。2逓倍クロック信号CLKX2のLowを受けて、コンパレータ10にリセットがかかり、コンパレータ10の第1の出力COPはLowからHighとなる。第2の出力CONはHighを保つ。

【0047】

実施例1によれば、コンパレータ10の第1、第2の出力COP、CONの値の変化時点(比較結果確定時点)まで、入力クロック信号CLKの立ち上がりエッジを遅延させて遅延クロック信号CLKDの立ち上がりエッジを生成し、該入力クロック信号CLKと該遅延クロック信号CLKDに基づき逓倍クロック信号CLKX2を生成しているため、前記関連技術の前記問題点を解消している。

【0048】

<実施例2>

次に、実施例2を説明する。図5は、実施例2の構成を示す図である。図5を参照すると、実施例2は、図3の実施例1の構成において、可変遅延器(D型ラッチ)16の出力と位相比較器18の入力の間のパスに、遅延回路15が挿入されている。図3において、コンパレータ10の第1、第2の出力COP、CONから2逓倍クロック信号CLKX2までの遅延時間が、仮に0sec(すなわち、遅延無し)と仮定すると、コンパレータ10の比較動作の終了過程時に、トリガ信号DLCLKがHighに立ち上がり、直ちに2逓倍クロック信号CLKX2がLowに立ち下がり、コンパレータ10にリセットをかけ、第1、第2の出力COP、CONをHighにリセットしてしまう可能性がある。この場合、コンパレータ10の第1、第2の出力COP、CONは、正しく後段のSRラッチ11等に伝達されない。

【0049】

本実施例では、図5に示すように、可変遅延器(D型ラッチ)16と位相比較器18の間に遅延回路15を挿入し、コンパレータ10の比較動作の終了過程に、直ちに2逓倍クロック信号CLKX2がLowに立ち下がって、コンパレータ10にリセットをかける事態の発生を回避している。遅延回路15は、CMOSインバータを複数段接続する構成としてもよいし、あるいは配線遅延等を利用した構成としてもよい。本実施例によれば、コンパレータ10の比較動作の終了過程時に、コンパレータ10にリセットをかけ、第1、第2の出力COP、CONをHighにリセットしてしまうことを確実に回避することができる。

【0050】

<実施例3>

次に、実施例3を説明する。図6は、入力クロック信号CLKのデューティに誤差が生じた場合における、図3の前記実施例1の2逓倍クロック信号CLKX2の波形の一例を示す図である。前記実施例1において、2逓倍器20は、入力クロック信号CLKの立ち上がりと立ち下がりエッジを使用して、2逓倍クロック信号CLKX2を生成している。このため、入力クロック信号CLKにデューティ誤差が生じると、入力クロック信号CLKのHigh期間とLow期間の差により、2逓倍クロック信号CLKX2の周波数にずれが生じる。例えば図6に示すように、入力クロック信号CLKのHigh期間が短いと、入力クロック信号CLKの立ち上がりと立ち下がりに応答して生成される2逓倍クロック信号CLKX2の2発のHighパルスの時間間隔が狭まり、次のCLKの立ち上がりに応答して生成される2逓倍クロック信号CLKX2のHighパルスとの間の時間間隔は広がる。

【0051】

図7は、実施例3の構成を示す図である。実施例3では、この問題を解決するため、図7に示すように、図3の構成において、入力クロック信号CLKを入力しデューティを補正するデューティ補正回路17を備え、デューティ補正回路17の出力を、位相比較器18とD型ラッチ16に入力している。デューティ補正回路17において、入力クロック信号CLKのデューティが50%(High期間とLow期間が等しい)となるように補正した信号を位相比較器18に入力し、デューティを補正した信号の立ち上がりエッジと立ち下がりエッジに応答して、2逓倍クロック信号CLKX2の立ち上がりエッジを生成している。このため、図6のCLKX2のような波形となることは回避される。デューティ補正回路17は、入力クロック信号CLKのデューティを例えば50%に近づくように補正するものであり、任意の公知の構成を用いることができる。本実施例によれば、入力クロック信号CLKのデューティを例えば50%に近づくように補正するため、入力クロック信号CLKにデューティ誤差が生じた場合でも、図6のような2逓倍クロック信号CLKX2が出力されることを回避することができる。

【0052】

<実施例4>

図8は、実施例4の構成を示す図である。図8に示すように、本実施例は、図3の実施例1の構成に、前記実施例2の遅延回路15と、前記実施例3のデューティ補正回路17を備えている。実施例4は、前記実施例2と前記実施例3の作用効果を併せ持つ。

【0053】

<実施例5>

図9は、前記実施形態及び各実施例で説明したコンパレータ10の構成の一例を示す図である。なお、コンパレータ10の構成は図9の構成に限定されるものでないことは勿論である。図9を参照すると、

ソースがGND(あるいはVSS:0V)に接続され、ゲートがINP端子に接続されたNMOSトランジスタNM1と、

ソースがGND(あるいはVSS)に接続され、ゲートがINN端子に接続されたNMOSトランジスタNM2と、

NMOSトランジスタNM1のドレインにソースが接続され、ゲートがCOP端子に接続されたNMOSトランジスタNM3と、

NMOSトランジスタNM2のドレインにソースが接続され、ゲートがCON端子に接続されたNMOSトランジスタNM4と、

NMOSトランジスタNM3のドレインにソースが接続され、ゲートがCLKX2端子に接続されたNMOSトランジスタNM5と、

NMOSトランジスタNM4のドレインにソースが接続され、ゲートがCLKX2端子に接続されたNMOSトランジスタNM6と、

ソースが電源VDDに接続され、NMOSトランジスタNM5のドレインにドレインが接続され、ゲートがCLKX2端子に接続されたPMOSトランジスタPM1と、

ソースが電源VDDに接続され、NMOSトランジスタNM5のドレインにドレインが接続され、ゲートがCOP端子に接続されたPMOSトランジスタPM2と、

ソースが電源VDDに接続され、NMOSトランジスタNM6のドレインにドレインが接続され、ゲートがCON端子に接続されたPMOSトランジスタPM3と、

ソースが電源VDDに接続され、NMOSトランジスタNM6のドレインにドレインが接続され、ゲートがCLKX2端子に接続されたPMOSトランジスタPM4と、を備えている。

【0054】

CLKX2端子がLowのとき(コンパレータ10のリセット時)、PMOSトランジスタPM1、PM4がオン(導通)し、NMOSトランジスタNM5、NM6はオフ(非導通)状態であるため、COP、CON端子は、電源電圧(VDD:Highレベル)に充電される。CON、COP端子がともに電源電圧VDDに充電されると、PMOSトランジスタPM2、PM3はオフ状態となる。なお、NMOSトランジスタNM5、NM6はオフ(非導通)状態であるため、電源VDDとGND間の電流パスはカットオフ状態とされる。

【0055】

この状態から、CLKX2端子がHighとなると、PMOSトランジスタPM1、PM4がオフ(非導通)となり、NMOSトランジスタNM5、NM6がオン(導通)する。この時点で、COP、CONがHighであることから、NMOSトランジスタNM3、NM4がオン(導通)し、PMOSトランジスタPM2、PM3はオフ(非導通)となる。このとき、INP、INN端子の電圧レベルが、INP<INNの場合、INN端子にゲートが接続されたNMOSトランジスタNM2がオンし、オン状態のNMOSトランジスタMN4、MN6を介してCOP端子の電荷をGNDに放電し、COP端子はHighからLowに立ち下がる。COP端子がLow側に立ち下がると、COP端子にゲートが接続されたNMOSトランジスタNM3がオフし、CON端子と、NMOSトランジスタNM5、NM3、NM1、GND間のパスはカットオフされる。このため、INPの電圧が、NMOSトランジスタNM1の閾値電圧以上であり、INNにゲートが接続されたNMOSトランジスタNM1がオン状態であっても、CON端子はHighレベルに保持される。また、COP端子のLowに応答して、PMOSトランジスタPM2はオンし、CON端子をHigh(電源電圧VDD)に充電する。そして、CON端子がHighに保持されるため、NMOSトランジスタNM4はオン状態に保持される。ゲートをドレイン(COP、CON端子)に交差接続したPMOSトランジスタPM2、PM3と、ゲートをCOP、CON端子に交差接続したNMOSトランジスタNM3、NM4とは、比較動作時(CLKX2がHighのとき)、NMOSトランジスタNM1、NM2によるINP、INN端子の比較結果を差動増幅して保持する差動ラッチとして機能する。

【0056】

一方、INP、INN端子の電圧レベルがINP>INNの場合、INP端子にゲートが接続されたNMOSトランジスタNM1がオンし、オン状態のNMOSトランジスタMN3、MN5を介してCON端子の電荷をGNDに放電し、CON端子はHighからLowに立ち下がる。CON端子がLow側に立ち下がると、NMOSトランジスタNM4がオフし、COP端子と、NMOSトランジスタNM6、NM5、NM2、GND間のパスがカットオフされる。このため、INNの電圧がNMOSトランジスタNM2の閾値電圧以上であり、INNにゲートが接続されたNMOSトランジスタNM2がオン状態であっても、COP端子はHighレベルに保持される。また、CON端子のLowに応答してPMOSトランジスタPM3はオンし、COP端子をHigh(電源電圧)に充電する。そして、COP端子がHighに保持されるため、NMOSトランジスタNM3はオン状態に保持される。

【0057】

<実施例6>

実施例6では、前記実施形態及び実施例のコンパレータ10を備えた半導体装置を開示する。図10(A)、(B)は、クロック周波数を2逓倍する2逓倍器20を搭載する半導体チップを説明する図である。図10(A)の例では、発振回路4は、クロック信号CLKを出力し、2逓倍器(X2)20で2逓倍したクロック信号がアナログデジタルコンバータ(ADC)3、コンパレータ10に供給されている。図10(B)では、発振回路4は、クロック信号CLKを出力し、第1、第2の2逓倍器(X2)20で2逓倍したクロック信号がそれぞれアナログデジタルコンバータ(ADC)3、コンパレータ10に供給されている。

【0058】

図10において、コンパレータ10に2逓倍クロック信号を供給する2逓倍器(X2)20として、図12、図13に示した関連技術の2逓倍器30、20を用いた場合、図15を参照して説明した上記問題点を有している。一方、図10において、コンパレータ10に2逓倍クロック信号を供給する2逓倍器(X2)20を、例えば前記した図3の構成とし、コンパレータ10の出力をモニタする出力モニタ&トリガ発生回路を追加することで、前記実施例で説明した作用効果を奏することができる。なお、図10では、半導体チップ1は、発振回路4を搭載しているが、これは外部クロック信号を入力し内部クロック信号CLKを生成するクロック生成回路であってもよい。図10では、CPU(Central Processing Unit)2、センサ5、ADC3等を同一チップ上に備えているが、本発明はかかる構成に制限されるものでないことは勿論である。また、半導体装置としては、ADC3、CPU2等を同一チップ上で実装する構成に限定されるものでなく、基板等に実装した構成としてもよい。

【0059】

図11(A)は、発振回路4からのクロック信号CLKを2逓倍器20で2逓倍したクロック信号CLKX2を入力するコンパレータ10を備えたADC3の一例を例示した図である。特に制限されないが、ADC3は、例えば逐次比較型のADCからなり、入力信号をサンプルしたアナログ電圧を比較電圧とコンパレータ10で比較し、比較結果の大小に応じて、次の探索範囲を絞り込み、次の比較電圧を生成する逐次比較アルゴリズムにより、デジタル信号に変換する。

【0060】

図11(B)は、発振回路4からのクロック信号CLKを2逓倍器20で2逓倍したクロック信号CLKX2を入力するコンパレータ10を例示した図である。コンパレータ10に2逓倍クロック信号を供給する2逓倍器(X2)20を、図3の構成とし、コンパレータ10の出力をモニタする出力モニタ&トリガ発生回路を追加することで、前記実施例で説明した作用効果を奏することができる。

【0061】

なお、図10、図11等には、コンパレータを備えた半導体チップ、コンパレータを備えたADC、コンパレータ単体を例示したが、本発明はかかる構成に制限されるものでないことは勿論である。

【0062】

上記非特許文献の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0063】

1 半導体チップ

2 CPU

3 ADC

4 発振回路

5 センサ

10 コンパレータ

11 SRラッチ

12 出力モニタ回路

13 出力モニタ及びトリガ発生回路(NAND回路)

14 トリガ発生回路

15 遅延回路

16 可変遅延器(D型ラッチ)

17 デューティ補正回路

18 位相比較器(排他的論理和回路)

19 遅延(Delay)回路

20、20’ 2逓倍器

30 2逓倍PLL

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、例えば2逓倍クロック信号を入力するコンパレータに適用して好適な構成の半導体装置に関する。

【背景技術】

【0002】

クロック信号(CLK)の周波数を2逓倍した2逓倍クロック信号(CLKX2)に基づき比較動作を行うコンパレータが用いられている(図11(B)参照)。このコンパレータは、例えばアナログ信号をデジタル信号に変換するアナログデジタル変換器(ADC)において2つの信号の電圧レベルを比較するコンパレータとして用いられる(図11(A)参照)。

【0003】

図12は、コンパレータに2逓倍クロック信号を供給する2逓倍器(Frequecny Doubler)として、PLL(Phase Locked Loop:位相同期ループ)を用いた典型的な回路構成の一例を示す図である。2逓倍PLL30は、発振回路(図11(B)の4)等のクロック生成回路から供給されるクロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成し、コンパレータ10に供給する。特に制限されないが、コンパレータ10は、第1、第2の入力信号INP、INNを入力し、2逓倍クロック信号CLKX2がHigh(例えば電源電位)のとき、第1、第2の入力信号INP、INNの電圧を比較し、第1、第2の出力COP、CONに比較結果を出力し、2逓倍クロック信号CLKX2がLow(例えばグランド電位)のとき、第1、第2の出力COP、CONはともにHighレベル(電源電圧)にリセットされる。

【0004】

図12の例では、SRラッチ(SR Latch)11は、コンパレータ10の第1、第2の出力COP、CONをセット入力端子 ̄S、リセット入力端子 ̄Rに受けて、相補の出力Q、QBを出力する。SRラッチ11は、( ̄S、 ̄R)=(Low、High)のとき、(Q、QB)=(High、Low)にセットされ、( ̄S、 ̄R)=(High、Low)のとき、(Q、QB)=(Low、High)にリセットされ、( ̄S、 ̄R)=(High、High)のとき、(Q、QB)は前の状態を保持する。なお、図12において、端子S、Rの上のバー( ̄)は該端子に入力される信号がLowレベルでアクティブであることを表している。コンパレータ10の出力(COP、CON)=(Low、High)に応答して、SRラッチ11の出力は(Q、QB)=(High、Low)にセットされ、(COP、CON)=(High、Low)に応答して、(Q、QB)=(Low、High)にリセットされ、(COP、CON)=(High、High)のときは、(Q、QB)は前の状態を保持する。以下、他の図面のSRラッチ11も、図12のSRラッチ11と同様の構成とされる。

【0005】

なお、図12では、2逓倍PLL30の内部構成は図示されていないが、PLLは、よく知られているように、例えば制御電圧で発振周波数を可変させるVCO(Voltage Controlled Oscillator:電圧制御発振器)と、VCOの発振信号を分周する分周器(Divider)と、分周器の出力と入力クロック信号の位相差を検出する位相比較器(PD:Phase Detector又はPFD:Phase Frequency Detector)と、位相比較器の出力を受け容量を充電、放電するチャージポンプ(CP:Charge Pump)と、チャージポンプの電圧を平滑化するループフィルタ(LPF: Loop Filter)を備え、ループフィルタの出力電圧が制御電圧としてVCOに供給される。2逓倍PLL30では、VCOの発振信号を分周する分周器として、例えば第1の分周器で2逓倍クロック信号CLKX2を生成し、2逓倍クロック信号CLKX2をさらに2分周してクロック信号CLKと同一周波数のクロック信号を生成し位相比較器に入力する。2逓倍PLL30は、入力クロック信号CLKに位相同期した逓倍クロック信号CLKX2を生成する。なお、PLLは、完全デジタルPLL(ADPLL:All Digital PLL)であってもよい。

【0006】

2逓倍器としてPLLを用いた図12の構成の場合、回路面積が増大し電力が増加する。

【0007】

より簡素な回路構成として、時間遅延技術(Time−Delay Technique)を用いた2逓倍器が知られている。図13は、時間遅延技術(Time−Delay Technique)を用いた2逓倍器の典型的な回路構成を示す図である。Time−Delay Techniqueの詳細は、例えば非特許文献1が参照される。

【0008】

図13を参照すると、2逓倍器20’は、遅延τがT/4(ただし、TはCLKの周期)の遅延回路19(Delay)と、位相比較器として機能する排他的論理和(Exclusive OR)回路18とを備えている。なお、図13の2逓倍器20’は、非特許文献1のFigure.1に基づき、本願で新たに作成したものである。図13において、コンパレータ10、SRラッチ11は、図12と同一であるため、説明は省略する。

【0009】

2逓倍器20’において、遅延回路19は、入力クロック信号CLK(デューティ=50%とする)をτ=T/4遅延させたクロック信号(遅延クロック信号)CLKDを生成する。遅延クロック信号CLKDと入力クロック信号CLKは排他的論理和回路18に入力され、排他的論理和回路18から2逓倍クロック信号CLKX2が出力される。すなわち、排他的論理和回路18は、入力クロック信号CLKと遅延クロック信号CLKDが同一論理レベル(ともにHighレベルであるか、又はともにLowレベル)のとき、Lowを出力し、入力クロック信号CLKと遅延クロック信号CLKDが互いに異なる論理レベルのとき、Highを出力する。なお、非特許文献1のFigure.1では、遅延回路は、積分器とコンパレータを備え、積分器は、矩形波である入力クロック信号CLKを積分して三角波を出力し、コンパレータは、積分器からの三角波を基準電圧と比較しCLKからT/4遅延させた矩形波を出力する構成とされている。図13において、遅延回路19は、積分器とコンパレータの構成に制限されるものでなく、例えばCMOSインバータを偶数段接続した構成としてもよい。

【0010】

図14は、図13の回路において、入力クロック信号CLKと、遅延回路10の出力信号(遅延クロック信号)CLKDと、排他的論理和回路18の出力信号である2逓倍クロック信号CLKX2のそれぞれのタイミング波形を示す図である。ここでは、クロック信号CLKの周期をTとし、そのデューティ=50%であるものとし、遅延回路19の遅延τ=T/4とする。入力クロック信号CLKを遅延回路19でτ=T/4遅延させた遅延クロック信号CLKDと、入力クロック信号CLKとを排他的論理和回路18で比較することで、遅延クロック信号CLKDと入力クロック信号CLKの論理レベルの異なるときに、Highとなる2逓倍クロック信号CLKX2が生成される。図14に示すように、入力クロック信号CLKの立ち上がりエッジと立ち下がりエッジにそれぞれ応答してHighに立ち上がるパルス(パルス幅=T/4)、周期=T/2の2逓倍クロック信号CLKX2が生成される。図14では、2逓倍クロック信号CLKX2のデューティは50%である。

【0011】

図13の2逓倍器20’は、遅延回路19と1つの論理ゲート(Exclusive OR)で構成され、回路構成が簡素化されており、図12の2逓倍PLL30を備えた構成と比較して、回路面積の削減、消費電力の低減が可能である。

【先行技術文献】

【非特許文献】

【0012】

【非特許文献1】Brad R. Jackson and Carlos E. Saavedra, "An L-Band CMOS Frequency Doubler using a Time-Delay Technique" Silicon Monolithic Integrated Circuits in RF Systems, Jan. 2006

【発明の概要】

【発明が解決しようとする課題】

【0013】

以下に、本発明者によって為された関連技術の分析を示す。

【0014】

前述したように、2逓倍器として、図12に示した2逓倍PLLを備えた構成は、入力クロック信号CLKに位相同期した2逓倍クロック信号CLKX2を生成することができるが、PLL自体の構成が、コンパレータ等と比べて大きく且つ複雑であることから、面積及び電力がともに増加する、という問題点を有している。

【0015】

一方、図13の2逓倍器20’の場合、遅延回路19の遅延時間τは、製造プロセスや、電源電圧変動、温度等によってばらつく。

【0016】

図15は、図13の構成のタイミング動作上の問題点を説明するための図である。図15(A)、図15(B)には、図13の入力クロック信号CLK、遅延クロック信号CLKD、2逓倍クロック信号CLKX2のタイミング波形が示されており、図15(A)では、さらに、コンパレータ10の状態(CMP状態)が示されている。コンパレータ10の状態(CMP状態)の「動作」は、コンパレータ10がINPとINNの電圧を比較する動作状態にあることを表しており、CMP状態の「停止」は、コンパレータ10がINPとINNの電圧比較動作を停止している状態を表している。コンパレータ10は、2逓倍クロック信号CLKX2がHighとなってから、第1、第2の出力COP、CONの値(比較結果)を確定するまでに時間CMP_Delayを要する。

【0017】

図15(A)は、図13の構成の第1の問題点を説明する図である。第1の問題点は、遅延回路19の遅延τがコンパレータ10の判定動作時間よりも小さくなる場合に生じる。図15(A)の場合、遅延回路19の遅延τ’はτ=T/4(Tはクロック信号CLKの1周期)よりも短く、コンパレータ10の比較動作の確定に必要な時間区間(CMP_Delay)よりも短い。すなわち、遅延クロック信号CLKDは、入力クロック信号CLKのLowからHighへの立ち上がりから遅延τ’で、LowからHighに立ち上がる。入力クロック信号CLKの立ち上がりでHighとなった2逓倍クロック信号CLKX2は、遅延クロック信号CLKDのLowからHighへの立ち上がりエッジに応答して、図15(A)の破線のタイミングでHighからLowに立ち下がる。2逓倍クロック信号CLKX2のHighパルス期間(コンパレータの動作期間)は、コンパレータ10の比較動作の確定に必要な時間区間(=CMP_Delay)よりも短い。この結果、図15(A)の「CMP状態」に示すように、コンパレータ10の比較結果が確定する前に、CLKDがHighとなり、CLKX2がLowとなるため、コンパレータ10は比較動作を停止してしまう。この結果、コンパレータ10の第1、第2の出力COP、CONには正しい比較結果が出力されない。

【0018】

図15(B)は、図13の構成の第2の問題点を説明する図である。図13の遅延回路19の遅延τ’が、入力クロック信号CLKの半周期(=T/2)よりも大きくなると、2逓倍クロック信号CLKX2は、コンパレータ10が正しく動作するために必要な2逓倍波形とはならない。図15(B)では、遅延クロック信号CLKDは入力クロック信号CLKがLowからHighに立ち上がり、その後、HighからLowに立ち下ったのちに、LowからHighに立ち上がっている(τ’>T/2)。このため、2逓倍クロック信号CLKX2は、入力クロック信号CLKの立ち上がりでHighとなり、T/2後の入力クロック信号CLKの立ち下がりでLowとなり、時間区間(τ’−T/2)ののち、遅延クロック信号CLKDの立ち上がりでHighとなり、次サイクルの入力クロック信号CLKがLowからHighに立ち上がるまでの期間Highとなる。このCLKX2の波形は、入力クロック信号CLKの1周期(=T)内において、連続する2つのHighパルスのうち1発目のHighパルスのパルス幅がT/2となり、時間(τ’−T/2)の間Lowとなり、次のHighパルスは、次サイクルの入力クロック信号CLKの立ち上がりまでの時間区間(T−τ’)Highとなる。図15(B)のCLKX2の波形では、連続する2つのHighパルスの間のLow期間が短いため、コンパレータ10のリセット動作に必要な時間が確保できない場合がある。

【0019】

したがって、本発明は、遅延回路の遅延時間のばらつき等に起因して生じる上記問題点に鑑みて創案されたものであって、その目的は、回路構成の簡素化を図るとともに、上記問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供することにある。

【課題を解決するための手段】

【0020】

上記課題を解決するため、概略以下の構成の半導体装置が提供される(ただし、以下に制限されるものでない)。

【0021】

本発明によれば、入力クロック信号を第1の遅延回路で遅延させた遅延クロック信号と、前記入力クロック信号とを位相比較器に入力し、前記入力クロック信号の周波数を2逓倍した2逓倍クロック信号を生成する2逓倍回路と、

前記2逓倍回路からの前記2逓倍クロック信号を受け、前記2逓倍クロック信号が第1の論理レベルのとき、第1、第2の入力信号の大小の比較動作を行い、前記2逓倍クロック信号が第2の論理レベルのとき、比較動作を停止するコンパレータと、

前記コンパレータの出力をモニタし、前記コンパレータが比較動作を完了したことを検出した時点でトリガ信号を出力する第1の回路と、を備え、前記第1の遅延回路は、前記入力クロック信号を、少なくとも前記第1の回路から前記トリガ信号が出力される時点まで遅延させ、前記遅延クロック信号として出力する可変遅延器を備えた半導体装置が提供される。

【発明の効果】

【0022】

本発明によれば、回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる上記問題点を解消し、コンパレータの動作を保証することができる。

【図面の簡単な説明】

【0023】

【図1】本発明の一実施形態の構成を示す図である。

【図2】本発明の一実施形態の動作を説明するためのタイミング図である。

【図3】本発明の実施例1の構成を示す図である。

【図4】本発明の実施例1の動作を説明するためのタイミング図である。

【図5】本発明の実施例2の構成を示す図である。

【図6】実施例1(2)において、クロック信号CLKにDuty誤差が生じたときのCLKX2の波形を示す図である。

【図7】本発明の実施例3の構成を示す図である。

【図8】本発明の実施例4の構成を示す図である。

【図9】コンパレータの構成例を示す図である。

【図10】周波数2逓倍器を搭載する半導体チップの一例を示す図である。

【図11】(A)はADCのコンパレータクロックに周波数2逓倍器を使用した回路を示す図である。(B)はコンパレータ単体のクロックに周波数2逓倍器を使用した回路を示す。

【図12】コンパレータクロックに2逓倍器としてPLL2逓倍器を使用した関連技術を示す図である。

【図13】コンパレータクロックに2逓倍器としてTime−Delay Techniqueの2逓倍器を使用した関連技術を示す図である。

【図14】図13の2逓倍器の動作を説明するためのタイミング図である。

【図15】(A)、(B)は図13の2逓倍器の問題点を説明するためのタイミング図である。

【発明を実施するための形態】

【0024】

本発明の好ましい形態の1つによれば、入力クロック信号(CLK)を第1の遅延回路(例えば図1の可変遅延器16)で遅延させた遅延クロック信号(CLKD)と、入力クロック信号(CLK)の位相を位相比較器(例えば図1の18)で比較することにより、入力クロック信号(CLK)の周波数を2逓倍した2逓倍クロック信号(CLKX2)を生成する2逓倍回路(例えば図1の2逓倍器20)と、2逓倍回路(図1の20)からの2逓倍クロック信号(CLKX2)を受け、2逓倍クロック信号(CLKX2)が第1の論理レベル(例えばHighレベル)のとき、比較動作を行い、2逓倍クロック信号(CLKX2)が第2の論理レベル(例えばLowレベル)のとき、比較動作を停止するコンパレータ(10)と、前記コンパレータ(10)の出力をモニタし、前記コンパレータ(10)の比較結果を出力したことが確認された時点で、トリガ信号(DLCLK)を生成する回路(例えば図1の12、14、あるいは図3の13)を備えている。第1の遅延回路(図1の16)は、少なくとも、第1の回路(図1の12、14、あるいは図3の13)からトリガ信号(DLCLK)が出力される時点まで、前記入力クロック信号(CLK)を可変に遅延させた信号を前記遅延クロック信号(CLKD)として出力する。位相比較器(図1の18)は、遅延クロック信号(CLKD)と入力クロック信号(CLK)が互いに異なる論理レベルのとき、第1の論理レベル(例えばHighレベル)を出力し、遅延クロック信号(CLKD)と入力クロック信号(CLK)が同一の論理レベルのとき、第2の論理レベル(例えばLowレベル)を出力する。

【0025】

2逓倍クロック信号(CLLX2)は、入力クロック信号(CLK)の第2の論理レベル(Lowレベル)から第1の論理レベル(Highレベル)への遷移に応答して第1の論理レベル(Highレベル)となり、入力クロック信号(CLK)を、トリガ信号(DLCLK)が出力される時点まで遅延させた遅延クロック信号(CLKD)の第1の論理レベル(Highレベル)への遷移に応答して、第2の論理レベル(Lowレベル)となる。このため、コンパレータ(10)は、比較動作が確定(完了)したのちに、比較動作を停止する。このため、製造プロセスによるばらつき、電源電圧変動、温度変化等による遅延回路の遅延変動により、逓倍クロック信号の第1の論理レベルの期間が狭まり、コンパレータ(10)が比較動作を確定する前に停止してしまうという、図13の回路に関する第1の問題点を解消している。

【0026】

また、2逓倍クロック信号(CLLX2)は入力クロック信号(CLK)の第2の論理レベルから第1の論理レベルへの遷移で第1の論理レベルに遷移し、コンパレータ(10)での比較動作が確定した時点で第2の論理レベルに遷移させるように制御するため、図13の回路に関する上記第2の問題点を解消している。図13の回路では、2逓倍クロック信号(CLLX2)は、入力クロック信号(CLK)の第2の論理レベル(例えばLow)から第1の論理レベル(例えばHigh)への遷移で第1の論理レベルに遷移し、遅延回路(19)の遅延τの後に第2の論理レベルとなる。一方、図13の回路では、2逓倍クロック信号(CLLX2)の第1の論理レベル(Highレベル)から第2の論理レベル(Lowレベル)への遷移はコンパレータ(10)での比較動作が確定する時点とは無関係とされる。以下実施形態に即して説明する。

【0027】

<実施形態>

図1は、本発明の一実施形態の構成を示す図である。図1を参照すると、本実施形態においては、コンパレータ10と、出力モニタ回路12と、トリガ発生回路14と、可変遅延器16と、位相比較器18を備えている。可変遅延器16と、位相比較器18は2逓倍器20を構成している。コンパレータ10は、図12、図13を参照して説明したものと同一の構成とされ、2逓倍クロック信号CLKX2がHighのとき、入力信号INP、INNの電圧比較を行い、2逓倍クロック信号CLKX2がHighからLowになると、比較動作を停止する。特に制限されないが、2逓倍クロック信号CLKX2がLowの期間、出力COP/NともHighレベルにプリチャージされる。

【0028】

出力モニタ回路12と、トリガ発生回路14は、コンパレータ10の出力COP/Nをモニタリングし、コンパレータ10が比較結果を出したことを検出すると、トリガ信号DLCLKを出力する。出力モニタ回路12とトリガ発生回路14を1つの回路ブロック又は論理ゲートで構成するようにしてもよいことは勿論である。

【0029】

可変遅延器16は、入力クロック信号CLKを入力し、入力クロック信号CLKの立ち上がりエッジをトリガ信号DLCLKの出力タイミング(DLCLKのLowからHighへの立ち上がりのタイミング)まで遅延させた遅延クロック信号CLKDを出力する。

【0030】

位相比較器18は、入力クロック信号CLKと遅延クロック信号CLKDの位相を比較し、位相差(一方がHigh、他方がLowのとき、その位相差)に応じたパルス幅のHighパルスを出力する。

【0031】

図2は、図1の回路の動作を説明するタイミング図である。図2は、図1の入力クロック信号CLK、2逓倍クロック信号CLKX2、コンパレータ出力COP/Nの一方COP、トリガ信号DLCLK、遅延クロック信号CLKDのタイミング波形の一例が示されている。COPの波形において、枠で囲んだ区間は、コンパレータの判定区間を模式的に表している。図1、図2を参照して、本実施形態の動作を説明する。

【0032】

まず、入力クロック信号CLKがLowからHighに立ち上がった時、遅延クロック信号CLKDがLowの場合、位相誤差があるため、位相比較器18の出力である2逓倍クロック信号CLKX2はHighとなる。

【0033】

2逓倍クロック信号CLKX2のHighを受け、コンパレータ10はINPとINNの電圧の比較動作を開始する。

【0034】

コンパレータ10の出力をモニタする出力モニタ回路12とトリガ発生回路14は、コンパレータ10の比較結果の出力を検出すると、トリガ信号DLCLKを活性状態(例えばHIghレベル)とする。

【0035】

可変遅延器16は、トリガ信号DLCLKのLowからHighへの立ち上がりを受けて、入力クロック信号CLKのエッジ(例えば立ち上がりエッジ)をトリガ信号DLCLKの立ち上がりエッジまで遅延させる。トリガ信号DLCLKの立ち上がりエッジに応答して、可変遅延器16から出力される遅延クロック信号CLKDはHighとなる。

【0036】

遅延クロック信号CLKDがLowからHighになると、入力ロック信号CLKと遅延クロック信号CLKDがともにHighであることから、これらの信号に位相差はなくなり、位相比較器18はその出力である2逓倍クロック信号CLKX2をLowとする。

【0037】

つづいて、入力ロック信号CLKがHighからLowに立ち下がると、遅延クロック信号CLKDはHighであるため、位相比較器18から出力される2逓倍クロック信号CLKX2はHighとなる。2逓倍クロック信号CLKX2のHighを受け、コンパレータ10はINPとINNの電圧の比較動作を開始する。この後の動作は、前述の動作を繰り返す。

【0038】

本実施形態によれば、コンパレータ10での比較動作の終了(比較結果の確定)の検出結果に基づき、トリガ信号DLCLKを活性化し、トリガ信号DLCLKの活性化のタイミングに対応して、遅延クロック信号CLKDの立ち上がりエッジを生成し、位相比較器18で遅延クロック信号CLKDと入力クロック信号CLKと位相比較して2逓倍クロック信号CLKX2を生成している。このため、図15(A)、(B)で説明した問題点を解消し、コンパレータ10の動作を保証している。

【0039】

<実施例1>

図3は、実施例1として、図1の具体的な構成例を示す図である。図3を参照すると、コンパレータ10と、SRラッチ11と、NAND回路(否定論理積回路)からなる出力モニタ&トリガ発生回路13と、可変遅延器(D Latch)16と、位相比較器(排他的論理和回路)18とからなる。実施例1の出力モニタ&トリガ発生回路(NAND回路)13は、図1の出力モニタ回路12とトリガ発生回路14に対応し、図1の出力モニタ回路12とトリガ発生回路14を1つの回路にまとめたものである。図1の可変遅延器16は、入力クロック信号CLKをデータ端子に入力し、トリガ信号をクロック端子に入力し、クロック端子の立ち上がりエッジでデータ端子の信号値をキャプチャ出力するエッジトリガ型のD型ラッチ(D Latch)で構成される。D型ラッチは、エッジトリガ型のD型フリップフロップで構成してもよい。位相比較器18は、図13と同様、排他的論理和回路(EXOR)で構成される。以下では、説明の簡単のため、可変遅延器を構成するD型ラッチを参照符号16、位相比較器を構成する排他的論理和回路を参照符号18で参照する場合もある。図4は、図3の動作例を説明するタイミング波形図である。

【0040】

図3と図4を参照して、コンパレータ10に入力される第1、第2の入力信号INP、INNの電圧レベルがINP<INNの場合の動作を説明する。

【0041】

コンパレータ10は、2逓倍クロック信号CLKX2がLowの期間でリセットがかかり、第1、第2の出力COP、CONをともにHighとする。

【0042】

遅延クロック信号CLKDがLowレベルのときに、入力クロック信号CLKがLowからHighに立ち上がると、位相比較器18の出力である2逓倍クロック信号CLKX2は、入力クロック信号CLKのHighへの立ち上がりに応答してHighに立ち上がる。

【0043】

2逓倍クロック信号CLKX2がHighとなると、コンパレータ10は第1、第2の入力信号INP、INNの電圧レベルを比較する比較動作を行う。

【0044】

コンパレータ10の比較判定に要する時間(図15(A)のCMP_Delay)に従い、2逓倍クロック信号CLKX2がLowからHighに立ち上がってからしばらくして、INP<INNに対応して、第1の出力COPがHighからLowとなる。第2の出力CONはHighのまま変化せず比較動作が終了する。なお、INP>INNの場合、2逓倍クロック信号CLKX2がLowからHighに立ち上がってからしばらくして、第2の出力CONがHighからLowとなり、第1の出力COPはHighのまま変化せず比較動作が終了する。

【0045】

INP<INNに対応して、コンパレータ10の第1の出力COPがHighからLowとなり、第2の出力CONはHighのままであるため、第1、第2の出力COP、CONを入力するNAND回路13の出力信号であるトリガ信号DLCLKは、LowからHighとなる。D型ラッチ16は、トリガ信号DLCLKのLowからHighへの立ち上がりエッジに応答して、入力クロック信号CLK(その時点でHighレベル)をキャプチャし、Highを出力する。すなわち、D型ラッチ16の出力信号である遅延クロック信号CLKDはHighとなる。

【0046】

遅延クロック信号CLKDがLowからHighに変化した時点で、入力クロック信号CLKはHighであるため、位相比較器18の入力はともにHighとなり、位相比較器18から出力される2逓倍クロック信号CLKX2はHighからLowに変化する。2逓倍クロック信号CLKX2のLowを受けて、コンパレータ10にリセットがかかり、コンパレータ10の第1の出力COPはLowからHighとなる。第2の出力CONはHighを保つ。

【0047】

実施例1によれば、コンパレータ10の第1、第2の出力COP、CONの値の変化時点(比較結果確定時点)まで、入力クロック信号CLKの立ち上がりエッジを遅延させて遅延クロック信号CLKDの立ち上がりエッジを生成し、該入力クロック信号CLKと該遅延クロック信号CLKDに基づき逓倍クロック信号CLKX2を生成しているため、前記関連技術の前記問題点を解消している。

【0048】

<実施例2>

次に、実施例2を説明する。図5は、実施例2の構成を示す図である。図5を参照すると、実施例2は、図3の実施例1の構成において、可変遅延器(D型ラッチ)16の出力と位相比較器18の入力の間のパスに、遅延回路15が挿入されている。図3において、コンパレータ10の第1、第2の出力COP、CONから2逓倍クロック信号CLKX2までの遅延時間が、仮に0sec(すなわち、遅延無し)と仮定すると、コンパレータ10の比較動作の終了過程時に、トリガ信号DLCLKがHighに立ち上がり、直ちに2逓倍クロック信号CLKX2がLowに立ち下がり、コンパレータ10にリセットをかけ、第1、第2の出力COP、CONをHighにリセットしてしまう可能性がある。この場合、コンパレータ10の第1、第2の出力COP、CONは、正しく後段のSRラッチ11等に伝達されない。

【0049】

本実施例では、図5に示すように、可変遅延器(D型ラッチ)16と位相比較器18の間に遅延回路15を挿入し、コンパレータ10の比較動作の終了過程に、直ちに2逓倍クロック信号CLKX2がLowに立ち下がって、コンパレータ10にリセットをかける事態の発生を回避している。遅延回路15は、CMOSインバータを複数段接続する構成としてもよいし、あるいは配線遅延等を利用した構成としてもよい。本実施例によれば、コンパレータ10の比較動作の終了過程時に、コンパレータ10にリセットをかけ、第1、第2の出力COP、CONをHighにリセットしてしまうことを確実に回避することができる。

【0050】

<実施例3>

次に、実施例3を説明する。図6は、入力クロック信号CLKのデューティに誤差が生じた場合における、図3の前記実施例1の2逓倍クロック信号CLKX2の波形の一例を示す図である。前記実施例1において、2逓倍器20は、入力クロック信号CLKの立ち上がりと立ち下がりエッジを使用して、2逓倍クロック信号CLKX2を生成している。このため、入力クロック信号CLKにデューティ誤差が生じると、入力クロック信号CLKのHigh期間とLow期間の差により、2逓倍クロック信号CLKX2の周波数にずれが生じる。例えば図6に示すように、入力クロック信号CLKのHigh期間が短いと、入力クロック信号CLKの立ち上がりと立ち下がりに応答して生成される2逓倍クロック信号CLKX2の2発のHighパルスの時間間隔が狭まり、次のCLKの立ち上がりに応答して生成される2逓倍クロック信号CLKX2のHighパルスとの間の時間間隔は広がる。

【0051】

図7は、実施例3の構成を示す図である。実施例3では、この問題を解決するため、図7に示すように、図3の構成において、入力クロック信号CLKを入力しデューティを補正するデューティ補正回路17を備え、デューティ補正回路17の出力を、位相比較器18とD型ラッチ16に入力している。デューティ補正回路17において、入力クロック信号CLKのデューティが50%(High期間とLow期間が等しい)となるように補正した信号を位相比較器18に入力し、デューティを補正した信号の立ち上がりエッジと立ち下がりエッジに応答して、2逓倍クロック信号CLKX2の立ち上がりエッジを生成している。このため、図6のCLKX2のような波形となることは回避される。デューティ補正回路17は、入力クロック信号CLKのデューティを例えば50%に近づくように補正するものであり、任意の公知の構成を用いることができる。本実施例によれば、入力クロック信号CLKのデューティを例えば50%に近づくように補正するため、入力クロック信号CLKにデューティ誤差が生じた場合でも、図6のような2逓倍クロック信号CLKX2が出力されることを回避することができる。

【0052】

<実施例4>

図8は、実施例4の構成を示す図である。図8に示すように、本実施例は、図3の実施例1の構成に、前記実施例2の遅延回路15と、前記実施例3のデューティ補正回路17を備えている。実施例4は、前記実施例2と前記実施例3の作用効果を併せ持つ。

【0053】

<実施例5>

図9は、前記実施形態及び各実施例で説明したコンパレータ10の構成の一例を示す図である。なお、コンパレータ10の構成は図9の構成に限定されるものでないことは勿論である。図9を参照すると、

ソースがGND(あるいはVSS:0V)に接続され、ゲートがINP端子に接続されたNMOSトランジスタNM1と、

ソースがGND(あるいはVSS)に接続され、ゲートがINN端子に接続されたNMOSトランジスタNM2と、

NMOSトランジスタNM1のドレインにソースが接続され、ゲートがCOP端子に接続されたNMOSトランジスタNM3と、

NMOSトランジスタNM2のドレインにソースが接続され、ゲートがCON端子に接続されたNMOSトランジスタNM4と、

NMOSトランジスタNM3のドレインにソースが接続され、ゲートがCLKX2端子に接続されたNMOSトランジスタNM5と、

NMOSトランジスタNM4のドレインにソースが接続され、ゲートがCLKX2端子に接続されたNMOSトランジスタNM6と、

ソースが電源VDDに接続され、NMOSトランジスタNM5のドレインにドレインが接続され、ゲートがCLKX2端子に接続されたPMOSトランジスタPM1と、

ソースが電源VDDに接続され、NMOSトランジスタNM5のドレインにドレインが接続され、ゲートがCOP端子に接続されたPMOSトランジスタPM2と、

ソースが電源VDDに接続され、NMOSトランジスタNM6のドレインにドレインが接続され、ゲートがCON端子に接続されたPMOSトランジスタPM3と、

ソースが電源VDDに接続され、NMOSトランジスタNM6のドレインにドレインが接続され、ゲートがCLKX2端子に接続されたPMOSトランジスタPM4と、を備えている。

【0054】

CLKX2端子がLowのとき(コンパレータ10のリセット時)、PMOSトランジスタPM1、PM4がオン(導通)し、NMOSトランジスタNM5、NM6はオフ(非導通)状態であるため、COP、CON端子は、電源電圧(VDD:Highレベル)に充電される。CON、COP端子がともに電源電圧VDDに充電されると、PMOSトランジスタPM2、PM3はオフ状態となる。なお、NMOSトランジスタNM5、NM6はオフ(非導通)状態であるため、電源VDDとGND間の電流パスはカットオフ状態とされる。

【0055】

この状態から、CLKX2端子がHighとなると、PMOSトランジスタPM1、PM4がオフ(非導通)となり、NMOSトランジスタNM5、NM6がオン(導通)する。この時点で、COP、CONがHighであることから、NMOSトランジスタNM3、NM4がオン(導通)し、PMOSトランジスタPM2、PM3はオフ(非導通)となる。このとき、INP、INN端子の電圧レベルが、INP<INNの場合、INN端子にゲートが接続されたNMOSトランジスタNM2がオンし、オン状態のNMOSトランジスタMN4、MN6を介してCOP端子の電荷をGNDに放電し、COP端子はHighからLowに立ち下がる。COP端子がLow側に立ち下がると、COP端子にゲートが接続されたNMOSトランジスタNM3がオフし、CON端子と、NMOSトランジスタNM5、NM3、NM1、GND間のパスはカットオフされる。このため、INPの電圧が、NMOSトランジスタNM1の閾値電圧以上であり、INNにゲートが接続されたNMOSトランジスタNM1がオン状態であっても、CON端子はHighレベルに保持される。また、COP端子のLowに応答して、PMOSトランジスタPM2はオンし、CON端子をHigh(電源電圧VDD)に充電する。そして、CON端子がHighに保持されるため、NMOSトランジスタNM4はオン状態に保持される。ゲートをドレイン(COP、CON端子)に交差接続したPMOSトランジスタPM2、PM3と、ゲートをCOP、CON端子に交差接続したNMOSトランジスタNM3、NM4とは、比較動作時(CLKX2がHighのとき)、NMOSトランジスタNM1、NM2によるINP、INN端子の比較結果を差動増幅して保持する差動ラッチとして機能する。

【0056】

一方、INP、INN端子の電圧レベルがINP>INNの場合、INP端子にゲートが接続されたNMOSトランジスタNM1がオンし、オン状態のNMOSトランジスタMN3、MN5を介してCON端子の電荷をGNDに放電し、CON端子はHighからLowに立ち下がる。CON端子がLow側に立ち下がると、NMOSトランジスタNM4がオフし、COP端子と、NMOSトランジスタNM6、NM5、NM2、GND間のパスがカットオフされる。このため、INNの電圧がNMOSトランジスタNM2の閾値電圧以上であり、INNにゲートが接続されたNMOSトランジスタNM2がオン状態であっても、COP端子はHighレベルに保持される。また、CON端子のLowに応答してPMOSトランジスタPM3はオンし、COP端子をHigh(電源電圧)に充電する。そして、COP端子がHighに保持されるため、NMOSトランジスタNM3はオン状態に保持される。

【0057】

<実施例6>

実施例6では、前記実施形態及び実施例のコンパレータ10を備えた半導体装置を開示する。図10(A)、(B)は、クロック周波数を2逓倍する2逓倍器20を搭載する半導体チップを説明する図である。図10(A)の例では、発振回路4は、クロック信号CLKを出力し、2逓倍器(X2)20で2逓倍したクロック信号がアナログデジタルコンバータ(ADC)3、コンパレータ10に供給されている。図10(B)では、発振回路4は、クロック信号CLKを出力し、第1、第2の2逓倍器(X2)20で2逓倍したクロック信号がそれぞれアナログデジタルコンバータ(ADC)3、コンパレータ10に供給されている。

【0058】

図10において、コンパレータ10に2逓倍クロック信号を供給する2逓倍器(X2)20として、図12、図13に示した関連技術の2逓倍器30、20を用いた場合、図15を参照して説明した上記問題点を有している。一方、図10において、コンパレータ10に2逓倍クロック信号を供給する2逓倍器(X2)20を、例えば前記した図3の構成とし、コンパレータ10の出力をモニタする出力モニタ&トリガ発生回路を追加することで、前記実施例で説明した作用効果を奏することができる。なお、図10では、半導体チップ1は、発振回路4を搭載しているが、これは外部クロック信号を入力し内部クロック信号CLKを生成するクロック生成回路であってもよい。図10では、CPU(Central Processing Unit)2、センサ5、ADC3等を同一チップ上に備えているが、本発明はかかる構成に制限されるものでないことは勿論である。また、半導体装置としては、ADC3、CPU2等を同一チップ上で実装する構成に限定されるものでなく、基板等に実装した構成としてもよい。

【0059】

図11(A)は、発振回路4からのクロック信号CLKを2逓倍器20で2逓倍したクロック信号CLKX2を入力するコンパレータ10を備えたADC3の一例を例示した図である。特に制限されないが、ADC3は、例えば逐次比較型のADCからなり、入力信号をサンプルしたアナログ電圧を比較電圧とコンパレータ10で比較し、比較結果の大小に応じて、次の探索範囲を絞り込み、次の比較電圧を生成する逐次比較アルゴリズムにより、デジタル信号に変換する。

【0060】

図11(B)は、発振回路4からのクロック信号CLKを2逓倍器20で2逓倍したクロック信号CLKX2を入力するコンパレータ10を例示した図である。コンパレータ10に2逓倍クロック信号を供給する2逓倍器(X2)20を、図3の構成とし、コンパレータ10の出力をモニタする出力モニタ&トリガ発生回路を追加することで、前記実施例で説明した作用効果を奏することができる。

【0061】

なお、図10、図11等には、コンパレータを備えた半導体チップ、コンパレータを備えたADC、コンパレータ単体を例示したが、本発明はかかる構成に制限されるものでないことは勿論である。

【0062】

上記非特許文献の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0063】

1 半導体チップ

2 CPU

3 ADC

4 発振回路

5 センサ

10 コンパレータ

11 SRラッチ

12 出力モニタ回路

13 出力モニタ及びトリガ発生回路(NAND回路)

14 トリガ発生回路

15 遅延回路

16 可変遅延器(D型ラッチ)

17 デューティ補正回路

18 位相比較器(排他的論理和回路)

19 遅延(Delay)回路

20、20’ 2逓倍器

30 2逓倍PLL

【特許請求の範囲】

【請求項1】

入力クロック信号を第1の遅延回路で遅延させた遅延クロック信号と、前記入力クロック信号とを位相比較器に入力し、前記位相比較器から、前記入力クロック信号の周波数を2逓倍した2逓倍クロック信号を出力する2逓倍回路と、

前記2逓倍回路からの前記2逓倍クロック信号を受け、前記2逓倍クロック信号が第1の論理レベルのとき、第1、第2の入力信号の大小の比較動作を行い、前記2逓倍クロック信号が第2の論理レベルのとき、比較動作を停止するコンパレータと、

前記コンパレータの出力をモニタし、前記コンパレータが比較動作を完了したことを検出した時点でトリガ信号を出力する第1の回路と、

を備え、

前記第1の遅延回路は、前記入力クロック信号を、少なくとも前記第1の回路から前記トリガ信号が出力される時点まで遅延させ、前記遅延クロック信号として出力する可変遅延器を備えた、ことを特徴とする半導体装置。

【請求項2】

前記コンパレータが、予め定められた第1の電位に共通に設定された第1、第2の出力のうち、前記第1、第2の入力信号の大小の比較結果に応じて、いずれか一方を、第2の電位に設定し、

前記第1の回路は、前記コンパレータの前記第1、第2の出力を入力し、前記第1、第2の出力の一方が前記第2の電位となったことを検出したときに、出力を活性状態とし前記トリガ信号として出力する回路を備えている、ことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記可変遅延器は、前記トリガ信号の非活性状態から活性状態への遷移に応答して、前記入力クロック信号をキャプチャして出力する回路を備えている、ことを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記第1の遅延回路の出力と前記位相比較器の間にさらに第2の遅延回路を備えている、ことを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記入力クロック信号のデューティを補正するデューティ補正回路をさらに備え、

前記デューティ補正回路で前記入力クロック信号のデューティを補正した信号が、前記第1の遅延回路と前記位相比較器とに入力される、ことを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

入力クロック信号を遅延させた遅延クロック信号を出力する第1の遅延回路と、

前記入力クロック信号と前記遅延クロック信号を入力し、これらの信号が互いに異なる論理レベルの場合、同一の論理レベルの場合に、それぞれ第1、第2の論理レベルを出力する第1の論理ゲートを含む位相比較器と、

を備え、前記位相比較器から、前記入力クロック信号の周波数を2逓倍した2逓倍クロック信号を生成する2逓倍回路と、

前記2逓倍回路からの前記2逓倍クロック信号を受け、前記2逓倍クロック信号が第1の論理レベルのとき、第1、第2の入力信号の大小の比較動作を行い、前記2逓倍クロック信号が第2の論理レベルのとき、比較動作を停止し、

前記2逓倍クロック信号が第2の論理レベルのとき、第1、第2の出力は前記第1、第2の論理レベルのうち予め定められた一方の論理レベルに対応する電圧に共通に設定され、前記2逓倍クロック信号が第1の論理レベルのとき、前記第1、第2の入力信号の電圧の比較結果に応じて、前記第1、第2の出力のいずれか一方を他方の論理レベルに対応する電圧に設定するコンパレータと、

前記コンパレータの前記第1、第2の出力を入力し、前記第1、第2の出力が異なる論理レベルとなったことを検出したときに、出力を活性状態とし前記トリガ信号として出力する第2の論理ゲートを備えた第1の回路と、

を備え、

前記第1の遅延回路は、前記第1の回路から出力される前記トリガ信号の活性化のタイミングに応答して、前記入力クロック信号をキャプチャして出力する回路を備えた、ことを特徴とする半導体装置。

【請求項7】

前記第1の遅延回路の出力と前記位相比較器の間にさらに第2の遅延回路を備えた、ことを特徴とする請求項6記載の半導体装置。

【請求項8】

前記入力クロック信号のデューティを補正するデューティ補正回路をさらに備え、

前記デューティ補正回路で前記入力クロック信号のデューティを補正した信号が、前記第1の遅延回路と前記位相比較器に入力される、ことを特徴とする請求項6又は7記載の半導体装置。

【請求項9】

前記コンパレータが、前記2逓倍クロック信号が前記第2の論理レベルのとき、前記第1、第2の出力を前記第1の論理レベルに対応する第1の電源電圧にプリチャージするプリチャージ回路と、前記2逓倍クロック信号が前記第1の論理レベルのとき、前記プリチャージ回路は非活性状態とされ、前記第1、第2の入力信号を差動ラッチし前記第1、第2の出力の一方を前記第2の論理レベルに対応する第2の電源電位に設定する回路と、を備えた、ことを特徴とする請求項6乃至8のいずれか1項に半導体装置。

【請求項10】

前記コンパレータの前記第1、第2の出力をセット端子、リセット端子に入力するセット・リセット型ラッチ回路を備えた、ことを特徴とする請求項2乃至8のいずれか1項に半導体装置。

【請求項1】

入力クロック信号を第1の遅延回路で遅延させた遅延クロック信号と、前記入力クロック信号とを位相比較器に入力し、前記位相比較器から、前記入力クロック信号の周波数を2逓倍した2逓倍クロック信号を出力する2逓倍回路と、

前記2逓倍回路からの前記2逓倍クロック信号を受け、前記2逓倍クロック信号が第1の論理レベルのとき、第1、第2の入力信号の大小の比較動作を行い、前記2逓倍クロック信号が第2の論理レベルのとき、比較動作を停止するコンパレータと、

前記コンパレータの出力をモニタし、前記コンパレータが比較動作を完了したことを検出した時点でトリガ信号を出力する第1の回路と、

を備え、

前記第1の遅延回路は、前記入力クロック信号を、少なくとも前記第1の回路から前記トリガ信号が出力される時点まで遅延させ、前記遅延クロック信号として出力する可変遅延器を備えた、ことを特徴とする半導体装置。

【請求項2】

前記コンパレータが、予め定められた第1の電位に共通に設定された第1、第2の出力のうち、前記第1、第2の入力信号の大小の比較結果に応じて、いずれか一方を、第2の電位に設定し、

前記第1の回路は、前記コンパレータの前記第1、第2の出力を入力し、前記第1、第2の出力の一方が前記第2の電位となったことを検出したときに、出力を活性状態とし前記トリガ信号として出力する回路を備えている、ことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記可変遅延器は、前記トリガ信号の非活性状態から活性状態への遷移に応答して、前記入力クロック信号をキャプチャして出力する回路を備えている、ことを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記第1の遅延回路の出力と前記位相比較器の間にさらに第2の遅延回路を備えている、ことを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記入力クロック信号のデューティを補正するデューティ補正回路をさらに備え、

前記デューティ補正回路で前記入力クロック信号のデューティを補正した信号が、前記第1の遅延回路と前記位相比較器とに入力される、ことを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

入力クロック信号を遅延させた遅延クロック信号を出力する第1の遅延回路と、

前記入力クロック信号と前記遅延クロック信号を入力し、これらの信号が互いに異なる論理レベルの場合、同一の論理レベルの場合に、それぞれ第1、第2の論理レベルを出力する第1の論理ゲートを含む位相比較器と、

を備え、前記位相比較器から、前記入力クロック信号の周波数を2逓倍した2逓倍クロック信号を生成する2逓倍回路と、

前記2逓倍回路からの前記2逓倍クロック信号を受け、前記2逓倍クロック信号が第1の論理レベルのとき、第1、第2の入力信号の大小の比較動作を行い、前記2逓倍クロック信号が第2の論理レベルのとき、比較動作を停止し、

前記2逓倍クロック信号が第2の論理レベルのとき、第1、第2の出力は前記第1、第2の論理レベルのうち予め定められた一方の論理レベルに対応する電圧に共通に設定され、前記2逓倍クロック信号が第1の論理レベルのとき、前記第1、第2の入力信号の電圧の比較結果に応じて、前記第1、第2の出力のいずれか一方を他方の論理レベルに対応する電圧に設定するコンパレータと、

前記コンパレータの前記第1、第2の出力を入力し、前記第1、第2の出力が異なる論理レベルとなったことを検出したときに、出力を活性状態とし前記トリガ信号として出力する第2の論理ゲートを備えた第1の回路と、

を備え、

前記第1の遅延回路は、前記第1の回路から出力される前記トリガ信号の活性化のタイミングに応答して、前記入力クロック信号をキャプチャして出力する回路を備えた、ことを特徴とする半導体装置。

【請求項7】

前記第1の遅延回路の出力と前記位相比較器の間にさらに第2の遅延回路を備えた、ことを特徴とする請求項6記載の半導体装置。

【請求項8】

前記入力クロック信号のデューティを補正するデューティ補正回路をさらに備え、

前記デューティ補正回路で前記入力クロック信号のデューティを補正した信号が、前記第1の遅延回路と前記位相比較器に入力される、ことを特徴とする請求項6又は7記載の半導体装置。

【請求項9】

前記コンパレータが、前記2逓倍クロック信号が前記第2の論理レベルのとき、前記第1、第2の出力を前記第1の論理レベルに対応する第1の電源電圧にプリチャージするプリチャージ回路と、前記2逓倍クロック信号が前記第1の論理レベルのとき、前記プリチャージ回路は非活性状態とされ、前記第1、第2の入力信号を差動ラッチし前記第1、第2の出力の一方を前記第2の論理レベルに対応する第2の電源電位に設定する回路と、を備えた、ことを特徴とする請求項6乃至8のいずれか1項に半導体装置。

【請求項10】

前記コンパレータの前記第1、第2の出力をセット端子、リセット端子に入力するセット・リセット型ラッチ回路を備えた、ことを特徴とする請求項2乃至8のいずれか1項に半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−102282(P2013−102282A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−243769(P2011−243769)

【出願日】平成23年11月7日(2011.11.7)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月7日(2011.11.7)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]