半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電気回路の技術に関する。より詳しくは、トランジスタを具備する電気回路

の技術に関する。

【背景技術】

【0002】

近年、携帯電話や携帯端末などに幅広く使用されている集積回路(IC)は、5mm四方

程度のシリコン基板上に、数十万〜数百万ものトランジスタや抵抗などを形成したもので

、装置の小型化及び高信頼化、装置の大量生産に重要な役割を果たしている。

【0003】

そして、集積回路(IC)等に用いられる電気回路を設計するときには、多くの場合にお

いて、振幅が小さい信号の電圧や電流を増幅する機能を有する増幅回路が設計される。増

幅回路は、ひずみの発生をなくし、電気回路を安定に働かせるためには不可欠な回路であ

るため、幅広く用いられている。

【0004】

ここで、増幅回路の一例として、ソースフォロワ回路の構成とその動作について説明す

る。最初に図5(A)にソースフォロワ回路の構成例を示し、定常状態における動作につ

いて説明する。次いで、図5(B)(C)を用いて、ソースフォロワ回路の動作点につい

て説明する。最後に、図6に図5(A)とは異なる構成のソースフォロワ回路の例を示し

、過渡状態における動作について説明する。

【0005】

まず図5(A)にソースフォロワ回路を用いて、定常状態における動作について説明す

る。

【0006】

図5(A)において、11はnチャネル型の増幅用トランジスタ、12はnチャネル型

のバイアス用トランジスタである。なお図5(A)に示す増幅用トランジスタ11及びバ

イアス用トランジスタ12はnチャネル型とするが、pチャネル型トランジスタを用いて

構成してもよい。またここでは簡単のため、増幅用トランジスタ11及びバイアス用トラ

ンジスタ12は、その特性及びサイズが同一であるとし、さらに電流特性も理想的なもの

であるとする。つまり、増幅用トランジスタ11及びバイアス用トランジスタ12のソー

ス・ドレイン間電圧が変化しても、飽和領域における電流値は変化しないと仮定する。

【0007】

また、増幅用トランジスタ11のドレイン領域は電源線13に接続され、ソース領域は

バイアス用トランジスタ12のドレイン領域に接続している。バイアス用トランジスタ1

2のソース領域は、電源線14に接続されている。

【0008】

バイアス用トランジスタ12のゲート電極には、バイアス電位Vbが印加される。そして

電源線13には電源電位Vddが印加され、電源線14には、接地電位Vss(=0V)が印加

される。

【0009】

図5(A)に示すソースフォロワ回路において、増幅用トランジスタ11のゲート電極

は、入力端子となっており、増幅用トランジスタ11のゲート電極には、入力電位Vinが

入力される。また増幅用トランジスタ11のソース領域が出力端子となっており、増幅用

トランジスタ11のソース領域の電位が、出力電位Voutとなる。バイアス用トランジスタ

12のゲート電極にはバイアス電位Vbが印加されており、該バイアス用トランジスタ12

が飽和領域で動作するときには、Ibで示す電流が流れるとする。このとき、増幅用トラ

ンジスタ11及びバイアス用トランジスタ12は直列に接続されているため、両トランジ

スタには同量の電流が流れる。つまり、バイアス用トランジスタ12に電流Ibが流れると

きには、増幅用トランジスタ11にも電流Ibが流れる。

【0010】

ここで、ソースフォロワ回路における出力電位Voutを求めてみる。出力電位Voutは、入

力電位Vinよりも増幅用トランジスタ11のゲート・ソース間電圧Vgs1の分だけ低い値と

なる。このとき、入力電位Vin、出力電位Vout及びゲート・ソース間電圧Vgs1の関係は、

以下の式(1)を満たす。

【0011】

Vout=Vin-Vgs1・・・(1)

【0012】

そして、増幅用トランジスタ11が飽和領域で動作している場合は、増幅用トランジス

タ11に電流Ibが流れるためには、増幅用トランジスタ11のゲート・ソース間電圧Vgs1

がバイアス電位Vbと等しいということが必要である。そうすると、以下の式(2)の式が

成立する。但し式(2)は、増幅用トランジスタ11及びバイアス用トランジスタ12が

飽和領域で動作するときにのみにおいて成立する。

【0013】

Vout=Vin-Vb・・・(2)

【0014】

次いで、増幅用トランジスタ11及びバイアス用トランジスタ12の電圧と電流の関係

を示した図5(B)(C)を用いて、ソースフォロワ回路の動作点について説明する。さ

らに詳しくは、増幅用トランジスタ11のゲート・ソース間電圧Vgs1と、バイアス用トラ

ンジスタ12のゲート・ソース間電圧Vgs2が同じ値の場合について、図5(B)を用いて

説明する。次いで、増幅用トランジスタ11のゲート・ソース間電圧Vgs1と、バイアス用

トランジスタ12のゲート・ソース間電圧Vgs2とが異なる値の場合であって、例えばバイ

アス用トランジスタ12が線形領域で動作している場合について、図5(C)を用いて説

明する。

【0015】

図5(B)において、点線21は増幅用トランジスタ11のゲート・ソース間電圧Vgs1

がVbであるときの電圧と電流の関係を示し、実線22はバイアス用トランジスタ12のゲ

ート・ソース間電圧Vgs2がVbであるときの電圧と電流の関係を示す。また図5(C)にお

いて、点線21は増幅用トランジスタ11のゲート・ソース間電圧Vgs1がVb’であるとき

の電圧と電流の関係を示し、実線22はバイアス用トランジスタ12のゲート・ソース間

電圧Vgs2がVbであるときの電圧と電流の関係を示す。

【0016】

図5(B)において、増幅用トランジスタ11のゲート・ソース間電圧Vgs1と、バイア

ス用トランジスタ12のゲート・ソース間電圧Vgs2が同じ値であり、さらにバイアス電位

Vbと、バイアス用トランジスタ12のゲート・ソース間電圧Vgs2は同じ値であるため、増

幅用トランジスタ11のゲート・ソース間電圧Vgs1は、バイアス電位Vbと同じ値である。

つまり、Vgs1=Vgs2=Vbとなり、図5(B)

に示すように、増幅用トランジスタ11及びバイアス用トランジスタ12は飽和領域で動

作している。このとき、入力電位Vinと出力電位Voutの関係は線形となる。

【0017】

一方、図5(C)において、増幅用トランジスタ11のゲート・ソース間電圧Vgs1は、

バイアス用トランジスタ12のゲート・ソース間電圧Vgs2とは異なる値である。そして、

バイアス用トランジスタ12のゲート・ソース間電圧Vgs2はバイアス電位Vbと同じ値であ

る。また、増幅用トランジスタ11のゲート・ソース間電圧Vgs1は、バイアス電位Vb'で

あるとする。つまり、Vgs2=Vb、Vgs1=Vb’となり、図5(C)で示すように、増幅用ト

ランジスタ11は飽和領域で動作しており、バイアス用トランジスタ12が線形領域で動

作している。このとき、入力電位Vin、出力電位Vout及びバイアス電位Vb'の関係は以下の

式(3)を満たす。

【0018】

Vout=Vin-Vb'・・・(3)

【0019】

バイアス用トランジスタ12が線形領域で動作するときに流れる電流をIb'とすると、I

b'<Ibとなる。つまり、Vb'<Vbとなって、入力電位Vinと電流Ib'の両者の値は小さくなる

。そうすると、バイアス電位Vb'も小さくなる。このとき入力電位Vinと出力電位Voutの関

係は、非線形となる。

【0020】

以上をまとめると、定常状態におけるソースフォロワ回路において、出力電位Voutの振

幅を大きくするためには、バイアス電位Vbを小さくすることが好ましい。これは以下の2

つの理由による。

【0021】

1つ目の理由は、式(2)に示すように、バイアス電位Vbが小さいと、出力電位Voutを

大きくすることが出来るからである。2つ目の理由は、バイアス電位Vbの値が大きい場合

には、入力電位Vinを小さくすると、バイアス用トランジスタ12が線形領域で動作しや

すくなってしまうからである。バイアス用トランジスタ12が線形領域で動作すると、入

力電位Vinと出力電位Voutの関係は、非線形となりやすい。

【0022】

なおバイアス用トランジスタ12は、導通状態であることが必要であるため、バイアス

電位Vbの値は、バイアス用トランジスタ12のしきい値電圧よりも大きい値にする必要が

ある。

【0023】

これまでは、ソースフォロワ回路の定常状態での動作について説明してきたが、続いて

、ソースフォロワ回路の過渡状態での動作について、図6を用いて説明する。

【0024】

図6に示すソースフォロワ回路は、図5(A)の回路に容量素子15が追加して設計さ

れた構成である。容量素子15の一方の端子は増幅用トランジスタ11のソース領域に接

続され、他方の端子は電源線16に接続されている。電源線16には、接地電位Vssが印

加されている。

【0025】

容量素子15の両電極間の電位差は、ソースフォロワ回路の出力電位Voutと同一となる

。ここでは、図6(A)を用いてVout<Vin-Vbの場合の動作について説明し、次いで図6

(B)を用いてVout>Vin-Vbの場合の動作について説明する。

【0026】

まず、図6(A)を用いてVout<Vin-Vbの場合のソースフォロワ回路の過渡状態におけ

る動作について説明する。

【0027】

図6(A)において、t=0のときには、増幅用トランジスタ11のゲート・ソース間電

圧Vgs1の値は、バイアス用トランジスタ12のゲート・ソース間電圧Vgs2の値よりも大き

い。そのため、増幅用トランジスタ11には、大きな電流が流れて、容量素子15には急

速に電荷が保持される。そうすると、出力電位Voutは大きくなり、増幅用トランジスタ1

1のゲート・ソース間電圧Vgs1の値は減少する。

【0028】

そして時間の経過に伴い(t=t1、t1>0)、増幅用トランジスタ11のゲート・ソース間

電圧Vgs1がバイアス電位Vbに等しくなると定常状態になる。このとき、出力電位Vout、入

力電位Vin及びバイアス電位Vbの関係は、上記の式(2)を満たす。

【0029】

以上をまとめると、Vout<Vin-Vbの場合には、増幅用トランジスタ11のゲート・ソー

ス間電圧Vgs1の値が、バイアス電位Vbよりも大きいため、増幅用トランジスタ11には

大きな電流が流れて、容量素子15に急速に電荷が保持される。そのため、容量素子15

が所定の電荷の保持を行う時間、言い換えると容量素子15に対する信号の書き込みに要

する時間は短くてすむ。

【0030】

次いで、図6(B)を用いてVout>Vin-Vbの場合のソースフォロワ回路の過渡状態にお

ける動作について説明する。

【0031】

図6(B)において、t=0のときには、増幅用トランジスタ11のゲート・ソース間電

圧Vgs1は、該増幅用トランジスタ11のしきい値電圧よりも小さい値である。そのため、

増幅用トランジスタ11は非導通状態にある。そして容量素子15に蓄積されていた電荷

は、バイアス用トランジスタ12を介して接地電位Vssの方向に流れていき、最終的には

放電される。このとき、バイアス用トランジスタ12のゲート・ソース間電圧Vgs2は、バ

イアス電位Vbと同じ値であるので、バイアス用トランジスタ12を流れる電流はIbとなる

。

【0032】

そして時間の経過に伴い(t=t1、t1>0)、出力電位Voutが小さくなり、増幅用トランジ

スタ11のゲート・ソース間電圧Vgs1が大きくなる。そして増幅用トランジスタ11のゲ

ート・ソース間電圧Vgs1がバイアス電位Vbに等しくなると、定常状態となる。このとき、

出力電位Vout、入力電位Vin及びバイアス電位Vbの関係は、上記の式(2)を満たす。な

お定常状態では、出力電位Voutは一定の値を保っており、容量素子15に電荷は流れない

。そして、増幅用トランジスタ11及びバイアス用トランジスタ12には、電流Ibが流れ

る。

【0033】

以上をまとめると、Vout>Vin-Vbの場合には、容量素子15が所定の電荷の保持を行う

時間、言い換えると容量素子15に対する信号の書き込み時間は、バイアス用トランジス

タ12を流れる電流Ibに依存する。そして、電流Ibはバイアス電位Vbの大きさに依存する

。従って、電流Ibを大きくして、容量素子15に対する信号の書き込み時間を短くするた

めには、バイアス電位Vbを大きくする必要が生ずる。

【0034】

なおトランジスタのしきい値電圧のバラツキを補正する方法として、信号が入力された

回路の出力によりバラツキをみて、その後、そのバラツキを入力するフィードバックさせ

て補正するという方法がある(例えば、非特許文献1参照。)。

【先行技術文献】

【非特許文献】

【0035】

【非特許文献1】H.Sekine et al,「Amplifier Compensation Method for a Poly-Si TFT LCLV with an Integrated Data-Driver」,IDRC'97,p.45-48

【発明の概要】

【発明が解決しようとする課題】

【0036】

上述したソースフォロワ回路の動作は、増幅用トランジスタ11及びバイアス用トラン

ジスタ12の特性が同じであると仮定した上で行われるものである。しかし、両トランジ

スタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネ

ル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが

生じてしまう。

【0037】

例えば図5(A)において、増幅用トランジスタ11のしきい値電圧が3Vであり、バ

イアス用トランジスタ12のしきい値電圧が4Vとして、1Vのバラツキが生じていたと

する。そうすると、電流Ibを流すためには、増幅用トランジスタ11のゲート・ソース

間電圧Vgs1には、バイアス用トランジスタ12のゲート・ソース間電圧Vgs2よりも1V低

い電圧を加える必要が生ずる。つまりVgs1=Vb-1となる。そうすると、Vout=Vin-Vgs1=Vin

-Vb+1となってしまう。つまり、増幅用トランジスタ11及びバイアス用トランジスタ1

2のしきい値電圧に1Vでもバラツキが生じていると、出力電位Voutにもバラツキが生じ

てしまう。

【0038】

本発明は上記の問題点を鑑みてなされたものであり、トランジスタの特性バラツキの影

響を抑制した電気回路を提供することを課題とする。さらに詳しくは、電流を増幅する機

能を有する電気回路において、トランジスタのしきい値電圧のバラツキの影響を抑制して

、所望の電圧を供給することができる電気回路を提供することを課題とする。

【課題を解決するための手段】

【0039】

本発明は、上記の問題点を解決するために、以下に示す構成の電気回路を用いる。

【0040】

図3(A)に示す電気回路は、スイッチング機能を有するスイッチング素子31、32

(以下、sw31、sw32と表記)、nチャネル型のトランジスタ33、容量素子34

により構成される。トランジスタ33のソース領域は電源線36に接続され、ドレイン領

域はsw31を介して電源線35に接続されている。

トランジスタ33のゲート電極は容量素子34の一方の端子に接続されている。

また、容量素子34の他方の端子は電源線37に接続されている。容量素子34は、トラ

ンジスタ33のゲート・ソース間電圧Vgsを保持する役目を担う。また、電源線35には

電源電位Vddが印加され、電源線36、37には接地電位Vssが印加される。

【0041】

図3(A)〜図3(C)においては、トランジスタ33はnチャネル型とするが、これ

に限定されず、pチャネル型で構成することも可能である。また図3(C)には、図3(

A)と同じ回路素子を有し、且つ接続構成が異なる電気回路を示す。図3(C)に示す電

気回路の動作は、後述する図3(A)に示す回路の動作に準ずるので、ここでは省略する

。

【0042】

そして図3(A)に示す電気回路では、容量素子34の両電極間の電位差が、トランジ

スタ33のしきい値電圧と同じ値となるように、該容量素子34に電荷が保持される。こ

の動作について、以下に説明する。

【0043】

図3(A)において、sw31及びsw32はオンである。この状態において、電源線

35には電源電位Vddが印加され、電源線36、37には接地電位Vssが印加されているた

め、電源線35と、電源線36及び電源線37との間には電位差が生じる。その結果、電

源線35から、sw31及びsw32を介して、トランジスタ33及び容量素子34の方

向に向かって、電流Idsが流れる。このとき、電流Idsは、I1とI2に分かれて流れる。な

お電流Idsは、Ids=I1+I2を満たす。

【0044】

電源線35から、電源線36及び電源線37の方向に電流が流れ始めた瞬間には、容量

素子34には電荷は保持されていない。そのため、トランジスタ33はオフである。よっ

て、I2=0であり、Ids=I1となる。

【0045】

そして徐々に容量素子34に電荷が蓄積されて、容量素子34の両電極間に電位差が生

じ始める。両電極間の電位差がVthになると、トランジスタ33がオンして、I2>0とな

る、上述したようにIds=I1+I2となるので、I1は次第に減少するが、依然電流は流れてい

る。

【0046】

そして容量素子34では、該容量素子34の両電極間の電位差がVddになるまで、電荷

の蓄積が続けられる。容量素子34において、電荷の蓄積が終了すると(図3(D)(E

)、A点)、電流I2は流れなくなり、さらにトランジスタ33はオンであるので、Ids=I

1となる。

【0047】

続いて、図3(B)に示すように、sw31をオフにする。sw32は引き続きオンで

ある。そうすると、容量素子34に保持された電荷は、sw32を介して、トランジスタ

33の方向に流れていく。より詳しくは、容量素子34に保持された電荷は、トランジス

タ33のドレイン領域からソース領域を介して、電源線36の方向に流れていって放電す

る。この動作は、トランジスタ33がオフになるまで行われる。つまり、容量素子34に

保持されている電荷が、トランジスタ33のしきい値電圧と同じ値になるまで続けられる

(図3(D)(E)、B点)。

【0048】

このようにすると、容量素子34の両電極間の電位差が、トランジスタ33のしきい値

電圧と同じ値となるように電荷が保持される。

【0049】

上述したように、本発明は、容量素子の両電極がある特定のトランジスタのゲート・ソ

ース間電圧を保持できるように配置した電気回路を提供する。そして本発明は、容量素子

の両電極間の電位差が、ある特定のトランジスタのしきい値電圧となるように設定できる

機能を有する電気回路を提供する。

【0050】

さらに本発明では、容量素子に保持されているある特定のトランジスタのゲート・ソー

ス間電圧をそのまま保存して、且つ該トランジスタのゲート電極に信号電圧(ビデオ信号

の電圧など)を入力する。そうすると、前記トランジスタのゲート電極には、容量素子に

保持されているゲート・ソース間電圧に加えて、前記信号電圧を上乗せした電圧が入力さ

れる。その結果、トランジスタのゲート電極には、該トランジスタのしきい値電圧と信号

電圧とを足した値が入力される。つまり本発明では、トランジスタ間にしきい値電圧にバ

ラツキが生じていても、信号電圧が入力されるトランジスタでは、常に該トランジスタの

しきい値電圧と信号電圧を足した値が入力されることになる。そのため、トランジスタ間

のしきい値電圧のバラツキの影響を抑制した電気回路を提供することが出来る。

【0051】

なお容量素子に保持されているゲート・ソース間電圧に加えて、信号電圧が上乗せされ

る仕組みは電荷保存則により説明される。電荷保存則とは、正電気量と負電気量の代数的

な和の全電気量は一定であるという事実を示す。ここで電荷保存則について、図4を用い

て説明する。

【0052】

図4において、26は電源(定電圧源)であり、27は容量素子である。電源26と容

量素子27はsw28を介して接続されている。電源26は電源線29に接続され、容量

素子27は電源線30に接続されている。

【0053】

図4(A)において、sw28がオンであり、電源線29及び電源線30には0Vが印

加されている。そして電源26には電圧Vxが印加されており、この状態において、sw

28は導通状態である。その結果、容量素子27の両電極間の電位差がVxとなるように

、該容量素子27に電荷が保持される。

【0054】

次いで、図4(B)において、sw28をオフにする。このとき、容量素子27に保持

されている電荷は、電荷保存則によって引き続き保持される。

【0055】

そして、図4(C)において、容量素子27の一方の端子に接続された電源線30に電

圧Vyを印加する。sw28はオフであり、また電源線29には0Vが印加されている。

このとき、容量素子27に保持されている電荷は保存されて、電源線30に印加される電

圧Vyが上乗せされる。つまり、図4(C)に示すように、容量素子27の一方の端子の

電位は(Vy+Vx)となる。

【0056】

このように、容量素子27では、保持されている電荷はそのまま保存されて、該容量素

子27の一方の端子の電位が上昇すると、それに合わせて、他方の端子の電位が上昇する

。

【0057】

なお本発明では、どのような材料を用いたトランジスタ、どのような手段、製造方法を

経たトランジスタを用いてもよく、またどのようなタイプのトランジスタを用いてもよい

。例えば、薄膜トランジスタ(TFT)を用いてもよい。TFTとしては、半導体層が非

晶質(アモルファス)、多結晶(ポリクリスタル、ポリシリコン)、単結晶のいずれを用

いてもよい。その他のトランジスタとして、単結晶基板において作られたトランジスタで

もよいし、SOI基板において作られたトランジスタでもよい。また、有機物やカーボン

ナノチューブで形成されたトランジスタでもよい。さらに、MOS型トランジスタでもよ

いし、バイポーラ型トランジスタでもよい。

【発明の効果】

【0058】

本発明は、容量素子の両電極がある特定のトランジスタのゲート・ソース間電圧を保持

できるように配置した電気回路を提供する。そして本発明は、容量素子の両電極間の電位

差が、ある特定のトランジスタのしきい値電圧となるように設定できる機能を有する電気

回路を提供する。

【0059】

さらに本発明では、容量素子に保持されているある特定のトランジスタのゲート・ソー

ス間電圧をそのまま保存して、且つ該トランジスタのゲート電極に信号電圧(ビデオ信号

の電圧など)を入力する。そうすると、前記トランジスタのゲート電極には、容量素子に

保持されているゲート・ソース間電圧に加えて、前記信号電圧を上乗せした電圧が入力さ

れる。その結果、トランジスタのゲート電極には、該トランジスタのしきい値電圧と信号

電圧とを足した値が入力される。つまり本発明では、トランジスタ間にしきい値電圧にバ

ラツキが生じていても、信号電圧が入力されるトランジスタでは、常に該トランジスタの

しきい値電圧と信号電圧を足した値が入力されることになる。そのため、トランジスタ間

のしきい値電圧のバラツキの影響を抑制した電気回路を提供することが出来る。

【図面の簡単な説明】

【0060】

【図1】本発明のソースフォロワ回路の動作を説明する図。

【図2】本発明のソースフォロワ回路の動作を説明する図。

【図3】本発明の電気回路の構成とその動作を説明する図。

【図4】電荷保存則を説明する図。

【図5】ソースフォロワ回路の動作を説明する図。

【図6】ソースフォロワ回路の動作を説明する図。

【図7】本発明のソースフォロワ回路の動作を説明する図。

【図8】本発明の差動増幅回路の構成を説明する図。

【図9】本発明の差動増幅回路の構成を説明する図。

【図10】本発明のオペアンプの構成を説明する図。

【図11】本発明の半導体装置を示す図。

【図12】本発明の半導体装置の画素とバイアス用回路を示す図。

【図13】本発明の電気回路の構成を説明する図。

【図14】本発明の信号線駆動回路の図。

【図15】本発明の信号線駆動回路の図。

【図16】本発明の信号線駆動回路の動作を説明する図。

【図17】本発明のオペアンプを示す図。

【図18】本発明のオペアンプを示す図。

【図19】本発明のオペアンプを示す図。

【図20】本発明が適用される電気機器の図。

【図21】本発明のオペアンプの構成を説明する図。

【図22】本発明のオペアンプを示す図。

【図23】本発明のオペアンプを示す図。

【発明を実施するための形態】

【0061】

(実施の形態1)

本実施の形態では、本発明の電気回路の一例として、ソースフォロワ回路を示し、その

構成と動作について図1、2を用いて説明する。

【0062】

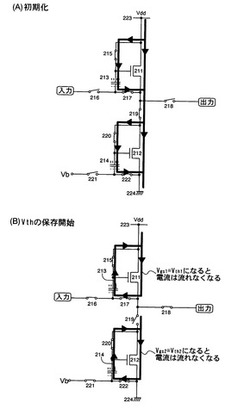

図1、2において、211はnチャネル型の増幅用トランジスタであり、212はnチ

ャネル型のバイアス用トランジスタである。213及び214は容量素子である。また、

215〜222はスイッチング機能を有する素子であり、好ましくはトランジスタやアナ

ログスイッチなどの半導体素子が用いられる。223及び224は電源線であり、電源線

223には電源電位Vddが印加され、電源線224には接地電位Vssが印加される。

【0063】

なお本実施の形態では、増幅用トランジスタ211及びバイアス用トランジスタ212

がnチャネル型の場合を示すが、本発明はこれに限定されず、両トランジスタがpチャネ

ル型であってもよい。また、両トランジスタの極性が異なっていてもよい。

【0064】

両トランジスタの極性が異なっている場合は、プッシュプル回路を構成していることに

なるので、両トランジスタとも、増幅用トランジスタとして機能する。

よって、両トランジスタに、信号が入力される。

【0065】

増幅用トランジスタ211のドレイン領域は電源線223に接続され、ソース領域はス

イッチ217〜スイッチ219に接続されている。増幅用トランジスタ211のゲート電

極は容量素子213の一方の端子に接続されている。容量素子213の他方の端子は、ス

イッチ217を介してトランジスタ211のソース領域に接続されている。容量素子21

3は、増幅用トランジスタ211のゲート・ソース間電圧(しきい値電圧)を保持する役

目を担う。なお以下には増幅用トランジスタ211は、トランジスタ211と表記する。

【0066】

バイアス用トランジスタ212のソース領域は電源線224に接続され、ドレイン領域

はスイッチ219、220に接続されている。バイアス用トランジスタ212のゲート電

極は容量素子214の一方の端子に接続されている。容量素子214の他方の端子は、ス

イッチ222を介してバイアス用トランジスタ212のソース領域に接続されている。容

量素子214は、バイアス用トランジスタ212のゲート・ソース間電圧(しきい値電圧

)を保持する役目を担う。なお以下にはバイアス用トランジスタ212は、トランジスタ

212と表記する。

【0067】

スイッチ215〜スイッチ222は、入力される信号によって、導通又は非導通(オン

又はオフ)が制御される。しかし、図1、2においては、説明を簡単にするために、スイ

ッチ215〜スイッチ222に信号を入力する信号線等の図示は省略する。

【0068】

図1、2に示すソースフォロワ回路において、スイッチ216の一方の端子が入力端子

となる。前記入力端子を介して、入力電位Vin(信号電圧)は、スイッチ216及び容量

素子213を介して、トランジスタ211のゲート電極に入力される。またスイッチ22

1の一方の端子からはバイアス電位Vbが入力される。

バイアス電位Vbは、スイッチ221及び容量素子214を介して、トランジスタ212の

ゲート電極に入力される。また、スイッチ218の一方の端子が出力端子となっており、

トランジスタ211のソース領域の電位が出力電位Voutとなる。

【0069】

なおスイッチ218は、トランジスタ211のソース領域と接続され、且つスイッチ2

19を介してトランジスタ212のドレイン領域とに接続されているが、本発明はこれに

限定されない。スイッチ218は、トランジスタ212のドレイン領域と接続され、且つ

スイッチ219を介してトランジスタ211のソース領域とに接続されていてもよい。

【0070】

但しスイッチ218は、トランジスタ211のソース領域と接続され、且つスイッチ2

19を介してトランジスタ212のドレイン領域とに接続されている方が好ましい。これ

は、スイッチ218が、トランジスタ212のドレイン領域と接続され、且つスイッチ2

19を介してトランジスタ211のソース領域とに接続されている場合には、スイッチ2

19にオン抵抗があると、出力電位Voutがその影響を受けてしまうために、出力電位Vout

が低下してしまうからである。

【0071】

次いで、図1、2に示したソースフォロワ回路の動作について説明する。

【0072】

図1(A)において、スイッチ215、スイッチ217、スイッチ219、スイッチ2

20及びスイッチ222をオンにする。そして上記以外のスイッチはオフにする。この状

態において、電源線223にはVddが印加され、電源線224にはVssが印加されているた

め、電源線223と電源線224の間には電位差が生じる。その結果、電源線223から

電源線224の方向に向かって電流が流れる。

【0073】

電源線223から、電源線224の方向に電流が流れ始めた瞬間には、容量素子213

及び容量素子214には電荷は保持されていない。そのため、トランジスタ211及びト

ランジスタ212はオフである。電流は、電源線223からスイッチ215、スイッチ2

17を介し、次いでスイッチ219を介し、さらにスイッチ220、スイッチ222を介

して、電源線224の方向に流れていく。

【0074】

そして徐々に容量素子213、214に電荷が蓄積されて、該容量素子213、214

の両電極間に電位差が生じ始める。容量素子213の両電極間の電位差がトランジスタ2

11のしきい値電圧Vth1になると、トランジスタ211はオンする。同様に、容量素子2

14の両電極間の電位差がトランジスタ212のしきい値電圧Vth2になると、トランジス

タ212はオンする。

【0075】

容量素子213、214では、定常状態になるまで、電荷の蓄積が続けられる。

【0076】

続いて、図1(B)に示すように、容量素子213、214において電荷の蓄積が終了

して定常状態になると、スイッチ219をオンからオフにして、それ以外のスイッチは図

1(A)の状態を維持する。

【0077】

そうすると、容量素子213に保持された正の電荷は、スイッチ215を介して、トラ

ンジスタ211の方向に流れていく。より詳しくは、容量素子213に保持された正の電

荷は、スイッチ215を介してトランジスタ211のドレイン領域からソース領域を介し

て、さらにスイッチ217を介して容量素子213の方向に流れていく。その結果、容量

素子213の両電極間の電位差は減少していく。この動作は、トランジスタ211がオフ

になるまで行われる。つまり、容量素子213に保持されている電荷が、トランジスタ2

11のしきい値電圧Vth1と同じ値になるまで続けられる。

【0078】

また、容量素子214に保持された正の電荷は、スイッチ220を介して、トランジス

タ212の方向に流れていく。より詳しくは、容量素子214に保持された正の電荷は、

スイッチ220を介してトランジスタ212のドレイン領域からソース領域を介して、電

源線224の方向に流れていく。この動作は、トランジスタ212がオフになるまで行わ

れる。つまり、容量素子214に保持されている電荷が、トランジスタ212のしきい値

電圧Vth2と同じ値になるまで続けられる。

【0079】

このようにすると、容量素子213の両電極間の電位差がトランジスタ211のしきい

値電圧Vth1と同じ値になる。また、容量素子214の両電極間の電位差がトランジスタ2

12のしきい値電圧Vth2と同じ値になる。

【0080】

このように、容量素子213の両電極間の電位差がトランジスタ211のしきい値電圧

Vth1と同じ値になり、且つ容量素子214の両電極間の電位差がトランジスタ212のし

きい値電圧Vth2と同じ値になったら、スイッチ215、スイッチ217、スイッチ220

及びスイッチ222をオフにする(図2(A))。つまりこのときには、全てのスイッチ

215〜スイッチ222はオフである。

【0081】

なおスイッチ215、スイッチ217、スイッチ220及びスイッチ222は、容量素

子213、214の両電極間の電位差がトランジスタ211、212のしきい値電圧Vth1

、Vth2と同じ値になってからオフにすることが望ましい。しかし、本発明はこれに限定さ

れない。トランジスタ211、212のバラツキが小さい場合は、電気回路の動作では特

に問題とはならないため、容量素子213、214の両電極間の電位差がトランジスタ2

11、212のしきい値電圧Vth1、Vth2と近い値のときに、スイッチ215、スイッチ2

17、スイッチ220及びスイッチ222をオフにしてもよく、そのタイミングは特に限

定されない。

【0082】

続いて、スイッチ216、スイッチ218、スイッチ219及びスイッチ221をオン

にする(図2(B))。上記以外のスイッチはオフが維持される。このとき入力端子から

スイッチ216及び容量素子213を介して、入力電位Vinがトランジスタ211のゲー

ト電極に加わる。このとき、電荷保存則により、トランジスタ211のゲート電極には、

該トランジスタ211のしきい値電圧Vth1に加えて、入力電位Vinが上乗せされた値(Vth

1+Vin)が加えられる。また、トランジスタ212のゲート電極には、該トランジスタ2

12のしきい値電圧Vth2に加えて、入力電位Vbが上乗せされた値(Vth2+Vb)が加えられ

る。

【0083】

なおトランジスタが、飽和領域で動作するときには、以下の式(4)が成立する。Ids

はトランジスタのチャネル形成領域を流れる電流量であり、Vgsはトランジスタのゲート

・ソース間電圧である。またVthはトランジスタのしきい値電圧である。

【0084】

Ids∝(Vgs−Vth)2・・(4)

【0085】

上記の式(4)において、Vk=Vgs-Vthとすると、以下の式(5)が成立する。

【0086】

Ids∝Vk2・・(5)

【0087】

式(5)より、Idsは、VgsからVthの値を引いた値であるVkの2乗に比例していること

がわかる。

【0088】

ここで、トランジスタ211、212に上記の式(4)(5)を適用して、出力電位Vo

utを求める。なお本実施の形態では、トランジスタ211、212のゲート幅(W)、ゲ

ート長(L)にはバラツキが生じておらず、同一であるとする。

一方、トランジスタ211、212のしきい値電圧Vth1、Vth2にはバラツキが生じている

とする。

【0089】

トランジスタ212のゲート電極に加えられた電圧をVa2とすると、Va2=Vb+Vth2が成立

する。さらに、トランジスタ212のゲート電極に加えられた電圧Va2からしきい値電圧V

th2を引いた値をVk2とすると、以下の式(6)が成立する。

【0090】

Vk2=Va2-Vth2=(Vb+Vth2)-Vth2=Vb・・(6)

【0091】

そして、トランジスタ211のゲート電極に加えられた電圧をVa1とすると、以下の式

(7)が成立する。

【0092】

Va1=Vin+Vth1・・(7)

【0093】

さらに、トランジスタ211のゲート・ソース間電圧Vgs1からしきい値電圧Vth1を引い

た値をVk1とすると、以下の式(8)が成立する。

【0094】

Vk1=Vgs1-Vth1・・(8)

【0095】

ここで、トランジスタ211、212には同量の電流が流れるため、以下の式(9)が

成立する。

【0096】

Vk1=Vk2=Vb・・(9)

【0097】

そして、出力電位Voutは、トランジスタ211のソース領域の電位であることから、以

下の式(10)が成立する。

【0098】

Vout=Va1-Vgs1=(Vin+Vth1)-(Vb+Vth1)=Vin-Vb・・・(10)

【0099】

式(10)に示すように、出力電位Voutは、入力電位Vinからバイアス電位Vbを引いた

値になっており、しきい値電圧には依存していない。そのため、トランジスタ211、2

12のしきい値電圧にバラツキが生じていても、出力電位Voutに対する影響を抑制するこ

とが出来る。

【0100】

なお上記の説明では、トランジスタ211、212のゲート幅(W)、ゲート長(L)は

バラツキが生じておらず、同一であるとしたが、両トランジスタのゲート幅(W)、ゲー

ト長(L)の大きさは特に限定されない。

【0101】

また図7(C)には、バイアス用トランジスタ212を配置していない場合のソースフ

ォロワ回路を示す。図7(C)に示すソースフォロワ回路の動作は、スイッチ219が出

力動作のときにオフになる以外は、上述した図1、2の動作と同じであるので、本実施の

形態では説明を省略する。

【0102】

なお本明細書では、容量素子に所定の電荷の保持を行う動作を設定動作と呼ぶ。本実施

の形態では、図1(A)(B)及び図2(A)の動作が設定動作に相当する。また、入力

電位Vin及びバイアス電位Vbを入力して、出力電位Voutを取り出す動作を出力動作とよぶ

。本実施の形態では、図2(B)の動作が出力動作に相当する。

【0103】

このように本発明では、トランジスタ間にしきい値電圧にバラツキが生じていても、入

力電位Vinやバイアス電位Vbなどの信号電圧が入力されるトランジスタでは、常に該トラ

ンジスタのしきい値電圧と信号電圧を足した値が入力されることになる。そのため、トラ

ンジスタ間のしきい値電圧のバラツキの影響を抑制した電気回路を提供することが出来る

。

【0104】

(実施の形態2)

図1、2に示したソースフォロワ回路では、nチャネル型の増幅用トランジスタ211

と、nチャネル型のバイアス用トランジスタ212により構成した場合を示した。次いで

本実施の形態では、pチャネル型の増幅用トランジスタ211と、pチャネル型のバイア

ス用トランジスタ212により構成されたソースフォロワ回路を図7に示し、その構成に

ついて説明する。なお図7に示したソースフォロワ回路の動作は、実施の形態1の動作に

準ずるので、本実施の形態では説明は省略する。

【0105】

図7において、231はpチャネル型のバイアス用トランジスタであり、232はpチ

ャネル型の増幅用トランジスタである。233及び234は容量素子である。また、23

5〜242はスイッチング機能を有する素子であり、好ましくはトランジスタやアナログ

スイッチなどの半導体素子が用いられる。243及び244は電源線であり、電源線24

3には電源電位Vddが印加され、電源線244には接地電位Vssが印加される。

【0106】

なお本実施の形態では、増幅用トランジスタ232及びバイアス用トランジスタ23

1がpチャネル型の場合を示すが、両トランジスタの極性が異なっていて、プッシュプル

回路のようになっていてもよい。

【0107】

バイアス用トランジスタ231のソース領域は電源線243に接続され、ドレイン領域

はスイッチ235、239に接続されている。バイアス用トランジスタ231のゲート電

極は容量素子233の一方の端子に接続されている。容量素子233の他方の端子は、ス

イッチ237を介して電源線243に接続されている。容量素子233は、バイアス用ト

ランジスタ231のゲート・ソース間電圧(しきい値電圧)を保持する役目を担う。

【0108】

増幅用トランジスタ232のドレイン領域は電源線244に接続され、ソース領域はス

イッチ238、239、242に接続されている。増幅用トランジスタ232のゲート電

極は容量素子234の一方の端子に接続されている。容量素子234の他方の端子は、ス

イッチ242を介して増幅用トランジスタ232のソース領域に接続されている。容量素

子234は、増幅用トランジスタ232のゲート・ソース間電圧(しきい値電圧)を保持

する役目を担う。

【0109】

スイッチ235〜スイッチ242は、入力される信号によって、導通又は非導通(オン

又はオフ)が制御される。しかし、図7においては、説明を簡単にするために、スイッチ

235〜スイッチ242に信号を入力する信号線等の図示は省略する。

【0110】

なおスイッチ238は、増幅用トランジスタ232のソース領域と接続され、且つスイ

ッチ239を介してバイアス用トランジスタ231のドレイン領域とに接続されているが

、本発明はこれに限定されない。スイッチ238は、バイアス用トランジスタ231のド

レイン領域と接続され、且つスイッチ239を介して増幅用トランジスタ232のソース

領域とに接続されていてもよい。

【0111】

但しスイッチ238は、増幅用トランジスタ232のソース領域と接続され、且つスイ

ッチ239を介してバイアス用トランジスタ231のドレイン領域とに接続されている方

が好ましい。これは、スイッチ238が、バイアス用トランジスタ231のドレイン領域

と接続され、且つスイッチ239を介して増幅用トランジスタ232のソース領域とに接

続されている場合には、スイッチ239にオン抵抗があると、出力電位Voutがその影響を

受けてしまうために、出力電位Voutが低下してしまうからである。

【0112】

図7に示すソースフォロワ回路において、スイッチ241の一方の端子が入力端子とな

る。前記入力端子から入力される入力電位Vin(信号電圧)は、スイッチ241及び容量

素子234を介して、増幅用トランジスタ232のゲート電極に入力される。またスイッ

チ236の一方の端子からはバイアス電位Vbが入力される。バイアス電位Vbは、スイッチ

236及び容量素子233を介して、トランジスタ231のゲート電極に入力される。ま

た、スイッチ238の一方の端子が出力端子となっており、増幅用トランジスタ232の

ソース領域の電位が出力電位Voutとなる。

【0113】

なお、バイアス用トランジスタ231、増幅用トランジスタ232のゲート幅(W)、

ゲート長(L)の大きさは特に限定されない。

【0114】

また図7(B)には、バイアス用トランジスタ231を配置していない場合のソースフ

ォロワ回路を示す。図7(B)に示すソースフォロワ回路の動作は、スイッチ239が出

力動作のときにオフになる以外は、上述した図1、2の動作に準ずるので、本実施の形態

では説明を省略する。

【0115】

本実施の形態は、実施の形態1と任意に組み合わせることが可能である。

【0116】

(実施の形態3)

前述した実施の形態1、2では、本発明を適用したソースフォロワ回路について説明し

た。しかし本発明は、差動増幅回路、センスアンプ、オペアンプなどに代表される演算回

路など、さまざまな回路にも適用することが出来る。本実施の形態では、本発明を適用し

た演算回路について図8〜図10を用いて説明する。

【0117】

まず、本発明を適用した差動増幅回路について、図8を用いて説明する。差動増幅回路

では、入力電位Vin1及び入力電位Vin2の差の演算を行って出力電位Voutを出力する。

【0118】

図8に示す差動増幅回路において、272、273はpチャネル型のトランジスタであ

り、274、275及び286はnチャネル型のトランジスタである。

276、277及び287は容量素子である。また、スイッチ278〜スイッチ285、

スイッチ351、スイッチ288〜スイッチ290は、スイッチング機能を有する素子で

あり、好ましくはトランジスタなどの半導体素子が用いられる。また電源線271には電

源電位Vddが印加され、電源線291には接地電位Vssが印加される。

【0119】

図8に示す差動増幅回路において、トランジスタ274のゲート電極が入力端子となっ

ており、トランジスタ274のゲート電極には入力電位Vin1が入力される。またトランジ

スタ275のゲート電極も入力端子となっており、トランジスタ275のゲート電極には

入力電位Vin2が入力される。またトランジスタ275のドレイン領域が出力端子となって

おり、トランジスタ275のドレイン領域の電位が出力電位Voutとなる。

【0120】

トランジスタ272のドレイン領域は電源線271に接続され、ソース領域はトランジ

スタ274のドレイン領域に接続されている。トランジスタ273のドレイン領域は電源

線271に接続され、ソース領域はトランジスタ275のドレイン領域に接続されている

。トランジスタ272のゲート電極とトランジスタ273のゲート電極は接続されている

。なおトランジスタ272及びトランジスタ273の代わりに、抵抗を配置してもよい。

【0121】

トランジスタ274のドレイン領域は、トランジスタ272を介して電源線271に接

続され、ソース領域はスイッチ282を介して、容量素子276の一方の端子に接続され

ている。トランジスタ274のゲート電極は、容量素子276の他方の端子に接続されて

いる。容量素子276は、トランジスタ274のゲート・ソース間電圧(しきい値電圧)

を保持する役目を担う。

【0122】

トランジスタ275のドレイン領域は、トランジスタ273を介して電源線271に接

続され、ソース領域はスイッチ283を介して、容量素子277の一方の端子に接続され

ている。トランジスタ275のゲート電極は、容量素子277の他方の端子に接続されて

いる。容量素子277は、トランジスタ275のゲート・ソース間電圧(しきい値電圧)

を保持する役目を担う。

【0123】

トランジスタ286のドレイン領域は、スイッチ285やスイッチ351を介してトラ

ンジスタ274のソース領域及びトランジスタ275のソース領域に接続され、トランジ

スタ286のソース領域はスイッチ290を介して、容量素子287の一方の端子に接続

されている。トランジスタ286のゲート電極は、容量素子287の他方の端子に接続さ

れている。容量素子287は、トランジスタ286のゲート・ソース間電圧(しきい値電

圧)を保持する役目を担う。

【0124】

そして、容量素子276に所定の電荷の保持を行う動作、容量素子277に所定の電荷

の保持を行う動作、容量素子287に所定の電荷の保持を行う動作の説明は、実施の形態

1に準ずるので、簡単に説明する。

【0125】

まず、図18に示すように、初期化を行う。初期化を行うためには、トランジスタ27

4、275、286がオンになるような状態にすればよい。そして、図19に示すように

、トランジスタ274、275、286のゲート・ソース間電圧がしきい値電圧に収束す

るように動作させる。

【0126】

そして、容量素子276に所定の電荷の保持が終了したら、図22に示すように、トラ

ンジスタ274のゲート電極に入力電位Vin1が入力され、また容量素子277に所定の電

荷の保持が終了したら、トランジスタ275のゲート電極に入力電位Vin2が入力される。

また容量素子287に所定の電荷の保持が終了したら、トランジスタ286のゲート電極

にバイアス電位Vbが入力されて、出力動作を行う。このときの動作の説明は、実施の形態

1に準ずるので本実施の形態では省略する。

【0127】

なお、図8の回路は、図17に示す回路のように改良してもよい。図17では、トラン

ジスタ272、273と並列に、スイッチ352、353を追加して配置している。スイ

ッチ352、353は、設定動作を行っている時(しきい値電圧を取得している時)には

オンにしておき、出力動作を行っている時(通常の差動回路として動作させている時)に

はオフにしておく。上記スイッチの追加により、設定動作を行っている時にはトランジス

タ274、275に電流を供給しやすくしたり、トランジスタ274、275のドレイン

の電位を固定しやすくしたりすることが出来る。

【0128】

また、図8と図17の回路では、スイッチ285、351の位置が異なる。しかし、し

きい値電圧を取得する動作の時に、トランジスタ274、275、286を電気的に接続

されない状態にすればよいので、それを満たすならば、スイッチ285、351は、どこ

に配置してもよい。

【0129】

続いて、図8に示す差動増幅回路を構成するトランジスタが逆の導電型を有する場合に

ついて、図9、図23を用いて説明する。

【0130】

図9、図23に示す差動増幅回路において、272、273がnチャネル型のトランジ

スタであり、274、275及び286がpチャネル型のトランジスタである。トランジ

スタ274のゲート電極が入力端子となっており、トランジスタ274のゲート電極には

入力電位Vin1が入力される。またトランジスタ275のゲート電極も入力端子となってお

り、トランジスタ275のゲート電極には入力電位Vin2が入力される。また、トランジス

タ275のソース領域の電位が出力電位Voutとなる。さらに、トランジスタ286のゲー

ト電極にはバイアス電位Vbが入力される。

【0131】

なお図9、図23に示す差動増幅回路においては、電源線291に電源電位Vddが印加

され、電源線271に接地電位Vssが印加されている点以外は、図8、図17に示す差動

増幅回路の構成、及びその動作と同じであるので、ここでは説明を省略する。

【0132】

また本実施の形態では、図8、9に示す電気回路を差動増幅回路として示したが、本発

明はこれに限定されず、入力電位Vin1と入力電位Vin2として入力する電圧を適宜変更して

、センスアンプなどの他の演算回路として用いることも出来る。

【0133】

次いで、本発明を適用したオペアンプについて、図10を用いて説明する。図10(A

)にはオペアンプの回路記号を示し、図10(B)には該オペアンプの回路構成を示す。

【0134】

なお、オペアンプの回路構成としては、さまざまなものがある。そこで、図10では、

もっとも簡単な場合として、差動増幅回路にソースフォロワ回路を組み合わせた場合につ

いて述べる。よって、回路構成は、図10に限定されない。

【0135】

図10(A)に示すオペアンプでは、入力電位Vin1及び入力電位Vin2と、出力電位Vout

との関係によって特性が定義される。より詳しくは、オペアンプは、入力電位Vin1及び入

力電位Vin2との差の電圧に対し、増幅度Aを掛けて出力電位Voutを出力する機能を有する

。

【0136】

図10(B)に示すオペアンプにおいて、トランジスタ274のゲート電極は、入力端

子となっており、該トランジスタ274のゲート電極には、入力電位Vin1が入力される。

またトランジスタ275のゲート電極も入力端子となっており、該トランジスタ275の

ゲート電極には入力電位Vin2が入力される。また、トランジスタ292のソース領域の電

位が出力電位Voutとなる。またトランジスタ286のゲート電極には、バイアス電位が入

力される。

【0137】

図10(B)に示す回路において、305で示す点線で囲んだ部分は、図8に示す差動

増幅回路と同じ構成である。そして、306で示す点線で囲んだ部分は、図1、2に示し

たソースフォロワ回路と同じであるので、図10(B)に示したオペアンプの詳しい構成

の説明は省略する。

【0138】

また図21には、トランジスタ299がpチャネル型である場合のオペアンプを示す。

図21(B)において、容量素子300の一方の端子は、スイッチ302、スイッチ27

8を介して、トランジスタ275のドレイン領域と接続されている。

【0139】

なお本実施の形態は、実施の形態1、2と任意に組み合わせることが可能である。

【0140】

(実施の形態4)

本実施の形態では、本発明を適用した光電変換素子を有する半導体装置(電気回路)に

おける画素及び駆動回路(バイアス回路)の構成とその動作について、図11、12を用

いて説明する。

【0141】

図11(A)に示す半導体装置(電気回路)は、基板701上に、複数の画素がマトリ

クス上に配置された画素部702を有し、画素部702の周辺には、信号線駆動回路70

3、第1〜第4の走査線駆動回路704〜707を有する。図11(A)に示す半導体装

置は、信号線駆動回路703と、4組の走査線駆動回路704〜707を有しているが、

本発明はこれに限定されず、信号線駆動回路と走査線駆動回路の数は画素の構成に応じて

任意に配置することが出来る。また、信号線駆動回路703と、第1〜第4の走査線駆動

回路704〜707には、FPC708を介して外部より信号が供給されている。しかし本

発明はこれに限定されず、画素部以外の電気回路は、ICなどを用いて外部から供給する

ようにしてもよい。

【0142】

最初に、第1の走査線駆動回路704及び第2の走査線駆動回路705の構成について

、図11(B)を用いて説明する。第3の走査線駆動回路706及び第4の走査線駆動回

路707は、図11(B)の図に準ずるので、図示は省略する。

【0143】

第1の走査線駆動回路704は、シフトレジスタ709、バッファ710を有する。第

2の走査線駆動回路705は、シフトレジスタ711、バッファ712を有する。動作を

簡単に説明すると、シフトレジスタ709、711は、クロック信号(G-CLK)、スター

トパルス(S-SP)及びクロック反転信号(G-CLKb)に従って、順次サンプリングパルスを

出力する。その後バッファ710、712で増幅されたサンプリングパルスは、走査線に

入力されて、1行ずつ選択状態にしていく。

【0144】

なおシフトレジスタ(709、711)とバッファ(710、712)との間にはレベ

ルシフタ回路を配置した構成にしてもよい。レベルシフタ回路を配置することによって、

電圧振幅を大きくすることが出来る。

【0145】

次いで、信号線駆動回路703の構成について、図11(C)を用いて説明する。

【0146】

信号線駆動回路703は、信号出力線用駆動回路715、サンプルホールド回路716

、バイアス回路714及び増幅回路717を有する。それぞれの回路が有する機能を簡単

に説明すると、バイアス回路714は、各画素の増幅用トランジスタと対になって、ソー

スフォロワ回路を形成する。サンプルホールド回路716は、信号を一時的に保存したり

、アナログ・デジタル変換を行ったり、雑音を低減したりする機能を有する。信号出力用

駆動回路715は、一時的に保存されていた信号を、順に出力していくための信号を出力

する機能を有する。そして、増幅回路717は、サンプルホールド回路716と信号出力

用駆動回路715により出力された信号を増幅する回路を有している。なお、増幅回路7

17は、信号を増幅する必要のない場合には配置しなくてもよい。

【0147】

そして、画素部702においてi列目j行目に配置される画素713の回路と、i列目

の周辺のバイアス回路714の構成とその動作について、図12を用いて説明する。

【0148】

最初に、i列目j行目に配置される画素713の回路と、i列目の周辺のバイアス回路

714の構成について説明する。

【0149】

図12に示す画素は、第1〜第4の走査線Ga(j)〜Gd(j)、信号線S(i)、

電源線V(i)を有する。また、nチャネル型のトランジスタ255、光電変換素子25

7、スイッチ250〜スイッチ254を有する。

【0150】

本実施の形態においては、トランジスタ255はnチャネル型としたが、本発明はこれ

に限定されず、pチャネル型でもよい。但し、トランジスタ255とトランジスタ260

により、ソースフォロワ回路を形成するので、両トランジスタは同じ極性であることが好

ましい。

【0151】

スイッチ250〜スイッチ254は、スイッチング機能を有する半導体素子であり、好

ましくはトランジスタが用いられる。スイッチ251及びスイッチ252は、第1の走査

線Ga(j)から入力される信号により、オン又はオフが制御される。スイッチ250は

、第2の走査線Gb(j)から入力される信号により、オン又はオフが制御される。スイ

ッチ253は、第3の走査線Gc(j)から入力される信号により、オン又はオフが制御

される。スイッチ254は、第4の走査線Gd(j)から入力される信号により、オン又

はオフが制御される。

【0152】

トランジスタ255のソース領域とドレイン領域は、一方は電源線V(i)に接続され

、他方はスイッチ250を介して信号線S(i)に接続されている。トランジスタ255

のゲート電極は、容量素子256の一方の端子に接続されている。また容量素子256の

他方の端子はスイッチ253を介して光電変換素子257の一方の端子に接続されている

。光電変換素子257の他方の端子は電源線258に接続されている。電源線258には

、接地電位Vssが印加される。容量素子256は、トランジスタ255のゲート・ソース

間電圧(しきい値電圧)を保持する役目を担う。

【0153】

バイアス回路714は、トランジスタ260、容量素子261、スイッチ259、スイ

ッチ262及びスイッチ263を有する。トランジスタ260のソース領域は電源線26

4に接続され、ドレイン領域は信号線S(i)に接続されている。電源線264には、接

地電位Vssが印加される。トランジスタ260のゲート電極は、容量素子261の一方の

端子に接続されている。容量素子261の他方の端子はスイッチ262を介して電源線2

64に接続されている。容量素子261は、トランジスタ260のゲート・ソース間電圧

(しきい値電圧)を保持する役目を担う。

【0154】

そして、図12において、719で示す点線で囲んだ部分と714で示す点線で囲んだ

部分とがソースフォロワ回路に相当する。

【0155】

次いで、i列目j行目に配置される画素713の回路と、i列目の周辺のバイアス回路

714の動作を簡単に説明する。

【0156】

まず、画素713においてスイッチ250〜スイッチ252、バイアス回路714にお

いてスイッチ259、262をオン状態にする。そして、それ以外のスイッチはオフにす

る。そうすると、電源線V(i)と、電源線264との間に電位差が生じる。その結果、

電源線V(i)から、スイッチ252、スイッチ251を介して、次いでスイッチ250

、スイッチ259を介して、さらにスイッチ262を介して電源線264の方向に流れる

。

【0157】

電流が流れ始めた瞬間には、容量素子256、261には電荷は保持されていない。そ

のため、トランジスタ255、260はオフである。

【0158】

そして徐々に容量素子256、261に電荷が蓄積されて、該容量素子256、261

の両電極間に電位差が生じ始める。容量素子256、261の両電極間の電位差が、トラ

ンジスタ255、260のしきい値電圧になると、該トランジスタ255、260はオン

となる。

【0159】

そして容量素子256、261では、定常状態になるまで、電荷の蓄積が続けられる。

【0160】

続いて、容量素子256、261において、電荷の蓄積が終了して定常状態になった後

、スイッチ250をオフにする。スイッチ251、252は引き続きオンである。またス

イッチ259、262も引き続きオンである。そして上記以外のスイッチは全てオフであ

る。

【0161】

そうすると、容量素子256に保持された正の電荷は、スイッチ252、トランジスタ

255、さらにスイッチ251を介して容量素子256の方向に流れていく。より詳しく

は、容量素子256に保持された正の電荷は、スイッチ252、トランジスタ255のソ

ース領域からドレイン領域を介して、さらにスイッチ251を介して容量素子256の方

向に流れていく。その結果、容量素子256の両電極間の電位差は減少していく。この動

作は、トランジスタ255がオフになるまで行われる。つまり、容量素子256に保持さ

れている電荷が、トランジスタ255のしきい値電圧と同じ値になるまで続けられる。

【0162】

また、容量素子261に保持された正の電荷は、スイッチ259、トランジスタ260

を介して電源線264の方向に流れていく。より詳しくは、容量素子261に保持された

正の電荷は、スイッチ259、トランジスタ260のソース領域からドレイン領域を介し

て、電源線264の方向に流れていく。この動作は、トランジスタ260がオフになるま

で行われる。つまり、容量素子261に保持されている電荷が、トランジスタ260のし

きい値電圧と同じ値になるまで続けられる。

【0163】

このとき、容量素子256にはトランジスタ255のしきい値電圧が保持された状態で

あり、また、容量素子261にはトランジスタ260のしきい値電圧が保持された状態で

ある。この状態において、画素713においては、スイッチ250、スイッチ253をオ

ンにして、それ以外のスイッチはオフとする。またバイアス回路714においては、スイ

ッチ263をオンとして、それ以外のスイッチはオフとする。

【0164】

そうすると、トランジスタ255のゲート電極には、容量素子256を介して、光電変

換素子257から信号が入力される。また同時に、トランジスタ260のゲート電極には

、容量素子261を介してバイアス電位Vbが入力される。

【0165】

このとき、トランジスタ255のゲート電極には、該トランジスタのしきい値電圧に加

えて、光電変換素子257からの信号が上乗せされた値が入力される。

また、トランジスタ260のゲート電極には、該トランジスタのしきい値電圧に加えて、

バイアス電位が上乗せされた値が入力される。つまり、トランジスタ255、260のゲ

ート電極に入力される信号は、該トランジスタ255、260のしきい値電圧に加えて、

該トランジスタのゲート電極に入力される信号となる。そのため、両トランジスタのしき

い値電圧のバラツキの影響を抑制することができる。

【0166】

そしてトランジスタ255のソース領域の電位が出力電位Voutとなり、該出力電位Vout

は、光電変換素子257により読み取られた信号として、スイッチ250を介して信号線

S(i)に出力される。

【0167】

次いで、スイッチ254をオンにして、それ以外のスイッチは全てオフにして、光電変

換素子257を初期化する。より詳しくは、光電変換素子257のnチャネル側端子の電

位が電源線258の電位と同じになるように、光電変換素子257が保持している電荷を

スイッチ254を介して、電源線V(i)の方向に流れるようにする。以後、上記の動作

を繰り返す。

【0168】

上記のような構成を有する本発明の半導体装置は、トランジスタのしきい値電圧のバラ

ツキの影響を抑制することができる。

【0169】

本発明は、実施の形態1〜実施の形態3と任意に組み合わせることが可能である。

【0170】

(実施の形態5)

本実施の形態では、本発明を適用した電気回路において、実施の形態2〜実施の形態4

とは異なる例について、図13〜図16を用いて説明する。

【0171】

図13(A)において、310は図1、2で示したソースフォロワ回路である。ソース

フォロワ回路310の回路構成と動作は、図1、2と同じであるので、本実施の形態では

説明は省略する。

【0172】

ソースフォロワ回路310の動作は、大別して設定動作と出力動作に分別できることは

上述した。なお設定動作とは、容量素子に所定の電荷の保持を行う動作であり、図1(A

)(B)及び図2(A)の動作に相当する。また出力動作とは、入力電位Vin及びバイア

ス電位Vbを入力して、出力電位Voutを取り出す動作のことであり、図2(B)の動作に相

当する。

【0173】

ソースフォロワ回路310において、端子aが入力端子に相当し、端子bが出力端子に

相当する。そして、スイッチ216、218、221は端子cから入力される信号により

制御される。スイッチ215、217、220及び222は端子dから入力される信号に

より制御される。スイッチ219は端子eから入力される信号により制御される。

【0174】

そして、ソースフォロワ回路310を有する電気回路を設計するときには、図13(B

)に示すように、少なくとも2つのソースフォロワ回路315、316を配置するとよい

。そしてソースフォロワ回路315、316のうち、一方は設定動作を行って、他方は出

力動作を行うようにするとよい。そうすると、同時に2つのことができ、動作に無駄がな

く、無駄な時間が必要なくなるので、電気回路の動作をより高速で行うことができる。

【0175】

例えば、信号線駆動回路にソースフォロワ回路を用いて設計するときには、信号線ごと

に少なくとも2個のソースフォロワ回路を配置するとよい。また走査線駆動回路にソース

フォロワ回路を用いて設計するときには、走査線ごとに少なくとも2個のソースフォロワ

回路を配置するとよい。また画素にソースフォロワ回路を用いて設計するときには、画素

ごとに少なくとも2つのソースフォロワ回路を配置するとよい。

【0176】

図13(B)において、311〜314はスイッチ機能を有する素子であり、好ましく

はトランジスタなどが用いられる。そして、スイッチ311、312がオンのときは、ス

イッチ313、314はオフとなる。またスイッチ311、312がオフのときには、ス

イッチ313、314はオンとなる。このようにして、2つのソースフォロワ回路315

、316のうち、一方は設定動作を行って、他方は出力動作を行うようにする。なお、ス

イッチ311〜スイッチ314を配置せずに、ソースフォロワ回路310が有するスイッ

チ216、218を制御することによって、2つのソースフォロワ回路315、316を

制御するようにしてもよい。

【0177】

また本実施の形態では、点線で囲んだ部分315、316は、ソースフォロワ回路に相

当するとしたが、本発明はこれに限定されず、図7〜図10などに示した差動増幅回路、

オペアンプなどを適用してもよい。

【0178】

そして本実施の形態では、信号線ごとに少なくとも2個のソースフォロワ回路を配置し

た信号線駆動回路の構成とその動作について、図14〜図16を用いて説明する。

【0179】

図14には信号線駆動回路を示しており、該信号線駆動回路は、シフトレジスタ321

、第1のラッチ回路322、第2のラッチ回路323、D/A変換回路324及び信号増

幅回路325を有する。

【0180】

なお、第1のラッチ回路322や第2のラッチ回路323が、アナログデータを保存で

きる回路である場合は、D/A変換回路324は省略できる場合が多い。また、信号線に

出力するデータが2値、つまり、デジタル量である場合は、D/A変換回路324は省略

できる場合が多い。また、D/A変換回路324には、ガンマ補正回路が内蔵されている

場合もある。このように、信号線駆動回路は、図17に限定されない。

【0181】

動作を簡単に説明すると、シフトレジスタ321は、フリップフロップ回路(FF)等

を複数列用いて構成され、クロック信号(S-CLK)、スタートパルス(S-SP)、クロ

ック反転信号(S-CLKb)が入力される、これらの信号のタイミングに従って、順次サ

ンプリングパルスが出力される。

【0182】

シフトレジスタ321より出力されたサンプリングパルスは、第1のラッチ回路322

に入力される。第1のラッチ回路322には、ビデオ信号が入力されており、サンプリン

グパルスが入力されるタイミングに従って、各列でビデオ信号を保持していく。

【0183】

第1のラッチ回路322において、最終列までビデオ信号の保持が完了すると、水平帰

線期間中に、第2のラッチ回路323にラッチパルス(Latch Pulse)

が入力され、第1のラッチ回路322に保持されていたビデオ信号は、一斉に第2のラッ

チ回路323に転送される。その後、第2のラッチ回路323に保持されたビデオ信号は

、1行分が同時に、D/A変換回路324へと入力される。そして、D/A変換回路32

4から入力される信号は信号増幅回路325へ入力される。

【0184】

第2のラッチ回路323に保持されたビデオ信号がD/A変換回路324に入力されて

いる間、シフトレジスタ321においては再びサンプリングパルスが出力される。以後、

この動作を繰り返す。

【0185】

そして、i列目から(i+2)列目の3本信号線の周辺の信号増幅回路325の構成を

図15を用いて説明する。

【0186】

信号増幅回路325は、列ごとに2つのソースフォロワ回路315、316を有する。

ソースフォロワ回路315、316は、それぞれ端子a〜端子eまでの5つの端子を有す

る。端子aはソースフォロワ回路315、316における入力端子に相当し、端子bはソ

ースフォロワ回路315、316における出力端子に相当する。また、端子cから入力さ

れる信号によりスイッチ216、218及び221が制御され、端子dから入力される信

号によりスイッチ215、217、220及び222が制御される。さらに端子eから入

力される信号によりスイッチ219が制御される。

【0187】

また図15に示す信号増幅回路325において、初期化用信号線326、設定用信号線

327及びしきい値用信号線328の3本の信号線と、ソースフォロワ回路315、31

6との間には、論理演算子が配置されている。329はインバータ、330はAND、3

31はOR、332はインバータ、333はAND、334はインバータ、335はOR

である。そして、端子c〜端子eには、設定用信号線327から出力される信号、又は上

記の論理演算子の出力端子から出力される信号のどちらかが入力される。

【0188】

次いで、初期化用信号線326、設定用信号線327及びしきい値用信号線328の3

本の信号線から出力される信号と、ソースフォロワ回路315における端子c〜端子eを

介して各スイッチに入力される信号を図16を用いて説明する。

【0189】

なお、端子c〜端子eを介して信号が入力されるスイッチは、Highの信号が入力される

とオンになり、Lowの信号が入力されるとオフになるとする。

【0190】

そして、初期化用信号線326、設定用信号線327及びしきい値用信号線328の3

本の信号線からは、図16に示すような信号が入力される。さらに、ソースフォロワ回路

315における端子cには、設定用信号線327から入力される信号がそのまま入力され

る。端子dにはAND333の出力端子から出力される信号が入力され、端子eにはOR

331の出力端子から出力される信号が入力される。そうすると、ソースフォロワ回路3

15では、設定動作と出力動作のどちらか一方の動作を行うように制御することが出来る

。

【0191】

またソースフォロワ回路316における端子cには、インバータ332の出力端子から

出力される信号が入力される。端子dには、AND330の出力端子から出力される信号

が入力され、端子eにはOR335の出力端子から出力される信号が入力される。そうす

ると、ソースフォロワ回路316では、設定動作と出力動作のどちらか一方の動作を行う

ように制御することが出来る。

【0192】

なお、信号線駆動回路の各信号線の先には、複数の画素が接続されている場合が多い。

当該画素は、信号線から入力される電圧によって、状態を変化させるものであることが多

い。例としては、液晶素子を有する画素や有機ELに代表される発光素子を有する画素な

どがあげられる。その他にも、さまざまな構成の画素を接続することが可能である。

【0193】

なお、本実施の形態は、実施の形態1〜実施の形態4と任意に組み合わせることが可能

である。

【0194】

(実施の形態6)

本発明の電気回路を用いて完成される電子機器として、ビデオカメラ、デジタルカメラ

、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、

音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュー

タ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機また

は電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(

DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)など

が挙げられる。それらの電子機器の具体例を図20に示す。

【0195】

図20(A)はディスプレイ(発光装置)であり、筐体3001、支持台3002、表示部3003

、スピーカー部3004、ビデオ入力端子3005等を含む。本発明は表示部3003を構成する電気

回路に用いることができる。また本発明により、図20(A)

に示す発光装置が完成される。発光装置は自発光型であるためバックライトが必要なく、

液晶ディスプレイよりも薄い表示部とすることができる。なお、発光装置は、パソコン用

、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

【0196】

図20(B)はデジタルスチルカメラであり、本体3101、表示部3102、受像部3103、操

作キー3104、外部接続ポート3105、シャッター3106等を含む。本発明は、表示部3102を構

成する電気回路に用いることができる。また本発明により、図20(B)に示すデジタル

スチルカメラが完成される。

【0197】

図20(C)はノート型パーソナルコンピュータであり、本体3201、筐体3202、表示部

3203、キーボード3204、外部接続ポート3205、ポインティングマウス3206等を含む。本発

明は、表示部3203を構成する電気回路に用いることができる。

また本発明により、図20(C)に示すノート型コンピュータが完成される。

【0198】

図20(D)はモバイルコンピュータであり、本体3301、表示部3302、スイッチ3303、

操作キー3304、赤外線ポート3305等を含む。本発明は、表示部3302を構成する電気回路に

用いることができる。また本発明により、図20(D)に示すモバイルコンピュータが完

成される。

【0199】

図20(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)

であり、本体3401、筐体3402、表示部A3403、表示部B3404、記録媒体(DVD等)読み

込み部3405、操作キー3406、スピーカー部3407等を含む。表示部A3403は主として画像情

報を表示し、表示部B3404は主として文字情報を表示するが、本発明は、表示部A、B34

03、3404を構成する電気回路に用いることができる。なお、記録媒体を備えた画像再生装

置には家庭用ゲーム機器なども含まれる。また本発明により、図20(E)に示すDVD

再生装置が完成される。

【0200】

図20(F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体

3501、表示部3502、アーム部3503を含む。本発明は、表示部3502を構成する電気回路に用

いることができる。また本発明により、図20(F)に示すゴーグル型ディスプレイが完

成される。

【0201】

図20(G)はビデオカメラであり、本体3601、表示部3602、筐体3603、外部接続ポー

ト3604、リモコン受信部3605、受像部3606、バッテリー3607、音声入力部3608、操作キー

3609等を含む。本発明は、表示部3602を構成する電気回路に用いることができる。また本

発明により、図20(G)に示すビデオカメラが完成される。

【0202】

図20(H)は携帯電話であり、本体3701、筐体3702、表示部3703、音声

入力部3704、音声出力部3705、操作キー3706、外部接続ポート3707、ア

ンテナ3708等を含む。本発明は、表示部3703を構成する電気回路に用いることが

できる。なお、表示部3703は黒色の背景に白色の文字を表示することで携帯電話の消

費電流を抑えることができる。また本発明により、図20(H)に示す携帯電話が完成さ

れる。

【0203】

なお、将来的に発光材料の発光輝度が高くなれば、出力した画像情報を含む光をレンズ

等で拡大投影してフロント型若しくはリア型のプロジェクターに用いることも可能となる

。

【0204】

また、上記電子機器はインターネットやCATV(ケーブルテレビ)などの電子通信回

線を通じて配信された情報を表示することが多くなり、特に動画情報を表示する機会が増

してきている。発光材料の応答速度は非常に高いため、発光装置は動画表示に好ましい。

【0205】

また、発光装置は発光している部分が電力を消費するため、発光部分が極力少なくなる

ように情報を表示することが望ましい。従って、携帯情報端末、特に携帯電話や音響再生

装置のような文字情報を主とする表示部に発光装置を用いる場合には、非発光部分を背景

として文字情報を発光部分で形成するように駆動することが望ましい。

【0206】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが

可能である。また本実施の形態の電子機器は、実施の形態1〜実施の形態5に示したいず

れの構成の電気回路を用いても良い。

【0207】

なお、TFTの特性バラツキの影響を抑制する効果を実現する本発明は、多結晶半導体

(ポリシリコン)を用いて画素及び駆動回路を同一基板上に形成する技術に大きく貢献し

、上記電子機器のうち、本技術を採用する携帯端末には特に優れた効果をもたらす。

【技術分野】

【0001】

本発明は、電気回路の技術に関する。より詳しくは、トランジスタを具備する電気回路

の技術に関する。

【背景技術】

【0002】

近年、携帯電話や携帯端末などに幅広く使用されている集積回路(IC)は、5mm四方

程度のシリコン基板上に、数十万〜数百万ものトランジスタや抵抗などを形成したもので

、装置の小型化及び高信頼化、装置の大量生産に重要な役割を果たしている。

【0003】

そして、集積回路(IC)等に用いられる電気回路を設計するときには、多くの場合にお

いて、振幅が小さい信号の電圧や電流を増幅する機能を有する増幅回路が設計される。増

幅回路は、ひずみの発生をなくし、電気回路を安定に働かせるためには不可欠な回路であ

るため、幅広く用いられている。

【0004】

ここで、増幅回路の一例として、ソースフォロワ回路の構成とその動作について説明す

る。最初に図5(A)にソースフォロワ回路の構成例を示し、定常状態における動作につ

いて説明する。次いで、図5(B)(C)を用いて、ソースフォロワ回路の動作点につい

て説明する。最後に、図6に図5(A)とは異なる構成のソースフォロワ回路の例を示し

、過渡状態における動作について説明する。

【0005】

まず図5(A)にソースフォロワ回路を用いて、定常状態における動作について説明す

る。

【0006】

図5(A)において、11はnチャネル型の増幅用トランジスタ、12はnチャネル型

のバイアス用トランジスタである。なお図5(A)に示す増幅用トランジスタ11及びバ

イアス用トランジスタ12はnチャネル型とするが、pチャネル型トランジスタを用いて

構成してもよい。またここでは簡単のため、増幅用トランジスタ11及びバイアス用トラ

ンジスタ12は、その特性及びサイズが同一であるとし、さらに電流特性も理想的なもの

であるとする。つまり、増幅用トランジスタ11及びバイアス用トランジスタ12のソー

ス・ドレイン間電圧が変化しても、飽和領域における電流値は変化しないと仮定する。

【0007】

また、増幅用トランジスタ11のドレイン領域は電源線13に接続され、ソース領域は

バイアス用トランジスタ12のドレイン領域に接続している。バイアス用トランジスタ1

2のソース領域は、電源線14に接続されている。

【0008】

バイアス用トランジスタ12のゲート電極には、バイアス電位Vbが印加される。そして

電源線13には電源電位Vddが印加され、電源線14には、接地電位Vss(=0V)が印加

される。

【0009】

図5(A)に示すソースフォロワ回路において、増幅用トランジスタ11のゲート電極

は、入力端子となっており、増幅用トランジスタ11のゲート電極には、入力電位Vinが

入力される。また増幅用トランジスタ11のソース領域が出力端子となっており、増幅用

トランジスタ11のソース領域の電位が、出力電位Voutとなる。バイアス用トランジスタ

12のゲート電極にはバイアス電位Vbが印加されており、該バイアス用トランジスタ12

が飽和領域で動作するときには、Ibで示す電流が流れるとする。このとき、増幅用トラ

ンジスタ11及びバイアス用トランジスタ12は直列に接続されているため、両トランジ

スタには同量の電流が流れる。つまり、バイアス用トランジスタ12に電流Ibが流れると

きには、増幅用トランジスタ11にも電流Ibが流れる。

【0010】

ここで、ソースフォロワ回路における出力電位Voutを求めてみる。出力電位Voutは、入

力電位Vinよりも増幅用トランジスタ11のゲート・ソース間電圧Vgs1の分だけ低い値と

なる。このとき、入力電位Vin、出力電位Vout及びゲート・ソース間電圧Vgs1の関係は、

以下の式(1)を満たす。

【0011】

Vout=Vin-Vgs1・・・(1)

【0012】

そして、増幅用トランジスタ11が飽和領域で動作している場合は、増幅用トランジス

タ11に電流Ibが流れるためには、増幅用トランジスタ11のゲート・ソース間電圧Vgs1

がバイアス電位Vbと等しいということが必要である。そうすると、以下の式(2)の式が

成立する。但し式(2)は、増幅用トランジスタ11及びバイアス用トランジスタ12が

飽和領域で動作するときにのみにおいて成立する。

【0013】

Vout=Vin-Vb・・・(2)

【0014】

次いで、増幅用トランジスタ11及びバイアス用トランジスタ12の電圧と電流の関係

を示した図5(B)(C)を用いて、ソースフォロワ回路の動作点について説明する。さ

らに詳しくは、増幅用トランジスタ11のゲート・ソース間電圧Vgs1と、バイアス用トラ

ンジスタ12のゲート・ソース間電圧Vgs2が同じ値の場合について、図5(B)を用いて

説明する。次いで、増幅用トランジスタ11のゲート・ソース間電圧Vgs1と、バイアス用

トランジスタ12のゲート・ソース間電圧Vgs2とが異なる値の場合であって、例えばバイ

アス用トランジスタ12が線形領域で動作している場合について、図5(C)を用いて説

明する。

【0015】

図5(B)において、点線21は増幅用トランジスタ11のゲート・ソース間電圧Vgs1

がVbであるときの電圧と電流の関係を示し、実線22はバイアス用トランジスタ12のゲ

ート・ソース間電圧Vgs2がVbであるときの電圧と電流の関係を示す。また図5(C)にお

いて、点線21は増幅用トランジスタ11のゲート・ソース間電圧Vgs1がVb’であるとき

の電圧と電流の関係を示し、実線22はバイアス用トランジスタ12のゲート・ソース間

電圧Vgs2がVbであるときの電圧と電流の関係を示す。

【0016】

図5(B)において、増幅用トランジスタ11のゲート・ソース間電圧Vgs1と、バイア

ス用トランジスタ12のゲート・ソース間電圧Vgs2が同じ値であり、さらにバイアス電位

Vbと、バイアス用トランジスタ12のゲート・ソース間電圧Vgs2は同じ値であるため、増

幅用トランジスタ11のゲート・ソース間電圧Vgs1は、バイアス電位Vbと同じ値である。

つまり、Vgs1=Vgs2=Vbとなり、図5(B)

に示すように、増幅用トランジスタ11及びバイアス用トランジスタ12は飽和領域で動

作している。このとき、入力電位Vinと出力電位Voutの関係は線形となる。

【0017】

一方、図5(C)において、増幅用トランジスタ11のゲート・ソース間電圧Vgs1は、

バイアス用トランジスタ12のゲート・ソース間電圧Vgs2とは異なる値である。そして、

バイアス用トランジスタ12のゲート・ソース間電圧Vgs2はバイアス電位Vbと同じ値であ

る。また、増幅用トランジスタ11のゲート・ソース間電圧Vgs1は、バイアス電位Vb'で

あるとする。つまり、Vgs2=Vb、Vgs1=Vb’となり、図5(C)で示すように、増幅用ト

ランジスタ11は飽和領域で動作しており、バイアス用トランジスタ12が線形領域で動

作している。このとき、入力電位Vin、出力電位Vout及びバイアス電位Vb'の関係は以下の

式(3)を満たす。

【0018】

Vout=Vin-Vb'・・・(3)

【0019】

バイアス用トランジスタ12が線形領域で動作するときに流れる電流をIb'とすると、I

b'<Ibとなる。つまり、Vb'<Vbとなって、入力電位Vinと電流Ib'の両者の値は小さくなる

。そうすると、バイアス電位Vb'も小さくなる。このとき入力電位Vinと出力電位Voutの関

係は、非線形となる。

【0020】

以上をまとめると、定常状態におけるソースフォロワ回路において、出力電位Voutの振

幅を大きくするためには、バイアス電位Vbを小さくすることが好ましい。これは以下の2

つの理由による。

【0021】

1つ目の理由は、式(2)に示すように、バイアス電位Vbが小さいと、出力電位Voutを

大きくすることが出来るからである。2つ目の理由は、バイアス電位Vbの値が大きい場合

には、入力電位Vinを小さくすると、バイアス用トランジスタ12が線形領域で動作しや

すくなってしまうからである。バイアス用トランジスタ12が線形領域で動作すると、入

力電位Vinと出力電位Voutの関係は、非線形となりやすい。

【0022】

なおバイアス用トランジスタ12は、導通状態であることが必要であるため、バイアス

電位Vbの値は、バイアス用トランジスタ12のしきい値電圧よりも大きい値にする必要が

ある。

【0023】

これまでは、ソースフォロワ回路の定常状態での動作について説明してきたが、続いて

、ソースフォロワ回路の過渡状態での動作について、図6を用いて説明する。

【0024】

図6に示すソースフォロワ回路は、図5(A)の回路に容量素子15が追加して設計さ

れた構成である。容量素子15の一方の端子は増幅用トランジスタ11のソース領域に接

続され、他方の端子は電源線16に接続されている。電源線16には、接地電位Vssが印

加されている。

【0025】

容量素子15の両電極間の電位差は、ソースフォロワ回路の出力電位Voutと同一となる

。ここでは、図6(A)を用いてVout<Vin-Vbの場合の動作について説明し、次いで図6

(B)を用いてVout>Vin-Vbの場合の動作について説明する。

【0026】

まず、図6(A)を用いてVout<Vin-Vbの場合のソースフォロワ回路の過渡状態におけ

る動作について説明する。

【0027】

図6(A)において、t=0のときには、増幅用トランジスタ11のゲート・ソース間電

圧Vgs1の値は、バイアス用トランジスタ12のゲート・ソース間電圧Vgs2の値よりも大き

い。そのため、増幅用トランジスタ11には、大きな電流が流れて、容量素子15には急

速に電荷が保持される。そうすると、出力電位Voutは大きくなり、増幅用トランジスタ1

1のゲート・ソース間電圧Vgs1の値は減少する。

【0028】

そして時間の経過に伴い(t=t1、t1>0)、増幅用トランジスタ11のゲート・ソース間

電圧Vgs1がバイアス電位Vbに等しくなると定常状態になる。このとき、出力電位Vout、入

力電位Vin及びバイアス電位Vbの関係は、上記の式(2)を満たす。

【0029】

以上をまとめると、Vout<Vin-Vbの場合には、増幅用トランジスタ11のゲート・ソー

ス間電圧Vgs1の値が、バイアス電位Vbよりも大きいため、増幅用トランジスタ11には

大きな電流が流れて、容量素子15に急速に電荷が保持される。そのため、容量素子15

が所定の電荷の保持を行う時間、言い換えると容量素子15に対する信号の書き込みに要

する時間は短くてすむ。

【0030】

次いで、図6(B)を用いてVout>Vin-Vbの場合のソースフォロワ回路の過渡状態にお

ける動作について説明する。

【0031】

図6(B)において、t=0のときには、増幅用トランジスタ11のゲート・ソース間電

圧Vgs1は、該増幅用トランジスタ11のしきい値電圧よりも小さい値である。そのため、

増幅用トランジスタ11は非導通状態にある。そして容量素子15に蓄積されていた電荷

は、バイアス用トランジスタ12を介して接地電位Vssの方向に流れていき、最終的には

放電される。このとき、バイアス用トランジスタ12のゲート・ソース間電圧Vgs2は、バ

イアス電位Vbと同じ値であるので、バイアス用トランジスタ12を流れる電流はIbとなる

。

【0032】

そして時間の経過に伴い(t=t1、t1>0)、出力電位Voutが小さくなり、増幅用トランジ

スタ11のゲート・ソース間電圧Vgs1が大きくなる。そして増幅用トランジスタ11のゲ

ート・ソース間電圧Vgs1がバイアス電位Vbに等しくなると、定常状態となる。このとき、

出力電位Vout、入力電位Vin及びバイアス電位Vbの関係は、上記の式(2)を満たす。な

お定常状態では、出力電位Voutは一定の値を保っており、容量素子15に電荷は流れない

。そして、増幅用トランジスタ11及びバイアス用トランジスタ12には、電流Ibが流れ

る。

【0033】

以上をまとめると、Vout>Vin-Vbの場合には、容量素子15が所定の電荷の保持を行う

時間、言い換えると容量素子15に対する信号の書き込み時間は、バイアス用トランジス

タ12を流れる電流Ibに依存する。そして、電流Ibはバイアス電位Vbの大きさに依存する

。従って、電流Ibを大きくして、容量素子15に対する信号の書き込み時間を短くするた

めには、バイアス電位Vbを大きくする必要が生ずる。

【0034】

なおトランジスタのしきい値電圧のバラツキを補正する方法として、信号が入力された

回路の出力によりバラツキをみて、その後、そのバラツキを入力するフィードバックさせ

て補正するという方法がある(例えば、非特許文献1参照。)。

【先行技術文献】

【非特許文献】

【0035】

【非特許文献1】H.Sekine et al,「Amplifier Compensation Method for a Poly-Si TFT LCLV with an Integrated Data-Driver」,IDRC'97,p.45-48

【発明の概要】

【発明が解決しようとする課題】

【0036】

上述したソースフォロワ回路の動作は、増幅用トランジスタ11及びバイアス用トラン

ジスタ12の特性が同じであると仮定した上で行われるものである。しかし、両トランジ

スタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネ

ル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが

生じてしまう。

【0037】

例えば図5(A)において、増幅用トランジスタ11のしきい値電圧が3Vであり、バ

イアス用トランジスタ12のしきい値電圧が4Vとして、1Vのバラツキが生じていたと

する。そうすると、電流Ibを流すためには、増幅用トランジスタ11のゲート・ソース

間電圧Vgs1には、バイアス用トランジスタ12のゲート・ソース間電圧Vgs2よりも1V低

い電圧を加える必要が生ずる。つまりVgs1=Vb-1となる。そうすると、Vout=Vin-Vgs1=Vin

-Vb+1となってしまう。つまり、増幅用トランジスタ11及びバイアス用トランジスタ1

2のしきい値電圧に1Vでもバラツキが生じていると、出力電位Voutにもバラツキが生じ

てしまう。

【0038】

本発明は上記の問題点を鑑みてなされたものであり、トランジスタの特性バラツキの影

響を抑制した電気回路を提供することを課題とする。さらに詳しくは、電流を増幅する機

能を有する電気回路において、トランジスタのしきい値電圧のバラツキの影響を抑制して

、所望の電圧を供給することができる電気回路を提供することを課題とする。

【課題を解決するための手段】

【0039】

本発明は、上記の問題点を解決するために、以下に示す構成の電気回路を用いる。

【0040】

図3(A)に示す電気回路は、スイッチング機能を有するスイッチング素子31、32

(以下、sw31、sw32と表記)、nチャネル型のトランジスタ33、容量素子34

により構成される。トランジスタ33のソース領域は電源線36に接続され、ドレイン領

域はsw31を介して電源線35に接続されている。

トランジスタ33のゲート電極は容量素子34の一方の端子に接続されている。

また、容量素子34の他方の端子は電源線37に接続されている。容量素子34は、トラ

ンジスタ33のゲート・ソース間電圧Vgsを保持する役目を担う。また、電源線35には

電源電位Vddが印加され、電源線36、37には接地電位Vssが印加される。

【0041】

図3(A)〜図3(C)においては、トランジスタ33はnチャネル型とするが、これ

に限定されず、pチャネル型で構成することも可能である。また図3(C)には、図3(

A)と同じ回路素子を有し、且つ接続構成が異なる電気回路を示す。図3(C)に示す電

気回路の動作は、後述する図3(A)に示す回路の動作に準ずるので、ここでは省略する

。

【0042】

そして図3(A)に示す電気回路では、容量素子34の両電極間の電位差が、トランジ

スタ33のしきい値電圧と同じ値となるように、該容量素子34に電荷が保持される。こ

の動作について、以下に説明する。

【0043】

図3(A)において、sw31及びsw32はオンである。この状態において、電源線

35には電源電位Vddが印加され、電源線36、37には接地電位Vssが印加されているた

め、電源線35と、電源線36及び電源線37との間には電位差が生じる。その結果、電

源線35から、sw31及びsw32を介して、トランジスタ33及び容量素子34の方

向に向かって、電流Idsが流れる。このとき、電流Idsは、I1とI2に分かれて流れる。な

お電流Idsは、Ids=I1+I2を満たす。

【0044】

電源線35から、電源線36及び電源線37の方向に電流が流れ始めた瞬間には、容量

素子34には電荷は保持されていない。そのため、トランジスタ33はオフである。よっ

て、I2=0であり、Ids=I1となる。

【0045】

そして徐々に容量素子34に電荷が蓄積されて、容量素子34の両電極間に電位差が生

じ始める。両電極間の電位差がVthになると、トランジスタ33がオンして、I2>0とな

る、上述したようにIds=I1+I2となるので、I1は次第に減少するが、依然電流は流れてい

る。

【0046】

そして容量素子34では、該容量素子34の両電極間の電位差がVddになるまで、電荷

の蓄積が続けられる。容量素子34において、電荷の蓄積が終了すると(図3(D)(E

)、A点)、電流I2は流れなくなり、さらにトランジスタ33はオンであるので、Ids=I

1となる。

【0047】

続いて、図3(B)に示すように、sw31をオフにする。sw32は引き続きオンで

ある。そうすると、容量素子34に保持された電荷は、sw32を介して、トランジスタ

33の方向に流れていく。より詳しくは、容量素子34に保持された電荷は、トランジス

タ33のドレイン領域からソース領域を介して、電源線36の方向に流れていって放電す

る。この動作は、トランジスタ33がオフになるまで行われる。つまり、容量素子34に

保持されている電荷が、トランジスタ33のしきい値電圧と同じ値になるまで続けられる

(図3(D)(E)、B点)。

【0048】

このようにすると、容量素子34の両電極間の電位差が、トランジスタ33のしきい値

電圧と同じ値となるように電荷が保持される。

【0049】

上述したように、本発明は、容量素子の両電極がある特定のトランジスタのゲート・ソ

ース間電圧を保持できるように配置した電気回路を提供する。そして本発明は、容量素子

の両電極間の電位差が、ある特定のトランジスタのしきい値電圧となるように設定できる

機能を有する電気回路を提供する。

【0050】

さらに本発明では、容量素子に保持されているある特定のトランジスタのゲート・ソー

ス間電圧をそのまま保存して、且つ該トランジスタのゲート電極に信号電圧(ビデオ信号

の電圧など)を入力する。そうすると、前記トランジスタのゲート電極には、容量素子に

保持されているゲート・ソース間電圧に加えて、前記信号電圧を上乗せした電圧が入力さ

れる。その結果、トランジスタのゲート電極には、該トランジスタのしきい値電圧と信号

電圧とを足した値が入力される。つまり本発明では、トランジスタ間にしきい値電圧にバ

ラツキが生じていても、信号電圧が入力されるトランジスタでは、常に該トランジスタの

しきい値電圧と信号電圧を足した値が入力されることになる。そのため、トランジスタ間

のしきい値電圧のバラツキの影響を抑制した電気回路を提供することが出来る。

【0051】

なお容量素子に保持されているゲート・ソース間電圧に加えて、信号電圧が上乗せされ

る仕組みは電荷保存則により説明される。電荷保存則とは、正電気量と負電気量の代数的

な和の全電気量は一定であるという事実を示す。ここで電荷保存則について、図4を用い

て説明する。

【0052】

図4において、26は電源(定電圧源)であり、27は容量素子である。電源26と容

量素子27はsw28を介して接続されている。電源26は電源線29に接続され、容量

素子27は電源線30に接続されている。

【0053】

図4(A)において、sw28がオンであり、電源線29及び電源線30には0Vが印

加されている。そして電源26には電圧Vxが印加されており、この状態において、sw

28は導通状態である。その結果、容量素子27の両電極間の電位差がVxとなるように

、該容量素子27に電荷が保持される。

【0054】

次いで、図4(B)において、sw28をオフにする。このとき、容量素子27に保持

されている電荷は、電荷保存則によって引き続き保持される。

【0055】

そして、図4(C)において、容量素子27の一方の端子に接続された電源線30に電

圧Vyを印加する。sw28はオフであり、また電源線29には0Vが印加されている。

このとき、容量素子27に保持されている電荷は保存されて、電源線30に印加される電

圧Vyが上乗せされる。つまり、図4(C)に示すように、容量素子27の一方の端子の

電位は(Vy+Vx)となる。

【0056】

このように、容量素子27では、保持されている電荷はそのまま保存されて、該容量素

子27の一方の端子の電位が上昇すると、それに合わせて、他方の端子の電位が上昇する

。

【0057】

なお本発明では、どのような材料を用いたトランジスタ、どのような手段、製造方法を

経たトランジスタを用いてもよく、またどのようなタイプのトランジスタを用いてもよい

。例えば、薄膜トランジスタ(TFT)を用いてもよい。TFTとしては、半導体層が非

晶質(アモルファス)、多結晶(ポリクリスタル、ポリシリコン)、単結晶のいずれを用

いてもよい。その他のトランジスタとして、単結晶基板において作られたトランジスタで

もよいし、SOI基板において作られたトランジスタでもよい。また、有機物やカーボン

ナノチューブで形成されたトランジスタでもよい。さらに、MOS型トランジスタでもよ

いし、バイポーラ型トランジスタでもよい。

【発明の効果】

【0058】

本発明は、容量素子の両電極がある特定のトランジスタのゲート・ソース間電圧を保持

できるように配置した電気回路を提供する。そして本発明は、容量素子の両電極間の電位

差が、ある特定のトランジスタのしきい値電圧となるように設定できる機能を有する電気

回路を提供する。

【0059】

さらに本発明では、容量素子に保持されているある特定のトランジスタのゲート・ソー

ス間電圧をそのまま保存して、且つ該トランジスタのゲート電極に信号電圧(ビデオ信号

の電圧など)を入力する。そうすると、前記トランジスタのゲート電極には、容量素子に

保持されているゲート・ソース間電圧に加えて、前記信号電圧を上乗せした電圧が入力さ

れる。その結果、トランジスタのゲート電極には、該トランジスタのしきい値電圧と信号

電圧とを足した値が入力される。つまり本発明では、トランジスタ間にしきい値電圧にバ

ラツキが生じていても、信号電圧が入力されるトランジスタでは、常に該トランジスタの

しきい値電圧と信号電圧を足した値が入力されることになる。そのため、トランジスタ間

のしきい値電圧のバラツキの影響を抑制した電気回路を提供することが出来る。

【図面の簡単な説明】

【0060】

【図1】本発明のソースフォロワ回路の動作を説明する図。

【図2】本発明のソースフォロワ回路の動作を説明する図。

【図3】本発明の電気回路の構成とその動作を説明する図。

【図4】電荷保存則を説明する図。

【図5】ソースフォロワ回路の動作を説明する図。

【図6】ソースフォロワ回路の動作を説明する図。

【図7】本発明のソースフォロワ回路の動作を説明する図。

【図8】本発明の差動増幅回路の構成を説明する図。

【図9】本発明の差動増幅回路の構成を説明する図。

【図10】本発明のオペアンプの構成を説明する図。

【図11】本発明の半導体装置を示す図。

【図12】本発明の半導体装置の画素とバイアス用回路を示す図。

【図13】本発明の電気回路の構成を説明する図。

【図14】本発明の信号線駆動回路の図。

【図15】本発明の信号線駆動回路の図。

【図16】本発明の信号線駆動回路の動作を説明する図。

【図17】本発明のオペアンプを示す図。

【図18】本発明のオペアンプを示す図。

【図19】本発明のオペアンプを示す図。

【図20】本発明が適用される電気機器の図。

【図21】本発明のオペアンプの構成を説明する図。

【図22】本発明のオペアンプを示す図。

【図23】本発明のオペアンプを示す図。

【発明を実施するための形態】

【0061】

(実施の形態1)

本実施の形態では、本発明の電気回路の一例として、ソースフォロワ回路を示し、その

構成と動作について図1、2を用いて説明する。

【0062】

図1、2において、211はnチャネル型の増幅用トランジスタであり、212はnチ

ャネル型のバイアス用トランジスタである。213及び214は容量素子である。また、

215〜222はスイッチング機能を有する素子であり、好ましくはトランジスタやアナ

ログスイッチなどの半導体素子が用いられる。223及び224は電源線であり、電源線

223には電源電位Vddが印加され、電源線224には接地電位Vssが印加される。

【0063】

なお本実施の形態では、増幅用トランジスタ211及びバイアス用トランジスタ212

がnチャネル型の場合を示すが、本発明はこれに限定されず、両トランジスタがpチャネ

ル型であってもよい。また、両トランジスタの極性が異なっていてもよい。

【0064】

両トランジスタの極性が異なっている場合は、プッシュプル回路を構成していることに

なるので、両トランジスタとも、増幅用トランジスタとして機能する。

よって、両トランジスタに、信号が入力される。

【0065】

増幅用トランジスタ211のドレイン領域は電源線223に接続され、ソース領域はス

イッチ217〜スイッチ219に接続されている。増幅用トランジスタ211のゲート電

極は容量素子213の一方の端子に接続されている。容量素子213の他方の端子は、ス

イッチ217を介してトランジスタ211のソース領域に接続されている。容量素子21

3は、増幅用トランジスタ211のゲート・ソース間電圧(しきい値電圧)を保持する役

目を担う。なお以下には増幅用トランジスタ211は、トランジスタ211と表記する。

【0066】

バイアス用トランジスタ212のソース領域は電源線224に接続され、ドレイン領域

はスイッチ219、220に接続されている。バイアス用トランジスタ212のゲート電

極は容量素子214の一方の端子に接続されている。容量素子214の他方の端子は、ス

イッチ222を介してバイアス用トランジスタ212のソース領域に接続されている。容

量素子214は、バイアス用トランジスタ212のゲート・ソース間電圧(しきい値電圧

)を保持する役目を担う。なお以下にはバイアス用トランジスタ212は、トランジスタ

212と表記する。

【0067】

スイッチ215〜スイッチ222は、入力される信号によって、導通又は非導通(オン

又はオフ)が制御される。しかし、図1、2においては、説明を簡単にするために、スイ

ッチ215〜スイッチ222に信号を入力する信号線等の図示は省略する。

【0068】

図1、2に示すソースフォロワ回路において、スイッチ216の一方の端子が入力端子

となる。前記入力端子を介して、入力電位Vin(信号電圧)は、スイッチ216及び容量

素子213を介して、トランジスタ211のゲート電極に入力される。またスイッチ22

1の一方の端子からはバイアス電位Vbが入力される。

バイアス電位Vbは、スイッチ221及び容量素子214を介して、トランジスタ212の

ゲート電極に入力される。また、スイッチ218の一方の端子が出力端子となっており、

トランジスタ211のソース領域の電位が出力電位Voutとなる。

【0069】

なおスイッチ218は、トランジスタ211のソース領域と接続され、且つスイッチ2

19を介してトランジスタ212のドレイン領域とに接続されているが、本発明はこれに

限定されない。スイッチ218は、トランジスタ212のドレイン領域と接続され、且つ

スイッチ219を介してトランジスタ211のソース領域とに接続されていてもよい。

【0070】

但しスイッチ218は、トランジスタ211のソース領域と接続され、且つスイッチ2

19を介してトランジスタ212のドレイン領域とに接続されている方が好ましい。これ

は、スイッチ218が、トランジスタ212のドレイン領域と接続され、且つスイッチ2

19を介してトランジスタ211のソース領域とに接続されている場合には、スイッチ2

19にオン抵抗があると、出力電位Voutがその影響を受けてしまうために、出力電位Vout

が低下してしまうからである。

【0071】

次いで、図1、2に示したソースフォロワ回路の動作について説明する。

【0072】

図1(A)において、スイッチ215、スイッチ217、スイッチ219、スイッチ2

20及びスイッチ222をオンにする。そして上記以外のスイッチはオフにする。この状

態において、電源線223にはVddが印加され、電源線224にはVssが印加されているた

め、電源線223と電源線224の間には電位差が生じる。その結果、電源線223から

電源線224の方向に向かって電流が流れる。

【0073】

電源線223から、電源線224の方向に電流が流れ始めた瞬間には、容量素子213

及び容量素子214には電荷は保持されていない。そのため、トランジスタ211及びト

ランジスタ212はオフである。電流は、電源線223からスイッチ215、スイッチ2

17を介し、次いでスイッチ219を介し、さらにスイッチ220、スイッチ222を介

して、電源線224の方向に流れていく。

【0074】

そして徐々に容量素子213、214に電荷が蓄積されて、該容量素子213、214

の両電極間に電位差が生じ始める。容量素子213の両電極間の電位差がトランジスタ2

11のしきい値電圧Vth1になると、トランジスタ211はオンする。同様に、容量素子2

14の両電極間の電位差がトランジスタ212のしきい値電圧Vth2になると、トランジス

タ212はオンする。

【0075】

容量素子213、214では、定常状態になるまで、電荷の蓄積が続けられる。

【0076】

続いて、図1(B)に示すように、容量素子213、214において電荷の蓄積が終了

して定常状態になると、スイッチ219をオンからオフにして、それ以外のスイッチは図

1(A)の状態を維持する。

【0077】

そうすると、容量素子213に保持された正の電荷は、スイッチ215を介して、トラ

ンジスタ211の方向に流れていく。より詳しくは、容量素子213に保持された正の電

荷は、スイッチ215を介してトランジスタ211のドレイン領域からソース領域を介し

て、さらにスイッチ217を介して容量素子213の方向に流れていく。その結果、容量

素子213の両電極間の電位差は減少していく。この動作は、トランジスタ211がオフ

になるまで行われる。つまり、容量素子213に保持されている電荷が、トランジスタ2

11のしきい値電圧Vth1と同じ値になるまで続けられる。

【0078】

また、容量素子214に保持された正の電荷は、スイッチ220を介して、トランジス

タ212の方向に流れていく。より詳しくは、容量素子214に保持された正の電荷は、

スイッチ220を介してトランジスタ212のドレイン領域からソース領域を介して、電

源線224の方向に流れていく。この動作は、トランジスタ212がオフになるまで行わ

れる。つまり、容量素子214に保持されている電荷が、トランジスタ212のしきい値

電圧Vth2と同じ値になるまで続けられる。

【0079】

このようにすると、容量素子213の両電極間の電位差がトランジスタ211のしきい

値電圧Vth1と同じ値になる。また、容量素子214の両電極間の電位差がトランジスタ2

12のしきい値電圧Vth2と同じ値になる。

【0080】

このように、容量素子213の両電極間の電位差がトランジスタ211のしきい値電圧

Vth1と同じ値になり、且つ容量素子214の両電極間の電位差がトランジスタ212のし

きい値電圧Vth2と同じ値になったら、スイッチ215、スイッチ217、スイッチ220

及びスイッチ222をオフにする(図2(A))。つまりこのときには、全てのスイッチ

215〜スイッチ222はオフである。

【0081】

なおスイッチ215、スイッチ217、スイッチ220及びスイッチ222は、容量素

子213、214の両電極間の電位差がトランジスタ211、212のしきい値電圧Vth1

、Vth2と同じ値になってからオフにすることが望ましい。しかし、本発明はこれに限定さ

れない。トランジスタ211、212のバラツキが小さい場合は、電気回路の動作では特

に問題とはならないため、容量素子213、214の両電極間の電位差がトランジスタ2

11、212のしきい値電圧Vth1、Vth2と近い値のときに、スイッチ215、スイッチ2

17、スイッチ220及びスイッチ222をオフにしてもよく、そのタイミングは特に限

定されない。

【0082】

続いて、スイッチ216、スイッチ218、スイッチ219及びスイッチ221をオン

にする(図2(B))。上記以外のスイッチはオフが維持される。このとき入力端子から

スイッチ216及び容量素子213を介して、入力電位Vinがトランジスタ211のゲー

ト電極に加わる。このとき、電荷保存則により、トランジスタ211のゲート電極には、

該トランジスタ211のしきい値電圧Vth1に加えて、入力電位Vinが上乗せされた値(Vth

1+Vin)が加えられる。また、トランジスタ212のゲート電極には、該トランジスタ2

12のしきい値電圧Vth2に加えて、入力電位Vbが上乗せされた値(Vth2+Vb)が加えられ

る。

【0083】

なおトランジスタが、飽和領域で動作するときには、以下の式(4)が成立する。Ids

はトランジスタのチャネル形成領域を流れる電流量であり、Vgsはトランジスタのゲート

・ソース間電圧である。またVthはトランジスタのしきい値電圧である。

【0084】

Ids∝(Vgs−Vth)2・・(4)

【0085】

上記の式(4)において、Vk=Vgs-Vthとすると、以下の式(5)が成立する。

【0086】

Ids∝Vk2・・(5)

【0087】

式(5)より、Idsは、VgsからVthの値を引いた値であるVkの2乗に比例していること

がわかる。

【0088】

ここで、トランジスタ211、212に上記の式(4)(5)を適用して、出力電位Vo

utを求める。なお本実施の形態では、トランジスタ211、212のゲート幅(W)、ゲ

ート長(L)にはバラツキが生じておらず、同一であるとする。

一方、トランジスタ211、212のしきい値電圧Vth1、Vth2にはバラツキが生じている

とする。

【0089】

トランジスタ212のゲート電極に加えられた電圧をVa2とすると、Va2=Vb+Vth2が成立

する。さらに、トランジスタ212のゲート電極に加えられた電圧Va2からしきい値電圧V

th2を引いた値をVk2とすると、以下の式(6)が成立する。

【0090】

Vk2=Va2-Vth2=(Vb+Vth2)-Vth2=Vb・・(6)

【0091】

そして、トランジスタ211のゲート電極に加えられた電圧をVa1とすると、以下の式

(7)が成立する。

【0092】

Va1=Vin+Vth1・・(7)

【0093】

さらに、トランジスタ211のゲート・ソース間電圧Vgs1からしきい値電圧Vth1を引い

た値をVk1とすると、以下の式(8)が成立する。

【0094】

Vk1=Vgs1-Vth1・・(8)

【0095】

ここで、トランジスタ211、212には同量の電流が流れるため、以下の式(9)が

成立する。

【0096】

Vk1=Vk2=Vb・・(9)

【0097】

そして、出力電位Voutは、トランジスタ211のソース領域の電位であることから、以

下の式(10)が成立する。

【0098】

Vout=Va1-Vgs1=(Vin+Vth1)-(Vb+Vth1)=Vin-Vb・・・(10)

【0099】

式(10)に示すように、出力電位Voutは、入力電位Vinからバイアス電位Vbを引いた

値になっており、しきい値電圧には依存していない。そのため、トランジスタ211、2

12のしきい値電圧にバラツキが生じていても、出力電位Voutに対する影響を抑制するこ

とが出来る。

【0100】

なお上記の説明では、トランジスタ211、212のゲート幅(W)、ゲート長(L)は

バラツキが生じておらず、同一であるとしたが、両トランジスタのゲート幅(W)、ゲー

ト長(L)の大きさは特に限定されない。

【0101】

また図7(C)には、バイアス用トランジスタ212を配置していない場合のソースフ

ォロワ回路を示す。図7(C)に示すソースフォロワ回路の動作は、スイッチ219が出

力動作のときにオフになる以外は、上述した図1、2の動作と同じであるので、本実施の

形態では説明を省略する。

【0102】

なお本明細書では、容量素子に所定の電荷の保持を行う動作を設定動作と呼ぶ。本実施

の形態では、図1(A)(B)及び図2(A)の動作が設定動作に相当する。また、入力

電位Vin及びバイアス電位Vbを入力して、出力電位Voutを取り出す動作を出力動作とよぶ

。本実施の形態では、図2(B)の動作が出力動作に相当する。

【0103】

このように本発明では、トランジスタ間にしきい値電圧にバラツキが生じていても、入

力電位Vinやバイアス電位Vbなどの信号電圧が入力されるトランジスタでは、常に該トラ

ンジスタのしきい値電圧と信号電圧を足した値が入力されることになる。そのため、トラ

ンジスタ間のしきい値電圧のバラツキの影響を抑制した電気回路を提供することが出来る

。

【0104】

(実施の形態2)

図1、2に示したソースフォロワ回路では、nチャネル型の増幅用トランジスタ211

と、nチャネル型のバイアス用トランジスタ212により構成した場合を示した。次いで

本実施の形態では、pチャネル型の増幅用トランジスタ211と、pチャネル型のバイア

ス用トランジスタ212により構成されたソースフォロワ回路を図7に示し、その構成に

ついて説明する。なお図7に示したソースフォロワ回路の動作は、実施の形態1の動作に

準ずるので、本実施の形態では説明は省略する。

【0105】

図7において、231はpチャネル型のバイアス用トランジスタであり、232はpチ

ャネル型の増幅用トランジスタである。233及び234は容量素子である。また、23

5〜242はスイッチング機能を有する素子であり、好ましくはトランジスタやアナログ

スイッチなどの半導体素子が用いられる。243及び244は電源線であり、電源線24

3には電源電位Vddが印加され、電源線244には接地電位Vssが印加される。

【0106】

なお本実施の形態では、増幅用トランジスタ232及びバイアス用トランジスタ23

1がpチャネル型の場合を示すが、両トランジスタの極性が異なっていて、プッシュプル

回路のようになっていてもよい。

【0107】

バイアス用トランジスタ231のソース領域は電源線243に接続され、ドレイン領域

はスイッチ235、239に接続されている。バイアス用トランジスタ231のゲート電

極は容量素子233の一方の端子に接続されている。容量素子233の他方の端子は、ス

イッチ237を介して電源線243に接続されている。容量素子233は、バイアス用ト

ランジスタ231のゲート・ソース間電圧(しきい値電圧)を保持する役目を担う。

【0108】

増幅用トランジスタ232のドレイン領域は電源線244に接続され、ソース領域はス

イッチ238、239、242に接続されている。増幅用トランジスタ232のゲート電

極は容量素子234の一方の端子に接続されている。容量素子234の他方の端子は、ス

イッチ242を介して増幅用トランジスタ232のソース領域に接続されている。容量素

子234は、増幅用トランジスタ232のゲート・ソース間電圧(しきい値電圧)を保持

する役目を担う。

【0109】

スイッチ235〜スイッチ242は、入力される信号によって、導通又は非導通(オン

又はオフ)が制御される。しかし、図7においては、説明を簡単にするために、スイッチ

235〜スイッチ242に信号を入力する信号線等の図示は省略する。

【0110】

なおスイッチ238は、増幅用トランジスタ232のソース領域と接続され、且つスイ

ッチ239を介してバイアス用トランジスタ231のドレイン領域とに接続されているが

、本発明はこれに限定されない。スイッチ238は、バイアス用トランジスタ231のド

レイン領域と接続され、且つスイッチ239を介して増幅用トランジスタ232のソース

領域とに接続されていてもよい。

【0111】

但しスイッチ238は、増幅用トランジスタ232のソース領域と接続され、且つスイ

ッチ239を介してバイアス用トランジスタ231のドレイン領域とに接続されている方

が好ましい。これは、スイッチ238が、バイアス用トランジスタ231のドレイン領域

と接続され、且つスイッチ239を介して増幅用トランジスタ232のソース領域とに接

続されている場合には、スイッチ239にオン抵抗があると、出力電位Voutがその影響を

受けてしまうために、出力電位Voutが低下してしまうからである。

【0112】

図7に示すソースフォロワ回路において、スイッチ241の一方の端子が入力端子とな

る。前記入力端子から入力される入力電位Vin(信号電圧)は、スイッチ241及び容量

素子234を介して、増幅用トランジスタ232のゲート電極に入力される。またスイッ

チ236の一方の端子からはバイアス電位Vbが入力される。バイアス電位Vbは、スイッチ

236及び容量素子233を介して、トランジスタ231のゲート電極に入力される。ま

た、スイッチ238の一方の端子が出力端子となっており、増幅用トランジスタ232の

ソース領域の電位が出力電位Voutとなる。

【0113】

なお、バイアス用トランジスタ231、増幅用トランジスタ232のゲート幅(W)、

ゲート長(L)の大きさは特に限定されない。

【0114】

また図7(B)には、バイアス用トランジスタ231を配置していない場合のソースフ

ォロワ回路を示す。図7(B)に示すソースフォロワ回路の動作は、スイッチ239が出

力動作のときにオフになる以外は、上述した図1、2の動作に準ずるので、本実施の形態

では説明を省略する。

【0115】

本実施の形態は、実施の形態1と任意に組み合わせることが可能である。

【0116】

(実施の形態3)

前述した実施の形態1、2では、本発明を適用したソースフォロワ回路について説明し

た。しかし本発明は、差動増幅回路、センスアンプ、オペアンプなどに代表される演算回

路など、さまざまな回路にも適用することが出来る。本実施の形態では、本発明を適用し

た演算回路について図8〜図10を用いて説明する。

【0117】

まず、本発明を適用した差動増幅回路について、図8を用いて説明する。差動増幅回路

では、入力電位Vin1及び入力電位Vin2の差の演算を行って出力電位Voutを出力する。

【0118】

図8に示す差動増幅回路において、272、273はpチャネル型のトランジスタであ

り、274、275及び286はnチャネル型のトランジスタである。

276、277及び287は容量素子である。また、スイッチ278〜スイッチ285、

スイッチ351、スイッチ288〜スイッチ290は、スイッチング機能を有する素子で

あり、好ましくはトランジスタなどの半導体素子が用いられる。また電源線271には電

源電位Vddが印加され、電源線291には接地電位Vssが印加される。

【0119】

図8に示す差動増幅回路において、トランジスタ274のゲート電極が入力端子となっ

ており、トランジスタ274のゲート電極には入力電位Vin1が入力される。またトランジ

スタ275のゲート電極も入力端子となっており、トランジスタ275のゲート電極には

入力電位Vin2が入力される。またトランジスタ275のドレイン領域が出力端子となって

おり、トランジスタ275のドレイン領域の電位が出力電位Voutとなる。

【0120】

トランジスタ272のドレイン領域は電源線271に接続され、ソース領域はトランジ

スタ274のドレイン領域に接続されている。トランジスタ273のドレイン領域は電源

線271に接続され、ソース領域はトランジスタ275のドレイン領域に接続されている

。トランジスタ272のゲート電極とトランジスタ273のゲート電極は接続されている

。なおトランジスタ272及びトランジスタ273の代わりに、抵抗を配置してもよい。

【0121】

トランジスタ274のドレイン領域は、トランジスタ272を介して電源線271に接

続され、ソース領域はスイッチ282を介して、容量素子276の一方の端子に接続され

ている。トランジスタ274のゲート電極は、容量素子276の他方の端子に接続されて

いる。容量素子276は、トランジスタ274のゲート・ソース間電圧(しきい値電圧)

を保持する役目を担う。

【0122】

トランジスタ275のドレイン領域は、トランジスタ273を介して電源線271に接

続され、ソース領域はスイッチ283を介して、容量素子277の一方の端子に接続され

ている。トランジスタ275のゲート電極は、容量素子277の他方の端子に接続されて

いる。容量素子277は、トランジスタ275のゲート・ソース間電圧(しきい値電圧)

を保持する役目を担う。

【0123】

トランジスタ286のドレイン領域は、スイッチ285やスイッチ351を介してトラ

ンジスタ274のソース領域及びトランジスタ275のソース領域に接続され、トランジ

スタ286のソース領域はスイッチ290を介して、容量素子287の一方の端子に接続

されている。トランジスタ286のゲート電極は、容量素子287の他方の端子に接続さ

れている。容量素子287は、トランジスタ286のゲート・ソース間電圧(しきい値電

圧)を保持する役目を担う。

【0124】

そして、容量素子276に所定の電荷の保持を行う動作、容量素子277に所定の電荷

の保持を行う動作、容量素子287に所定の電荷の保持を行う動作の説明は、実施の形態

1に準ずるので、簡単に説明する。

【0125】

まず、図18に示すように、初期化を行う。初期化を行うためには、トランジスタ27

4、275、286がオンになるような状態にすればよい。そして、図19に示すように

、トランジスタ274、275、286のゲート・ソース間電圧がしきい値電圧に収束す

るように動作させる。

【0126】

そして、容量素子276に所定の電荷の保持が終了したら、図22に示すように、トラ

ンジスタ274のゲート電極に入力電位Vin1が入力され、また容量素子277に所定の電

荷の保持が終了したら、トランジスタ275のゲート電極に入力電位Vin2が入力される。

また容量素子287に所定の電荷の保持が終了したら、トランジスタ286のゲート電極

にバイアス電位Vbが入力されて、出力動作を行う。このときの動作の説明は、実施の形態

1に準ずるので本実施の形態では省略する。

【0127】

なお、図8の回路は、図17に示す回路のように改良してもよい。図17では、トラン

ジスタ272、273と並列に、スイッチ352、353を追加して配置している。スイ

ッチ352、353は、設定動作を行っている時(しきい値電圧を取得している時)には

オンにしておき、出力動作を行っている時(通常の差動回路として動作させている時)に

はオフにしておく。上記スイッチの追加により、設定動作を行っている時にはトランジス

タ274、275に電流を供給しやすくしたり、トランジスタ274、275のドレイン

の電位を固定しやすくしたりすることが出来る。

【0128】

また、図8と図17の回路では、スイッチ285、351の位置が異なる。しかし、し

きい値電圧を取得する動作の時に、トランジスタ274、275、286を電気的に接続

されない状態にすればよいので、それを満たすならば、スイッチ285、351は、どこ

に配置してもよい。

【0129】

続いて、図8に示す差動増幅回路を構成するトランジスタが逆の導電型を有する場合に

ついて、図9、図23を用いて説明する。

【0130】

図9、図23に示す差動増幅回路において、272、273がnチャネル型のトランジ

スタであり、274、275及び286がpチャネル型のトランジスタである。トランジ

スタ274のゲート電極が入力端子となっており、トランジスタ274のゲート電極には

入力電位Vin1が入力される。またトランジスタ275のゲート電極も入力端子となってお

り、トランジスタ275のゲート電極には入力電位Vin2が入力される。また、トランジス

タ275のソース領域の電位が出力電位Voutとなる。さらに、トランジスタ286のゲー

ト電極にはバイアス電位Vbが入力される。

【0131】

なお図9、図23に示す差動増幅回路においては、電源線291に電源電位Vddが印加

され、電源線271に接地電位Vssが印加されている点以外は、図8、図17に示す差動

増幅回路の構成、及びその動作と同じであるので、ここでは説明を省略する。

【0132】

また本実施の形態では、図8、9に示す電気回路を差動増幅回路として示したが、本発

明はこれに限定されず、入力電位Vin1と入力電位Vin2として入力する電圧を適宜変更して

、センスアンプなどの他の演算回路として用いることも出来る。

【0133】

次いで、本発明を適用したオペアンプについて、図10を用いて説明する。図10(A

)にはオペアンプの回路記号を示し、図10(B)には該オペアンプの回路構成を示す。

【0134】

なお、オペアンプの回路構成としては、さまざまなものがある。そこで、図10では、

もっとも簡単な場合として、差動増幅回路にソースフォロワ回路を組み合わせた場合につ

いて述べる。よって、回路構成は、図10に限定されない。

【0135】

図10(A)に示すオペアンプでは、入力電位Vin1及び入力電位Vin2と、出力電位Vout

との関係によって特性が定義される。より詳しくは、オペアンプは、入力電位Vin1及び入

力電位Vin2との差の電圧に対し、増幅度Aを掛けて出力電位Voutを出力する機能を有する

。

【0136】

図10(B)に示すオペアンプにおいて、トランジスタ274のゲート電極は、入力端

子となっており、該トランジスタ274のゲート電極には、入力電位Vin1が入力される。

またトランジスタ275のゲート電極も入力端子となっており、該トランジスタ275の

ゲート電極には入力電位Vin2が入力される。また、トランジスタ292のソース領域の電

位が出力電位Voutとなる。またトランジスタ286のゲート電極には、バイアス電位が入

力される。

【0137】

図10(B)に示す回路において、305で示す点線で囲んだ部分は、図8に示す差動

増幅回路と同じ構成である。そして、306で示す点線で囲んだ部分は、図1、2に示し

たソースフォロワ回路と同じであるので、図10(B)に示したオペアンプの詳しい構成

の説明は省略する。

【0138】

また図21には、トランジスタ299がpチャネル型である場合のオペアンプを示す。

図21(B)において、容量素子300の一方の端子は、スイッチ302、スイッチ27

8を介して、トランジスタ275のドレイン領域と接続されている。

【0139】

なお本実施の形態は、実施の形態1、2と任意に組み合わせることが可能である。

【0140】

(実施の形態4)

本実施の形態では、本発明を適用した光電変換素子を有する半導体装置(電気回路)に

おける画素及び駆動回路(バイアス回路)の構成とその動作について、図11、12を用

いて説明する。

【0141】

図11(A)に示す半導体装置(電気回路)は、基板701上に、複数の画素がマトリ

クス上に配置された画素部702を有し、画素部702の周辺には、信号線駆動回路70

3、第1〜第4の走査線駆動回路704〜707を有する。図11(A)に示す半導体装

置は、信号線駆動回路703と、4組の走査線駆動回路704〜707を有しているが、

本発明はこれに限定されず、信号線駆動回路と走査線駆動回路の数は画素の構成に応じて

任意に配置することが出来る。また、信号線駆動回路703と、第1〜第4の走査線駆動

回路704〜707には、FPC708を介して外部より信号が供給されている。しかし本

発明はこれに限定されず、画素部以外の電気回路は、ICなどを用いて外部から供給する

ようにしてもよい。

【0142】

最初に、第1の走査線駆動回路704及び第2の走査線駆動回路705の構成について

、図11(B)を用いて説明する。第3の走査線駆動回路706及び第4の走査線駆動回

路707は、図11(B)の図に準ずるので、図示は省略する。

【0143】

第1の走査線駆動回路704は、シフトレジスタ709、バッファ710を有する。第

2の走査線駆動回路705は、シフトレジスタ711、バッファ712を有する。動作を

簡単に説明すると、シフトレジスタ709、711は、クロック信号(G-CLK)、スター

トパルス(S-SP)及びクロック反転信号(G-CLKb)に従って、順次サンプリングパルスを

出力する。その後バッファ710、712で増幅されたサンプリングパルスは、走査線に

入力されて、1行ずつ選択状態にしていく。

【0144】

なおシフトレジスタ(709、711)とバッファ(710、712)との間にはレベ

ルシフタ回路を配置した構成にしてもよい。レベルシフタ回路を配置することによって、

電圧振幅を大きくすることが出来る。

【0145】

次いで、信号線駆動回路703の構成について、図11(C)を用いて説明する。

【0146】

信号線駆動回路703は、信号出力線用駆動回路715、サンプルホールド回路716

、バイアス回路714及び増幅回路717を有する。それぞれの回路が有する機能を簡単

に説明すると、バイアス回路714は、各画素の増幅用トランジスタと対になって、ソー

スフォロワ回路を形成する。サンプルホールド回路716は、信号を一時的に保存したり

、アナログ・デジタル変換を行ったり、雑音を低減したりする機能を有する。信号出力用

駆動回路715は、一時的に保存されていた信号を、順に出力していくための信号を出力

する機能を有する。そして、増幅回路717は、サンプルホールド回路716と信号出力

用駆動回路715により出力された信号を増幅する回路を有している。なお、増幅回路7

17は、信号を増幅する必要のない場合には配置しなくてもよい。

【0147】

そして、画素部702においてi列目j行目に配置される画素713の回路と、i列目

の周辺のバイアス回路714の構成とその動作について、図12を用いて説明する。

【0148】

最初に、i列目j行目に配置される画素713の回路と、i列目の周辺のバイアス回路

714の構成について説明する。

【0149】

図12に示す画素は、第1〜第4の走査線Ga(j)〜Gd(j)、信号線S(i)、

電源線V(i)を有する。また、nチャネル型のトランジスタ255、光電変換素子25

7、スイッチ250〜スイッチ254を有する。

【0150】

本実施の形態においては、トランジスタ255はnチャネル型としたが、本発明はこれ

に限定されず、pチャネル型でもよい。但し、トランジスタ255とトランジスタ260

により、ソースフォロワ回路を形成するので、両トランジスタは同じ極性であることが好

ましい。

【0151】

スイッチ250〜スイッチ254は、スイッチング機能を有する半導体素子であり、好

ましくはトランジスタが用いられる。スイッチ251及びスイッチ252は、第1の走査

線Ga(j)から入力される信号により、オン又はオフが制御される。スイッチ250は

、第2の走査線Gb(j)から入力される信号により、オン又はオフが制御される。スイ

ッチ253は、第3の走査線Gc(j)から入力される信号により、オン又はオフが制御

される。スイッチ254は、第4の走査線Gd(j)から入力される信号により、オン又

はオフが制御される。

【0152】

トランジスタ255のソース領域とドレイン領域は、一方は電源線V(i)に接続され

、他方はスイッチ250を介して信号線S(i)に接続されている。トランジスタ255

のゲート電極は、容量素子256の一方の端子に接続されている。また容量素子256の

他方の端子はスイッチ253を介して光電変換素子257の一方の端子に接続されている

。光電変換素子257の他方の端子は電源線258に接続されている。電源線258には

、接地電位Vssが印加される。容量素子256は、トランジスタ255のゲート・ソース

間電圧(しきい値電圧)を保持する役目を担う。

【0153】

バイアス回路714は、トランジスタ260、容量素子261、スイッチ259、スイ

ッチ262及びスイッチ263を有する。トランジスタ260のソース領域は電源線26

4に接続され、ドレイン領域は信号線S(i)に接続されている。電源線264には、接

地電位Vssが印加される。トランジスタ260のゲート電極は、容量素子261の一方の

端子に接続されている。容量素子261の他方の端子はスイッチ262を介して電源線2

64に接続されている。容量素子261は、トランジスタ260のゲート・ソース間電圧

(しきい値電圧)を保持する役目を担う。

【0154】

そして、図12において、719で示す点線で囲んだ部分と714で示す点線で囲んだ

部分とがソースフォロワ回路に相当する。

【0155】

次いで、i列目j行目に配置される画素713の回路と、i列目の周辺のバイアス回路

714の動作を簡単に説明する。

【0156】

まず、画素713においてスイッチ250〜スイッチ252、バイアス回路714にお

いてスイッチ259、262をオン状態にする。そして、それ以外のスイッチはオフにす

る。そうすると、電源線V(i)と、電源線264との間に電位差が生じる。その結果、

電源線V(i)から、スイッチ252、スイッチ251を介して、次いでスイッチ250

、スイッチ259を介して、さらにスイッチ262を介して電源線264の方向に流れる

。

【0157】

電流が流れ始めた瞬間には、容量素子256、261には電荷は保持されていない。そ

のため、トランジスタ255、260はオフである。

【0158】

そして徐々に容量素子256、261に電荷が蓄積されて、該容量素子256、261

の両電極間に電位差が生じ始める。容量素子256、261の両電極間の電位差が、トラ

ンジスタ255、260のしきい値電圧になると、該トランジスタ255、260はオン

となる。

【0159】

そして容量素子256、261では、定常状態になるまで、電荷の蓄積が続けられる。

【0160】

続いて、容量素子256、261において、電荷の蓄積が終了して定常状態になった後

、スイッチ250をオフにする。スイッチ251、252は引き続きオンである。またス

イッチ259、262も引き続きオンである。そして上記以外のスイッチは全てオフであ

る。

【0161】

そうすると、容量素子256に保持された正の電荷は、スイッチ252、トランジスタ

255、さらにスイッチ251を介して容量素子256の方向に流れていく。より詳しく

は、容量素子256に保持された正の電荷は、スイッチ252、トランジスタ255のソ

ース領域からドレイン領域を介して、さらにスイッチ251を介して容量素子256の方

向に流れていく。その結果、容量素子256の両電極間の電位差は減少していく。この動

作は、トランジスタ255がオフになるまで行われる。つまり、容量素子256に保持さ

れている電荷が、トランジスタ255のしきい値電圧と同じ値になるまで続けられる。

【0162】

また、容量素子261に保持された正の電荷は、スイッチ259、トランジスタ260

を介して電源線264の方向に流れていく。より詳しくは、容量素子261に保持された

正の電荷は、スイッチ259、トランジスタ260のソース領域からドレイン領域を介し

て、電源線264の方向に流れていく。この動作は、トランジスタ260がオフになるま

で行われる。つまり、容量素子261に保持されている電荷が、トランジスタ260のし

きい値電圧と同じ値になるまで続けられる。

【0163】

このとき、容量素子256にはトランジスタ255のしきい値電圧が保持された状態で

あり、また、容量素子261にはトランジスタ260のしきい値電圧が保持された状態で

ある。この状態において、画素713においては、スイッチ250、スイッチ253をオ

ンにして、それ以外のスイッチはオフとする。またバイアス回路714においては、スイ

ッチ263をオンとして、それ以外のスイッチはオフとする。

【0164】

そうすると、トランジスタ255のゲート電極には、容量素子256を介して、光電変

換素子257から信号が入力される。また同時に、トランジスタ260のゲート電極には

、容量素子261を介してバイアス電位Vbが入力される。

【0165】

このとき、トランジスタ255のゲート電極には、該トランジスタのしきい値電圧に加

えて、光電変換素子257からの信号が上乗せされた値が入力される。

また、トランジスタ260のゲート電極には、該トランジスタのしきい値電圧に加えて、

バイアス電位が上乗せされた値が入力される。つまり、トランジスタ255、260のゲ

ート電極に入力される信号は、該トランジスタ255、260のしきい値電圧に加えて、

該トランジスタのゲート電極に入力される信号となる。そのため、両トランジスタのしき

い値電圧のバラツキの影響を抑制することができる。

【0166】

そしてトランジスタ255のソース領域の電位が出力電位Voutとなり、該出力電位Vout

は、光電変換素子257により読み取られた信号として、スイッチ250を介して信号線

S(i)に出力される。

【0167】

次いで、スイッチ254をオンにして、それ以外のスイッチは全てオフにして、光電変

換素子257を初期化する。より詳しくは、光電変換素子257のnチャネル側端子の電

位が電源線258の電位と同じになるように、光電変換素子257が保持している電荷を

スイッチ254を介して、電源線V(i)の方向に流れるようにする。以後、上記の動作

を繰り返す。

【0168】

上記のような構成を有する本発明の半導体装置は、トランジスタのしきい値電圧のバラ

ツキの影響を抑制することができる。

【0169】

本発明は、実施の形態1〜実施の形態3と任意に組み合わせることが可能である。

【0170】

(実施の形態5)

本実施の形態では、本発明を適用した電気回路において、実施の形態2〜実施の形態4

とは異なる例について、図13〜図16を用いて説明する。

【0171】

図13(A)において、310は図1、2で示したソースフォロワ回路である。ソース

フォロワ回路310の回路構成と動作は、図1、2と同じであるので、本実施の形態では

説明は省略する。

【0172】

ソースフォロワ回路310の動作は、大別して設定動作と出力動作に分別できることは

上述した。なお設定動作とは、容量素子に所定の電荷の保持を行う動作であり、図1(A

)(B)及び図2(A)の動作に相当する。また出力動作とは、入力電位Vin及びバイア

ス電位Vbを入力して、出力電位Voutを取り出す動作のことであり、図2(B)の動作に相

当する。

【0173】

ソースフォロワ回路310において、端子aが入力端子に相当し、端子bが出力端子に

相当する。そして、スイッチ216、218、221は端子cから入力される信号により

制御される。スイッチ215、217、220及び222は端子dから入力される信号に

より制御される。スイッチ219は端子eから入力される信号により制御される。

【0174】

そして、ソースフォロワ回路310を有する電気回路を設計するときには、図13(B

)に示すように、少なくとも2つのソースフォロワ回路315、316を配置するとよい

。そしてソースフォロワ回路315、316のうち、一方は設定動作を行って、他方は出

力動作を行うようにするとよい。そうすると、同時に2つのことができ、動作に無駄がな

く、無駄な時間が必要なくなるので、電気回路の動作をより高速で行うことができる。

【0175】

例えば、信号線駆動回路にソースフォロワ回路を用いて設計するときには、信号線ごと

に少なくとも2個のソースフォロワ回路を配置するとよい。また走査線駆動回路にソース

フォロワ回路を用いて設計するときには、走査線ごとに少なくとも2個のソースフォロワ

回路を配置するとよい。また画素にソースフォロワ回路を用いて設計するときには、画素

ごとに少なくとも2つのソースフォロワ回路を配置するとよい。

【0176】

図13(B)において、311〜314はスイッチ機能を有する素子であり、好ましく

はトランジスタなどが用いられる。そして、スイッチ311、312がオンのときは、ス

イッチ313、314はオフとなる。またスイッチ311、312がオフのときには、ス

イッチ313、314はオンとなる。このようにして、2つのソースフォロワ回路315

、316のうち、一方は設定動作を行って、他方は出力動作を行うようにする。なお、ス

イッチ311〜スイッチ314を配置せずに、ソースフォロワ回路310が有するスイッ

チ216、218を制御することによって、2つのソースフォロワ回路315、316を

制御するようにしてもよい。

【0177】

また本実施の形態では、点線で囲んだ部分315、316は、ソースフォロワ回路に相

当するとしたが、本発明はこれに限定されず、図7〜図10などに示した差動増幅回路、

オペアンプなどを適用してもよい。

【0178】

そして本実施の形態では、信号線ごとに少なくとも2個のソースフォロワ回路を配置し

た信号線駆動回路の構成とその動作について、図14〜図16を用いて説明する。

【0179】

図14には信号線駆動回路を示しており、該信号線駆動回路は、シフトレジスタ321

、第1のラッチ回路322、第2のラッチ回路323、D/A変換回路324及び信号増

幅回路325を有する。

【0180】

なお、第1のラッチ回路322や第2のラッチ回路323が、アナログデータを保存で

きる回路である場合は、D/A変換回路324は省略できる場合が多い。また、信号線に

出力するデータが2値、つまり、デジタル量である場合は、D/A変換回路324は省略

できる場合が多い。また、D/A変換回路324には、ガンマ補正回路が内蔵されている

場合もある。このように、信号線駆動回路は、図17に限定されない。

【0181】

動作を簡単に説明すると、シフトレジスタ321は、フリップフロップ回路(FF)等

を複数列用いて構成され、クロック信号(S-CLK)、スタートパルス(S-SP)、クロ

ック反転信号(S-CLKb)が入力される、これらの信号のタイミングに従って、順次サ

ンプリングパルスが出力される。

【0182】

シフトレジスタ321より出力されたサンプリングパルスは、第1のラッチ回路322

に入力される。第1のラッチ回路322には、ビデオ信号が入力されており、サンプリン

グパルスが入力されるタイミングに従って、各列でビデオ信号を保持していく。

【0183】

第1のラッチ回路322において、最終列までビデオ信号の保持が完了すると、水平帰

線期間中に、第2のラッチ回路323にラッチパルス(Latch Pulse)

が入力され、第1のラッチ回路322に保持されていたビデオ信号は、一斉に第2のラッ

チ回路323に転送される。その後、第2のラッチ回路323に保持されたビデオ信号は

、1行分が同時に、D/A変換回路324へと入力される。そして、D/A変換回路32

4から入力される信号は信号増幅回路325へ入力される。

【0184】

第2のラッチ回路323に保持されたビデオ信号がD/A変換回路324に入力されて

いる間、シフトレジスタ321においては再びサンプリングパルスが出力される。以後、

この動作を繰り返す。

【0185】

そして、i列目から(i+2)列目の3本信号線の周辺の信号増幅回路325の構成を

図15を用いて説明する。

【0186】

信号増幅回路325は、列ごとに2つのソースフォロワ回路315、316を有する。

ソースフォロワ回路315、316は、それぞれ端子a〜端子eまでの5つの端子を有す

る。端子aはソースフォロワ回路315、316における入力端子に相当し、端子bはソ

ースフォロワ回路315、316における出力端子に相当する。また、端子cから入力さ

れる信号によりスイッチ216、218及び221が制御され、端子dから入力される信

号によりスイッチ215、217、220及び222が制御される。さらに端子eから入

力される信号によりスイッチ219が制御される。

【0187】

また図15に示す信号増幅回路325において、初期化用信号線326、設定用信号線

327及びしきい値用信号線328の3本の信号線と、ソースフォロワ回路315、31

6との間には、論理演算子が配置されている。329はインバータ、330はAND、3

31はOR、332はインバータ、333はAND、334はインバータ、335はOR

である。そして、端子c〜端子eには、設定用信号線327から出力される信号、又は上

記の論理演算子の出力端子から出力される信号のどちらかが入力される。

【0188】

次いで、初期化用信号線326、設定用信号線327及びしきい値用信号線328の3

本の信号線から出力される信号と、ソースフォロワ回路315における端子c〜端子eを

介して各スイッチに入力される信号を図16を用いて説明する。

【0189】

なお、端子c〜端子eを介して信号が入力されるスイッチは、Highの信号が入力される

とオンになり、Lowの信号が入力されるとオフになるとする。

【0190】

そして、初期化用信号線326、設定用信号線327及びしきい値用信号線328の3

本の信号線からは、図16に示すような信号が入力される。さらに、ソースフォロワ回路

315における端子cには、設定用信号線327から入力される信号がそのまま入力され

る。端子dにはAND333の出力端子から出力される信号が入力され、端子eにはOR

331の出力端子から出力される信号が入力される。そうすると、ソースフォロワ回路3

15では、設定動作と出力動作のどちらか一方の動作を行うように制御することが出来る

。

【0191】

またソースフォロワ回路316における端子cには、インバータ332の出力端子から

出力される信号が入力される。端子dには、AND330の出力端子から出力される信号

が入力され、端子eにはOR335の出力端子から出力される信号が入力される。そうす

ると、ソースフォロワ回路316では、設定動作と出力動作のどちらか一方の動作を行う

ように制御することが出来る。

【0192】

なお、信号線駆動回路の各信号線の先には、複数の画素が接続されている場合が多い。

当該画素は、信号線から入力される電圧によって、状態を変化させるものであることが多

い。例としては、液晶素子を有する画素や有機ELに代表される発光素子を有する画素な

どがあげられる。その他にも、さまざまな構成の画素を接続することが可能である。

【0193】

なお、本実施の形態は、実施の形態1〜実施の形態4と任意に組み合わせることが可能

である。

【0194】

(実施の形態6)

本発明の電気回路を用いて完成される電子機器として、ビデオカメラ、デジタルカメラ

、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、

音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュー

タ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機また

は電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(

DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)など

が挙げられる。それらの電子機器の具体例を図20に示す。

【0195】

図20(A)はディスプレイ(発光装置)であり、筐体3001、支持台3002、表示部3003

、スピーカー部3004、ビデオ入力端子3005等を含む。本発明は表示部3003を構成する電気

回路に用いることができる。また本発明により、図20(A)

に示す発光装置が完成される。発光装置は自発光型であるためバックライトが必要なく、

液晶ディスプレイよりも薄い表示部とすることができる。なお、発光装置は、パソコン用

、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

【0196】

図20(B)はデジタルスチルカメラであり、本体3101、表示部3102、受像部3103、操

作キー3104、外部接続ポート3105、シャッター3106等を含む。本発明は、表示部3102を構

成する電気回路に用いることができる。また本発明により、図20(B)に示すデジタル

スチルカメラが完成される。

【0197】

図20(C)はノート型パーソナルコンピュータであり、本体3201、筐体3202、表示部

3203、キーボード3204、外部接続ポート3205、ポインティングマウス3206等を含む。本発

明は、表示部3203を構成する電気回路に用いることができる。

また本発明により、図20(C)に示すノート型コンピュータが完成される。

【0198】

図20(D)はモバイルコンピュータであり、本体3301、表示部3302、スイッチ3303、

操作キー3304、赤外線ポート3305等を含む。本発明は、表示部3302を構成する電気回路に

用いることができる。また本発明により、図20(D)に示すモバイルコンピュータが完

成される。

【0199】

図20(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)

であり、本体3401、筐体3402、表示部A3403、表示部B3404、記録媒体(DVD等)読み

込み部3405、操作キー3406、スピーカー部3407等を含む。表示部A3403は主として画像情

報を表示し、表示部B3404は主として文字情報を表示するが、本発明は、表示部A、B34

03、3404を構成する電気回路に用いることができる。なお、記録媒体を備えた画像再生装

置には家庭用ゲーム機器なども含まれる。また本発明により、図20(E)に示すDVD

再生装置が完成される。

【0200】