半導体装置

【課題】基板電位を安定化させることができる半導体装置を提供する。

【解決手段】半導体装置に含まれるFET素子1は、N角形をなす外周端部30pと貫通孔を形作る内周端部30iとを有する環状のゲート電極30を備える。またFET素子1は、貫通孔の直下方に形成された内側不純物拡散領域21と、ゲート電極30のN角形の辺の外側に形成された外側不純物拡散領域22A〜22Dと、ゲート電極30の頂点の外側に形成されたバックゲート領域23A〜23Dとを備える。バックゲート領域23A〜23Dは、ゲート電極30のN角形の辺のうちゲート電極30の頂点をなす2辺の延長線Ex,Eyの少なくとも一方を跨るように形成されている。

【解決手段】半導体装置に含まれるFET素子1は、N角形をなす外周端部30pと貫通孔を形作る内周端部30iとを有する環状のゲート電極30を備える。またFET素子1は、貫通孔の直下方に形成された内側不純物拡散領域21と、ゲート電極30のN角形の辺の外側に形成された外側不純物拡散領域22A〜22Dと、ゲート電極30の頂点の外側に形成されたバックゲート領域23A〜23Dとを備える。バックゲート領域23A〜23Dは、ゲート電極30のN角形の辺のうちゲート電極30の頂点をなす2辺の延長線Ex,Eyの少なくとも一方を跨るように形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路におけるMOSFET(Metal−Oxide−Semiconductor Field−Effect Transistor)などの電界効果トランジスタを含む半導体装置に関する。

【背景技術】

【0002】

多数の電界効果トランジスタ(FET)を含む半導体集積回路では、当該半導体集積回路の製造条件のばらつきによりFET間で閾値電圧などの素子特性のばらつきが生じ、歩留まり低下や半導体集積回路の動作不良の原因となることがある。製造条件のばらつきは、たとえば、リソグラフィ工程でのレジスト露光量の空間的なばらつき、あるいは、斜めイオン注入工程で導入された不純物濃度の空間分布のばらつきに起因して生じ得る。また、製造条件のばらつきが小さくても、パワー半導体素子などの熱源または応力発生源からの距離に応じてFET間で素子特性のばらつきが製造後に生じることもある。複数のFETを用いる高精度なアナログ集積回路(たとえば、差動型オペアンプやカレントミラー回路)では、FET間の素子特性のばらつきが抑制されるように素子のレイアウト設計を行うことが重要である。

【0003】

上記のような素子特性のばらつきを打ち消す方法としては、従来より、複数のFETの配置に幾何学的対称性を持たせるレイアウトが存在する。この種のレイアウトの1つとしては、コモンセントロイド(common centroid)配置が知られている。たとえば、差動型オペアンプの差動入力段やカレント・ミラー回路のように一対のMOSFETを有する半導体集積回路では、これらMOSFETの素子特性を互いにマッチングさせる必要がある。コモンセントロイド配置はこのようなマッチングが要求される回路に有効である。

【0004】

また、FETの形状自体に幾何学的対称性(たとえば、点対称性、線対称性もしくはこれらの組み合わせ)を持たせることで、FET間の特性のばらつき発生を抑制するレイアウトも提案されている。この種のレイアウトは、たとえば、特開2009−188223号公報(特許文献1)に開示されている。図1は、この特許文献1に開示されているレイアウト構造の平面図である。図1のFETは、中空矩形状のゲート電極130Gと、このゲート電極130Gに囲まれる領域に形成されたドレイン領域130Dと、ゲート電極130Gの外周を取り囲むように形成されたソース領域130Sとを有する。このFETは、X1軸及びY1軸に関してそれぞれ線対称構造を有している。チャネルは、ゲート電極130Gの内周と外周との間で360°の方向に形成される。このため、仮にソース領域130S及びドレイン領域130Dの不純物濃度の空間分布に偏りがある場合でも、その偏りに起因する素子特性のばらつき発生を抑制することができる。

【0005】

また、特開2008−78469号公報(特許文献2)には、図1のFETと類似する幾何学的対称性を有するFET構造が開示されている。図2は、特許文献2に開示されているレイアウト構造の平面図(上面図)である。図2のFETは、4つの辺を有する矩形環状のゲート電極131Gと、ゲート電極131Gの内側に形成されたドレイン電極131Dと、4つの辺の外側の領域にそれぞれ形成されたソース領域131Sa,131Sb,131Sc,131Sdと、ゲート電極131Gの4つの頂点の外側にそれぞれ形成されたバックゲート領域131BGa,131BGb,131BGc,131BGdとを有する。ゲート電極131Gは、図1のゲート電極130Gと同様の線対称構造を有している。ただし、図2のFETの構造は、単位ゲート幅当たりのドレイン容量を低減することを目的とする構造であり、素子特性のばらつき抑制を目的としたものではない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−188223号公報(図3,段落0020)

【特許文献2】特開2008−78469号公報(図1及び図2,段落0018〜0026)

【発明の概要】

【発明が解決しようとする課題】

【0007】

図1のFETは、バックゲート領域を持たないので、基板バイアス効果(基板電位の変化に応じてFETの閾値電圧が変化する現象)を利用してFETの特性を制御することができない。これに対し、図2のFETには、バックゲート領域131BGa〜131BGdが形成されている。しかしながら、これらバックゲート領域131BGa〜131BGdの配置では、基板電位を安定化させることに限界がある。特に、図2のFETの構造をマトリクス状に配列してなる半導体集積回路の場合、FET間の基板電位のばらつきを抑制することが難しいという問題がある。

【0008】

上記に鑑みて本発明の目的は、基板電位を十分に安定化させることができる半導体装置を提供することである。

【課題を解決するための手段】

【0009】

本発明の一態様による半導体装置は、複数の電界効果トランジスタ素子を備えた半導体装置であって、前記各電界効果トランジスタ素子は、半導体基板の主面上に形成され、前記主面を平面視したときにN角形(Nは3以上の整数)をなす外周端部と前記主面の面内方向に垂直な方向の貫通孔を形作る内周端部とを有する環状のゲート電極と、前記半導体基板の主面と前記ゲート電極との間に介在するゲート絶縁膜と、前記半導体基板の内部で前記貫通孔の直下方に形成され、ソース領域及びドレイン領域の一方をなす第1導電型の内側不純物拡散領域と、前記半導体基板の内部で前記N角形のN個の辺の外側にそれぞれ形成され、前記ソース領域及び前記ドレイン領域の他方をなす前記第1導電型のN個の外側不純物拡散領域と、前記半導体基板の内部で前記ゲート電極のN角形の頂点の外側に形成された、前記第1導電型とは逆の第2導電型のバックゲート領域とを有し、前記バックゲート領域は、前記N角形のN個の辺のうち当該頂点をなす2辺の少なくとも一方の延長線上を前記外側不純物拡散領域のいずれかに近接する方向へ跨るように形成されていることを特徴とする。

【発明の効果】

【0010】

本発明の一態様によれば、各バックゲート領域は、N角形状のゲート電極の頂点をなす2辺の少なくとも一方の延長線上を外側不純物拡散領域に近接する方向へ跨るように形成されているので、バックゲート領域の占有面積を大きくすることができる。したがって、電界効果トランジスタ素子の基板電位の安定化と素子特性のばらつき抑制とを実現することができる。

【図面の簡単な説明】

【0011】

【図1】特許文献1(特開2009−188223号公報)に開示されているレイアウト構造の平面図である。

【図2】特許文献2(特開2008−78469号公報)に開示されているレイアウト構造の平面図である。

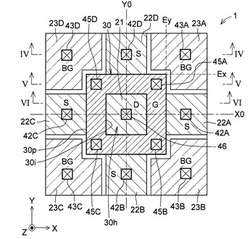

【図3】本発明に係る実施の形態の半導体装置に含まれる電界効果トランジスタ素子(FET素子)のレイアウトを概略的に示す平面図である。

【図4】図3のFET素子のIV−IV線における概略断面図である。

【図5】図3のFET素子のV−V線における概略断面図である。

【図6】図3のFET素子1のVI−VI線における概略断面図である。

【図7】本発明に係る実施の形態2の半導体装置に含まれるFET素子群のレイアウトの一例を概略的に示す平面図である。

【図8】図7のFET素子群のコモンセントロイド配置を示す図である。

【図9】(A)〜(C)は、コモンセントロイド配置を例示する図である。

【図10】一対のnチャネルFETからなる回路構成を示す図である。

【図11】(A),(B),(C)は、図10の回路を作製するための上層配線パターンの一例の第1乃至第3の形成手順を示す図である。

【図12】(A),(B)は、図10の回路を作製するための上層配線パターンの一例の第4乃至第5の形成手順を示す図である。

【図13】(A),(B),(C)は、図10の回路を作製するための上層配線パターンの他の例の形成手順を示す図である。

【図14】多数のFET素子をマトリクス状に配列してなる半導体装置のレイアウトを概略的に示す図である。

【図15】図14のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第1の形成手順を示す図である。

【図16】図14のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第2の形成手順を示す図である。

【図17】図13のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第3の形成手順を示す図である。

【図18】図13のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第4の形成手順を示す図である。

【図19】図13のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第5の形成手順を示す図である。

【図20】特許文献2に開示されている従来のレイアウト構造を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明に係る種々の実施の形態について図面を参照しつつ説明する。

【0013】

実施の形態1.

図3は、本発明に係る実施の形態1の半導体装置に含まれる電界効果トランジスタ素子(FET素子)1のレイアウトを概略的に示す平面図である。図3には、3次元直交座標系をなすX軸、Y軸及びZ軸が示されている。また、図4は、図3のFET素子1のIV−IV線における概略断面図を示し、図5は、図3のFET素子1のV−V線における概略断面図を示し、図6は、図3のFET素子1のVI−VI線における概略断面図を示している。図3のX軸及びY軸の方向は、図4〜図6の半導体基板10の上面すなわち主面に平行であり、Z軸の方向は、半導体基板10の主面に垂直である。図4〜図6には層間絶縁膜40の断面が示されているが、図3の平面図には、説明の便宜上、層間絶縁膜40は示されていない。なお、図4〜図6に示される断面構造は一例であり、FET素子1の断面構造はこれに限定されるものではない。

【0014】

図3に示されるように、FET素子1は、正四角形状の外周端部30pと内周端部30iとを持つ環状のゲート電極30を有する。またFET素子1は、ゲート電極30の内周端部30iの内側でゲート電極30に囲まれるように形成された第1導電型のドレイン領域(内側不純物拡散領域)21と、ゲート電極30の外側に形成された第1導電型のソース領域(外側不純物拡散領域)22A,22B,22C,22Dと、第1導電型とは逆の第2導電型の不純物拡散領域であるバックゲート領域23A,23B,23C,23Dとを有する。これらバックゲート領域23A,23B,23C,23Dは、外周端部30pの頂点の外側にそれぞれ形成されている。ゲート電極30の上面には、当該ゲート電極30とZ軸方向上方のメタル配線との間を電気的に接続するコンタクトプラグ45A,45B,45C,45Dが形成されている。説明の便宜上、図3では、ゲート電極30は記号「G」と、ドレイン領域21は記号「D」と、ソース領域22A〜22Dは記号「S」と、バックゲート領域23A〜23Dは記号「BG」とでそれぞれ表されている。他の図面でも同様の記号が使用される。

【0015】

本実施の形態のFET素子1は、ゲート電極30の直下にn型チャネルを形成するnチャネルFETであるため、第1導電型はn型、第2導電型はp型であるが、これに限定されるものではない。第1導電型をp型とし、第2導電型をn型としてpチャネルFETを構成してもよい。

【0016】

また、図3に示されるように、ソース領域22A,22B,22C,22Dの上面にはコンタクトプラグ42A,42B,42C,42Dがそれぞれ形成され、ドレイン領域21の上面にはコンタクトプラグ46が形成され、バックゲート領域23A,23B,23C,23Dの上面にはコンタクトプラグ43A,43B,43C,43Dがそれぞれ形成されている。これらコンタクトプラグ42A〜42D,43A〜43D,46は、Z軸方向上方のメタル配線パターン(図示せず)と不純物拡散領域22A〜22D,23A〜23D,46との間を電気的に接続するために形成されている。ただし、必ずしもこれらコンタクトプラグ42A〜42D,43A〜43Dの全てを形成する必要はなく、上層のメタル配線パターンに対応するコンタクトプラグのみを形成すればよい。

【0017】

本実施の形態のFET素子1は、図4〜図6の断面図に示されるように、半導体基板10と第1半導体層11と第2半導体層20とからなる半導体構造を用いて作製される。本実施の形態では、半導体基板10として、たとえばp型の単結晶シリコン基板を使用することができる。第1半導体層11は、半導体基板10の上面を下地として形成されたn型のエピタキシャル成長層(Si層)であり、第2半導体層20は、第1半導体層11の上面を下地として形成されたp型のエピタキシャル成長層(Si層)である。埋め込み拡散領域12は、p+型不純物拡散層である。この埋め込み拡散領域12は、たとえば、リソグラフィ工程とイオン注入工程とにより半導体基板10の上層部にボロンやフッ化ボロンなどのp型不純物を選択的にイオン注入した後に、半導体基板10上に第1半導体層11をエピタキシャル成長させ、その後、導入されたp型不純物を熱処理で拡散させることで形成することができる。

【0018】

また、ソース領域22A〜22D及びドレイン領域21は、リソグラフィ工程とイオン注入工程とにより、第2半導体層20の上層部にリンや砒素などのn型不純物を選択的にイオン注入し、注入されたn型不純物を熱処理で活性化させることで形成される。バックゲート領域23A〜23Dは、リソグラフィ工程とイオン注入工程とにより、第2半導体層20に対してボロンやフッ化ボロンなどのp型不純物をイオン注入し、注入されたp型不純物を熱処理で活性化させることで形成される。バックゲート領域23A〜23Dは、図4及び図5に例示されるように、埋め込み拡散領域12の上面に到達する深さを有する。

【0019】

ゲート電極30は、図5及び図6に示されるように、シリコン酸化薄膜などのゲート絶縁膜25上に形成されている。ゲート絶縁膜25は、たとえば、第2半導体層20の表面を熱酸化することで形成することができる。ゲート電極30は、たとえば減圧CVD(low−pressure Chemical Vapor Deposition)法により、全面に亘って、リンが高濃度にドープされたポリシリコンからなる導電性材料層を成膜し、この導電性材料層をリソグラフィ工程とエッチング工程とでパターニングして形成され得る。

【0020】

図3を参照すると、ゲート電極30の外周端部30pは、X−Y平面でX軸方向に延在する2辺とY軸方向に延在する2辺と4つの頂点とを有する。ゲート電極30は、X−Y平面で矩形状(正4角形状)をなす外周端部30pを有し、また、この外周端部30pの形状と相似形をなす環状の内周端部30iを有する。この内周端部30iは、図3及び図6に示されるように、層厚方向(Z軸方向)の貫通孔30hをゲート電極30の中心部に形作るものである。ドレイン領域21は、この貫通孔30hの直下方に形成されており、ドレイン領域21の平面視形状は、図3に示されるように貫通孔30hの形状と略同じである。

【0021】

ソース領域22A〜22Dとドレイン領域21との間にドレイン電圧が印加された状態で、ゲート電極30とソース領域22A〜22Dとの間に所定のゲート電圧(ゲート・ソース間電圧)が印加されると、ソース領域22A〜22Dとドレイン領域21との間でゲート電極30の直下領域にキャリアが誘起され、n型チャネルが形成される。この結果、ソース領域22A〜22Dとドレイン領域21との間にドレイン電流が流れる。

【0022】

図3を参照すると、ソース領域22A,22B,22C,22Dは、ゲート電極30の外周端部30pの4辺の外側にそれぞれ形成されている。また、右方のソース領域22Aは、バックゲート領域23A,23B間に形成され、下方のソース領域22Bは、バックゲート領域23B,23C間に形成され、左方のソース領域22Cは、バックゲート領域23C,23D間に形成され、上方のソース領域22Dは、バックゲート領域23D,23A間に形成されている。さらに、ソース領域22AのY軸方向の幅は、これに対応するドレイン領域21のY軸方向の幅(一辺の長さ)と略同じあり、ソース領域22BのX軸方向の幅は、これに対応するドレイン領域21のX軸方向の幅(一辺の長さ)と略同じあり、ソース領域22CのY軸方向の幅は、これに対応するドレイン領域21のY軸方向の幅(一辺の長さ)と略同じあり、ソース領域22DのX軸方向の幅は、これに対応するドレイン領域21のX軸方向の幅(一辺の長さ)と略同じある。よって、ソース領域22A〜22Dの形成範囲は、ゲート電極30の頂点を除く4辺を介してドレイン領域21と対向する範囲に限定される。このため、ソース領域22A〜22Dとドレイン領域21との間に形成されるn型チャネルは、ゲート電極30の頂点付近には形成されない。それ故、FET素子1を実際に作製する前にチャネルの形成範囲を正確に予測することができる。したがって、レイアウト設計段階でチャネル長とチャネル幅とを正確に定めることが可能である。

【0023】

また、図3を参照すると、バックゲート領域23A,23B,23C,23Dは、これら4つの頂点の外側にそれぞれ形成されており、ゲート電極30の外周端部30pを取り囲むように配列されている。また、各バックゲート領域は、最も近い頂点をなす2辺の延長線を跨ぐように形成される。たとえば、右側上方のバックゲート領域23Aは、外周端部30pの頂点をなす2辺の延長線Ex,Eyをそれぞれ跨ぐように形成されている。このため、図2の従来のレイアウトと比べると、バックゲート領域23A〜23Dの占有面積が大きく、FET素子1の基板電位の安定化と、ESD(Electro−Static Damage)耐性(静電気によるLSIの破壊耐性)の向上とを実現することができる。

【0024】

また、図3を参照すると、n型チャネルは、ゲート電極30の直下において、ドレイン領域21とソース領域22A間の領域と、ドレイン領域21とソース領域22B間の領域と、ドレイン領域21とソース領域22C間の領域と、ドレイン領域21とソース領域22C間の領域とにそれぞれ形成されるので、n型チャネルは、ゲート電極30の外周端部30pの頂点付近には形成されない。よって、ゲート電極30を上層のメタル配線に接続するコンタクトプラグ45A,45B,45C,45Dは、n型チャネルが形成されない領域の直上に形成されている。このため、層間絶縁膜40にコンタクトホールを形成するためのエッチング工程でオーバエッチングによりゲート電極30とゲート絶縁膜25とがエッチングされた場合でも、チャネル形成領域がそのエッチングの影響を受けることを確実に回避することができる。また、仮に、ゲート電極30が薄く、コンタクトプラグ45A,45B,45C,45Dの構成材料がゲート電極30に拡散した場合でも、チャネル特性に影響を与えることを確実に回避することが可能である。

【0025】

また、FET素子1は、X−Y平面において幾何学的対称性を有している。すなわち、FET素子1は、図3のFET素子1の幾何学的中心(すなわちゲート電極30の幾何学的中心)を通るX軸方向に沿ったX0軸と、同じ中心を通るY軸方向に沿ったY0軸という2つの軸を幾何学的対称軸として有している。よって、FET素子1は、X0軸とY0軸とに関してそれぞれ線対称構造を有する。また、FET素子1は、X0軸とY0軸との交差点を通り且つZ軸方向に沿った回転対称軸を有している。この回転対称軸の周りにFET素子1を回転させると、90°回転ごとに元の形状が得られることが分かる。したがって、製造条件のばらつきが生じたとしても、FET素子1の特性のばらつきを抑制することができる。たとえば、ソース領域22A〜22D及びドレイン領域21の不純物濃度の空間分布に或る方向の偏りがあったとしても、FET素子1は、その偏りを打ち消す幾何学的対称性を有している。このため、不純物濃度の空間分布に偏りを持つ場合とそれを持たない場合とでFET素子1の特性に差が生じることを抑制できる。

【0026】

以上に説明したように本実施の形態のFET素子1では、バックゲート領域23A〜23Dの各々がゲート電極30の外周端部30pの頂点をなす2辺の延長線上をソース領域22A〜22Dのいずれかに近接する方向へ跨るように形成されているので、バックゲート領域23A〜23Dの占有面積が大きい。したがって、FET素子1の基板電位の安定化と素子特性のばらつき抑制とを実現することができる。

【0027】

また、ソース領域22A〜22Dの各々は、バックゲート領域23A〜23Dのいずれか2つの領域間に形成されており、ソース領域22A〜22Dの形成範囲は、ゲート電極30の四角形の4辺を介してドレイン領域21と対向する範囲に限定されている。よって、n型チャネルは、ゲート電極30の頂点付近には形成されないため、レイアウト設計段階でチャネル長とチャネル幅とを正確に定めることができ、設計コストの抑制と開発期間の短縮化とを実現することができる。このようにソース領域22A〜22Dの形成範囲が限定されている構造であっても、バックゲート領域23A〜23Dの各々がゲート電極30の外周端部30pの頂点をなす2辺の延長線上を跨るように形成されているので、FET素子1の基板電位の安定化と素子特性のばらつき抑制とを実現することが可能である。

【0028】

実施の形態2.

次に、本発明に係る実施の形態2について説明する。図7は、実施の形態2の半導体装置に含まれるFET素子のレイアウトの一例を概略的に示す平面図である。図7に示されるように、各々が実施の形態1のFET素子1と同じ構造を有するFET素子1A,1B,1A,1Bがマトリクス状に配列されている。図8は、これらFET素子1A,1B,1A,1Bの配置を模式的に示す図である。

【0029】

図7に示されるように、互いに隣接するFET素子1A,1Bは、1つのソース領域(S)を共有し、さらに、2つのバックゲート領域(BG)を共有している。このため、半導体装置におけるFET素子1A,1B,1A,1B全体の占有面積を小さくすることができる。

【0030】

また、同一符号を付されたFET素子1A,1Aは、同じFET素子群に属し、互いに並列に接続されている。すなわち、FET素子1A,1Aにおいて、ゲート電極(G)は互いに接続され、ドレイン領域(D)は互いに接続され、ソース領域(S)は互いに接続され、バックゲート領域(BG)は互いに接続される。一方、FET素子1B,1Bも、同じFET素子群に属し、互いに並列に接続されている。

【0031】

さらに、FET素子1A,1Aからなるトランジスタ素子群の幾何学的重心は、FET素子1B,1Bからなるトランジスタ素子群の幾何学的重心と同じである。よって、本実施の形態のFET素子1A,1B,1A,1Bのレイアウトは、コモンセントロイド配置となるように構成されている。したがって、FET素子間の素子特性のばらつきを抑制することができる。

【0032】

図9(A)〜図9(C)は、他のコモンセントロイド配置を例示する図である。図9(A),(B)は、4つのFET素子1A,1A,1A,1AからなるFET素子群の幾何学的重心と4つのFET素子1B,1B,1B,1BからなるFET素子群の幾何学的重心とが一致する配置を示す図である。また、図9(C)は、6つのFET素子1A,1A,1A,1A,1A,1AからなるFET素子群の幾何学的重心と4つのFET素子1B,1B,1B,1B,1B,1BからなるFET素子群の幾何学的重心とが一致する配置を示す図である。

【0033】

次に、図7のレイアウトを用いて図10のFET対を構成する場合の上層配線パターンについて説明する。図10は、一対のnチャネルFET2A,2Bからなる回路構成を示す図である。図11(A),(B),(C)及び図12(A),(B)は、図10の回路を作製するための上層配線パターンの一例の形成手順を示す図である。

【0034】

まず、図11(A)に示されるように、図7のFET素子1A,1B,1A,1Bの全てのバックゲート領域(BG)とソース領域(S)とに接続するメタル配線51を形成する。次に、図11(B)に示されるように、メタル配線51よりも上方の上層配線として、右側上方のFET素子1Aのゲート電極(G)と左側下方のFET素子1Aのゲート電極(G)とに接続するメタル配線52が形成される。次に、図11(C)に示されるように、メタル配線52よりも上方の上層配線として、左側上方のFET素子1Bのゲート電極(G)と右側下方のFET素子1Bのゲート電極(G)とに接続するメタル配線53が形成される。次に、図12(A)に示されるように、メタル配線53よりも上方の上層配線として、左側上方のFET素子1Bのドレイン領域(D)と右側下方のFET素子1Bのドレイン領域(D)とに接続するメタル配線54が形成される。そして、図12(B)に示されるように、メタル配線54よりも上方の上層配線として、右側上方のFET素子1Aのドレイン領域(D)と右側下方のFET素子1Aのドレイン領域(D)とに接続するメタル配線55が形成される。これにより、一対のFET素子1A,1AからなるnチャネルFET2Aと、一対のFET素子1B,1BからなるnチャネルFET2Bとを有する回路が作製される。

【0035】

図11(A),(B),(C)及び図12(A),(B)は、合計5層の上層配線51〜55の形成手順を示すものであったが、合計3層の上層配線を形成して図10の回路を作製することも可能である。図13(A),(B),(C)は、図10の回路を作製するための上層配線パターンの他の例の形成手順を示す図である。

【0036】

まず、図13(A)に示されるように、図7のFET素子1A,1B,1A,1Bの全てのバックゲート領域(BG)とソース領域(S)とに接続するメタル配線61が形成される。次に、図13(B)に示されるように、メタル配線61よりも上方の上層配線として、右側上方のFET素子1Aのゲート電極(G)と左側下方のFET素子1Aのゲート電極(G)とに接続するメタル配線62Aと、左側上方のFET素子1Bのドレイン領域(D)と右側下方のFET素子1Bのドレイン領域(D)とに接続するメタル配線62Bとが形成される。次に、図13(C)に示されるように、メタル配線62A,62Bよりも上方の上層配線として、左側上方のFET素子1Bのゲート電極(G)と右側下方のFET素子1Bのゲート電極(G)とに接続するメタル配線63Aと、右側上方のFET素子1Aのドレイン領域(D)と右側下方のFET素子1Aのドレイン領域(D)とに接続するメタル配線63Bとが形成される。これにより、一対のFET素子1A,1AからなるnチャネルFET2Aと、一対のFET素子1B,1BからなるnチャネルFET2Bとを有する回路が作製される。

【0037】

以上、合計4個のFET素子1A,1B,1A,1Bのコモンセントロイド配置に対する上層配線パターンを示したが、より多くのFET素子のコモンセントロイド配置に対して上層配線パターンを形成することもできる。図14は、多数のFET素子1,1,…をマトリクス状に配列してなるコモンセントロイド配置のレイアウトを概略的に示す平面図である。図15〜図19は、図14のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の形成手順を示す図である。

【0038】

まず、図15に示されるように、図14のFET素子1,1,…の全てのバックゲート領域(BG)とソース領域(S)とに接続するメタル配線71が形成される。次に、図16に示されるように、メタル配線71よりも上方の上層配線として、右斜め方向に互いに隣接するFET素子1,1のゲート電極(G)に接続するメタル配線72が形成される。次に、図17に示されるように、メタル配線72よりも上方の上層配線として、左斜め方向に互いに隣接するFET素子1,1のゲート電極(G)に接続するメタル配線73が形成される。次に、図18に示されるように、メタル配線73よりも上方の上層配線として、右斜め方向に互いに隣接するFET素子1,1のドレイン領域(D)に接続するメタル配線74が形成される。そして、図19に示されるように、メタル配線74よりも上方の上層配線として、左斜め方向に互いに隣接するFET素子1,1のドレイン領域(D)に接続するメタル配線75が形成される。

【0039】

以上に説明したように実施の形態1のFET素子1をマトリクス状に配列することで素子密度の高いコモンセントロイド配置を実現することができる。

【0040】

また、上述したように、図3のコンタクトプラグ45A,45B,45C,45Dは、チャネルが形成されない領域の直上に形成されている。よって、特許文献2に開示されている従来のレイアウト構造と比べると、バックゲート領域(G)の占有面積を大きくすることができるので、基板電位の安定化と素子特性のばらつき抑制とを向上させることができる。図20は、特許文献2に開示されている従来のレイアウト構造を示す図である。図20に示されるように、バックゲート領域(BG)は、レイアウトの最外周部にのみ配置されており、レイアウトの内側領域には配置されていない。しかも、ゲート電極配線(G)が格子状に形成されているのでバックゲート領域(BG)の占有面積を拡大することができない。また、バックゲート領域(BG)が最外周部よりも内側にないため、最外周部のトランジスタと内側(特に中央部)のトランジスタとの間で基板バイアス効果に差が生じ、これによりトランジスタ特性に差が生じるおそれがある。さらに、バックゲート領域(BG)が最外周部よりも内側にないため、外来ノイズによる過電圧(サージ)により内部のトランジスタ素子が静電破壊されてしまうおそれがある。

【0041】

これに対し、本実施の形態のレイアウト構造では、各FET素子が複数のバックゲート領域を有し、これらバックゲート領域が幾何学的対称性(線対称性及び回転対称性)を有する。したがって、本実施の形態のレイアウト構成は、回路規模が大きい場合にも、素子特性とESD耐性に優れている。また、FET素子間の特性のばらつきが抑制された大規模なトランジスタ群を作製することができる。

【0042】

実施の形態1,2の変形例.

以上、図面を参照して本発明に係る実施の形態について述べたが、これらは本発明の例示であり、上記以外の様々な形態を採用することもできる。たとえば、上記ゲート電極30の外周端部30p及び内周端部30iの平面視形状は矩形状であったが、これに限定されるものではない。ゲート電極30の外周端部30p及び内周端部30iの形状がN個の辺(Nは3以上の正整数)を有する正多角形であってよい。

【0043】

また、ドレイン容量を低い値にする観点からは、図3に示されるように、環状のゲート電極30で囲まれる内側の領域にドレイン領域21を形成し、ゲート電極30の外側の領域にソース領域22A〜22Dを形成することが好ましいが、これに限定されるものではない。ゲート電極30で囲まれる内側の領域にソース領域を形成し、ゲート電極30の外側の領域にドレイン領域を形成してもよい。

【0044】

そして、上記実施の形態1,2の構成は、全ての種類のFETに適用可能である。たとえば、nチャネルFETだけでなくpチャネルFETに適用することができ、エンハンスメント形FET、ディプレッション形FETなどの種類のFETにも適用可能である。

【符号の説明】

【0045】

1,1A,1B 電界効果トランジスタ素子(FET素子)、 10 半導体基板、 11 第1半導体層、 12 埋め込み拡散領域、 20 第2半導体層、 21 ドレイン領域、 22A〜22D ソース領域、 23A〜23D バックゲート領域、 25 ゲート絶縁膜、 30 ゲート電極、 40 層間絶縁膜、 42A〜42D,43A〜43D,45A〜45D,46 コンタクトプラグ、 Ex,Ey 延長線。

【技術分野】

【0001】

本発明は、半導体集積回路におけるMOSFET(Metal−Oxide−Semiconductor Field−Effect Transistor)などの電界効果トランジスタを含む半導体装置に関する。

【背景技術】

【0002】

多数の電界効果トランジスタ(FET)を含む半導体集積回路では、当該半導体集積回路の製造条件のばらつきによりFET間で閾値電圧などの素子特性のばらつきが生じ、歩留まり低下や半導体集積回路の動作不良の原因となることがある。製造条件のばらつきは、たとえば、リソグラフィ工程でのレジスト露光量の空間的なばらつき、あるいは、斜めイオン注入工程で導入された不純物濃度の空間分布のばらつきに起因して生じ得る。また、製造条件のばらつきが小さくても、パワー半導体素子などの熱源または応力発生源からの距離に応じてFET間で素子特性のばらつきが製造後に生じることもある。複数のFETを用いる高精度なアナログ集積回路(たとえば、差動型オペアンプやカレントミラー回路)では、FET間の素子特性のばらつきが抑制されるように素子のレイアウト設計を行うことが重要である。

【0003】

上記のような素子特性のばらつきを打ち消す方法としては、従来より、複数のFETの配置に幾何学的対称性を持たせるレイアウトが存在する。この種のレイアウトの1つとしては、コモンセントロイド(common centroid)配置が知られている。たとえば、差動型オペアンプの差動入力段やカレント・ミラー回路のように一対のMOSFETを有する半導体集積回路では、これらMOSFETの素子特性を互いにマッチングさせる必要がある。コモンセントロイド配置はこのようなマッチングが要求される回路に有効である。

【0004】

また、FETの形状自体に幾何学的対称性(たとえば、点対称性、線対称性もしくはこれらの組み合わせ)を持たせることで、FET間の特性のばらつき発生を抑制するレイアウトも提案されている。この種のレイアウトは、たとえば、特開2009−188223号公報(特許文献1)に開示されている。図1は、この特許文献1に開示されているレイアウト構造の平面図である。図1のFETは、中空矩形状のゲート電極130Gと、このゲート電極130Gに囲まれる領域に形成されたドレイン領域130Dと、ゲート電極130Gの外周を取り囲むように形成されたソース領域130Sとを有する。このFETは、X1軸及びY1軸に関してそれぞれ線対称構造を有している。チャネルは、ゲート電極130Gの内周と外周との間で360°の方向に形成される。このため、仮にソース領域130S及びドレイン領域130Dの不純物濃度の空間分布に偏りがある場合でも、その偏りに起因する素子特性のばらつき発生を抑制することができる。

【0005】

また、特開2008−78469号公報(特許文献2)には、図1のFETと類似する幾何学的対称性を有するFET構造が開示されている。図2は、特許文献2に開示されているレイアウト構造の平面図(上面図)である。図2のFETは、4つの辺を有する矩形環状のゲート電極131Gと、ゲート電極131Gの内側に形成されたドレイン電極131Dと、4つの辺の外側の領域にそれぞれ形成されたソース領域131Sa,131Sb,131Sc,131Sdと、ゲート電極131Gの4つの頂点の外側にそれぞれ形成されたバックゲート領域131BGa,131BGb,131BGc,131BGdとを有する。ゲート電極131Gは、図1のゲート電極130Gと同様の線対称構造を有している。ただし、図2のFETの構造は、単位ゲート幅当たりのドレイン容量を低減することを目的とする構造であり、素子特性のばらつき抑制を目的としたものではない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−188223号公報(図3,段落0020)

【特許文献2】特開2008−78469号公報(図1及び図2,段落0018〜0026)

【発明の概要】

【発明が解決しようとする課題】

【0007】

図1のFETは、バックゲート領域を持たないので、基板バイアス効果(基板電位の変化に応じてFETの閾値電圧が変化する現象)を利用してFETの特性を制御することができない。これに対し、図2のFETには、バックゲート領域131BGa〜131BGdが形成されている。しかしながら、これらバックゲート領域131BGa〜131BGdの配置では、基板電位を安定化させることに限界がある。特に、図2のFETの構造をマトリクス状に配列してなる半導体集積回路の場合、FET間の基板電位のばらつきを抑制することが難しいという問題がある。

【0008】

上記に鑑みて本発明の目的は、基板電位を十分に安定化させることができる半導体装置を提供することである。

【課題を解決するための手段】

【0009】

本発明の一態様による半導体装置は、複数の電界効果トランジスタ素子を備えた半導体装置であって、前記各電界効果トランジスタ素子は、半導体基板の主面上に形成され、前記主面を平面視したときにN角形(Nは3以上の整数)をなす外周端部と前記主面の面内方向に垂直な方向の貫通孔を形作る内周端部とを有する環状のゲート電極と、前記半導体基板の主面と前記ゲート電極との間に介在するゲート絶縁膜と、前記半導体基板の内部で前記貫通孔の直下方に形成され、ソース領域及びドレイン領域の一方をなす第1導電型の内側不純物拡散領域と、前記半導体基板の内部で前記N角形のN個の辺の外側にそれぞれ形成され、前記ソース領域及び前記ドレイン領域の他方をなす前記第1導電型のN個の外側不純物拡散領域と、前記半導体基板の内部で前記ゲート電極のN角形の頂点の外側に形成された、前記第1導電型とは逆の第2導電型のバックゲート領域とを有し、前記バックゲート領域は、前記N角形のN個の辺のうち当該頂点をなす2辺の少なくとも一方の延長線上を前記外側不純物拡散領域のいずれかに近接する方向へ跨るように形成されていることを特徴とする。

【発明の効果】

【0010】

本発明の一態様によれば、各バックゲート領域は、N角形状のゲート電極の頂点をなす2辺の少なくとも一方の延長線上を外側不純物拡散領域に近接する方向へ跨るように形成されているので、バックゲート領域の占有面積を大きくすることができる。したがって、電界効果トランジスタ素子の基板電位の安定化と素子特性のばらつき抑制とを実現することができる。

【図面の簡単な説明】

【0011】

【図1】特許文献1(特開2009−188223号公報)に開示されているレイアウト構造の平面図である。

【図2】特許文献2(特開2008−78469号公報)に開示されているレイアウト構造の平面図である。

【図3】本発明に係る実施の形態の半導体装置に含まれる電界効果トランジスタ素子(FET素子)のレイアウトを概略的に示す平面図である。

【図4】図3のFET素子のIV−IV線における概略断面図である。

【図5】図3のFET素子のV−V線における概略断面図である。

【図6】図3のFET素子1のVI−VI線における概略断面図である。

【図7】本発明に係る実施の形態2の半導体装置に含まれるFET素子群のレイアウトの一例を概略的に示す平面図である。

【図8】図7のFET素子群のコモンセントロイド配置を示す図である。

【図9】(A)〜(C)は、コモンセントロイド配置を例示する図である。

【図10】一対のnチャネルFETからなる回路構成を示す図である。

【図11】(A),(B),(C)は、図10の回路を作製するための上層配線パターンの一例の第1乃至第3の形成手順を示す図である。

【図12】(A),(B)は、図10の回路を作製するための上層配線パターンの一例の第4乃至第5の形成手順を示す図である。

【図13】(A),(B),(C)は、図10の回路を作製するための上層配線パターンの他の例の形成手順を示す図である。

【図14】多数のFET素子をマトリクス状に配列してなる半導体装置のレイアウトを概略的に示す図である。

【図15】図14のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第1の形成手順を示す図である。

【図16】図14のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第2の形成手順を示す図である。

【図17】図13のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第3の形成手順を示す図である。

【図18】図13のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第4の形成手順を示す図である。

【図19】図13のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の第5の形成手順を示す図である。

【図20】特許文献2に開示されている従来のレイアウト構造を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明に係る種々の実施の形態について図面を参照しつつ説明する。

【0013】

実施の形態1.

図3は、本発明に係る実施の形態1の半導体装置に含まれる電界効果トランジスタ素子(FET素子)1のレイアウトを概略的に示す平面図である。図3には、3次元直交座標系をなすX軸、Y軸及びZ軸が示されている。また、図4は、図3のFET素子1のIV−IV線における概略断面図を示し、図5は、図3のFET素子1のV−V線における概略断面図を示し、図6は、図3のFET素子1のVI−VI線における概略断面図を示している。図3のX軸及びY軸の方向は、図4〜図6の半導体基板10の上面すなわち主面に平行であり、Z軸の方向は、半導体基板10の主面に垂直である。図4〜図6には層間絶縁膜40の断面が示されているが、図3の平面図には、説明の便宜上、層間絶縁膜40は示されていない。なお、図4〜図6に示される断面構造は一例であり、FET素子1の断面構造はこれに限定されるものではない。

【0014】

図3に示されるように、FET素子1は、正四角形状の外周端部30pと内周端部30iとを持つ環状のゲート電極30を有する。またFET素子1は、ゲート電極30の内周端部30iの内側でゲート電極30に囲まれるように形成された第1導電型のドレイン領域(内側不純物拡散領域)21と、ゲート電極30の外側に形成された第1導電型のソース領域(外側不純物拡散領域)22A,22B,22C,22Dと、第1導電型とは逆の第2導電型の不純物拡散領域であるバックゲート領域23A,23B,23C,23Dとを有する。これらバックゲート領域23A,23B,23C,23Dは、外周端部30pの頂点の外側にそれぞれ形成されている。ゲート電極30の上面には、当該ゲート電極30とZ軸方向上方のメタル配線との間を電気的に接続するコンタクトプラグ45A,45B,45C,45Dが形成されている。説明の便宜上、図3では、ゲート電極30は記号「G」と、ドレイン領域21は記号「D」と、ソース領域22A〜22Dは記号「S」と、バックゲート領域23A〜23Dは記号「BG」とでそれぞれ表されている。他の図面でも同様の記号が使用される。

【0015】

本実施の形態のFET素子1は、ゲート電極30の直下にn型チャネルを形成するnチャネルFETであるため、第1導電型はn型、第2導電型はp型であるが、これに限定されるものではない。第1導電型をp型とし、第2導電型をn型としてpチャネルFETを構成してもよい。

【0016】

また、図3に示されるように、ソース領域22A,22B,22C,22Dの上面にはコンタクトプラグ42A,42B,42C,42Dがそれぞれ形成され、ドレイン領域21の上面にはコンタクトプラグ46が形成され、バックゲート領域23A,23B,23C,23Dの上面にはコンタクトプラグ43A,43B,43C,43Dがそれぞれ形成されている。これらコンタクトプラグ42A〜42D,43A〜43D,46は、Z軸方向上方のメタル配線パターン(図示せず)と不純物拡散領域22A〜22D,23A〜23D,46との間を電気的に接続するために形成されている。ただし、必ずしもこれらコンタクトプラグ42A〜42D,43A〜43Dの全てを形成する必要はなく、上層のメタル配線パターンに対応するコンタクトプラグのみを形成すればよい。

【0017】

本実施の形態のFET素子1は、図4〜図6の断面図に示されるように、半導体基板10と第1半導体層11と第2半導体層20とからなる半導体構造を用いて作製される。本実施の形態では、半導体基板10として、たとえばp型の単結晶シリコン基板を使用することができる。第1半導体層11は、半導体基板10の上面を下地として形成されたn型のエピタキシャル成長層(Si層)であり、第2半導体層20は、第1半導体層11の上面を下地として形成されたp型のエピタキシャル成長層(Si層)である。埋め込み拡散領域12は、p+型不純物拡散層である。この埋め込み拡散領域12は、たとえば、リソグラフィ工程とイオン注入工程とにより半導体基板10の上層部にボロンやフッ化ボロンなどのp型不純物を選択的にイオン注入した後に、半導体基板10上に第1半導体層11をエピタキシャル成長させ、その後、導入されたp型不純物を熱処理で拡散させることで形成することができる。

【0018】

また、ソース領域22A〜22D及びドレイン領域21は、リソグラフィ工程とイオン注入工程とにより、第2半導体層20の上層部にリンや砒素などのn型不純物を選択的にイオン注入し、注入されたn型不純物を熱処理で活性化させることで形成される。バックゲート領域23A〜23Dは、リソグラフィ工程とイオン注入工程とにより、第2半導体層20に対してボロンやフッ化ボロンなどのp型不純物をイオン注入し、注入されたp型不純物を熱処理で活性化させることで形成される。バックゲート領域23A〜23Dは、図4及び図5に例示されるように、埋め込み拡散領域12の上面に到達する深さを有する。

【0019】

ゲート電極30は、図5及び図6に示されるように、シリコン酸化薄膜などのゲート絶縁膜25上に形成されている。ゲート絶縁膜25は、たとえば、第2半導体層20の表面を熱酸化することで形成することができる。ゲート電極30は、たとえば減圧CVD(low−pressure Chemical Vapor Deposition)法により、全面に亘って、リンが高濃度にドープされたポリシリコンからなる導電性材料層を成膜し、この導電性材料層をリソグラフィ工程とエッチング工程とでパターニングして形成され得る。

【0020】

図3を参照すると、ゲート電極30の外周端部30pは、X−Y平面でX軸方向に延在する2辺とY軸方向に延在する2辺と4つの頂点とを有する。ゲート電極30は、X−Y平面で矩形状(正4角形状)をなす外周端部30pを有し、また、この外周端部30pの形状と相似形をなす環状の内周端部30iを有する。この内周端部30iは、図3及び図6に示されるように、層厚方向(Z軸方向)の貫通孔30hをゲート電極30の中心部に形作るものである。ドレイン領域21は、この貫通孔30hの直下方に形成されており、ドレイン領域21の平面視形状は、図3に示されるように貫通孔30hの形状と略同じである。

【0021】

ソース領域22A〜22Dとドレイン領域21との間にドレイン電圧が印加された状態で、ゲート電極30とソース領域22A〜22Dとの間に所定のゲート電圧(ゲート・ソース間電圧)が印加されると、ソース領域22A〜22Dとドレイン領域21との間でゲート電極30の直下領域にキャリアが誘起され、n型チャネルが形成される。この結果、ソース領域22A〜22Dとドレイン領域21との間にドレイン電流が流れる。

【0022】

図3を参照すると、ソース領域22A,22B,22C,22Dは、ゲート電極30の外周端部30pの4辺の外側にそれぞれ形成されている。また、右方のソース領域22Aは、バックゲート領域23A,23B間に形成され、下方のソース領域22Bは、バックゲート領域23B,23C間に形成され、左方のソース領域22Cは、バックゲート領域23C,23D間に形成され、上方のソース領域22Dは、バックゲート領域23D,23A間に形成されている。さらに、ソース領域22AのY軸方向の幅は、これに対応するドレイン領域21のY軸方向の幅(一辺の長さ)と略同じあり、ソース領域22BのX軸方向の幅は、これに対応するドレイン領域21のX軸方向の幅(一辺の長さ)と略同じあり、ソース領域22CのY軸方向の幅は、これに対応するドレイン領域21のY軸方向の幅(一辺の長さ)と略同じあり、ソース領域22DのX軸方向の幅は、これに対応するドレイン領域21のX軸方向の幅(一辺の長さ)と略同じある。よって、ソース領域22A〜22Dの形成範囲は、ゲート電極30の頂点を除く4辺を介してドレイン領域21と対向する範囲に限定される。このため、ソース領域22A〜22Dとドレイン領域21との間に形成されるn型チャネルは、ゲート電極30の頂点付近には形成されない。それ故、FET素子1を実際に作製する前にチャネルの形成範囲を正確に予測することができる。したがって、レイアウト設計段階でチャネル長とチャネル幅とを正確に定めることが可能である。

【0023】

また、図3を参照すると、バックゲート領域23A,23B,23C,23Dは、これら4つの頂点の外側にそれぞれ形成されており、ゲート電極30の外周端部30pを取り囲むように配列されている。また、各バックゲート領域は、最も近い頂点をなす2辺の延長線を跨ぐように形成される。たとえば、右側上方のバックゲート領域23Aは、外周端部30pの頂点をなす2辺の延長線Ex,Eyをそれぞれ跨ぐように形成されている。このため、図2の従来のレイアウトと比べると、バックゲート領域23A〜23Dの占有面積が大きく、FET素子1の基板電位の安定化と、ESD(Electro−Static Damage)耐性(静電気によるLSIの破壊耐性)の向上とを実現することができる。

【0024】

また、図3を参照すると、n型チャネルは、ゲート電極30の直下において、ドレイン領域21とソース領域22A間の領域と、ドレイン領域21とソース領域22B間の領域と、ドレイン領域21とソース領域22C間の領域と、ドレイン領域21とソース領域22C間の領域とにそれぞれ形成されるので、n型チャネルは、ゲート電極30の外周端部30pの頂点付近には形成されない。よって、ゲート電極30を上層のメタル配線に接続するコンタクトプラグ45A,45B,45C,45Dは、n型チャネルが形成されない領域の直上に形成されている。このため、層間絶縁膜40にコンタクトホールを形成するためのエッチング工程でオーバエッチングによりゲート電極30とゲート絶縁膜25とがエッチングされた場合でも、チャネル形成領域がそのエッチングの影響を受けることを確実に回避することができる。また、仮に、ゲート電極30が薄く、コンタクトプラグ45A,45B,45C,45Dの構成材料がゲート電極30に拡散した場合でも、チャネル特性に影響を与えることを確実に回避することが可能である。

【0025】

また、FET素子1は、X−Y平面において幾何学的対称性を有している。すなわち、FET素子1は、図3のFET素子1の幾何学的中心(すなわちゲート電極30の幾何学的中心)を通るX軸方向に沿ったX0軸と、同じ中心を通るY軸方向に沿ったY0軸という2つの軸を幾何学的対称軸として有している。よって、FET素子1は、X0軸とY0軸とに関してそれぞれ線対称構造を有する。また、FET素子1は、X0軸とY0軸との交差点を通り且つZ軸方向に沿った回転対称軸を有している。この回転対称軸の周りにFET素子1を回転させると、90°回転ごとに元の形状が得られることが分かる。したがって、製造条件のばらつきが生じたとしても、FET素子1の特性のばらつきを抑制することができる。たとえば、ソース領域22A〜22D及びドレイン領域21の不純物濃度の空間分布に或る方向の偏りがあったとしても、FET素子1は、その偏りを打ち消す幾何学的対称性を有している。このため、不純物濃度の空間分布に偏りを持つ場合とそれを持たない場合とでFET素子1の特性に差が生じることを抑制できる。

【0026】

以上に説明したように本実施の形態のFET素子1では、バックゲート領域23A〜23Dの各々がゲート電極30の外周端部30pの頂点をなす2辺の延長線上をソース領域22A〜22Dのいずれかに近接する方向へ跨るように形成されているので、バックゲート領域23A〜23Dの占有面積が大きい。したがって、FET素子1の基板電位の安定化と素子特性のばらつき抑制とを実現することができる。

【0027】

また、ソース領域22A〜22Dの各々は、バックゲート領域23A〜23Dのいずれか2つの領域間に形成されており、ソース領域22A〜22Dの形成範囲は、ゲート電極30の四角形の4辺を介してドレイン領域21と対向する範囲に限定されている。よって、n型チャネルは、ゲート電極30の頂点付近には形成されないため、レイアウト設計段階でチャネル長とチャネル幅とを正確に定めることができ、設計コストの抑制と開発期間の短縮化とを実現することができる。このようにソース領域22A〜22Dの形成範囲が限定されている構造であっても、バックゲート領域23A〜23Dの各々がゲート電極30の外周端部30pの頂点をなす2辺の延長線上を跨るように形成されているので、FET素子1の基板電位の安定化と素子特性のばらつき抑制とを実現することが可能である。

【0028】

実施の形態2.

次に、本発明に係る実施の形態2について説明する。図7は、実施の形態2の半導体装置に含まれるFET素子のレイアウトの一例を概略的に示す平面図である。図7に示されるように、各々が実施の形態1のFET素子1と同じ構造を有するFET素子1A,1B,1A,1Bがマトリクス状に配列されている。図8は、これらFET素子1A,1B,1A,1Bの配置を模式的に示す図である。

【0029】

図7に示されるように、互いに隣接するFET素子1A,1Bは、1つのソース領域(S)を共有し、さらに、2つのバックゲート領域(BG)を共有している。このため、半導体装置におけるFET素子1A,1B,1A,1B全体の占有面積を小さくすることができる。

【0030】

また、同一符号を付されたFET素子1A,1Aは、同じFET素子群に属し、互いに並列に接続されている。すなわち、FET素子1A,1Aにおいて、ゲート電極(G)は互いに接続され、ドレイン領域(D)は互いに接続され、ソース領域(S)は互いに接続され、バックゲート領域(BG)は互いに接続される。一方、FET素子1B,1Bも、同じFET素子群に属し、互いに並列に接続されている。

【0031】

さらに、FET素子1A,1Aからなるトランジスタ素子群の幾何学的重心は、FET素子1B,1Bからなるトランジスタ素子群の幾何学的重心と同じである。よって、本実施の形態のFET素子1A,1B,1A,1Bのレイアウトは、コモンセントロイド配置となるように構成されている。したがって、FET素子間の素子特性のばらつきを抑制することができる。

【0032】

図9(A)〜図9(C)は、他のコモンセントロイド配置を例示する図である。図9(A),(B)は、4つのFET素子1A,1A,1A,1AからなるFET素子群の幾何学的重心と4つのFET素子1B,1B,1B,1BからなるFET素子群の幾何学的重心とが一致する配置を示す図である。また、図9(C)は、6つのFET素子1A,1A,1A,1A,1A,1AからなるFET素子群の幾何学的重心と4つのFET素子1B,1B,1B,1B,1B,1BからなるFET素子群の幾何学的重心とが一致する配置を示す図である。

【0033】

次に、図7のレイアウトを用いて図10のFET対を構成する場合の上層配線パターンについて説明する。図10は、一対のnチャネルFET2A,2Bからなる回路構成を示す図である。図11(A),(B),(C)及び図12(A),(B)は、図10の回路を作製するための上層配線パターンの一例の形成手順を示す図である。

【0034】

まず、図11(A)に示されるように、図7のFET素子1A,1B,1A,1Bの全てのバックゲート領域(BG)とソース領域(S)とに接続するメタル配線51を形成する。次に、図11(B)に示されるように、メタル配線51よりも上方の上層配線として、右側上方のFET素子1Aのゲート電極(G)と左側下方のFET素子1Aのゲート電極(G)とに接続するメタル配線52が形成される。次に、図11(C)に示されるように、メタル配線52よりも上方の上層配線として、左側上方のFET素子1Bのゲート電極(G)と右側下方のFET素子1Bのゲート電極(G)とに接続するメタル配線53が形成される。次に、図12(A)に示されるように、メタル配線53よりも上方の上層配線として、左側上方のFET素子1Bのドレイン領域(D)と右側下方のFET素子1Bのドレイン領域(D)とに接続するメタル配線54が形成される。そして、図12(B)に示されるように、メタル配線54よりも上方の上層配線として、右側上方のFET素子1Aのドレイン領域(D)と右側下方のFET素子1Aのドレイン領域(D)とに接続するメタル配線55が形成される。これにより、一対のFET素子1A,1AからなるnチャネルFET2Aと、一対のFET素子1B,1BからなるnチャネルFET2Bとを有する回路が作製される。

【0035】

図11(A),(B),(C)及び図12(A),(B)は、合計5層の上層配線51〜55の形成手順を示すものであったが、合計3層の上層配線を形成して図10の回路を作製することも可能である。図13(A),(B),(C)は、図10の回路を作製するための上層配線パターンの他の例の形成手順を示す図である。

【0036】

まず、図13(A)に示されるように、図7のFET素子1A,1B,1A,1Bの全てのバックゲート領域(BG)とソース領域(S)とに接続するメタル配線61が形成される。次に、図13(B)に示されるように、メタル配線61よりも上方の上層配線として、右側上方のFET素子1Aのゲート電極(G)と左側下方のFET素子1Aのゲート電極(G)とに接続するメタル配線62Aと、左側上方のFET素子1Bのドレイン領域(D)と右側下方のFET素子1Bのドレイン領域(D)とに接続するメタル配線62Bとが形成される。次に、図13(C)に示されるように、メタル配線62A,62Bよりも上方の上層配線として、左側上方のFET素子1Bのゲート電極(G)と右側下方のFET素子1Bのゲート電極(G)とに接続するメタル配線63Aと、右側上方のFET素子1Aのドレイン領域(D)と右側下方のFET素子1Aのドレイン領域(D)とに接続するメタル配線63Bとが形成される。これにより、一対のFET素子1A,1AからなるnチャネルFET2Aと、一対のFET素子1B,1BからなるnチャネルFET2Bとを有する回路が作製される。

【0037】

以上、合計4個のFET素子1A,1B,1A,1Bのコモンセントロイド配置に対する上層配線パターンを示したが、より多くのFET素子のコモンセントロイド配置に対して上層配線パターンを形成することもできる。図14は、多数のFET素子1,1,…をマトリクス状に配列してなるコモンセントロイド配置のレイアウトを概略的に示す平面図である。図15〜図19は、図14のレイアウトを用いて図10の回路を作製するための上層配線パターンの一例の形成手順を示す図である。

【0038】

まず、図15に示されるように、図14のFET素子1,1,…の全てのバックゲート領域(BG)とソース領域(S)とに接続するメタル配線71が形成される。次に、図16に示されるように、メタル配線71よりも上方の上層配線として、右斜め方向に互いに隣接するFET素子1,1のゲート電極(G)に接続するメタル配線72が形成される。次に、図17に示されるように、メタル配線72よりも上方の上層配線として、左斜め方向に互いに隣接するFET素子1,1のゲート電極(G)に接続するメタル配線73が形成される。次に、図18に示されるように、メタル配線73よりも上方の上層配線として、右斜め方向に互いに隣接するFET素子1,1のドレイン領域(D)に接続するメタル配線74が形成される。そして、図19に示されるように、メタル配線74よりも上方の上層配線として、左斜め方向に互いに隣接するFET素子1,1のドレイン領域(D)に接続するメタル配線75が形成される。

【0039】

以上に説明したように実施の形態1のFET素子1をマトリクス状に配列することで素子密度の高いコモンセントロイド配置を実現することができる。

【0040】

また、上述したように、図3のコンタクトプラグ45A,45B,45C,45Dは、チャネルが形成されない領域の直上に形成されている。よって、特許文献2に開示されている従来のレイアウト構造と比べると、バックゲート領域(G)の占有面積を大きくすることができるので、基板電位の安定化と素子特性のばらつき抑制とを向上させることができる。図20は、特許文献2に開示されている従来のレイアウト構造を示す図である。図20に示されるように、バックゲート領域(BG)は、レイアウトの最外周部にのみ配置されており、レイアウトの内側領域には配置されていない。しかも、ゲート電極配線(G)が格子状に形成されているのでバックゲート領域(BG)の占有面積を拡大することができない。また、バックゲート領域(BG)が最外周部よりも内側にないため、最外周部のトランジスタと内側(特に中央部)のトランジスタとの間で基板バイアス効果に差が生じ、これによりトランジスタ特性に差が生じるおそれがある。さらに、バックゲート領域(BG)が最外周部よりも内側にないため、外来ノイズによる過電圧(サージ)により内部のトランジスタ素子が静電破壊されてしまうおそれがある。

【0041】

これに対し、本実施の形態のレイアウト構造では、各FET素子が複数のバックゲート領域を有し、これらバックゲート領域が幾何学的対称性(線対称性及び回転対称性)を有する。したがって、本実施の形態のレイアウト構成は、回路規模が大きい場合にも、素子特性とESD耐性に優れている。また、FET素子間の特性のばらつきが抑制された大規模なトランジスタ群を作製することができる。

【0042】

実施の形態1,2の変形例.

以上、図面を参照して本発明に係る実施の形態について述べたが、これらは本発明の例示であり、上記以外の様々な形態を採用することもできる。たとえば、上記ゲート電極30の外周端部30p及び内周端部30iの平面視形状は矩形状であったが、これに限定されるものではない。ゲート電極30の外周端部30p及び内周端部30iの形状がN個の辺(Nは3以上の正整数)を有する正多角形であってよい。

【0043】

また、ドレイン容量を低い値にする観点からは、図3に示されるように、環状のゲート電極30で囲まれる内側の領域にドレイン領域21を形成し、ゲート電極30の外側の領域にソース領域22A〜22Dを形成することが好ましいが、これに限定されるものではない。ゲート電極30で囲まれる内側の領域にソース領域を形成し、ゲート電極30の外側の領域にドレイン領域を形成してもよい。

【0044】

そして、上記実施の形態1,2の構成は、全ての種類のFETに適用可能である。たとえば、nチャネルFETだけでなくpチャネルFETに適用することができ、エンハンスメント形FET、ディプレッション形FETなどの種類のFETにも適用可能である。

【符号の説明】

【0045】

1,1A,1B 電界効果トランジスタ素子(FET素子)、 10 半導体基板、 11 第1半導体層、 12 埋め込み拡散領域、 20 第2半導体層、 21 ドレイン領域、 22A〜22D ソース領域、 23A〜23D バックゲート領域、 25 ゲート絶縁膜、 30 ゲート電極、 40 層間絶縁膜、 42A〜42D,43A〜43D,45A〜45D,46 コンタクトプラグ、 Ex,Ey 延長線。

【特許請求の範囲】

【請求項1】

複数の電界効果トランジスタ素子を備えた半導体装置であって、

前記各電界効果トランジスタ素子は、

半導体基板の主面上に形成され、前記主面を平面視したときにN角形(Nは3以上の整数)をなす外周端部と前記主面の面内方向に垂直な方向の貫通孔を形作る内周端部とを有する環状のゲート電極と、

前記半導体基板の主面と前記ゲート電極との間に介在するゲート絶縁膜と、

前記半導体基板の内部で前記貫通孔の直下方に形成され、ソース領域及びドレイン領域の一方をなす第1導電型の内側不純物拡散領域と、

前記半導体基板の内部で前記N角形のN個の辺の外側にそれぞれ形成され、前記ソース領域及び前記ドレイン領域の他方をなす前記第1導電型のN個の外側不純物拡散領域と、

前記半導体基板の内部で前記ゲート電極のN角形の頂点の外側に形成された、前記第1導電型とは逆の第2導電型のバックゲート領域と

を有し、

前記バックゲート領域は、前記N角形のN個の辺のうち当該頂点をなす2辺の少なくとも一方の延長線上を前記外側不純物拡散領域のいずれかに近接する方向へ跨るように形成されている

ことを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記バックゲート領域は、複数形成されており、

前記各外側不純物拡散領域は、当該N角形の各辺の両端をなす2つの頂点の一方の外側に形成された当該バックゲート領域の1つと、当該2つの頂点の他方の外側に形成された当該バックゲート領域の他の1つとの間に形成されている

ことを特徴とする半導体装置。

【請求項3】

請求項1または2に記載の半導体装置であって、前記各電界効果トランジスタ素子は、前記N角形の中心を通る少なくとも1つの幾何学的対称軸を有することを特徴とする半導体装置。

【請求項4】

請求項3に記載の半導体装置であって、前記N角形は四角形であることを特徴とする半導体装置。

【請求項5】

請求項3または4に記載の半導体装置であって、前記内周端部は、前記N角形と相似形をなすことを特徴とする半導体装置。

【請求項6】

請求項1から5のうちのいずれか1項に記載の半導体装置であって、

前記内側不純物拡散領域は、前記ドレイン領域であり、

前記N個の外側不純物拡散領域は、前記ソース領域である

ことを特徴とする半導体装置。

【請求項7】

請求項1から6のうちのいずれか1項に記載の半導体装置であって、

前記複数の電界効果トランジスタ素子は、前記半導体基板の当該主面に沿ってマトリクス状に配列されており、

前記複数の電界効果トランジスタ素子のうち互いに隣接する電界効果トランジスタ素子は、前記外側不純物拡散領域のいずれかを共有する

ことを特徴とする半導体装置。

【請求項8】

請求項7に記載の半導体装置であって、前記複数の電界効果トランジスタ素子のうち互いに隣接する電界効果トランジスタ素子は、前記バックゲート領域を共有することを特徴とする半導体装置。

【請求項9】

請求項7または8に記載の半導体装置であって、

前記複数の電界効果トランジスタ素子は、複数のトランジスタ素子群に分類されており、

前記複数のトランジスタ素子群の配置は、コモンセントロイド配置である

ことを特徴とする半導体装置。

【請求項10】

請求項9に記載の半導体装置であって、前記複数のトランジスタ素子群のうち同じトランジスタ素子群に属する2個以上の電界効果トランジスタ素子は、互いに並列に接続されていることを特徴とする半導体装置。

【請求項11】

請求項1から10のうちのいずれか1項に記載の半導体装置であって、

前記ゲート電極よりも上方に形成された上層配線と、

前記ゲート電極と前記上層配線との間に介在して前記ゲート電極の上面と前記上層配線との間に形成されたコンタクトホールを有する層間絶縁膜と、

前記コンタクトホール内に埋設され、前記ゲート電極の上面と前記上層配線との間を電気的に接続する複数のコンタクトプラグと

をさらに備え、

前記複数のコンタクトプラグは、前記N角形のN個の頂点付近に形成されている

ことを特徴とする半導体装置。

【請求項1】

複数の電界効果トランジスタ素子を備えた半導体装置であって、

前記各電界効果トランジスタ素子は、

半導体基板の主面上に形成され、前記主面を平面視したときにN角形(Nは3以上の整数)をなす外周端部と前記主面の面内方向に垂直な方向の貫通孔を形作る内周端部とを有する環状のゲート電極と、

前記半導体基板の主面と前記ゲート電極との間に介在するゲート絶縁膜と、

前記半導体基板の内部で前記貫通孔の直下方に形成され、ソース領域及びドレイン領域の一方をなす第1導電型の内側不純物拡散領域と、

前記半導体基板の内部で前記N角形のN個の辺の外側にそれぞれ形成され、前記ソース領域及び前記ドレイン領域の他方をなす前記第1導電型のN個の外側不純物拡散領域と、

前記半導体基板の内部で前記ゲート電極のN角形の頂点の外側に形成された、前記第1導電型とは逆の第2導電型のバックゲート領域と

を有し、

前記バックゲート領域は、前記N角形のN個の辺のうち当該頂点をなす2辺の少なくとも一方の延長線上を前記外側不純物拡散領域のいずれかに近接する方向へ跨るように形成されている

ことを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記バックゲート領域は、複数形成されており、

前記各外側不純物拡散領域は、当該N角形の各辺の両端をなす2つの頂点の一方の外側に形成された当該バックゲート領域の1つと、当該2つの頂点の他方の外側に形成された当該バックゲート領域の他の1つとの間に形成されている

ことを特徴とする半導体装置。

【請求項3】

請求項1または2に記載の半導体装置であって、前記各電界効果トランジスタ素子は、前記N角形の中心を通る少なくとも1つの幾何学的対称軸を有することを特徴とする半導体装置。

【請求項4】

請求項3に記載の半導体装置であって、前記N角形は四角形であることを特徴とする半導体装置。

【請求項5】

請求項3または4に記載の半導体装置であって、前記内周端部は、前記N角形と相似形をなすことを特徴とする半導体装置。

【請求項6】

請求項1から5のうちのいずれか1項に記載の半導体装置であって、

前記内側不純物拡散領域は、前記ドレイン領域であり、

前記N個の外側不純物拡散領域は、前記ソース領域である

ことを特徴とする半導体装置。

【請求項7】

請求項1から6のうちのいずれか1項に記載の半導体装置であって、

前記複数の電界効果トランジスタ素子は、前記半導体基板の当該主面に沿ってマトリクス状に配列されており、

前記複数の電界効果トランジスタ素子のうち互いに隣接する電界効果トランジスタ素子は、前記外側不純物拡散領域のいずれかを共有する

ことを特徴とする半導体装置。

【請求項8】

請求項7に記載の半導体装置であって、前記複数の電界効果トランジスタ素子のうち互いに隣接する電界効果トランジスタ素子は、前記バックゲート領域を共有することを特徴とする半導体装置。

【請求項9】

請求項7または8に記載の半導体装置であって、

前記複数の電界効果トランジスタ素子は、複数のトランジスタ素子群に分類されており、

前記複数のトランジスタ素子群の配置は、コモンセントロイド配置である

ことを特徴とする半導体装置。

【請求項10】

請求項9に記載の半導体装置であって、前記複数のトランジスタ素子群のうち同じトランジスタ素子群に属する2個以上の電界効果トランジスタ素子は、互いに並列に接続されていることを特徴とする半導体装置。

【請求項11】

請求項1から10のうちのいずれか1項に記載の半導体装置であって、

前記ゲート電極よりも上方に形成された上層配線と、

前記ゲート電極と前記上層配線との間に介在して前記ゲート電極の上面と前記上層配線との間に形成されたコンタクトホールを有する層間絶縁膜と、

前記コンタクトホール内に埋設され、前記ゲート電極の上面と前記上層配線との間を電気的に接続する複数のコンタクトプラグと

をさらに備え、

前記複数のコンタクトプラグは、前記N角形のN個の頂点付近に形成されている

ことを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2013−110308(P2013−110308A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−255093(P2011−255093)

【出願日】平成23年11月22日(2011.11.22)

【出願人】(308033711)ラピスセミコンダクタ株式会社 (898)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月22日(2011.11.22)

【出願人】(308033711)ラピスセミコンダクタ株式会社 (898)

【Fターム(参考)】

[ Back to top ]