半導体装置

【課題】低電圧動作を実現可能なレベルシフト回路を提供する。

【解決手段】入力電位は、GNDとVDDとの間で切り替わる。電源端子には、VDDよりも高いVDDOが印加される。レベルシフト回路は、クランプ回路と接続制御回路を備える。クランプ回路は、ソースが第1ノードに接続され、ドレインがP側出力端子に接続され、ゲートが電源端子に接続された第1NMOSトランジスタと、ソースが第1ノードに接続され、ドレインがN側出力端子に接続され、ゲートがグランド端子に接続された第1PMOSトランジスタと、を備える。入力電位がGNDとVDDの一方の場合、接続制御回路は、P側出力端子にVDDOを印加し、且つ、N側出力端子とグランド端子との間の電気的接続を遮断する。入力電位がGNDとVDDの他方の場合、接続制御回路は、N側出力端子にGNDを印加し、且つ、P側出力端子と電源端子との間の電気的接続を遮断する。

【解決手段】入力電位は、GNDとVDDとの間で切り替わる。電源端子には、VDDよりも高いVDDOが印加される。レベルシフト回路は、クランプ回路と接続制御回路を備える。クランプ回路は、ソースが第1ノードに接続され、ドレインがP側出力端子に接続され、ゲートが電源端子に接続された第1NMOSトランジスタと、ソースが第1ノードに接続され、ドレインがN側出力端子に接続され、ゲートがグランド端子に接続された第1PMOSトランジスタと、を備える。入力電位がGNDとVDDの一方の場合、接続制御回路は、P側出力端子にVDDOを印加し、且つ、N側出力端子とグランド端子との間の電気的接続を遮断する。入力電位がGNDとVDDの他方の場合、接続制御回路は、N側出力端子にGNDを印加し、且つ、P側出力端子と電源端子との間の電気的接続を遮断する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、レベルシフト回路を備える半導体装置に関する。

【背景技術】

【0002】

低電源電位VDDで動作する内部回路と高電源電位VDDOで動作する外部回路との間には、入出力インタフェース回路が設けられる。入出力インタフェース回路において内部回路の信号を外部回路の信号に変換するために、レベルシフト回路が一般的に用いられている。そのようなレベルシフト回路は、例えば、特許文献1(特開平9−172368号公報)や特許文献2(特開2005−260350号公報)に記載されている。

【0003】

図1は、特許文献1に記載されている半導体出力回路(レベルシフト回路)の構成を示している。この半導体出力回路は、低電源電位VDD側の入力信号を入力端子INから受け取り、その入力信号のレベルシフトを行い、高電源電位VDDO側の出力信号を出力端子OUTから出力する。

【0004】

より詳細には、図1に示される半導体出力回路は、第1のPMOSトランジスタ111、第2のPMOSトランジスタ112、ラッチ回路170、クランプ回路171、及びラッチ反転回路172を備えている。ラッチ回路170は、クロスカップルしたPMOSトランジスタ151、152で構成されている。クランプ回路171は、ゲートに低電源電位VDDが共通に印加されるPMOSトランジスタ153、154及びNMOSトランジスタ161、162で構成されている。ラッチ反転回路172は、相補信号がゲートに入力されるNMOSトランジスタ163、164で構成されている。

【0005】

図1に示されるような回路構成の場合、第1のPMOSトランジスタ111のゲート電位Vg11は、次のような値を取る(特許文献1の図2を参照)。すなわち、第1のPMOSトランジスタ111のゲート電位Vg11は、Highレベルの場合に高電源電位VDDOとなり、Lowレベルの場合に低電源電位VDDとなる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平9−172368号公報

【特許文献2】特開2005−260350号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

近年、半導体装置の低電圧化が進んでおり、高電源電位VDDOも低下してきている。例えば、LPDDR2規格(モバイル系のメモリインターフェース規格の一つ)では、出力電圧は1.2Vで規定されており、入出力回路をこの1.2Vで動作させる必要がある。

【0008】

一例として、高電源電位VDDOが1.2Vであり、低電源電位VDDが1.0Vであるような低電圧動作を考える。この場合、上述の図1で示された回路構成では、Lowレベルのゲート電位Vg11は1.0Vとなる。この時の第1のPMOSトランジスタ111のゲート−ソース電圧Vgsは、1.2V−1.0V=0.2Vであり、第1のPMOSトランジスタ111をONさせるには不十分である。すなわち、図1で示された回路構成では、低電圧動作が不可能である。

【課題を解決するための手段】

【0009】

以下に、[発明を実施するための形態]で使用される番号・符号を用いて、[課題を解決するための手段]を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための形態]との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0010】

本発明の1つの観点において、レベルシフト回路(10)を具備する半導体装置が提供される。レベルシフト回路(10)は、グランド電位(GND)が印加されるグランド端子と、グランド電位(GND)と第1電源電位(VDD)との間で電位が切り替わる入力信号(SI)が入力される入力端子(IN)と、第1電源電位(VDD)よりも高い第2電源電位(VDDO)が印加される電源端子と、P側出力端子(OUT−P)と、N側出力端子(OUT−N)と、クランプ回路(40)と、接続制御回路(20,30)と、を備える。

【0011】

クランプ回路(40)は、P側出力端子(OUT−P)とN側出力端子(OUT−N)との間に接続されている。クランプ回路(40)は、ソースが第1ノード(NF)に接続され、ドレインがP側出力端子(OUT−P)に接続され、ゲートが電源端子に接続された第1NMOSトランジスタ(MN42)と、ソースが第1ノード(NF)に接続され、ドレインがN側出力端子(OUT−N)に接続され、ゲートがグランド端子に接続された第1PMOSトランジスタ(MP42)と、を備える。

【0012】

接続制御回路(20,30)は、入力信号(SI)の電位に応じて、グランド端子と電源端子とP側出力端子(OUT−P)とN側出力端子(OUT−N)との間の電気的接続を制御する。より詳細には、入力信号(SI)の電位がグランド電位(GND)と第1電源電位(VDD)の一方の場合、接続制御回路(20,30)は、P側出力端子(OUT−P)に第2電源電位(VDDO)を印加し、且つ、N側出力端子(OUT−N)とグランド端子との間の電気的接続を遮断する。入力信号(SI)の電位がグランド電位(GND)と第1電源電位(VDD)の他方の場合、接続制御回路(20,30)は、N側出力端子(OUT−N)にグランド電位(GND)を印加し、且つ、P側出力端子(OUT−P)と電源端子との間の電気的接続を遮断する。

【0013】

クランプ回路(40)は、更に、ソースが第2ノード(NE)に接続され、ドレインが第3ノード(NC)に接続され、ゲートが電源端子に接続された第2NMOSトランジスタ(MN41)と、ソースが第2ノード(NE)に接続され、ドレインが第4ノード(ND)に接続され、ゲートがグランド端子に接続された第2PMOSトランジスタ(MP41)と、を備えてもよい。入力信号(SI)の電位がグランド電位(GND)と第1電源電位(VDD)の一方の場合、接続制御回路(20,30)は、第4ノード(ND)にグランド電位(GND)を印加し、且つ、第3ノード(NC)と電源端子との間の電気的接続を遮断する。入力信号(SI)の電位がグランド電位(GND)と第1電源電位(VDD)の他方の場合、接続制御回路(20,30)は、第3ノード(NC)に第2電源電位(VDDO)を印加し、且つ、第4ノード(ND)とグランド端子との間の電気的接続を遮断する。

【0014】

入力信号(SI)の反転信号は、反転入力信号である。接続制御回路(20,30)は、ソースが電源端子に接続され、ドレインが第3ノード(NC)に接続され、ゲートが第1ノード(NF)に接続された第3PMOSトランジスタ(MP21)と、ソースが電源端子に接続され、ドレインがP側出力端子(OUT−P)に接続され、ゲートが第2ノード(NE)に接続された第4PMOSトランジスタ(MP22)と、を備えてもよい。接続制御回路(20,30)は、更に、ソースがグランド端子に接続され、ドレインが第4ノード(ND)に接続され、ゲートに入力信号(SI)と反転入力信号の一方が入力される第3NMOSトランジスタ(MN31)と、ソースがグランド端子に接続され、ドレインがN側出力端子(OUT−N)に接続され、ゲートに入力信号(SI)と反転入力信号の他方が入力される第4NMOSトランジスタ(MN32)と、を備えてもよい。

【0015】

レベルシフト回路(10)のP側出力端子(OUT−P)から出力される信号は、P側制御信号(SP)である。HighレベルのP側制御信号(SP)の電位は、第2電源電位(VDDO)である。LowレベルのP側制御信号(SP)の電位は、グランド電位(GND)から第1PMOSトランジスタ(MP42)の閾値電圧(Vthp)の分だけ増加した電位である。HighレベルとLowレベルの電位がP側制御信号(SP)のものと同じである信号は、P側信号である。

【0016】

レベルシフト回路(10)のN側出力端子(OUT−N)から出力される信号は、N側制御信号(SN)である。HighレベルのN側制御信号(SN)の電位は、第2電源電位(VDDO)から第1NMOSトランジスタ(MN42)の閾値電圧(Vthn)の分だけ低下した電位である。LowレベルのN側制御信号(SN)の電位は、グランド電位(GND)である。HighレベルとLowレベルの電位がN側制御信号(SN)のものと同じである信号は、N側信号である。

【0017】

本発明に係る半導体装置は、更に、出力回路(50)を具備してもよい。その出力回路(50)は、P側信号が入力されるP側入力端子(IN−P)と、N側信号が入力されるN側入力端子(IN−N)と、出力端子(OUT)と、を備える。その出力回路(50)は、更に、ソースが電源端子に接続され、ドレインが出力端子(OUT)に接続され、ゲートがP側入力端子(IN−P)に接続された第5PMOSトランジスタ(MP51)と、ソースがグランド端子に接続され、ドレインが出力端子(OUT)に接続され、ゲートがN側入力端子(IN−N)に接続された第5NMOSトランジスタ(MN51)と、を備える。

【0018】

出力回路(50)は、更に、ソースが第5PMOSトランジスタ(MP51)のドレインに接続され、ドレインが出力端子(OUT)に接続され、ゲートに所定のゲート電位(VDP)が印加される第6PMOSトランジスタ(MP52)と、ソースが第5NMOSトランジスタ(MN51)のドレインに接続され、ドレインが出力端子(OUT)に接続され、ゲートに第1電源電位(VDD)が印加される第6NMOSトランジスタ(MN52)と、を備えてもよい。

【0019】

第2電源電位(VDDO)がVDDOであり、第6PMOSトランジスタ(MP52)の閾値電圧及び耐圧がそれぞれVthp、Vbであるとき、所定のゲート電位(VDP)は、VDDO−Vb以上、且つ、Vb−Vthp以下である。

【0020】

本発明に係る半導体装置は、更に、論理ゲート(60,70,80)を備えてもよい。論理ゲート(60,70,80)は、P側信号の1つであるP側入力信号(SPin)が入力されるP側論理入力端子(IN−P)と、N側信号の1つであるN側入力信号(SNin)が入力されるN側論理入力端子(IN−N)と、P側信号の1つであるP側出力信号(SPout)が出力されるP側論理出力端子(OUT−P)と、N側信号の1つであるN側出力信号(SNout)が出力されるN側論理出力端子(OUT−N)と、論理演算部と、を備える。論理演算部は、P側入力信号(SPin)及びN側入力信号(SNin)に基づいて所定の論理演算を行い、P側出力信号(SPout)及びN側出力信号(SNout)を生成する。

【0021】

論理演算部は、ソースが第5ノード(NI,NK,NM)に接続され、ドレインがP側論理出力端子(OUT−P)に接続され、ゲートが電源端子に接続された第7NMOSトランジスタ(MN62,MN73,MN83)と、ソースが第5ノード(NI,NK,NM)に接続され、ドレインがN側論理出力端子(OUT−N)に接続され、ゲートがグランド端子に接続された第7PMOSトランジスタ(MP62,MP73,MP83)と、を備えてもよい。P側出力信号(SPout)及びN側出力信号(SNout)がHighレベルである場合、論理演算部は、P側論理出力端子(OUT−P)に第2電源電位(VDDO)を印加し、且つ、N側論理出力端子(OUT−N)とグランド端子との間の電気的接続を遮断する。P側出力信号(SPout)及びN側出力信号(SNout)がLowレベルである場合、論理演算部は、N側論理出力端子(OUT−N)にグランド電位(GND)を印加し、且つ、P側論理出力端子(OUT−P)と電源端子との間の電気的接続を遮断する。

【発明の効果】

【0022】

本発明に係るレベルシフト回路によれば、低電圧動作の場合であっても、出力段のトランジスタを十分にONさせることが可能となる。

【図面の簡単な説明】

【0023】

【図1】図1は、特許文献1(特開平9−172368号公報)に記載されている半導体出力回路の構成を示す回路図である。

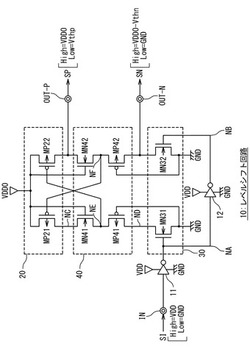

【図2】図2は、本発明の実施の形態に係るレベルシフト回路の構成を示す回路図である。

【図3】図3は、入力信号がLowレベルである場合のレベルシフト回路の状態を示す回路図である。

【図4】図4は、入力信号がHighレベルである場合のレベルシフト回路の状態を示す回路図である。

【図5】図5は、レベルシフト回路の動作を示すタイミングチャートである。

【図6】図6は、レベルシフト回路中の各トランジスタに印加される電圧を要約的に示すテーブルである。

【図7】図7は、本発明の実施の形態に係る出力回路の構成を示す回路図である。

【図8】図8は、入力信号がLowレベルである場合の出力回路の状態を示す回路図である。

【図9】図9は、入力信号がHighレベルである場合の出力回路の状態を示す回路図である。

【図10】図10は、出力回路中の各トランジスタに印加される電圧を要約的に示すテーブルである。

【図11】図11は、本発明の実施の形態に係るレベルシフト回路及び出力回路を備える半導体装置を示すブロック図である。

【図12】図12は、本発明の実施の形態に係るインバータの構成を示す回路図である。

【図13】図13は、入力信号がLowレベルである場合のインバータの状態を示す回路図である。

【図14】図14は、入力信号がHighレベルである場合のインバータの状態を示す回路図である。

【図15】図15は、本発明の実施の形態に係るNANDゲートの構成を示す回路図である。

【図16】図16は、第1入力信号がLowレベルであり第2入力信号がHighレベルである場合のNANDゲートの状態を示す回路図である。

【図17】図17は、第1入力信号がHighレベルであり第2入力信号がHighレベルである場合のNANDゲートの状態を示す回路図である。

【図18】図18は、本発明の実施の形態に係るNORゲートの構成を示す回路図である。

【図19】図19は、第1入力信号がLowレベルであり第2入力信号がLowレベルである場合のNORゲートの状態を示す回路図である。

【図20】図20は、第1入力信号がHighレベルであり第2入力信号がLowレベルである場合のNORゲートの状態を示す回路図である。

【図21】図21は、本発明の実施の形態に係るレベルシフト回路、論理回路及び出力回路を備える半導体装置を示すブロック図である。

【図22】図22は、本発明の実施の形態に係るレベルシフト回路、論理回路及び出力回路を備える半導体装置の一例を示すブロック図である。

【図23】図23は、比較例を示すブロック図である。

【発明を実施するための形態】

【0024】

添付図面を参照して、本発明の実施の形態を説明する。

【0025】

1.レベルシフト回路

1−1.構成

図2は、本発明の実施の形態に係るレベルシフト回路10の構成を示す回路図である。このレベルシフト回路10は、入出力インタフェース回路において内部回路の信号を外部回路の信号に変換するために用いられる。内部回路は、内部電源電位である低電源電位VDD(第1電源電位)で動作し、外部回路は、外部電源電位である高電源電位VDDO(第2電源電位)で動作する。高電源電位VDDOは、低電源電位VDDより高い。例えば、高電源電位VDDOは1.2Vであり、低電源電位VDDは1.0Vである。

【0026】

図2に示されるように、レベルシフト回路10は、入力端子IN、P側出力端子OUT−P、及びN側出力端子OUT−Nを備えている。つまり、レベルシフト回路10は、1入力2出力の構成を有している。

【0027】

入力端子INには、内部回路からの信号が入力信号SIとして入力される。入力信号SIの電位は、低電源電位VDDとグランド電位GND(0V)との間で切り替わる。つまり、Highレベルの入力信号SIの電位は低電源電位VDDであり、Lowレベルの入力信号SIの電位はグランド電位GNDである。

【0028】

P側出力端子OUT−Pからは、P側制御信号SPが出力される。後に詳しく説明されるように、P側制御信号SPの電位は、高電源電位VDDOと電位Vthpとの間で切り替わる。つまり、HighレベルのP側制御信号SPの電位は高電源電位VDDOであり、LowレベルのP側制御信号SPの電位はVthpである。ここで、電位Vthpは、レベルシフト回路10内で用いられるPMOSトランジスタの閾値電圧であり、例えば0.5Vである。

【0029】

N側出力端子OUT−Nからは、N側制御信号SNが出力される。後に詳しく説明されるように、N側制御信号SNの電位は、電位VDDO−Vthnとグランド電位GNDとの間で切り替わる。つまり、HighレベルのN側制御信号SNの電位はVDDO−Vthnであり、LowレベルのN側制御信号SNの電位はグランド電位GNDである。ここで、電位Vthnは、レベルシフト回路10内で用いられるNMOSトランジスタの閾値電圧であり、例えば0.5Vである。

【0030】

P側制御信号SPとN側制御信号SNは同相(in-phase)である。つまり、P側制御信号SPがHighレベルのとき、N側制御信号SNもHighレベルである。また、P側制御信号SPがLowレベルのとき、N側制御信号SNもLowレベルである。

【0031】

図2に示されるように、レベルシフト回路10は更に、インバータ11、12、ラッチ回路20、ラッチ反転回路30、及びクランプ回路40を備えている。

【0032】

インバータ11の入力は入力端子INに接続されており、その出力はノードNAに接続されている。また、インバータ11は、VDD端子(低電源電位VDDが印加される端子)とグランド端子(グランド電位GNDが印加される端子)に接続されている。入力信号SIの電位が低電源電位VDD(Highレベル)の場合、インバータ11は、グランド電位GND(Lowレベル)をノードNAに出力する。一方、入力信号SIの電位がグランド電位GND(Lowレベル)の場合、インバータ11は、低電源電位VDD(Highレベル)をノードNAに出力する。つまり、ノードNAには、入力信号SIの論理レベルが反転した反転入力信号が現れる。

【0033】

インバータ12の入力はノードNAに接続されており、その出力はノードNBに接続されている。また、インバータ12は、VDD端子とグランド端子に接続されている。ノードNAの電位が低電源電位VDD(Highレベル)の場合、インバータ12は、グランド電位GND(Lowレベル)をノードNBに出力する。一方、ノードNAの電位がグランド電位GND(Lowレベル)の場合、インバータ12は、低電源電位VDD(Highレベル)をノードNBに出力する。つまり、ノードNBには、入力信号SIと同じ論理レベルの信号が現れる。

【0034】

ラッチ回路20は、PMOSトランジスタMP21とPMOSトランジスタMP22を備えている。PMOSトランジスタMP21のソース、ドレイン、及びゲートは、それぞれ、VDDO端子(高電源電位VDDOが印加される端子)、ノードNC、及びノードNFに接続されている。PMOSトランジスタMP22のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、P側出力端子OUT−P、及びノードNEに接続されている。

【0035】

ラッチ反転回路30は、NMOSトランジスタMN31とNMOSトランジスタMN32を備えている。NMOSトランジスタMN31のソース、ドレイン、及びゲートは、それぞれ、グランド端子、ノードND、及びノードNAに接続されている。NMOSトランジスタMN32のソース、ドレイン、及びゲートは、それぞれ、グランド端子、N側出力端子OUT−N、及びノードNBに接続されている。NMOSトランジスタMN31のゲート(ノードNA)には反転入力信号が入力され、NMOSトランジスタMN32のゲート(ノードNB)には入力信号SIが入力される。従って、NMOSトランジスタMN31、MN32の一方がONするとき、他方はOFFする。尚、ノードNAに入力信号SIが現れ、ノードNBに反転入力信号が現れてもよい。その場合、各ノードの論理レベルが逆になるだけで、同じ議論が適用可能である。

【0036】

後に説明されるように、ラッチ回路20とラッチ反転回路30は、「接続制御回路」として機能する。この接続制御回路は、入力信号SIの電位に応じて、グランド端子とVDDO端子とP側出力端子OUT−PとN側出力端子OUT−Nとの間の電気的接続を制御する。

【0037】

クランプ回路40は、P側出力端子OUT−PとN側出力端子OUT−Nとの間に接続されている。より詳細には、クランプ回路40は、NMOSトランジスタMN41、NMOSトランジスタMN42、PMOSトランジスタMP41、及びPMOSトランジスタMP42を備えている。NMOSトランジスタMN41のソース、ドレイン、及びゲートは、それぞれ、ノードNE、ノードNC、及びVDDO端子に接続されている。NMOSトランジスタMN42のソース、ドレイン、及びゲートは、それぞれ、ノードNF、P側出力端子OUT−P、及びVDDO端子に接続されている。PMOSトランジスタMP41のソース、ドレイン、及びゲートは、それぞれ、ノードNE、ノードND、及びグランド端子に接続されている。PMOSトランジスタMP42のソース、ドレイン、及びゲートは、それぞれ、ノードNF、N側出力端子OUT−N、及びグランド端子に接続されている。

【0038】

1−2.動作

図3は、入力信号SIがLowレベルである場合のレベルシフト回路10の状態を示している。ノードNAの電位は低電源電位VDDであり、NMOSトランジスタMN31はONする。一方、ノードNBの電位はグランド電位GNDであり、NMOSトランジスタMN32はOFFする。つまり、N側出力端子OUT−Nとグランド端子との間の電気的接続が遮断される。

【0039】

NMOSトランジスタMN31がONするため、ノードNDとグランド端子とが電気的に接続され、ノードNDにはNMOSトランジスタMN31を通してグランド電位GNDが印加される。更に、PMOSトランジスタMP41のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNEの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP41の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN41はONし、ノードNCの電位も“Vthp”となる。

【0040】

ノードNEの電位がVthpであるため、PMOSトランジスタMP22はONする。その結果、P側出力端子OUT−PとVDDO端子とが電気的に接続され、P側出力端子OUT−PにはPMOSトランジスタMP22を通して高電源電位VDDOが印加される。つまり、P側制御信号SPの電位は、高電源電位VDDO(Highレベル)となる。

【0041】

NMOSトランジスタMN42のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNFの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN42の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。よって、PMOSトランジスタMP21はOFFし、ノードNCとVDDO端子との間の電気的接続が遮断される。

【0042】

ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP42はONし、N側出力端子OUT−Nの電位も“VDDO−Vthn”となる。つまり、N側制御信号SNの電位は、“VDDO−Vthn”(Highレベル)となる。

【0043】

このように、入力信号SIがLowレベルである場合、ラッチ回路20(接続制御回路)は、P側出力端子OUT−PとVDDO端子とを電気的に接続することによって、P側出力端子OUT−Pに高電源電位VDDOを印加する。これにより、P側制御信号SPの電位は、高電源電位VDDO(Highレベル)となる。また、ラッチ反転回路30(接続制御回路)は、N側出力端子OUT−Nとグランド端子との間の電気的接続を遮断する。更に、P側出力端子OUT−PとN側出力端子OUT−Nの間には、ゲート電位が高電源電位VDDOに固定されたNMOSトランジスタMN42が介在している。これにより、N側出力端子OUT−Nの電位、すなわち、N側制御信号SNの電位は、“VDDO−Vthn”(Highレベル)となる。

【0044】

図4は、入力信号SIがHighレベルである場合のレベルシフト回路10の状態を示している。ノードNAの電位はグランド電位GNDであり、NMOSトランジスタMN31はOFFする。つまり、ノードNDとグランド端子との間の電気的接続が遮断される。一方、ノードNBの電位は低電源電位VDDであり、NMOSトランジスタMN32はONする。

【0045】

NMOSトランジスタMN32がONするため、N側出力端子OUT−Nとグランド端子とが電気的に接続され、N側出力端子OUT−NにはNMOSトランジスタMN32を通してグランド電位GNDが印加される。これにより、N側制御信号SNの電位は、グランド電位GND(Lowレベル)となる。

【0046】

PMOSトランジスタMP42のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNFの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP42の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN42はONし、P側出力端子OUT−Pの電位も“Vthp”となる。つまり、P側制御信号SPの電位は、“Vthp”(Lowレベル)となる。

【0047】

ノードNFの電位がVthpであるため、PMOSトランジスタMP21はONする。その結果、ノードNCとVDDO端子とが電気的に接続され、ノードNCにはPMOSトランジスタMP21を通して高電源電位VDDOが印加される。NMOSトランジスタMN41のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNEの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN41の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。よって、PMOSトランジスタMP22はOFFし、P側出力端子OUT−PとVDDO端子との間の電気的接続が遮断される。また、ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP41はONし、ノードNDの電位も“VDDO−Vthn”となる。

【0048】

このように、入力信号SIがHighレベルである場合、ラッチ反転回路30(接続制御回路)は、N側出力端子OUT−Nとグランド端子とを電気的に接続することによって、N側出力端子OUT−Nにグランド電位GNDを印加する。これにより、N側制御信号SNの電位は、グランド電位GND(Lowレベル)となる。また、ラッチ回路20(接続制御回路)は、P側出力端子OUT−PとVDDO端子との間の電気的接続を遮断する。更に、P側出力端子OUT−PとN側出力端子OUT−Nの間には、ゲート電位がグランド電位GNDに固定されたPMOSトランジスタMP42が介在している。これにより、P側出力端子OUT−Pの電位、すなわち、P側制御信号SPの電位は、“Vthp”(Lowレベル)となる。

【0049】

図5は、レベルシフト回路10の動作を示すタイミングチャートである。図5には、入力端子IN(入力信号SI)、N側出力端子OUT−N(N側制御信号SN)、ノードNF、及びP側出力端子OUT−P(P側制御信号SP)のそれぞれの電位が示されている。ここで、例えば、VDDO=1.2V、VDD=1.0V、GND=0.0V、Vthp,Vthn=0.5Vであるとする。

【0050】

入力信号SIの電位は、低電源電位VDD(High)とグランド電位GND(Low)との間で切り替わる。N側制御信号SNの電位は、電位VDDO−Vthn(High)とグランド電位GND(Low)との間で切り替わる。P側制御信号SPの電位は、高電源電位VDDO(High)と電位Vthp(Low)との間で切り替わる。また、P側制御信号SPとN側制御信号SNは同相である。尚、図3〜図5で示された例において、入力信号SIと出力制御信号(SP,SN)とは逆相であるが、それらは同相であってもよい。

【0051】

1−3.耐圧

図6は、上記の図3及び図4で示されたそれぞれの状態において各トランジスタに印加される電圧を示している。Vgsはゲート−ソース間の電圧(電位差)であり、Vgdはゲート−ドレイン間の電圧(電位差)であり、Vdsはドレイン−ソース間の電圧(電位差)である。各トランジスタの耐圧がVbである場合、その耐圧Vbは次の条件を満たせばよい。

【0052】

Vb≧Vthn

Vb≧Vthp

Vb≧VDDO−Vthn

Vb≧VDDO−Vthp

Vb≧VDDO−Vthn−Vthp

Vb≧VDD

【0053】

一例として、VDDO=1.2V、VDD=1.0V、Vthp=0.5V、Vthn=0.5Vである場合を考える。この場合、耐圧Vbは次の条件を満たせばよい。

【0054】

Vb≧Vthn=0.5V

Vb≧Vthp=0.5V

Vb≧VDDO−Vthn=1.2V−0.5V=0.7V

Vb≧VDDO−Vthp=1.2V−0.5V=0.7V

Vb≧VDDO−Vthn−Vthp=1.2V−0.5V−0.5V=0.2V

Vb≧VDD=1.0V

【0055】

従って、図3及び図4で示された状態を考えた場合、各トランジスタの耐圧Vbは、1.0V以上であればよい。逆に言えば、耐圧Vbとして、高電源電位VDDOほどの高レベルは不要である。つまり、本実施の形態では、各トランジスタの耐圧Vbを、高電源電位VDDOより低くすることが可能である(VDDO>Vb)。これは、レベルシフト回路10内のトランジスタを全て「低耐圧トランジスタ」で構成可能であることを意味する。レベルシフト回路10を低耐圧トランジスタだけで構成することにより、製造コストと回路面積が削減される。

【0056】

クランプ回路40は「耐圧保護回路」としての役割を果たしているとも言える。クランプ回路40により、N側出力端子OUT−NとノードNDの電位の上限値は、“VDDO−Vthn”となる。これにより、グランド電位GNDが印加されるNMOSトランジスタMN31、MN32及びPMOSトランジスタMP41、MP42の破壊が防止される。また、クランプ回路40により、P側出力端子OUT−PとノードNCの電位の下限値は、“Vthp”となる。これにより、高電源電位VDDOが印加されるPMOSトランジスタMP21、MP22及びNMOSトランジスタMN41、MN42の破壊が防止される。

【0057】

1−4.効果

以上に説明されたように、本実施の形態に係るレベルシフト回路10は、入力信号SIのレベルシフトにより、2種類の制御信号SP、SNを生成する。例えば、それら制御信号SP、SNを、出力回路中のトランジスタのON/OFF制御に用いることができる(この例については、次の第2節においても詳しく説明される)。

【0058】

P側制御信号SPを、高電源電位VDDOを出力するための「PMOS出力トランジスタ」のゲート制御信号として用いることを考える。P側制御信号SPの電位は、高電源電位VDDO(High)と電位Vthp(Low)との間で切り替わる。Lowレベルの電位がVthpであるため、VDDO=1.2V程度の低電圧動作の場合であっても、PMOS出力トランジスタを十分にONさせることが可能となる。また、PMOS出力トランジスタのゲート電位がVthp以上となるため、PMOS出力トランジスタを低耐圧トランジスタで構成することも可能となる。この場合、出力回路の製造コストと回路面積が削減される。

【0059】

N側制御信号SNを、グランド電位GNDを出力するための「NMOS出力トランジスタ」のゲート制御信号として用いることを考える。N側制御信号SNの電位は、電位VDDO−Vthn(High)とグランド電位GND(Low)との間で切り替わる。Highレベルの電位がVDDO−Vthnであるため、NMOS出力トランジスタを十分にONさせることが可能となる。また、NMOS出力トランジスタのゲート電位がVDDO−Vthn以下となるため、NMOS出力トランジスタを低耐圧トランジスタで構成することも可能となる。この場合、出力回路の製造コストと回路面積が削減される。

【0060】

また、上述の通り、クランプ回路40は、レベルシフト回路10内のトランジスタの破壊を防止する「耐圧保護回路」としての役割も果たしている。レベルシフト回路10内のトランジスタを全て低耐圧トランジスタで構成することも可能であり、その場合、製造コストと回路面積が削減される。

【0061】

2.出力回路

2−1.構成

図7は、本実施の形態に係る出力回路50の構成を示す回路図である。この出力回路50は、上述のP側制御信号SP及びN側制御信号SNをサポートしており、それら制御信号SP、SNに応じた出力信号SOを生成、出力することができる。より詳細には、出力回路50は、P側入力端子IN−P、N側入力端子IN−N及び出力端子OUTを備えている。

【0062】

P側入力端子IN−Pには、上記のレベルシフト回路10から出力されたP側制御信号SP、あるいは、P側制御信号SPと同じ電位変化をする信号が入力される。そのような信号は、以下、「P側信号SP」と参照される。P側信号SPの電位は、高電源電位VDDOと電位Vthpとの間で切り替わる。つまり、HighレベルのP側信号SPの電位は高電源電位VDDOであり、LowレベルのP側信号SPの電位はVthpである。

【0063】

N側入力端子IN−Nには、上記のレベルシフト回路10から出力されたN側制御信号SN、あるいは、N側制御信号SNと同じ電位変化をする信号が入力される。そのような信号は、以下、「N側信号SN」と参照される。N側信号SNの電位は、電位VDDO−Vthnとグランド電位GNDとの間で切り替わる。つまり、HighレベルのN側信号SNの電位はVDDO−Vthnであり、LowレベルのN側信号SNの電位はグランド電位GNDである。

【0064】

P側信号SPとN側信号SNは同相(in-phase)である。つまり、P側信号SPがHighレベルのとき、N側信号SNもHighレベルである。また、P側信号SPがLowレベルのとき、N側信号SNもLowレベルである。この同相のP側信号SP及びN側信号SNが、入力信号として出力回路50に入力される。

【0065】

出力端子OUTからは、出力信号SOが出力される。出力信号SOの電位は、高電源電位VDDOとグランド電位GNDとの間で切り替わる。つまり、Highレベルの出力信号SOの電位はVDDOであり、Lowレベルの出力信号SOの電位はグランド電位GNDである。

【0066】

図7に示されるように、出力回路50は更に、PMOSトランジスタMP51、MP52、NMOSトランジスタMN51、MN52、及び中間電位生成回路52を備えている。中間電位生成回路52は、所定のゲート電位VDPを生成、出力する。

【0067】

PMOSトランジスタMP51のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、ノードNG、及びP側入力端子IN−Pに接続されている。ノードNGは、PMOSトランジスタMP52を介して、出力端子OUTに接続されている。具体的には、PMOSトランジスタMP52のソースがノードNGに接続されており、そのドレインが出力端子OUTに接続されている。また、PMOSトランジスタMP52のゲートには、中間電位生成回路52によって生成された所定のゲート電位VDPが印加される。

【0068】

NMOSトランジスタMN51のソース、ドレイン、及びゲートは、それぞれ、グランド端子、ノードNH、及びN側入力端子IN−Nに接続されている。ノードNHは、NMOSトランジスタMN52を介して、出力端子OUTに接続されている。具体的には、NMOSトランジスタMN52のソースがノードNHに接続されており、そのドレインが出力端子OUTに接続されている。また、NMOSトランジスタMN52のゲートには、低電源電位VDDが印加される。

【0069】

2−2.動作

図8は、入力信号SP、SNがLowレベルである場合の出力回路50の状態を示している。P側入力端子IN−Pの電位、すなわち、PMOSトランジスタMP51のゲート電位はVthpである。よって、PMOSトランジスタMP51は十分にONする。一方、N側入力端子IN−Nの電位、すなわち、NMOSトランジスタMN51のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN51はOFFし、ノードNHとグランド端子との間の電気的接続は遮断される。

【0070】

PMOSトランジスタMP51がONするため、ノードNGとVDDO端子とが電気的に接続され、ノードNGにはPMOSトランジスタMP51を通して高電源電位VDDOが印加される。更に、ゲート電位VDPが適切に設定されたPMOSトランジスタMP52もONし、出力端子OUTの電位も高電源電位VDDOとなる。よって、出力信号SOの電位は、高電源電位VDDO(Highレベル)となる。

【0071】

その一方で、NMOSトランジスタMN52のゲート電位は低電源電位VDDに固定されているため、そのソース電位、すなわち、ノードNHの電位は、ゲート電位(低電源電位VDD)からNMOSトランジスタMN52の閾値電圧Vthnの分だけ低下した“VDD−Vthn”となる。つまり、ノードNHに高電源電位VDDOが印加されることが防止されている。NMOSトランジスタMN52は、グランド電位GNDが印加されるNMOSトランジスタMN51の耐圧保護の役割を果たしている。

【0072】

図9は、入力信号SP、SNがHighレベルである場合の出力回路50の状態を示している。P側入力端子IN−Pの電位、すなわち、PMOSトランジスタMP51のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP51はOFFし、ノードNGとVDDO端子との間の電気的接続は遮断される。一方、N側入力端子IN−Nの電位、すなわち、NMOSトランジスタMN51のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN51は十分にONする。

【0073】

NMOSトランジスタMN51がONするため、ノードNHとグランド端子とが電気的に接続され、ノードNHにはNMOSトランジスタMN51を通してグランド電位GNDが印加される。更に、ゲート電位が低電源電位VDDであるNMOSトランジスタMN52もONし、出力端子OUTの電位もグランド電位GNDとなる。よって、出力信号SOの電位は、グランド電位GND(Lowレベル)となる。

【0074】

その一方で、PMOSトランジスタMP52のゲート電位はVDPに固定されているため、そのソース電位、すなわち、ノードNGの電位は、ゲート電位VDPからPMOSトランジスタMP52の閾値電圧Vthnの分だけ増加した“VDP+Vthp”となる。つまり、ノードNGにグランド電位GNDが印加されることが防止されている。PMOSトランジスタMP52は、高電源電位VDDOが印加されるPMOSトランジスタMP51の耐圧保護の役割を果たしている。

【0075】

2−3.耐圧

図10は、上記の図8及び図9で示されたそれぞれの状態において各トランジスタに印加される電圧を示している。Vgsはゲート−ソース間の電圧(電位差)であり、Vgdはゲート−ドレイン間の電圧(電位差)であり、Vdsはドレイン−ソース間の電圧(電位差)である。各トランジスタの耐圧がVbである場合、その耐圧Vbは次の条件を満たせばよい。

【0076】

Vb≧Vthn

Vb≧Vthp

Vb≧VDDO−Vthn

Vb≧VDDO−Vthp

Vb≧VDDO−VDD

Vb≧VDDO−VDD+Vthn

Vb≧VDD−Vthn

Vb≧VDD

Vb≧VDDO−VDP

Vb≧VDDO−VDP−Vthp

Vb≧VDP

Vb≧VDP+Vthp

【0077】

また、これら条件から、ゲート電位VDPは、次の関係式「Vb−Vthp≧VDP≧VDDO−Vb」を満たせばよいことが分かる。一例として、VDDO=1.2V、VDD=1.0V、Vthp=0.5V、Vthn=0.5Vである場合を考える。この場合、耐圧Vbは次の条件を満たせばよい。

【0078】

Vb≧Vthn=0.5V

Vb≧Vthp=0.5V

Vb≧VDDO−Vthn=1.2V−0.5V=0.7V

Vb≧VDDO−Vthp=1.2V−0.5V=0.7V

Vb≧VDDO−VDD=1.2V−1.0V=0.2V

Vb≧VDDO−VDD+Vthn=1.2V−1.0V+0.5V=0.7V

Vb≧VDD−Vthn=1.0V−0.5V=0.5V

Vb≧VDD=1.0V

Vb≧VDDO−VDP=1.2V−VDP

Vb≧VDDO−VDP−Vthp=1.2V−VDP−0.5V=0.7V−VDP

Vb≧VDP

Vb≧VDP+Vthp=VDP+0.5V

【0079】

各トランジスタが低耐圧トランジスタであり、耐圧Vbが例えば1.0Vである場合を考える。この場合、ゲート電位VDPは、1.0V−0.5V≧VDP≧1.2V−1.0Vを満たせばよい。例えば、ゲート電位VDPは0.3Vに設定される。これにより、全ての条件が満たされる。そして、出力回路50を低耐圧トランジスタだけで構成することにより、製造コストと回路面積が削減される。

【0080】

2−4.効果

図11は、本実施の形態に係るレベルシフト回路10と出力回路50を備える半導体装置(出力インタフェース回路)である。レベルシフト回路10は、入力信号SIを受け取り、その入力信号SIに応じたP側制御信号SP及びN側制御信号SNを生成する。出力回路50は、レベルシフト回路10から出力されるP側制御信号SP及びN側制御信号SNを受け取り、それに応じた出力信号SOを出力する。入力信号SIの電位が低電源電位VDD(Highレベル)の場合、出力信号SOの電位は高電源電位VDDO(Highレベル)である。入力信号SIの電位がグランド電位GND(Lowレベル)の場合、出力信号SOの電位はグランド電位GND(Lowレベル)である。但し、入出力論理関係は逆であってもよい。

【0081】

本実施の形態によれば、VDDO=1.2V程度の低電圧動作の場合であっても、各トランジスタを十分にONさせることが可能である。また、各トランジスタを低耐圧トランジスタで構成することも可能である。すなわち、本実施の形態によれば、耐圧を保護しつつ、低電圧動作が可能な出力インタフェース回路を実現することが可能となる。

【0082】

3.論理ゲート

第3節では、P側信号SP及びN側信号SNをサポートする「論理ゲート」を提案する。論理ゲートに入力されるP側信号SP及びN側信号SNは、それぞれ、P側入力信号SPin及びN側入力信号SNinである。論理ゲートから出力されるP側信号SP及びN側信号SNは、それぞれ、P側出力信号SPout及びN側出力信号SNoutである。論理ゲートは、入力信号(SPin、SNin)を受け取り、その入力信号に基づいて所定の論理演算を行い、その論理演算の結果を出力信号(SPout、SNout)として出力する。

【0083】

3−1.インバータ

図12は、本実施の形態に係るインバータ60の構成を示す回路図である。インバータ60は、入力端子(IN−P、IN−N)及び出力端子(OUT−P、OUT−N)を備えている。入力端子(IN−P、IN−N)には、同相の入力信号(SPin、SNin)が入力される。出力端子(OUT−P、OUT−N)からは、同相の出力信号(SPout、SNout)が出力される。

【0084】

インバータ60は更に、論理演算部を備えている。論理演算部は、入力信号(SPin、SNin)の論理を反転させ、その反転論理を出力信号(SPout、SNout)として出力する。より詳細には、論理演算部は、PMOSトランジスタMP61及びNMOSトランジスタMN61を備えている。PMOSトランジスタMP61のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、P側出力端子OUT−P、及びP側入力端子IN−Pに接続されている。NMOSトランジスタMN61のソース、ドレイン、及びゲートは、それぞれ、グランド端子、N側出力端子OUT−N、及びN側入力端子IN−Nに接続されている。

【0085】

論理演算部は更に、P側出力端子OUT−PとN側出力端子OUT−Nとの間に接続されたクランプ回路62を備えている。クランプ回路62は、NMOSトランジスタMN62及びPMOSトランジスタMP62を備えている。NMOSトランジスタMN62のソース、ドレイン、及びゲートは、それぞれ、ノードNI、P側出力端子OUT−P、及びVDDO端子に接続されている。PMOSトランジスタMP62のソース、ドレイン、及びゲートは、それぞれ、ノードNI、N側出力端子OUT−N、及びグランド端子に接続されている。

【0086】

図13は、入力信号(SPin、SNin)がLowレベルである場合のインバータ60の状態を示している。P側入力端子IN−Pの電位、すなわち、PMOSトランジスタMP61のゲート電位はVthpである。よって、PMOSトランジスタMP61は十分にONする。一方、N側入力端子IN−Nの電位、すなわち、NMOSトランジスタMN61のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN61はOFFし、N側出力端子OUT−Nとグランド端子との間の電気的接続は遮断される。

【0087】

PMOSトランジスタMP61がONするため、P側出力端子OUT−PとVDDO端子とが電気的に接続され、P側出力端子OUT−PにはPMOSトランジスタMP61を通して高電源電位VDDOが印加される。つまり、P側出力信号SPoutの電位は、高電源電位VDDO(Highレベル)となる。

【0088】

NMOSトランジスタMN62のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNIの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN62の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP62はONし、N側出力端子OUT−Nの電位も“VDDO−Vthn”となる。つまり、N側出力信号SNoutの電位は、“VDDO−Vthn”(Highレベル)となる。

【0089】

図14は、入力信号(SPin、SNin)がHighレベルである場合のインバータ60の状態を示している。P側入力端子IN−Pの電位、すなわち、PMOSトランジスタMP61のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP61はOFFし、P側出力端子OUT−PとVDDO端子との間の電気的接続は遮断される。一方、N側入力端子IN−Nの電位、すなわち、NMOSトランジスタMN61のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN61は十分にONする。

【0090】

NMOSトランジスタMN61がONするため、N側出力端子OUT−Nとグランド端子とが電気的に接続され、N側出力端子OUT−NにはNMOSトランジスタMN61を通してグランド電位GNDが印加される。つまり、N側出力信号SNoutの電位は、グランド電位GND(Lowレベル)となる。

【0091】

PMOSトランジスタMP62のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNIの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP62の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN62はONし、P側出力端子OUT−Pの電位も“Vthp”となる。つまり、P側出力信号SPoutの電位は、“Vthp”(Lowレベル)となる。

【0092】

レベルシフト回路10のクランプ回路40と同様に、インバータ60のクランプ回路62は、「耐圧保護回路」としての役割も果たしている。クランプ回路62により、N側出力端子OUT−Nの電位の上限値は“VDDO−Vthn”となる。これにより、グランド電位GNDが印加されるNMOSトランジスタMN61の破壊が防止される。また、クランプ回路62により、P側出力端子OUT−Pの電位の下限値は“Vthp”となる。これにより、高電源電位VDDOが印加されるPMOSトランジスタMP61の破壊が防止される。

【0093】

各トランジスタの耐圧に関しても、レベルシフト回路10の場合と同様であり、各トランジスタを低耐圧トランジスタで構成可能である。

【0094】

3−2.NANDゲート

図15は、本実施の形態に係るNANDゲート70の構成を示す回路図である。NANDゲート70は、第1入力端子(IN1−P、IN1−N)、第2入力端子(IN2−P、IN2−N)、及び出力端子(OUT−P、OUT−N)を備えている。第1入力端子(IN1−P、IN1−N)には、同相の第1入力信号(SPin1、SNin1)が入力される。第2入力端子(IN2−P、IN2−N)には、同相の第2入力信号(SPin2、SNin2)が入力される。出力端子(OUT−P、OUT−N)からは、同相の出力信号(SPout、SNout)が出力される。

【0095】

NANDゲート70は更に、論理演算部を備えている。論理演算部は、第1入力信号(SPin1、SNin1)及び第2入力信号(SPin2、SNin2)に基づいてNAND論理演算を行い、出力信号(SPout、SNout)を生成する。より詳細には、論理演算部は、PMOSトランジスタMP71、MP72、及びNMOSトランジスタMN71、MN72を備えている。PMOSトランジスタMP71のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、P側出力端子OUT−P、及び第1P側入力端子IN1−Pに接続されている。PMOSトランジスタMP72のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、P側出力端子OUT−P、及び第2P側入力端子IN2−Pに接続されている。NMOSトランジスタMN71のソース、ドレイン、及びゲートは、それぞれ、ノードNJ、N側出力端子OUT−N、及び第1N側入力端子IN1−Nに接続されている。NMOSトランジスタMN72のソース、ドレイン、及びゲートは、それぞれ、グランド端子、ノードNJ、及び第2N側入力端子IN2−Nに接続されている。

【0096】

論理演算部は更に、P側出力端子OUT−PとN側出力端子OUT−Nとの間に接続されたクランプ回路73を備えている。クランプ回路73は、NMOSトランジスタMN73及びPMOSトランジスタMP73を備えている。NMOSトランジスタMN73のソース、ドレイン、及びゲートは、それぞれ、ノードNK、P側出力端子OUT−P、及びVDDO端子に接続されている。PMOSトランジスタMP73のソース、ドレイン、及びゲートは、それぞれ、ノードNK、N側出力端子OUT−N、及びグランド端子に接続されている。

【0097】

図16は、第1入力信号(SPin1、SNin1)がLowレベルであり、第2入力信号(SPin2、SNin2)がHighレベルである場合のNANDゲート70の状態を示している。

【0098】

第1P側入力端子IN1−Pの電位、すなわち、PMOSトランジスタMP71のゲート電位はVthpである。よって、PMOSトランジスタMP71は十分にONする。第2P側入力端子IN2−Pの電位、すなわち、PMOSトランジスタMP72のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP72はOFFする。

【0099】

第2N側入力端子IN2−Nの電位、すなわち、NMOSトランジスタMN72のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN72はONし、ノードNJにグランド電位GNDが印加される。第1N側入力端子IN1−Nの電位、すなわち、NMOSトランジスタMN71のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN71はOFFする。結果として、N側出力端子OUT−Nとグランド端子との間の電気的接続は遮断される。

【0100】

PMOSトランジスタMP71がONするため、P側出力端子OUT−PとVDDO端子とが電気的に接続され、P側出力端子OUT−PにはPMOSトランジスタMP71を通して高電源電位VDDOが印加される。つまり、P側出力信号SPoutの電位は、高電源電位VDDO(Highレベル)となる。

【0101】

NMOSトランジスタMN73のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNKの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN73の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP73はONし、N側出力端子OUT−Nの電位も“VDDO−Vthn”となる。つまり、N側出力信号SNoutの電位は、“VDDO−Vthn”(Highレベル)となる。

【0102】

第1入力信号(SPin1、SNin1)と第2入力信号(SPin2、SNin2)のうち少なくとも一方がLowレベルであれば、出力信号(SPout、SNout)や出力端子(OUT−P、OUT−N)の電位状態は、図16で示されたものと同じになる。

【0103】

図17は、第1入力信号(SPin1、SNin1)と第2入力信号(SPin2、SNin2)が共にHighレベルである場合のNANDゲート70の状態を示している。

【0104】

第1P側入力端子IN1−Pの電位、すなわち、PMOSトランジスタMP71のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP71はOFFする。第2P側入力端子IN2−Pの電位、すなわち、PMOSトランジスタMP72のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP72はOFFする。結果として、P側出力端子OUT−PとVDDO端子との間の電気的接続は遮断される。

【0105】

第1N側入力端子IN1−Nの電位、すなわち、NMOSトランジスタMN71のゲート電位は“VDDO−Vthn”である。また、第2N側入力端子IN2−Nの電位、すなわち、NMOSトランジスタMN72のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN71、MN72は共に十分にONする。

【0106】

NMOSトランジスタMN71、MN72が共にONするため、N側出力端子OUT−Nとグランド端子とが電気的に接続され、N側出力端子OUT−NにはNMOSトランジスタMN71、MN72を通してグランド電位GNDが印加される。つまり、N側出力信号SNoutの電位は、グランド電位GND(Lowレベル)となる。

【0107】

PMOSトランジスタMP73のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNKの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP73の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN73はONし、P側出力端子OUT−Pの電位も“Vthp”となる。つまり、P側出力信号SPoutの電位は、“Vthp”(Lowレベル)となる。

【0108】

レベルシフト回路10のクランプ回路40と同様に、NANDゲート70のクランプ回路73は、「耐圧保護回路」としての役割も果たしている。クランプ回路73により、N側出力端子OUT−Nの電位の上限値は“VDDO−Vthn”となる。これにより、グランド電位GNDが印加されるNMOSトランジスタMN71、MN72の破壊が防止される。また、クランプ回路73により、P側出力端子OUT−Pの電位の下限値は“Vthp”となる。これにより、高電源電位VDDOが印加されるPMOSトランジスタMP71、MP72の破壊が防止される。

【0109】

各トランジスタの耐圧に関しても、レベルシフト回路10の場合と同様であり、各トランジスタを低耐圧トランジスタで構成可能である。

【0110】

3−3.NORゲート

図18は、本実施の形態に係るNORゲート80の構成を示す回路図である。NORゲート80は、第1入力端子(IN1−P、IN1−N)、第2入力端子(IN2−P、IN2−N)、及び出力端子(OUT−P、OUT−N)を備えている。第1入力端子(IN1−P、IN1−N)には、同相の第1入力信号(SPin1、SNin1)が入力される。第2入力端子(IN2−P、IN2−N)には、同相の第2入力信号(SPin2、SNin2)が入力される。出力端子(OUT−P、OUT−N)からは、同相の出力信号(SPout、SNout)が出力される。

【0111】

NORゲート80は更に、論理演算部を備えている。論理演算部は、第1入力信号(SPin1、SNin1)及び第2入力信号(SPin2、SNin2)に基づいてNOR論理演算を行い、出力信号(SPout、SNout)を生成する。より詳細には、論理演算部は、PMOSトランジスタMP81、MP82、及びNMOSトランジスタMN81、MN82を備えている。PMOSトランジスタMP81のソース、ドレイン、及びゲートは、それぞれ、ノードNL、P側出力端子OUT−P、及び第1P側入力端子IN1−Pに接続されている。PMOSトランジスタMP82のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、ノードNL、及び第2P側入力端子IN2−Pに接続されている。NMOSトランジスタMN81のソース、ドレイン、及びゲートは、それぞれ、グランド端子、N側出力端子OUT−N、及び第1N側入力端子IN1−Nに接続されている。NMOSトランジスタMN82のソース、ドレイン、及びゲートは、それぞれ、グランド端子、N側出力端子OUT−N、及び第2N側入力端子IN2−Nに接続されている。

【0112】

論理演算部は更に、P側出力端子OUT−PとN側出力端子OUT−Nとの間に接続されたクランプ回路83を備えている。クランプ回路83は、NMOSトランジスタMN83及びPMOSトランジスタMP83を備えている。NMOSトランジスタMN83のソース、ドレイン、及びゲートは、それぞれ、ノードNM、P側出力端子OUT−P、及びVDDO端子に接続されている。PMOSトランジスタMP83のソース、ドレイン、及びゲートは、それぞれ、ノードNM、N側出力端子OUT−N、及びグランド端子に接続されている。

【0113】

図19は、第1入力信号(SPin1、SNin1)と第2入力信号(SPin2、SNin2)が共にLowレベルである場合のNORゲート80の状態を示している。

【0114】

第1P側入力端子IN1−Pの電位、すなわち、PMOSトランジスタMP81のゲート電位はVthpである。また、第2P側入力端子IN2−Pの電位、すなわち、PMOSトランジスタMP82のゲート電位はVthpである。よって、PMOSトランジスタMP81、MP82は共に十分にONする。

【0115】

第1N側入力端子IN1−Nの電位、すなわち、NMOSトランジスタMN81のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN81はOFFする。第2N側入力端子IN2−Nの電位、すなわち、NMOSトランジスタMN82のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN82はOFFする。結果として、N側出力端子OUT−Nとグランド端子との間の電気的接続は遮断される。

【0116】

PMOSトランジスタMP81、MP82が共にONするため、P側出力端子OUT−PとVDDO端子とが電気的に接続され、P側出力端子OUT−PにはPMOSトランジスタMP81、MP82を通して高電源電位VDDOが印加される。つまり、P側出力信号SPoutの電位は、高電源電位VDDO(Highレベル)となる。

【0117】

NMOSトランジスタMN83のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNMの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN83の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP83はONし、N側出力端子OUT−Nの電位も“VDDO−Vthn”となる。つまり、N側出力信号SNoutの電位は、“VDDO−Vthn”(Highレベル)となる。

【0118】

図20は、第1入力信号(SPin1、SNin1)がHighレベルであり、第2入力信号(SPin2、SNin2)がLowレベルである場合のNORゲート80の状態を示している。

【0119】

第2P側入力端子IN2−Pの電位、すなわち、PMOSトランジスタMP82のゲート電位はVthpである。よって、PMOSトランジスタMP82はONし、ノードNLに高電源電位VDDOが印加される。第1P側入力端子IN1−Pの電位、すなわち、PMOSトランジスタMP81のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP81はOFFする。結果として、P側出力端子OUT−PとVDDO端子との間の電気的接続は遮断される。

【0120】

第1N側入力端子IN1−Nの電位、すなわち、NMOSトランジスタMN81のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN81は十分にONする。第2N側入力端子IN2−Nの電位、すなわち、NMOSトランジスタMN82のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN82はOFFする。

【0121】

NMOSトランジスタMN81が共にONするため、N側出力端子OUT−Nとグランド端子とが電気的に接続され、N側出力端子OUT−NにはNMOSトランジスタMN81を通してグランド電位GNDが印加される。つまり、N側出力信号SNoutの電位は、グランド電位GND(Lowレベル)となる。

【0122】

PMOSトランジスタMP83のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNMの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP83の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN83はONし、P側出力端子OUT−Pの電位も“Vthp”となる。つまり、P側出力信号SPoutの電位は、“Vthp”(Lowレベル)となる。

【0123】

第1入力信号(SPin1、SNin1)と第2入力信号(SPin2、SNin2)のうち少なくとも一方がHighレベルであれば、出力信号(SPout、SNout)や出力端子(OUT−P、OUT−N)の電位状態は、図20で示されたものと同じになる。

【0124】

レベルシフト回路10のクランプ回路40と同様に、NORゲート80のクランプ回路83は、「耐圧保護回路」としての役割も果たしている。クランプ回路83により、N側出力端子OUT−Nの電位の上限値は“VDDO−Vthn”となる。これにより、グランド電位GNDが印加されるNMOSトランジスタMN81、MN82の破壊が防止される。また、クランプ回路83により、P側出力端子OUT−Pの電位の下限値は“Vthp”となる。これにより、高電源電位VDDOが印加されるPMOSトランジスタMP81、MP82の破壊が防止される。

【0125】

各トランジスタの耐圧に関しても、レベルシフト回路10の場合と同様であり、各トランジスタを低耐圧トランジスタで構成可能である。

【0126】

3−4.応用

図21は、本実施の形態に係るレベルシフト回路10、論理回路90及び出力回路50を備える半導体装置を示している。論理回路90は、所望の論理演算が実現されるように上述のインバータ60、NANDゲート70、NORゲート80を適宜組み合わせることで構成される。論理回路90は、P側信号SP及びN側信号SNをサポートしているため、レベルシフト回路10の出力に基づいて所望の論理演算を実行することが可能である。出力回路50は、その論理演算の結果に応じた出力信号SOを出力する。

【0127】

図22は、回路の一例を示している。図22に示される回路は、3つの入力端子IN、DRV1、DRV2、4つの出力端子OUT1〜OUT4、3つのレベルシフト回路10−1〜10−3、4つの出力回路50−1〜50−4、及び論理回路90を備えている。レベルシフト回路10−1〜10−3は、入力端子IN、DRV1、DRV2のそれぞれに入力される入力信号のレベルシフトを行う。論理回路90は、レベルシフト回路10−1〜10−3の出力に基づいて所定の論理演算を行う。出力回路50−1〜50−4は、その論理演算の結果に応じた出力信号を出力端子OUT1〜OUT4のそれぞれに出力する。3つの入力端子IN、DRV1、DRV2の論理レベルによって、4つの出力端子OUT1〜OUT4の論理レベルが制御される。

【0128】

図23は、比較例を示している。比較例では、本実施の形態に係る論理ゲート(60、70、80)は用いられない。その代わり、P側信号SP及びN側信号SNをサポートしていない通常の論理ゲートで、図22と同じ論理演算が実現される。この場合、レベルシフト回路10よりも前の段で、論理演算を行っておく必要がある。よって、図23に示されるように、4個のレベルシフト回路10−1〜10−4が必要となる。

【0129】

図22と図23の比較から明らかなように、本実施の形態に係る論理ゲート(60、70、80)を利用することによって、レベルシフト回路10の数を削減することが可能となる。これにより、回路面積が削減される。更に、後段の負荷を軽くすることができるため、レベルシフト回路10自体のWサイズも削減できる。このことも、回路面積の削減に寄与する。

【0130】

以上、本発明の実施の形態が添付の図面を参照することにより説明された。但し、本発明は、上述の実施の形態に限定されず、要旨を逸脱しない範囲で当業者により適宜変更され得る。

【符号の説明】

【0131】

10 レベルシフト回路

11 インバータ

12 インバータ

20 ラッチ回路

30 ラッチ反転回路

40 クランプ回路

50 出力回路

52 中間電位生成回路

60 インバータ

62 クランプ回路

70 NANDゲート

73 クランプ回路

80 NORゲート

83 クランプ回路

90 論理回路

MP PMOSトランジスタ

MN NMOSトランジスタ

IN 入力端子

IN−P P側入力端子

IN−N N側入力端子

OUT 出力端子

OUT−P P側出力端子

OUT−N N側出力端子

SI 入力信号

SO 出力信号

SP P側制御信号

SN N側制御信号

VDD 低電源電位(内部電源電位、第1電源電位)

VDDO 高電源電位(第2電源電位)

Vthp PMOS閾値電圧

Vthn NMOS閾値電圧

GND グランド電位

【技術分野】

【0001】

本発明は、レベルシフト回路を備える半導体装置に関する。

【背景技術】

【0002】

低電源電位VDDで動作する内部回路と高電源電位VDDOで動作する外部回路との間には、入出力インタフェース回路が設けられる。入出力インタフェース回路において内部回路の信号を外部回路の信号に変換するために、レベルシフト回路が一般的に用いられている。そのようなレベルシフト回路は、例えば、特許文献1(特開平9−172368号公報)や特許文献2(特開2005−260350号公報)に記載されている。

【0003】

図1は、特許文献1に記載されている半導体出力回路(レベルシフト回路)の構成を示している。この半導体出力回路は、低電源電位VDD側の入力信号を入力端子INから受け取り、その入力信号のレベルシフトを行い、高電源電位VDDO側の出力信号を出力端子OUTから出力する。

【0004】

より詳細には、図1に示される半導体出力回路は、第1のPMOSトランジスタ111、第2のPMOSトランジスタ112、ラッチ回路170、クランプ回路171、及びラッチ反転回路172を備えている。ラッチ回路170は、クロスカップルしたPMOSトランジスタ151、152で構成されている。クランプ回路171は、ゲートに低電源電位VDDが共通に印加されるPMOSトランジスタ153、154及びNMOSトランジスタ161、162で構成されている。ラッチ反転回路172は、相補信号がゲートに入力されるNMOSトランジスタ163、164で構成されている。

【0005】

図1に示されるような回路構成の場合、第1のPMOSトランジスタ111のゲート電位Vg11は、次のような値を取る(特許文献1の図2を参照)。すなわち、第1のPMOSトランジスタ111のゲート電位Vg11は、Highレベルの場合に高電源電位VDDOとなり、Lowレベルの場合に低電源電位VDDとなる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平9−172368号公報

【特許文献2】特開2005−260350号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

近年、半導体装置の低電圧化が進んでおり、高電源電位VDDOも低下してきている。例えば、LPDDR2規格(モバイル系のメモリインターフェース規格の一つ)では、出力電圧は1.2Vで規定されており、入出力回路をこの1.2Vで動作させる必要がある。

【0008】

一例として、高電源電位VDDOが1.2Vであり、低電源電位VDDが1.0Vであるような低電圧動作を考える。この場合、上述の図1で示された回路構成では、Lowレベルのゲート電位Vg11は1.0Vとなる。この時の第1のPMOSトランジスタ111のゲート−ソース電圧Vgsは、1.2V−1.0V=0.2Vであり、第1のPMOSトランジスタ111をONさせるには不十分である。すなわち、図1で示された回路構成では、低電圧動作が不可能である。

【課題を解決するための手段】

【0009】

以下に、[発明を実施するための形態]で使用される番号・符号を用いて、[課題を解決するための手段]を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための形態]との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0010】

本発明の1つの観点において、レベルシフト回路(10)を具備する半導体装置が提供される。レベルシフト回路(10)は、グランド電位(GND)が印加されるグランド端子と、グランド電位(GND)と第1電源電位(VDD)との間で電位が切り替わる入力信号(SI)が入力される入力端子(IN)と、第1電源電位(VDD)よりも高い第2電源電位(VDDO)が印加される電源端子と、P側出力端子(OUT−P)と、N側出力端子(OUT−N)と、クランプ回路(40)と、接続制御回路(20,30)と、を備える。

【0011】

クランプ回路(40)は、P側出力端子(OUT−P)とN側出力端子(OUT−N)との間に接続されている。クランプ回路(40)は、ソースが第1ノード(NF)に接続され、ドレインがP側出力端子(OUT−P)に接続され、ゲートが電源端子に接続された第1NMOSトランジスタ(MN42)と、ソースが第1ノード(NF)に接続され、ドレインがN側出力端子(OUT−N)に接続され、ゲートがグランド端子に接続された第1PMOSトランジスタ(MP42)と、を備える。

【0012】

接続制御回路(20,30)は、入力信号(SI)の電位に応じて、グランド端子と電源端子とP側出力端子(OUT−P)とN側出力端子(OUT−N)との間の電気的接続を制御する。より詳細には、入力信号(SI)の電位がグランド電位(GND)と第1電源電位(VDD)の一方の場合、接続制御回路(20,30)は、P側出力端子(OUT−P)に第2電源電位(VDDO)を印加し、且つ、N側出力端子(OUT−N)とグランド端子との間の電気的接続を遮断する。入力信号(SI)の電位がグランド電位(GND)と第1電源電位(VDD)の他方の場合、接続制御回路(20,30)は、N側出力端子(OUT−N)にグランド電位(GND)を印加し、且つ、P側出力端子(OUT−P)と電源端子との間の電気的接続を遮断する。

【0013】

クランプ回路(40)は、更に、ソースが第2ノード(NE)に接続され、ドレインが第3ノード(NC)に接続され、ゲートが電源端子に接続された第2NMOSトランジスタ(MN41)と、ソースが第2ノード(NE)に接続され、ドレインが第4ノード(ND)に接続され、ゲートがグランド端子に接続された第2PMOSトランジスタ(MP41)と、を備えてもよい。入力信号(SI)の電位がグランド電位(GND)と第1電源電位(VDD)の一方の場合、接続制御回路(20,30)は、第4ノード(ND)にグランド電位(GND)を印加し、且つ、第3ノード(NC)と電源端子との間の電気的接続を遮断する。入力信号(SI)の電位がグランド電位(GND)と第1電源電位(VDD)の他方の場合、接続制御回路(20,30)は、第3ノード(NC)に第2電源電位(VDDO)を印加し、且つ、第4ノード(ND)とグランド端子との間の電気的接続を遮断する。

【0014】

入力信号(SI)の反転信号は、反転入力信号である。接続制御回路(20,30)は、ソースが電源端子に接続され、ドレインが第3ノード(NC)に接続され、ゲートが第1ノード(NF)に接続された第3PMOSトランジスタ(MP21)と、ソースが電源端子に接続され、ドレインがP側出力端子(OUT−P)に接続され、ゲートが第2ノード(NE)に接続された第4PMOSトランジスタ(MP22)と、を備えてもよい。接続制御回路(20,30)は、更に、ソースがグランド端子に接続され、ドレインが第4ノード(ND)に接続され、ゲートに入力信号(SI)と反転入力信号の一方が入力される第3NMOSトランジスタ(MN31)と、ソースがグランド端子に接続され、ドレインがN側出力端子(OUT−N)に接続され、ゲートに入力信号(SI)と反転入力信号の他方が入力される第4NMOSトランジスタ(MN32)と、を備えてもよい。

【0015】

レベルシフト回路(10)のP側出力端子(OUT−P)から出力される信号は、P側制御信号(SP)である。HighレベルのP側制御信号(SP)の電位は、第2電源電位(VDDO)である。LowレベルのP側制御信号(SP)の電位は、グランド電位(GND)から第1PMOSトランジスタ(MP42)の閾値電圧(Vthp)の分だけ増加した電位である。HighレベルとLowレベルの電位がP側制御信号(SP)のものと同じである信号は、P側信号である。

【0016】

レベルシフト回路(10)のN側出力端子(OUT−N)から出力される信号は、N側制御信号(SN)である。HighレベルのN側制御信号(SN)の電位は、第2電源電位(VDDO)から第1NMOSトランジスタ(MN42)の閾値電圧(Vthn)の分だけ低下した電位である。LowレベルのN側制御信号(SN)の電位は、グランド電位(GND)である。HighレベルとLowレベルの電位がN側制御信号(SN)のものと同じである信号は、N側信号である。

【0017】

本発明に係る半導体装置は、更に、出力回路(50)を具備してもよい。その出力回路(50)は、P側信号が入力されるP側入力端子(IN−P)と、N側信号が入力されるN側入力端子(IN−N)と、出力端子(OUT)と、を備える。その出力回路(50)は、更に、ソースが電源端子に接続され、ドレインが出力端子(OUT)に接続され、ゲートがP側入力端子(IN−P)に接続された第5PMOSトランジスタ(MP51)と、ソースがグランド端子に接続され、ドレインが出力端子(OUT)に接続され、ゲートがN側入力端子(IN−N)に接続された第5NMOSトランジスタ(MN51)と、を備える。

【0018】

出力回路(50)は、更に、ソースが第5PMOSトランジスタ(MP51)のドレインに接続され、ドレインが出力端子(OUT)に接続され、ゲートに所定のゲート電位(VDP)が印加される第6PMOSトランジスタ(MP52)と、ソースが第5NMOSトランジスタ(MN51)のドレインに接続され、ドレインが出力端子(OUT)に接続され、ゲートに第1電源電位(VDD)が印加される第6NMOSトランジスタ(MN52)と、を備えてもよい。

【0019】

第2電源電位(VDDO)がVDDOであり、第6PMOSトランジスタ(MP52)の閾値電圧及び耐圧がそれぞれVthp、Vbであるとき、所定のゲート電位(VDP)は、VDDO−Vb以上、且つ、Vb−Vthp以下である。

【0020】

本発明に係る半導体装置は、更に、論理ゲート(60,70,80)を備えてもよい。論理ゲート(60,70,80)は、P側信号の1つであるP側入力信号(SPin)が入力されるP側論理入力端子(IN−P)と、N側信号の1つであるN側入力信号(SNin)が入力されるN側論理入力端子(IN−N)と、P側信号の1つであるP側出力信号(SPout)が出力されるP側論理出力端子(OUT−P)と、N側信号の1つであるN側出力信号(SNout)が出力されるN側論理出力端子(OUT−N)と、論理演算部と、を備える。論理演算部は、P側入力信号(SPin)及びN側入力信号(SNin)に基づいて所定の論理演算を行い、P側出力信号(SPout)及びN側出力信号(SNout)を生成する。

【0021】

論理演算部は、ソースが第5ノード(NI,NK,NM)に接続され、ドレインがP側論理出力端子(OUT−P)に接続され、ゲートが電源端子に接続された第7NMOSトランジスタ(MN62,MN73,MN83)と、ソースが第5ノード(NI,NK,NM)に接続され、ドレインがN側論理出力端子(OUT−N)に接続され、ゲートがグランド端子に接続された第7PMOSトランジスタ(MP62,MP73,MP83)と、を備えてもよい。P側出力信号(SPout)及びN側出力信号(SNout)がHighレベルである場合、論理演算部は、P側論理出力端子(OUT−P)に第2電源電位(VDDO)を印加し、且つ、N側論理出力端子(OUT−N)とグランド端子との間の電気的接続を遮断する。P側出力信号(SPout)及びN側出力信号(SNout)がLowレベルである場合、論理演算部は、N側論理出力端子(OUT−N)にグランド電位(GND)を印加し、且つ、P側論理出力端子(OUT−P)と電源端子との間の電気的接続を遮断する。

【発明の効果】

【0022】

本発明に係るレベルシフト回路によれば、低電圧動作の場合であっても、出力段のトランジスタを十分にONさせることが可能となる。

【図面の簡単な説明】

【0023】

【図1】図1は、特許文献1(特開平9−172368号公報)に記載されている半導体出力回路の構成を示す回路図である。

【図2】図2は、本発明の実施の形態に係るレベルシフト回路の構成を示す回路図である。

【図3】図3は、入力信号がLowレベルである場合のレベルシフト回路の状態を示す回路図である。

【図4】図4は、入力信号がHighレベルである場合のレベルシフト回路の状態を示す回路図である。

【図5】図5は、レベルシフト回路の動作を示すタイミングチャートである。

【図6】図6は、レベルシフト回路中の各トランジスタに印加される電圧を要約的に示すテーブルである。

【図7】図7は、本発明の実施の形態に係る出力回路の構成を示す回路図である。

【図8】図8は、入力信号がLowレベルである場合の出力回路の状態を示す回路図である。

【図9】図9は、入力信号がHighレベルである場合の出力回路の状態を示す回路図である。

【図10】図10は、出力回路中の各トランジスタに印加される電圧を要約的に示すテーブルである。

【図11】図11は、本発明の実施の形態に係るレベルシフト回路及び出力回路を備える半導体装置を示すブロック図である。

【図12】図12は、本発明の実施の形態に係るインバータの構成を示す回路図である。

【図13】図13は、入力信号がLowレベルである場合のインバータの状態を示す回路図である。

【図14】図14は、入力信号がHighレベルである場合のインバータの状態を示す回路図である。

【図15】図15は、本発明の実施の形態に係るNANDゲートの構成を示す回路図である。

【図16】図16は、第1入力信号がLowレベルであり第2入力信号がHighレベルである場合のNANDゲートの状態を示す回路図である。

【図17】図17は、第1入力信号がHighレベルであり第2入力信号がHighレベルである場合のNANDゲートの状態を示す回路図である。

【図18】図18は、本発明の実施の形態に係るNORゲートの構成を示す回路図である。

【図19】図19は、第1入力信号がLowレベルであり第2入力信号がLowレベルである場合のNORゲートの状態を示す回路図である。

【図20】図20は、第1入力信号がHighレベルであり第2入力信号がLowレベルである場合のNORゲートの状態を示す回路図である。

【図21】図21は、本発明の実施の形態に係るレベルシフト回路、論理回路及び出力回路を備える半導体装置を示すブロック図である。

【図22】図22は、本発明の実施の形態に係るレベルシフト回路、論理回路及び出力回路を備える半導体装置の一例を示すブロック図である。

【図23】図23は、比較例を示すブロック図である。

【発明を実施するための形態】

【0024】

添付図面を参照して、本発明の実施の形態を説明する。

【0025】

1.レベルシフト回路

1−1.構成

図2は、本発明の実施の形態に係るレベルシフト回路10の構成を示す回路図である。このレベルシフト回路10は、入出力インタフェース回路において内部回路の信号を外部回路の信号に変換するために用いられる。内部回路は、内部電源電位である低電源電位VDD(第1電源電位)で動作し、外部回路は、外部電源電位である高電源電位VDDO(第2電源電位)で動作する。高電源電位VDDOは、低電源電位VDDより高い。例えば、高電源電位VDDOは1.2Vであり、低電源電位VDDは1.0Vである。

【0026】

図2に示されるように、レベルシフト回路10は、入力端子IN、P側出力端子OUT−P、及びN側出力端子OUT−Nを備えている。つまり、レベルシフト回路10は、1入力2出力の構成を有している。

【0027】

入力端子INには、内部回路からの信号が入力信号SIとして入力される。入力信号SIの電位は、低電源電位VDDとグランド電位GND(0V)との間で切り替わる。つまり、Highレベルの入力信号SIの電位は低電源電位VDDであり、Lowレベルの入力信号SIの電位はグランド電位GNDである。

【0028】

P側出力端子OUT−Pからは、P側制御信号SPが出力される。後に詳しく説明されるように、P側制御信号SPの電位は、高電源電位VDDOと電位Vthpとの間で切り替わる。つまり、HighレベルのP側制御信号SPの電位は高電源電位VDDOであり、LowレベルのP側制御信号SPの電位はVthpである。ここで、電位Vthpは、レベルシフト回路10内で用いられるPMOSトランジスタの閾値電圧であり、例えば0.5Vである。

【0029】

N側出力端子OUT−Nからは、N側制御信号SNが出力される。後に詳しく説明されるように、N側制御信号SNの電位は、電位VDDO−Vthnとグランド電位GNDとの間で切り替わる。つまり、HighレベルのN側制御信号SNの電位はVDDO−Vthnであり、LowレベルのN側制御信号SNの電位はグランド電位GNDである。ここで、電位Vthnは、レベルシフト回路10内で用いられるNMOSトランジスタの閾値電圧であり、例えば0.5Vである。

【0030】

P側制御信号SPとN側制御信号SNは同相(in-phase)である。つまり、P側制御信号SPがHighレベルのとき、N側制御信号SNもHighレベルである。また、P側制御信号SPがLowレベルのとき、N側制御信号SNもLowレベルである。

【0031】

図2に示されるように、レベルシフト回路10は更に、インバータ11、12、ラッチ回路20、ラッチ反転回路30、及びクランプ回路40を備えている。

【0032】

インバータ11の入力は入力端子INに接続されており、その出力はノードNAに接続されている。また、インバータ11は、VDD端子(低電源電位VDDが印加される端子)とグランド端子(グランド電位GNDが印加される端子)に接続されている。入力信号SIの電位が低電源電位VDD(Highレベル)の場合、インバータ11は、グランド電位GND(Lowレベル)をノードNAに出力する。一方、入力信号SIの電位がグランド電位GND(Lowレベル)の場合、インバータ11は、低電源電位VDD(Highレベル)をノードNAに出力する。つまり、ノードNAには、入力信号SIの論理レベルが反転した反転入力信号が現れる。

【0033】

インバータ12の入力はノードNAに接続されており、その出力はノードNBに接続されている。また、インバータ12は、VDD端子とグランド端子に接続されている。ノードNAの電位が低電源電位VDD(Highレベル)の場合、インバータ12は、グランド電位GND(Lowレベル)をノードNBに出力する。一方、ノードNAの電位がグランド電位GND(Lowレベル)の場合、インバータ12は、低電源電位VDD(Highレベル)をノードNBに出力する。つまり、ノードNBには、入力信号SIと同じ論理レベルの信号が現れる。

【0034】

ラッチ回路20は、PMOSトランジスタMP21とPMOSトランジスタMP22を備えている。PMOSトランジスタMP21のソース、ドレイン、及びゲートは、それぞれ、VDDO端子(高電源電位VDDOが印加される端子)、ノードNC、及びノードNFに接続されている。PMOSトランジスタMP22のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、P側出力端子OUT−P、及びノードNEに接続されている。

【0035】

ラッチ反転回路30は、NMOSトランジスタMN31とNMOSトランジスタMN32を備えている。NMOSトランジスタMN31のソース、ドレイン、及びゲートは、それぞれ、グランド端子、ノードND、及びノードNAに接続されている。NMOSトランジスタMN32のソース、ドレイン、及びゲートは、それぞれ、グランド端子、N側出力端子OUT−N、及びノードNBに接続されている。NMOSトランジスタMN31のゲート(ノードNA)には反転入力信号が入力され、NMOSトランジスタMN32のゲート(ノードNB)には入力信号SIが入力される。従って、NMOSトランジスタMN31、MN32の一方がONするとき、他方はOFFする。尚、ノードNAに入力信号SIが現れ、ノードNBに反転入力信号が現れてもよい。その場合、各ノードの論理レベルが逆になるだけで、同じ議論が適用可能である。

【0036】

後に説明されるように、ラッチ回路20とラッチ反転回路30は、「接続制御回路」として機能する。この接続制御回路は、入力信号SIの電位に応じて、グランド端子とVDDO端子とP側出力端子OUT−PとN側出力端子OUT−Nとの間の電気的接続を制御する。

【0037】

クランプ回路40は、P側出力端子OUT−PとN側出力端子OUT−Nとの間に接続されている。より詳細には、クランプ回路40は、NMOSトランジスタMN41、NMOSトランジスタMN42、PMOSトランジスタMP41、及びPMOSトランジスタMP42を備えている。NMOSトランジスタMN41のソース、ドレイン、及びゲートは、それぞれ、ノードNE、ノードNC、及びVDDO端子に接続されている。NMOSトランジスタMN42のソース、ドレイン、及びゲートは、それぞれ、ノードNF、P側出力端子OUT−P、及びVDDO端子に接続されている。PMOSトランジスタMP41のソース、ドレイン、及びゲートは、それぞれ、ノードNE、ノードND、及びグランド端子に接続されている。PMOSトランジスタMP42のソース、ドレイン、及びゲートは、それぞれ、ノードNF、N側出力端子OUT−N、及びグランド端子に接続されている。

【0038】

1−2.動作

図3は、入力信号SIがLowレベルである場合のレベルシフト回路10の状態を示している。ノードNAの電位は低電源電位VDDであり、NMOSトランジスタMN31はONする。一方、ノードNBの電位はグランド電位GNDであり、NMOSトランジスタMN32はOFFする。つまり、N側出力端子OUT−Nとグランド端子との間の電気的接続が遮断される。

【0039】

NMOSトランジスタMN31がONするため、ノードNDとグランド端子とが電気的に接続され、ノードNDにはNMOSトランジスタMN31を通してグランド電位GNDが印加される。更に、PMOSトランジスタMP41のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNEの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP41の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN41はONし、ノードNCの電位も“Vthp”となる。

【0040】

ノードNEの電位がVthpであるため、PMOSトランジスタMP22はONする。その結果、P側出力端子OUT−PとVDDO端子とが電気的に接続され、P側出力端子OUT−PにはPMOSトランジスタMP22を通して高電源電位VDDOが印加される。つまり、P側制御信号SPの電位は、高電源電位VDDO(Highレベル)となる。

【0041】

NMOSトランジスタMN42のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNFの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN42の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。よって、PMOSトランジスタMP21はOFFし、ノードNCとVDDO端子との間の電気的接続が遮断される。

【0042】

ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP42はONし、N側出力端子OUT−Nの電位も“VDDO−Vthn”となる。つまり、N側制御信号SNの電位は、“VDDO−Vthn”(Highレベル)となる。

【0043】

このように、入力信号SIがLowレベルである場合、ラッチ回路20(接続制御回路)は、P側出力端子OUT−PとVDDO端子とを電気的に接続することによって、P側出力端子OUT−Pに高電源電位VDDOを印加する。これにより、P側制御信号SPの電位は、高電源電位VDDO(Highレベル)となる。また、ラッチ反転回路30(接続制御回路)は、N側出力端子OUT−Nとグランド端子との間の電気的接続を遮断する。更に、P側出力端子OUT−PとN側出力端子OUT−Nの間には、ゲート電位が高電源電位VDDOに固定されたNMOSトランジスタMN42が介在している。これにより、N側出力端子OUT−Nの電位、すなわち、N側制御信号SNの電位は、“VDDO−Vthn”(Highレベル)となる。

【0044】

図4は、入力信号SIがHighレベルである場合のレベルシフト回路10の状態を示している。ノードNAの電位はグランド電位GNDであり、NMOSトランジスタMN31はOFFする。つまり、ノードNDとグランド端子との間の電気的接続が遮断される。一方、ノードNBの電位は低電源電位VDDであり、NMOSトランジスタMN32はONする。

【0045】

NMOSトランジスタMN32がONするため、N側出力端子OUT−Nとグランド端子とが電気的に接続され、N側出力端子OUT−NにはNMOSトランジスタMN32を通してグランド電位GNDが印加される。これにより、N側制御信号SNの電位は、グランド電位GND(Lowレベル)となる。

【0046】

PMOSトランジスタMP42のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNFの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP42の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN42はONし、P側出力端子OUT−Pの電位も“Vthp”となる。つまり、P側制御信号SPの電位は、“Vthp”(Lowレベル)となる。

【0047】

ノードNFの電位がVthpであるため、PMOSトランジスタMP21はONする。その結果、ノードNCとVDDO端子とが電気的に接続され、ノードNCにはPMOSトランジスタMP21を通して高電源電位VDDOが印加される。NMOSトランジスタMN41のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNEの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN41の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。よって、PMOSトランジスタMP22はOFFし、P側出力端子OUT−PとVDDO端子との間の電気的接続が遮断される。また、ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP41はONし、ノードNDの電位も“VDDO−Vthn”となる。

【0048】

このように、入力信号SIがHighレベルである場合、ラッチ反転回路30(接続制御回路)は、N側出力端子OUT−Nとグランド端子とを電気的に接続することによって、N側出力端子OUT−Nにグランド電位GNDを印加する。これにより、N側制御信号SNの電位は、グランド電位GND(Lowレベル)となる。また、ラッチ回路20(接続制御回路)は、P側出力端子OUT−PとVDDO端子との間の電気的接続を遮断する。更に、P側出力端子OUT−PとN側出力端子OUT−Nの間には、ゲート電位がグランド電位GNDに固定されたPMOSトランジスタMP42が介在している。これにより、P側出力端子OUT−Pの電位、すなわち、P側制御信号SPの電位は、“Vthp”(Lowレベル)となる。

【0049】

図5は、レベルシフト回路10の動作を示すタイミングチャートである。図5には、入力端子IN(入力信号SI)、N側出力端子OUT−N(N側制御信号SN)、ノードNF、及びP側出力端子OUT−P(P側制御信号SP)のそれぞれの電位が示されている。ここで、例えば、VDDO=1.2V、VDD=1.0V、GND=0.0V、Vthp,Vthn=0.5Vであるとする。

【0050】

入力信号SIの電位は、低電源電位VDD(High)とグランド電位GND(Low)との間で切り替わる。N側制御信号SNの電位は、電位VDDO−Vthn(High)とグランド電位GND(Low)との間で切り替わる。P側制御信号SPの電位は、高電源電位VDDO(High)と電位Vthp(Low)との間で切り替わる。また、P側制御信号SPとN側制御信号SNは同相である。尚、図3〜図5で示された例において、入力信号SIと出力制御信号(SP,SN)とは逆相であるが、それらは同相であってもよい。

【0051】

1−3.耐圧

図6は、上記の図3及び図4で示されたそれぞれの状態において各トランジスタに印加される電圧を示している。Vgsはゲート−ソース間の電圧(電位差)であり、Vgdはゲート−ドレイン間の電圧(電位差)であり、Vdsはドレイン−ソース間の電圧(電位差)である。各トランジスタの耐圧がVbである場合、その耐圧Vbは次の条件を満たせばよい。

【0052】

Vb≧Vthn

Vb≧Vthp

Vb≧VDDO−Vthn

Vb≧VDDO−Vthp

Vb≧VDDO−Vthn−Vthp

Vb≧VDD

【0053】

一例として、VDDO=1.2V、VDD=1.0V、Vthp=0.5V、Vthn=0.5Vである場合を考える。この場合、耐圧Vbは次の条件を満たせばよい。

【0054】

Vb≧Vthn=0.5V

Vb≧Vthp=0.5V

Vb≧VDDO−Vthn=1.2V−0.5V=0.7V

Vb≧VDDO−Vthp=1.2V−0.5V=0.7V

Vb≧VDDO−Vthn−Vthp=1.2V−0.5V−0.5V=0.2V

Vb≧VDD=1.0V

【0055】

従って、図3及び図4で示された状態を考えた場合、各トランジスタの耐圧Vbは、1.0V以上であればよい。逆に言えば、耐圧Vbとして、高電源電位VDDOほどの高レベルは不要である。つまり、本実施の形態では、各トランジスタの耐圧Vbを、高電源電位VDDOより低くすることが可能である(VDDO>Vb)。これは、レベルシフト回路10内のトランジスタを全て「低耐圧トランジスタ」で構成可能であることを意味する。レベルシフト回路10を低耐圧トランジスタだけで構成することにより、製造コストと回路面積が削減される。

【0056】

クランプ回路40は「耐圧保護回路」としての役割を果たしているとも言える。クランプ回路40により、N側出力端子OUT−NとノードNDの電位の上限値は、“VDDO−Vthn”となる。これにより、グランド電位GNDが印加されるNMOSトランジスタMN31、MN32及びPMOSトランジスタMP41、MP42の破壊が防止される。また、クランプ回路40により、P側出力端子OUT−PとノードNCの電位の下限値は、“Vthp”となる。これにより、高電源電位VDDOが印加されるPMOSトランジスタMP21、MP22及びNMOSトランジスタMN41、MN42の破壊が防止される。

【0057】

1−4.効果

以上に説明されたように、本実施の形態に係るレベルシフト回路10は、入力信号SIのレベルシフトにより、2種類の制御信号SP、SNを生成する。例えば、それら制御信号SP、SNを、出力回路中のトランジスタのON/OFF制御に用いることができる(この例については、次の第2節においても詳しく説明される)。

【0058】

P側制御信号SPを、高電源電位VDDOを出力するための「PMOS出力トランジスタ」のゲート制御信号として用いることを考える。P側制御信号SPの電位は、高電源電位VDDO(High)と電位Vthp(Low)との間で切り替わる。Lowレベルの電位がVthpであるため、VDDO=1.2V程度の低電圧動作の場合であっても、PMOS出力トランジスタを十分にONさせることが可能となる。また、PMOS出力トランジスタのゲート電位がVthp以上となるため、PMOS出力トランジスタを低耐圧トランジスタで構成することも可能となる。この場合、出力回路の製造コストと回路面積が削減される。

【0059】

N側制御信号SNを、グランド電位GNDを出力するための「NMOS出力トランジスタ」のゲート制御信号として用いることを考える。N側制御信号SNの電位は、電位VDDO−Vthn(High)とグランド電位GND(Low)との間で切り替わる。Highレベルの電位がVDDO−Vthnであるため、NMOS出力トランジスタを十分にONさせることが可能となる。また、NMOS出力トランジスタのゲート電位がVDDO−Vthn以下となるため、NMOS出力トランジスタを低耐圧トランジスタで構成することも可能となる。この場合、出力回路の製造コストと回路面積が削減される。

【0060】

また、上述の通り、クランプ回路40は、レベルシフト回路10内のトランジスタの破壊を防止する「耐圧保護回路」としての役割も果たしている。レベルシフト回路10内のトランジスタを全て低耐圧トランジスタで構成することも可能であり、その場合、製造コストと回路面積が削減される。

【0061】

2.出力回路

2−1.構成

図7は、本実施の形態に係る出力回路50の構成を示す回路図である。この出力回路50は、上述のP側制御信号SP及びN側制御信号SNをサポートしており、それら制御信号SP、SNに応じた出力信号SOを生成、出力することができる。より詳細には、出力回路50は、P側入力端子IN−P、N側入力端子IN−N及び出力端子OUTを備えている。

【0062】

P側入力端子IN−Pには、上記のレベルシフト回路10から出力されたP側制御信号SP、あるいは、P側制御信号SPと同じ電位変化をする信号が入力される。そのような信号は、以下、「P側信号SP」と参照される。P側信号SPの電位は、高電源電位VDDOと電位Vthpとの間で切り替わる。つまり、HighレベルのP側信号SPの電位は高電源電位VDDOであり、LowレベルのP側信号SPの電位はVthpである。

【0063】

N側入力端子IN−Nには、上記のレベルシフト回路10から出力されたN側制御信号SN、あるいは、N側制御信号SNと同じ電位変化をする信号が入力される。そのような信号は、以下、「N側信号SN」と参照される。N側信号SNの電位は、電位VDDO−Vthnとグランド電位GNDとの間で切り替わる。つまり、HighレベルのN側信号SNの電位はVDDO−Vthnであり、LowレベルのN側信号SNの電位はグランド電位GNDである。

【0064】

P側信号SPとN側信号SNは同相(in-phase)である。つまり、P側信号SPがHighレベルのとき、N側信号SNもHighレベルである。また、P側信号SPがLowレベルのとき、N側信号SNもLowレベルである。この同相のP側信号SP及びN側信号SNが、入力信号として出力回路50に入力される。

【0065】

出力端子OUTからは、出力信号SOが出力される。出力信号SOの電位は、高電源電位VDDOとグランド電位GNDとの間で切り替わる。つまり、Highレベルの出力信号SOの電位はVDDOであり、Lowレベルの出力信号SOの電位はグランド電位GNDである。

【0066】

図7に示されるように、出力回路50は更に、PMOSトランジスタMP51、MP52、NMOSトランジスタMN51、MN52、及び中間電位生成回路52を備えている。中間電位生成回路52は、所定のゲート電位VDPを生成、出力する。

【0067】

PMOSトランジスタMP51のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、ノードNG、及びP側入力端子IN−Pに接続されている。ノードNGは、PMOSトランジスタMP52を介して、出力端子OUTに接続されている。具体的には、PMOSトランジスタMP52のソースがノードNGに接続されており、そのドレインが出力端子OUTに接続されている。また、PMOSトランジスタMP52のゲートには、中間電位生成回路52によって生成された所定のゲート電位VDPが印加される。

【0068】

NMOSトランジスタMN51のソース、ドレイン、及びゲートは、それぞれ、グランド端子、ノードNH、及びN側入力端子IN−Nに接続されている。ノードNHは、NMOSトランジスタMN52を介して、出力端子OUTに接続されている。具体的には、NMOSトランジスタMN52のソースがノードNHに接続されており、そのドレインが出力端子OUTに接続されている。また、NMOSトランジスタMN52のゲートには、低電源電位VDDが印加される。

【0069】

2−2.動作

図8は、入力信号SP、SNがLowレベルである場合の出力回路50の状態を示している。P側入力端子IN−Pの電位、すなわち、PMOSトランジスタMP51のゲート電位はVthpである。よって、PMOSトランジスタMP51は十分にONする。一方、N側入力端子IN−Nの電位、すなわち、NMOSトランジスタMN51のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN51はOFFし、ノードNHとグランド端子との間の電気的接続は遮断される。

【0070】

PMOSトランジスタMP51がONするため、ノードNGとVDDO端子とが電気的に接続され、ノードNGにはPMOSトランジスタMP51を通して高電源電位VDDOが印加される。更に、ゲート電位VDPが適切に設定されたPMOSトランジスタMP52もONし、出力端子OUTの電位も高電源電位VDDOとなる。よって、出力信号SOの電位は、高電源電位VDDO(Highレベル)となる。

【0071】

その一方で、NMOSトランジスタMN52のゲート電位は低電源電位VDDに固定されているため、そのソース電位、すなわち、ノードNHの電位は、ゲート電位(低電源電位VDD)からNMOSトランジスタMN52の閾値電圧Vthnの分だけ低下した“VDD−Vthn”となる。つまり、ノードNHに高電源電位VDDOが印加されることが防止されている。NMOSトランジスタMN52は、グランド電位GNDが印加されるNMOSトランジスタMN51の耐圧保護の役割を果たしている。

【0072】

図9は、入力信号SP、SNがHighレベルである場合の出力回路50の状態を示している。P側入力端子IN−Pの電位、すなわち、PMOSトランジスタMP51のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP51はOFFし、ノードNGとVDDO端子との間の電気的接続は遮断される。一方、N側入力端子IN−Nの電位、すなわち、NMOSトランジスタMN51のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN51は十分にONする。

【0073】

NMOSトランジスタMN51がONするため、ノードNHとグランド端子とが電気的に接続され、ノードNHにはNMOSトランジスタMN51を通してグランド電位GNDが印加される。更に、ゲート電位が低電源電位VDDであるNMOSトランジスタMN52もONし、出力端子OUTの電位もグランド電位GNDとなる。よって、出力信号SOの電位は、グランド電位GND(Lowレベル)となる。

【0074】

その一方で、PMOSトランジスタMP52のゲート電位はVDPに固定されているため、そのソース電位、すなわち、ノードNGの電位は、ゲート電位VDPからPMOSトランジスタMP52の閾値電圧Vthnの分だけ増加した“VDP+Vthp”となる。つまり、ノードNGにグランド電位GNDが印加されることが防止されている。PMOSトランジスタMP52は、高電源電位VDDOが印加されるPMOSトランジスタMP51の耐圧保護の役割を果たしている。

【0075】

2−3.耐圧

図10は、上記の図8及び図9で示されたそれぞれの状態において各トランジスタに印加される電圧を示している。Vgsはゲート−ソース間の電圧(電位差)であり、Vgdはゲート−ドレイン間の電圧(電位差)であり、Vdsはドレイン−ソース間の電圧(電位差)である。各トランジスタの耐圧がVbである場合、その耐圧Vbは次の条件を満たせばよい。

【0076】

Vb≧Vthn

Vb≧Vthp

Vb≧VDDO−Vthn

Vb≧VDDO−Vthp

Vb≧VDDO−VDD

Vb≧VDDO−VDD+Vthn

Vb≧VDD−Vthn

Vb≧VDD

Vb≧VDDO−VDP

Vb≧VDDO−VDP−Vthp

Vb≧VDP

Vb≧VDP+Vthp

【0077】

また、これら条件から、ゲート電位VDPは、次の関係式「Vb−Vthp≧VDP≧VDDO−Vb」を満たせばよいことが分かる。一例として、VDDO=1.2V、VDD=1.0V、Vthp=0.5V、Vthn=0.5Vである場合を考える。この場合、耐圧Vbは次の条件を満たせばよい。

【0078】

Vb≧Vthn=0.5V

Vb≧Vthp=0.5V

Vb≧VDDO−Vthn=1.2V−0.5V=0.7V

Vb≧VDDO−Vthp=1.2V−0.5V=0.7V

Vb≧VDDO−VDD=1.2V−1.0V=0.2V

Vb≧VDDO−VDD+Vthn=1.2V−1.0V+0.5V=0.7V

Vb≧VDD−Vthn=1.0V−0.5V=0.5V

Vb≧VDD=1.0V

Vb≧VDDO−VDP=1.2V−VDP

Vb≧VDDO−VDP−Vthp=1.2V−VDP−0.5V=0.7V−VDP

Vb≧VDP

Vb≧VDP+Vthp=VDP+0.5V

【0079】

各トランジスタが低耐圧トランジスタであり、耐圧Vbが例えば1.0Vである場合を考える。この場合、ゲート電位VDPは、1.0V−0.5V≧VDP≧1.2V−1.0Vを満たせばよい。例えば、ゲート電位VDPは0.3Vに設定される。これにより、全ての条件が満たされる。そして、出力回路50を低耐圧トランジスタだけで構成することにより、製造コストと回路面積が削減される。

【0080】

2−4.効果

図11は、本実施の形態に係るレベルシフト回路10と出力回路50を備える半導体装置(出力インタフェース回路)である。レベルシフト回路10は、入力信号SIを受け取り、その入力信号SIに応じたP側制御信号SP及びN側制御信号SNを生成する。出力回路50は、レベルシフト回路10から出力されるP側制御信号SP及びN側制御信号SNを受け取り、それに応じた出力信号SOを出力する。入力信号SIの電位が低電源電位VDD(Highレベル)の場合、出力信号SOの電位は高電源電位VDDO(Highレベル)である。入力信号SIの電位がグランド電位GND(Lowレベル)の場合、出力信号SOの電位はグランド電位GND(Lowレベル)である。但し、入出力論理関係は逆であってもよい。

【0081】

本実施の形態によれば、VDDO=1.2V程度の低電圧動作の場合であっても、各トランジスタを十分にONさせることが可能である。また、各トランジスタを低耐圧トランジスタで構成することも可能である。すなわち、本実施の形態によれば、耐圧を保護しつつ、低電圧動作が可能な出力インタフェース回路を実現することが可能となる。

【0082】

3.論理ゲート

第3節では、P側信号SP及びN側信号SNをサポートする「論理ゲート」を提案する。論理ゲートに入力されるP側信号SP及びN側信号SNは、それぞれ、P側入力信号SPin及びN側入力信号SNinである。論理ゲートから出力されるP側信号SP及びN側信号SNは、それぞれ、P側出力信号SPout及びN側出力信号SNoutである。論理ゲートは、入力信号(SPin、SNin)を受け取り、その入力信号に基づいて所定の論理演算を行い、その論理演算の結果を出力信号(SPout、SNout)として出力する。

【0083】

3−1.インバータ

図12は、本実施の形態に係るインバータ60の構成を示す回路図である。インバータ60は、入力端子(IN−P、IN−N)及び出力端子(OUT−P、OUT−N)を備えている。入力端子(IN−P、IN−N)には、同相の入力信号(SPin、SNin)が入力される。出力端子(OUT−P、OUT−N)からは、同相の出力信号(SPout、SNout)が出力される。

【0084】

インバータ60は更に、論理演算部を備えている。論理演算部は、入力信号(SPin、SNin)の論理を反転させ、その反転論理を出力信号(SPout、SNout)として出力する。より詳細には、論理演算部は、PMOSトランジスタMP61及びNMOSトランジスタMN61を備えている。PMOSトランジスタMP61のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、P側出力端子OUT−P、及びP側入力端子IN−Pに接続されている。NMOSトランジスタMN61のソース、ドレイン、及びゲートは、それぞれ、グランド端子、N側出力端子OUT−N、及びN側入力端子IN−Nに接続されている。

【0085】

論理演算部は更に、P側出力端子OUT−PとN側出力端子OUT−Nとの間に接続されたクランプ回路62を備えている。クランプ回路62は、NMOSトランジスタMN62及びPMOSトランジスタMP62を備えている。NMOSトランジスタMN62のソース、ドレイン、及びゲートは、それぞれ、ノードNI、P側出力端子OUT−P、及びVDDO端子に接続されている。PMOSトランジスタMP62のソース、ドレイン、及びゲートは、それぞれ、ノードNI、N側出力端子OUT−N、及びグランド端子に接続されている。

【0086】

図13は、入力信号(SPin、SNin)がLowレベルである場合のインバータ60の状態を示している。P側入力端子IN−Pの電位、すなわち、PMOSトランジスタMP61のゲート電位はVthpである。よって、PMOSトランジスタMP61は十分にONする。一方、N側入力端子IN−Nの電位、すなわち、NMOSトランジスタMN61のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN61はOFFし、N側出力端子OUT−Nとグランド端子との間の電気的接続は遮断される。

【0087】

PMOSトランジスタMP61がONするため、P側出力端子OUT−PとVDDO端子とが電気的に接続され、P側出力端子OUT−PにはPMOSトランジスタMP61を通して高電源電位VDDOが印加される。つまり、P側出力信号SPoutの電位は、高電源電位VDDO(Highレベル)となる。

【0088】

NMOSトランジスタMN62のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNIの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN62の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP62はONし、N側出力端子OUT−Nの電位も“VDDO−Vthn”となる。つまり、N側出力信号SNoutの電位は、“VDDO−Vthn”(Highレベル)となる。

【0089】

図14は、入力信号(SPin、SNin)がHighレベルである場合のインバータ60の状態を示している。P側入力端子IN−Pの電位、すなわち、PMOSトランジスタMP61のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP61はOFFし、P側出力端子OUT−PとVDDO端子との間の電気的接続は遮断される。一方、N側入力端子IN−Nの電位、すなわち、NMOSトランジスタMN61のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN61は十分にONする。

【0090】

NMOSトランジスタMN61がONするため、N側出力端子OUT−Nとグランド端子とが電気的に接続され、N側出力端子OUT−NにはNMOSトランジスタMN61を通してグランド電位GNDが印加される。つまり、N側出力信号SNoutの電位は、グランド電位GND(Lowレベル)となる。

【0091】

PMOSトランジスタMP62のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNIの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP62の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN62はONし、P側出力端子OUT−Pの電位も“Vthp”となる。つまり、P側出力信号SPoutの電位は、“Vthp”(Lowレベル)となる。

【0092】

レベルシフト回路10のクランプ回路40と同様に、インバータ60のクランプ回路62は、「耐圧保護回路」としての役割も果たしている。クランプ回路62により、N側出力端子OUT−Nの電位の上限値は“VDDO−Vthn”となる。これにより、グランド電位GNDが印加されるNMOSトランジスタMN61の破壊が防止される。また、クランプ回路62により、P側出力端子OUT−Pの電位の下限値は“Vthp”となる。これにより、高電源電位VDDOが印加されるPMOSトランジスタMP61の破壊が防止される。

【0093】

各トランジスタの耐圧に関しても、レベルシフト回路10の場合と同様であり、各トランジスタを低耐圧トランジスタで構成可能である。

【0094】

3−2.NANDゲート

図15は、本実施の形態に係るNANDゲート70の構成を示す回路図である。NANDゲート70は、第1入力端子(IN1−P、IN1−N)、第2入力端子(IN2−P、IN2−N)、及び出力端子(OUT−P、OUT−N)を備えている。第1入力端子(IN1−P、IN1−N)には、同相の第1入力信号(SPin1、SNin1)が入力される。第2入力端子(IN2−P、IN2−N)には、同相の第2入力信号(SPin2、SNin2)が入力される。出力端子(OUT−P、OUT−N)からは、同相の出力信号(SPout、SNout)が出力される。

【0095】

NANDゲート70は更に、論理演算部を備えている。論理演算部は、第1入力信号(SPin1、SNin1)及び第2入力信号(SPin2、SNin2)に基づいてNAND論理演算を行い、出力信号(SPout、SNout)を生成する。より詳細には、論理演算部は、PMOSトランジスタMP71、MP72、及びNMOSトランジスタMN71、MN72を備えている。PMOSトランジスタMP71のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、P側出力端子OUT−P、及び第1P側入力端子IN1−Pに接続されている。PMOSトランジスタMP72のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、P側出力端子OUT−P、及び第2P側入力端子IN2−Pに接続されている。NMOSトランジスタMN71のソース、ドレイン、及びゲートは、それぞれ、ノードNJ、N側出力端子OUT−N、及び第1N側入力端子IN1−Nに接続されている。NMOSトランジスタMN72のソース、ドレイン、及びゲートは、それぞれ、グランド端子、ノードNJ、及び第2N側入力端子IN2−Nに接続されている。

【0096】

論理演算部は更に、P側出力端子OUT−PとN側出力端子OUT−Nとの間に接続されたクランプ回路73を備えている。クランプ回路73は、NMOSトランジスタMN73及びPMOSトランジスタMP73を備えている。NMOSトランジスタMN73のソース、ドレイン、及びゲートは、それぞれ、ノードNK、P側出力端子OUT−P、及びVDDO端子に接続されている。PMOSトランジスタMP73のソース、ドレイン、及びゲートは、それぞれ、ノードNK、N側出力端子OUT−N、及びグランド端子に接続されている。

【0097】

図16は、第1入力信号(SPin1、SNin1)がLowレベルであり、第2入力信号(SPin2、SNin2)がHighレベルである場合のNANDゲート70の状態を示している。

【0098】

第1P側入力端子IN1−Pの電位、すなわち、PMOSトランジスタMP71のゲート電位はVthpである。よって、PMOSトランジスタMP71は十分にONする。第2P側入力端子IN2−Pの電位、すなわち、PMOSトランジスタMP72のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP72はOFFする。

【0099】

第2N側入力端子IN2−Nの電位、すなわち、NMOSトランジスタMN72のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN72はONし、ノードNJにグランド電位GNDが印加される。第1N側入力端子IN1−Nの電位、すなわち、NMOSトランジスタMN71のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN71はOFFする。結果として、N側出力端子OUT−Nとグランド端子との間の電気的接続は遮断される。

【0100】

PMOSトランジスタMP71がONするため、P側出力端子OUT−PとVDDO端子とが電気的に接続され、P側出力端子OUT−PにはPMOSトランジスタMP71を通して高電源電位VDDOが印加される。つまり、P側出力信号SPoutの電位は、高電源電位VDDO(Highレベル)となる。

【0101】

NMOSトランジスタMN73のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNKの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN73の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP73はONし、N側出力端子OUT−Nの電位も“VDDO−Vthn”となる。つまり、N側出力信号SNoutの電位は、“VDDO−Vthn”(Highレベル)となる。

【0102】

第1入力信号(SPin1、SNin1)と第2入力信号(SPin2、SNin2)のうち少なくとも一方がLowレベルであれば、出力信号(SPout、SNout)や出力端子(OUT−P、OUT−N)の電位状態は、図16で示されたものと同じになる。

【0103】

図17は、第1入力信号(SPin1、SNin1)と第2入力信号(SPin2、SNin2)が共にHighレベルである場合のNANDゲート70の状態を示している。

【0104】

第1P側入力端子IN1−Pの電位、すなわち、PMOSトランジスタMP71のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP71はOFFする。第2P側入力端子IN2−Pの電位、すなわち、PMOSトランジスタMP72のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP72はOFFする。結果として、P側出力端子OUT−PとVDDO端子との間の電気的接続は遮断される。

【0105】

第1N側入力端子IN1−Nの電位、すなわち、NMOSトランジスタMN71のゲート電位は“VDDO−Vthn”である。また、第2N側入力端子IN2−Nの電位、すなわち、NMOSトランジスタMN72のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN71、MN72は共に十分にONする。

【0106】

NMOSトランジスタMN71、MN72が共にONするため、N側出力端子OUT−Nとグランド端子とが電気的に接続され、N側出力端子OUT−NにはNMOSトランジスタMN71、MN72を通してグランド電位GNDが印加される。つまり、N側出力信号SNoutの電位は、グランド電位GND(Lowレベル)となる。

【0107】

PMOSトランジスタMP73のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNKの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP73の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN73はONし、P側出力端子OUT−Pの電位も“Vthp”となる。つまり、P側出力信号SPoutの電位は、“Vthp”(Lowレベル)となる。

【0108】

レベルシフト回路10のクランプ回路40と同様に、NANDゲート70のクランプ回路73は、「耐圧保護回路」としての役割も果たしている。クランプ回路73により、N側出力端子OUT−Nの電位の上限値は“VDDO−Vthn”となる。これにより、グランド電位GNDが印加されるNMOSトランジスタMN71、MN72の破壊が防止される。また、クランプ回路73により、P側出力端子OUT−Pの電位の下限値は“Vthp”となる。これにより、高電源電位VDDOが印加されるPMOSトランジスタMP71、MP72の破壊が防止される。

【0109】

各トランジスタの耐圧に関しても、レベルシフト回路10の場合と同様であり、各トランジスタを低耐圧トランジスタで構成可能である。

【0110】

3−3.NORゲート

図18は、本実施の形態に係るNORゲート80の構成を示す回路図である。NORゲート80は、第1入力端子(IN1−P、IN1−N)、第2入力端子(IN2−P、IN2−N)、及び出力端子(OUT−P、OUT−N)を備えている。第1入力端子(IN1−P、IN1−N)には、同相の第1入力信号(SPin1、SNin1)が入力される。第2入力端子(IN2−P、IN2−N)には、同相の第2入力信号(SPin2、SNin2)が入力される。出力端子(OUT−P、OUT−N)からは、同相の出力信号(SPout、SNout)が出力される。

【0111】

NORゲート80は更に、論理演算部を備えている。論理演算部は、第1入力信号(SPin1、SNin1)及び第2入力信号(SPin2、SNin2)に基づいてNOR論理演算を行い、出力信号(SPout、SNout)を生成する。より詳細には、論理演算部は、PMOSトランジスタMP81、MP82、及びNMOSトランジスタMN81、MN82を備えている。PMOSトランジスタMP81のソース、ドレイン、及びゲートは、それぞれ、ノードNL、P側出力端子OUT−P、及び第1P側入力端子IN1−Pに接続されている。PMOSトランジスタMP82のソース、ドレイン、及びゲートは、それぞれ、VDDO端子、ノードNL、及び第2P側入力端子IN2−Pに接続されている。NMOSトランジスタMN81のソース、ドレイン、及びゲートは、それぞれ、グランド端子、N側出力端子OUT−N、及び第1N側入力端子IN1−Nに接続されている。NMOSトランジスタMN82のソース、ドレイン、及びゲートは、それぞれ、グランド端子、N側出力端子OUT−N、及び第2N側入力端子IN2−Nに接続されている。

【0112】

論理演算部は更に、P側出力端子OUT−PとN側出力端子OUT−Nとの間に接続されたクランプ回路83を備えている。クランプ回路83は、NMOSトランジスタMN83及びPMOSトランジスタMP83を備えている。NMOSトランジスタMN83のソース、ドレイン、及びゲートは、それぞれ、ノードNM、P側出力端子OUT−P、及びVDDO端子に接続されている。PMOSトランジスタMP83のソース、ドレイン、及びゲートは、それぞれ、ノードNM、N側出力端子OUT−N、及びグランド端子に接続されている。

【0113】

図19は、第1入力信号(SPin1、SNin1)と第2入力信号(SPin2、SNin2)が共にLowレベルである場合のNORゲート80の状態を示している。

【0114】

第1P側入力端子IN1−Pの電位、すなわち、PMOSトランジスタMP81のゲート電位はVthpである。また、第2P側入力端子IN2−Pの電位、すなわち、PMOSトランジスタMP82のゲート電位はVthpである。よって、PMOSトランジスタMP81、MP82は共に十分にONする。

【0115】

第1N側入力端子IN1−Nの電位、すなわち、NMOSトランジスタMN81のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN81はOFFする。第2N側入力端子IN2−Nの電位、すなわち、NMOSトランジスタMN82のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN82はOFFする。結果として、N側出力端子OUT−Nとグランド端子との間の電気的接続は遮断される。

【0116】

PMOSトランジスタMP81、MP82が共にONするため、P側出力端子OUT−PとVDDO端子とが電気的に接続され、P側出力端子OUT−PにはPMOSトランジスタMP81、MP82を通して高電源電位VDDOが印加される。つまり、P側出力信号SPoutの電位は、高電源電位VDDO(Highレベル)となる。

【0117】

NMOSトランジスタMN83のゲート電位は高電源電位VDDOに固定されているため、そのソース電位、すなわち、ノードNMの電位は、ゲート電位(高電源電位VDDO)からNMOSトランジスタMN83の閾値電圧Vthnの分だけ低下した“VDDO−Vthn”となる。ゲート電位がグランド電位GNDに固定され、ソース電位が“VDDO−Vthn”であるPMOSトランジスタMP83はONし、N側出力端子OUT−Nの電位も“VDDO−Vthn”となる。つまり、N側出力信号SNoutの電位は、“VDDO−Vthn”(Highレベル)となる。

【0118】

図20は、第1入力信号(SPin1、SNin1)がHighレベルであり、第2入力信号(SPin2、SNin2)がLowレベルである場合のNORゲート80の状態を示している。

【0119】

第2P側入力端子IN2−Pの電位、すなわち、PMOSトランジスタMP82のゲート電位はVthpである。よって、PMOSトランジスタMP82はONし、ノードNLに高電源電位VDDOが印加される。第1P側入力端子IN1−Pの電位、すなわち、PMOSトランジスタMP81のゲート電位は高電源電位VDDOである。よって、PMOSトランジスタMP81はOFFする。結果として、P側出力端子OUT−PとVDDO端子との間の電気的接続は遮断される。

【0120】

第1N側入力端子IN1−Nの電位、すなわち、NMOSトランジスタMN81のゲート電位は“VDDO−Vthn”である。よって、NMOSトランジスタMN81は十分にONする。第2N側入力端子IN2−Nの電位、すなわち、NMOSトランジスタMN82のゲート電位はグランド電位GNDである。よって、NMOSトランジスタMN82はOFFする。

【0121】

NMOSトランジスタMN81が共にONするため、N側出力端子OUT−Nとグランド端子とが電気的に接続され、N側出力端子OUT−NにはNMOSトランジスタMN81を通してグランド電位GNDが印加される。つまり、N側出力信号SNoutの電位は、グランド電位GND(Lowレベル)となる。

【0122】

PMOSトランジスタMP83のゲート電位はグランド電位GNDに固定されているため、そのソース電位、すなわち、ノードNMの電位は、ゲート電位(グランド電位GND)からPMOSトランジスタMP83の閾値電圧Vthpの分だけ増加した“Vthp”となる。ゲート電位が高電源電位VDDOに固定され、ソース電位が“Vthp”であるNMOSトランジスタMN83はONし、P側出力端子OUT−Pの電位も“Vthp”となる。つまり、P側出力信号SPoutの電位は、“Vthp”(Lowレベル)となる。

【0123】

第1入力信号(SPin1、SNin1)と第2入力信号(SPin2、SNin2)のうち少なくとも一方がHighレベルであれば、出力信号(SPout、SNout)や出力端子(OUT−P、OUT−N)の電位状態は、図20で示されたものと同じになる。

【0124】

レベルシフト回路10のクランプ回路40と同様に、NORゲート80のクランプ回路83は、「耐圧保護回路」としての役割も果たしている。クランプ回路83により、N側出力端子OUT−Nの電位の上限値は“VDDO−Vthn”となる。これにより、グランド電位GNDが印加されるNMOSトランジスタMN81、MN82の破壊が防止される。また、クランプ回路83により、P側出力端子OUT−Pの電位の下限値は“Vthp”となる。これにより、高電源電位VDDOが印加されるPMOSトランジスタMP81、MP82の破壊が防止される。

【0125】

各トランジスタの耐圧に関しても、レベルシフト回路10の場合と同様であり、各トランジスタを低耐圧トランジスタで構成可能である。

【0126】

3−4.応用

図21は、本実施の形態に係るレベルシフト回路10、論理回路90及び出力回路50を備える半導体装置を示している。論理回路90は、所望の論理演算が実現されるように上述のインバータ60、NANDゲート70、NORゲート80を適宜組み合わせることで構成される。論理回路90は、P側信号SP及びN側信号SNをサポートしているため、レベルシフト回路10の出力に基づいて所望の論理演算を実行することが可能である。出力回路50は、その論理演算の結果に応じた出力信号SOを出力する。

【0127】

図22は、回路の一例を示している。図22に示される回路は、3つの入力端子IN、DRV1、DRV2、4つの出力端子OUT1〜OUT4、3つのレベルシフト回路10−1〜10−3、4つの出力回路50−1〜50−4、及び論理回路90を備えている。レベルシフト回路10−1〜10−3は、入力端子IN、DRV1、DRV2のそれぞれに入力される入力信号のレベルシフトを行う。論理回路90は、レベルシフト回路10−1〜10−3の出力に基づいて所定の論理演算を行う。出力回路50−1〜50−4は、その論理演算の結果に応じた出力信号を出力端子OUT1〜OUT4のそれぞれに出力する。3つの入力端子IN、DRV1、DRV2の論理レベルによって、4つの出力端子OUT1〜OUT4の論理レベルが制御される。

【0128】

図23は、比較例を示している。比較例では、本実施の形態に係る論理ゲート(60、70、80)は用いられない。その代わり、P側信号SP及びN側信号SNをサポートしていない通常の論理ゲートで、図22と同じ論理演算が実現される。この場合、レベルシフト回路10よりも前の段で、論理演算を行っておく必要がある。よって、図23に示されるように、4個のレベルシフト回路10−1〜10−4が必要となる。

【0129】

図22と図23の比較から明らかなように、本実施の形態に係る論理ゲート(60、70、80)を利用することによって、レベルシフト回路10の数を削減することが可能となる。これにより、回路面積が削減される。更に、後段の負荷を軽くすることができるため、レベルシフト回路10自体のWサイズも削減できる。このことも、回路面積の削減に寄与する。

【0130】

以上、本発明の実施の形態が添付の図面を参照することにより説明された。但し、本発明は、上述の実施の形態に限定されず、要旨を逸脱しない範囲で当業者により適宜変更され得る。

【符号の説明】

【0131】

10 レベルシフト回路

11 インバータ

12 インバータ

20 ラッチ回路

30 ラッチ反転回路

40 クランプ回路

50 出力回路

52 中間電位生成回路

60 インバータ

62 クランプ回路

70 NANDゲート

73 クランプ回路

80 NORゲート

83 クランプ回路

90 論理回路

MP PMOSトランジスタ

MN NMOSトランジスタ

IN 入力端子

IN−P P側入力端子

IN−N N側入力端子

OUT 出力端子

OUT−P P側出力端子

OUT−N N側出力端子

SI 入力信号

SO 出力信号

SP P側制御信号

SN N側制御信号

VDD 低電源電位(内部電源電位、第1電源電位)

VDDO 高電源電位(第2電源電位)

Vthp PMOS閾値電圧

Vthn NMOS閾値電圧

GND グランド電位

【特許請求の範囲】

【請求項1】

レベルシフト回路を具備する半導体装置であって、

前記レベルシフト回路は、

グランド電位が印加されるグランド端子と、

前記グランド電位と第1電源電位との間で電位が切り替わる入力信号が入力される入力端子と、

前記第1電源電位よりも高い第2電源電位が印加される電源端子と、

P側出力端子と、

N側出力端子と、

前記P側出力端子と前記N側出力端子との間に接続されたクランプ回路と、

前記入力信号の電位に応じて、前記グランド端子と前記電源端子と前記P側出力端子と前記N側出力端子との間の電気的接続を制御する接続制御回路と

を備え、

前記クランプ回路は、

ソースが第1ノードに接続され、ドレインが前記P側出力端子に接続され、ゲートが前記電源端子に接続された第1NMOSトランジスタと、

ソースが前記第1ノードに接続され、ドレインが前記N側出力端子に接続され、ゲートが前記グランド端子に接続された第1PMOSトランジスタと

を備え、

前記入力信号の電位が前記グランド電位と前記第1電源電位の一方の場合、前記接続制御回路は、前記P側出力端子に前記第2電源電位を印加し、且つ、前記N側出力端子と前記グランド端子との間の電気的接続を遮断し、

前記入力信号の電位が前記グランド電位と前記第1電源電位の他方の場合、前記接続制御回路は、前記N側出力端子に前記グランド電位を印加し、且つ、前記P側出力端子と前記電源端子との間の電気的接続を遮断する

半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記クランプ回路は、更に、

ソースが第2ノードに接続され、ドレインが第3ノードに接続され、ゲートが前記電源端子に接続された第2NMOSトランジスタと、

ソースが前記第2ノードに接続され、ドレインが第4ノードに接続され、ゲートが前記グランド端子に接続された第2PMOSトランジスタと

を備え、

前記入力信号の電位が前記グランド電位と前記第1電源電位の前記一方の場合、前記接続制御回路は、前記第4ノードに前記グランド電位を印加し、且つ、前記第3ノードと前記電源端子との間の電気的接続を遮断し、

前記入力信号の電位が前記グランド電位と前記第1電源電位の前記他方の場合、前記接続制御回路は、前記第3ノードに前記第2電源電位を印加し、且つ、前記第4ノードと前記グランド端子との間の電気的接続を遮断する

半導体装置。

【請求項3】

請求項2に記載の半導体装置であって、

前記入力信号の反転信号は、反転入力信号であり、

前記接続制御回路は、

ソースが前記電源端子に接続され、ドレインが前記第3ノードに接続され、ゲートが前記第1ノードに接続された第3PMOSトランジスタと、

ソースが前記電源端子に接続され、ドレインが前記P側出力端子に接続され、ゲートが前記第2ノードに接続された第4PMOSトランジスタと、

ソースが前記グランド端子に接続され、ドレインが前記第4ノードに接続され、ゲートに前記入力信号と前記反転入力信号の一方が入力される第3NMOSトランジスタと、

ソースが前記グランド端子に接続され、ドレインが前記N側出力端子に接続され、ゲートに前記入力信号と前記反転入力信号の他方が入力される第4NMOSトランジスタと

を備える

半導体装置。

【請求項4】

請求項1乃至3のいずれか一項に記載の半導体装置であって、

前記レベルシフト回路の前記P側出力端子から出力される信号は、P側制御信号であり、

Highレベルの前記P側制御信号の電位は、前記第2電源電位であり、

Lowレベルの前記P側制御信号の電位は、前記グランド電位から前記第1PMOSトランジスタの閾値電圧の分だけ増加した電位であり、

HighレベルとLowレベルの電位が前記P側制御信号のものと同じである信号は、P側信号であり、

前記レベルシフト回路の前記N側出力端子から出力される信号は、N側制御信号であり、

Highレベルの前記N側制御信号の電位は、前記第2電源電位から前記第1NMOSトランジスタの閾値電圧の分だけ低下した電位であり、

Lowレベルの前記N側制御信号の電位は、前記グランド電位であり、

HighレベルとLowレベルの電位が前記N側制御信号のものと同じである信号は、N側信号である

半導体装置。

【請求項5】

請求項4に記載の半導体装置であって、

更に、出力回路を具備し、

前記出力回路は、

前記P側信号が入力されるP側入力端子と、

前記N側信号が入力されるN側入力端子と、

出力端子と、

ソースが前記電源端子に接続され、ドレインが前記出力端子に接続され、ゲートが前記P側入力端子に接続された第5PMOSトランジスタと、

ソースが前記グランド端子に接続され、ドレインが前記出力端子に接続され、ゲートが前記N側入力端子に接続された第5NMOSトランジスタと

を備える

半導体装置。

【請求項6】

請求項5に記載の半導体装置であって、

前記出力回路は、更に、

ソースが前記第5PMOSトランジスタの前記ドレインに接続され、ドレインが前記出力端子に接続され、ゲートに所定のゲート電位が印加される第6PMOSトランジスタと、

ソースが前記第5NMOSトランジスタの前記ドレインに接続され、ドレインが前記出力端子に接続され、ゲートに前記第1電源電位が印加される第6NMOSトランジスタと

を備える

半導体装置。

【請求項7】

請求項6に記載の半導体装置であって、

前記第2電源電位がVDDOであり、前記第6PMOSトランジスタの閾値電圧及び耐圧がそれぞれVthp、Vbであるとき、

前記所定のゲート電位は、VDDO−Vb以上、且つ、Vb−Vthp以下である

半導体装置。

【請求項8】

請求項4乃至7のいずれか一項に記載の半導体装置であって、

更に、論理ゲートを備え、

前記論理ゲートは、

前記P側信号の1つであるP側入力信号が入力されるP側論理入力端子と、

前記N側信号の1つであるN側入力信号が入力されるN側論理入力端子と、

前記P側信号の1つであるP側出力信号が出力されるP側論理出力端子と、

前記N側信号の1つであるN側出力信号が出力されるN側論理出力端子と、

前記P側入力信号及び前記N側入力信号に基づいて所定の論理演算を行い、前記P側出力信号及び前記N側出力信号を生成する論理演算部と

を備える

半導体装置。

【請求項9】

請求項8に記載の半導体装置であって、

前記論理演算部は、

ソースが第5ノードに接続され、ドレインが前記P側論理出力端子に接続され、ゲートが前記電源端子に接続された第7NMOSトランジスタと、

ソースが前記第5ノードに接続され、ドレインが前記N側論理出力端子に接続され、ゲートが前記グランド端子に接続された第7PMOSトランジスタと

を備え、

前記P側出力信号及び前記N側出力信号がHighレベルである場合、前記論理演算部は、前記P側論理出力端子に前記第2電源電位を印加し、且つ、前記N側論理出力端子と前記グランド端子との間の電気的接続を遮断し、

前記P側出力信号及び前記N側出力信号がLowレベルである場合、前記論理演算部は、前記N側論理出力端子に前記グランド電位を印加し、且つ、前記P側論理出力端子と前記電源端子との間の電気的接続を遮断する

半導体装置。

【請求項1】

レベルシフト回路を具備する半導体装置であって、

前記レベルシフト回路は、

グランド電位が印加されるグランド端子と、

前記グランド電位と第1電源電位との間で電位が切り替わる入力信号が入力される入力端子と、

前記第1電源電位よりも高い第2電源電位が印加される電源端子と、

P側出力端子と、

N側出力端子と、

前記P側出力端子と前記N側出力端子との間に接続されたクランプ回路と、

前記入力信号の電位に応じて、前記グランド端子と前記電源端子と前記P側出力端子と前記N側出力端子との間の電気的接続を制御する接続制御回路と

を備え、

前記クランプ回路は、

ソースが第1ノードに接続され、ドレインが前記P側出力端子に接続され、ゲートが前記電源端子に接続された第1NMOSトランジスタと、

ソースが前記第1ノードに接続され、ドレインが前記N側出力端子に接続され、ゲートが前記グランド端子に接続された第1PMOSトランジスタと

を備え、

前記入力信号の電位が前記グランド電位と前記第1電源電位の一方の場合、前記接続制御回路は、前記P側出力端子に前記第2電源電位を印加し、且つ、前記N側出力端子と前記グランド端子との間の電気的接続を遮断し、

前記入力信号の電位が前記グランド電位と前記第1電源電位の他方の場合、前記接続制御回路は、前記N側出力端子に前記グランド電位を印加し、且つ、前記P側出力端子と前記電源端子との間の電気的接続を遮断する

半導体装置。

【請求項2】

請求項1に記載の半導体装置であって、

前記クランプ回路は、更に、

ソースが第2ノードに接続され、ドレインが第3ノードに接続され、ゲートが前記電源端子に接続された第2NMOSトランジスタと、

ソースが前記第2ノードに接続され、ドレインが第4ノードに接続され、ゲートが前記グランド端子に接続された第2PMOSトランジスタと

を備え、

前記入力信号の電位が前記グランド電位と前記第1電源電位の前記一方の場合、前記接続制御回路は、前記第4ノードに前記グランド電位を印加し、且つ、前記第3ノードと前記電源端子との間の電気的接続を遮断し、

前記入力信号の電位が前記グランド電位と前記第1電源電位の前記他方の場合、前記接続制御回路は、前記第3ノードに前記第2電源電位を印加し、且つ、前記第4ノードと前記グランド端子との間の電気的接続を遮断する

半導体装置。

【請求項3】

請求項2に記載の半導体装置であって、

前記入力信号の反転信号は、反転入力信号であり、

前記接続制御回路は、

ソースが前記電源端子に接続され、ドレインが前記第3ノードに接続され、ゲートが前記第1ノードに接続された第3PMOSトランジスタと、

ソースが前記電源端子に接続され、ドレインが前記P側出力端子に接続され、ゲートが前記第2ノードに接続された第4PMOSトランジスタと、

ソースが前記グランド端子に接続され、ドレインが前記第4ノードに接続され、ゲートに前記入力信号と前記反転入力信号の一方が入力される第3NMOSトランジスタと、

ソースが前記グランド端子に接続され、ドレインが前記N側出力端子に接続され、ゲートに前記入力信号と前記反転入力信号の他方が入力される第4NMOSトランジスタと

を備える

半導体装置。

【請求項4】

請求項1乃至3のいずれか一項に記載の半導体装置であって、

前記レベルシフト回路の前記P側出力端子から出力される信号は、P側制御信号であり、

Highレベルの前記P側制御信号の電位は、前記第2電源電位であり、

Lowレベルの前記P側制御信号の電位は、前記グランド電位から前記第1PMOSトランジスタの閾値電圧の分だけ増加した電位であり、

HighレベルとLowレベルの電位が前記P側制御信号のものと同じである信号は、P側信号であり、

前記レベルシフト回路の前記N側出力端子から出力される信号は、N側制御信号であり、

Highレベルの前記N側制御信号の電位は、前記第2電源電位から前記第1NMOSトランジスタの閾値電圧の分だけ低下した電位であり、

Lowレベルの前記N側制御信号の電位は、前記グランド電位であり、

HighレベルとLowレベルの電位が前記N側制御信号のものと同じである信号は、N側信号である

半導体装置。

【請求項5】

請求項4に記載の半導体装置であって、

更に、出力回路を具備し、

前記出力回路は、

前記P側信号が入力されるP側入力端子と、

前記N側信号が入力されるN側入力端子と、

出力端子と、

ソースが前記電源端子に接続され、ドレインが前記出力端子に接続され、ゲートが前記P側入力端子に接続された第5PMOSトランジスタと、

ソースが前記グランド端子に接続され、ドレインが前記出力端子に接続され、ゲートが前記N側入力端子に接続された第5NMOSトランジスタと

を備える

半導体装置。

【請求項6】

請求項5に記載の半導体装置であって、

前記出力回路は、更に、

ソースが前記第5PMOSトランジスタの前記ドレインに接続され、ドレインが前記出力端子に接続され、ゲートに所定のゲート電位が印加される第6PMOSトランジスタと、

ソースが前記第5NMOSトランジスタの前記ドレインに接続され、ドレインが前記出力端子に接続され、ゲートに前記第1電源電位が印加される第6NMOSトランジスタと

を備える

半導体装置。

【請求項7】

請求項6に記載の半導体装置であって、

前記第2電源電位がVDDOであり、前記第6PMOSトランジスタの閾値電圧及び耐圧がそれぞれVthp、Vbであるとき、

前記所定のゲート電位は、VDDO−Vb以上、且つ、Vb−Vthp以下である

半導体装置。

【請求項8】

請求項4乃至7のいずれか一項に記載の半導体装置であって、

更に、論理ゲートを備え、

前記論理ゲートは、

前記P側信号の1つであるP側入力信号が入力されるP側論理入力端子と、

前記N側信号の1つであるN側入力信号が入力されるN側論理入力端子と、

前記P側信号の1つであるP側出力信号が出力されるP側論理出力端子と、

前記N側信号の1つであるN側出力信号が出力されるN側論理出力端子と、

前記P側入力信号及び前記N側入力信号に基づいて所定の論理演算を行い、前記P側出力信号及び前記N側出力信号を生成する論理演算部と

を備える

半導体装置。

【請求項9】

請求項8に記載の半導体装置であって、

前記論理演算部は、

ソースが第5ノードに接続され、ドレインが前記P側論理出力端子に接続され、ゲートが前記電源端子に接続された第7NMOSトランジスタと、

ソースが前記第5ノードに接続され、ドレインが前記N側論理出力端子に接続され、ゲートが前記グランド端子に接続された第7PMOSトランジスタと

を備え、

前記P側出力信号及び前記N側出力信号がHighレベルである場合、前記論理演算部は、前記P側論理出力端子に前記第2電源電位を印加し、且つ、前記N側論理出力端子と前記グランド端子との間の電気的接続を遮断し、

前記P側出力信号及び前記N側出力信号がLowレベルである場合、前記論理演算部は、前記N側論理出力端子に前記グランド電位を印加し、且つ、前記P側論理出力端子と前記電源端子との間の電気的接続を遮断する

半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2013−110584(P2013−110584A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−254026(P2011−254026)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]