半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は半導体装置に関する。

【背景技術】

【0002】

電界効果トランジスタでは、その微細化に伴ってゲート電極によるチャネル領域のポテンシャル制御性が低下し、短チャネル効果が顕著になり、短チャネル効果低減と電流駆動力増大の両立が困難になっている。

【0003】

一方、フィン型トランジスタでは、チャネル領域の両側にゲート電極が設けられているため、チャネル領域のポテンシャル制御性が向上し、短チャネル効果低減と電流駆動力増大の両立を図るのに有効である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】US2007/063224

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の一つの実施形態の目的は、トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させることが可能な半導体装置を提供することである。

【課題を解決するための手段】

【0006】

実施形態の半導体装置によれば、半導体突出部と、ソース/ドレイン層と、ゲート電極と、チャネル領域とが設けられている。半導体突出部は、半導体基板上に形成されている。ソース/ドレイン層は、前記半導体突出部の上下方向に設けられている。ゲート電極は、前記半導体突出部の側面にゲート絶縁膜を介して設けられている。チャネル領域は、前記半導体突出部の側面に設けられ、前記ソース/ドレイン層と前記半導体突出部との間に形成される空乏層以外の領域において、前記ドレイン層側と前記ソース層側とでポテンシャルの高さが異なっている。

【図面の簡単な説明】

【0007】

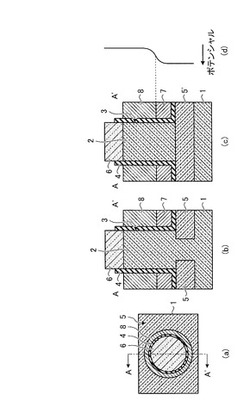

【図1】図1(a)は、第1実施形態に係る半導体装置の概略構成を示す平面図、図1(b)は、第1実施形態に係る半導体装置の概略構成を示す断面図、図1(c)は、第1実施形態に係る半導体装置の概略構成のその他の例を示す断面図、図1(d)は、第1実施形態に係る半導体装置の半導体突出部2の上下方向に沿ったチャネル領域のポテンシャルを示す図である。

【図2】図2(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図2(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図3】図3(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図3(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図4】図4(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図4(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】図5(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図5(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】図6(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図6(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】図7(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図7(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図8】図8(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図8(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図9】図9(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図9(b)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。

【図10】図10(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図10(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図11】図11(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図11(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図12】図12(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図12(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図13】図13(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図13(b)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。

【図14】図14(a)は、第4実施形態に係る半導体装置の概略構成を示す平面図、図14(b)は、第4実施形態に係る半導体装置の概略構成を示す断面図、図14(c)は、第4実施形態に係る半導体装置の概略構成のその他の例を示す断面図である。

【図15】図15(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図15(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図16】図16(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図16(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図17】図17(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図17(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図18】図18(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図18(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図19】図19(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図19(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図20】図20(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図20(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図21】図21(a)は、第6実施形態に係る半導体装置の概略構成を示す平面図、図21(b)は、第6実施形態に係る半導体装置の概略構成を示す断面図である。

【発明を実施するための形態】

【0008】

以下、実施形態に係る半導体装置について図面を参照しながら説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0009】

(第1実施形態)

図1(a)は、第1実施形態に係る半導体装置の概略構成を示す平面図、図1(b)は、第1実施形態に係る半導体装置の概略構成を示す断面図、図1(c)は、第1実施形態に係る半導体装置の概略構成のその他の例を示す断面図、図1(d)は、第1実施形態に係る半導体装置の半導体突出部2の上下方向に沿ったチャネル領域のポテンシャルを示す図である。なお、図1(b)および図1(c)は、図1(a)のA−A線で切断した。

図1(a)〜図1(c)において、半導体基板1上には半導体突出部2が形成されている。なお、半導体基板1および半導体突出部2の材料は、Si、Ge、SiGe、SiC、SiSn、PbS、GaAs、InP、InGaAsP、GaP、GaNおよびZnSeなどから選択することができる。また、半導体基板1と半導体突出部2は材料が互いに同一であってもよいし、互いに異なっていてもよい。半導体突出部2の形状は、円柱状であってもよいし、角柱状であってもよい。あるいはフィン状であってもよい。

【0010】

なお、半導体突出部2の形状を円柱とした場合、半導体突出部2に角が形成されないようにでき、電界集中を防止することが可能となることから、トランジスタのオフ電流を低減することができる。

【0011】

また、半導体突出部2の上下方向にはソース層5およびドレイン層6が形成されている。この時、ソース層5を半導体基板1側に形成し、ドレイン層6を半導体突出部2の頂上面側に形成するようにしてもよいし、ドレイン層6を半導体基板1側に形成し、ソース層5を半導体突出部2の頂上面側に形成するようにしてもよい。

【0012】

また、図1(b)に示すように、例えば、ソース層5を半導体基板1側に形成した場合、半導体突出部2の底面側の一部にソース層5がかかるようにしてもよいし、図1(c)に示すように、半導体突出部2の底面側の全体にソース層5´がかかるようにしてもよい。なお、半導体突出部2の底面側の一部にソース層5がかかるようにした場合、半導体突出部2がソース層5にて半導体基板1と電気的に分離されないようにすることができ、基板バイアス効果を及ぼすことができる。

【0013】

また、半導体突出部2の側面にはゲート絶縁膜4を介してゲート電極7、8が形成されている。ここで、ゲート電極7はソース層5側に配置し、ゲート電極8はドレイン層6側に配置されている。なお、半導体突出部2の形状が円柱状または角柱状の場合、半導体突出部2の周囲を取り囲むようにゲート電極7、8を形成するようにしてもよい。また、半導体突出部2の形状がフィン状の場合、半導体突出部2を両側から挟み込むようにゲート電極7、8を形成するようにしてもよい。また、ゲート電極7、8の材料は、ゲート電極7、8の仕事関数が互いに異なるように選択することができる。

【0014】

そして、ソース層5とドレイン層6の間において、半導体突出部2の側面にはチャネル領域3が設けられている。ここで、図1(d)に示すように、チャネル領域3は、ソース層5およびドレイン層6と半導体突出部2との間に形成される空乏層以外の領域において、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。この時、ソース層5ではドレイン層6側に比べてポテンシャルの高さが高くなるようにすることができる。なお、ソース層5ではドレイン層6側に比べてポテンシャルの高さが高くなるようにするために、ゲート電極7は、ゲート電極8に比べて仕事関数を高くすることができる。

【0015】

例えば、ゲート電極7の材料は、例えば、W、ゲート電極8の材料は、例えば、Alを用いることができる。あるいは、ゲート電極7の材料は、例えば、TaN、RuおよびTiAlNなどから選択するようにしてもよいし、ゲート電極8の材料は、例えば、HfN、NiSi、Mo、TiNなどから選択するようにしてもよい。また、ゲート電極7、8の材料として、n型多結晶シリコンとp型多結晶シリコンとを組み合わせて用いるようにしてもよいし、n型多結晶シリコンまたはp型多結晶シリコンの不純物濃度を変化させた構成を用いるようにしてもよい。また、ゲート絶縁膜4の材料は、例えば、SiO2、HfO、HfSiO、HfSiON、HfAlO、HfAlSiONおよびLa2O3などから選択することができる。

【0016】

また、チャネル領域3の不純物濃度のばらつきに起因する電界効果トランジスタの電気的特性のばらつきや移動度の低下を抑制するために、チャネル領域3の不純物濃度を低減し、チャネル領域3を完全空乏化することが好ましい。

【0017】

ここで、半導体突出部2の上下方向にソース層5およびドレイン層6を形成し、半導体突出部2を取り囲むようにゲート電極7、8を配置することにより、半導体基板1側でパンチスルーが起きるのを防止しつつ、チャネル領域3のポテンシャル制御性を向上させることができ、短チャネル効果低減と電流駆動力増大の両立を図ることができる。

【0018】

また、ソース層5ではドレイン層6側に比べてポテンシャルの高さを高くすることにより、短チャネル効果を抑制しつつ、実効的なゲート長を短くすることが可能となり、オフリーク電流の増大を抑制しつつ、電流駆動力増大を図ることが可能となる。

【0019】

なお、上述した実施形態では、ドレイン層6側とソース層5側とでチャネル領域3のポテンシャルの高さを異ならせるために、ゲート電極7、8の仕事関数を互いに異ならせる方法について説明したが、ドレイン層6側とソース層5側とでゲート絶縁膜4の実効膜厚を互いに異ならせるようにしてもよい。この場合、ゲート電極7、8の仕事関数は互いに異なっていてもよいし、互いに同一であってもよい。また、ドレイン層6側とソース層5側とでゲート絶縁膜4の実効膜厚を異ならせる方法としては、ゲート絶縁膜4の膜厚を互いに異ならせるようにしてもよいし、ゲート絶縁膜4の材料を互いに異ならせるようにしてもよい。

【0020】

(第2実施形態)

図2(a)〜図8(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図2(b)〜図8(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。なお、図2(b)〜図8(b)は、図2(a)〜図8(a)のA−A線でそれぞれ切断した。

【0021】

図2(a)および図2(b)において、CVDなどの方法にて半導体基板1上の全面にキャップ絶縁膜M1を成膜する。そして、フォトリソグラフィ技術およびエッチング技術を用いることにより、半導体基板1上のキャップ絶縁膜M1を円盤状にパターニングする。なお、キャップ絶縁膜M1の材料は、例えば、SiO2またはSiNを用いることができる。そして、キャップ絶縁膜M1をマスクとして半導体基板1の表面をエッチングすることにより、半導体基板1上に半導体突出部2を形成する。

【0022】

次に、図3(a)および図3(b)に示すように、CVDまたは熱酸化などの方法を用いることにより、半導体突出部2の側面にゲート絶縁膜4を形成する。

【0023】

次に、図4(a)および図4(b)に示すように、半導体基板1および半導体突出部2にイオン注入P1を行うことにより、半導体基板1側の半導体突出部2の周囲にソース層5を形成するとともに、半導体突出部2の頂上面側にドレイン層6を形成する。なお、イオン注入P1の注入エネルギーは、半導体突出部2を貫通しないように設定することができる。また、イオン注入P1後に半導体突出部2の熱処理を行うことにより、半導体突出部2の周囲に形成されたソース層5を半導体突出部2の中心方向に張り出させるようにしてもよい。

【0024】

次に、図5(a)および図5(b)に示すように、CVDなどの方法を用いることにより、半導体突出部2が埋め込まれるようにゲート電極7を半導体基板1上に形成する。そして、CMPなどの方法にてキャップ絶縁膜M1が露出するまでゲート電極7を平坦化する。この時、キャップ絶縁膜M1はCMPのストッパ膜として用いることができる。

【0025】

次に、図6(a)および図6(b)に示すように、ゲート電極7のエッチバックを行うことにより、ゲート電極7の上部を除去し、半導体突出部2の上部のゲート絶縁膜4を露出させる。

【0026】

次に、図7(a)および図7(b)に示すように、CVDなどの方法を用いることにより、半導体突出部2の上部が埋め込まれるようにゲート電極8をゲート電極7上に形成する。そして、CMPなどの方法にてキャップ絶縁膜M1が露出するまでゲート電極8を平坦化する。この時、キャップ絶縁膜M1はCMPのストッパ膜として用いることができる。

【0027】

次に、図8(a)および図8(b)に示すように、ゲート電極8のエッチバックを行うことにより、ゲート電極8の上部を除去し、ドレイン層6の側面のゲート絶縁膜4を露出させる。

【0028】

ここで、半導体突出部2の上下方向にソース層5およびドレイン層6を形成することにより、ゲート電極7上にゲート電極8を積層することでドレイン層6側とソース層5側とでチャネル領域3のポテンシャルの高さを異ならせることができる。このため、ゲート電極7、8のマスク加工工程の増大を抑制しつつ、DWF(Double Work Function)型トランジスタを製造することができる。

【0029】

(第3実施形態)

図9(a)〜図13(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図9(b)〜図13(b)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。なお、図9(b)〜図13(b)は、図9(a)〜図13(a)のA−A線でそれぞれ切断した。

【0030】

図9(a)および図9(b)において、図3の工程後、CVDなどの方法を用いることにより、半導体突出部2が埋め込まれるようにゲート電極7を半導体基板1上に形成する。

【0031】

次に、図10(a)および図10(b)に示すように、ゲート電極7のエッチバックを行うことにより、半導体突出部2の下部の側面にゲート電極7を残したまま、それ以外のゲート電極7を除去し、半導体突出部2の上部のゲート絶縁膜4を露出させる。

【0032】

次に、図11(a)および図11(b)に示すように、CVDなどの方法を用いることにより、半導体突出部2の上部およびゲート電極7が埋め込まれるようにゲート電極8を半導体基板1上に形成する。

【0033】

次に、図12(a)および図12(b)に示すように、ゲート電極8のエッチバックを行うことにより、半導体突出部2の上部の側面にゲート電極8を残したまま、それ以外のゲート電極8を除去し、半導体突出部2の上部のゲート絶縁膜4を露出させる。

【0034】

次に、図13(a)および図13(b)に示すように、半導体基板1および半導体突出部2にイオン注入P2を行うことにより、半導体基板1側の半導体突出部2の周囲にソース層5を形成するとともに、半導体突出部2の頂上面側にドレイン層6を形成する。

【0035】

(第4実施形態)

図14(a)は、第4実施形態に係る半導体装置の概略構成を示す平面図、図14(b)は、第4実施形態に係る半導体装置の概略構成を示す断面図、図14(c)は、第4実施形態に係る半導体装置の概略構成のその他の例を示す断面図である。なお、図14(b)および図14(c)は、図14(a)のA−A線で切断した。

【0036】

図14(a)〜図14(c)において、この半導体装置では、図1(b)および図1(c)の半導体突出部2の代わりに半導体突出部2a、2bが設けられている。そして、半導体突出部2aは半導体基板1上に形成され、半導体突出部2bは半導体突出部2a上に形成されている。ここで、半導体突出部2a、2bは、バンドギャップが互いに異なるように構成することができる。半導体突出部2a、2bの材料は、例えば、Si、Ge、SiGe、SiC、SiSn、PbS、GaAs、InP、InGaAsP、GaP、GaNおよびZnSeなどから選択することができる。この時、半導体突出部2a、2bのバンドギャップが互いに異なるように構成するために、半導体突出部2a、2bの材料を互いに異ならせるようにしてもよいし、半導体突出部2a、2bの構造を互いに異ならせるようにしてもよい。半導体突出部2a、2bの構造としては、例えば、単結晶、多結晶およびアモルファルを挙げることができる。

【0037】

そして、半導体突出部2a、2bの側面にはチャネル領域3a、3bがそれぞれ設けられている。この時、チャネル領域3aではチャネル領域3bに比べてポテンシャルの高さが高くなるようにすることができる。なお、チャネル領域3aではチャネル領域3bに比べてポテンシャルの高さが高くなるようにするために、半導体突出部2aは、半導体突出部2bに比べてバンドギャップを広くすることができる。

【0038】

ここで、半導体突出部2a、2bは、バンドギャップが互いに異なるように構成することにより、短チャネル効果を抑制しつつ、実効的なゲート長を短くすることが可能となり、オフリーク電流の増大を抑制しつつ、電流駆動力増大を図ることが可能となる。

【0039】

(第5実施形態)

図15(a)〜図20(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図15(b)〜図20(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。なお、図15(b)〜図20(b)は、図15(a)〜図20(a)のA−A線でそれぞれ切断した。

【0040】

図15(a)および図15(b)において、CVDまたは熱酸化などの方法を用いることにより、半導体基板1上に絶縁膜9を形成する。そして、CVDなどの方法を用いることにより、半導体基板1上にゲート電極7を形成する。

【0041】

次に、図16(a)および図16(b)に示すように、CVDなどの方法を用いることにより、ゲート電極7上にゲート電極8を形成する。

【0042】

次に、図17(a)および図17(b)に示すように、CVDなどの方法を用いることにより、ゲート電極8上に絶縁膜10を形成する。そして、フォトリソグラフィ技術およびエッチング技術を用いることにより、絶縁膜9、10およびゲート電極7、8に開口部K1を形成し、開口部K1を通して半導体基板1の表面を露出させる。

【0043】

次に、図18(a)および図18(b)に示すように、CVDまたは熱酸化などの方法を用いることにより、ゲート電極7、8の側面にゲート絶縁膜4を形成する。

【0044】

次に、図19(a)および図19(b)に示すように、CVDなどの方法を用いることにより、開口部K1内に半導体突出部11を埋め込み、半導体基板1上に半導体突出部11を形成する。なお、半導体突出部11は、例えば、アモルファス半導体を用いることができる。

【0045】

次に、図20(a)および図20(b)に示すように、半導体突出部11の熱処理を行うことにより、半導体突出部11の構造を変化させ、半導体突出部2a、2bを半導体基板1上に形成する。なお、半導体突出部2aは単結晶半導体、半導体突出部2bは多結晶半導体を用いることができる。

【0046】

ここで、半導体突出部2a、2bの上下方向にソース層5およびドレイン層6を形成することにより、半導体突出部2a上に半導体突出部2bを積層することでチャネル領域3a、3bのポテンシャルの高さを互いに異ならせることができる。このため、半導体突出部2a、2bのマスク加工工程の増大を抑制しつつ、DWF(Double Work Function)型トランジスタを製造することができる。

【0047】

(第6実施形態)

図21(a)は、第6実施形態に係る半導体装置の概略構成を示す平面図、図21(b)は、第4実施形態に係る半導体装置の概略構成を示す断面図である。なお、図21(b)は、図21(a)のA−A線で切断した。

図21(a)および図21(b)において、半導体突出部2の側壁にはゲート絶縁膜4を介してゲート電極G1〜G4が形成されている。ここで、ゲート電極G1〜G4は、層間絶縁膜H1〜H4を介して順次積層されている。この時、各ゲート電極G1〜G4は、図1(b)のゲート電極7、8にて構成することができる。

【0048】

なお、半導体突出部2には、各層間絶縁膜H1〜H3の高さ方向に位置に対応して拡散層F1〜F3が形成されている。なお、拡散層F1〜F3を半導体突出部2に形成しないようにしてもよい。

【0049】

ここで、半導体突出部2の上下方向にソース層5およびドレイン層6を形成することにより、ゲート電極G1〜G4を積層することで複数のトランジスタを1個分の半導体突出部2に形成することが可能となる。このため、レイアウト面積の増大を抑制しつつ、複数のトランジスタを集積化することが可能となるとともに、短チャネル効果低減と電流駆動力増大の両立を図ることができる。

【0050】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0051】

1 半導体基板、2、2a、2b、11 半導体突出部、3、3a、3b チャネル領域、4 ゲート絶縁膜、5、5´ ソース層、6 ドレイン層、7、8、G1〜G4 ゲート電極、M1 キャップ絶縁膜、9、10 絶縁膜、K1 開口部、H1〜H4 層間絶縁膜、F1〜F3 拡散層

【技術分野】

【0001】

本発明の実施形態は半導体装置に関する。

【背景技術】

【0002】

電界効果トランジスタでは、その微細化に伴ってゲート電極によるチャネル領域のポテンシャル制御性が低下し、短チャネル効果が顕著になり、短チャネル効果低減と電流駆動力増大の両立が困難になっている。

【0003】

一方、フィン型トランジスタでは、チャネル領域の両側にゲート電極が設けられているため、チャネル領域のポテンシャル制御性が向上し、短チャネル効果低減と電流駆動力増大の両立を図るのに有効である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】US2007/063224

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の一つの実施形態の目的は、トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させることが可能な半導体装置を提供することである。

【課題を解決するための手段】

【0006】

実施形態の半導体装置によれば、半導体突出部と、ソース/ドレイン層と、ゲート電極と、チャネル領域とが設けられている。半導体突出部は、半導体基板上に形成されている。ソース/ドレイン層は、前記半導体突出部の上下方向に設けられている。ゲート電極は、前記半導体突出部の側面にゲート絶縁膜を介して設けられている。チャネル領域は、前記半導体突出部の側面に設けられ、前記ソース/ドレイン層と前記半導体突出部との間に形成される空乏層以外の領域において、前記ドレイン層側と前記ソース層側とでポテンシャルの高さが異なっている。

【図面の簡単な説明】

【0007】

【図1】図1(a)は、第1実施形態に係る半導体装置の概略構成を示す平面図、図1(b)は、第1実施形態に係る半導体装置の概略構成を示す断面図、図1(c)は、第1実施形態に係る半導体装置の概略構成のその他の例を示す断面図、図1(d)は、第1実施形態に係る半導体装置の半導体突出部2の上下方向に沿ったチャネル領域のポテンシャルを示す図である。

【図2】図2(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図2(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図3】図3(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図3(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図4】図4(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図4(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】図5(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図5(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】図6(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図6(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】図7(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図7(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図8】図8(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図8(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図9】図9(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図9(b)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。

【図10】図10(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図10(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図11】図11(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図11(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図12】図12(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図12(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図13】図13(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図13(b)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。

【図14】図14(a)は、第4実施形態に係る半導体装置の概略構成を示す平面図、図14(b)は、第4実施形態に係る半導体装置の概略構成を示す断面図、図14(c)は、第4実施形態に係る半導体装置の概略構成のその他の例を示す断面図である。

【図15】図15(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図15(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図16】図16(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図16(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図17】図17(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図17(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図18】図18(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図18(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図19】図19(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図19(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図20】図20(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図20(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。

【図21】図21(a)は、第6実施形態に係る半導体装置の概略構成を示す平面図、図21(b)は、第6実施形態に係る半導体装置の概略構成を示す断面図である。

【発明を実施するための形態】

【0008】

以下、実施形態に係る半導体装置について図面を参照しながら説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0009】

(第1実施形態)

図1(a)は、第1実施形態に係る半導体装置の概略構成を示す平面図、図1(b)は、第1実施形態に係る半導体装置の概略構成を示す断面図、図1(c)は、第1実施形態に係る半導体装置の概略構成のその他の例を示す断面図、図1(d)は、第1実施形態に係る半導体装置の半導体突出部2の上下方向に沿ったチャネル領域のポテンシャルを示す図である。なお、図1(b)および図1(c)は、図1(a)のA−A線で切断した。

図1(a)〜図1(c)において、半導体基板1上には半導体突出部2が形成されている。なお、半導体基板1および半導体突出部2の材料は、Si、Ge、SiGe、SiC、SiSn、PbS、GaAs、InP、InGaAsP、GaP、GaNおよびZnSeなどから選択することができる。また、半導体基板1と半導体突出部2は材料が互いに同一であってもよいし、互いに異なっていてもよい。半導体突出部2の形状は、円柱状であってもよいし、角柱状であってもよい。あるいはフィン状であってもよい。

【0010】

なお、半導体突出部2の形状を円柱とした場合、半導体突出部2に角が形成されないようにでき、電界集中を防止することが可能となることから、トランジスタのオフ電流を低減することができる。

【0011】

また、半導体突出部2の上下方向にはソース層5およびドレイン層6が形成されている。この時、ソース層5を半導体基板1側に形成し、ドレイン層6を半導体突出部2の頂上面側に形成するようにしてもよいし、ドレイン層6を半導体基板1側に形成し、ソース層5を半導体突出部2の頂上面側に形成するようにしてもよい。

【0012】

また、図1(b)に示すように、例えば、ソース層5を半導体基板1側に形成した場合、半導体突出部2の底面側の一部にソース層5がかかるようにしてもよいし、図1(c)に示すように、半導体突出部2の底面側の全体にソース層5´がかかるようにしてもよい。なお、半導体突出部2の底面側の一部にソース層5がかかるようにした場合、半導体突出部2がソース層5にて半導体基板1と電気的に分離されないようにすることができ、基板バイアス効果を及ぼすことができる。

【0013】

また、半導体突出部2の側面にはゲート絶縁膜4を介してゲート電極7、8が形成されている。ここで、ゲート電極7はソース層5側に配置し、ゲート電極8はドレイン層6側に配置されている。なお、半導体突出部2の形状が円柱状または角柱状の場合、半導体突出部2の周囲を取り囲むようにゲート電極7、8を形成するようにしてもよい。また、半導体突出部2の形状がフィン状の場合、半導体突出部2を両側から挟み込むようにゲート電極7、8を形成するようにしてもよい。また、ゲート電極7、8の材料は、ゲート電極7、8の仕事関数が互いに異なるように選択することができる。

【0014】

そして、ソース層5とドレイン層6の間において、半導体突出部2の側面にはチャネル領域3が設けられている。ここで、図1(d)に示すように、チャネル領域3は、ソース層5およびドレイン層6と半導体突出部2との間に形成される空乏層以外の領域において、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。この時、ソース層5ではドレイン層6側に比べてポテンシャルの高さが高くなるようにすることができる。なお、ソース層5ではドレイン層6側に比べてポテンシャルの高さが高くなるようにするために、ゲート電極7は、ゲート電極8に比べて仕事関数を高くすることができる。

【0015】

例えば、ゲート電極7の材料は、例えば、W、ゲート電極8の材料は、例えば、Alを用いることができる。あるいは、ゲート電極7の材料は、例えば、TaN、RuおよびTiAlNなどから選択するようにしてもよいし、ゲート電極8の材料は、例えば、HfN、NiSi、Mo、TiNなどから選択するようにしてもよい。また、ゲート電極7、8の材料として、n型多結晶シリコンとp型多結晶シリコンとを組み合わせて用いるようにしてもよいし、n型多結晶シリコンまたはp型多結晶シリコンの不純物濃度を変化させた構成を用いるようにしてもよい。また、ゲート絶縁膜4の材料は、例えば、SiO2、HfO、HfSiO、HfSiON、HfAlO、HfAlSiONおよびLa2O3などから選択することができる。

【0016】

また、チャネル領域3の不純物濃度のばらつきに起因する電界効果トランジスタの電気的特性のばらつきや移動度の低下を抑制するために、チャネル領域3の不純物濃度を低減し、チャネル領域3を完全空乏化することが好ましい。

【0017】

ここで、半導体突出部2の上下方向にソース層5およびドレイン層6を形成し、半導体突出部2を取り囲むようにゲート電極7、8を配置することにより、半導体基板1側でパンチスルーが起きるのを防止しつつ、チャネル領域3のポテンシャル制御性を向上させることができ、短チャネル効果低減と電流駆動力増大の両立を図ることができる。

【0018】

また、ソース層5ではドレイン層6側に比べてポテンシャルの高さを高くすることにより、短チャネル効果を抑制しつつ、実効的なゲート長を短くすることが可能となり、オフリーク電流の増大を抑制しつつ、電流駆動力増大を図ることが可能となる。

【0019】

なお、上述した実施形態では、ドレイン層6側とソース層5側とでチャネル領域3のポテンシャルの高さを異ならせるために、ゲート電極7、8の仕事関数を互いに異ならせる方法について説明したが、ドレイン層6側とソース層5側とでゲート絶縁膜4の実効膜厚を互いに異ならせるようにしてもよい。この場合、ゲート電極7、8の仕事関数は互いに異なっていてもよいし、互いに同一であってもよい。また、ドレイン層6側とソース層5側とでゲート絶縁膜4の実効膜厚を異ならせる方法としては、ゲート絶縁膜4の膜厚を互いに異ならせるようにしてもよいし、ゲート絶縁膜4の材料を互いに異ならせるようにしてもよい。

【0020】

(第2実施形態)

図2(a)〜図8(a)は、第2実施形態に係る半導体装置の製造方法を示す平面図、図2(b)〜図8(b)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。なお、図2(b)〜図8(b)は、図2(a)〜図8(a)のA−A線でそれぞれ切断した。

【0021】

図2(a)および図2(b)において、CVDなどの方法にて半導体基板1上の全面にキャップ絶縁膜M1を成膜する。そして、フォトリソグラフィ技術およびエッチング技術を用いることにより、半導体基板1上のキャップ絶縁膜M1を円盤状にパターニングする。なお、キャップ絶縁膜M1の材料は、例えば、SiO2またはSiNを用いることができる。そして、キャップ絶縁膜M1をマスクとして半導体基板1の表面をエッチングすることにより、半導体基板1上に半導体突出部2を形成する。

【0022】

次に、図3(a)および図3(b)に示すように、CVDまたは熱酸化などの方法を用いることにより、半導体突出部2の側面にゲート絶縁膜4を形成する。

【0023】

次に、図4(a)および図4(b)に示すように、半導体基板1および半導体突出部2にイオン注入P1を行うことにより、半導体基板1側の半導体突出部2の周囲にソース層5を形成するとともに、半導体突出部2の頂上面側にドレイン層6を形成する。なお、イオン注入P1の注入エネルギーは、半導体突出部2を貫通しないように設定することができる。また、イオン注入P1後に半導体突出部2の熱処理を行うことにより、半導体突出部2の周囲に形成されたソース層5を半導体突出部2の中心方向に張り出させるようにしてもよい。

【0024】

次に、図5(a)および図5(b)に示すように、CVDなどの方法を用いることにより、半導体突出部2が埋め込まれるようにゲート電極7を半導体基板1上に形成する。そして、CMPなどの方法にてキャップ絶縁膜M1が露出するまでゲート電極7を平坦化する。この時、キャップ絶縁膜M1はCMPのストッパ膜として用いることができる。

【0025】

次に、図6(a)および図6(b)に示すように、ゲート電極7のエッチバックを行うことにより、ゲート電極7の上部を除去し、半導体突出部2の上部のゲート絶縁膜4を露出させる。

【0026】

次に、図7(a)および図7(b)に示すように、CVDなどの方法を用いることにより、半導体突出部2の上部が埋め込まれるようにゲート電極8をゲート電極7上に形成する。そして、CMPなどの方法にてキャップ絶縁膜M1が露出するまでゲート電極8を平坦化する。この時、キャップ絶縁膜M1はCMPのストッパ膜として用いることができる。

【0027】

次に、図8(a)および図8(b)に示すように、ゲート電極8のエッチバックを行うことにより、ゲート電極8の上部を除去し、ドレイン層6の側面のゲート絶縁膜4を露出させる。

【0028】

ここで、半導体突出部2の上下方向にソース層5およびドレイン層6を形成することにより、ゲート電極7上にゲート電極8を積層することでドレイン層6側とソース層5側とでチャネル領域3のポテンシャルの高さを異ならせることができる。このため、ゲート電極7、8のマスク加工工程の増大を抑制しつつ、DWF(Double Work Function)型トランジスタを製造することができる。

【0029】

(第3実施形態)

図9(a)〜図13(a)は、第3実施形態に係る半導体装置の製造方法を示す平面図、図9(b)〜図13(b)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。なお、図9(b)〜図13(b)は、図9(a)〜図13(a)のA−A線でそれぞれ切断した。

【0030】

図9(a)および図9(b)において、図3の工程後、CVDなどの方法を用いることにより、半導体突出部2が埋め込まれるようにゲート電極7を半導体基板1上に形成する。

【0031】

次に、図10(a)および図10(b)に示すように、ゲート電極7のエッチバックを行うことにより、半導体突出部2の下部の側面にゲート電極7を残したまま、それ以外のゲート電極7を除去し、半導体突出部2の上部のゲート絶縁膜4を露出させる。

【0032】

次に、図11(a)および図11(b)に示すように、CVDなどの方法を用いることにより、半導体突出部2の上部およびゲート電極7が埋め込まれるようにゲート電極8を半導体基板1上に形成する。

【0033】

次に、図12(a)および図12(b)に示すように、ゲート電極8のエッチバックを行うことにより、半導体突出部2の上部の側面にゲート電極8を残したまま、それ以外のゲート電極8を除去し、半導体突出部2の上部のゲート絶縁膜4を露出させる。

【0034】

次に、図13(a)および図13(b)に示すように、半導体基板1および半導体突出部2にイオン注入P2を行うことにより、半導体基板1側の半導体突出部2の周囲にソース層5を形成するとともに、半導体突出部2の頂上面側にドレイン層6を形成する。

【0035】

(第4実施形態)

図14(a)は、第4実施形態に係る半導体装置の概略構成を示す平面図、図14(b)は、第4実施形態に係る半導体装置の概略構成を示す断面図、図14(c)は、第4実施形態に係る半導体装置の概略構成のその他の例を示す断面図である。なお、図14(b)および図14(c)は、図14(a)のA−A線で切断した。

【0036】

図14(a)〜図14(c)において、この半導体装置では、図1(b)および図1(c)の半導体突出部2の代わりに半導体突出部2a、2bが設けられている。そして、半導体突出部2aは半導体基板1上に形成され、半導体突出部2bは半導体突出部2a上に形成されている。ここで、半導体突出部2a、2bは、バンドギャップが互いに異なるように構成することができる。半導体突出部2a、2bの材料は、例えば、Si、Ge、SiGe、SiC、SiSn、PbS、GaAs、InP、InGaAsP、GaP、GaNおよびZnSeなどから選択することができる。この時、半導体突出部2a、2bのバンドギャップが互いに異なるように構成するために、半導体突出部2a、2bの材料を互いに異ならせるようにしてもよいし、半導体突出部2a、2bの構造を互いに異ならせるようにしてもよい。半導体突出部2a、2bの構造としては、例えば、単結晶、多結晶およびアモルファルを挙げることができる。

【0037】

そして、半導体突出部2a、2bの側面にはチャネル領域3a、3bがそれぞれ設けられている。この時、チャネル領域3aではチャネル領域3bに比べてポテンシャルの高さが高くなるようにすることができる。なお、チャネル領域3aではチャネル領域3bに比べてポテンシャルの高さが高くなるようにするために、半導体突出部2aは、半導体突出部2bに比べてバンドギャップを広くすることができる。

【0038】

ここで、半導体突出部2a、2bは、バンドギャップが互いに異なるように構成することにより、短チャネル効果を抑制しつつ、実効的なゲート長を短くすることが可能となり、オフリーク電流の増大を抑制しつつ、電流駆動力増大を図ることが可能となる。

【0039】

(第5実施形態)

図15(a)〜図20(a)は、第5実施形態に係る半導体装置の製造方法を示す平面図、図15(b)〜図20(b)は、第5実施形態に係る半導体装置の製造方法を示す断面図である。なお、図15(b)〜図20(b)は、図15(a)〜図20(a)のA−A線でそれぞれ切断した。

【0040】

図15(a)および図15(b)において、CVDまたは熱酸化などの方法を用いることにより、半導体基板1上に絶縁膜9を形成する。そして、CVDなどの方法を用いることにより、半導体基板1上にゲート電極7を形成する。

【0041】

次に、図16(a)および図16(b)に示すように、CVDなどの方法を用いることにより、ゲート電極7上にゲート電極8を形成する。

【0042】

次に、図17(a)および図17(b)に示すように、CVDなどの方法を用いることにより、ゲート電極8上に絶縁膜10を形成する。そして、フォトリソグラフィ技術およびエッチング技術を用いることにより、絶縁膜9、10およびゲート電極7、8に開口部K1を形成し、開口部K1を通して半導体基板1の表面を露出させる。

【0043】

次に、図18(a)および図18(b)に示すように、CVDまたは熱酸化などの方法を用いることにより、ゲート電極7、8の側面にゲート絶縁膜4を形成する。

【0044】

次に、図19(a)および図19(b)に示すように、CVDなどの方法を用いることにより、開口部K1内に半導体突出部11を埋め込み、半導体基板1上に半導体突出部11を形成する。なお、半導体突出部11は、例えば、アモルファス半導体を用いることができる。

【0045】

次に、図20(a)および図20(b)に示すように、半導体突出部11の熱処理を行うことにより、半導体突出部11の構造を変化させ、半導体突出部2a、2bを半導体基板1上に形成する。なお、半導体突出部2aは単結晶半導体、半導体突出部2bは多結晶半導体を用いることができる。

【0046】

ここで、半導体突出部2a、2bの上下方向にソース層5およびドレイン層6を形成することにより、半導体突出部2a上に半導体突出部2bを積層することでチャネル領域3a、3bのポテンシャルの高さを互いに異ならせることができる。このため、半導体突出部2a、2bのマスク加工工程の増大を抑制しつつ、DWF(Double Work Function)型トランジスタを製造することができる。

【0047】

(第6実施形態)

図21(a)は、第6実施形態に係る半導体装置の概略構成を示す平面図、図21(b)は、第4実施形態に係る半導体装置の概略構成を示す断面図である。なお、図21(b)は、図21(a)のA−A線で切断した。

図21(a)および図21(b)において、半導体突出部2の側壁にはゲート絶縁膜4を介してゲート電極G1〜G4が形成されている。ここで、ゲート電極G1〜G4は、層間絶縁膜H1〜H4を介して順次積層されている。この時、各ゲート電極G1〜G4は、図1(b)のゲート電極7、8にて構成することができる。

【0048】

なお、半導体突出部2には、各層間絶縁膜H1〜H3の高さ方向に位置に対応して拡散層F1〜F3が形成されている。なお、拡散層F1〜F3を半導体突出部2に形成しないようにしてもよい。

【0049】

ここで、半導体突出部2の上下方向にソース層5およびドレイン層6を形成することにより、ゲート電極G1〜G4を積層することで複数のトランジスタを1個分の半導体突出部2に形成することが可能となる。このため、レイアウト面積の増大を抑制しつつ、複数のトランジスタを集積化することが可能となるとともに、短チャネル効果低減と電流駆動力増大の両立を図ることができる。

【0050】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0051】

1 半導体基板、2、2a、2b、11 半導体突出部、3、3a、3b チャネル領域、4 ゲート絶縁膜、5、5´ ソース層、6 ドレイン層、7、8、G1〜G4 ゲート電極、M1 キャップ絶縁膜、9、10 絶縁膜、K1 開口部、H1〜H4 層間絶縁膜、F1〜F3 拡散層

【特許請求の範囲】

【請求項1】

半導体基板上に形成された半導体突出部と、

前記半導体突出部の上下方向に設けられたソース/ドレイン層と、

前記半導体突出部の側面にゲート絶縁膜を介して設けられたゲート電極と、

前記半導体突出部の側面に設けられ、前記ドレイン層側と前記ソース層側とでポテンシャルの高さが異なるチャネル領域とを備えることを特徴とする半導体装置。

【請求項2】

前記半導体突出部は、前記ドレイン層側と前記ソース層側とでバンドギャップが互いに異なることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記ゲート絶縁膜は、前記ドレイン層側と前記ソース層側とで実効膜厚が互いに異なることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記ゲート電極は、前記ドレイン層側と前記ソース層側とで仕事関数が互いに異なることを特徴とする請求項1から3のいずれか1項に記載の半導体装置。

【請求項5】

前記ゲート電極は、前記半導体突出部の上下方向に複数積層されていることを特徴とする請求項4に記載の半導体装置。

【請求項1】

半導体基板上に形成された半導体突出部と、

前記半導体突出部の上下方向に設けられたソース/ドレイン層と、

前記半導体突出部の側面にゲート絶縁膜を介して設けられたゲート電極と、

前記半導体突出部の側面に設けられ、前記ドレイン層側と前記ソース層側とでポテンシャルの高さが異なるチャネル領域とを備えることを特徴とする半導体装置。

【請求項2】

前記半導体突出部は、前記ドレイン層側と前記ソース層側とでバンドギャップが互いに異なることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記ゲート絶縁膜は、前記ドレイン層側と前記ソース層側とで実効膜厚が互いに異なることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記ゲート電極は、前記ドレイン層側と前記ソース層側とで仕事関数が互いに異なることを特徴とする請求項1から3のいずれか1項に記載の半導体装置。

【請求項5】

前記ゲート電極は、前記半導体突出部の上下方向に複数積層されていることを特徴とする請求項4に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2013−21274(P2013−21274A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2011−155854(P2011−155854)

【出願日】平成23年7月14日(2011.7.14)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成23年7月14日(2011.7.14)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]