半導体装置

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上である。

【解決手段】p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその作製方法、並びに表示装置に関する。

【背景技術】

【0002】

電界効果トランジスタの一種として、絶縁表面を有する基板上に形成された半導体膜を用いてチャネル領域が形成される薄膜トランジスタが知られている。薄膜トランジスタのチャネル領域に用いられる半導体膜に、非晶質シリコン、微結晶シリコン、または多結晶シリコンを用いる技術がある。薄膜トランジスタの代表的な応用例は、液晶テレビジョン装置であり、表示画面を構成する各画素のスイッチングトランジスタとして実用化されている。

【0003】

また、大型のテレビジョン装置を量産高く作製するため、画素のスイッチングトランジスタとして逆スタガ型の薄膜トランジスタを用いた技術が開示されている(特許文献1参照。)。また、高精細な(画素数の多い)液晶表示装置(例えば、フルハイビジョン(FHD)、2k×4k、4k×8k等)を作製するためには、オン電流の高い薄膜トランジスタが必要である。そこで、画素のスイッチングトランジスタとして、非晶質半導体膜をチャネル領域に有する薄膜トランジスタよりオン電流の高い、微結晶半導体膜をチャネル領域に有する薄膜トランジスタが注目されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−21571号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、微結晶シリコン膜を用いてチャネル領域が形成される薄膜トランジスタは、非晶質シリコン膜でチャネル領域が形成される薄膜トランジスタと比較して、オン電流及び電界効果移動度は向上するものオフ電流が高くなってしまい、十分なスイッチング特性が得られないといった問題がある。

【0006】

また、微結晶シリコン膜に光が照射されると、光リーク電流が発生する。このため、逆スタガ型の薄膜トランジスタにおいては、バックライトが微結晶シリコン膜に照射されないように、ゲート電極に遮光機能を設け、上面形状において、ゲート電極から微結晶シリコン膜がはみ出ず、重畳する位置関係とすることが好ましい。

【0007】

しかしながら、p型の薄膜トランジスタがオフ状態の際に、微結晶シリコン膜とソース電極またはドレイン電極とが接する領域であって、ゲート電極と重畳する領域においては、ドレイン電極から微結晶シリコン膜に電子が注入され、オフ電流が上昇するという問題がある。

【0008】

そこで、本発明の一態様は、オフ電流を低減した優れた特性を有する薄膜トランジスタを作製することを課題とする。

【課題を解決するための手段】

【0009】

本発明の一態様は、p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上であることを特徴とする。

【0010】

本発明の一態様は、p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数φMが4.30eV以上、好ましくは4.30eV以上5.05eV以下、更に好ましくは4.40eV以上4.90eV以下であることを特徴とする。

【0011】

なお、p型のスタガ型の薄膜トランジスタにおいて、上記半導体膜は、ゲート絶縁膜に接する微結晶半導体領域と、当該微結晶半導体領域に接する一対の非晶質半導体領域と、当該非晶質半導体領域に接する一対の不純物半導体領域とが順に積層される。

【0012】

また、一対の配線は、タンタル、モリブデン、銅、タングステン、ニッケル、クロム、酸化タングステン、酸化モリブデン、窒化タンタル、窒化チタン、窒化タングステン、窒化モリブデン、アルミニウム−亜鉛酸化物(AZOと示す。)、インジウムースズ酸化物(ITOと示す。)、酸化シリコンを含むインジウム−スズ酸化物等のいずれか一以上を有する。また、一対の配線が積層構造の場合、半導体膜に接する側が、上記材料の一で形成されていればよい。

【発明の効果】

【0013】

本発明の一態様を適用することで、オフ電流が低く優れた電気特性を有する半導体装置を作製することができる。また、電気特性が優れた半導体装置を、生産性高く作製することができる。

【図面の簡単な説明】

【0014】

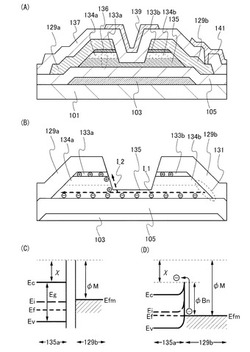

【図1】本発明の一実施の形態に係る半導体装置を説明する断面図及びバンド図である。

【図2】薄膜トランジスタの電流電圧特性を説明する図である。

【図3】半導体膜の電子密度分布を説明する図である。

【図4】薄膜トランジスタの配線及び微結晶半導体のショットキーバリアとオフ電流の関係を説明する図である。

【図5】本発明の一実施の形態に係る半導体装置を説明する断面図である。

【図6】薄膜トランジスタの電流電圧特性を説明する図である。

【図7】半導体膜の電子密度分布を説明する図である。

【図8】薄膜トランジスタの配線及び微結晶半導体のショットキーバリアとオフ電流の関係を説明する図である。

【図9】本発明の一実施の形態に係る半導体装置の作製方法を説明する断面図である。

【図10】本発明の一実施の形態に係る半導体装置の作製方法を説明する断面図である。

【図11】本発明の一実施の形態に係る半導体装置の作製方法を説明する上面図である。

【図12】本発明の一実施の形態に係る半導体装置の作製方法を説明する断面図である。

【図13】本発明の一実施の形態に係る半導体装置の作製方法を説明する断面図である。

【図14】電子書籍の一例を示す斜視図である。

【発明を実施するための形態】

【0015】

本発明の実施の形態について、図面を参照して以下に説明する。ただし、本発明は以下の説明に限定されるものではない。本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解されるからである。したがって、本発明は以下に示す実施の形態の記載内容のみに限定して解釈されるものではない。なお、図面を用いて本発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。

【0016】

(実施の形態1)

本実施の形態では、p型の薄膜トランジスタにおいて、オフ電流が低く、電気特性に優れた薄膜トランジスタについて説明する。

【0017】

図1(A)は、本実施の形態に示す薄膜トランジスタの断面図を示す。

【0018】

図1(A)に示す薄膜トランジスタは、基板101上に、ゲート電極103(第1のゲート電極ともいう。)と、半導体膜136と、ゲート電極103及び半導体膜136の間に設けられるゲート絶縁膜105(第1のゲート絶縁膜ともいう。)と、半導体膜136に接する一対の配線129a、129bとを有する。半導体膜136は、微結晶半導体領域135、一対の非晶質半導体領域134a、134b、及び一対の不純物半導体領域133a、133bが、ゲート絶縁膜105側から順に積層される。また、不純物半導体領域133a、133bは、p型を呈する。

【0019】

また、ゲート絶縁膜105、半導体膜136、配線129a、129bを覆う絶縁膜137(第2のゲート絶縁膜ともいう。)を有してもよい。また、絶縁膜137上にバックゲート電極139(第2のゲート電極ともいう。)及び画素電極141を有してもよい。

【0020】

本実施の形態に示す薄膜トランジスタは、半導体膜136の全てがゲート電極103と重畳している。即ち、平面形状において、半導体膜136の端部がゲート電極103の端部より内側に位置する。このため、基板101側からバックライトが薄膜トランジスタに照射されても、ゲート電極103が当該光を遮光するため、半導体膜136に光が入射されず、薄膜トランジスタの光リーク電流を低減することができる。

【0021】

しかしながら、当該構造の薄膜トランジスタにおいては、オフ状態において、半導体膜136及び一対の配線129a、129bが接する領域での電子の注入により、リーク電流(オフ電流)が上昇してしまう。ここで、p型の薄膜トランジスタにおいて、オフ電流の流れる原理について、図1(B)を用いて説明する。

【0022】

図1(B)は、図1(A)に示す薄膜トランジスタの一部を拡大した図である。なお、図1(B)においては、ハッチングパターンを省略している。以下、配線129aをソース、配線129bをドレインとして説明する。

【0023】

図1(B)において、微結晶半導体領域135及び配線129bが接する領域131が存在する。薄膜トランジスタはp型であるため、薄膜トランジスタがオフ状態となる電圧(しきい値電圧より高い電圧)がゲート電極103に印加されると、領域131において、ドレインである配線129bから微結晶半導体領域135に電子が注入される。この結果、配線129bから微結晶半導体領域135を介して配線129aに流れる電流I_1と、配線129bから微結晶半導体領域135、非晶質半導体領域134a、及び不純物半導体領域133aを介して配線129aに流れる電流I_2とが発生する。なお、電流I_2は、配線129bから微結晶半導体領域135に注入された電子と、不純物半導体領域133aから非晶質半導体領域134a及び微結晶半導体領域135に注入された正孔が再結合して流れる電流である。

【0024】

ここで、微結晶半導体領域135の代表例である微結晶シリコン135aと、配線129bとが接する領域のエネルギーバンド図を図1(C)に示す。

【0025】

図1(C)は、平衡状態の微結晶シリコン135a及び配線129bのエネルギーバンド図である。微結晶シリコン135aにおいて、χは微結晶シリコンの電子親和力(真空準位と、微結晶シリコン135aの伝導帯下端Ecとの間のポテンシャル差)を示し、Egは、微結晶シリコン135aの禁制帯幅(伝導帯下端Ecと、価電子帯上端Evとの間のポテンシャル差)を示す。なお、薄膜トランジスタはp型であるため、微結晶シリコン135aのフェルミ準位Efは、真性フェルミ準位Eiと価電子帯Evの上端との間に位置する。なお、微結晶シリコン135aのフェルミ準位はアクセプター濃度が高い程、即ち、よりp型である程、価電子帯Evの上端に近づく。また、配線129bにおいて、φMは配線129bの材料の仕事関数を示す。

【0026】

図1(D)に示すように、微結晶シリコン135a及び配線129bを接合すると(但し、ゲート電圧Vg、及びソースドレイン電圧Vdsは0V)、微結晶シリコン135a及び配線129bが接する領域において、微結晶シリコン135aのフェルミ準位Efと、配線129bのフェルミ準位Efmが一致する。φBnは、微結晶シリコン135a及び配線129bが接する領域での障壁(ショットキーバリア)を示す。ショットキーバリアは数式1で表される。

【0027】

【数1】

【0028】

ショットキーバリアφBnが大きければ大きい程、配線129bから微結晶シリコン135aに電子が注入されにくく、オフ電流が流れにくい。このため、ショットキーバリアφBnを0.65eV以上とすることで、p型の薄膜トランジスタのオフ電流を低減することができる。

【0029】

微結晶半導体領域の電子親和力χは3.55eV以上3.75eV以下である。微結晶半導体領域の電子親和力χが3.65eVのとき、配線129bの材料の仕事関数φMを、4.3eV以上とすることで、ショットキーバリアφbnが大きくなり、0.65V以上となるため、p型の薄膜トランジスタのオフ電流を低減することができる。

【0030】

p型の薄膜トランジスタにおいて、オフ電流を低減することが可能な配線129a、129bの材料としては、タンタル、モリブデン、銅、タングステン、ニッケル、クロム、酸化タングステン、酸化モリブデン、窒化タンタル、窒化チタン、窒化タングステン、窒化モリブデン、アルミニウム−亜鉛酸化物(AZOと示す。)、インジウムースズ酸化物(ITOと示す。)、酸化シリコンを含むインジウム−スズ酸化物等がある。これらの仕事関数φMを表1に示す。なお、配線129a、129bは、これらの材料に限定されず、仕事関数φMが4.30eV以上である材料を適宜用いることができる。

【0031】

【表1】

【0032】

表1に示す材料の仕事関数φMは、UPS法(紫外線光電子分光法)、光電子分光法(PES)、電場電子放出法等で得られる。なお、配線129a、129bは、積層構造とすることが可能であり、この場合は、表1に示す材料で形成される膜を半導体膜136側に設ければよく、表1の他の材料との積層構造することができる。

【0033】

ここで、p型の薄膜トランジスタの特性と、配線の材料の仕事関数φMの関係について、計算機を用いて検証した結果について説明する。具体的には、配線の材料の仕事関数φMと薄膜トランジスタの電流電圧特性について比較した。なお、計算には、デバイスシミュレーションソフトAtlas(Silvaco Data Systems社製)を用いた。

【0034】

計算に用いた薄膜トランジスタの構造を図1(A)に示す。

【0035】

計算に用いた薄膜トランジスタの詳細について説明する。

【0036】

ゲート電極103としては、仕事関数φMが4.1eVの導電膜を用いた。

【0037】

ゲート絶縁膜105としては、厚さ300nm、比誘電率6.85のSiNxを用いた。

【0038】

微結晶半導体領域135としては、微結晶シリコンを想定して各物性パラメータを以下に示す値を用いた。禁制帯幅Egを1.1eV、電子親和力χを3.65eV、電子の移動度μnを0.1cm2/Vs、正孔の移動度μpを0.7cm2/Vs、アクセプター濃度Naを1×1015cm−3とした。なお、アクセプター濃度Naは濃度が低いため、実際のプロセス工程ではアクセプターを添加しなくともよい。また、微結晶半導体領域135の側面とゲート絶縁膜105の間でなす角度を45度とした。また、微結晶半導体領域135において、非晶質半導体領域134a、134bと重畳する領域の厚さを70nm、非晶質半導体領域134a、134bと重畳しない領域の厚さを50nmとした。

【0039】

非晶質半導体領域134a、134bとしては、アモルファスシリコンを想定して各物性パラメータを以下に示す値を用いた。禁制帯幅Egを1.7eV、電子親和力χを3.4eV、電子の移動度μnを1cm2/Vs、正孔の移動度μpを0.1cm2/Vsとし、厚さを80nmとした。

【0040】

不純物半導体領域133a、133bとしては、アクセプター濃度Naを6×1016cm−3、厚さを50nmとし、ボロンを含むアモルファスシリコンを想定した。

【0041】

配線129a、129bとしては、仕事関数φMが3.8〜4.5eVの材料を用いた。

【0042】

チャネル長方向の微結晶半導体領域135の長さを19.5μmとし、チャネル長を3.3μm、チャネル幅を20μmとした。

【0043】

また、ゲート絶縁膜105及び微結晶半導体領域135の界面に、欠陥準位を仮定した。また、Band to Band Tunneling Model(BBT Model)を仮定した。BBT Modelにおいて、数式2に示すトンネル電流の発生率GBBTを用いた。

【0044】

【数2】

【0045】

なお、数式2において、Eは電界強度である。微結晶シリコンに対しては、A=2×1013、B=2×106、γ=1.5を用いた。また、アモルファスシリコンに対しては、A=1×1010、B=3×106、γ=1.5を用いた。

【0046】

また、計算の都合上、配線129b及び半導体膜136をショットキー接合と仮定した。また、配線129a及び半導体膜136をオーミック接合と仮定した。

【0047】

このときの薄膜トランジスタの電流電圧特性を図2に示す。太曲線は配線129bの仕事関数φMが4.3eV〜4.6eVの電流電圧特性であり、細曲線は配線129bの仕事関数φMが3.9eV〜4.2eVの電流電圧特性である。配線129bの仕事関数φMが4.3eV以上では、ゲート電圧Vgが10Vのとき、オフ電流が1×10−12Aより低い。一方、配線129bの仕事関数φMが4.3eVより低くなると、ゲート電圧Vgが10Vのときのオフ電流が1×10−12A以上であるため、オフ状態において、リーク電流が上昇している。

【0048】

また、半導体膜の電子密度分布を図3に示す。なお、ゲート電圧Vgを10V、ソースドレイン電圧(Vds)を−3Vとした。

【0049】

図3(A)は、配線129bの仕事関数φMを4.0eV、図3(B)は、配線129bの仕事関数φMを4.3eVとしたときの、半導体膜における電子密度分布である。なお、等高線上またはその近傍に電子密度の値を示す。

【0050】

図3から、配線129bの仕事関数φMが4.0eVのときと比較して、4.3eVでは、微結晶半導体領域及び配線が接する領域131での電子密度が低い。

【0051】

次に、室温(27℃)の時の、配線129b及び微結晶シリコン135aのショットキーバリアとオフ電流について、図4に示す。

【0052】

図4において、横軸はショットキーバリアφBnであり、縦軸はゲート電圧Vgが(Vth+10)Vのときのオフ電流である。また、微結晶シリコンの電子親和力χが3.55eV、3.65eV、3.75eVにおける、ショットキーバリア及びオフ電流の関係を示す。

【0053】

図4から、ショットキーバリアφBnが0.65eV以上において、オフ電流が1×10−12Aより低いことがわかる。

【0054】

以上のことから、p型の薄膜トランジスタにおいて、微結晶半導体領域の電子親和力χが3.65eVのとき、仕事関数φMを4.30eV以上、好ましくは4.40eV以上とすることで、配線から微結晶半導体領域への電子注入を低減し、薄膜トランジスタのオフ電流を低減することができる。また、ショットキーバリアφBnを0.65eV以上とすることで、p型の薄膜トランジスタのオフ電流を低減することができる。

【0055】

次に、オフ電流を低減できるより好ましい配線の仕事関数φMの範囲について説明する。

【0056】

配線の仕事関数φMが高くなると、ゲート電極103にオフ状態となる電圧(しきい値電圧より高い電圧)が印加された状態において、半導体膜の価電子帯及び伝導帯がより急峻な曲線となる。そのため、微結晶半導体領域から不純物半導体領域における電界が強くなる。この結果、図5に示すように、図1(B)と同様に電流I_1及びI_2が流れると共に、不純物半導体領域133bの正孔と、非晶質半導体領域134a、134bの間でトンネル電流I_3が発生し、非晶質半導体領域134bの電子密度が増加する。このため、オフ電流がさらに上昇する。

【0057】

微結晶半導体領域の電子親和力χが3.65eVのとき、配線129bの仕事関数φMを、5.05eV以下、更に好ましくは4.9eVとすることで、p型の薄膜トランジスタのオフ電流の増加を防ぐことができる。即ち、配線129bの仕事関数φMを、4.30eV以上5.05eV以下、更に好ましくは4.40eV以上4.90eVとすることで、p型の薄膜トランジスタのオフ電流を低減することができる。

【0058】

ここで、上記計算機を用いた検証と同様に、デバイスシミュレーションソフトAtlas(Silvaco Data Systems社製)を用いて、p型の薄膜トランジスタの特性と、配線の材料の仕事関数φMの関係について、計算機を用いて検証した結果について説明する。

【0059】

計算に用いた薄膜トランジスタの構造及び条件は、上記検証と同様とし、且つ、配線129bとして、仕事関数φMが4.7〜5.4eVの材料を用いて計算を行った。このときの薄膜トランジスタの電流電圧特性を図6に示す。太曲線は配線129bの仕事関数φMが4.7eV〜5.0eVの電流電圧特性であり、細曲線は配線129bの仕事関数φMが5.1eV〜5.4eVの電流電圧特性である。

【0060】

配線129bの仕事関数φMが5.0eV以下では、Vgが10Vのとき、オフ電流が1×10−12Aより低い。一方、配線129bの仕事関数φMが5.0eVより高くなると、Vgが10Vのときオフ電流が1×10−12A以上であるため、オフ状態において、リーク電流が上昇している。

【0061】

また、半導体膜の電子密度分布を図7に示す。なお、ゲート電圧Vgを10V、ソースドレイン電圧(Vds)を−3Vとした。

【0062】

図7(A)は、配線129bの仕事関数φMを5.0eV、図7(B)は、配線129bを仕事関数φMが5.3eVとしたときの、半導体膜における電子密度分布である。なお、等高線上またはその近傍に電子密度の値を示す。

【0063】

図7から、配線129bの仕事関数φMが5.0eVでは、非晶質半導体領域134bにおける電子密度は低い。一方、配線129bの仕事関数φMが5.3eVでは、非晶質半導体領域134bにおける電子密度が高い。これは、非晶質半導体領域134bでトンネル電流が発生したためである。

【0064】

また、室温(27℃)の時の、配線129bの仕事関数φMとオフ電流について、図8に示す。

【0065】

図8において、横軸は仕事関数、縦軸はゲート電圧Vgが(Vth+10)Vのときのオフ電流である。また、微結晶シリコンの電子親和力χが3.65eVにおける、仕事関数及びオフ電流の関係を示す。

【0066】

図8から、仕事関数φMが5.05eV以下において、オフ電流が1×10−12Aより低いことがわかる。

【0067】

以上のことから、配線129bの仕事関数φMを5.05eV以下とすることで、p型の薄膜トランジスタのオフ電流の増加を防ぐことができる。

【0068】

p型の薄膜トランジスタにおいて、微結晶半導体領域の電子親和力χが3.65eVのとき、仕事関数φMを4.30eV以上、好ましくは4.30eV以上5.05eV以下、更に好ましくは4.40eV以上4.90eV以下とすることで、配線から微結晶半導体領域への電子注入を低減し、薄膜トランジスタのオフ電流を低減することができる。また、ショットキーバリアφBnを0.65eV以上とすることで、p型の薄膜トランジスタのオフ電流を低減することができる。

【0069】

ここで、図1(A)に示す薄膜トランジスタの各構成について、以下に説明する。

【0070】

基板101としては、ガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板等を用いることができる。また、基板に透光性を要しない場合には、ステンレス等の金属基板を用いてもよい。ガラス基板としては、例えば、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス若しくはアルミノケイ酸ガラス等の無アルカリガラス基板を用いるとよい。なお、基板101のサイズに限定はなく、例えばフラットパネルディスプレイの分野でよく使われる第3世代〜第10世代のガラス基板を用いることができる。

【0071】

ゲート電極103は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム、ニッケル等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体、Ag−Pd−Cu合金、Al−Nd合金、Al−Ni合金などを用いてもよい。

【0072】

例えば、ゲート電極103の二層の積層構造としては、アルミニウム膜上にモリブデン膜を積層した二層の積層構造、または銅膜上にモリブデン膜を積層した二層構造、または銅膜上に窒化チタン膜若しくは窒化タンタル膜を積層した二層構造、窒化チタン膜とモリブデン膜とを積層した二層構造、酸素を含む銅−マグネシウム合金膜と銅膜とを積層した二層構造、酸素を含む銅−マンガン合金膜と銅膜とを積層した二層構造、銅−マンガン合金膜と銅膜とを積層した二層構造などとすることが好ましい。三層の積層構造としては、タングステン膜または窒化タングステン膜と、アルミニウムとシリコンの合金膜またはアルミニウムとチタンの合金膜と、窒化チタン膜またはチタン膜とを積層した三層構造とすることが好ましい。電気的抵抗が低い膜上にバリア膜として機能する金属膜が積層されることで、電気的抵抗を低くでき、且つ金属膜から半導体膜への金属元素の拡散を防止することができる。

【0073】

ゲート絶縁膜105は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、または窒化酸化アルミニウム膜を、単層でまたは積層して形成することができる。

【0074】

なお、ここでは、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS:Hydrogen Forward Scattering Spectrometry)を用いて測定した場合に、組成範囲として酸素が50〜70原子%、窒素が0.5〜15原子%、シリコンが25〜35原子%、水素が0.1〜10原子%の範囲で含まれるものをいう。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS及びHFSを用いて測定した場合に、組成範囲として酸素が5〜30原子%、窒素が20〜55原子%、シリコンが25〜35原子%、水素が10〜30原子%の範囲で含まれるものをいう。ただし、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

【0075】

なお、ゲート絶縁膜105を酸化シリコンまたは酸化窒化シリコン等の酸化絶縁膜により形成することで、薄膜トランジスタの閾値電圧の変動を低減することができる。

【0076】

半導体膜136を構成する微結晶半導体領域135は、微結晶シリコン、微結晶シリコンゲルマニウム、微結晶ゲルマニウム等の電子親和力χが3.55eV以上3.75eV以下である半導体で形成される。微結晶半導体は、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造の半導体で形成される。このため、微結晶半導体は非晶質半導体領域を有する。微結晶半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な半導体であり、混相粒径が2nm以上200nm以下、好ましくは10nm以上80nm以下、より好ましくは、20nm以上50nm以下の柱状または針状の混相粒が基板表面に対して法線方向に成長している。このため、柱状または針状の混相粒の界面には、粒界が形成される場合もある。なお、ここでの結晶粒径は、基板表面に対して平行な面における結晶粒の最大直径をいう。また、混相粒とは、非晶質半導体領域と、単結晶とみなせる微小結晶である結晶子とを含む結晶粒である。

【0077】

微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルのピークが単結晶シリコンを示す520cm−1よりも低波数側に、シフトしている。即ち、単結晶シリコンを示す520cm−1とアモルファスシリコンを示す480cm−1の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手(ダングリングボンド)を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含んでいる。さらに、ヘリウム、アルゴン、ネオン、クリプトン、キセノンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体が得られる。このような微結晶半導体に関する記述は、例えば、米国特許4,409,134号で開示されている。

【0078】

半導体膜136を構成する非晶質半導体領域134a、134bは、アモルファスシリコン、アモルファスシリコン−ゲルマニウム等で形成される。

【0079】

半導体膜136を構成する不純物半導体領域133a、133bは、p型を呈する半導体で形成され、代表的には、ボロンを有するアモルファスシリコン、またはボロンを有する微結晶シリコンで形成される。

【0080】

絶縁膜137は、ゲート絶縁膜105に示す材料を適宜用いて形成することができる。

【0081】

バックゲート電極139及び画素電極141は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、または酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を用いて形成することができる。

【0082】

また、バックゲート電極139及び画素電極141は、透光性を有する導電性高分子(導電性ポリマーともいう。)を含む導電性組成物を用いて形成することができる。バックゲート電極139は、シート抵抗が10000Ω/sq以下であって、且つ波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1Ω・cm以下であることが好ましい。

【0083】

導電性高分子としては、いわゆるπ電子共役系導電性高分子を用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、または、アニリン、ピロール及びチオフェンの2種以上の共重合体若しくはその誘導体等がある。

【0084】

本実施の形態に示すp型の薄膜トランジスタは、微結晶半導体領域及び配線の接する領域における電子の注入を低減することが可能である。この結果、薄膜トランジスタのオフ電流を低減することができる。また、本実施の形態に示す薄膜トランジスタは逆スタガ型であるため、オフ電流が低く電気特性に優れた薄膜トランジスタを量産性高く作製することができる。

【0085】

(実施の形態2)

本実施の形態では、本発明の一形態である半導体装置に形成される薄膜トランジスタの作製方法について、図9乃至図11を参照して説明する。なお、同一の基板上に形成する薄膜トランジスタを全て同じ極性に統一すると、工程数を抑えることができて好ましい。本実施の形態では、p型の薄膜トランジスタの作製方法について説明する。

【0086】

なお、オン電流とは、薄膜トランジスタがオン状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、p型の薄膜トランジスタの場合には、ゲート電圧が薄膜トランジスタの閾値電圧よりも低いときにソース電極とドレイン電極との間に流れる電流である。

【0087】

また、オフ電流とは、薄膜トランジスタがオフ状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、p型の薄膜トランジスタの場合には、ゲート電圧が薄膜トランジスタの閾値電圧よりも高いときにソース電極とドレイン電極との間に流れる電流である。

【0088】

図9(A)に示すように、基板101上にゲート電極103(第1のゲート電極ともいう。)を形成する。次に、ゲート電極103を覆うゲート絶縁膜105を形成し、ゲート絶縁膜105上に、微結晶半導体膜107、非晶質半導体膜109、及び不純物半導体膜111を形成する。

【0089】

ゲート電極103は、基板101上に、CVD法、スパッタリング法または真空蒸着法を用いて、上記した材料を用いて導電膜を形成し、該導電膜上にフォトリソグラフィ法またはインクジェット法等によりマスクを形成し、該マスクを用いて導電膜をエッチングして形成することができる。また、銀、金または銅等の導電性ナノペーストをインクジェット法により基板上に吐出し、焼成することで形成することもできる。なお、ゲート電極103と、基板101との密着性向上を目的として、上記の金属材料の窒化物膜を、基板101と、ゲート電極103との間に設けてもよい。ここでは、基板101上に導電膜を形成し、フォトリソグラフィ工程により形成したマスクを用いて、当該導電膜をエッチングして、ゲート電極103を形成する。

【0090】

なお、ゲート電極103の側面は、テーパー形状とすることが好ましい。例えば、基板101及びゲート電極103の側面のなす角度を、20度以上60度以下、好ましくは30度以上50度以下とすることが好ましい。これは、後の工程で、ゲート電極103上に形成される絶縁膜、半導体膜及び配線が、ゲート電極103の段差箇所において切断されないようにするためである。ゲート電極103の側面をテーパー形状にするためには、マスクを後退させつつエッチングを行えばよい。

【0091】

また、ゲート電極103を形成する工程により、ゲート配線(走査線)及び容量配線も同時に形成することができる。なお、走査線とは画素を選択する配線をいい、容量配線とは画素の保持容量の一方の電極に接続された配線をいう。ただし、これに限定されず、ゲート配線及び容量配線の一方または双方と、ゲート電極103とは別に設けてもよい。

【0092】

ゲート絶縁膜105は、CVD法またはスパッタリング法等を用いて形成することができる。プラズマCVD法によるゲート絶縁膜105の形成工程において、グロー放電プラズマの生成は、3MHzから30MHz、代表的には13.56MHz、27.12MHzのHF帯の高周波電力、または30MHzより大きく300MHz程度までのVHF帯の高周波電力、代表的には、60MHzを印加することで行われる。また、1GHz以上のマイクロ波の高周波電力を印加することで行われる。なお、高周波電力がパルス状に印加されるパルス発振や、連続的に印加される連続発振とすることができる。また、HF帯の高周波電力と、VHF帯の高周波電力を重畳させることで、大面積基板においてもプラズマのムラを低減し、膜厚及び膜質の均一性を高めることができると共に、堆積速度を高めることができる。また、高周波数が1GHz以上であるマイクロ波プラズマCVD装置を用いてゲート絶縁膜105を形成すると、ゲート絶縁膜の耐圧を向上させることができるため、信頼性の高い薄膜トランジスタを得ることができる。

【0093】

また、ゲート絶縁膜105として、有機シランガスを用いたCVD法により酸化シリコン膜を形成することで、後に形成する半導体膜の微結晶半導体領域の結晶性を高めることが可能であるため、薄膜トランジスタのオン電流及び電界効果移動度を高めることができる。有機シランガスとしては、テトラエトキシシラン(TEOS:化学式Si(OC2H5)4)、テトラメチルシラン(TMS:化学式Si(CH3)4)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OC2H5)3)、トリスジメチルアミノシラン(SiH(N(CH3)2)3)等のシリコン含有化合物を用いることができる。

【0094】

ここでは、プラズマCVD法によりゲート絶縁膜105を形成する。

【0095】

微結晶半導体膜107は、原料ガスとして、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合する、プラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合し、グロー放電プラズマにより形成する。ここでは、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を50倍以上6000倍以下、好ましくは50倍以上3000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上50000Pa以下(0.5Torr以上370Torr以下)、更に好ましくは67Pa以上13332Pa以下(0.5Torr以上100Torr以下)とする条件により、微結晶半導体膜107を形成する。

【0096】

このときの堆積温度は、室温〜350℃とすることが好ましく、より好ましくは150〜280℃とする。なお、上部電極及び下部電極の間隔は、プラズマが発生しうる間隔とすればよい。なお、本明細書において、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量は、希釈されてない100%のシリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量である。このため、シリコンまたはゲルマニウムを含む堆積性気体が希釈されている場合は、シリコンまたはゲルマニウムを含む堆積性気体を100%として、水素流量を調整すればよい。

【0097】

非晶質半導体膜109として、原料ガスとして、シリコンまたはゲルマニウムを含む堆積性気体を用いるプラズマCVD法により形成する。または、原料ガスとして、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合する、プラズマCVD法により形成する。ここでは、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を0.1倍以上10倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上50000Pa以下(0.5Torr以上370Torr以下)、更に好ましくは67Pa以上13332Pa以下(0.5Torr以上100Torr以下)とする条件により、非晶質半導体膜109を形成する。

【0098】

このときの堆積温度は、室温〜350℃とすることが好ましく、より好ましくは150〜280℃とする。なお、上部電極及び下部電極の間隔は、プラズマが発生しうる間隔とすればよい。

【0099】

不純物半導体膜111は、プラズマCVD装置の処理室内において、シリコンを含む堆積性気体と、水素と、ジボラン(水素希釈またはシラン希釈)とを混合する、プラズマCVD法により、不純物半導体膜111を形成する。

【0100】

なお、シリコンまたはゲルマニウムを含む堆積性気体の代表例としては、SiH4、Si2H6、GeH4、Ge2H6等がある。

【0101】

また、プラズマCVD法による微結晶半導体膜107、非晶質半導体膜109、及び不純物半導体膜111の形成工程において、グロー放電のプラズマ生成は、ゲート絶縁膜105で列挙した高周波電力を適宜供給することで行われる。

【0102】

次に、不純物半導体膜111上にマスクを形成した後、微結晶半導体膜107、非晶質半導体膜109、及び不純物半導体膜111のそれぞれ一部をエッチングして、図9(B)に示すように、微結晶半導体領域117a、非晶質半導体領域117b、及び不純物半導体領域117cを有する半導体膜117を形成する。

【0103】

次に、図9(C)に示すように、ゲート絶縁膜105及び半導体膜117上に導電膜127を形成する。

【0104】

導電膜127は、配線129a、129bに列挙する材料を適宜用いて形成する。

【0105】

導電膜127は、CVD法、スパッタリング法または真空蒸着法を用いて形成する。

【0106】

次に、導電膜127上にマスクを形成した後、該マスクを用いて導電膜127をエッチングしてソース電極及びドレイン電極として機能する配線129a、129b形成する。次に、半導体膜117の一部をエッチングして、ソース領域及びドレイン領域として機能する一対の不純物半導体領域133a、133b、一対の非晶質半導体領域134a、134b、及び凹部を有する微結晶半導体領域135を有する半導体膜136を形成する(図10(A)参照)。

【0107】

導電膜127のエッチングは、ドライエッチングまたはウェットエッチングを用いることができる。エッチング条件は、導電膜127をエッチングする条件を適宜用いる。ドライエッチング方法については特に限定はなく、誘導結合型プラズマ(ICP:Inductively Coupled Plasma)方式、容量結合型プラズマ(CCP:Capacitively Coupled Plasma)方式、電子サイクロトン共鳴プラズマ(ECR:Electron Cyclotron Resonance)方式、反応性イオンエッチング(RIE:Reactive Ion Etching)方式等を適宜用いることができる。

【0108】

なお、配線129a、129bの一方は、ソース電極またはドレイン電極のみならず信号線としても機能する。ただし、これに限定されず、ソース電極及びドレイン電極とは別に信号線を設けてもよい。

【0109】

なお、ここでは、導電膜127から、微結晶半導体領域117aの一部までのエッチングを一度のエッチング工程で行ったが、以下に示すように、複数工程で行ってもよい。例えば、導電膜127上にマスクを形成し、該マスクを用いて導電膜127、不純物半導体領域117c、及び非晶質半導体領域117bの一部をエッチングする。当該、エッチング工程においては、微結晶半導体領域117aを露出しないように半導体膜117をエッチングする必要があり、少なくとも不純物半導体領域117cをエッチングする。この後、マスクを除去する。当該工程においてマスクを除去する溶液の一部が、非晶質半導体領域の表面に残存する場合がある。

【0110】

次に、配線129a、129bをマスクとして、非晶質半導体領域、及び微結晶半導体領域117aの一部をエッチングして、図10(A)に示すように分離された一対の非晶質半導体領域134a、134bと、凹部を有する微結晶半導体領域135を形成する。即ち、微結晶半導体領域135、一対の非晶質半導体領域134a、134b、及び一対の不純物半導体領域133a、133bを有する半導体膜136を形成する。

【0111】

上記工程のように、エッチング工程を2段階とし、1段階目のエッチングで、微結晶半導体領域が露出しない状態までエッチングし、その後マスクを除去する。当該、マスク除去の工程においては、微結晶半導体領域117aが非晶質半導体領域132に覆われているため、微結晶半導体領域177aが、残渣物と触れることがない。また、マスクを除去した後、2段階目のエッチングとして、配線129a、129bをマスクとして用いて、非晶質半導体領域132をエッチングして、微結晶半導体領域135を形成する。このため、残渣物は、バックチャネルには残存しない。

【0112】

以上のことから後にバックゲート電極を形成する場合、微結晶半導体領域135の凹部は、薄膜トランジスタのバックゲート側のチャネル領域となるため、当該領域の残渣物を除去することで、バックチャネルに残存した残渣物が原因のリーク電流が発生しないため、薄膜トランジスタのオフ電流をより低減することができる。

【0113】

次に、微結晶半導体領域135及び非晶質半導体領域134a、134bの表面にプラズマ処理、代表的には水プラズマ処理、酸素プラズマ処理、アンモニアプラズマ処理、窒素プラズマ処理、酸素及び水素の混合ガスによるプラズマ処理等を行ってもよい。

【0114】

ドライエッチングに続けて水プラズマ処理を行うことで、マスクの残渣を除去すると共に、微結晶半導体領域135の欠陥を低減することができる。また、プラズマ処理を行うことで、ソース領域とドレイン領域との間の絶縁性を高めることができ、完成する薄膜トランジスタのオフ電流を低減し、電気的特性のばらつきを低減することができる。

【0115】

以上の工程によりシングルゲート型の薄膜トランジスタを作製することができる。また、本実施の形態に示す構造とすることで、オフ電流が低いシングルゲート型の薄膜トランジスタを生産性高く作製することができる。

【0116】

次に、図10(B)に示すように、半導体膜136上に絶縁膜137(第2のゲート絶縁膜ともいう。)を形成する。絶縁膜137は、ゲート絶縁膜105と同様に形成することができる。

【0117】

次に、フォトリソグラフィ工程によりマスクを形成し、当該マスクを用いて絶縁膜137に開口部(図示しない。)を形成する。次に、絶縁膜137上にバックゲート電極139(第2のゲート電極ともいう。)及び画素電極141を形成する(図10(C)参照)。以上の工程により、デュアルゲート型の薄膜トランジスタを作製することができる。

【0118】

バックゲート電極139及び画素電極141は、CVD法、スパッタリング法または真空蒸着法を用いて、上記材料のいずれかを用いた薄膜を形成した後、フォトリソグラフィ工程によって形成したマスクを用いて上記薄膜をエッチングすることで、形成できる。また、バックゲート電極139及び画素電極141は、銀、金または銅等の導電性ナノペーストを用いてスクリーン印刷法またはインクジェット法等を用いて吐出し、焼成することで形成しても良い。

【0119】

次に、薄膜トランジスタの上面図である図11を用いて、バックゲート電極の形状を説明する。

【0120】

図11(A)に示すように、バックゲート電極139は、ゲート電極103と平行に形成することができる。この場合、バックゲート電極139に印加する電位と、ゲート電極103に印加する電位とを、それぞれ任意に制御することが可能である。このため、薄膜トランジスタのしきい値電圧を制御することができる。また、キャリアが流れる領域、即ちチャネル領域が、微結晶半導体領域のゲート絶縁膜105側、及び絶縁膜137側に形成されるため、薄膜トランジスタのオン電流を高めることができる。

【0121】

また、図11(B)に示すように、バックゲート電極139は、ゲート電極103に接続させることができる。即ち、ゲート絶縁膜105及び絶縁膜137に形成した開口部150において、ゲート電極103及びバックゲート電極139が接続する構造とすることができる。この場合、バックゲート電極139に印加する電位と、ゲート電極103に印加する電位とは、等しい。この結果、半導体膜において、キャリアが流れる領域、即ちチャネル領域が、微結晶半導体領域のゲート絶縁膜105側、及び絶縁膜137側に形成されるため、薄膜トランジスタのオン電流を高めることができる。

【0122】

また、図11(C)に示すように、バックゲート電極139は、ゲート電極103と接続せず、フローティングでもよい。バックゲート電極139に印加せずとも、チャネル領域が、微結晶半導体領域のゲート絶縁膜105側、及び絶縁膜137側に形成されるため、薄膜トランジスタのオン電流を高めることができる。

【0123】

さらには、図11(D)に示すように、バックゲート電極139は、絶縁膜137を介して配線129a、129bと重畳してもよい。ここでは、図11(A)に示す構造のバックゲート電極139を用いて示したが、図11(B)及び図11(C)に示すバックゲート電極139も同様に配線129a、129bと重畳してもよい。

【0124】

本実施の形態により、オフ電流の低いp型の逆スタガ型薄膜トランジスタを量産性高く作製することができる。

【0125】

(実施の形態3)

本実施の形態では、実施の形態1と比較して、オフ電流を低減しつつオン電流を高めることが可能な薄膜トランジスタの作製方法について、図12を用いて説明する。

【0126】

本実施の形態では、図9(A)において、微結晶半導体膜107、非晶質半導体膜109、及び不純物半導体膜111の代わりに、図12に示すような半導体膜118を形成することを特徴とする。なお、図12は、図9(A)のゲート絶縁膜105から不純物半導体膜111の間の拡大図である。

【0127】

半導体膜118は、微結晶半導体膜118a、微結晶半導体領域118c及び非晶質半導体領域118dを有する半導体膜118b、並びに不純物半導体膜111を有する。半導体膜118は、微結晶半導体領域118c及び非晶質半導体領域118dの界面が凹凸状であることを特徴とする。なお、微結晶半導体膜118a及び半導体膜118bの界面を点線で示したが、実際には当該界面は観察されない。

【0128】

図12(A)に示すように、半導体膜118bの微結晶半導体領域118c及び非晶質半導体領域118dの界面は凹凸状であり、凸部はゲート絶縁膜105から不純物半導体膜111に向かって、先端が狭まる(凸部の先端が鋭角である)凸状(錐形状)である。なお、凸部の形状は、ゲート絶縁膜105から不純物半導体膜111に向かって幅が広がる凸状(逆錐形状)であってもよい。

【0129】

微結晶半導体領域118cが凹凸状であるため、薄膜トランジスタのオン電流を高めることができる。

【0130】

また、微結晶半導体膜118a及び半導体膜118bに含まれる酸素の二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)によって計測される濃度を、1×1018atoms/cm3未満とすることで、微結晶半導体膜118a及び微結晶半導体領域118cの結晶性を高めることができるため好ましい。また、二次イオン質量分析法によって計測される半導体膜118の窒素濃度プロファイルのピーク濃度は、1×1020atoms/cm3以上1×1021atoms/cm3以下、好ましくは2×1020atoms/cm3以上1×1021atoms/cm3以下である。

【0131】

非晶質半導体領域118dは、窒素を有する非晶質半導体で形成される。窒素を有する非晶質半導体に含まれる窒素は、例えばNH基またはNH2基として存在していてもよい。非晶質半導体としては、アモルファスシリコンを用いる。

【0132】

窒素を含む非晶質半導体は、従来の非晶質半導体と比較して、CPM(Constant photocurrent method)やフォトルミネッセンス分光測定で測定されるUrbach端のエネルギーが小さく、欠陥吸収スペクトル量が少ない半導体である。即ち、窒素を含む非晶質半導体は、従来の非晶質半導体と比較して、欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い半導体である。窒素を含む非晶質半導体は、価電子帯のバンド端における準位のテール(裾)の傾きが急峻であるため、バンドギャップが広くなり、トンネル電流が流れにくい。このため、窒素を含む非晶質半導体を微結晶半導体領域118cと、不純物半導体膜111との間に設けることで、薄膜トランジスタのオフ電流を低減することができる。また、窒素を含む非晶質半導体を設けることで、オン電流と電界効果移動度を高めることが可能である。

【0133】

なお、窒素を含む非晶質半導体は、低温フォトルミネッセンス分光によるスペクトルのピークが、1.31eV以上1.39eV以下の範囲にある。なお、微結晶半導体、代表的には微結晶シリコンを低温フォトルミネッセンス分光により測定したスペクトルのピーク領域は、0.98eV以上1.02eV以下であり、窒素を含む非晶質半導体は、微結晶半導体とは異なるものである。

【0134】

また、非晶質半導体領域118dの他に、微結晶半導体領域118cにも、NH基またはNH2基を有してもよい。

【0135】

また、図12(B)に示すように、非晶質半導体領域118dに、粒径が1nm以上10nm以下、好ましくは1nm以上5nm以下の半導体結晶粒118eを含ませることで、更にオン電流と電界効果移動度を高めることが可能である。

【0136】

ゲート絶縁膜105から不純物半導体膜111に向かって、先端が狭まる凸状(錐形状)の微結晶半導体は、微結晶半導体膜118aを結晶核としつつ、結晶成長を抑制する条件で結晶成長させると共に、非晶質半導体を堆積することで、このような構造となる。

【0137】

半導体膜118bの作製方法の代表例としては、プラズマCVD装置の処理室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体とを混合するプラズマCVD法により形成する。窒素を含む気体としては、アンモニア、窒素、フッ化窒素、塩化窒素、クロロアミン、フルオロアミン等がある。グロー放電プラズマの生成は、ゲート絶縁膜105と同様にすることができる。

【0138】

このとき、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比は、実施の形態2に示す微結晶半導体膜107と同様の流量比を用い、さらに原料ガスに窒素を含む気体を用いる条件とすることで、微結晶半導体膜107の堆積条件よりも、結晶成長を抑制することができる。具体的には、半導体膜118bの堆積初期においては、原料ガスに窒素を含む気体が含まれるため、部分的に結晶成長が抑制され、錐形状の微結晶半導体領域が成長すると共に、非晶質半導体領域が形成される。さらに、堆積中期または後期では、錐形状の微結晶半導体領域の結晶成長が停止し、非晶質半導体領域のみが堆積される。この結果、半導体膜118bにおいて、微結晶半導体領域118c、及び欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い半導体で形成される非晶質半導体領域118dを形成することができる。

【0139】

ここでは、半導体膜118bの原料ガスに窒素を含む気体を含ませて、微結晶半導体領域118c及び非晶質半導体領域118dを有する半導体膜118bを形成したが、他の半導体膜118bの形成方法として、微結晶半導体膜118aの表面に窒素を含む気体を曝して、微結晶半導体膜118aの表面に窒素を吸着させた後、シリコンまたはゲルマニウムを含む堆積性気体及び水素を原料ガスとして、微結晶半導体領域118c及び非晶質半導体領域118dを有する半導体膜118bを形成することができる。

【0140】

または、半導体膜118bとして、実施の形態1に示す微結晶半導体領域117aとなる微結晶半導体膜の成膜条件を用いて第1の微結晶半導体膜領域を形成した後、上記実施の形態1に示す微結晶半導体領域117aとなる微結晶半導体膜に示す流量比を満たす原料ガスに、さらに窒素を含む気体を用いる条件で第2の微結晶半導体領域及び非晶質半導体領域を形成してもよい。なお、第1の微結晶半導体領域の成膜条件において、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比を、微結晶半導体膜118aと比較して低くすることで、成膜速度を高めることができる。

【0141】

半導体膜118bに含まれる微結晶半導体領域118cは、錐形状または逆錐形状であるため、オン状態でソース電極及びドレイン電極の間に電圧が印加されたときの縦方向(膜厚方向)における抵抗、即ち、半導体膜118bの抵抗を下げることが可能である。また、微結晶半導体膜118aと不純物半導体膜111との間に、欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い、窒素を含む非晶質半導体を有するため、トンネル電流が流れにくくなる。以上のことから、本実施の形態に示す薄膜トランジスタは、オン電流及び電界効果移動度を高めるとともに、オフ電流を低減することができる。

【0142】

(実施の形態4)

本実施の形態では、実施の形態1に示す微結晶半導体膜107または実施の形態3に示す微結晶半導体膜118aにおいて、結晶性が高く、混相粒が密である微結晶半導体膜の作製方法について、図13を用いて説明する。

【0143】

図13(A)に示すように、基板101上にゲート絶縁膜105を形成し、ゲート絶縁膜105上に種結晶157を形成する。

【0144】

種結晶157としては、微結晶半導体、代表的には、微結晶シリコン、微結晶シリコンゲルマニウム、微結晶ゲルマニウム等を用いて形成する。種結晶157は、複数の混相粒が分散した状態、混相粒が連続した膜の状態、または混相粒及び非晶質半導体領域が連続した膜の状態を含む。このため、種結晶157は、混相粒157aが隣接せず、混相粒157aの間に隙間157bを有するものも含む。さらに、混相粒の粒密度(面内における混相粒の存在割合)が低く、且つ混相粒の結晶性が高いことを特徴とする。

【0145】

種結晶157は、プラズマCVD装置の処理室内において、混相粒の粒密度が低く、且つ混相粒の結晶性が高くなるような第1の条件を用いて、原料ガスであるシリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合するプラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合するプラズマCVD法により形成する。ここでは、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上50000Pa以下(0.5Torr以上370Torr以下)、更に好ましくは67Pa以上13332Pa以下(0.5Torr以上100Torr以下)とする第1の条件により、種結晶157を形成する。第1の条件に示すような、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を高くする条件を用いて形成することで、結晶成長が促進され、種結晶157に含まれる混相粒157aの結晶性が高まる。即ち、種結晶157に含まれる混相粒157aに含まれる結晶子の大きさが増大する。また、隣り合う混相粒157aの間に隙間157bができ、混相粒157aの粒密度が低下する。

【0146】

種結晶157を形成する際のグロー放電のプラズマの生成は、ゲート絶縁膜105に列挙した高周波電力を適宜印加することで行われる。また、種結晶157の堆積温度は、微結晶半導体膜107に列挙した堆積温度を適宜用いる。

【0147】

次に、図13(B)に示すように、種結晶157上に第1の微結晶半導体膜159を形成する。第1の微結晶半導体膜159は、種結晶157の隙間を埋めつつ、結晶成長を促す条件で形成することを特徴とする。

【0148】

第1の微結晶半導体膜159は、プラズマCVD装置の処理室内において、第2の条件により、原料ガスであるシリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合するプラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合し、グロー放電プラズマにより形成する。ここでは、第2の条件を、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を100倍以上6000倍以下、好ましくは100倍以上3000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を1333Pa以上50000Pa以下(10Torr以上370Torr以下)、更に好ましくは1333Pa以上13332Pa以下(10Torr以上100Torr以下)とする。

【0149】

なお、処理室内の圧力が1333Pa以上50000Pa以下(10Torr以上370Torr以下)、更に好ましくは1333Pa以上13332Pa以下(10Torr以上100Torr以下)であれば、第1の条件の圧力より第2の条件の圧力が高くともよい。または、第2の条件より第1の条件の圧力が高くともよい。または、第1の条件及び第2の条件の圧力は同じであってもよい。

【0150】

上記第2の条件により、第1の微結晶半導体膜159として微結晶シリコン膜、微結晶シリコンゲルマニウム膜、微結晶ゲルマニウム膜等を形成する。

【0151】

第1の微結晶半導体膜159を形成する際のグロー放電のプラズマの生成は、ゲート絶縁膜105に列挙した高周波電力を適宜印加することで行われる。なお、種結晶157及び第1の微結晶半導体膜159のグロー放電のプラズマ生成は、同じ条件で行うことでスループットを向上させることができるが、異なっていてもよい。また、種結晶157の堆積温度は、微結晶半導体膜107に列挙した堆積温度を適宜用いる。

【0152】

第1の微結晶半導体膜159は、種結晶157の混相粒157aの隙間157bを埋めつつ、結晶成長を促す第2の条件で形成される。第2の条件を上記条件とすると、処理室内の圧力が高いため、平均自由行程が短く、イオンのエネルギーが低くなり、被覆率が向上すると共に、イオンダメージが低減し、欠陥低減に寄与する。また、シリコンまたはゲルマニウムを含む堆積性気体の希釈比が高く、水素ラジカルの生成量が増加するため、非晶質半導体領域をエッチングしつつ、混相粒157aに含まれる結晶子を核として結晶成長する。この結果、第1の微結晶半導体膜159は、非晶質半導体領域に対する結晶領域の割合が増加し、結晶性が高まる。また、堆積中の第1の微結晶半導体膜159の欠陥低減に寄与する。

【0153】

第1の微結晶半導体膜159は、種結晶157の混相粒157aに含まれる結晶子を核として結晶成長する。また、第1の微結晶半導体膜159の混相粒の大きさは、種結晶157の混相粒157aの間隔に依存する。このため、種結晶157の混相粒157aの粒密度が低いと、混相粒157aの間隔が広がるため、第1の微結晶半導体膜159の混相粒の結晶成長距離が伸び、第1の微結晶半導体膜159の混相粒の大粒径化が可能である。

【0154】

次に、図13(C)に示すように、第1の微結晶半導体膜159上に第2の微結晶半導体膜161を形成する。第2の微結晶半導体膜161は、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ第1の微結晶半導体膜159より結晶性の高い微結晶半導体膜を成膜する条件で形成することを特徴とする。

【0155】

第2の微結晶半導体膜161は、プラズマCVD装置の処理室内において、第3の条件により、原料ガスとしてシリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合するプラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合するプラズマCVD法により形成する。ここでは、第3の条件は、処理室内の圧力を1333Pa以上50000Pa以下、更に好ましくは1333Pa以上13332Pa以下とし、且つ微結晶半導体を堆積する第1の周期と、当該微結晶半導体に含まれる非晶質半導体領域を選択的にエッチングする上記第1の周期より長い第2の周期とを交互に行う条件である。

【0156】

微結晶半導体を堆積する第1の周期と、当該微結晶半導体に含まれる非晶質半導体領域を選択的にエッチングする上記第1の周期より長い第2の周期とを交互に行うためには、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比を交互に増減すればよく、具体的にはシリコンまたはゲルマニウムを含む堆積性気体または水素の流量を増減すればよい。シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比が低い場合、代表的には堆積性気体の流量に対する水素の流量を100倍以上2000倍以下にすることで、微結晶半導体の堆積及び結晶成長が優先的に生じる。一方、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比が高い場合、代表的にはシランまたはゲルマニウムを含む堆積性気体を0sccm以上0.3sccm以下とし、水素流量を1000sccmより高くすることで、微結晶半導体に含まれる非晶質半導体領域のエッチングが優先的に生じる。このとき、水素の流量を一定とし、シリコンまたはゲルマニウムを含む堆積性気体の流量を増減させる場合は、第1の周期と同様の流量の水素を処理室に導入することで、第1の周期及び第2の周期において処理室内の圧力を一定に保つことが可能であるため、第2の微結晶半導体膜の膜質の均一性を高めることができる。なお、処理室の圧力を1333Pa以上50000Pa以下、更に好ましくは1333Pa以上13332Pa以下とすることで、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比が高い場合は、微結晶半導体に含まれる結晶子よりも非晶質半導体領域が優先的にエッチングされる。

【0157】

上記第1の周期及び第2の周期を繰り返すことで、第2の周期では非晶質半導体領域の優先的なエッチングによる結晶子の露出と、第1の周期で露出された結晶子を核とする結晶成長とが交互に起きるため、混相粒の結晶子の大きさが大きくなり、さらには配向面を有する結晶成長が生じる。また、第1の周期よりも第2の周期の方を長くすると、微結晶半導体に含まれる非晶質半導体領域のエッチングが十分に行われるため、第2の微結晶半導体膜に含まれる非晶質半導体量を低減することが可能である。これらの結果、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ第1の微結晶半導体膜より結晶性の高い第2の微結晶半導体膜を形成することができる。また、第2の微結晶半導体膜161の欠陥を低減することができる。

【0158】

また、第2の周期において、わずかな流量、代表的には0sccmより高く0.3sccm以下の流量のシリコンまたはゲルマニウムを含む堆積性気体を流すことで、当該堆積性気体から生成されるわずかなラジカル(代表的には、シリルラジカル)が、非晶質半導体領域のエッチングにより露出された結晶子のダングリングボンドに結合するため、結晶性の高い結晶成長が生じる。即ち、エッチングと共に、結晶成長が生じるため、第2の微結晶半導体膜161の結晶性がより高くなる。

【0159】

上記第3の条件により、第2の微結晶半導体膜161として微結晶シリコン膜、微結晶シリコンゲルマニウム膜、微結晶ゲルマニウム膜等を形成する。

【0160】

第2の微結晶半導体膜161を形成する際の、グロー放電のプラズマの生成は、ゲート絶縁膜105に列挙した高周波電力を適宜印加することで行われる。なお、種結晶157、第1の微結晶半導体膜159、及び第2の微結晶半導体膜161のグロー放電プラズマの生成を同じ条件で行うことで、スループットを向上させることができるが、異なっていてもよい。また、第2の微結晶半導体膜161の堆積温度は、微結晶半導体膜107に列挙した堆積温度を適宜用いる。

【0161】

次に、図13(D)に示すように、第2の微結晶半導体膜161上に第3の微結晶半導体膜163を形成する。第3の微結晶半導体膜163は、第2の微結晶半導体膜161の混相粒の隙間を埋めつつ、結晶成長を促す条件で形成することを特徴とする。

【0162】

第3の微結晶半導体膜163は、プラズマCVD装置の処理室内において、第4の条件により、原料ガスとしてシリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合するプラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合するプラズマCVD法により形成する。なお、第4の条件は、第2の条件と同様である。

【0163】

上記第4の条件により、第3の微結晶半導体膜163として微結晶シリコン膜、微結晶シリコンゲルマニウム膜、微結晶ゲルマニウム膜等を形成する。

【0164】

第4の条件を上記第2条件と同様とすると、処理室内の圧力が高いため、平均自由行程が短く、イオンのエネルギーが低くなり、被覆率が向上する。また、シリコンまたはゲルマニウムを含む堆積性気体の希釈比が高く、水素ラジカルの生成量が増加するため、非晶質半導体領域をエッチングしつつ、第2の微結晶半導体膜161に含まれる結晶子を核として結晶成長する。この結果、第3の微結晶半導体膜163は、非晶質半導体領域に対する結晶領域の割合が増加し、結晶性が高まる。また、第2の微結晶半導体膜161及び堆積中の第3の微結晶半導体膜163の平坦化に寄与する。

【0165】

以上の工程により、微結晶半導体膜164を形成することができる。

【0166】

ここで、図13(E)〜図13(H)に、本実施の形態に示す微結晶半導体膜164の成膜概念図を示す。図13(E)〜図13(H)は、それぞれ図13(A)〜図13(D)における堆積状態をイメージした拡大図である。

【0167】

図13(E)に示すように、種結晶157の堆積工程は、微結晶半導体膜に含まれる混相粒の大きさを大きくするために、種結晶粒子を散在させる工程である。このため、図13(E)に示すように、種結晶157は、種結晶粒子となる混相粒157aが隙間157bをおいて堆積される。

【0168】

図13(F)に示すように、第1の微結晶半導体膜159の堆積工程は、種結晶を元に結晶成長させ、隙間の極めて少ない混相粒を有する膜を形成する工程である。このため、混相粒157aを種結晶として結晶成長しながら微結晶半導体158が堆積される。なお、第2の条件を用いることで、微結晶半導体158は、膜厚方向だけでなく、平面方向にも結晶成長するため、微結晶半導体158同士の隙間が埋まり、微結晶半導体158が接する。

【0169】

図13(G)に示すように、第2の微結晶半導体膜161の堆積工程は、微結晶半導体158上に更に結晶性の高い微結晶半導体160を堆積させる工程である。第2の微結晶半導体膜161の堆積工程においては、微結晶半導体の堆積及び結晶成長の工程と、微結晶半導体に含まれる非晶質半導体領域を優先的にエッチングし、微結晶半導体に含まれる結晶子を露出させる工程が交互に行われる。また、処理室の圧力が1333Pa以上50000Pa以下(10Torr以上370Torr以下)、更に好ましくは1333Pa以上13332Pa以下(10Torr以上100Torr以下)であるため、微結晶半導体に含まれる非晶質半導体領域が優先的にエッチングされる。これらのため、露出された結晶子に微結晶半導体が堆積する際、エピタキシャル成長が生じやすい。この結果、第2の微結晶半導体膜161の堆積工程においては、微結晶半導体の配向性が高くなり、配向面を有する微結晶半導体160が堆積される。

【0170】

図13(H)に示すように、第3の微結晶半導体膜163の堆積工程は、第2の微結晶半導体膜161を元に結晶成長させ、第2の微結晶半導体膜161の混相粒の隙間を埋めつつ、第2の微結晶半導体膜161の凹凸を低減し、平坦化する工程である。このため、微結晶半導体160を種結晶として結晶成長しながら微結晶半導体162が堆積される。

【0171】

なお、第1の条件の圧力が第2の条件の圧力より低いと、基板面内における種結晶157の分布の均一性が高まるため好ましい。また、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比において、第1の条件が第2の条件より低いと、第2の条件によって混相粒が密となるように、種結晶157の堆積割合が高まるため好ましい。また、第1の微結晶半導体膜159の結晶性及び膜密度が高まるため好ましい。

【0172】

図13(E)乃至図13(H)の工程を経ることで、結晶性が高く、混相粒の隙間が極めて少なく、且つ配向面を有する混相粒を有する微結晶半導体膜164を形成することができる。なお、微結晶半導体膜164に含まれる混相粒は、種結晶157、第1の微結晶半導体膜159、第2の微結晶半導体膜161、及び第3の微結晶半導体膜163のそれぞれで堆積した微結晶半導体の場合もある。または、種結晶157、第1の微結晶半導体膜159、第2の微結晶半導体膜161、及び第3の微結晶半導体膜163の二以上が結晶成長しながら堆積した微結晶半導体の場合もある。

【0173】

本実施の形態では、図13(A)〜図13(D)の4工程を用いて微結晶半導体膜を形成する工程を説明したが、この代わりに、図13(A)及び図13(B)の工程を用いてもよい。または、図13(A)乃至図13(C)の工程を用いてもよい。

【0174】

(実施の形態5)

薄膜トランジスタを作製し、該薄膜トランジスタを画素部、さらには駆動回路に用いて表示機能を有する半導体装置(表示装置ともいう)を作製することができる。また、薄膜トランジスタを用いた駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

【0175】

表示装置は表示素子を含む。表示素子としては液晶素子(液晶表示素子ともいう)、発光素子(発光表示素子ともいう)を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL(Electro Luminescence)、有機EL等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

【0176】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに、該表示装置を作製する過程における、表示素子が完成する前の一形態に相当する素子基板に関し、該素子基板は、電流を表示素子に供給するための手段を複数の各画素に備える。素子基板は、具体的には、表示素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を形成した後であって、エッチングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

【0177】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源(照明装置含む)を指す。また、コネクタ、例えばFPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass)方式によりIC(集積回路)が直接実装されたモジュールも全て表示装置に含むものとする。

【0178】

(実施の形態6)

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機、電子ペーパーとして適用することができる。電子ペーパーは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍(電子ブック)、ポスター、デジタルサイネージ、PID(Public Information Display)、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図14に示す。

【0179】

図14は、電子書籍の一例を示している。例えば、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

【0180】

筐体2701には表示部2705及び光電変換装置2706が組み込まれ、筐体2703には表示部2707及び光電変換装置2708が組み込まれている。表示部2705および表示部2707は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とすることで、例えば右側の表示部(図14では表示部2705)に文章を表示し、左側の表示部(図14では表示部2707)に画像を表示することができる。

【0181】

また、図14では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

【0182】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【技術分野】

【0001】

本発明は、半導体装置及びその作製方法、並びに表示装置に関する。

【背景技術】

【0002】

電界効果トランジスタの一種として、絶縁表面を有する基板上に形成された半導体膜を用いてチャネル領域が形成される薄膜トランジスタが知られている。薄膜トランジスタのチャネル領域に用いられる半導体膜に、非晶質シリコン、微結晶シリコン、または多結晶シリコンを用いる技術がある。薄膜トランジスタの代表的な応用例は、液晶テレビジョン装置であり、表示画面を構成する各画素のスイッチングトランジスタとして実用化されている。

【0003】

また、大型のテレビジョン装置を量産高く作製するため、画素のスイッチングトランジスタとして逆スタガ型の薄膜トランジスタを用いた技術が開示されている(特許文献1参照。)。また、高精細な(画素数の多い)液晶表示装置(例えば、フルハイビジョン(FHD)、2k×4k、4k×8k等)を作製するためには、オン電流の高い薄膜トランジスタが必要である。そこで、画素のスイッチングトランジスタとして、非晶質半導体膜をチャネル領域に有する薄膜トランジスタよりオン電流の高い、微結晶半導体膜をチャネル領域に有する薄膜トランジスタが注目されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−21571号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、微結晶シリコン膜を用いてチャネル領域が形成される薄膜トランジスタは、非晶質シリコン膜でチャネル領域が形成される薄膜トランジスタと比較して、オン電流及び電界効果移動度は向上するものオフ電流が高くなってしまい、十分なスイッチング特性が得られないといった問題がある。

【0006】

また、微結晶シリコン膜に光が照射されると、光リーク電流が発生する。このため、逆スタガ型の薄膜トランジスタにおいては、バックライトが微結晶シリコン膜に照射されないように、ゲート電極に遮光機能を設け、上面形状において、ゲート電極から微結晶シリコン膜がはみ出ず、重畳する位置関係とすることが好ましい。

【0007】

しかしながら、p型の薄膜トランジスタがオフ状態の際に、微結晶シリコン膜とソース電極またはドレイン電極とが接する領域であって、ゲート電極と重畳する領域においては、ドレイン電極から微結晶シリコン膜に電子が注入され、オフ電流が上昇するという問題がある。

【0008】

そこで、本発明の一態様は、オフ電流を低減した優れた特性を有する薄膜トランジスタを作製することを課題とする。

【課題を解決するための手段】

【0009】

本発明の一態様は、p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上であることを特徴とする。

【0010】

本発明の一態様は、p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数φMが4.30eV以上、好ましくは4.30eV以上5.05eV以下、更に好ましくは4.40eV以上4.90eV以下であることを特徴とする。

【0011】

なお、p型のスタガ型の薄膜トランジスタにおいて、上記半導体膜は、ゲート絶縁膜に接する微結晶半導体領域と、当該微結晶半導体領域に接する一対の非晶質半導体領域と、当該非晶質半導体領域に接する一対の不純物半導体領域とが順に積層される。

【0012】

また、一対の配線は、タンタル、モリブデン、銅、タングステン、ニッケル、クロム、酸化タングステン、酸化モリブデン、窒化タンタル、窒化チタン、窒化タングステン、窒化モリブデン、アルミニウム−亜鉛酸化物(AZOと示す。)、インジウムースズ酸化物(ITOと示す。)、酸化シリコンを含むインジウム−スズ酸化物等のいずれか一以上を有する。また、一対の配線が積層構造の場合、半導体膜に接する側が、上記材料の一で形成されていればよい。

【発明の効果】

【0013】

本発明の一態様を適用することで、オフ電流が低く優れた電気特性を有する半導体装置を作製することができる。また、電気特性が優れた半導体装置を、生産性高く作製することができる。

【図面の簡単な説明】

【0014】

【図1】本発明の一実施の形態に係る半導体装置を説明する断面図及びバンド図である。

【図2】薄膜トランジスタの電流電圧特性を説明する図である。

【図3】半導体膜の電子密度分布を説明する図である。

【図4】薄膜トランジスタの配線及び微結晶半導体のショットキーバリアとオフ電流の関係を説明する図である。

【図5】本発明の一実施の形態に係る半導体装置を説明する断面図である。

【図6】薄膜トランジスタの電流電圧特性を説明する図である。

【図7】半導体膜の電子密度分布を説明する図である。

【図8】薄膜トランジスタの配線及び微結晶半導体のショットキーバリアとオフ電流の関係を説明する図である。

【図9】本発明の一実施の形態に係る半導体装置の作製方法を説明する断面図である。

【図10】本発明の一実施の形態に係る半導体装置の作製方法を説明する断面図である。

【図11】本発明の一実施の形態に係る半導体装置の作製方法を説明する上面図である。

【図12】本発明の一実施の形態に係る半導体装置の作製方法を説明する断面図である。

【図13】本発明の一実施の形態に係る半導体装置の作製方法を説明する断面図である。

【図14】電子書籍の一例を示す斜視図である。

【発明を実施するための形態】

【0015】

本発明の実施の形態について、図面を参照して以下に説明する。ただし、本発明は以下の説明に限定されるものではない。本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解されるからである。したがって、本発明は以下に示す実施の形態の記載内容のみに限定して解釈されるものではない。なお、図面を用いて本発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。

【0016】

(実施の形態1)

本実施の形態では、p型の薄膜トランジスタにおいて、オフ電流が低く、電気特性に優れた薄膜トランジスタについて説明する。

【0017】

図1(A)は、本実施の形態に示す薄膜トランジスタの断面図を示す。

【0018】

図1(A)に示す薄膜トランジスタは、基板101上に、ゲート電極103(第1のゲート電極ともいう。)と、半導体膜136と、ゲート電極103及び半導体膜136の間に設けられるゲート絶縁膜105(第1のゲート絶縁膜ともいう。)と、半導体膜136に接する一対の配線129a、129bとを有する。半導体膜136は、微結晶半導体領域135、一対の非晶質半導体領域134a、134b、及び一対の不純物半導体領域133a、133bが、ゲート絶縁膜105側から順に積層される。また、不純物半導体領域133a、133bは、p型を呈する。

【0019】

また、ゲート絶縁膜105、半導体膜136、配線129a、129bを覆う絶縁膜137(第2のゲート絶縁膜ともいう。)を有してもよい。また、絶縁膜137上にバックゲート電極139(第2のゲート電極ともいう。)及び画素電極141を有してもよい。

【0020】

本実施の形態に示す薄膜トランジスタは、半導体膜136の全てがゲート電極103と重畳している。即ち、平面形状において、半導体膜136の端部がゲート電極103の端部より内側に位置する。このため、基板101側からバックライトが薄膜トランジスタに照射されても、ゲート電極103が当該光を遮光するため、半導体膜136に光が入射されず、薄膜トランジスタの光リーク電流を低減することができる。

【0021】

しかしながら、当該構造の薄膜トランジスタにおいては、オフ状態において、半導体膜136及び一対の配線129a、129bが接する領域での電子の注入により、リーク電流(オフ電流)が上昇してしまう。ここで、p型の薄膜トランジスタにおいて、オフ電流の流れる原理について、図1(B)を用いて説明する。

【0022】

図1(B)は、図1(A)に示す薄膜トランジスタの一部を拡大した図である。なお、図1(B)においては、ハッチングパターンを省略している。以下、配線129aをソース、配線129bをドレインとして説明する。

【0023】

図1(B)において、微結晶半導体領域135及び配線129bが接する領域131が存在する。薄膜トランジスタはp型であるため、薄膜トランジスタがオフ状態となる電圧(しきい値電圧より高い電圧)がゲート電極103に印加されると、領域131において、ドレインである配線129bから微結晶半導体領域135に電子が注入される。この結果、配線129bから微結晶半導体領域135を介して配線129aに流れる電流I_1と、配線129bから微結晶半導体領域135、非晶質半導体領域134a、及び不純物半導体領域133aを介して配線129aに流れる電流I_2とが発生する。なお、電流I_2は、配線129bから微結晶半導体領域135に注入された電子と、不純物半導体領域133aから非晶質半導体領域134a及び微結晶半導体領域135に注入された正孔が再結合して流れる電流である。

【0024】

ここで、微結晶半導体領域135の代表例である微結晶シリコン135aと、配線129bとが接する領域のエネルギーバンド図を図1(C)に示す。

【0025】

図1(C)は、平衡状態の微結晶シリコン135a及び配線129bのエネルギーバンド図である。微結晶シリコン135aにおいて、χは微結晶シリコンの電子親和力(真空準位と、微結晶シリコン135aの伝導帯下端Ecとの間のポテンシャル差)を示し、Egは、微結晶シリコン135aの禁制帯幅(伝導帯下端Ecと、価電子帯上端Evとの間のポテンシャル差)を示す。なお、薄膜トランジスタはp型であるため、微結晶シリコン135aのフェルミ準位Efは、真性フェルミ準位Eiと価電子帯Evの上端との間に位置する。なお、微結晶シリコン135aのフェルミ準位はアクセプター濃度が高い程、即ち、よりp型である程、価電子帯Evの上端に近づく。また、配線129bにおいて、φMは配線129bの材料の仕事関数を示す。

【0026】

図1(D)に示すように、微結晶シリコン135a及び配線129bを接合すると(但し、ゲート電圧Vg、及びソースドレイン電圧Vdsは0V)、微結晶シリコン135a及び配線129bが接する領域において、微結晶シリコン135aのフェルミ準位Efと、配線129bのフェルミ準位Efmが一致する。φBnは、微結晶シリコン135a及び配線129bが接する領域での障壁(ショットキーバリア)を示す。ショットキーバリアは数式1で表される。

【0027】

【数1】

【0028】

ショットキーバリアφBnが大きければ大きい程、配線129bから微結晶シリコン135aに電子が注入されにくく、オフ電流が流れにくい。このため、ショットキーバリアφBnを0.65eV以上とすることで、p型の薄膜トランジスタのオフ電流を低減することができる。

【0029】

微結晶半導体領域の電子親和力χは3.55eV以上3.75eV以下である。微結晶半導体領域の電子親和力χが3.65eVのとき、配線129bの材料の仕事関数φMを、4.3eV以上とすることで、ショットキーバリアφbnが大きくなり、0.65V以上となるため、p型の薄膜トランジスタのオフ電流を低減することができる。

【0030】

p型の薄膜トランジスタにおいて、オフ電流を低減することが可能な配線129a、129bの材料としては、タンタル、モリブデン、銅、タングステン、ニッケル、クロム、酸化タングステン、酸化モリブデン、窒化タンタル、窒化チタン、窒化タングステン、窒化モリブデン、アルミニウム−亜鉛酸化物(AZOと示す。)、インジウムースズ酸化物(ITOと示す。)、酸化シリコンを含むインジウム−スズ酸化物等がある。これらの仕事関数φMを表1に示す。なお、配線129a、129bは、これらの材料に限定されず、仕事関数φMが4.30eV以上である材料を適宜用いることができる。

【0031】

【表1】

【0032】

表1に示す材料の仕事関数φMは、UPS法(紫外線光電子分光法)、光電子分光法(PES)、電場電子放出法等で得られる。なお、配線129a、129bは、積層構造とすることが可能であり、この場合は、表1に示す材料で形成される膜を半導体膜136側に設ければよく、表1の他の材料との積層構造することができる。

【0033】

ここで、p型の薄膜トランジスタの特性と、配線の材料の仕事関数φMの関係について、計算機を用いて検証した結果について説明する。具体的には、配線の材料の仕事関数φMと薄膜トランジスタの電流電圧特性について比較した。なお、計算には、デバイスシミュレーションソフトAtlas(Silvaco Data Systems社製)を用いた。

【0034】

計算に用いた薄膜トランジスタの構造を図1(A)に示す。

【0035】

計算に用いた薄膜トランジスタの詳細について説明する。

【0036】

ゲート電極103としては、仕事関数φMが4.1eVの導電膜を用いた。

【0037】

ゲート絶縁膜105としては、厚さ300nm、比誘電率6.85のSiNxを用いた。

【0038】

微結晶半導体領域135としては、微結晶シリコンを想定して各物性パラメータを以下に示す値を用いた。禁制帯幅Egを1.1eV、電子親和力χを3.65eV、電子の移動度μnを0.1cm2/Vs、正孔の移動度μpを0.7cm2/Vs、アクセプター濃度Naを1×1015cm−3とした。なお、アクセプター濃度Naは濃度が低いため、実際のプロセス工程ではアクセプターを添加しなくともよい。また、微結晶半導体領域135の側面とゲート絶縁膜105の間でなす角度を45度とした。また、微結晶半導体領域135において、非晶質半導体領域134a、134bと重畳する領域の厚さを70nm、非晶質半導体領域134a、134bと重畳しない領域の厚さを50nmとした。

【0039】

非晶質半導体領域134a、134bとしては、アモルファスシリコンを想定して各物性パラメータを以下に示す値を用いた。禁制帯幅Egを1.7eV、電子親和力χを3.4eV、電子の移動度μnを1cm2/Vs、正孔の移動度μpを0.1cm2/Vsとし、厚さを80nmとした。

【0040】

不純物半導体領域133a、133bとしては、アクセプター濃度Naを6×1016cm−3、厚さを50nmとし、ボロンを含むアモルファスシリコンを想定した。

【0041】

配線129a、129bとしては、仕事関数φMが3.8〜4.5eVの材料を用いた。

【0042】

チャネル長方向の微結晶半導体領域135の長さを19.5μmとし、チャネル長を3.3μm、チャネル幅を20μmとした。

【0043】

また、ゲート絶縁膜105及び微結晶半導体領域135の界面に、欠陥準位を仮定した。また、Band to Band Tunneling Model(BBT Model)を仮定した。BBT Modelにおいて、数式2に示すトンネル電流の発生率GBBTを用いた。

【0044】

【数2】

【0045】

なお、数式2において、Eは電界強度である。微結晶シリコンに対しては、A=2×1013、B=2×106、γ=1.5を用いた。また、アモルファスシリコンに対しては、A=1×1010、B=3×106、γ=1.5を用いた。

【0046】

また、計算の都合上、配線129b及び半導体膜136をショットキー接合と仮定した。また、配線129a及び半導体膜136をオーミック接合と仮定した。

【0047】

このときの薄膜トランジスタの電流電圧特性を図2に示す。太曲線は配線129bの仕事関数φMが4.3eV〜4.6eVの電流電圧特性であり、細曲線は配線129bの仕事関数φMが3.9eV〜4.2eVの電流電圧特性である。配線129bの仕事関数φMが4.3eV以上では、ゲート電圧Vgが10Vのとき、オフ電流が1×10−12Aより低い。一方、配線129bの仕事関数φMが4.3eVより低くなると、ゲート電圧Vgが10Vのときのオフ電流が1×10−12A以上であるため、オフ状態において、リーク電流が上昇している。

【0048】

また、半導体膜の電子密度分布を図3に示す。なお、ゲート電圧Vgを10V、ソースドレイン電圧(Vds)を−3Vとした。

【0049】

図3(A)は、配線129bの仕事関数φMを4.0eV、図3(B)は、配線129bの仕事関数φMを4.3eVとしたときの、半導体膜における電子密度分布である。なお、等高線上またはその近傍に電子密度の値を示す。

【0050】

図3から、配線129bの仕事関数φMが4.0eVのときと比較して、4.3eVでは、微結晶半導体領域及び配線が接する領域131での電子密度が低い。

【0051】

次に、室温(27℃)の時の、配線129b及び微結晶シリコン135aのショットキーバリアとオフ電流について、図4に示す。

【0052】

図4において、横軸はショットキーバリアφBnであり、縦軸はゲート電圧Vgが(Vth+10)Vのときのオフ電流である。また、微結晶シリコンの電子親和力χが3.55eV、3.65eV、3.75eVにおける、ショットキーバリア及びオフ電流の関係を示す。

【0053】

図4から、ショットキーバリアφBnが0.65eV以上において、オフ電流が1×10−12Aより低いことがわかる。

【0054】

以上のことから、p型の薄膜トランジスタにおいて、微結晶半導体領域の電子親和力χが3.65eVのとき、仕事関数φMを4.30eV以上、好ましくは4.40eV以上とすることで、配線から微結晶半導体領域への電子注入を低減し、薄膜トランジスタのオフ電流を低減することができる。また、ショットキーバリアφBnを0.65eV以上とすることで、p型の薄膜トランジスタのオフ電流を低減することができる。

【0055】

次に、オフ電流を低減できるより好ましい配線の仕事関数φMの範囲について説明する。

【0056】

配線の仕事関数φMが高くなると、ゲート電極103にオフ状態となる電圧(しきい値電圧より高い電圧)が印加された状態において、半導体膜の価電子帯及び伝導帯がより急峻な曲線となる。そのため、微結晶半導体領域から不純物半導体領域における電界が強くなる。この結果、図5に示すように、図1(B)と同様に電流I_1及びI_2が流れると共に、不純物半導体領域133bの正孔と、非晶質半導体領域134a、134bの間でトンネル電流I_3が発生し、非晶質半導体領域134bの電子密度が増加する。このため、オフ電流がさらに上昇する。

【0057】

微結晶半導体領域の電子親和力χが3.65eVのとき、配線129bの仕事関数φMを、5.05eV以下、更に好ましくは4.9eVとすることで、p型の薄膜トランジスタのオフ電流の増加を防ぐことができる。即ち、配線129bの仕事関数φMを、4.30eV以上5.05eV以下、更に好ましくは4.40eV以上4.90eVとすることで、p型の薄膜トランジスタのオフ電流を低減することができる。

【0058】

ここで、上記計算機を用いた検証と同様に、デバイスシミュレーションソフトAtlas(Silvaco Data Systems社製)を用いて、p型の薄膜トランジスタの特性と、配線の材料の仕事関数φMの関係について、計算機を用いて検証した結果について説明する。

【0059】

計算に用いた薄膜トランジスタの構造及び条件は、上記検証と同様とし、且つ、配線129bとして、仕事関数φMが4.7〜5.4eVの材料を用いて計算を行った。このときの薄膜トランジスタの電流電圧特性を図6に示す。太曲線は配線129bの仕事関数φMが4.7eV〜5.0eVの電流電圧特性であり、細曲線は配線129bの仕事関数φMが5.1eV〜5.4eVの電流電圧特性である。

【0060】

配線129bの仕事関数φMが5.0eV以下では、Vgが10Vのとき、オフ電流が1×10−12Aより低い。一方、配線129bの仕事関数φMが5.0eVより高くなると、Vgが10Vのときオフ電流が1×10−12A以上であるため、オフ状態において、リーク電流が上昇している。

【0061】

また、半導体膜の電子密度分布を図7に示す。なお、ゲート電圧Vgを10V、ソースドレイン電圧(Vds)を−3Vとした。

【0062】

図7(A)は、配線129bの仕事関数φMを5.0eV、図7(B)は、配線129bを仕事関数φMが5.3eVとしたときの、半導体膜における電子密度分布である。なお、等高線上またはその近傍に電子密度の値を示す。

【0063】

図7から、配線129bの仕事関数φMが5.0eVでは、非晶質半導体領域134bにおける電子密度は低い。一方、配線129bの仕事関数φMが5.3eVでは、非晶質半導体領域134bにおける電子密度が高い。これは、非晶質半導体領域134bでトンネル電流が発生したためである。

【0064】

また、室温(27℃)の時の、配線129bの仕事関数φMとオフ電流について、図8に示す。

【0065】

図8において、横軸は仕事関数、縦軸はゲート電圧Vgが(Vth+10)Vのときのオフ電流である。また、微結晶シリコンの電子親和力χが3.65eVにおける、仕事関数及びオフ電流の関係を示す。

【0066】

図8から、仕事関数φMが5.05eV以下において、オフ電流が1×10−12Aより低いことがわかる。

【0067】

以上のことから、配線129bの仕事関数φMを5.05eV以下とすることで、p型の薄膜トランジスタのオフ電流の増加を防ぐことができる。

【0068】

p型の薄膜トランジスタにおいて、微結晶半導体領域の電子親和力χが3.65eVのとき、仕事関数φMを4.30eV以上、好ましくは4.30eV以上5.05eV以下、更に好ましくは4.40eV以上4.90eV以下とすることで、配線から微結晶半導体領域への電子注入を低減し、薄膜トランジスタのオフ電流を低減することができる。また、ショットキーバリアφBnを0.65eV以上とすることで、p型の薄膜トランジスタのオフ電流を低減することができる。

【0069】

ここで、図1(A)に示す薄膜トランジスタの各構成について、以下に説明する。

【0070】

基板101としては、ガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板等を用いることができる。また、基板に透光性を要しない場合には、ステンレス等の金属基板を用いてもよい。ガラス基板としては、例えば、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス若しくはアルミノケイ酸ガラス等の無アルカリガラス基板を用いるとよい。なお、基板101のサイズに限定はなく、例えばフラットパネルディスプレイの分野でよく使われる第3世代〜第10世代のガラス基板を用いることができる。

【0071】

ゲート電極103は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム、ニッケル等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体、Ag−Pd−Cu合金、Al−Nd合金、Al−Ni合金などを用いてもよい。

【0072】

例えば、ゲート電極103の二層の積層構造としては、アルミニウム膜上にモリブデン膜を積層した二層の積層構造、または銅膜上にモリブデン膜を積層した二層構造、または銅膜上に窒化チタン膜若しくは窒化タンタル膜を積層した二層構造、窒化チタン膜とモリブデン膜とを積層した二層構造、酸素を含む銅−マグネシウム合金膜と銅膜とを積層した二層構造、酸素を含む銅−マンガン合金膜と銅膜とを積層した二層構造、銅−マンガン合金膜と銅膜とを積層した二層構造などとすることが好ましい。三層の積層構造としては、タングステン膜または窒化タングステン膜と、アルミニウムとシリコンの合金膜またはアルミニウムとチタンの合金膜と、窒化チタン膜またはチタン膜とを積層した三層構造とすることが好ましい。電気的抵抗が低い膜上にバリア膜として機能する金属膜が積層されることで、電気的抵抗を低くでき、且つ金属膜から半導体膜への金属元素の拡散を防止することができる。

【0073】

ゲート絶縁膜105は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、または窒化酸化アルミニウム膜を、単層でまたは積層して形成することができる。

【0074】

なお、ここでは、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS:Hydrogen Forward Scattering Spectrometry)を用いて測定した場合に、組成範囲として酸素が50〜70原子%、窒素が0.5〜15原子%、シリコンが25〜35原子%、水素が0.1〜10原子%の範囲で含まれるものをいう。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS及びHFSを用いて測定した場合に、組成範囲として酸素が5〜30原子%、窒素が20〜55原子%、シリコンが25〜35原子%、水素が10〜30原子%の範囲で含まれるものをいう。ただし、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

【0075】

なお、ゲート絶縁膜105を酸化シリコンまたは酸化窒化シリコン等の酸化絶縁膜により形成することで、薄膜トランジスタの閾値電圧の変動を低減することができる。

【0076】

半導体膜136を構成する微結晶半導体領域135は、微結晶シリコン、微結晶シリコンゲルマニウム、微結晶ゲルマニウム等の電子親和力χが3.55eV以上3.75eV以下である半導体で形成される。微結晶半導体は、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造の半導体で形成される。このため、微結晶半導体は非晶質半導体領域を有する。微結晶半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な半導体であり、混相粒径が2nm以上200nm以下、好ましくは10nm以上80nm以下、より好ましくは、20nm以上50nm以下の柱状または針状の混相粒が基板表面に対して法線方向に成長している。このため、柱状または針状の混相粒の界面には、粒界が形成される場合もある。なお、ここでの結晶粒径は、基板表面に対して平行な面における結晶粒の最大直径をいう。また、混相粒とは、非晶質半導体領域と、単結晶とみなせる微小結晶である結晶子とを含む結晶粒である。

【0077】

微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルのピークが単結晶シリコンを示す520cm−1よりも低波数側に、シフトしている。即ち、単結晶シリコンを示す520cm−1とアモルファスシリコンを示す480cm−1の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手(ダングリングボンド)を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含んでいる。さらに、ヘリウム、アルゴン、ネオン、クリプトン、キセノンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体が得られる。このような微結晶半導体に関する記述は、例えば、米国特許4,409,134号で開示されている。

【0078】

半導体膜136を構成する非晶質半導体領域134a、134bは、アモルファスシリコン、アモルファスシリコン−ゲルマニウム等で形成される。

【0079】

半導体膜136を構成する不純物半導体領域133a、133bは、p型を呈する半導体で形成され、代表的には、ボロンを有するアモルファスシリコン、またはボロンを有する微結晶シリコンで形成される。

【0080】

絶縁膜137は、ゲート絶縁膜105に示す材料を適宜用いて形成することができる。

【0081】

バックゲート電極139及び画素電極141は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、または酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を用いて形成することができる。

【0082】

また、バックゲート電極139及び画素電極141は、透光性を有する導電性高分子(導電性ポリマーともいう。)を含む導電性組成物を用いて形成することができる。バックゲート電極139は、シート抵抗が10000Ω/sq以下であって、且つ波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1Ω・cm以下であることが好ましい。

【0083】

導電性高分子としては、いわゆるπ電子共役系導電性高分子を用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、または、アニリン、ピロール及びチオフェンの2種以上の共重合体若しくはその誘導体等がある。

【0084】

本実施の形態に示すp型の薄膜トランジスタは、微結晶半導体領域及び配線の接する領域における電子の注入を低減することが可能である。この結果、薄膜トランジスタのオフ電流を低減することができる。また、本実施の形態に示す薄膜トランジスタは逆スタガ型であるため、オフ電流が低く電気特性に優れた薄膜トランジスタを量産性高く作製することができる。

【0085】

(実施の形態2)

本実施の形態では、本発明の一形態である半導体装置に形成される薄膜トランジスタの作製方法について、図9乃至図11を参照して説明する。なお、同一の基板上に形成する薄膜トランジスタを全て同じ極性に統一すると、工程数を抑えることができて好ましい。本実施の形態では、p型の薄膜トランジスタの作製方法について説明する。

【0086】

なお、オン電流とは、薄膜トランジスタがオン状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、p型の薄膜トランジスタの場合には、ゲート電圧が薄膜トランジスタの閾値電圧よりも低いときにソース電極とドレイン電極との間に流れる電流である。

【0087】

また、オフ電流とは、薄膜トランジスタがオフ状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、p型の薄膜トランジスタの場合には、ゲート電圧が薄膜トランジスタの閾値電圧よりも高いときにソース電極とドレイン電極との間に流れる電流である。

【0088】

図9(A)に示すように、基板101上にゲート電極103(第1のゲート電極ともいう。)を形成する。次に、ゲート電極103を覆うゲート絶縁膜105を形成し、ゲート絶縁膜105上に、微結晶半導体膜107、非晶質半導体膜109、及び不純物半導体膜111を形成する。

【0089】

ゲート電極103は、基板101上に、CVD法、スパッタリング法または真空蒸着法を用いて、上記した材料を用いて導電膜を形成し、該導電膜上にフォトリソグラフィ法またはインクジェット法等によりマスクを形成し、該マスクを用いて導電膜をエッチングして形成することができる。また、銀、金または銅等の導電性ナノペーストをインクジェット法により基板上に吐出し、焼成することで形成することもできる。なお、ゲート電極103と、基板101との密着性向上を目的として、上記の金属材料の窒化物膜を、基板101と、ゲート電極103との間に設けてもよい。ここでは、基板101上に導電膜を形成し、フォトリソグラフィ工程により形成したマスクを用いて、当該導電膜をエッチングして、ゲート電極103を形成する。

【0090】

なお、ゲート電極103の側面は、テーパー形状とすることが好ましい。例えば、基板101及びゲート電極103の側面のなす角度を、20度以上60度以下、好ましくは30度以上50度以下とすることが好ましい。これは、後の工程で、ゲート電極103上に形成される絶縁膜、半導体膜及び配線が、ゲート電極103の段差箇所において切断されないようにするためである。ゲート電極103の側面をテーパー形状にするためには、マスクを後退させつつエッチングを行えばよい。

【0091】

また、ゲート電極103を形成する工程により、ゲート配線(走査線)及び容量配線も同時に形成することができる。なお、走査線とは画素を選択する配線をいい、容量配線とは画素の保持容量の一方の電極に接続された配線をいう。ただし、これに限定されず、ゲート配線及び容量配線の一方または双方と、ゲート電極103とは別に設けてもよい。

【0092】

ゲート絶縁膜105は、CVD法またはスパッタリング法等を用いて形成することができる。プラズマCVD法によるゲート絶縁膜105の形成工程において、グロー放電プラズマの生成は、3MHzから30MHz、代表的には13.56MHz、27.12MHzのHF帯の高周波電力、または30MHzより大きく300MHz程度までのVHF帯の高周波電力、代表的には、60MHzを印加することで行われる。また、1GHz以上のマイクロ波の高周波電力を印加することで行われる。なお、高周波電力がパルス状に印加されるパルス発振や、連続的に印加される連続発振とすることができる。また、HF帯の高周波電力と、VHF帯の高周波電力を重畳させることで、大面積基板においてもプラズマのムラを低減し、膜厚及び膜質の均一性を高めることができると共に、堆積速度を高めることができる。また、高周波数が1GHz以上であるマイクロ波プラズマCVD装置を用いてゲート絶縁膜105を形成すると、ゲート絶縁膜の耐圧を向上させることができるため、信頼性の高い薄膜トランジスタを得ることができる。

【0093】

また、ゲート絶縁膜105として、有機シランガスを用いたCVD法により酸化シリコン膜を形成することで、後に形成する半導体膜の微結晶半導体領域の結晶性を高めることが可能であるため、薄膜トランジスタのオン電流及び電界効果移動度を高めることができる。有機シランガスとしては、テトラエトキシシラン(TEOS:化学式Si(OC2H5)4)、テトラメチルシラン(TMS:化学式Si(CH3)4)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OC2H5)3)、トリスジメチルアミノシラン(SiH(N(CH3)2)3)等のシリコン含有化合物を用いることができる。

【0094】

ここでは、プラズマCVD法によりゲート絶縁膜105を形成する。

【0095】

微結晶半導体膜107は、原料ガスとして、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合する、プラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合し、グロー放電プラズマにより形成する。ここでは、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を50倍以上6000倍以下、好ましくは50倍以上3000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上50000Pa以下(0.5Torr以上370Torr以下)、更に好ましくは67Pa以上13332Pa以下(0.5Torr以上100Torr以下)とする条件により、微結晶半導体膜107を形成する。

【0096】

このときの堆積温度は、室温〜350℃とすることが好ましく、より好ましくは150〜280℃とする。なお、上部電極及び下部電極の間隔は、プラズマが発生しうる間隔とすればよい。なお、本明細書において、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量は、希釈されてない100%のシリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量である。このため、シリコンまたはゲルマニウムを含む堆積性気体が希釈されている場合は、シリコンまたはゲルマニウムを含む堆積性気体を100%として、水素流量を調整すればよい。

【0097】

非晶質半導体膜109として、原料ガスとして、シリコンまたはゲルマニウムを含む堆積性気体を用いるプラズマCVD法により形成する。または、原料ガスとして、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合する、プラズマCVD法により形成する。ここでは、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を0.1倍以上10倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上50000Pa以下(0.5Torr以上370Torr以下)、更に好ましくは67Pa以上13332Pa以下(0.5Torr以上100Torr以下)とする条件により、非晶質半導体膜109を形成する。

【0098】

このときの堆積温度は、室温〜350℃とすることが好ましく、より好ましくは150〜280℃とする。なお、上部電極及び下部電極の間隔は、プラズマが発生しうる間隔とすればよい。

【0099】

不純物半導体膜111は、プラズマCVD装置の処理室内において、シリコンを含む堆積性気体と、水素と、ジボラン(水素希釈またはシラン希釈)とを混合する、プラズマCVD法により、不純物半導体膜111を形成する。

【0100】

なお、シリコンまたはゲルマニウムを含む堆積性気体の代表例としては、SiH4、Si2H6、GeH4、Ge2H6等がある。

【0101】

また、プラズマCVD法による微結晶半導体膜107、非晶質半導体膜109、及び不純物半導体膜111の形成工程において、グロー放電のプラズマ生成は、ゲート絶縁膜105で列挙した高周波電力を適宜供給することで行われる。

【0102】

次に、不純物半導体膜111上にマスクを形成した後、微結晶半導体膜107、非晶質半導体膜109、及び不純物半導体膜111のそれぞれ一部をエッチングして、図9(B)に示すように、微結晶半導体領域117a、非晶質半導体領域117b、及び不純物半導体領域117cを有する半導体膜117を形成する。

【0103】

次に、図9(C)に示すように、ゲート絶縁膜105及び半導体膜117上に導電膜127を形成する。

【0104】

導電膜127は、配線129a、129bに列挙する材料を適宜用いて形成する。

【0105】

導電膜127は、CVD法、スパッタリング法または真空蒸着法を用いて形成する。

【0106】

次に、導電膜127上にマスクを形成した後、該マスクを用いて導電膜127をエッチングしてソース電極及びドレイン電極として機能する配線129a、129b形成する。次に、半導体膜117の一部をエッチングして、ソース領域及びドレイン領域として機能する一対の不純物半導体領域133a、133b、一対の非晶質半導体領域134a、134b、及び凹部を有する微結晶半導体領域135を有する半導体膜136を形成する(図10(A)参照)。

【0107】

導電膜127のエッチングは、ドライエッチングまたはウェットエッチングを用いることができる。エッチング条件は、導電膜127をエッチングする条件を適宜用いる。ドライエッチング方法については特に限定はなく、誘導結合型プラズマ(ICP:Inductively Coupled Plasma)方式、容量結合型プラズマ(CCP:Capacitively Coupled Plasma)方式、電子サイクロトン共鳴プラズマ(ECR:Electron Cyclotron Resonance)方式、反応性イオンエッチング(RIE:Reactive Ion Etching)方式等を適宜用いることができる。

【0108】

なお、配線129a、129bの一方は、ソース電極またはドレイン電極のみならず信号線としても機能する。ただし、これに限定されず、ソース電極及びドレイン電極とは別に信号線を設けてもよい。

【0109】

なお、ここでは、導電膜127から、微結晶半導体領域117aの一部までのエッチングを一度のエッチング工程で行ったが、以下に示すように、複数工程で行ってもよい。例えば、導電膜127上にマスクを形成し、該マスクを用いて導電膜127、不純物半導体領域117c、及び非晶質半導体領域117bの一部をエッチングする。当該、エッチング工程においては、微結晶半導体領域117aを露出しないように半導体膜117をエッチングする必要があり、少なくとも不純物半導体領域117cをエッチングする。この後、マスクを除去する。当該工程においてマスクを除去する溶液の一部が、非晶質半導体領域の表面に残存する場合がある。

【0110】

次に、配線129a、129bをマスクとして、非晶質半導体領域、及び微結晶半導体領域117aの一部をエッチングして、図10(A)に示すように分離された一対の非晶質半導体領域134a、134bと、凹部を有する微結晶半導体領域135を形成する。即ち、微結晶半導体領域135、一対の非晶質半導体領域134a、134b、及び一対の不純物半導体領域133a、133bを有する半導体膜136を形成する。

【0111】

上記工程のように、エッチング工程を2段階とし、1段階目のエッチングで、微結晶半導体領域が露出しない状態までエッチングし、その後マスクを除去する。当該、マスク除去の工程においては、微結晶半導体領域117aが非晶質半導体領域132に覆われているため、微結晶半導体領域177aが、残渣物と触れることがない。また、マスクを除去した後、2段階目のエッチングとして、配線129a、129bをマスクとして用いて、非晶質半導体領域132をエッチングして、微結晶半導体領域135を形成する。このため、残渣物は、バックチャネルには残存しない。

【0112】

以上のことから後にバックゲート電極を形成する場合、微結晶半導体領域135の凹部は、薄膜トランジスタのバックゲート側のチャネル領域となるため、当該領域の残渣物を除去することで、バックチャネルに残存した残渣物が原因のリーク電流が発生しないため、薄膜トランジスタのオフ電流をより低減することができる。

【0113】

次に、微結晶半導体領域135及び非晶質半導体領域134a、134bの表面にプラズマ処理、代表的には水プラズマ処理、酸素プラズマ処理、アンモニアプラズマ処理、窒素プラズマ処理、酸素及び水素の混合ガスによるプラズマ処理等を行ってもよい。

【0114】

ドライエッチングに続けて水プラズマ処理を行うことで、マスクの残渣を除去すると共に、微結晶半導体領域135の欠陥を低減することができる。また、プラズマ処理を行うことで、ソース領域とドレイン領域との間の絶縁性を高めることができ、完成する薄膜トランジスタのオフ電流を低減し、電気的特性のばらつきを低減することができる。

【0115】

以上の工程によりシングルゲート型の薄膜トランジスタを作製することができる。また、本実施の形態に示す構造とすることで、オフ電流が低いシングルゲート型の薄膜トランジスタを生産性高く作製することができる。

【0116】

次に、図10(B)に示すように、半導体膜136上に絶縁膜137(第2のゲート絶縁膜ともいう。)を形成する。絶縁膜137は、ゲート絶縁膜105と同様に形成することができる。

【0117】

次に、フォトリソグラフィ工程によりマスクを形成し、当該マスクを用いて絶縁膜137に開口部(図示しない。)を形成する。次に、絶縁膜137上にバックゲート電極139(第2のゲート電極ともいう。)及び画素電極141を形成する(図10(C)参照)。以上の工程により、デュアルゲート型の薄膜トランジスタを作製することができる。

【0118】

バックゲート電極139及び画素電極141は、CVD法、スパッタリング法または真空蒸着法を用いて、上記材料のいずれかを用いた薄膜を形成した後、フォトリソグラフィ工程によって形成したマスクを用いて上記薄膜をエッチングすることで、形成できる。また、バックゲート電極139及び画素電極141は、銀、金または銅等の導電性ナノペーストを用いてスクリーン印刷法またはインクジェット法等を用いて吐出し、焼成することで形成しても良い。

【0119】

次に、薄膜トランジスタの上面図である図11を用いて、バックゲート電極の形状を説明する。

【0120】

図11(A)に示すように、バックゲート電極139は、ゲート電極103と平行に形成することができる。この場合、バックゲート電極139に印加する電位と、ゲート電極103に印加する電位とを、それぞれ任意に制御することが可能である。このため、薄膜トランジスタのしきい値電圧を制御することができる。また、キャリアが流れる領域、即ちチャネル領域が、微結晶半導体領域のゲート絶縁膜105側、及び絶縁膜137側に形成されるため、薄膜トランジスタのオン電流を高めることができる。

【0121】

また、図11(B)に示すように、バックゲート電極139は、ゲート電極103に接続させることができる。即ち、ゲート絶縁膜105及び絶縁膜137に形成した開口部150において、ゲート電極103及びバックゲート電極139が接続する構造とすることができる。この場合、バックゲート電極139に印加する電位と、ゲート電極103に印加する電位とは、等しい。この結果、半導体膜において、キャリアが流れる領域、即ちチャネル領域が、微結晶半導体領域のゲート絶縁膜105側、及び絶縁膜137側に形成されるため、薄膜トランジスタのオン電流を高めることができる。

【0122】

また、図11(C)に示すように、バックゲート電極139は、ゲート電極103と接続せず、フローティングでもよい。バックゲート電極139に印加せずとも、チャネル領域が、微結晶半導体領域のゲート絶縁膜105側、及び絶縁膜137側に形成されるため、薄膜トランジスタのオン電流を高めることができる。

【0123】

さらには、図11(D)に示すように、バックゲート電極139は、絶縁膜137を介して配線129a、129bと重畳してもよい。ここでは、図11(A)に示す構造のバックゲート電極139を用いて示したが、図11(B)及び図11(C)に示すバックゲート電極139も同様に配線129a、129bと重畳してもよい。

【0124】

本実施の形態により、オフ電流の低いp型の逆スタガ型薄膜トランジスタを量産性高く作製することができる。

【0125】

(実施の形態3)

本実施の形態では、実施の形態1と比較して、オフ電流を低減しつつオン電流を高めることが可能な薄膜トランジスタの作製方法について、図12を用いて説明する。

【0126】

本実施の形態では、図9(A)において、微結晶半導体膜107、非晶質半導体膜109、及び不純物半導体膜111の代わりに、図12に示すような半導体膜118を形成することを特徴とする。なお、図12は、図9(A)のゲート絶縁膜105から不純物半導体膜111の間の拡大図である。

【0127】

半導体膜118は、微結晶半導体膜118a、微結晶半導体領域118c及び非晶質半導体領域118dを有する半導体膜118b、並びに不純物半導体膜111を有する。半導体膜118は、微結晶半導体領域118c及び非晶質半導体領域118dの界面が凹凸状であることを特徴とする。なお、微結晶半導体膜118a及び半導体膜118bの界面を点線で示したが、実際には当該界面は観察されない。

【0128】

図12(A)に示すように、半導体膜118bの微結晶半導体領域118c及び非晶質半導体領域118dの界面は凹凸状であり、凸部はゲート絶縁膜105から不純物半導体膜111に向かって、先端が狭まる(凸部の先端が鋭角である)凸状(錐形状)である。なお、凸部の形状は、ゲート絶縁膜105から不純物半導体膜111に向かって幅が広がる凸状(逆錐形状)であってもよい。

【0129】

微結晶半導体領域118cが凹凸状であるため、薄膜トランジスタのオン電流を高めることができる。

【0130】

また、微結晶半導体膜118a及び半導体膜118bに含まれる酸素の二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)によって計測される濃度を、1×1018atoms/cm3未満とすることで、微結晶半導体膜118a及び微結晶半導体領域118cの結晶性を高めることができるため好ましい。また、二次イオン質量分析法によって計測される半導体膜118の窒素濃度プロファイルのピーク濃度は、1×1020atoms/cm3以上1×1021atoms/cm3以下、好ましくは2×1020atoms/cm3以上1×1021atoms/cm3以下である。

【0131】

非晶質半導体領域118dは、窒素を有する非晶質半導体で形成される。窒素を有する非晶質半導体に含まれる窒素は、例えばNH基またはNH2基として存在していてもよい。非晶質半導体としては、アモルファスシリコンを用いる。

【0132】

窒素を含む非晶質半導体は、従来の非晶質半導体と比較して、CPM(Constant photocurrent method)やフォトルミネッセンス分光測定で測定されるUrbach端のエネルギーが小さく、欠陥吸収スペクトル量が少ない半導体である。即ち、窒素を含む非晶質半導体は、従来の非晶質半導体と比較して、欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い半導体である。窒素を含む非晶質半導体は、価電子帯のバンド端における準位のテール(裾)の傾きが急峻であるため、バンドギャップが広くなり、トンネル電流が流れにくい。このため、窒素を含む非晶質半導体を微結晶半導体領域118cと、不純物半導体膜111との間に設けることで、薄膜トランジスタのオフ電流を低減することができる。また、窒素を含む非晶質半導体を設けることで、オン電流と電界効果移動度を高めることが可能である。

【0133】

なお、窒素を含む非晶質半導体は、低温フォトルミネッセンス分光によるスペクトルのピークが、1.31eV以上1.39eV以下の範囲にある。なお、微結晶半導体、代表的には微結晶シリコンを低温フォトルミネッセンス分光により測定したスペクトルのピーク領域は、0.98eV以上1.02eV以下であり、窒素を含む非晶質半導体は、微結晶半導体とは異なるものである。

【0134】

また、非晶質半導体領域118dの他に、微結晶半導体領域118cにも、NH基またはNH2基を有してもよい。

【0135】

また、図12(B)に示すように、非晶質半導体領域118dに、粒径が1nm以上10nm以下、好ましくは1nm以上5nm以下の半導体結晶粒118eを含ませることで、更にオン電流と電界効果移動度を高めることが可能である。

【0136】

ゲート絶縁膜105から不純物半導体膜111に向かって、先端が狭まる凸状(錐形状)の微結晶半導体は、微結晶半導体膜118aを結晶核としつつ、結晶成長を抑制する条件で結晶成長させると共に、非晶質半導体を堆積することで、このような構造となる。

【0137】

半導体膜118bの作製方法の代表例としては、プラズマCVD装置の処理室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体とを混合するプラズマCVD法により形成する。窒素を含む気体としては、アンモニア、窒素、フッ化窒素、塩化窒素、クロロアミン、フルオロアミン等がある。グロー放電プラズマの生成は、ゲート絶縁膜105と同様にすることができる。

【0138】

このとき、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比は、実施の形態2に示す微結晶半導体膜107と同様の流量比を用い、さらに原料ガスに窒素を含む気体を用いる条件とすることで、微結晶半導体膜107の堆積条件よりも、結晶成長を抑制することができる。具体的には、半導体膜118bの堆積初期においては、原料ガスに窒素を含む気体が含まれるため、部分的に結晶成長が抑制され、錐形状の微結晶半導体領域が成長すると共に、非晶質半導体領域が形成される。さらに、堆積中期または後期では、錐形状の微結晶半導体領域の結晶成長が停止し、非晶質半導体領域のみが堆積される。この結果、半導体膜118bにおいて、微結晶半導体領域118c、及び欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い半導体で形成される非晶質半導体領域118dを形成することができる。

【0139】

ここでは、半導体膜118bの原料ガスに窒素を含む気体を含ませて、微結晶半導体領域118c及び非晶質半導体領域118dを有する半導体膜118bを形成したが、他の半導体膜118bの形成方法として、微結晶半導体膜118aの表面に窒素を含む気体を曝して、微結晶半導体膜118aの表面に窒素を吸着させた後、シリコンまたはゲルマニウムを含む堆積性気体及び水素を原料ガスとして、微結晶半導体領域118c及び非晶質半導体領域118dを有する半導体膜118bを形成することができる。

【0140】

または、半導体膜118bとして、実施の形態1に示す微結晶半導体領域117aとなる微結晶半導体膜の成膜条件を用いて第1の微結晶半導体膜領域を形成した後、上記実施の形態1に示す微結晶半導体領域117aとなる微結晶半導体膜に示す流量比を満たす原料ガスに、さらに窒素を含む気体を用いる条件で第2の微結晶半導体領域及び非晶質半導体領域を形成してもよい。なお、第1の微結晶半導体領域の成膜条件において、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比を、微結晶半導体膜118aと比較して低くすることで、成膜速度を高めることができる。

【0141】

半導体膜118bに含まれる微結晶半導体領域118cは、錐形状または逆錐形状であるため、オン状態でソース電極及びドレイン電極の間に電圧が印加されたときの縦方向(膜厚方向)における抵抗、即ち、半導体膜118bの抵抗を下げることが可能である。また、微結晶半導体膜118aと不純物半導体膜111との間に、欠陥が少なく、価電子帯のバンド端における準位のテール(裾)の傾きが急峻である秩序性の高い、窒素を含む非晶質半導体を有するため、トンネル電流が流れにくくなる。以上のことから、本実施の形態に示す薄膜トランジスタは、オン電流及び電界効果移動度を高めるとともに、オフ電流を低減することができる。

【0142】

(実施の形態4)

本実施の形態では、実施の形態1に示す微結晶半導体膜107または実施の形態3に示す微結晶半導体膜118aにおいて、結晶性が高く、混相粒が密である微結晶半導体膜の作製方法について、図13を用いて説明する。

【0143】

図13(A)に示すように、基板101上にゲート絶縁膜105を形成し、ゲート絶縁膜105上に種結晶157を形成する。

【0144】

種結晶157としては、微結晶半導体、代表的には、微結晶シリコン、微結晶シリコンゲルマニウム、微結晶ゲルマニウム等を用いて形成する。種結晶157は、複数の混相粒が分散した状態、混相粒が連続した膜の状態、または混相粒及び非晶質半導体領域が連続した膜の状態を含む。このため、種結晶157は、混相粒157aが隣接せず、混相粒157aの間に隙間157bを有するものも含む。さらに、混相粒の粒密度(面内における混相粒の存在割合)が低く、且つ混相粒の結晶性が高いことを特徴とする。

【0145】

種結晶157は、プラズマCVD装置の処理室内において、混相粒の粒密度が低く、且つ混相粒の結晶性が高くなるような第1の条件を用いて、原料ガスであるシリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合するプラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合するプラズマCVD法により形成する。ここでは、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上50000Pa以下(0.5Torr以上370Torr以下)、更に好ましくは67Pa以上13332Pa以下(0.5Torr以上100Torr以下)とする第1の条件により、種結晶157を形成する。第1の条件に示すような、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を高くする条件を用いて形成することで、結晶成長が促進され、種結晶157に含まれる混相粒157aの結晶性が高まる。即ち、種結晶157に含まれる混相粒157aに含まれる結晶子の大きさが増大する。また、隣り合う混相粒157aの間に隙間157bができ、混相粒157aの粒密度が低下する。

【0146】

種結晶157を形成する際のグロー放電のプラズマの生成は、ゲート絶縁膜105に列挙した高周波電力を適宜印加することで行われる。また、種結晶157の堆積温度は、微結晶半導体膜107に列挙した堆積温度を適宜用いる。

【0147】

次に、図13(B)に示すように、種結晶157上に第1の微結晶半導体膜159を形成する。第1の微結晶半導体膜159は、種結晶157の隙間を埋めつつ、結晶成長を促す条件で形成することを特徴とする。

【0148】

第1の微結晶半導体膜159は、プラズマCVD装置の処理室内において、第2の条件により、原料ガスであるシリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合するプラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合し、グロー放電プラズマにより形成する。ここでは、第2の条件を、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を100倍以上6000倍以下、好ましくは100倍以上3000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を1333Pa以上50000Pa以下(10Torr以上370Torr以下)、更に好ましくは1333Pa以上13332Pa以下(10Torr以上100Torr以下)とする。

【0149】

なお、処理室内の圧力が1333Pa以上50000Pa以下(10Torr以上370Torr以下)、更に好ましくは1333Pa以上13332Pa以下(10Torr以上100Torr以下)であれば、第1の条件の圧力より第2の条件の圧力が高くともよい。または、第2の条件より第1の条件の圧力が高くともよい。または、第1の条件及び第2の条件の圧力は同じであってもよい。

【0150】

上記第2の条件により、第1の微結晶半導体膜159として微結晶シリコン膜、微結晶シリコンゲルマニウム膜、微結晶ゲルマニウム膜等を形成する。

【0151】

第1の微結晶半導体膜159を形成する際のグロー放電のプラズマの生成は、ゲート絶縁膜105に列挙した高周波電力を適宜印加することで行われる。なお、種結晶157及び第1の微結晶半導体膜159のグロー放電のプラズマ生成は、同じ条件で行うことでスループットを向上させることができるが、異なっていてもよい。また、種結晶157の堆積温度は、微結晶半導体膜107に列挙した堆積温度を適宜用いる。

【0152】

第1の微結晶半導体膜159は、種結晶157の混相粒157aの隙間157bを埋めつつ、結晶成長を促す第2の条件で形成される。第2の条件を上記条件とすると、処理室内の圧力が高いため、平均自由行程が短く、イオンのエネルギーが低くなり、被覆率が向上すると共に、イオンダメージが低減し、欠陥低減に寄与する。また、シリコンまたはゲルマニウムを含む堆積性気体の希釈比が高く、水素ラジカルの生成量が増加するため、非晶質半導体領域をエッチングしつつ、混相粒157aに含まれる結晶子を核として結晶成長する。この結果、第1の微結晶半導体膜159は、非晶質半導体領域に対する結晶領域の割合が増加し、結晶性が高まる。また、堆積中の第1の微結晶半導体膜159の欠陥低減に寄与する。

【0153】

第1の微結晶半導体膜159は、種結晶157の混相粒157aに含まれる結晶子を核として結晶成長する。また、第1の微結晶半導体膜159の混相粒の大きさは、種結晶157の混相粒157aの間隔に依存する。このため、種結晶157の混相粒157aの粒密度が低いと、混相粒157aの間隔が広がるため、第1の微結晶半導体膜159の混相粒の結晶成長距離が伸び、第1の微結晶半導体膜159の混相粒の大粒径化が可能である。

【0154】

次に、図13(C)に示すように、第1の微結晶半導体膜159上に第2の微結晶半導体膜161を形成する。第2の微結晶半導体膜161は、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ第1の微結晶半導体膜159より結晶性の高い微結晶半導体膜を成膜する条件で形成することを特徴とする。

【0155】

第2の微結晶半導体膜161は、プラズマCVD装置の処理室内において、第3の条件により、原料ガスとしてシリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合するプラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合するプラズマCVD法により形成する。ここでは、第3の条件は、処理室内の圧力を1333Pa以上50000Pa以下、更に好ましくは1333Pa以上13332Pa以下とし、且つ微結晶半導体を堆積する第1の周期と、当該微結晶半導体に含まれる非晶質半導体領域を選択的にエッチングする上記第1の周期より長い第2の周期とを交互に行う条件である。

【0156】

微結晶半導体を堆積する第1の周期と、当該微結晶半導体に含まれる非晶質半導体領域を選択的にエッチングする上記第1の周期より長い第2の周期とを交互に行うためには、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比を交互に増減すればよく、具体的にはシリコンまたはゲルマニウムを含む堆積性気体または水素の流量を増減すればよい。シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比が低い場合、代表的には堆積性気体の流量に対する水素の流量を100倍以上2000倍以下にすることで、微結晶半導体の堆積及び結晶成長が優先的に生じる。一方、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比が高い場合、代表的にはシランまたはゲルマニウムを含む堆積性気体を0sccm以上0.3sccm以下とし、水素流量を1000sccmより高くすることで、微結晶半導体に含まれる非晶質半導体領域のエッチングが優先的に生じる。このとき、水素の流量を一定とし、シリコンまたはゲルマニウムを含む堆積性気体の流量を増減させる場合は、第1の周期と同様の流量の水素を処理室に導入することで、第1の周期及び第2の周期において処理室内の圧力を一定に保つことが可能であるため、第2の微結晶半導体膜の膜質の均一性を高めることができる。なお、処理室の圧力を1333Pa以上50000Pa以下、更に好ましくは1333Pa以上13332Pa以下とすることで、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比が高い場合は、微結晶半導体に含まれる結晶子よりも非晶質半導体領域が優先的にエッチングされる。

【0157】

上記第1の周期及び第2の周期を繰り返すことで、第2の周期では非晶質半導体領域の優先的なエッチングによる結晶子の露出と、第1の周期で露出された結晶子を核とする結晶成長とが交互に起きるため、混相粒の結晶子の大きさが大きくなり、さらには配向面を有する結晶成長が生じる。また、第1の周期よりも第2の周期の方を長くすると、微結晶半導体に含まれる非晶質半導体領域のエッチングが十分に行われるため、第2の微結晶半導体膜に含まれる非晶質半導体量を低減することが可能である。これらの結果、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ第1の微結晶半導体膜より結晶性の高い第2の微結晶半導体膜を形成することができる。また、第2の微結晶半導体膜161の欠陥を低減することができる。

【0158】

また、第2の周期において、わずかな流量、代表的には0sccmより高く0.3sccm以下の流量のシリコンまたはゲルマニウムを含む堆積性気体を流すことで、当該堆積性気体から生成されるわずかなラジカル(代表的には、シリルラジカル)が、非晶質半導体領域のエッチングにより露出された結晶子のダングリングボンドに結合するため、結晶性の高い結晶成長が生じる。即ち、エッチングと共に、結晶成長が生じるため、第2の微結晶半導体膜161の結晶性がより高くなる。

【0159】

上記第3の条件により、第2の微結晶半導体膜161として微結晶シリコン膜、微結晶シリコンゲルマニウム膜、微結晶ゲルマニウム膜等を形成する。

【0160】

第2の微結晶半導体膜161を形成する際の、グロー放電のプラズマの生成は、ゲート絶縁膜105に列挙した高周波電力を適宜印加することで行われる。なお、種結晶157、第1の微結晶半導体膜159、及び第2の微結晶半導体膜161のグロー放電プラズマの生成を同じ条件で行うことで、スループットを向上させることができるが、異なっていてもよい。また、第2の微結晶半導体膜161の堆積温度は、微結晶半導体膜107に列挙した堆積温度を適宜用いる。

【0161】

次に、図13(D)に示すように、第2の微結晶半導体膜161上に第3の微結晶半導体膜163を形成する。第3の微結晶半導体膜163は、第2の微結晶半導体膜161の混相粒の隙間を埋めつつ、結晶成長を促す条件で形成することを特徴とする。

【0162】

第3の微結晶半導体膜163は、プラズマCVD装置の処理室内において、第4の条件により、原料ガスとしてシリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合するプラズマCVD法により形成する。または、原料ガスに、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスを混合するプラズマCVD法により形成する。なお、第4の条件は、第2の条件と同様である。

【0163】

上記第4の条件により、第3の微結晶半導体膜163として微結晶シリコン膜、微結晶シリコンゲルマニウム膜、微結晶ゲルマニウム膜等を形成する。

【0164】

第4の条件を上記第2条件と同様とすると、処理室内の圧力が高いため、平均自由行程が短く、イオンのエネルギーが低くなり、被覆率が向上する。また、シリコンまたはゲルマニウムを含む堆積性気体の希釈比が高く、水素ラジカルの生成量が増加するため、非晶質半導体領域をエッチングしつつ、第2の微結晶半導体膜161に含まれる結晶子を核として結晶成長する。この結果、第3の微結晶半導体膜163は、非晶質半導体領域に対する結晶領域の割合が増加し、結晶性が高まる。また、第2の微結晶半導体膜161及び堆積中の第3の微結晶半導体膜163の平坦化に寄与する。

【0165】

以上の工程により、微結晶半導体膜164を形成することができる。

【0166】

ここで、図13(E)〜図13(H)に、本実施の形態に示す微結晶半導体膜164の成膜概念図を示す。図13(E)〜図13(H)は、それぞれ図13(A)〜図13(D)における堆積状態をイメージした拡大図である。

【0167】

図13(E)に示すように、種結晶157の堆積工程は、微結晶半導体膜に含まれる混相粒の大きさを大きくするために、種結晶粒子を散在させる工程である。このため、図13(E)に示すように、種結晶157は、種結晶粒子となる混相粒157aが隙間157bをおいて堆積される。

【0168】

図13(F)に示すように、第1の微結晶半導体膜159の堆積工程は、種結晶を元に結晶成長させ、隙間の極めて少ない混相粒を有する膜を形成する工程である。このため、混相粒157aを種結晶として結晶成長しながら微結晶半導体158が堆積される。なお、第2の条件を用いることで、微結晶半導体158は、膜厚方向だけでなく、平面方向にも結晶成長するため、微結晶半導体158同士の隙間が埋まり、微結晶半導体158が接する。

【0169】

図13(G)に示すように、第2の微結晶半導体膜161の堆積工程は、微結晶半導体158上に更に結晶性の高い微結晶半導体160を堆積させる工程である。第2の微結晶半導体膜161の堆積工程においては、微結晶半導体の堆積及び結晶成長の工程と、微結晶半導体に含まれる非晶質半導体領域を優先的にエッチングし、微結晶半導体に含まれる結晶子を露出させる工程が交互に行われる。また、処理室の圧力が1333Pa以上50000Pa以下(10Torr以上370Torr以下)、更に好ましくは1333Pa以上13332Pa以下(10Torr以上100Torr以下)であるため、微結晶半導体に含まれる非晶質半導体領域が優先的にエッチングされる。これらのため、露出された結晶子に微結晶半導体が堆積する際、エピタキシャル成長が生じやすい。この結果、第2の微結晶半導体膜161の堆積工程においては、微結晶半導体の配向性が高くなり、配向面を有する微結晶半導体160が堆積される。

【0170】

図13(H)に示すように、第3の微結晶半導体膜163の堆積工程は、第2の微結晶半導体膜161を元に結晶成長させ、第2の微結晶半導体膜161の混相粒の隙間を埋めつつ、第2の微結晶半導体膜161の凹凸を低減し、平坦化する工程である。このため、微結晶半導体160を種結晶として結晶成長しながら微結晶半導体162が堆積される。

【0171】

なお、第1の条件の圧力が第2の条件の圧力より低いと、基板面内における種結晶157の分布の均一性が高まるため好ましい。また、シリコンまたはゲルマニウムを含む堆積性気体に対する水素の流量比において、第1の条件が第2の条件より低いと、第2の条件によって混相粒が密となるように、種結晶157の堆積割合が高まるため好ましい。また、第1の微結晶半導体膜159の結晶性及び膜密度が高まるため好ましい。

【0172】

図13(E)乃至図13(H)の工程を経ることで、結晶性が高く、混相粒の隙間が極めて少なく、且つ配向面を有する混相粒を有する微結晶半導体膜164を形成することができる。なお、微結晶半導体膜164に含まれる混相粒は、種結晶157、第1の微結晶半導体膜159、第2の微結晶半導体膜161、及び第3の微結晶半導体膜163のそれぞれで堆積した微結晶半導体の場合もある。または、種結晶157、第1の微結晶半導体膜159、第2の微結晶半導体膜161、及び第3の微結晶半導体膜163の二以上が結晶成長しながら堆積した微結晶半導体の場合もある。

【0173】

本実施の形態では、図13(A)〜図13(D)の4工程を用いて微結晶半導体膜を形成する工程を説明したが、この代わりに、図13(A)及び図13(B)の工程を用いてもよい。または、図13(A)乃至図13(C)の工程を用いてもよい。

【0174】

(実施の形態5)

薄膜トランジスタを作製し、該薄膜トランジスタを画素部、さらには駆動回路に用いて表示機能を有する半導体装置(表示装置ともいう)を作製することができる。また、薄膜トランジスタを用いた駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

【0175】

表示装置は表示素子を含む。表示素子としては液晶素子(液晶表示素子ともいう)、発光素子(発光表示素子ともいう)を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL(Electro Luminescence)、有機EL等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

【0176】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに、該表示装置を作製する過程における、表示素子が完成する前の一形態に相当する素子基板に関し、該素子基板は、電流を表示素子に供給するための手段を複数の各画素に備える。素子基板は、具体的には、表示素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を形成した後であって、エッチングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

【0177】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源(照明装置含む)を指す。また、コネクタ、例えばFPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass)方式によりIC(集積回路)が直接実装されたモジュールも全て表示装置に含むものとする。

【0178】

(実施の形態6)

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機、電子ペーパーとして適用することができる。電子ペーパーは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍(電子ブック)、ポスター、デジタルサイネージ、PID(Public Information Display)、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図14に示す。

【0179】

図14は、電子書籍の一例を示している。例えば、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

【0180】

筐体2701には表示部2705及び光電変換装置2706が組み込まれ、筐体2703には表示部2707及び光電変換装置2708が組み込まれている。表示部2705および表示部2707は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とすることで、例えば右側の表示部(図14では表示部2705)に文章を表示し、左側の表示部(図14では表示部2707)に画像を表示することができる。

【0181】

また、図14では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

【0182】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【特許請求の範囲】

【請求項1】

ゲート電極と、

前記ゲート電極上に形成されるゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、且つ、微結晶半導体領域、一対の非晶質半導体領域、及び一対のp型の不純物半導体領域が積層された半導体膜と、

前記半導体膜の側面に接する領域が、前記ゲート絶縁膜を介して前記ゲート電極と重畳する一対の配線とを有し、

前記半導体膜及び前記一対の配線が接する領域において、前記一対の配線の仕事関数と、前記半導体膜の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上であることを特徴とする半導体装置。

【請求項2】

ゲート電極と、

前記ゲート電極上に形成されるゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、且つ、微結晶半導体領域、一対の非晶質半導体領域、及び一対のp型の不純物半導体領域が積層された半導体膜と、

前記半導体膜の側面に接する領域が、前記ゲート絶縁膜を介して前記ゲート電極と重畳する一対の配線とを有し、

前記一対の配線の仕事関数φMは4.30eV以上であることを特徴とする半導体装置。

【請求項3】

請求項2において、

前記一対の配線の仕事関数φMは4.30eV以上5.05eV以下であることを特徴とする半導体装置。

【請求項4】

請求項3において、

前記一対の配線の仕事関数φMは4.40eV以上4.90eV以下であることを特徴とする半導体装置。

【請求項5】

請求項1乃至請求項4のいずれか一項において、前記微結晶半導体領域は、前記ゲート絶縁膜に接し、前記非晶質半導体領域は、前記微結晶半導体領域及び前記一対のp型の不純物半導体領域に接することを特徴とする半導体装置。

【請求項1】

ゲート電極と、

前記ゲート電極上に形成されるゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、且つ、微結晶半導体領域、一対の非晶質半導体領域、及び一対のp型の不純物半導体領域が積層された半導体膜と、

前記半導体膜の側面に接する領域が、前記ゲート絶縁膜を介して前記ゲート電極と重畳する一対の配線とを有し、

前記半導体膜及び前記一対の配線が接する領域において、前記一対の配線の仕事関数と、前記半導体膜の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上であることを特徴とする半導体装置。

【請求項2】

ゲート電極と、

前記ゲート電極上に形成されるゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、且つ、微結晶半導体領域、一対の非晶質半導体領域、及び一対のp型の不純物半導体領域が積層された半導体膜と、

前記半導体膜の側面に接する領域が、前記ゲート絶縁膜を介して前記ゲート電極と重畳する一対の配線とを有し、

前記一対の配線の仕事関数φMは4.30eV以上であることを特徴とする半導体装置。

【請求項3】

請求項2において、

前記一対の配線の仕事関数φMは4.30eV以上5.05eV以下であることを特徴とする半導体装置。

【請求項4】

請求項3において、

前記一対の配線の仕事関数φMは4.40eV以上4.90eV以下であることを特徴とする半導体装置。

【請求項5】

請求項1乃至請求項4のいずれか一項において、前記微結晶半導体領域は、前記ゲート絶縁膜に接し、前記非晶質半導体領域は、前記微結晶半導体領域及び前記一対のp型の不純物半導体領域に接することを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−21316(P2013−21316A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2012−135585(P2012−135585)

【出願日】平成24年6月15日(2012.6.15)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成24年6月15日(2012.6.15)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]