半導体装置

【課題】電流消費を削減する。

【解決手段】第1のクロック信号(ICLK)を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号(LCLK)を出力する遅延回路(31)と、第2のクロック信号を受け、遅延された第3のクロック信号(RCLK)を出力するレプリカ回路(32)と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路(36)と、を備える。

【解決手段】第1のクロック信号(ICLK)を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号(LCLK)を出力する遅延回路(31)と、第2のクロック信号を受け、遅延された第3のクロック信号(RCLK)を出力するレプリカ回路(32)と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路(36)と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に係り、特に、DLL回路を備える半導体装置に係る。

【背景技術】

【0002】

DRAM(Dynamic Random Access Memory)やSRAM(Static Random Access Memory)に代表される半導体装置においては、そのデータ出力のタイミングを外部クロックのタイミングに合せるべく、内部クロックの位相を調整するDLL(Delay Locked Loop)回路が用いられることが多い。このようなDLL回路に関し、カウンタのコードが初期コードから近い値にある場合にはジッタを生じないように、遅延回路における遅延量を更新しないように制御する技術が特許文献1に開示されている。

【0003】

特許文献1に記載のクロック再生回路は、入力クロック信号と、内部クロック信号がフィードバックされた比較対象クロック信号との位相比較を実行可能な位相比較回路と、上記位相比較回路での位相比較結果をカウントするためのカウンタと、上記カウンタのカウント値をデコードするデコーダ回路と、上記デコーダからのデコード結果に基づいて上記内部クロック信号の生成を制御可能な制御回路とを設け、上記カウンタの出力コードが、予め設定された範囲に入る場合にはデコード出力を更新しない不感帯を設定することで、出力クロック信号の位相が一時的に変化された場合などにおいてジッタを生じないようにしている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−328459号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

以下の分析は本発明において与えられる。

【0006】

ところで、半導体装置には様々な仕様のものが存在し、その動作周波数が高いものでは、DLL回路における内部クロックの位相調整にも高精度が要求される。また、同じ1チップとしての設計であっても、広い周波数帯に対応するように設計されることが一般である。例えば、同じ設計のチップでも800MHz〜1.6GHz、DDR(Double-Data-Rate)方式であれば其々1.6Gbps、3.2Gbps等の範囲で動作することが必要とされる。従って、同じチップの設計であっても、1.6GHz側では高精度が要求され、800MHz側では相対的にそこまでの高精度は要求されないこととなる。

【0007】

一方、DLL回路は、回路規模も大きく、位相比較などを行う回路の特性等から消費電流が極めて大きい。近年の低消費電力化の要求を考慮すると、DLL回路においても低消費電力化を図ることが重要である。

【0008】

特許文献1は、カウンタの更新後のコードが初期コードから所定の範囲内にあるものを「不感帯」として遅延回路の遅延量を調整しない(不感帯の範囲内における変動をジッタとして扱う)ことを開示している。しかしながら、不感帯外の範囲に調整されるべき位相があった場合には結局微調整を行うこととなり、不感帯内においてもカウンタ等は動作し続ける(ロック状態でない)。したがって、消費電流が削減されず、低消費電力化を図ることができない。

【課題を解決するための手段】

【0009】

そこで本発明者は、DLL回路において相対的に高精度が要求されない状況(上記の800MHzの場合等)について着目した。この場合においてもDLL回路内における遅延回路の遅延調整幅は、例えば他の仕様(1.6GHz)を満たすべく、また、他の仕様がない場合においても製造初期の動作確認を確実に行うべく細かいものが用いられている。

【0010】

DLL回路は、比較対象クロック信号の位相に入力クロック信号の位相が実質的に等しくなるように遅延回路の遅延量を調整するものである。この調整は、高周波数帯で用いる製品(仕様)においては極めて重要である。しかしながら、相対的に低周波数帯で用いる製品(仕様)においては、調整のための回路が動作し続け、消費電力の点で有利とは言えない。

【0011】

そこで、本発明者は、入力クロック信号の位相を目標である比較対象クロック信号の位相に実質的に合わせにいくのではなく、入力クロック信号の位相が比較対象クロック信号の位相に対して所定の位相差範囲内に入った場合に積極的に位相調整を停止して(つまりロック状態として)、それ以降の電流消費を削減することを創案した。

【0012】

本発明の1つのアスペクト(側面)に係る半導体装置は、第1のクロック信号を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号を出力する遅延回路と、第2のクロック信号を受け、遅延された第3のクロック信号を出力するレプリカ回路と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路と、を備える。

【発明の効果】

【0013】

本発明によれば、低消費電力化が可能である。

【図面の簡単な説明】

【0014】

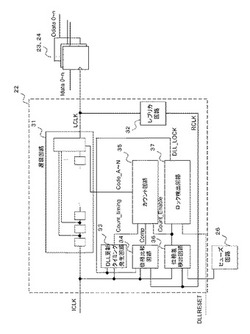

【図1】本発明の第1の実施例に係る半導体装置の構成を示す図である。

【図2】本発明の第1の実施例に係るDLL回路の構成を示すブロック図である。

【図3】本発明の第1の実施例に係る位相差検出回路の構成を示すブロック図である。

【図4】本発明の第1の実施例に係る位相差検出回路の動作を表す図である。

【図5】本発明の第1の実施例に係るDLL回路の各部の動作波形を示す図である。

【図6】クロック信号ICLK、RCLKの波形の拡大図である。

【図7】本発明の第2の実施例に係るDLL回路の構成を示すブロック図である。

【図8】本発明の第2の実施例に係るDLL回路の各部の動作波形を示す図である。

【発明を実施するための形態】

【0015】

以下、本発明を実施するための形態について、概説する。なお、以下の概説に付記した図面参照符号は、専ら理解を助けるための例示であり、図示の態様に限定することを意図するものではない。

【0016】

本発明の一実施形態に係る半導体装置は、第1のクロック信号(図2のICLK)を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号(図2のLCLK)を出力する遅延回路(図2の31)と、第2のクロック信号を受け、遅延された第3のクロック信号(図2のRCLK)を出力するレプリカ回路(図2の32)と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路(図2の36)と、を備える。

【0017】

半導体装置において、第3のクロック信号の位相が第1のクロック信号の位相よりも進んでいるか否かを検知する位相比較回路(図2の34)を更に備え、位相差検出回路は、第1および第3のクロック信号の位相差が所定時間以上である場合には位相比較回路の検出結果を有効として遅延回路の遅延量を変化させ、第1および第3のクロック信号の位相差が所定時間未満である場合には位相比較回路の検出結果を無効として遅延回路の遅延量を変化させないようにしてもよい。

【0018】

半導体装置において、位相差検出回路の動作モードを設定するヒューズ回路(図2の26)を備え、ヒューズ回路に第1のデータが書き込まれている時に、位相差検出回路は、第1および第3のクロック信号の位相差が所定時間以上であるか否かに関わらず位相比較回路の検出結果を有効として遅延回路の遅延量を変化させ、第2のデータが書き込まれている時に、位相差検出回路は、第1および第3のクロック信号の位相差が所定時間以上である場合には遅延回路の遅延量を変化させ、第1および第3のクロック信号の位相差が所定時間未満である場合には位相比較回路の検出結果を無効として遅延回路の遅延量を変化させない制御を行うようにしてもよい。

【0019】

半導体装置において、遅延回路の遅延量を位相比較回路からの検出結果信号に応じて変化させるコード信号を出力するカウント回路(図2の35)を更に備え、位相差検出回路は、第1および第3のクロック信号の位相差が所定時間以上である場合には位相比較回路の検知結果を有効としてカウント回路のコード信号を更新し、第1および第3のクロック信号の位相差が所定時間未満である場合には位相比較回路の検出結果を無効としてカウント回路のコード信号を更新しないようにしてもよい。

【0020】

半導体装置において、位相差検出回路(図7の36a)は、半導体自身の電源立ち上がり時の所定期間において活性化されるイニシャルシーケンス信号(図7のINIT)を受け、イニシャルシーケンス信号が活性状態を示す期間において、第1および第3のクロック信号の位相差が所定時間以上であるか否かに関わらず位相比較回路の検出結果を有効として遅延回路の遅延量を変化させ、イニシャルシーケンス信号が非活性状態を示す期間において、第1および第3のクロック信号の位相差が所定時間以上である場合には遅延回路の遅延量を変化させ、第1および第3のクロック信号の位相差が所定時間未満である場合には位相比較回路の検出結果を無効として遅延回路の遅延量を変化させないように制御してもよい。

【0021】

半導体装置において、位相差検出回路は、第1のクロック信号を遅延する第2の遅延回路(図3の41)と、第3のクロック信号を遅延する第3の遅延回路(図3の42)と、第2の遅延回路の出力信号と第3のクロック信号との位相差を比較する第1の位相差比較器(図3の43)と、第3の遅延回路の出力信号と第1のクロック信号との位相差を比較する第2の位相差比較器(図3の44)と、第1および第2の位相差比較器における位相差比較結果に基づいて第1および第3のクロック信号の位相差が所定時間以上であるか否かを判断するカウント制御回路(図3の45)と、を備えるようにしてもよい。

【0022】

以上のような半導体装置によれば、電流消費を削減することができる。

【0023】

以下、実施例に即し、図面を参照して詳しく説明する。

【実施例1】

【0024】

図1は、本発明の第1の実施例に係る半導体装置の構成を示す図である。図1において、半導体装置は、SDRAM(Synchronous Dynamic Random Access Memory)であって、アドレス入力回路11、アドレスラッチ回路12、コマンド入力回路13、コマンドデコード回路14、モードレジスタ15、リフレッシュ制御回路16、カラムデコーダ17、ロウデコーダ18、メモリセルアレイ19、クロック入力回路20、タイミングジェネレータ21、DLL回路22、FIFO回路23、入出力回路24、内部電源発生回路25、ヒューズ回路26を備える。

【0025】

アドレス入力回路11は、外部からアドレス信号ADDを入力してバッファリングし、アドレスラッチ回路12に出力する。アドレスラッチ回路12は、アドレス信号ADDをクロック信号ICLKのタイミングでラッチし、モードレジスタ15、カラムデコーダ17、ロウデコーダ18に出力する。

【0026】

コマンド入力回路13は、ロウアドレスストローブ信号/RAS、カラムアドレスストローブ信号/CAS、リセット信号/RSTを外部から入力し、コマンドに係る信号をコマンドデコード回路14に出力する。コマンドデコード回路14は、コマンドに係る信号をデコードし、カラムアドレスのデコードタイミングをカラムデコーダ17に出力し、ロウアドレスのデコードタイミングをロウデコーダ18に出力し、モード設定タイミングをモードレジスタ15に出力し、リフレッシュタイミングをリフレッシュ制御回路16に出力し、リセット信号DLLRESETをDLL回路22に出力する。

【0027】

モードレジスタ15は、モード設定タイミングに合わせてDRAMの動作モードを設定する。リフレッシュ制御回路16は、リフレッシュタイミングに応じてロウデコーダ18からリフレッシュアドレスを発生するようにロウデコーダ18を制御する。

【0028】

カラムデコーダ17は、カラムアドレスをメモリセルアレイ19に出力し、ロウデコーダ18は、ロウアドレスをメモリセルアレイ19に出力し、メモリセルアレイ19は、カラムアドレスとロウアドレスとに対応するメモリセルにアクセスする。

【0029】

クロック入力回路20は、外部からクロック信号CK、/CKを入力してバッファリングし、クロック信号ICLKをアドレスラッチ回路12、コマンドデコード回路14、タイミングジェネレータ21およびDLL回路22に出力する。タイミングジェネレータ21は、クロック信号ICLKに同期した各種タイミング信号を必要に応じて各部に分配し、各タイミング信号が半導体装置内を伝送する其々のタイミングを制御する。DLL回路22は、クロック信号ICLK、リセット信号DLLRESETを入力し、クロック信号ICLKの位相を調整したクロック信号LCLKをFIFO回路23および入出力回路24に出力する。

【0030】

FIFO回路23は、メモリセルアレイ19と入出力回路24間にあって入出力データをバッファリングする。入出力回路24は、DQ端子から入力されたライトデータをFIFO回路23に出力し、また、FIFO回路23から入力されたリードデータをDQ端子に出力する。この場合、クロック信号LCLKの位相は、クロック信号LCLKに同期してDQ端子から出力されるデータ信号が外部のクロック信号CKと同期するように調整される。

【0031】

内部電源発生回路25は、外部から電源VDD、VSSを供給されて、内部の電源電圧を発生する。

【0032】

ヒューズ回路26は、DLL回路22のロック機能を有効にするか否かを決定する設定用の回路であり、半導体装置の仕様、例えば、クロック信号CK、/CKの周波数が所定の値以上か否かに応じて設定される。すなわち、DLL回路22のロック機能が、例えば、半導体装置が高速動作品(1.6GHz)として利用される場合においては位相差検出回路の機能が無効とされ、低速動作品(800MHz)として利用される場合においては該機能が有効とされるように設定が可能である。

【0033】

次に、DLL回路の構成について説明する。図2は、本発明の第1の実施例に係るDLL回路の構成を示すブロック図である。図2において、DLL回路22は、遅延回路31、レプリカ回路32、DLL更新タイミング発生回路33、位相比較回路34、カウント回路35、位相差検出回路36、ロック検出回路37を備える。

【0034】

遅延回路31は、クロック信号ICLKに対し、カウント回路35が出力するコード信号Code_A〜Nに対応した遅延を与えてクロック信号LCLKとしてFIFO回路23、入出力回路24、およびレプリカ回路32に出力する。

【0035】

レプリカ回路32は、入出力回路24においてデータ出力のタイミングを外部クロックに合せるために入出力回路24における遅延時間と実質的に同等である遅延時間をクロック信号LCLKに与え、クロック信号RCLKとして位相比較回路34および位相差検出回路36に出力する。

【0036】

DLL更新タイミング発生回路33は、クロック信号ICLKからカウント回路35におけるカウントタイミングを定める信号Count_timingを生成してカウント回路35に出力する。なお、信号DLL_LOCKが活性状態にある場合には、信号Count_timingのカウント回路35への出力を停止する。

【0037】

位相比較回路34は、クロック信号ICLKとクロック信号RCLKとの位相を比較し、比較結果を示す信号Compをカウント回路35に出力する。なお、信号DLL_LOCKが活性状態にある場合には、位相比較を行うことなく、信号Compのカウント回路35への出力を停止する。

【0038】

カウント回路35は、信号Count_Enableの活性状態において、信号Count_timingのタイミングに従って信号Compをカウントし、カウント値をコード信号Code_A〜Nとして遅延回路31に出力する。すなわち、クロック信号ICLKの位相がクロック信号RCLKの位相より進んでいるか、遅れているかの検知結果を用いて、カウント回路35のカウント値が更新(+カウント/−カウント)され、遅延回路31の遅延段数が変化(遅延量増/遅延量減)する。そして、コード信号Code_A〜Nが例えば「+++−+」のように振動したことを検知してDLL回路の調整を終了する。なお、信号DLL_LOCKが活性状態にある場合には、信号Count_timing、Compが入力されないので、カウント動作を停止する。

【0039】

位相差検出回路36は、クロック信号ICLKとクロック信号RCLKとの位相差を検出し、位相差が所定の不感帯幅より大きな場合に、信号Count_Enableを活性状態としてカウント回路35およびロック検出回路37に出力する。なお、不感帯幅が無効となるようにヒューズ回路26が設定されている場合、位相差検出回路36は、位相差の如何に係らず信号Count_Enableを活性状態とする。

【0040】

ロック検出回路37は、信号DLLRESETが活性化されるとリセットされ、信号Count_Enableが非活性状態となった場合に、DLL_LOCKを活性状態としてDLL更新タイミング発生回路33、位相比較回路34に出力する。

【0041】

次に、位相差検出回路36について説明する。図3は、本発明の第1の実施例に係る位相差検出回路の構成を示すブロック図である。位相差検出回路36は、遅延回路41、42、位相差比較器43、44、カウント制御回路45を備える。

【0042】

遅延回路41は、クロック信号ICLKを遅延し、位相差比較器43の一方の入力端(+)に出力する。遅延回路42は、クロック信号RCLKを遅延し、位相差比較器44の一方の入力端(−)に出力する。位相差比較器43は、他方の入力端(−)にクロック信号RCLKを入力し、クロック信号ICLKを遅延した信号との位相差を比較し、比較結果を表す信号OUT_Aをカウント制御回路45に出力する。位相差比較器44は、他方の入力端(+)にクロック信号ICLKを入力し、クロック信号RCLKを遅延した信号との位相差を比較し、比較結果を表す信号OUT_Bをカウント制御回路45に出力する。カウント制御回路45は、信号OUT_A、OUT_Bからクロック信号ICLK、RCLKの位相差が所定の値未満であるか否かを表す信号Count_Enableを出力する。

【0043】

ここで遅延回路41、42では、例えば其々150psの遅延量が調整されているとする。つまり、遅延量を調整し、位相差が150ps以内に入った場合、又は当初から位相差が150ps以内の場合に、信号Count_Enableを非活性状態とする。

【0044】

位相差比較器43は、「クロック信号ICLK+150psの遅延」と「クロック信号RCLK」との位相比較を行い、位相差比較器44は、「クロック信号ICLK」と「クロック信号RCLK+150psの遅延」との位相比較を行う。

【0045】

クロック信号ICLKがクロック信号RCLKに対して150ps以上進んでいれば、位相差比較器41、42の出力は、共にHレベルとなり、クロック信号RCLKがクロック信号ICLKに対して150ps以上進んでいれば、位相差比較器41、42の出力は、共にLレベルとなる。この場合、カウント制御回路45は、図4に示すように信号Count_EnableをHレベルとして出力する。

【0046】

また、クロック信号ICLK、RCLKの差が150ps以内の場合には、位相差比較器41、42の其々の出力は、Lレベル、Hレベルとなる。この場合、カウント制御回路45は、図4に示すように信号Count_EnableをLレベルとして出力する。このようにカウント制御回路45は、信号OUT_A、OUT_Bに対して排他的論理和の機能を果たす。

【0047】

次に、DLL回路の動作について説明する。図5は、本発明の第1の実施例に係るDLL回路の各部の動作波形を示す図である。図5における各タイミングでは、以下のように動作する。

タイミングt1:クロック信号ICLK、RCLKの位相差が不感帯値nよりも大きい(不感帯外に存在する)ためカウント回路35が更新される。

タイミングt2:同じく更新される。

タイミングt3:クロック信号ICLK、RCLKの位相差が不感帯値nよりも小さくなった(不感帯内に存在する)ため、信号Count_EnableがLレベルとなり信号DLL_LOCKが活性化(Hレベル)とされ、カウント回路35は更新されない。

タイミングt4:デバイスの温度等の状態変化によって位相差が不感帯値nよりも大きくなり信号Count_EnableがHレベルとなる。しかし、信号DLL_LOCKが活性化状態であるためカウント回路35は更新されない。

タイミングt5:信号DLLRESETによってLOCKが解除され、位相差が不感帯値nよりも大きいためにカウント回路35が更新される。

【0048】

図6は、クロック信号ICLK、RCLKの波形の拡大図である。ここでは、ロック状態であってもその位相差範囲内を遅延回路31で更に細かく調整可能であるという点を示している。例えば、DLL回路22をロックさせる位相差をn=150ps、遅延回路31に含まれる遅延素子1段分の調整幅を30psとすることが出来る。

【0049】

本実施例のDLL回路22は、高速動作品(1.6GHz≒周期0.6ns)の半導体装置においては、クロック信号ICLK、RCLKの位相差が例えば150ps以内(位相差検出回路36の抽出範囲、不感帯)でも動作させる。一方、低速動作品(800MHz≒周期1.3ns)の半導体装置においては、そういった操作を行わない。後者における150psの割合は12%程度であり動作上許容されうるが、前者における割合は25%程度であり動作上許容出来ないためである。勿論、この値150psは図3における遅延回路41の遅延量を調整することで任意に変更可能である。即ち、DLL回路22は、潜在的には30psでの調整が可能ではあるが、低速動作品(800MHz)の半導体装置においては、微調整を行うことで発生する電力消費の増大を防ぐように、敢えて微調整を行わないように設定される。

【実施例2】

【0050】

図7は、本発明の第2の実施例に係るDLL回路の構成を示すブロック図である。図7において、図2と同一の符号は、同一物を表し、その説明を省略する。位相差検出回路36aは、図2の位相差検出回路36に対し、さらにイニシャルシーケンスを表す信号INITを入力する。

【0051】

DLL回路の動作タイミングを、イニシャルシーケンス(電源投入後の最初の調整)と、その後の調整(半導体装置動作中の微調整)とに分け、信号INITが活性状態(Hレベル)となるイニシャルシーケンス時には、実施例1で説明した不感帯内に入っても位相調整を停止せずに高精度にロック動作を行う。また、信号INITが非活性状態(Lレベル)となった、その後の他の調整においては、第1の実施例と同様の動作を行うものである。このように、最初に高精度にあわせ込んでいることから、その後の温度変化等によって多少の位相差が発生したとしても不感帯内に収まり、その結果、他の調整を省くことが可能となる。

【0052】

次に、DLL回路の動作について説明する。図8は、本発明の第2の実施例に係るDLL回路の各部の動作波形を示す図である。図5ではタイミングt3でカウント回路35を停止していたが、図8では、イニシャルシーケンスを表す信号INITによって信号Count_EnableをHに固定することで不感帯を無効とする。イニシャルシーケンス以外の期間においては、図2と同様に不感帯に基づいて動作する。

【0053】

すなわち、イニシャルシーケンスを表す信号INITが活性状態(Hレベル)にある場合、信号Count_Enableが活性状態(Hレベル)とされ、不感帯内に位相が調整された後も調整を継続し、ロック状態に至る。ロック状態では、先に述べたようにコード信号Code_A〜Nが例えば「+++−+」のように振動した状態とされる。

【0054】

本実施例のDLL回路は、イニシャル時のロックを高精度とし、イニシャル時以降では、位相差検出回路36が、クロック信号ICLK、RCLKの位相差が例えば150ps以上であることを検出しない限り、再調整を行わないように動作する。

【0055】

なお、前述の特許文献等の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0056】

11 アドレス入力回路

12 アドレスラッチ回路

13 コマンド入力回路

14 コマンドデコード回路

15 モードレジスタ

16 リフレッシュ制御回路

17 カラムデコーダ

18 ロウデコーダ

19 メモリセルアレイ

20 クロック入力回路

21 タイミングジェネレータ

22 DLL回路

23 FIFO回路

24 入出力回路

25 内部電源発生回路

26 ヒューズ回路

31、41、42 遅延回路

32 レプリカ回路

33 DLL更新タイミング発生回路

34 位相比較回路

35 カウント回路

36、36a 位相差検出回路

37 ロック検出回路

43、44 位相差比較器

45 カウント制御回路

【技術分野】

【0001】

本発明は、半導体装置に係り、特に、DLL回路を備える半導体装置に係る。

【背景技術】

【0002】

DRAM(Dynamic Random Access Memory)やSRAM(Static Random Access Memory)に代表される半導体装置においては、そのデータ出力のタイミングを外部クロックのタイミングに合せるべく、内部クロックの位相を調整するDLL(Delay Locked Loop)回路が用いられることが多い。このようなDLL回路に関し、カウンタのコードが初期コードから近い値にある場合にはジッタを生じないように、遅延回路における遅延量を更新しないように制御する技術が特許文献1に開示されている。

【0003】

特許文献1に記載のクロック再生回路は、入力クロック信号と、内部クロック信号がフィードバックされた比較対象クロック信号との位相比較を実行可能な位相比較回路と、上記位相比較回路での位相比較結果をカウントするためのカウンタと、上記カウンタのカウント値をデコードするデコーダ回路と、上記デコーダからのデコード結果に基づいて上記内部クロック信号の生成を制御可能な制御回路とを設け、上記カウンタの出力コードが、予め設定された範囲に入る場合にはデコード出力を更新しない不感帯を設定することで、出力クロック信号の位相が一時的に変化された場合などにおいてジッタを生じないようにしている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−328459号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

以下の分析は本発明において与えられる。

【0006】

ところで、半導体装置には様々な仕様のものが存在し、その動作周波数が高いものでは、DLL回路における内部クロックの位相調整にも高精度が要求される。また、同じ1チップとしての設計であっても、広い周波数帯に対応するように設計されることが一般である。例えば、同じ設計のチップでも800MHz〜1.6GHz、DDR(Double-Data-Rate)方式であれば其々1.6Gbps、3.2Gbps等の範囲で動作することが必要とされる。従って、同じチップの設計であっても、1.6GHz側では高精度が要求され、800MHz側では相対的にそこまでの高精度は要求されないこととなる。

【0007】

一方、DLL回路は、回路規模も大きく、位相比較などを行う回路の特性等から消費電流が極めて大きい。近年の低消費電力化の要求を考慮すると、DLL回路においても低消費電力化を図ることが重要である。

【0008】

特許文献1は、カウンタの更新後のコードが初期コードから所定の範囲内にあるものを「不感帯」として遅延回路の遅延量を調整しない(不感帯の範囲内における変動をジッタとして扱う)ことを開示している。しかしながら、不感帯外の範囲に調整されるべき位相があった場合には結局微調整を行うこととなり、不感帯内においてもカウンタ等は動作し続ける(ロック状態でない)。したがって、消費電流が削減されず、低消費電力化を図ることができない。

【課題を解決するための手段】

【0009】

そこで本発明者は、DLL回路において相対的に高精度が要求されない状況(上記の800MHzの場合等)について着目した。この場合においてもDLL回路内における遅延回路の遅延調整幅は、例えば他の仕様(1.6GHz)を満たすべく、また、他の仕様がない場合においても製造初期の動作確認を確実に行うべく細かいものが用いられている。

【0010】

DLL回路は、比較対象クロック信号の位相に入力クロック信号の位相が実質的に等しくなるように遅延回路の遅延量を調整するものである。この調整は、高周波数帯で用いる製品(仕様)においては極めて重要である。しかしながら、相対的に低周波数帯で用いる製品(仕様)においては、調整のための回路が動作し続け、消費電力の点で有利とは言えない。

【0011】

そこで、本発明者は、入力クロック信号の位相を目標である比較対象クロック信号の位相に実質的に合わせにいくのではなく、入力クロック信号の位相が比較対象クロック信号の位相に対して所定の位相差範囲内に入った場合に積極的に位相調整を停止して(つまりロック状態として)、それ以降の電流消費を削減することを創案した。

【0012】

本発明の1つのアスペクト(側面)に係る半導体装置は、第1のクロック信号を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号を出力する遅延回路と、第2のクロック信号を受け、遅延された第3のクロック信号を出力するレプリカ回路と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路と、を備える。

【発明の効果】

【0013】

本発明によれば、低消費電力化が可能である。

【図面の簡単な説明】

【0014】

【図1】本発明の第1の実施例に係る半導体装置の構成を示す図である。

【図2】本発明の第1の実施例に係るDLL回路の構成を示すブロック図である。

【図3】本発明の第1の実施例に係る位相差検出回路の構成を示すブロック図である。

【図4】本発明の第1の実施例に係る位相差検出回路の動作を表す図である。

【図5】本発明の第1の実施例に係るDLL回路の各部の動作波形を示す図である。

【図6】クロック信号ICLK、RCLKの波形の拡大図である。

【図7】本発明の第2の実施例に係るDLL回路の構成を示すブロック図である。

【図8】本発明の第2の実施例に係るDLL回路の各部の動作波形を示す図である。

【発明を実施するための形態】

【0015】

以下、本発明を実施するための形態について、概説する。なお、以下の概説に付記した図面参照符号は、専ら理解を助けるための例示であり、図示の態様に限定することを意図するものではない。

【0016】

本発明の一実施形態に係る半導体装置は、第1のクロック信号(図2のICLK)を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号(図2のLCLK)を出力する遅延回路(図2の31)と、第2のクロック信号を受け、遅延された第3のクロック信号(図2のRCLK)を出力するレプリカ回路(図2の32)と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路(図2の36)と、を備える。

【0017】

半導体装置において、第3のクロック信号の位相が第1のクロック信号の位相よりも進んでいるか否かを検知する位相比較回路(図2の34)を更に備え、位相差検出回路は、第1および第3のクロック信号の位相差が所定時間以上である場合には位相比較回路の検出結果を有効として遅延回路の遅延量を変化させ、第1および第3のクロック信号の位相差が所定時間未満である場合には位相比較回路の検出結果を無効として遅延回路の遅延量を変化させないようにしてもよい。

【0018】

半導体装置において、位相差検出回路の動作モードを設定するヒューズ回路(図2の26)を備え、ヒューズ回路に第1のデータが書き込まれている時に、位相差検出回路は、第1および第3のクロック信号の位相差が所定時間以上であるか否かに関わらず位相比較回路の検出結果を有効として遅延回路の遅延量を変化させ、第2のデータが書き込まれている時に、位相差検出回路は、第1および第3のクロック信号の位相差が所定時間以上である場合には遅延回路の遅延量を変化させ、第1および第3のクロック信号の位相差が所定時間未満である場合には位相比較回路の検出結果を無効として遅延回路の遅延量を変化させない制御を行うようにしてもよい。

【0019】

半導体装置において、遅延回路の遅延量を位相比較回路からの検出結果信号に応じて変化させるコード信号を出力するカウント回路(図2の35)を更に備え、位相差検出回路は、第1および第3のクロック信号の位相差が所定時間以上である場合には位相比較回路の検知結果を有効としてカウント回路のコード信号を更新し、第1および第3のクロック信号の位相差が所定時間未満である場合には位相比較回路の検出結果を無効としてカウント回路のコード信号を更新しないようにしてもよい。

【0020】

半導体装置において、位相差検出回路(図7の36a)は、半導体自身の電源立ち上がり時の所定期間において活性化されるイニシャルシーケンス信号(図7のINIT)を受け、イニシャルシーケンス信号が活性状態を示す期間において、第1および第3のクロック信号の位相差が所定時間以上であるか否かに関わらず位相比較回路の検出結果を有効として遅延回路の遅延量を変化させ、イニシャルシーケンス信号が非活性状態を示す期間において、第1および第3のクロック信号の位相差が所定時間以上である場合には遅延回路の遅延量を変化させ、第1および第3のクロック信号の位相差が所定時間未満である場合には位相比較回路の検出結果を無効として遅延回路の遅延量を変化させないように制御してもよい。

【0021】

半導体装置において、位相差検出回路は、第1のクロック信号を遅延する第2の遅延回路(図3の41)と、第3のクロック信号を遅延する第3の遅延回路(図3の42)と、第2の遅延回路の出力信号と第3のクロック信号との位相差を比較する第1の位相差比較器(図3の43)と、第3の遅延回路の出力信号と第1のクロック信号との位相差を比較する第2の位相差比較器(図3の44)と、第1および第2の位相差比較器における位相差比較結果に基づいて第1および第3のクロック信号の位相差が所定時間以上であるか否かを判断するカウント制御回路(図3の45)と、を備えるようにしてもよい。

【0022】

以上のような半導体装置によれば、電流消費を削減することができる。

【0023】

以下、実施例に即し、図面を参照して詳しく説明する。

【実施例1】

【0024】

図1は、本発明の第1の実施例に係る半導体装置の構成を示す図である。図1において、半導体装置は、SDRAM(Synchronous Dynamic Random Access Memory)であって、アドレス入力回路11、アドレスラッチ回路12、コマンド入力回路13、コマンドデコード回路14、モードレジスタ15、リフレッシュ制御回路16、カラムデコーダ17、ロウデコーダ18、メモリセルアレイ19、クロック入力回路20、タイミングジェネレータ21、DLL回路22、FIFO回路23、入出力回路24、内部電源発生回路25、ヒューズ回路26を備える。

【0025】

アドレス入力回路11は、外部からアドレス信号ADDを入力してバッファリングし、アドレスラッチ回路12に出力する。アドレスラッチ回路12は、アドレス信号ADDをクロック信号ICLKのタイミングでラッチし、モードレジスタ15、カラムデコーダ17、ロウデコーダ18に出力する。

【0026】

コマンド入力回路13は、ロウアドレスストローブ信号/RAS、カラムアドレスストローブ信号/CAS、リセット信号/RSTを外部から入力し、コマンドに係る信号をコマンドデコード回路14に出力する。コマンドデコード回路14は、コマンドに係る信号をデコードし、カラムアドレスのデコードタイミングをカラムデコーダ17に出力し、ロウアドレスのデコードタイミングをロウデコーダ18に出力し、モード設定タイミングをモードレジスタ15に出力し、リフレッシュタイミングをリフレッシュ制御回路16に出力し、リセット信号DLLRESETをDLL回路22に出力する。

【0027】

モードレジスタ15は、モード設定タイミングに合わせてDRAMの動作モードを設定する。リフレッシュ制御回路16は、リフレッシュタイミングに応じてロウデコーダ18からリフレッシュアドレスを発生するようにロウデコーダ18を制御する。

【0028】

カラムデコーダ17は、カラムアドレスをメモリセルアレイ19に出力し、ロウデコーダ18は、ロウアドレスをメモリセルアレイ19に出力し、メモリセルアレイ19は、カラムアドレスとロウアドレスとに対応するメモリセルにアクセスする。

【0029】

クロック入力回路20は、外部からクロック信号CK、/CKを入力してバッファリングし、クロック信号ICLKをアドレスラッチ回路12、コマンドデコード回路14、タイミングジェネレータ21およびDLL回路22に出力する。タイミングジェネレータ21は、クロック信号ICLKに同期した各種タイミング信号を必要に応じて各部に分配し、各タイミング信号が半導体装置内を伝送する其々のタイミングを制御する。DLL回路22は、クロック信号ICLK、リセット信号DLLRESETを入力し、クロック信号ICLKの位相を調整したクロック信号LCLKをFIFO回路23および入出力回路24に出力する。

【0030】

FIFO回路23は、メモリセルアレイ19と入出力回路24間にあって入出力データをバッファリングする。入出力回路24は、DQ端子から入力されたライトデータをFIFO回路23に出力し、また、FIFO回路23から入力されたリードデータをDQ端子に出力する。この場合、クロック信号LCLKの位相は、クロック信号LCLKに同期してDQ端子から出力されるデータ信号が外部のクロック信号CKと同期するように調整される。

【0031】

内部電源発生回路25は、外部から電源VDD、VSSを供給されて、内部の電源電圧を発生する。

【0032】

ヒューズ回路26は、DLL回路22のロック機能を有効にするか否かを決定する設定用の回路であり、半導体装置の仕様、例えば、クロック信号CK、/CKの周波数が所定の値以上か否かに応じて設定される。すなわち、DLL回路22のロック機能が、例えば、半導体装置が高速動作品(1.6GHz)として利用される場合においては位相差検出回路の機能が無効とされ、低速動作品(800MHz)として利用される場合においては該機能が有効とされるように設定が可能である。

【0033】

次に、DLL回路の構成について説明する。図2は、本発明の第1の実施例に係るDLL回路の構成を示すブロック図である。図2において、DLL回路22は、遅延回路31、レプリカ回路32、DLL更新タイミング発生回路33、位相比較回路34、カウント回路35、位相差検出回路36、ロック検出回路37を備える。

【0034】

遅延回路31は、クロック信号ICLKに対し、カウント回路35が出力するコード信号Code_A〜Nに対応した遅延を与えてクロック信号LCLKとしてFIFO回路23、入出力回路24、およびレプリカ回路32に出力する。

【0035】

レプリカ回路32は、入出力回路24においてデータ出力のタイミングを外部クロックに合せるために入出力回路24における遅延時間と実質的に同等である遅延時間をクロック信号LCLKに与え、クロック信号RCLKとして位相比較回路34および位相差検出回路36に出力する。

【0036】

DLL更新タイミング発生回路33は、クロック信号ICLKからカウント回路35におけるカウントタイミングを定める信号Count_timingを生成してカウント回路35に出力する。なお、信号DLL_LOCKが活性状態にある場合には、信号Count_timingのカウント回路35への出力を停止する。

【0037】

位相比較回路34は、クロック信号ICLKとクロック信号RCLKとの位相を比較し、比較結果を示す信号Compをカウント回路35に出力する。なお、信号DLL_LOCKが活性状態にある場合には、位相比較を行うことなく、信号Compのカウント回路35への出力を停止する。

【0038】

カウント回路35は、信号Count_Enableの活性状態において、信号Count_timingのタイミングに従って信号Compをカウントし、カウント値をコード信号Code_A〜Nとして遅延回路31に出力する。すなわち、クロック信号ICLKの位相がクロック信号RCLKの位相より進んでいるか、遅れているかの検知結果を用いて、カウント回路35のカウント値が更新(+カウント/−カウント)され、遅延回路31の遅延段数が変化(遅延量増/遅延量減)する。そして、コード信号Code_A〜Nが例えば「+++−+」のように振動したことを検知してDLL回路の調整を終了する。なお、信号DLL_LOCKが活性状態にある場合には、信号Count_timing、Compが入力されないので、カウント動作を停止する。

【0039】

位相差検出回路36は、クロック信号ICLKとクロック信号RCLKとの位相差を検出し、位相差が所定の不感帯幅より大きな場合に、信号Count_Enableを活性状態としてカウント回路35およびロック検出回路37に出力する。なお、不感帯幅が無効となるようにヒューズ回路26が設定されている場合、位相差検出回路36は、位相差の如何に係らず信号Count_Enableを活性状態とする。

【0040】

ロック検出回路37は、信号DLLRESETが活性化されるとリセットされ、信号Count_Enableが非活性状態となった場合に、DLL_LOCKを活性状態としてDLL更新タイミング発生回路33、位相比較回路34に出力する。

【0041】

次に、位相差検出回路36について説明する。図3は、本発明の第1の実施例に係る位相差検出回路の構成を示すブロック図である。位相差検出回路36は、遅延回路41、42、位相差比較器43、44、カウント制御回路45を備える。

【0042】

遅延回路41は、クロック信号ICLKを遅延し、位相差比較器43の一方の入力端(+)に出力する。遅延回路42は、クロック信号RCLKを遅延し、位相差比較器44の一方の入力端(−)に出力する。位相差比較器43は、他方の入力端(−)にクロック信号RCLKを入力し、クロック信号ICLKを遅延した信号との位相差を比較し、比較結果を表す信号OUT_Aをカウント制御回路45に出力する。位相差比較器44は、他方の入力端(+)にクロック信号ICLKを入力し、クロック信号RCLKを遅延した信号との位相差を比較し、比較結果を表す信号OUT_Bをカウント制御回路45に出力する。カウント制御回路45は、信号OUT_A、OUT_Bからクロック信号ICLK、RCLKの位相差が所定の値未満であるか否かを表す信号Count_Enableを出力する。

【0043】

ここで遅延回路41、42では、例えば其々150psの遅延量が調整されているとする。つまり、遅延量を調整し、位相差が150ps以内に入った場合、又は当初から位相差が150ps以内の場合に、信号Count_Enableを非活性状態とする。

【0044】

位相差比較器43は、「クロック信号ICLK+150psの遅延」と「クロック信号RCLK」との位相比較を行い、位相差比較器44は、「クロック信号ICLK」と「クロック信号RCLK+150psの遅延」との位相比較を行う。

【0045】

クロック信号ICLKがクロック信号RCLKに対して150ps以上進んでいれば、位相差比較器41、42の出力は、共にHレベルとなり、クロック信号RCLKがクロック信号ICLKに対して150ps以上進んでいれば、位相差比較器41、42の出力は、共にLレベルとなる。この場合、カウント制御回路45は、図4に示すように信号Count_EnableをHレベルとして出力する。

【0046】

また、クロック信号ICLK、RCLKの差が150ps以内の場合には、位相差比較器41、42の其々の出力は、Lレベル、Hレベルとなる。この場合、カウント制御回路45は、図4に示すように信号Count_EnableをLレベルとして出力する。このようにカウント制御回路45は、信号OUT_A、OUT_Bに対して排他的論理和の機能を果たす。

【0047】

次に、DLL回路の動作について説明する。図5は、本発明の第1の実施例に係るDLL回路の各部の動作波形を示す図である。図5における各タイミングでは、以下のように動作する。

タイミングt1:クロック信号ICLK、RCLKの位相差が不感帯値nよりも大きい(不感帯外に存在する)ためカウント回路35が更新される。

タイミングt2:同じく更新される。

タイミングt3:クロック信号ICLK、RCLKの位相差が不感帯値nよりも小さくなった(不感帯内に存在する)ため、信号Count_EnableがLレベルとなり信号DLL_LOCKが活性化(Hレベル)とされ、カウント回路35は更新されない。

タイミングt4:デバイスの温度等の状態変化によって位相差が不感帯値nよりも大きくなり信号Count_EnableがHレベルとなる。しかし、信号DLL_LOCKが活性化状態であるためカウント回路35は更新されない。

タイミングt5:信号DLLRESETによってLOCKが解除され、位相差が不感帯値nよりも大きいためにカウント回路35が更新される。

【0048】

図6は、クロック信号ICLK、RCLKの波形の拡大図である。ここでは、ロック状態であってもその位相差範囲内を遅延回路31で更に細かく調整可能であるという点を示している。例えば、DLL回路22をロックさせる位相差をn=150ps、遅延回路31に含まれる遅延素子1段分の調整幅を30psとすることが出来る。

【0049】

本実施例のDLL回路22は、高速動作品(1.6GHz≒周期0.6ns)の半導体装置においては、クロック信号ICLK、RCLKの位相差が例えば150ps以内(位相差検出回路36の抽出範囲、不感帯)でも動作させる。一方、低速動作品(800MHz≒周期1.3ns)の半導体装置においては、そういった操作を行わない。後者における150psの割合は12%程度であり動作上許容されうるが、前者における割合は25%程度であり動作上許容出来ないためである。勿論、この値150psは図3における遅延回路41の遅延量を調整することで任意に変更可能である。即ち、DLL回路22は、潜在的には30psでの調整が可能ではあるが、低速動作品(800MHz)の半導体装置においては、微調整を行うことで発生する電力消費の増大を防ぐように、敢えて微調整を行わないように設定される。

【実施例2】

【0050】

図7は、本発明の第2の実施例に係るDLL回路の構成を示すブロック図である。図7において、図2と同一の符号は、同一物を表し、その説明を省略する。位相差検出回路36aは、図2の位相差検出回路36に対し、さらにイニシャルシーケンスを表す信号INITを入力する。

【0051】

DLL回路の動作タイミングを、イニシャルシーケンス(電源投入後の最初の調整)と、その後の調整(半導体装置動作中の微調整)とに分け、信号INITが活性状態(Hレベル)となるイニシャルシーケンス時には、実施例1で説明した不感帯内に入っても位相調整を停止せずに高精度にロック動作を行う。また、信号INITが非活性状態(Lレベル)となった、その後の他の調整においては、第1の実施例と同様の動作を行うものである。このように、最初に高精度にあわせ込んでいることから、その後の温度変化等によって多少の位相差が発生したとしても不感帯内に収まり、その結果、他の調整を省くことが可能となる。

【0052】

次に、DLL回路の動作について説明する。図8は、本発明の第2の実施例に係るDLL回路の各部の動作波形を示す図である。図5ではタイミングt3でカウント回路35を停止していたが、図8では、イニシャルシーケンスを表す信号INITによって信号Count_EnableをHに固定することで不感帯を無効とする。イニシャルシーケンス以外の期間においては、図2と同様に不感帯に基づいて動作する。

【0053】

すなわち、イニシャルシーケンスを表す信号INITが活性状態(Hレベル)にある場合、信号Count_Enableが活性状態(Hレベル)とされ、不感帯内に位相が調整された後も調整を継続し、ロック状態に至る。ロック状態では、先に述べたようにコード信号Code_A〜Nが例えば「+++−+」のように振動した状態とされる。

【0054】

本実施例のDLL回路は、イニシャル時のロックを高精度とし、イニシャル時以降では、位相差検出回路36が、クロック信号ICLK、RCLKの位相差が例えば150ps以上であることを検出しない限り、再調整を行わないように動作する。

【0055】

なお、前述の特許文献等の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0056】

11 アドレス入力回路

12 アドレスラッチ回路

13 コマンド入力回路

14 コマンドデコード回路

15 モードレジスタ

16 リフレッシュ制御回路

17 カラムデコーダ

18 ロウデコーダ

19 メモリセルアレイ

20 クロック入力回路

21 タイミングジェネレータ

22 DLL回路

23 FIFO回路

24 入出力回路

25 内部電源発生回路

26 ヒューズ回路

31、41、42 遅延回路

32 レプリカ回路

33 DLL更新タイミング発生回路

34 位相比較回路

35 カウント回路

36、36a 位相差検出回路

37 ロック検出回路

43、44 位相差比較器

45 カウント制御回路

【特許請求の範囲】

【請求項1】

第1のクロック信号を受け、前記第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号を出力する遅延回路と、

前記第2のクロック信号を受け、遅延された第3のクロック信号を出力するレプリカ回路と、

前記第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、前記所定時間以上である場合には前記遅延回路の遅延量を変化させ、前記所定時間未満である場合には前記遅延回路の遅延量を変化させないように制御する位相差検出回路と、

を備えることを特徴とする半導体装置。

【請求項2】

前記第3のクロック信号の位相が前記第1のクロック信号の位相よりも進んでいるか否かを検知する位相比較回路を更に備え、

前記位相差検出回路は、前記第1および第3のクロック信号の位相差が前記所定時間以上である場合には前記位相比較回路の検出結果を有効として前記遅延回路の遅延量を変化させ、前記第1および第3のクロック信号の位相差が前記所定時間未満である場合には前記位相比較回路の検出結果を無効として前記遅延回路の遅延量を変化させないことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記位相差検出回路の動作モードを設定するヒューズ回路を備え、

前記ヒューズ回路に第1のデータが書き込まれている時に、前記位相差検出回路は、前記第1および第3のクロック信号の位相差が前記所定時間以上であるか否かに関わらず前記位相比較回路の検出結果を有効として前記遅延回路の遅延量を変化させ、第2のデータが書き込まれている時に、前記位相差検出回路は、前記第1および第3のクロック信号の位相差が前記所定時間以上である場合には前記遅延回路の遅延量を変化させ、前記第1および第3のクロック信号の位相差が前記所定時間未満である場合には前記位相比較回路の検出結果を無効として前記遅延回路の遅延量を変化させない制御を行うことを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記遅延回路の遅延量を前記位相比較回路からの検出結果信号に応じて変化させるコード信号を出力するカウント回路を更に備え、

前記位相差検出回路は、前記第1および第3のクロック信号の位相差が前記所定時間以上である場合には前記位相比較回路の検知結果を有効として前記カウント回路の前記コード信号を更新し、前記第1および第3のクロック信号の位相差が前記所定時間未満である場合には前記位相比較回路の検出結果を無効として前記カウント回路の前記コード信号を更新しないことを特徴とする請求項2に記載の半導体装置。

【請求項5】

前記位相差検出回路は、前記半導体自身の電源立ち上がり時の所定期間において活性化されるイニシャルシーケンス信号を受け、前記イニシャルシーケンス信号が活性状態を示す期間において、前記第1および第3のクロック信号の位相差が前記所定時間以上であるか否かに関わらず前記位相比較回路の検出結果を有効として前記遅延回路の遅延量を変化させ、前記イニシャルシーケンス信号が非活性状態を示す期間において、前記第1および第3のクロック信号の位相差が前記所定時間以上である場合には前記遅延回路の遅延量を変化させ、前記第1および第3のクロック信号の位相差が前記所定時間未満である場合には前記位相比較回路の検出結果を無効として前記遅延回路の遅延量を変化させないように制御することを特徴とする請求項2に記載の半導体装置。

【請求項6】

前記位相差検出回路は、

前記第1のクロック信号を遅延する第2の遅延回路と、

前記第3のクロック信号を遅延する第3の遅延回路と、

前記第2の遅延回路の出力信号と前記第3のクロック信号との位相差を比較する第1の位相差比較器と、

前記第3の遅延回路の出力信号と前記第1のクロック信号との位相差を比較する第2の位相差比較器と、

前記第1および第2の位相差比較器における位相差比較結果に基づいて前記第1および第3のクロック信号の位相差が前記所定時間以上であるか否かを判断するカウント制御回路と、

を備えることを特徴とする請求項1乃至5のいずれか一に記載の半導体装置。

【請求項1】

第1のクロック信号を受け、前記第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号を出力する遅延回路と、

前記第2のクロック信号を受け、遅延された第3のクロック信号を出力するレプリカ回路と、

前記第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、前記所定時間以上である場合には前記遅延回路の遅延量を変化させ、前記所定時間未満である場合には前記遅延回路の遅延量を変化させないように制御する位相差検出回路と、

を備えることを特徴とする半導体装置。

【請求項2】

前記第3のクロック信号の位相が前記第1のクロック信号の位相よりも進んでいるか否かを検知する位相比較回路を更に備え、

前記位相差検出回路は、前記第1および第3のクロック信号の位相差が前記所定時間以上である場合には前記位相比較回路の検出結果を有効として前記遅延回路の遅延量を変化させ、前記第1および第3のクロック信号の位相差が前記所定時間未満である場合には前記位相比較回路の検出結果を無効として前記遅延回路の遅延量を変化させないことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記位相差検出回路の動作モードを設定するヒューズ回路を備え、

前記ヒューズ回路に第1のデータが書き込まれている時に、前記位相差検出回路は、前記第1および第3のクロック信号の位相差が前記所定時間以上であるか否かに関わらず前記位相比較回路の検出結果を有効として前記遅延回路の遅延量を変化させ、第2のデータが書き込まれている時に、前記位相差検出回路は、前記第1および第3のクロック信号の位相差が前記所定時間以上である場合には前記遅延回路の遅延量を変化させ、前記第1および第3のクロック信号の位相差が前記所定時間未満である場合には前記位相比較回路の検出結果を無効として前記遅延回路の遅延量を変化させない制御を行うことを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記遅延回路の遅延量を前記位相比較回路からの検出結果信号に応じて変化させるコード信号を出力するカウント回路を更に備え、

前記位相差検出回路は、前記第1および第3のクロック信号の位相差が前記所定時間以上である場合には前記位相比較回路の検知結果を有効として前記カウント回路の前記コード信号を更新し、前記第1および第3のクロック信号の位相差が前記所定時間未満である場合には前記位相比較回路の検出結果を無効として前記カウント回路の前記コード信号を更新しないことを特徴とする請求項2に記載の半導体装置。

【請求項5】

前記位相差検出回路は、前記半導体自身の電源立ち上がり時の所定期間において活性化されるイニシャルシーケンス信号を受け、前記イニシャルシーケンス信号が活性状態を示す期間において、前記第1および第3のクロック信号の位相差が前記所定時間以上であるか否かに関わらず前記位相比較回路の検出結果を有効として前記遅延回路の遅延量を変化させ、前記イニシャルシーケンス信号が非活性状態を示す期間において、前記第1および第3のクロック信号の位相差が前記所定時間以上である場合には前記遅延回路の遅延量を変化させ、前記第1および第3のクロック信号の位相差が前記所定時間未満である場合には前記位相比較回路の検出結果を無効として前記遅延回路の遅延量を変化させないように制御することを特徴とする請求項2に記載の半導体装置。

【請求項6】

前記位相差検出回路は、

前記第1のクロック信号を遅延する第2の遅延回路と、

前記第3のクロック信号を遅延する第3の遅延回路と、

前記第2の遅延回路の出力信号と前記第3のクロック信号との位相差を比較する第1の位相差比較器と、

前記第3の遅延回路の出力信号と前記第1のクロック信号との位相差を比較する第2の位相差比較器と、

前記第1および第2の位相差比較器における位相差比較結果に基づいて前記第1および第3のクロック信号の位相差が前記所定時間以上であるか否かを判断するカウント制御回路と、

を備えることを特徴とする請求項1乃至5のいずれか一に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−31128(P2013−31128A)

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願番号】特願2011−167526(P2011−167526)

【出願日】平成23年7月29日(2011.7.29)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願日】平成23年7月29日(2011.7.29)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]