半導体装置

【課題】インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

半導体装置の微細化及び高速化に伴い、半導体装置の配線構造の多層化が進んでいる。半導体装置の微細化、高速化及び多層化が進むことにより、配線抵抗の増大及び配線間、配線層間の寄生容量の増大による信号伝播遅延が問題となる。信号伝播遅延を抑制するために、低誘電率の絶縁膜が層間絶縁膜として用いられている。

【0003】

インダクタの周囲に金属を配置する場合、インダクタと金属との距離が近いと、インダクタの磁力線を打ち消す方向に磁力線が発生するように、渦電流が金属に流れることによりインダクタのインダクタ性能(Q値)が低下する。そのため、インダクタを有する半導体装置においては、インダクタの下方の層間絶縁膜には金属を配置しない構造を採用している。

【0004】

金属が配置されていない層間絶縁膜には水が浸入しやすい。層間絶縁膜に水が浸入すると、層間絶縁膜(バリアメタル)が酸化され、Viaとの密着性が弱くなり、結果、ストレス

マイグレーション(S−MIG)のようなボイドが発生することによって抵抗値が上昇し、最悪オープン不良となる。そのため、半導体装置の配線形成工程において、層間絶縁膜に浸入した水を蒸発させる加熱処理(Bake処理)が行われている。しかし、Bake処理は、層間絶縁膜を傷つけるため、層間絶縁膜の径時破壊(TDDB)等の信頼性上の問題を誘発する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2005−286264号公報

【特許文献2】特開2002−141415号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

インダクタの下方の層間絶縁膜をリングによって囲むことにより、層間絶縁膜への水の浸入を抑制する技術がある。インダクタの下方の層間絶縁膜を囲むリングの形状によっては、インダクタ性能(インダクタのQ値)が低下する場合がある。本件は、インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制することを目的とする。

【課題を解決するための手段】

【0007】

本件の一観点による半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

【発明の効果】

【0008】

本件によれば、インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制することが可能となる。

【図面の簡単な説明】

【0009】

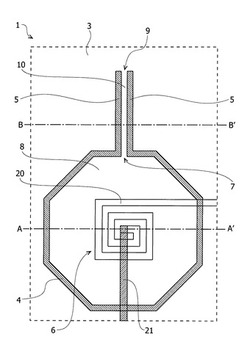

【図1】図1は、実施例1に係る半導体装置1の上面図である。

【図2】図2は、図1の一点鎖線A−A’における半導体装置1の断面図である。

【図3】図3は、図1の一点鎖線B−B’における半導体装置1の断面図である。

【図4】図4は、層間絶縁膜3及び導電体11及び12の形成工程の説明図である。

【図5】図5は、層間絶縁膜3及び導電体11及び12の形成工程の説明図である。

【図6】図6は、層間絶縁膜3及び導電体11及び12の形成工程の説明図である。

【図7】図7は、層間絶縁膜3及び導電体11及び12の形成工程の説明図である。

【図8】図8は、インダクタ6のQ値の変化の説明図である。

【図9】図9は、開口7を有していない金属壁4を半導体基板2上に設けた場合の半導体装置1の上面図である。

【図10】図10は、開口7を有する金属壁4を半導体基板2上に設けた場合の半導体装置1の上面図である。

【図11】図11は、開口7を有する金属壁4を半導体基板2上に設け、金属壁4を囲むように金属壁5を半導体基板2上に設けた場合の半導体装置1の上面図である。

【図12】図12は、実施例1に係る半導体装置1の上面図である。

【図13】図13は、実施例2に係る半導体装置1の上面図である。

【図14】図14は、図13の一点鎖線C−C’における半導体装置1の断面図である。

【図15】図15は、実施例2に係る半導体装置1の上面図である。

【図16】図16は、実施例2に係る半導体装置1の上面図である。

【発明を実施するための形態】

【0010】

以下、図面を参照して、発明を実施するための形態(以下、実施形態という)に係る半導体装置について実施例を挙げて説明する。以下の実施例の構成は例示であり、本実施形態は実施例の構成に限定されない。

【実施例1】

【0011】

実施例1に係る半導体装置1を図1から図3に示す。図1は、実施例1に係る半導体装置1の上面図である。図2は、図1の一点鎖線A−A’における半導体装置1の断面図である。図3は、図1の一点鎖線B−B’における半導体装置1の断面図である。

【0012】

図1から図3に示すように、半導体装置1は、半導体基板2と、半導体基板2上に設けられた層間絶縁膜3及び金属壁4、5と、層間絶縁膜3の上部に設けられたインダクタ6とを備える。半導体基板2は、例えば、シリコン(Si)基板である。層間絶縁膜3は、例えば、SiO2膜である。層間絶縁膜3として、例えば、LK(low-k)膜やELK(extreme low-k)膜を用いてもよい。層間絶縁膜3は積層化されている。層間絶縁膜3の形成については後述する。

【0013】

図1及び図2に示すように、金属壁4は、インダクタ6の下方の層間絶縁膜3を半導体基板2の平面方向で囲むようにして、半導体基板2上に設けられている。半導体基板2の平面方向は、層間絶縁膜3の積層方向(厚さ方向)と直交する方向である。すなわち、金属壁4は、層間絶縁膜3の積層方向(厚さ方向)に延在するように半導体基板2上に設けられ、インダクタ6の下方の層間絶縁膜3を囲んでいる。図1に示す金属壁4は、八角形の形状であるが、金属壁4の形状はこれに限定されない。金属壁4の形状は円形、楕円形等のリング形状であってもよいし、三角形、四角形等の多角形状であってもよい。

【0014】

図1に示すように、金属壁4は、金属壁4の両端部を非接触の状態とする開口7を有している。金属壁4に開口7を設けることにより、金属壁4の両端部が接触しない状態となり、金属壁4に渦電流が発生することが抑制される。図1に示すように、一対の金属壁5は金属壁4の両端部にそれぞれの一端が連結されており、金属壁4の外側の層間絶縁膜3を半導体基板2の平面方向で挟むようにして、半導体基板2上に設けられている。すなわち、一対の金属壁5が、層間絶縁膜3の積層方向(厚さ方向)に延在するように半導体基板2上に設けられ、金属壁4の外側の層間絶縁膜3を挟んでいる。そして、各金属壁5の一端が金属壁4の両端部に連結されている。図1に示すように、一対の金属壁5は、金属壁4で囲まれた領域8の外側の位置に開口9を有している。すなわち、金属壁5の開口9は、金属壁4の開口7と比較して、金属壁4で囲まれた領域8から離れた位置に設けられている。

【0015】

金属壁4の開口7を介して、金属壁4で囲まれた領域8の層間絶縁膜3と一対の金属壁5で挟まれた領域10の層間絶縁膜3とが接触している。すなわち、金属壁4で囲まれた領域8と一対の金属壁5で挟まれた領域10とは、金属壁4の開口7を介して繋がっている。また、金属壁5の開口9を介して、一対の金属壁5で挟まれた領域10の層間絶縁膜3と一対の金属壁5で挟まれた領域10の外側の層間絶縁膜3とが接触している。すなわち、一対の金属壁5で挟まれた領域10と一対の金属壁5で挟まれた領域10の外側の領域とは、金属壁5の開口9を介して繋がっている。

【0016】

金属壁4、5は、導電体11及び12を有する。導電体11及び12は、例えば、銅であるが、他の金属であってもよい。インダクタ6は、スパイラル形状の配線20と、直線形状の配線21と、ビア22とを有する。図1には、スパイラル形状のインダクタ6を例示しているが、インダクタ6は他の形状であってもよい。配線20は、層間絶縁膜3上に形成され、配線21は、層間絶縁膜3の上部に形成されている。ビア22は、配線20と配線21とを電気的に接続している。

【0017】

配線20の一方の端部は、ビア22を介して配線21と接続されており、配線20の他方の端部は、外部回路(図示せず)の端子等と接続されている。配線21の一方の端部は、ビア22を介して配線20と接続されており、配線21の他方の端部は、外部回路(図示せず)と接続されている。

【0018】

ここで、図4から図7を参照して、層間絶縁膜3、導電体11及び12の形成について説明する。図4の(A)に示すように、例えば、Chemical Vapor Deposition(CVD、

化学気相成長)法によって、半導体基板2上に層間絶縁膜3を形成する。次に、図4の(B)に示すように、例えば、スピンコート法により、層間絶縁膜3の上にレジスト膜を塗布した後、フォトリソグラフィによりレジスト膜をパターニングすることにより、層間絶縁膜3の上にレジストパターン30を形成する。その後、図4の(C)に示すように、レジストパターン30をマスクとして層間絶縁膜3を異方性エッチングすることにより、層間絶縁膜3に溝31を形成する。層間絶縁膜3に溝31を形成した後、アッシング処理によりレジストパターン30を除去する。

【0019】

次いで、層間絶縁膜3上及び溝31内にバリアメタルを形成する。バリアメタルは、例えば、Ti、TiN、W、WN、Ta、TaN等である。バリアメタルは、例えば、スパッタリング法又はCVD法により形成してもよい。次に、図5の(A)に示すように、層間絶縁膜3上及び溝31内に銅(Cu)膜32を形成する。銅膜32は、例えば、電解めっき法により形成してもよい。その後、図5の(B)に示すように、Chemical Mechanical Polishing(CMP、化学機械研磨)により、層間絶縁膜3上の銅膜32を研磨するこ

とで半導体基板2上に導電体11を形成する。

【0020】

次いで、図5の(C)に示すように、CVD法によって、層間絶縁膜3及び導電体11上に層間絶縁膜3を形成することにより層間絶縁膜3を多層化する。次に、図6の(A)に示すように、例えば、スピンコート法により、層間絶縁膜3の上にレジスト膜を塗布した後、フォトリソグラフィによりレジスト膜をパターニングすることにより、層間絶縁膜3の上にレジストパターン33を形成する。その後、図6の(B)に示すように、レジストパターン33をマスクとして層間絶縁膜3を異方性エッチングすることにより、層間絶縁膜3に溝34を形成する。層間絶縁膜3に溝34を形成した後、アッシング処理によりレジストパターン33を除去する。

【0021】

次いで、層間絶縁膜3上及び溝34内にバリアメタルを形成する。バリアメタルは、例えば、Ti、TiN、W、WN、Ta、TaN等である。バリアメタルは、例えば、スパッタリング法又はCVD法により形成してもよい。次に、図6の(C)に示すように、層間絶縁膜3上及び溝34内に銅(Cu)膜35を形成する。銅膜35は、例えば、電解めっき法により形成してもよい。その後、図7に示すように、CMPにより、層間絶縁膜3上の銅膜35を研磨することで導電体11上に導電体12を形成する。そして、図4から図7で説明した工程を繰り返して、導電体11及び12を複数形成することにより、図1から図3に示すように、金属壁4及5を形成する。

【0022】

なお、図4から図7においては、金属壁4を形成する工程を説明しているが、金属壁5を形成する工程も金属壁4を形成する工程と並行して行われる。金属壁5を形成する工程は、金属壁4を形成する工程と同様であるのでその説明を省略する。導電体11及び12は、例えば、配線及びビアを形成する工程と並行して行われる。具体的には、導電体11は配線を形成する工程と並行して行われ、導電体12はビアを形成する工程と並行して行われる。

【0023】

実施例1においては、図1に示すように、金属壁4の開口7の周辺に一対の金属壁5が設けられている。したがって、金属壁4の開口7の周辺に一対の金属壁5が設けられていない場合と比較して、外部から金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入が抑制される。金属壁4の開口7の周辺に一対の金属壁5が設けられていない場合、金属壁4で囲まれた領域8の外側の層間絶縁膜3に含まれている水が、金属壁4の開口7を介して金属壁4で囲まれた領域8の層間絶縁膜3に浸入し易い。一方、金属壁4の開口7の周辺に一対の金属壁5が設けられている場合、金属壁5の開口9を介して水が一対の金属壁5で挟まれた領域10の層間絶縁膜3に浸入する。金属壁5の開口9を介して外部から浸入する水が、一対の金属壁5で挟まれた領域10の層間絶縁膜3に溜まることにより、金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入が抑制される。金属壁4で囲まれた領域8の外側の位置に金属壁5の開口9を設けることにより、外部から金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入を抑制することができる。この結果、半導体装置1の耐湿性を向上させることができる。

【0024】

実施例1においては、図1に示すように、金属壁4は開口7を有しているため、金属壁4の両端部が接触していない。また、金属壁5は開口9を有しているため、金属壁5は2つに分割された状態で金属壁4に連結されている。したがって、金属壁4に開口7が設けられている場合、金属壁4に開口7が設けられていない場合と比較して、金属壁4に渦電流が発生することが抑制される。

【0025】

金属壁4の形状と、インダクタ6のQ値の変化との関係を図8から図11を用いて説明する。Q値とは、インダクタ性能を示す係数の一つであり、Q値が高いほど、損失が小さく高効率である。図8は、インダクタ6のQ値の変化の説明図であり、縦軸はインダクタ6のQ値を示し、横軸はインダクタ6を流れる電流の周波数(GHz)を示している。

【0026】

図8の実線Oは、半導体基板2上に金属壁4を設けていない場合のインダクタ6のQ値の変化を示している。図8の点線Aは、図9に示す半導体装置1が有するインダクタ6のQ値の変化を示している。図9は、開口7を有していない金属壁4を半導体基板2上に設けた場合の半導体装置1の上面図である。図8の点線Bは、図10に示す半導体装置1が有するインダクタ6のQ値の変化を示している。図10は、開口7を有する金属壁4を半導体基板2上に設けた場合の半導体装置1の上面図である。図8の一点鎖線Cは、図11に示す半導体装置1が有するインダクタ6のQ値の変化を示している。図11は、開口7を有する金属壁4を半導体基板2上に設け、金属壁4を囲むように金属壁5を半導体基板2上に設けた場合の半導体装置1の上面図である。なお、図11の金属壁5は、金属壁4とは連結されていない。

【0027】

図9に示す半導体装置1の場合、半導体基板2上に金属壁4を設けていない場合と比較して、インダクタ6のQ値は、全体的に低下する(図8の実線O及び点線A)。図9に示すように、半導体基板2上に設けられた金属壁4は開口7を有していないため、金属壁4に渦電流が発生し、インダクタ6のQ値が全体的に低下する。

【0028】

図10に示す半導体装置1の場合、半導体基板2上に金属壁4を設けていない場合と比較して、インダクタ6のQ値の低下はほとんどない(図8の実線O及び点線B)。図10に示すように、半導体基板2上に設けられた金属壁4は開口7を有するため、金属壁4に渦電流が発生することが抑制され、インダクタ6のQ値はほとんど低下していない。

【0029】

図11に示す半導体装置1の場合、半導体基板2上に金属壁4を設けていない場合と比較して、15GHz以上の高周波数において、インダクタ6のQ値が急激に低下する(図8の実線O及び一点鎖線C)。図11に示すように、金属壁4を囲むように金属壁5が設けられているため、15GHz以上の高周波数において、インダクタ6のQ値が急激に低下する。

【0030】

図10に示す半導体装置1の場合、インダクタ6のQ値の低下は少ない。しかし、上述したように、金属壁4の開口7の周辺に一対の金属壁5が設けられていない場合、金属壁4で囲まれた領域8の外側の層間絶縁膜3に含まれている水が、金属壁4の開口7を介して金属壁4で囲まれた領域8の層間絶縁膜3に浸入し易い。実施例1では、図1に示すように、金属壁4の開口7の周辺に一対の金属壁5が設けられているため、金属壁4の開口7の周辺に一対の金属壁5が設けられていない場合と比較して、外部から金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入が抑制される。実施例1では、図1に示すように、半導体基板2上に設けられた金属壁4は開口7を有するため、金属壁4に渦電流が発生することが抑制され、インダクタ6のQ値(インダクタ性能)の低下を抑制することができる。実施例1では、図1に示すように、一対の金属壁5は、金属壁4を囲むように設けられていないため、15GHz以上の高周波数においても、インダクタ6のQ値の低下を抑制することができる。

【0031】

図12は、実施例1に係る半導体装置1の上面図であり、図1に示した半導体装置1と比較して、一対の金属壁5が折れ曲がっている。すなわち、一対の金属壁5は折れ曲った平面形状を有している。各金属壁5は、互いに同方向に直角に折れ曲った折曲部を有して半導体基板2上に設けられている。図12では、一対の金属壁5は複数回折れ曲がっているが、一対の金属壁5を一回折れ曲がるようにしてもよい。図12では、一対の金属壁5を直角に折り曲げているが、一対の金属壁5を曲線状に折り曲げるようにしてもよい。折れ曲がった一対の金属壁5を半導体基板2上に設けることにより、層間絶縁膜3に対する水の浸透性を抑制することができ、一対の金属壁5で挟まれた領域10の層間絶縁膜3に水がより溜まり易くなる。したがって、折れ曲がった一対の金属壁5を半導体基板2上に設けることにより、外部から金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入をよ

り抑制することができる。

【実施例2】

【0032】

実施例2に係る半導体装置1を図13及び図14に示す。なお、実施例1と同一の構成要素については、実施例1と同一の符号を付し、その説明を省略する。図13は、実施例2に係る半導体装置1の上面図である。図14は、図13の一点鎖線C−C’における半導体装置1の断面図である。図13及び図14に示すように、半導体装置1は、半導体基板2と、半導体基板2上に設けられた層間絶縁膜3及び金属壁4、5、40と、層間絶縁膜3の上部に設けられたインダクタ6とを備える。金属壁40は、導電体11及び12を有する。導電体11及び12は、例えば、銅であるが、他の金属であってもよい。なお、金属壁40を形成する工程は、金属壁4及び5を形成する工程と並行して行われる。金属壁40を形成する工程は、金属壁4を形成する工程と同様である。

【0033】

図13及び図14に示すように、金属壁4は、インダクタ6の下方の層間絶縁膜3を半導体基板2の平面方向で囲むようにして、半導体基板2上に設けられている。図13に示す金属壁4は八角形の形状であるが、金属壁4の形状はこれに限定されない。金属壁4の形状は円、楕円等のリング形状であってもよいし、三角形、四角形等の多角形状であってもよい。

【0034】

図13に示すように、金属壁4は、金属壁4の両端部を非接触の状態とする開口7を有している。金属壁4に開口7を設けることにより、金属壁4の両端部が接触しない状態となり、金属壁4に渦電流が発生することが抑制される。実施例2では、図13に示すように、半導体基板2上に設けられた金属壁4は開口7を有するため、金属壁4に渦電流が発生することが抑制され、インダクタ6のQ値(インダクタ性能)の低下を抑制することができる。

【0035】

図13に示すように、一対の金属壁5は金属壁4の両端部にそれぞれの一端が連結されており、金属壁4の外側の層間絶縁膜3を半導体基板2の平面方向で挟むようにして、半導体基板2上に設けられている。また、図13に示すように、各金属壁5は互いに反対方向に直角に折れ曲がった折曲部を有して半導体基板2上に設けられ、金属壁5の折れ曲がった箇所、すなわち各折曲部の基端間に開口9を有している。図13に示すように、一対の金属壁5は、金属壁4で囲まれた領域8の外側の位置に開口9を有している。すなわち、金属壁5の開口9は、金属壁4の開口7と比較して、金属壁4で囲まれた領域8から離れた位置に設けられている。

【0036】

図13に示すように、金属壁40は、金属壁5の開口9と対向するように半導体基板2上に設けられている。金属壁40は、層間絶縁膜3の積層方向(厚さ方向)に延在するように半導体基板2上に設けられている。図13に示すように、金属壁40は、金属壁5の開口9及び前記一対の折曲部を囲むようにして折れ曲がった平面形状を有する。

【0037】

金属壁4の開口7を介して、金属壁4で囲まれた領域8の層間絶縁膜3と一対の金属壁5で挟まれた領域10の層間絶縁膜3とが接触している。すなわち、金属壁4で囲まれた領域8と一対の金属壁5で挟まれた領域10とは、金属壁4の開口7を介して繋がっている。また、金属壁5の開口9を介して、一対の金属壁5で挟まれた領域10の層間絶縁膜3と金属壁5及び40で挟まれた領域41の層間絶縁膜3とが接触している。すなわち、一対の金属壁5で挟まれた領域10と金属壁5及び40で挟まれた領域41とは、金属壁5の開口9を介して繋がっている。

【0038】

図13に示すように、金属壁4と金属壁40との間には開口42が設けられている。開口42を介して、金属壁4及び40で挟まれた領域43の層間絶縁膜3と金属壁4及び4

0で挟まれた領域43の外側の領域の層間絶縁膜3とが接触している。すなわち、金属壁4及び40で挟まれた領域43と金属壁4及び40で挟まれた領域43の外側の領域とは、開口42を介して繋がっている。

【0039】

金属壁5の開口9と対向するように金属壁40を半導体基板2上に設けることにより、一対の金属壁5で挟まれた領域10の層間絶縁膜3への水の浸入を抑制することができる。金属壁5の開口9を囲むようにして、金属壁40を折り曲げて半導体基板2上に設けることにより、一対の金属壁5で挟まれた領域10の層間絶縁膜3への水の浸入をより抑制することができる。

【0040】

図15は、実施例2に係る半導体装置1の上面図である。図15に示す半導体装置1は、図13に示した半導体装置1と比較して、一対の金属壁5を半導体基板2の平面方向に伸ばすことにより、金属壁5の開口9の位置と金属壁4の開口7の位置とを離すようにしている。一対の金属壁5を半導体基板2の平面方向に伸ばすことにより、金属壁5の開口9を介して外部から浸入する水が、金属壁4で囲まれた領域8の層間絶縁膜3まで浸透することが抑制される。すなわち、金属壁5の開口9を介して外部から浸入する水が、一対の金属壁5で挟まれた領域10の層間絶縁膜3により溜まることにより、金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入が抑制される。半導体基板2の平面方向における金属壁5の長さは、任意の値に設定することが可能である。

【0041】

図15に示すように、金属壁5と金属壁40との間には開口44が設けられている。開口44を介して、金属壁5及び40で挟まれた領域41の層間絶縁膜3と金属壁5及び40で挟まれた領域41の外側の領域の層間絶縁膜3とが接触している。すなわち、金属壁5及び40で挟まれた領域41と金属壁4及び40で挟まれた領域41の外側の領域とは、開口44を介して繋がっている。

【0042】

図16は、実施例2に係る半導体装置1の上面図である。図13に示した半導体装置1は、一対の金属壁5を折り曲げて金属壁4に連結させて、金属壁5を半導体基板2上に設けている。図16に示すように、一対の金属壁5を折り曲げずに、各金属壁5の一端を金属壁4に連結させて、金属壁5を半導体基板2上に設けてもよい。また、図13に示した半導体装置1は、金属壁40を折り曲げて、金属壁40を半導体基板2上に設けている。図16に示すように、金属壁40を折り曲げずに、金属壁5の開口9と対向するように金属壁40を半導体基板2上に設けてもよい。金属壁5の開口9と対向するように金属壁40を半導体基板2上に設けることにより、一対の金属壁5で挟まれた領域10の層間絶縁膜3への水の浸入を抑制することができる。

【0043】

図16に示した半導体装置1において、一対の金属壁5を折り曲げて金属壁4に連結させて、金属壁5を半導体基板2上に設けるようにしてもよい。この場合、一対の金属壁5を直角に折り曲げるようにしてもよいし、一対の金属壁5を曲線状に折り曲げるようにしてもよい。また、図16に示した半導体装置1において、金属壁40を、金属壁5の開口9を囲むようにして折り曲げて、金属壁40を半導体基板2上に設けるようにしてもよい。

【0044】

実施例1及び2における金属壁4、5及び40の高さは任意の値を設定することができる。例えば、金属壁4、5及び40の高さと、層間絶縁膜3の高さとを一致させてもよい。すなわち、金属壁4、5及び40を、層間絶縁膜3の上部(上面又は上面近辺)まで形成するようにしてもよい。

【符号の説明】

【0045】

1 半導体装置

2 半導体基板

3 層間絶縁膜

4、5、40 金属壁

6 インダクタ

7、9、42、44 開口

8、10、41、43 領域

11、12 導電体

20、21 配線

22 ビア

30、33 レジストパターン

31、34 溝

32、35 銅膜

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

半導体装置の微細化及び高速化に伴い、半導体装置の配線構造の多層化が進んでいる。半導体装置の微細化、高速化及び多層化が進むことにより、配線抵抗の増大及び配線間、配線層間の寄生容量の増大による信号伝播遅延が問題となる。信号伝播遅延を抑制するために、低誘電率の絶縁膜が層間絶縁膜として用いられている。

【0003】

インダクタの周囲に金属を配置する場合、インダクタと金属との距離が近いと、インダクタの磁力線を打ち消す方向に磁力線が発生するように、渦電流が金属に流れることによりインダクタのインダクタ性能(Q値)が低下する。そのため、インダクタを有する半導体装置においては、インダクタの下方の層間絶縁膜には金属を配置しない構造を採用している。

【0004】

金属が配置されていない層間絶縁膜には水が浸入しやすい。層間絶縁膜に水が浸入すると、層間絶縁膜(バリアメタル)が酸化され、Viaとの密着性が弱くなり、結果、ストレス

マイグレーション(S−MIG)のようなボイドが発生することによって抵抗値が上昇し、最悪オープン不良となる。そのため、半導体装置の配線形成工程において、層間絶縁膜に浸入した水を蒸発させる加熱処理(Bake処理)が行われている。しかし、Bake処理は、層間絶縁膜を傷つけるため、層間絶縁膜の径時破壊(TDDB)等の信頼性上の問題を誘発する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2005−286264号公報

【特許文献2】特開2002−141415号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

インダクタの下方の層間絶縁膜をリングによって囲むことにより、層間絶縁膜への水の浸入を抑制する技術がある。インダクタの下方の層間絶縁膜を囲むリングの形状によっては、インダクタ性能(インダクタのQ値)が低下する場合がある。本件は、インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制することを目的とする。

【課題を解決するための手段】

【0007】

本件の一観点による半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

【発明の効果】

【0008】

本件によれば、インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制することが可能となる。

【図面の簡単な説明】

【0009】

【図1】図1は、実施例1に係る半導体装置1の上面図である。

【図2】図2は、図1の一点鎖線A−A’における半導体装置1の断面図である。

【図3】図3は、図1の一点鎖線B−B’における半導体装置1の断面図である。

【図4】図4は、層間絶縁膜3及び導電体11及び12の形成工程の説明図である。

【図5】図5は、層間絶縁膜3及び導電体11及び12の形成工程の説明図である。

【図6】図6は、層間絶縁膜3及び導電体11及び12の形成工程の説明図である。

【図7】図7は、層間絶縁膜3及び導電体11及び12の形成工程の説明図である。

【図8】図8は、インダクタ6のQ値の変化の説明図である。

【図9】図9は、開口7を有していない金属壁4を半導体基板2上に設けた場合の半導体装置1の上面図である。

【図10】図10は、開口7を有する金属壁4を半導体基板2上に設けた場合の半導体装置1の上面図である。

【図11】図11は、開口7を有する金属壁4を半導体基板2上に設け、金属壁4を囲むように金属壁5を半導体基板2上に設けた場合の半導体装置1の上面図である。

【図12】図12は、実施例1に係る半導体装置1の上面図である。

【図13】図13は、実施例2に係る半導体装置1の上面図である。

【図14】図14は、図13の一点鎖線C−C’における半導体装置1の断面図である。

【図15】図15は、実施例2に係る半導体装置1の上面図である。

【図16】図16は、実施例2に係る半導体装置1の上面図である。

【発明を実施するための形態】

【0010】

以下、図面を参照して、発明を実施するための形態(以下、実施形態という)に係る半導体装置について実施例を挙げて説明する。以下の実施例の構成は例示であり、本実施形態は実施例の構成に限定されない。

【実施例1】

【0011】

実施例1に係る半導体装置1を図1から図3に示す。図1は、実施例1に係る半導体装置1の上面図である。図2は、図1の一点鎖線A−A’における半導体装置1の断面図である。図3は、図1の一点鎖線B−B’における半導体装置1の断面図である。

【0012】

図1から図3に示すように、半導体装置1は、半導体基板2と、半導体基板2上に設けられた層間絶縁膜3及び金属壁4、5と、層間絶縁膜3の上部に設けられたインダクタ6とを備える。半導体基板2は、例えば、シリコン(Si)基板である。層間絶縁膜3は、例えば、SiO2膜である。層間絶縁膜3として、例えば、LK(low-k)膜やELK(extreme low-k)膜を用いてもよい。層間絶縁膜3は積層化されている。層間絶縁膜3の形成については後述する。

【0013】

図1及び図2に示すように、金属壁4は、インダクタ6の下方の層間絶縁膜3を半導体基板2の平面方向で囲むようにして、半導体基板2上に設けられている。半導体基板2の平面方向は、層間絶縁膜3の積層方向(厚さ方向)と直交する方向である。すなわち、金属壁4は、層間絶縁膜3の積層方向(厚さ方向)に延在するように半導体基板2上に設けられ、インダクタ6の下方の層間絶縁膜3を囲んでいる。図1に示す金属壁4は、八角形の形状であるが、金属壁4の形状はこれに限定されない。金属壁4の形状は円形、楕円形等のリング形状であってもよいし、三角形、四角形等の多角形状であってもよい。

【0014】

図1に示すように、金属壁4は、金属壁4の両端部を非接触の状態とする開口7を有している。金属壁4に開口7を設けることにより、金属壁4の両端部が接触しない状態となり、金属壁4に渦電流が発生することが抑制される。図1に示すように、一対の金属壁5は金属壁4の両端部にそれぞれの一端が連結されており、金属壁4の外側の層間絶縁膜3を半導体基板2の平面方向で挟むようにして、半導体基板2上に設けられている。すなわち、一対の金属壁5が、層間絶縁膜3の積層方向(厚さ方向)に延在するように半導体基板2上に設けられ、金属壁4の外側の層間絶縁膜3を挟んでいる。そして、各金属壁5の一端が金属壁4の両端部に連結されている。図1に示すように、一対の金属壁5は、金属壁4で囲まれた領域8の外側の位置に開口9を有している。すなわち、金属壁5の開口9は、金属壁4の開口7と比較して、金属壁4で囲まれた領域8から離れた位置に設けられている。

【0015】

金属壁4の開口7を介して、金属壁4で囲まれた領域8の層間絶縁膜3と一対の金属壁5で挟まれた領域10の層間絶縁膜3とが接触している。すなわち、金属壁4で囲まれた領域8と一対の金属壁5で挟まれた領域10とは、金属壁4の開口7を介して繋がっている。また、金属壁5の開口9を介して、一対の金属壁5で挟まれた領域10の層間絶縁膜3と一対の金属壁5で挟まれた領域10の外側の層間絶縁膜3とが接触している。すなわち、一対の金属壁5で挟まれた領域10と一対の金属壁5で挟まれた領域10の外側の領域とは、金属壁5の開口9を介して繋がっている。

【0016】

金属壁4、5は、導電体11及び12を有する。導電体11及び12は、例えば、銅であるが、他の金属であってもよい。インダクタ6は、スパイラル形状の配線20と、直線形状の配線21と、ビア22とを有する。図1には、スパイラル形状のインダクタ6を例示しているが、インダクタ6は他の形状であってもよい。配線20は、層間絶縁膜3上に形成され、配線21は、層間絶縁膜3の上部に形成されている。ビア22は、配線20と配線21とを電気的に接続している。

【0017】

配線20の一方の端部は、ビア22を介して配線21と接続されており、配線20の他方の端部は、外部回路(図示せず)の端子等と接続されている。配線21の一方の端部は、ビア22を介して配線20と接続されており、配線21の他方の端部は、外部回路(図示せず)と接続されている。

【0018】

ここで、図4から図7を参照して、層間絶縁膜3、導電体11及び12の形成について説明する。図4の(A)に示すように、例えば、Chemical Vapor Deposition(CVD、

化学気相成長)法によって、半導体基板2上に層間絶縁膜3を形成する。次に、図4の(B)に示すように、例えば、スピンコート法により、層間絶縁膜3の上にレジスト膜を塗布した後、フォトリソグラフィによりレジスト膜をパターニングすることにより、層間絶縁膜3の上にレジストパターン30を形成する。その後、図4の(C)に示すように、レジストパターン30をマスクとして層間絶縁膜3を異方性エッチングすることにより、層間絶縁膜3に溝31を形成する。層間絶縁膜3に溝31を形成した後、アッシング処理によりレジストパターン30を除去する。

【0019】

次いで、層間絶縁膜3上及び溝31内にバリアメタルを形成する。バリアメタルは、例えば、Ti、TiN、W、WN、Ta、TaN等である。バリアメタルは、例えば、スパッタリング法又はCVD法により形成してもよい。次に、図5の(A)に示すように、層間絶縁膜3上及び溝31内に銅(Cu)膜32を形成する。銅膜32は、例えば、電解めっき法により形成してもよい。その後、図5の(B)に示すように、Chemical Mechanical Polishing(CMP、化学機械研磨)により、層間絶縁膜3上の銅膜32を研磨するこ

とで半導体基板2上に導電体11を形成する。

【0020】

次いで、図5の(C)に示すように、CVD法によって、層間絶縁膜3及び導電体11上に層間絶縁膜3を形成することにより層間絶縁膜3を多層化する。次に、図6の(A)に示すように、例えば、スピンコート法により、層間絶縁膜3の上にレジスト膜を塗布した後、フォトリソグラフィによりレジスト膜をパターニングすることにより、層間絶縁膜3の上にレジストパターン33を形成する。その後、図6の(B)に示すように、レジストパターン33をマスクとして層間絶縁膜3を異方性エッチングすることにより、層間絶縁膜3に溝34を形成する。層間絶縁膜3に溝34を形成した後、アッシング処理によりレジストパターン33を除去する。

【0021】

次いで、層間絶縁膜3上及び溝34内にバリアメタルを形成する。バリアメタルは、例えば、Ti、TiN、W、WN、Ta、TaN等である。バリアメタルは、例えば、スパッタリング法又はCVD法により形成してもよい。次に、図6の(C)に示すように、層間絶縁膜3上及び溝34内に銅(Cu)膜35を形成する。銅膜35は、例えば、電解めっき法により形成してもよい。その後、図7に示すように、CMPにより、層間絶縁膜3上の銅膜35を研磨することで導電体11上に導電体12を形成する。そして、図4から図7で説明した工程を繰り返して、導電体11及び12を複数形成することにより、図1から図3に示すように、金属壁4及5を形成する。

【0022】

なお、図4から図7においては、金属壁4を形成する工程を説明しているが、金属壁5を形成する工程も金属壁4を形成する工程と並行して行われる。金属壁5を形成する工程は、金属壁4を形成する工程と同様であるのでその説明を省略する。導電体11及び12は、例えば、配線及びビアを形成する工程と並行して行われる。具体的には、導電体11は配線を形成する工程と並行して行われ、導電体12はビアを形成する工程と並行して行われる。

【0023】

実施例1においては、図1に示すように、金属壁4の開口7の周辺に一対の金属壁5が設けられている。したがって、金属壁4の開口7の周辺に一対の金属壁5が設けられていない場合と比較して、外部から金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入が抑制される。金属壁4の開口7の周辺に一対の金属壁5が設けられていない場合、金属壁4で囲まれた領域8の外側の層間絶縁膜3に含まれている水が、金属壁4の開口7を介して金属壁4で囲まれた領域8の層間絶縁膜3に浸入し易い。一方、金属壁4の開口7の周辺に一対の金属壁5が設けられている場合、金属壁5の開口9を介して水が一対の金属壁5で挟まれた領域10の層間絶縁膜3に浸入する。金属壁5の開口9を介して外部から浸入する水が、一対の金属壁5で挟まれた領域10の層間絶縁膜3に溜まることにより、金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入が抑制される。金属壁4で囲まれた領域8の外側の位置に金属壁5の開口9を設けることにより、外部から金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入を抑制することができる。この結果、半導体装置1の耐湿性を向上させることができる。

【0024】

実施例1においては、図1に示すように、金属壁4は開口7を有しているため、金属壁4の両端部が接触していない。また、金属壁5は開口9を有しているため、金属壁5は2つに分割された状態で金属壁4に連結されている。したがって、金属壁4に開口7が設けられている場合、金属壁4に開口7が設けられていない場合と比較して、金属壁4に渦電流が発生することが抑制される。

【0025】

金属壁4の形状と、インダクタ6のQ値の変化との関係を図8から図11を用いて説明する。Q値とは、インダクタ性能を示す係数の一つであり、Q値が高いほど、損失が小さく高効率である。図8は、インダクタ6のQ値の変化の説明図であり、縦軸はインダクタ6のQ値を示し、横軸はインダクタ6を流れる電流の周波数(GHz)を示している。

【0026】

図8の実線Oは、半導体基板2上に金属壁4を設けていない場合のインダクタ6のQ値の変化を示している。図8の点線Aは、図9に示す半導体装置1が有するインダクタ6のQ値の変化を示している。図9は、開口7を有していない金属壁4を半導体基板2上に設けた場合の半導体装置1の上面図である。図8の点線Bは、図10に示す半導体装置1が有するインダクタ6のQ値の変化を示している。図10は、開口7を有する金属壁4を半導体基板2上に設けた場合の半導体装置1の上面図である。図8の一点鎖線Cは、図11に示す半導体装置1が有するインダクタ6のQ値の変化を示している。図11は、開口7を有する金属壁4を半導体基板2上に設け、金属壁4を囲むように金属壁5を半導体基板2上に設けた場合の半導体装置1の上面図である。なお、図11の金属壁5は、金属壁4とは連結されていない。

【0027】

図9に示す半導体装置1の場合、半導体基板2上に金属壁4を設けていない場合と比較して、インダクタ6のQ値は、全体的に低下する(図8の実線O及び点線A)。図9に示すように、半導体基板2上に設けられた金属壁4は開口7を有していないため、金属壁4に渦電流が発生し、インダクタ6のQ値が全体的に低下する。

【0028】

図10に示す半導体装置1の場合、半導体基板2上に金属壁4を設けていない場合と比較して、インダクタ6のQ値の低下はほとんどない(図8の実線O及び点線B)。図10に示すように、半導体基板2上に設けられた金属壁4は開口7を有するため、金属壁4に渦電流が発生することが抑制され、インダクタ6のQ値はほとんど低下していない。

【0029】

図11に示す半導体装置1の場合、半導体基板2上に金属壁4を設けていない場合と比較して、15GHz以上の高周波数において、インダクタ6のQ値が急激に低下する(図8の実線O及び一点鎖線C)。図11に示すように、金属壁4を囲むように金属壁5が設けられているため、15GHz以上の高周波数において、インダクタ6のQ値が急激に低下する。

【0030】

図10に示す半導体装置1の場合、インダクタ6のQ値の低下は少ない。しかし、上述したように、金属壁4の開口7の周辺に一対の金属壁5が設けられていない場合、金属壁4で囲まれた領域8の外側の層間絶縁膜3に含まれている水が、金属壁4の開口7を介して金属壁4で囲まれた領域8の層間絶縁膜3に浸入し易い。実施例1では、図1に示すように、金属壁4の開口7の周辺に一対の金属壁5が設けられているため、金属壁4の開口7の周辺に一対の金属壁5が設けられていない場合と比較して、外部から金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入が抑制される。実施例1では、図1に示すように、半導体基板2上に設けられた金属壁4は開口7を有するため、金属壁4に渦電流が発生することが抑制され、インダクタ6のQ値(インダクタ性能)の低下を抑制することができる。実施例1では、図1に示すように、一対の金属壁5は、金属壁4を囲むように設けられていないため、15GHz以上の高周波数においても、インダクタ6のQ値の低下を抑制することができる。

【0031】

図12は、実施例1に係る半導体装置1の上面図であり、図1に示した半導体装置1と比較して、一対の金属壁5が折れ曲がっている。すなわち、一対の金属壁5は折れ曲った平面形状を有している。各金属壁5は、互いに同方向に直角に折れ曲った折曲部を有して半導体基板2上に設けられている。図12では、一対の金属壁5は複数回折れ曲がっているが、一対の金属壁5を一回折れ曲がるようにしてもよい。図12では、一対の金属壁5を直角に折り曲げているが、一対の金属壁5を曲線状に折り曲げるようにしてもよい。折れ曲がった一対の金属壁5を半導体基板2上に設けることにより、層間絶縁膜3に対する水の浸透性を抑制することができ、一対の金属壁5で挟まれた領域10の層間絶縁膜3に水がより溜まり易くなる。したがって、折れ曲がった一対の金属壁5を半導体基板2上に設けることにより、外部から金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入をよ

り抑制することができる。

【実施例2】

【0032】

実施例2に係る半導体装置1を図13及び図14に示す。なお、実施例1と同一の構成要素については、実施例1と同一の符号を付し、その説明を省略する。図13は、実施例2に係る半導体装置1の上面図である。図14は、図13の一点鎖線C−C’における半導体装置1の断面図である。図13及び図14に示すように、半導体装置1は、半導体基板2と、半導体基板2上に設けられた層間絶縁膜3及び金属壁4、5、40と、層間絶縁膜3の上部に設けられたインダクタ6とを備える。金属壁40は、導電体11及び12を有する。導電体11及び12は、例えば、銅であるが、他の金属であってもよい。なお、金属壁40を形成する工程は、金属壁4及び5を形成する工程と並行して行われる。金属壁40を形成する工程は、金属壁4を形成する工程と同様である。

【0033】

図13及び図14に示すように、金属壁4は、インダクタ6の下方の層間絶縁膜3を半導体基板2の平面方向で囲むようにして、半導体基板2上に設けられている。図13に示す金属壁4は八角形の形状であるが、金属壁4の形状はこれに限定されない。金属壁4の形状は円、楕円等のリング形状であってもよいし、三角形、四角形等の多角形状であってもよい。

【0034】

図13に示すように、金属壁4は、金属壁4の両端部を非接触の状態とする開口7を有している。金属壁4に開口7を設けることにより、金属壁4の両端部が接触しない状態となり、金属壁4に渦電流が発生することが抑制される。実施例2では、図13に示すように、半導体基板2上に設けられた金属壁4は開口7を有するため、金属壁4に渦電流が発生することが抑制され、インダクタ6のQ値(インダクタ性能)の低下を抑制することができる。

【0035】

図13に示すように、一対の金属壁5は金属壁4の両端部にそれぞれの一端が連結されており、金属壁4の外側の層間絶縁膜3を半導体基板2の平面方向で挟むようにして、半導体基板2上に設けられている。また、図13に示すように、各金属壁5は互いに反対方向に直角に折れ曲がった折曲部を有して半導体基板2上に設けられ、金属壁5の折れ曲がった箇所、すなわち各折曲部の基端間に開口9を有している。図13に示すように、一対の金属壁5は、金属壁4で囲まれた領域8の外側の位置に開口9を有している。すなわち、金属壁5の開口9は、金属壁4の開口7と比較して、金属壁4で囲まれた領域8から離れた位置に設けられている。

【0036】

図13に示すように、金属壁40は、金属壁5の開口9と対向するように半導体基板2上に設けられている。金属壁40は、層間絶縁膜3の積層方向(厚さ方向)に延在するように半導体基板2上に設けられている。図13に示すように、金属壁40は、金属壁5の開口9及び前記一対の折曲部を囲むようにして折れ曲がった平面形状を有する。

【0037】

金属壁4の開口7を介して、金属壁4で囲まれた領域8の層間絶縁膜3と一対の金属壁5で挟まれた領域10の層間絶縁膜3とが接触している。すなわち、金属壁4で囲まれた領域8と一対の金属壁5で挟まれた領域10とは、金属壁4の開口7を介して繋がっている。また、金属壁5の開口9を介して、一対の金属壁5で挟まれた領域10の層間絶縁膜3と金属壁5及び40で挟まれた領域41の層間絶縁膜3とが接触している。すなわち、一対の金属壁5で挟まれた領域10と金属壁5及び40で挟まれた領域41とは、金属壁5の開口9を介して繋がっている。

【0038】

図13に示すように、金属壁4と金属壁40との間には開口42が設けられている。開口42を介して、金属壁4及び40で挟まれた領域43の層間絶縁膜3と金属壁4及び4

0で挟まれた領域43の外側の領域の層間絶縁膜3とが接触している。すなわち、金属壁4及び40で挟まれた領域43と金属壁4及び40で挟まれた領域43の外側の領域とは、開口42を介して繋がっている。

【0039】

金属壁5の開口9と対向するように金属壁40を半導体基板2上に設けることにより、一対の金属壁5で挟まれた領域10の層間絶縁膜3への水の浸入を抑制することができる。金属壁5の開口9を囲むようにして、金属壁40を折り曲げて半導体基板2上に設けることにより、一対の金属壁5で挟まれた領域10の層間絶縁膜3への水の浸入をより抑制することができる。

【0040】

図15は、実施例2に係る半導体装置1の上面図である。図15に示す半導体装置1は、図13に示した半導体装置1と比較して、一対の金属壁5を半導体基板2の平面方向に伸ばすことにより、金属壁5の開口9の位置と金属壁4の開口7の位置とを離すようにしている。一対の金属壁5を半導体基板2の平面方向に伸ばすことにより、金属壁5の開口9を介して外部から浸入する水が、金属壁4で囲まれた領域8の層間絶縁膜3まで浸透することが抑制される。すなわち、金属壁5の開口9を介して外部から浸入する水が、一対の金属壁5で挟まれた領域10の層間絶縁膜3により溜まることにより、金属壁4で囲まれた領域8の層間絶縁膜3への水の浸入が抑制される。半導体基板2の平面方向における金属壁5の長さは、任意の値に設定することが可能である。

【0041】

図15に示すように、金属壁5と金属壁40との間には開口44が設けられている。開口44を介して、金属壁5及び40で挟まれた領域41の層間絶縁膜3と金属壁5及び40で挟まれた領域41の外側の領域の層間絶縁膜3とが接触している。すなわち、金属壁5及び40で挟まれた領域41と金属壁4及び40で挟まれた領域41の外側の領域とは、開口44を介して繋がっている。

【0042】

図16は、実施例2に係る半導体装置1の上面図である。図13に示した半導体装置1は、一対の金属壁5を折り曲げて金属壁4に連結させて、金属壁5を半導体基板2上に設けている。図16に示すように、一対の金属壁5を折り曲げずに、各金属壁5の一端を金属壁4に連結させて、金属壁5を半導体基板2上に設けてもよい。また、図13に示した半導体装置1は、金属壁40を折り曲げて、金属壁40を半導体基板2上に設けている。図16に示すように、金属壁40を折り曲げずに、金属壁5の開口9と対向するように金属壁40を半導体基板2上に設けてもよい。金属壁5の開口9と対向するように金属壁40を半導体基板2上に設けることにより、一対の金属壁5で挟まれた領域10の層間絶縁膜3への水の浸入を抑制することができる。

【0043】

図16に示した半導体装置1において、一対の金属壁5を折り曲げて金属壁4に連結させて、金属壁5を半導体基板2上に設けるようにしてもよい。この場合、一対の金属壁5を直角に折り曲げるようにしてもよいし、一対の金属壁5を曲線状に折り曲げるようにしてもよい。また、図16に示した半導体装置1において、金属壁40を、金属壁5の開口9を囲むようにして折り曲げて、金属壁40を半導体基板2上に設けるようにしてもよい。

【0044】

実施例1及び2における金属壁4、5及び40の高さは任意の値を設定することができる。例えば、金属壁4、5及び40の高さと、層間絶縁膜3の高さとを一致させてもよい。すなわち、金属壁4、5及び40を、層間絶縁膜3の上部(上面又は上面近辺)まで形成するようにしてもよい。

【符号の説明】

【0045】

1 半導体装置

2 半導体基板

3 層間絶縁膜

4、5、40 金属壁

6 インダクタ

7、9、42、44 開口

8、10、41、43 領域

11、12 導電体

20、21 配線

22 ビア

30、33 レジストパターン

31、34 溝

32、35 銅膜

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上に設けられた層間絶縁膜と、

前記層間絶縁膜の上部に設けられたインダクタと、

前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、

前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、

を備え、

前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、

前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する、

ことを特徴とする半導体装置。

【請求項2】

前記第二の金属壁は折れ曲がった平面形状を有することを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第二の金属壁の開口と対向するように前記半導体基板上に設けられた第三の金属壁を備えることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記第三の金属壁は、前記第二の金属壁の開口を囲むようにして折れ曲がった平面形状を有することを特徴とする請求項3に記載の半導体装置。

【請求項1】

半導体基板と、

前記半導体基板上に設けられた層間絶縁膜と、

前記層間絶縁膜の上部に設けられたインダクタと、

前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、

前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、

を備え、

前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、

前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する、

ことを特徴とする半導体装置。

【請求項2】

前記第二の金属壁は折れ曲がった平面形状を有することを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第二の金属壁の開口と対向するように前記半導体基板上に設けられた第三の金属壁を備えることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記第三の金属壁は、前記第二の金属壁の開口を囲むようにして折れ曲がった平面形状を有することを特徴とする請求項3に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2013−38130(P2013−38130A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−171208(P2011−171208)

【出願日】平成23年8月4日(2011.8.4)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月4日(2011.8.4)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]