半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関し、DLL(Delay Lock Loop:遅延同期ループ)を備えた半導体装置に関する。

【背景技術】

【0002】

DLLでは、入力信号を入力する遅延時間可変型のディレイライン(遅延線)の出力信号を帰還させた信号と該入力信号の位相を比較し、位相比較結果に基づきディレイラインの遅延を調整し、出力信号と入力信号の位相が所望値となるように制御する。

【0003】

このDLLを搭載した半導体装置の一例として、DRAM(Dynamic Random Access Memory)デバイスの概要を図1を参照して説明する。特に制限されないが、図1のDRAMデバイスは8バンク構成のDDR(Double Data Rate:クロックの立ち上がりと立ち下がりの両エッジに同期してデータをやり取りする)SDRAM(Synchronous DRAM;クロック同期型DRAM)である。図1において、ロウデコーダ1−4は、ロウアドレスをデコードし選択されたワード線(不図示)を駆動する。センスアンプ1−2は、メモリセルアレイ1−1のビット線(不図示)に読み出されたデータを増幅し、リフレッシュ動作時にはリフレッシュアドレスで選択されたワード線のセルに接続するビット線に読み出されたセルデータを増幅して該セルへ書き戻す。カラムデコーダ1−3は、カラムアドレスをデコードし、選択されたYスイッチ(不図示)をオンとしてビット線を選択し、IO線(不図示)に接続する。コマンドデコーダ1−9は、チップセレクト信号/CS、ロウアドレスストローブ信号/RAS、カラムアドレスストローブ信号/CAS、ライトイネーブル信号/WE等を入力し、コマンドをデコードする(なお、信号名の/はLowでアクティブであることを示す)。カラムアドレスバッファ及びバーストカウンタ1−7は、コマンドデコーダ1−9からの制御信号を受けるコントロールロジック1−10の制御のもと、入力されたカラムアドレスから、バースト長分のアドレスを生成し、カラムデコーダ1−3に供給する。モードレジスタ1−5は、アドレス信号とバンク選択用(8バンクの中の1つを選択)の信号BA0、BA1、BA2を入力し、コントロールロジック1−10に制御信号を出力する。ロウアドレスバッファ及びリフレッシュカウンタ1−6のロウアドレスバッファは、入力されたロウアドレスを受けて、ロウデコーダ1−4に出力し、リフレッシュカウンタは、例えばリフレッシュコマンドが入力されると、コマンドデコーダ1−9でのデコード結果に基づき、コントロールロジック1−10からの制御信号に応答してカウントアップ動作し、カウント出力をリフレッシュアドレスとして出力する。なお、低電力動作時のセルフリフレッシュモードでは、例えば不図示の内部タイマーで規定されるリフレッシュサイクルでリフレッシュカウンタをカウントアップしリフレッシュアドレスとする。ロウアドレスバッファからのロウアドレスとリフレッシュカウンタからのリフレッシュアドレスはマルチプレクサ(不図示)に入力され、リフレッシュ時には、リフレッシュアドレスが選択され、それ以外は、ロウアドレスバッファからのロウアドレスを選択し、ロウデコーダ1−4に供給される。

【0004】

クロックジェネレータ1−14は、DRAMデバイスに供給される相補の外部クロックCK、/CKを受け、クロックイネーブル信号CKEがHighのとき、内部クロック信号を出力し、クロックイネーブル信号CKEがLowとなると、以降、内部クロック信号の供給を停止する。データコントロール回路1−8は、書き込みデータと読み出しデータの入出力を行う。ラッチ回路1−11は書き込みデータと読出しデータをラッチする。入出力バッファ1−13はデータ端子DQからのデータの入力と出力を行う。

【0005】

DLL1−12は、外部クロック信号CK、/CKに遅延同期した信号を生成し、入出力バッファ1−13に供給する。メモリセルアレイ1−1からの読み出しデータはラッチ回路1−11から入出力バッファ1−13に供給され、入出力バッファ1−13は、DLL1−12で外部クロックCKに同期したクロック信号の立ち上がりと立ち下がりのエッジを用いて、データ端子DQから読み出しデータをダブルデータレートで出力する。

【0006】

DQSは、データのライト(書き込み)、リード(読み出し)のタイミングを規定するデータストローブ信号であり、ライト動作時に、DRAM外部のコントローラ(不図示)側から入力される入力信号であり、リード動作時には、DRAMからコントローラ側に出力される出力信号(IO信号)である。外部クロックCK、/CKに同期し、DDR SDRAMでは、DQSの立ち上がりと立ち下がりの両エッジを基準としてデータ(DQ)の入出力が行われる。DQSは、リード動作時には、クロック信号CKの立ち上がりエッジに同期してDRAMから出力され、ライト動作時には、コントローラ(不図示)から、クロック信号CKの立ち上がりエッジから所定の位相遅延させて、DRAM側に入力される。ライト時には、DRAMのラッチ回路1−11は、コントローラ(不図示)から入力されるDQSのエッジのタイミングで、入出力バッファ1−13からのデータ(入出力バッファ1−13の入力バッファにDQ端子から入力された書き込みデータ)を取り込む。リード時には、コントローラ(不図示)等のレシーバは、DRAMのDQ端子から出力される読み出しデータを、DQSの両エッジ(立ち上がりエッジと立ち下がりエッジ)のタイミングで取り込む。

【0007】

DLL1−12において、入力された外部クロック信号(CK)をディレイラインで遅延させた信号を、さらに、入出力バッファ1−13の出力バッファ(出力回路)のレプリカ(Replica)(不図示)で遅延させたレプリカクロック信号(Repclk)と、外部クロック信号CKの位相を比較し、これらの位相が合うように、ディレイラインの遅延時間を可変させる。データ読み出し時、レプリカクロック信号(Repclk)と同位相のデータストローブ信号DQSを出力信号として外部(コントローラ等)に出力することができれば、当該DQSは外部クロック信号CKと同位相となる。

【0008】

図2に、DLLとその周辺回路(出力回路とレプリカ回路)の典型的な構成の一例を示す。図2に示すように、DRAM入力信号を入力するディレイライン100と、ディレイライン100の出力であるDLL出力信号を入力し、出力回路103の遅延時間Tを模した遅延T’を有するレプリカ回路104と、レプリカ回路104の出力信号であるレプリカクロック信号Repclkと、DLL入力信号(DRAM入力信号)を入力し両者の位相を比較する位相検出回路(PD:Phase Detector)105と、位相検出回路105での位相比較結果をディレイライン増減信号として入力するカウンタ回路102と、カウンタ回路102のカウント値をデコードしてディレイライン100の遅延時間を設定するデコーダ回路101を備えている。ディレイライン100は、単位遅延回路を複数段縦続形態に接続し、デコーダ回路101の出力に基づき、出力信号が取り出される段数が決定される(単位遅延回路の段数が増えれば、DLL出力信号の遅延時間は増大し、単位遅延回路の段数が減少すれば、DLL出力信号の遅延時間は減少する)。位相検出回路(PD)は、入力した2つの信号(Repclkと、DLL入力信号)の位相を比較し、どちらのエッジが時間的に進んでいるか(遅れているか)を検出するため、位相比較回路又は位相比較器とも呼ばれる。位相検出回路105での比較の結果、レプリカクロック信号Repclkの位相が、DRAM入力信号よりも遅れている場合、カウンタ回路102は、例えばカウンタダウンし、デコーダ回路101は、ディレイライン100の遅延時間を短縮させ、レプリカクロック信号Repclkの位相が、DRAM入力信号よりも進んでいる場合、カウンタ回路102は、例えばカウンタアップし、デコーダ回路101は、ディレイライン100の遅延時間を増加させる。

【0009】

ここで、DLLにおける位相の概念について、図3を参照して説明する。図3において、入力信号はDLLへの入力信号(外部クロック信号CK)、出力信号はDLLの出力信号である。図3には、未ロック状態のDLLにおける入出力信号の位相差が模式的に示されている。DLLは、ディレイラインの遅延時間を調整し、DLLの入力信号(図1の外部クロック信号CK)のエッジAと、DLLの出力信号(図2のレプリカクロック信号Repclk)のエッジBを合致させる。即ち、図3におけるc=b−a相当の時間、入力信号をディレイライン100で遅延させることで、入力信号のエッジAと、出力信号のエッジBをA=B(c=0)としている。c=0の状態を「ロック状態」という(あるいは「位相合致状態」ともいう)。

【0010】

図2において、レプリカ回路104の遅延(T’)は、出力回路103の固有遅延(T)を模しているため、一般的に、出力回路103と同一構成の回路をレプリカ回路104として搭載する。なお、出力回路103はDLL出力信号を受け、DLL出力信号のエッジに応答してDRAM出力信号(データ信号)を出力する。出力回路103とレプリカ回路104は、同一チップ内に設けられるため、半導体製造時のMOSFET(MOS電界効果トランジスタ)の閾値電圧(Vt)のばらつき等は同等である。よって、同一構造であれば、出力回路103とレプリカ回路104とは、同一の遅延時間であることが期待できる。また、出力回路103とレプリカ回路104において、閾値電圧(Vt)の温度特性は同等であるため、動作時の温度変化等によりMOSFETの閾値電圧(Vt)が変化した場合にも、出力回路103とレプリカ回路104において、同様に変化する。そのため、出力回路103とレプリカ回路104の遅延T、T’は同等と考えてよい。

【0011】

図2において、位相検出回路(PD)105は、DLL入力信号(DRAM入力信号)とレプリカクロック信号(Repclk)の位相の前後比較を行う。位相検出回路(PD)105の位相比較結果を「Rep位相前後情報」と呼ぶ場合もある。位相検出回路(PD)で得られた位相比較結果は、ディレイライン増減信号としてカウンタ回路102に送られる。レプリカクロック信号(Repclk)のエッジがDRAM入力信号(CK)のエッジよりも前の場合(レプリカクロック信号(Repclk)がDRAM入力信号(CK)よりも位相検出回路(PD)105に早く到達した場合)、カウンタ回路102のカウンタ値を増加させ、デコーダ回路101を介してディレイライン100の遅延段数を増加し、遅延時間を大とし、レプリカクロック信号(Repclk)がさらに遅延される。カウンタ回路102は、初期値(例えば零)を基準にカウントアップ/ダウンするアップダウンカウンタとして構成され、カウント値の正/負に応じて、遅延時間が基準(初期設定値)の遅延よりも長い/短い段数に位置する単位遅延回路の出力を選択する。なお、カウンタ回路102のカウント値のビット数、及び符号(コード)が、ディレイラインの複数の段数に対応し単位遅延の出力の1つを選択可能なコードとして構成されている場合、デコーダ回路は不用とされる。

【0012】

レプリカクロック信号(Repclk)のエッジがDLL入力信号(DRAM入力信号CK)のエッジよりも後の場合(したがって、RepclkがCKよりも遅くPDに到達した場合)、カウンタ回路102のカウンタ値を減少され、ディレイラインの遅延段の段数を減少し、Repclkのエッジを先行させる。

【0013】

上記一連の動作を継続することで、最終的に、図2のレプリカ回路104から出力されるレプリカクロック信号(Repclk)のエッジAがDRAM入力信号(CK)の位相の前後を横断し続ける状態に到達する。すなわち、図3において、c=0となり、エッジBがエッジAよりも位相が進む、又は遅れる状態を繰り返す。これが、前記ロック状態であり、Repclkの位相とCKの位相が合致するように、図2のディレイレイン100の遅延が調整された状態である。

【0014】

DLLのロック時において、レプリカ回路104から出力されるレプリカクロック信号(Repclk)と、DRAM入力信号(CK)間に発生する位相差を「ロック位相」(あるいは「ロック位相差」)という。Lock位相は、本来、0であることが望ましいが、回路形式・利用電圧等の条件により、一定量のシフトが発生する。そのため、一般的に、DLLのロックでは、ロック位相を考慮に入れ、本来ロック位相0が得られる値から、予め一定量のシフトを考慮して、ロックを行っている。

【0015】

なお、特許文献1には、位相検出回路を備えたDLLが開示されている(特許文献1の図2参照)。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2010−62937号公報

【発明の概要】

【発明が解決しようとする課題】

【0017】

以下、関連技術の分析を与える。

【0018】

位相検出回路(PD)において、当該位相検出回路(PD)を構成するMOSFETの閾値電圧(Vt)が変化すれば、位相検出回路(PD)の動作は変化する。位相検出回路(PD)動作の変化は、外部クロック信号CKとレプリカクロック信号(Repclk)の位相比較動作の変化として現れる。すなわち、サンプル(チップ)間に存在する閾値電圧(Vt)ばらつき(製造ばらつき)や、同一サンプル(同一チップ内)においても、動作温度等の変化により発生する閾値電圧(Vt)の変動に伴い、ロック位相(ロック時に、RepclkとCK間に発生する位相差)が変化する。閾値電圧(Vt)の変化に伴うロック位相の変化を以下に説明する。

【0019】

異なるサンプル(チップ)間で閾値電圧(Vt)が異なる。この場合、サンプル間でロック位相が異なる。

【0020】

同一サンプル(同一チップ内)であるが、動作温度により閾値電圧(Vt)が異なる。この場合、同一サンプルであるが、動作温度によって、ロック位相が変化する。

【0021】

図4は、DRAMデバイスにおける、ロック位相を示す図である。図4において、左側のY軸はロック位相を表している。白の四角(□)は位相検出回路(PD)の位相比較結果↑(アップ)、黒の菱型(◆)は位相検出回路(PD)の位相比較結果↓(ダウン)、右側のY軸=電流値、白の三角形(△)は電流を表している。

【0022】

X軸の1行目は温度であり、−5、110、25(一部条件のみ)℃。

【0023】

X軸の2行目は、位相検出回路(PD)の動作電圧(本例では1.1Vのみ)である。

【0024】

X軸の3行目は、入力信号リファレンスレベル(DRAM等の相補入力(相補クロックCK/CKB)を想定)している。

【0025】

入力VDD=1.3、1.5、1.7V、入力スイング=0.25Vにて、以下の分類となる。クロック波形のクロスポイント(相補クロック(CK、/CK)の立ち上がりと立ち下がりがクロスするポイント)として、

「低」は、CKと/CKBのクロスポイント=47.5[%]、

「普」は、CKと/CKBのクロスポイント=50.0[%](HighとLowの中央、Duty=50%の対称波形)、

「高」は、CKと/CKBのクロスポイント=52.5[%]。

【0026】

X軸の4行目は、電源電圧(VDD)、

X軸の5行目は、製造時の閾値電圧(Vt)

である。

【0027】

上記した区分けにて、温度・閾値電圧(Vt)変動に注目した場合、図3上のワーストケースとなる、丸で囲んだ1、2間のロック位相差は、50psである。他の状況にも、一様に、ロック位相差が存在することがわかる。このように、プロセス−閾値電圧(Vt)条件(P)、動作電圧条件(V)、温度条件(T)により、ロック位相にばらつきが見られる事がわかる。

【0028】

図4によれば、Lock位相は、PVT条件変動に伴い、例えば50ps程度の変動が起こり得る。以上のように、ロック位相の定常性は保たれていない。よって、サンプル・温度等の変位に伴い発生するロック位相の変動に対応し、補正するシステムの提案が求められている。

【0029】

また、近時の低電圧化の流れに伴い、上記の変動幅は、拡大していくものと考えられる。

【課題を解決するための手段】

【0030】

上記問題点の少なくとも1つを解決するため、本発明は概略以下の構成とされる(ただし以下に限定されない)。

【0031】

本発明によれば、DLLの位相検出回路を構成する複数のトランジスタのうち所定のトランジスタの閾値電圧を補正する補正回路を備えた半導体装置が提供される。

【発明の効果】

【0032】

本発明によれば、サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができる。

【図面の簡単な説明】

【0033】

【図1】DLLを備えた半導体装置の一例を示す図である。

【図2】DLLの構成の一例を示す図である。

【図3】未ロック状態のDLLにおける位相差を説明する図である。

【図4】PVT条件別のロック位相の変位を例示した図である。

【図5】本発明の一実施形態の構成を示す図である。

【図6】位相検出回路(PD)の構成を示す図である。

【図7】PDバックゲート電位変更回路の構成の一例を示す図である。

【発明を実施するための形態】

【0034】

本発明の課題を解決する技術思想(コンセプト)の代表的な一例は以下に示される。但し、本願の請求内容はこの技術思想に限られず、本願請求項に記載の内容であることは言うまでもない。いくつかの好ましい形態によれば、第1の信号と第2の信号の位相を比較する位相検出回路(105)と、前記位相検出回路(105)を構成する複数のトランジスタのうち所定のトランジスタの閾値電圧を補正する補正回路(例えば図5のPDバックゲート電位変更回路106)を備えている。位相検出回路(105)はDLLの入力信号と出力信号の位相を比較し、DLLのディレイラインの遅延時間を増減させるための信号を出力する。

【0035】

好ましい形態によれば、さらに、半導体装置内部の温度を検出するセンサ(図5の107)を備え、前記補正回路は、前記センサ(107)で検出された温度情報に基づき、前記位相検出回路を構成する前記所定のトランジスタの閾値電圧を補正する。あるいは、半導体装置毎又は半導体装置群単位(例えばウェハ単位、あるいはロット単位等)でのトランジスタの閾値電圧情報を記憶する記憶部(108)を備え、前記補正回路は、前記記憶部に記憶される前記半導体装置毎又は半導体装置群単位でのトランジスタの閾値電圧情報に基づき、前記位相検出回路を構成する前記所定のトランジスタの閾値電圧を補正する。

【0036】

好ましい形態によれば、前記補正回路が、前記位相検出回路(105)を構成する前記所定のトランジスタのバックゲートに与える電圧を生成する電圧源回路(図7の1064)を備え、前記センサからの前記温度情報、及び/又は、前記記憶部に記憶された前記トランジスタの閾値電圧情報に基づき、前記バックゲート電圧を可変に設定する。

【0037】

DLLの前記ディレイライン(100)から出力される前記信号に応答してデータ信号を出力端子に出力する出力バッファ回路(103)の遅延を模したレプリカ回路(104)を備え、前記ディレイライン(100)から出力された信号は、前記レプリカ回路(104)で遅延され、前記位相検出回路(105)に入力される。

【0038】

本発明によれば、温度及びサンプルの条件により、ダイナミックに位相検出回路のトランジスタの閾値電圧Vtを補正する。いくつかの好ましい形態(Preferred Modes)によれば、位相検出回路(PD)を構成するMOSトランジスタの閾値電圧(Vt)の変化の補正を行い、サンプル別、あるいは動作温度別に発生していたロック位相(ロック時にRepclkとCK間に発生する位相差)のばらつきを解消する。

【0039】

DLLは、レプリカクロック信号(Repclk)を用いて、外部クロックと位相比較し、ディレイラインの遅延時間をフィードバック制御する回路構成である。レプリカ回路の遅延が出力回路の遅延時間を模すこと(図2の遅延時間T=T’)で、ロック動作中にロック位相を読み取り、位相検出回路(PD)において、DLL入力信号の位相と、レプリカクロック信号(Repclk)の位相(どちらのエッジが時間的の前に位置するか)の前後を判断している。

【0040】

位相検出回路(PD)においては、前述したように、位相検出回路(PD)を構成するMOSFETの閾値電圧(Vt)に影響を受け、ロック位相が変化するという問題を持つが、本発明によれば、これを是正することができる。

【0041】

<実施形態>

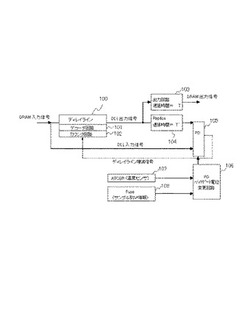

図5は、本発明の一実施形態を説明するための図である。図2の構成に対して、位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ(ATCSR(Auto Temperature Compensated Self Refresh:自動温度補償セルフリフレッシュ)107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備えている。温度センサ107の温度情報、ヒューズ(Fuse)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出される。

【0042】

図5において、ディレイライン100、デコーダ回路101、カウンタ回路102、出力回路103、レプリカ回路104は、図2の構成と同様である。すなわち、図1及び図2に示した構成に、さらに、図5の温度センサ107、サンプル別閾値電圧(Vt)情報を記憶するヒューズ(Fuse)108、PDバックゲート電位変更回路106を備えた構成が、この実施形態に係る半導体装置の一例となる。なお、図5のFuse(ヒューズ)108は、ROM(Read Only Memory)等他の任意の不揮発性記憶装置であってもよいことは勿論である。なお、ヒューズ(Fuse)108等にはデバイス製造時(例えばウエハテスト時、あるいは製品出荷時等)に、サンプル別閾値電圧(Vt)情報が設定される。以下では、本実施形態において、図1について共通部分の説明の重複は回避する。

【0043】

特に制限されないが、本実施形態では、ATCSRが温度センサ107として用いられている。ATCSRは、DRAM製品に搭載される温度センサの一種であり、DRAMデバイス内部に組み込まれた温度センサで検出された周囲温度情報に応じて自動的にリフレッシュ間隔を変更する。DRAMの場合、例えばモバイル用途等の低電圧動作品、DDR3以降の高速動作品においてATCSR機能の搭載が一般化しつつある。なお、ATCSRを具備している低電圧動作品・高速動作品に、本発明を適用する場合、新たに温度計を搭載する必要はなく、ATCSRの組み込み温度センサから出力される温度情報を利用すればよい。また特に制限されないが、ATCSR機能により読み出された情報は、温度レジスタ等にデジタル情報として設定される。なお、図5の温度センサ107として、ダイオード素子等(PN接合素子)を半導体装置内に組み込み、ダイオード素子に定電流を流し、端子間電圧を例えばAD変換器でアナログデジタル変換し温度情報に換算する構成としてもよい。ダイオード素子に流す電流(順方向電流)I、アノード・カソード間電圧V、絶対温度Tとの間には、

I≒Isexp(qV/kT) ・・・(1)

の関係があり(ただし、Isは飽和電流(逆方向飽和電流)、qは単位電荷、kはボルツマン定数)、上式の両辺の対数をとると、

V=(kT/q)ln(I/Is) ・・・(2)

が得られ、電圧Vは絶対温度Tに比例する。

【0044】

MOSトランジスタ(MOSFET)の閾値電圧(Vt)は、MOSFETのバックゲート電位(基板電位)により変化するという基板バイアス効果を利用し、PDバックゲート電位変更回路106は、温度センサ107からの温度情報、及び/又は、ヒューズ(Fuse)等によるサンプル別の閾値電圧(Vt)情報108に基づき、MOSFETのバックゲート電位を制御する。なお、MOSFETの閾値電圧(Vt)は負の温度特性を有し、温度が上昇すると、閾値電圧(Vt)は下る。

【0045】

MOSFETの閾値電圧(Vt)は、次式(3)で与えられる。

ただし、

Vt0はNch−MOSFETの場合、界面がp基板と同程度にn型に反転したときのゲート電圧であり、γは基板バイアス効果係数(典型的には、0.3〜0.4V1/2)、φFは(kT/q)ln(Nsub/ni)(ただし、qは単位電荷、kはボルツマン定数、Nsubは基板の不純物濃度、niは真性半導体内のキャリア(電子)濃度)、Vsbはソース・基板間電圧(又は、ソース・ウェル間電圧)である。

【0046】

Nch−MOSFETの場合、バックゲート電位(基板電位、あるいは、Nch−MOSFETが形成されるPウエルの電位)をソース電位(例えばVSS)よりも下げる(負電位とする)とVsbが正値となり、式(3)から、Vtは、バックゲート電位=VSSのときの値Vt0よりも増大する。一方、バックゲート電位をソース電位(例えばVSS)よりも上げると、Vtはバックゲート電位=VSSのときの値Vt0よりも減少する。一方、Pch−MOSFETの場合、バックゲート電位を電源VDDよりも上げると、閾値電圧(Vt)の絶対値|Vt|はバックゲート電位=VDDのときの絶対値|Vt0|よりも増大し、バックゲート電位を電源VDDよりも下げると、閾値電圧(Vt)の絶対値Vtは、バックゲート電位=VDDのときの絶対値|Vt0|よりも減少する。

【0047】

PDバックゲート電位変更回路106は、例えば図7に示すように、温度センサ107の温度情報、ヒューズ(Fuse)108に記憶されたサンプル別閾値電圧(Vt)情報をそれぞれ読み出す第1、第2の入力回路1061、1062と、第1、第2の入力回路1061、1062の読み出し情報に基づき、位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を確定するバックゲート電位決定回路1063と、バックゲート電位決定回路1063で決定されたバックゲート電位を、MOSFETのバックゲートにそれぞれ出力する電圧源回路1064と、制御回路1065を備えている。制御回路1065は、第1、第2の入力回路1061、1062の読み出しの開始/停止を制御する制御信号(指示信号・タイミング信号)や、バックゲート電位決定回路1063の動作の開始/停止を制御する制御信号(指示信号、タイミング信号)、電圧源回路1064を制御する制御信号をそれぞれ供給する。なお、特に制限されないが、バックゲート電位決定回路1063は、測定された周囲温度情報と、Pch−MOSFET又はNch−MOSFETのバックゲート電圧の対応をテーブル形式で記憶したROM(Read Only Memory)を備え、例えば周囲温度に対応するアドレスをROMに入力しバックゲート電位を読み出す方式としてもよい。さらに、第2の入力回路1062で読み取られたサンプル別閾値電圧(Vt)情報と、第1の入力回路1061で読み取られた温度情報を合わせた情報からROMのアドレス情報を生成しバックゲート電圧情報を取得するようにしてもよい。この場合、サンプル依存且つ温度依存でPDのMOSFETの閾値電圧を制御することができる。電圧源回路1064は、出力電圧が可変に設定可能な定電圧源(programmable constant voltage source)で構成され、位相検出回路(PD)105の所定のMOSFETが形成されたウエルコンタクトにバックゲート電圧VBBを供給する。また、制御回路1065は、制御回路1065から指示がない場合には、例えばNch−MOSFETのバックゲート電位VBBとしてVSS(Pch−MOSFETのバックゲート電位としてVDD電位)を出力し、バックゲート電位決定回路1063から新たなバックゲート電位情報が決定された場合に、制御回路1065から指示に基づき、位相検出回路(PD)の例えばMOSFETのバックゲートに、新たなバックゲート電位VBBを出力する構成としてもよい。Nch−MOSFETの場合、閾値電圧(Vt)を、VBB=VSSの場合よりも高くするには、VBB<VSSとし、低くするには、VBB>VSSとする。サンプル別閾値電圧(Vt)情報は、チップ毎に、あるいは、当該チップが形成されたウエハ単位、あるいは、ロット単位(例えば1ロットは12又は25枚分のウエハ)等、チップの集合(チップ群)単位に、閾値電圧情報を設定するようにしてもよい。

【0048】

なお、本実施形態において、PDバックゲート電位変更回路106において、温度情報の取得のタイミングとして、特に制限されないが、例えばDRAMデバイスでのセルフリフレッシュに応答して温度情報を取得するようにしてもよい。あるいは、DRAMデバイス外部のCPUからコントローラを介してDRAMに設定されるコマンド等の内容に応じて温度情報を取得するようにしてもよい。また特に制限されないが、サンプル別閾値電圧(Vt)情報は、DRAMデバイスのパワーオン時等の初期設定時等に、Fuse108から第2の入力回路1062に設定され記憶保持する構成としてもよい。なお、セルフリフレッシュは、セルフリフレッシュ開始コマンド(SREコマンド)の入力時、クロックイネーブル信号CKE(図1参照)をHighからLowとしておくことでセルフリフレッシュモード(DRAM側でリフレッシュを自動で行う)が開始し、セルフリフレッシュ中、クロックイネーブル信号CLKはLowに保持される。なお、クロックイネーブル信号CLKがLowとされることで内部クロックは停止する。セルフリフレッシュのリフレッシュ周期は内部タイマー等によって制御される。クロックイネーブル信号CKEをLowからHighとすると、セルフリフレッシュモードの終了となる。また、セルフリフレッシュ開始時、DLLは一旦リセットされ、セルフリフレッシュ終了時、動作可となる。このため、セルフリフレッシュの開始等に同期して、PDバックゲート電位変更回路106が温度センサ107から温度情報を取得する場合、温度センサ107からの温度情報を第1の入力回路1061のレジスタ等に設定するためのタイミング信号は、例えばクロックイネーブル信号CKEのHighからLowへの遷移、内部タイマーのタイムアウト発生等に応答して制御回路1065内で生成されるパルス等(ワンショット又はマルチショットパルス)で行うようにしてもよい。

【0049】

位相検出回路(PD)105のNch−MOSFETにおける閾値電圧制御の動作例を説明する。

【0050】

(1)Nch−MOSFETの閾値電圧(Vt)が高めのウエハの場合、ヒューズ(Fuse)108に記憶されたサンプル別の閾値電圧(Vt)情報に基づき、PDバックゲート電位変更回路106は、Nch−MOSFETのバックゲート電位(Nch−MOSFETが形成されたPウエル電位)を上げ、閾値電圧(Vt)を下げる。Nch−MOSFETは、シリコン基板に設けられたPウエル内にN+拡散層(ソース・ドレイン)とその間のゲートが作成され、バックゲートはPウエルとなる。Nch−MOSFETが形成されたPウエルのウエル電位を上げる。

【0051】

閾値電圧(Vt)が低めのウエハの場合には、PDバックゲート電位変更回路106は、Nch−MOSFETのバックゲート電位(Nch−MOSFETが形成されたPウエル電位)を下げ、閾値電圧(Vt)を上げる。

【0052】

(2)閾値電圧(Vt)が高まる低温時は、閾値電圧(Vt)を下げる。すなわち、PDバックゲート電位変更回路106は、Nch−MOSFETが形成されたPウエルのウエル電位を上げる。

【0053】

閾値電圧(Vt)が低まる高温時には、閾値電圧(Vt)を上げる。PDバックゲート電位変更回路106は、Nch−MOSFETが形成されたPウエルのウエル電位を下げる。

【0054】

以上の最適値(温度とNch−MOSFETのバックゲート電位、サンプル別Vt情報とNch−MOSFETバックゲート電位)を事前にシミュレーション等で求めておき、ATCSR情報、閾値電圧(Vt)情報(ヒューズ108等で保持)にしたがって、PDバックゲート電位変更回路106にて動的に変更するようにしてもよい。

【0055】

次に、位相検出回路(PD)105のPch−MOSFETにおける閾値電圧制御の動作例を説明する。

(1)閾値電圧(Vt)が高めのウエハの場合、閾値電圧(Vt)を下げる。Pch−MOSFETは、シリコン基板に設けられたNウエル内にP+拡散層(ソース・ドレイン)とその間のゲートが作成され、バックゲートはNウエルとなる。PDバックゲート電位変更回路106は、Pch−MOSFETが形成されたNウエルのウエル電位を下げる。

【0056】

閾値電圧(Vt)が低めのウエハの場合、閾値電圧(Vt)を上げる(基板電位を上げる)。PDバックゲート電位変更回路106は、Pch−MOSFETが形成されたNウエルのウエル電位を上げる。

【0057】

(2)閾値電圧(Vt)が高まる低温時には、閾値電圧(Vt)を下げる。PDバックゲート電位変更回路106は、Pch−MOSFETが形成されたNウエルのウエル電位を下げる。

【0058】

閾値電圧(Vt)が低まる高温時には、閾値電圧(Vt)を上げる。PDバックゲート電位変更回路106は、Pch−MOSFETが形成されたNウエルのウエル電位を上げる。

【0059】

以上の最適値(温度とPch−MOSFETのバックゲート電位、サンプル別Vt情報とPch−MOSFETバックゲート電位)を事前にシミュレーション等で求めておき、ATCSR情報、閾値電圧(Vt)情報(Fuse等で保持)にしたがって動的に変更する。なお、Nch−MOSFET〜Pch−MOSFET間では、基板電位(ウエル電位)の上下が逆転する。

【0060】

上記(1)〜(2)の操作に伴って、位相検出回路(PD)105を構成するMOSFETの閾値電圧(Vt)は、常に一定に保たれる。したがって、従来サンプル別、同一サンプル動作温度別に、発生していたRep位相情報の変化が抑制される。よって、ロック位相の定常性が保たれる。

【0061】

なお、Nch−MOSFETとPch−MOSETのそれぞれのバックゲート電位を独立に制御する場合、シリコン基板上にPウエル、Nウエルを備えたツインウエルCMOSプロセスを用いてもよい。

【0062】

電流消費低減・低電圧動作のトレンドに対して、近時、半導体製品のトレンドとして、電流消費低減・低電圧動作が目標となっている。電流消費低減のためには、MOSFETの閾値電圧(Vt)を高め、リーク電流等を削減する手法が有効である。しかしながら、閾値電圧(Vt)の上昇に伴い、MOSFET動作におけるゲート・オーバードライブ(=Vgs(ゲート・ソース間電圧)−閾値電圧(Vt))が低下し、MOSFETの最低動作電圧を押し上げてしまう。閾値電圧(Vt)の上昇は、低電圧動作のトレンドに対して逆行するものといえる。そのため、現在は、同一チップ内の一部MOSFETのみ(設計・製造時の作り分け等により)、低閾値電圧(Vt)−MOSFETを採用する等して対処している。

【0063】

位相検出回路(PD)にも、低閾値電圧(Vt)−MOSFETが採用される例はあるが、本発明を適用することで、位相検出回路(PD)を構成するMOSFETの閾値電圧(Vt)を動的に変化させることができる。つまり、他要素と同一(あるいは、高めの)閾値電圧(Vt)を利用して製造しておき、動作時に、位相検出回路(PD)の基板電位変更回路106を用いて位相検出回路(PD)105の閾値電圧(Vt)のみを下げるといった対策が可能である。

【0064】

本実施形態により、MOSFETの閾値電圧(Vt)を動的に変更することで、位相検出回路(PD)に関しては、低閾値電圧(Vt)−MOSFETを用いずに、電流消費削減、低電圧動作というトレンドに対して、効果的な対応が可能といえる。

【0065】

また位相検出回路(PD)の低閾値電圧(Vt)化を動的に行えることから、半導体製品全体を、高閾値電圧(Vt)化して製造し、製品全体のリーク電流等の削減に注力しつつ、位相検出回路(PD)のMOSFETの閾値電圧(Vt)を変更することで、通常品と同様のロック位相を保つといった応用も可能である。

【0066】

本実施形態によれば、製造コスト低減を可能としている。すなわち、位相検出回路(PD)以外の各要素を通常閾値電圧(Vt)で設計できた場合、上記の低閾値電圧(Vt)−MOSFETは、位相検出回路(PD)のみのために導入せざるを得ず、製造コストの増加に繋がっていた。本発明を適用し、位相検出回路(PD)以外の各要素を、通常閾値電圧(Vt)−MOSFETにて製造できた場合には、低閾値電圧(Vt)−MOSFETの製造工程そのものを排除できるケースが想定できる。このため、製造工程の削減がコスト削減に結びつく事はいうまでも無い。

【0067】

本実施形態によれば、高周波動作への対応を可能としている。すなわち、上記述べてきたように、本発明によれば、ロック位相のサンプル間ばらつき、動作温度ばらつきを低減するものである。したがって高周波動作時に厳しいタイミングマージンを満たす上でも効果がある。高周波動作半導体は必然的にタイミングスペックが厳しくなるが、位相検出回路(PD)の形式が同じである場合、ロック位相のばらつき分布は変わらず、タイミングスペックへの影響が、相対的に大きくなっていく。ロック位相が、温度・閾値電圧(Vt)等により変化する事は、先に述べたとおりであるが、本発明を適用することにより、一定のロック位相を保つことで、タイミングスペックへの悪影響を抑える事が可能である。

【0068】

以上より、本実施形態の位相検出回路(PD)は高周波動作に対する利点をも兼ね備える。

【0069】

さらに、回路形式の柔軟さ、増幅回路つき位相検出回路(PD)への利用が可能となる。本発明によれば、MOSトランジスタの閾値電圧(Vt)の一定化を目的としたものである。したがって、閾値電圧(Vt)の変動がロック位相に対して大きな影響を及ぼし、従来、利用が見送られてきた形式の位相検出回路(PD)があれば、本発明を適用する事で、実現が容易となる。

【0070】

図6に示す回路例は、閾値電圧(Vt)変動に敏感なダイナミックアンプを利用した位相検出回路(PD)例である。ダイナミックアンプは、クロック信号の活性化時(例えばHighパルス)のときアンプを駆動する電流源が活性化されて増幅動作する。

【0071】

図6の位相比較回路は、CKと、CKBの電圧を比較する電圧コンパレータを構成するNch差動対(201、202)と、差動対の差動出力(DLSAT、DLSAB)を差動でラッチする差動型フリップフロップ(203、204、205、206)と、差動出力(DLSAT、DLSAB)をプリチャージ・イコライズする回路(211−213)と、クロック信号Repclkに基づき、差動対(201、202)の電流源(207)の活性化を制御する回路(210、208)を備えている。

【0072】

レプリカクロック信号Repclkの立ち上がりエッジの到来時に、相補のクロック信号CK、CKBの状態を把握するものである。レプリカクロック信号RepclkがLowからHighとなった時点でのクロック信号CK、CKBの状態をサンプルし、CKがHighであれば、比較結果を出力する正転端子COTにLowパルスを出力する。CKBがHighであれば、比較結果を出力する反転端子COBにLowパルスを出力する。レプリカクロック信号RepclkがHighからLowとなると、COT、COBはともHighとされ、次の比較動作(レプリカクロック信号RepclkのHighパルスの入力)までともにHighに保持される。なお、図6のCKBは、図1、図5の/CK(クロック信号CKの相補信号)を入力する。

【0073】

より詳しくは、図6に示すように、共通接続されたソースが、Nch−MOSFET207、208を介してVSSに接続され、ゲートにCK、CKB(/CK)を入力するNch−MOSFET201、202と、ソースが電源VPERIに接続されたPch−MOSFET204、206と、Pch−MOSFET204、206のドレインにそれぞれドレインが接続され、共通接続されたソースがNch−MOSFET209のドレインに接続されたNch−MOSFET203、205と、ソースが電源VPERIに接続されたPch−MOSFET212、213と、Pch−MOSFET212、213のドレイン間に接続されたPch−MOSFET211と、を備えている。Pch−MOSFET212のドレインは、DLSABノードにおいて、Nch−MOSFET201のドレインに接続され、さらにPch−MOSFET204とNch−MOSFET203のドレインの接続点に接続され、DLSABノードはインバータ214の入力に接続され、Pch−MOSFET213のドレインは、DLSATノードにおいて、Nch−MOSFET202のドレインに接続され、さらにPch−MOSFET206とNch−MOSFET205のドレインの接続点に接続され、DLSATノードはインバータ217の入力に接続され、Pch−MOSFET204とNch−MOSFET203と共通ドレインと共通ゲートは、Pch−MOSFET206とNch−MOSFET205の共通ゲートと共通ドレインに交差接続されている。インバータ217、214の出力信号は、インバータ(反転型出力バッファ)218、216でそれぞれ反転され、端子COT、COBに出力される。Pch−MOSFET211、212、213、Nch−MOSFET207、209は、レプリカクロック信号Repclkに接続され、Nch−MOSFET208のゲートは、レプリカクロック信号Repclkをインバータ210で反転した信号Repclk2が入力される。レプリカクロック信号RepclkがLowからHighとなると、Repclk2はインバータ210の伝播遅延時間経過後、HighからLowとなる。したがって、RepclkがLowからHighとなった後、Repclk2がHighからLowとなるまでの期間、Nch−MOSFET207、208がオンし、差動対トランジスタ201、202の共通ソースに定電流を供給する。特に制限されないが、Nch−MOSFET207が定電流源トランジスタ、Nch−MOSFET208は、Repclk2に基づき、定電流源トランジスタ207の活性化を制御するスイッチトランジスタとして構成される。Nch−MOSFET207、208、209はRepclkインプットディスチャージ回路、Nch−MOSFET201、202は、CK、CKBインプットディスチャージ回路、MOSFET203、204、205、206はダイナミックバッファ、211はイコライザ、Pch−MOSFET212、113はプリチャージ回路を構成している。電源VPERIは、図1のDRAMの周辺回路を駆動する電源である。図6において、VPERIの代わりに、内部電源電圧VDD等であってもよいとは勿論である。また位相検出回路の出力を差動出力COT、COBの代わりに、シングルエンデッド出力としてもよいことは勿論である。

【0074】

図6に示すように、本実施形態では、Nch−MOSFET201、202、207、208等のバックゲートは、VSSの変わりに、PDバックゲート電位変更回路106から出力されるバックゲートバイアス電圧VBBに接続されている。

【0075】

レプリカクロック(Repclk)の立ち上がりエッジ到来時のCK、CKBの電位極性を、インバータ214、217以降の情報として出力する。すなわち、Repclkの立ち上がりエッジのタイミングで、CK=Low、CKB=Highの場合、COT=High、COB=Lowとなる。すなわち、Repclkの位相がCKよりも進んでおり(Repclkの遅延不足である)、DLLのカウンタ回路102(図5参照)のカウンタ値を増加させてディレイライン100(図5参照)の遅延を増加させる。

【0076】

Repclkの立ち上がりエッジのタイミングで、CK=High、CKB=Lowの場合、COT=Low、COB=Highとなる。Repclkの位相がCKよりも遅れており(Repclkの遅延が過剰である)、DLLのカウンタ回路102(図5参照)のカウンタ値を減少させてディレイライン100(図5参照)の遅延を減少させる。

【0077】

レプリカクロック信号Repclkの立ち下がりエッジ以降から立ち上がりジ到来までのLow期間中、プリチャージ用のPch−MOSFET212、213およびイコライズ用のPch−MOSFET211がオン(導通状態)である。また、レプリカ・インプット・ディスチャージ220のNch−MOSFET208、209はオフ(非導通状態)となり、差動対(201、202)の出力ノードDLSAT、DLSAB共にHigh電位(VPERI)とされ(プリチャージ状態)、COT、COBはともにHigh電位とされる。なお、このプリチャージ状態においても、外部よりCK、CKBは入力される。Nch−MOSFET210、202は、一定程度のアナログゲートレベルであるが、レプリカ・インプットディスチャージ回路220=非活性状態とされ、Nch−MOSFET210、202の共通ソースの電位はほぼ一定に保たれる。

【0078】

レプリカクロック信号Repclkの立ち上がりエッジにて、DLSAB、および、Nch−MOSFET210、202のソースの電位が低下する。この際、Nch−MOSFET210、202のゲート電位は相補の関係であるため、両者には電位差が生じる(一方は他方よりも高電位である)。したがって、ノードDLSABとDLSAT間電位に差が生じる。DLSABとDLSATの間に電位差が生じた状態がダイナミックアンプ(入力と出力が交差接続された2つのCMOSインバータ((203、204)と(205、206)からなる)219に発生することからその電位差が差動増幅される。差動増幅されたDLSAT、DLSABノード間の電位差は、インバータ217、218、インバータ214、216を通って出力端子COT、COBから外部(図5のカウンタ回路102)に伝播する。

【0079】

位相検出回路(PD)に、ダイナミックアンプによる増幅動作が組み込まれているのは、半導体製品外部入力(CK、CKB)が、電源レベルの1/2などに設定されたリファレンスレベルVef付近の差動小振幅な信号となっているためである。すなわち、コモン電圧をVrefとして、Vref±ΔVとされる(振幅=2ΔV、Vref=VDD/2、Vref+ΔV<VDD)。小振幅による差動伝送は、信号伝播時の電力消費抑制などに効果が大きいものの、差動信号を受けるレシーバ(例えば位相検出回路(PD))にて増幅が必要である。

【0080】

この様な小振幅な差動信号を扱う回路では、特性に影響を及ぼす閾値電圧(Vt)の影響が相対的に大きい。サンプル別・動作温度別閾値電圧(Vt)の影響を抑えるため、従来、例えば以下の対策が行われていた。

【0081】

(A)インプット・ディスチャージトランジスタ(201、202、207−209)を低閾値電圧(Vt)とする。

【0082】

(B)インプット・ディスチャージトランジスタのサイズを拡大する。

【0083】

これらの対策は、レプリカクロック信号Repclkの立ち上がりの到来時のインプット・ディスチャージトランジスタの電流を増加し、ダイナミックアンプの増幅初期差電位の増加を目指すものである。本質的なサンプル・動作温度ばらつきを抑制できるものではないが、本来ならば増幅初期差電位が小さい状況下でも、ダイナミックアンプの動作の確実化がなされるため、相対的に動作の平準化に寄与できる。ただし、インプット・ディスチャージ・トランジスタの電流増加に伴い、位相検出回路(PD)全体の消費電流増加がおき、また本質的なばらつき低減策ではないなど問題が多い。

【0084】

これに対して、本実施形態による閾値電圧(Vt)の均一化は、図6に示した位相検出回路(PD)のような増幅回路を備える形式へ適用する。

【0085】

本実施形態によれば、Nch−MOSFT(201、202、207−209)のバックゲートは、PDバックゲート電位変更回路106からのバックゲートバイアス電圧VBBに接続され、例えばVBB>VSSとすることで、低閾値電圧化を達成する。また、従来のサンプル・温度別ばらつきを本質的に解消し、またインプット・ディスチャージトランジスタの大電流化も抑制することができる。

【0086】

さらに、本実施形態によれば以下のような作用効果を奏する。

【0087】

ATCSR(例えばDRAM等が標準的に備える温度計)、Fuse等によるサンプル別閾値電圧(Vt)情報を基に、位相検出回路(PD)の基板電位を変更する。基板電位の変更に伴い、位相検出回路(PD)の動作に由来するロック位相が補正され、平準化される。

【0088】

DLLへの適用にあたり、基板電位の変更は、位相検出回路(PD)にのみ適用すればよく、複雑化増大の程度が小さい。

【0089】

電流消費低減・低電圧動作のトレンドに対応可能である。

【0090】

製造コストの低減を可能としている。

【0091】

高周波動作への対応を可能としている。

【0092】

閾値電圧(Vt)変化に過敏な回路に適用することで、位相検出回路(PD)への実用可能性をさらに高めることができる。

【0093】

上記の通り、実施形態では、増幅回路(ダイナミックアンプ)付き位相検出回路(PD)への本発明の適用による、

・ロック位相の定常化、

・位相検出回路(PD)自体の消費電力の低減、

・位相検出回路(PD)を構成するMOSトランジスタサイズの小型化

等の作用について説明した。

【0094】

本発明の技術思想は、様々な半導体装置に適用することができる。例えば、CPU(Central Processing Unit)、MCU(Micro Control Unit)、DSP(Digital Signal Processor)、ASIC(Application Specific Integrated Circuit)、ASSP(Application Specific Standard Product)、メモリ(Memory)等の半導体装置全般に、本発明を適用することができる。このような本発明が適用された半導体装置の製品形態としては、例えば、SOC(システムオンチップ)、MCP(マルチチップパッケージ)やPOP(パッケージオンパッケージ)などが挙げられる。これらの任意の製品形態、パッケージ形態を有する半導体装置に対して本発明を適用することができる。また、トランジスタは、電界効果トランジスタ(Field Effect Transistor;FET)であれば良く、MOS(Metal Oxide Semiconductor)以外にもMIS(Metal−Insulator Semiconductor)、TFT(Thin Film Transistor)等の様々なFETに適用できる。トランジスタ等の様々なFETに適用できる。更に、装置内に一部のバイポーラ型トランジスタを有しても良い。更に、PMOSFET(P型チャネルMOSFET)は、第2導電型のトランジスタ、Nch−MOSFET(N型チャネルMOSFET)は、第1導電型のトランジスタの代表例である。

【0095】

本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0096】

1−1 メモリセルアレイ

1−2 センスアンプ

1−3 カラムデコーダ

1−4 ロウデコーダ

1−5 モードレジスタ

1−6 ロウアドレスバッファ及びリフレッシュカウンタ

1−7 カラムアドレスバッファ及びバーストカウンタ

1−8 データコントロール回路

1−9 コマンドデコーダ

1−10 コントロールロジック

1−11 ラッチ回路

1−12 DLL

1−13 入出力バッファ

1−14 クロックジェネレータ

100 ディレイライン

101 デコーダ回路

102 カウンタ回路

103 出力回路

104 レプリカ回路

105 位相検出回路(PD)

106 PDバックゲート電位変更回路(電源回路)

107 ATCSR(温度計)

108 ヒューズ(Fuse)等よるサンプル別Vt情報

204、206、211−213 Pch−MOSFET

201〜203、205、207−209 Nch−MOSFET

210、214、217 インバータ

216、218 出力バッファ(インバータ)

219 ダイナミックアンプ

220 レプリカクロック・インプットディスチャージ

1061、1062 入力回路

1063 バックゲート電位決定回路

1064 電圧源回路

1065 制御回路

【技術分野】

【0001】

本発明は半導体装置に関し、DLL(Delay Lock Loop:遅延同期ループ)を備えた半導体装置に関する。

【背景技術】

【0002】

DLLでは、入力信号を入力する遅延時間可変型のディレイライン(遅延線)の出力信号を帰還させた信号と該入力信号の位相を比較し、位相比較結果に基づきディレイラインの遅延を調整し、出力信号と入力信号の位相が所望値となるように制御する。

【0003】

このDLLを搭載した半導体装置の一例として、DRAM(Dynamic Random Access Memory)デバイスの概要を図1を参照して説明する。特に制限されないが、図1のDRAMデバイスは8バンク構成のDDR(Double Data Rate:クロックの立ち上がりと立ち下がりの両エッジに同期してデータをやり取りする)SDRAM(Synchronous DRAM;クロック同期型DRAM)である。図1において、ロウデコーダ1−4は、ロウアドレスをデコードし選択されたワード線(不図示)を駆動する。センスアンプ1−2は、メモリセルアレイ1−1のビット線(不図示)に読み出されたデータを増幅し、リフレッシュ動作時にはリフレッシュアドレスで選択されたワード線のセルに接続するビット線に読み出されたセルデータを増幅して該セルへ書き戻す。カラムデコーダ1−3は、カラムアドレスをデコードし、選択されたYスイッチ(不図示)をオンとしてビット線を選択し、IO線(不図示)に接続する。コマンドデコーダ1−9は、チップセレクト信号/CS、ロウアドレスストローブ信号/RAS、カラムアドレスストローブ信号/CAS、ライトイネーブル信号/WE等を入力し、コマンドをデコードする(なお、信号名の/はLowでアクティブであることを示す)。カラムアドレスバッファ及びバーストカウンタ1−7は、コマンドデコーダ1−9からの制御信号を受けるコントロールロジック1−10の制御のもと、入力されたカラムアドレスから、バースト長分のアドレスを生成し、カラムデコーダ1−3に供給する。モードレジスタ1−5は、アドレス信号とバンク選択用(8バンクの中の1つを選択)の信号BA0、BA1、BA2を入力し、コントロールロジック1−10に制御信号を出力する。ロウアドレスバッファ及びリフレッシュカウンタ1−6のロウアドレスバッファは、入力されたロウアドレスを受けて、ロウデコーダ1−4に出力し、リフレッシュカウンタは、例えばリフレッシュコマンドが入力されると、コマンドデコーダ1−9でのデコード結果に基づき、コントロールロジック1−10からの制御信号に応答してカウントアップ動作し、カウント出力をリフレッシュアドレスとして出力する。なお、低電力動作時のセルフリフレッシュモードでは、例えば不図示の内部タイマーで規定されるリフレッシュサイクルでリフレッシュカウンタをカウントアップしリフレッシュアドレスとする。ロウアドレスバッファからのロウアドレスとリフレッシュカウンタからのリフレッシュアドレスはマルチプレクサ(不図示)に入力され、リフレッシュ時には、リフレッシュアドレスが選択され、それ以外は、ロウアドレスバッファからのロウアドレスを選択し、ロウデコーダ1−4に供給される。

【0004】

クロックジェネレータ1−14は、DRAMデバイスに供給される相補の外部クロックCK、/CKを受け、クロックイネーブル信号CKEがHighのとき、内部クロック信号を出力し、クロックイネーブル信号CKEがLowとなると、以降、内部クロック信号の供給を停止する。データコントロール回路1−8は、書き込みデータと読み出しデータの入出力を行う。ラッチ回路1−11は書き込みデータと読出しデータをラッチする。入出力バッファ1−13はデータ端子DQからのデータの入力と出力を行う。

【0005】

DLL1−12は、外部クロック信号CK、/CKに遅延同期した信号を生成し、入出力バッファ1−13に供給する。メモリセルアレイ1−1からの読み出しデータはラッチ回路1−11から入出力バッファ1−13に供給され、入出力バッファ1−13は、DLL1−12で外部クロックCKに同期したクロック信号の立ち上がりと立ち下がりのエッジを用いて、データ端子DQから読み出しデータをダブルデータレートで出力する。

【0006】

DQSは、データのライト(書き込み)、リード(読み出し)のタイミングを規定するデータストローブ信号であり、ライト動作時に、DRAM外部のコントローラ(不図示)側から入力される入力信号であり、リード動作時には、DRAMからコントローラ側に出力される出力信号(IO信号)である。外部クロックCK、/CKに同期し、DDR SDRAMでは、DQSの立ち上がりと立ち下がりの両エッジを基準としてデータ(DQ)の入出力が行われる。DQSは、リード動作時には、クロック信号CKの立ち上がりエッジに同期してDRAMから出力され、ライト動作時には、コントローラ(不図示)から、クロック信号CKの立ち上がりエッジから所定の位相遅延させて、DRAM側に入力される。ライト時には、DRAMのラッチ回路1−11は、コントローラ(不図示)から入力されるDQSのエッジのタイミングで、入出力バッファ1−13からのデータ(入出力バッファ1−13の入力バッファにDQ端子から入力された書き込みデータ)を取り込む。リード時には、コントローラ(不図示)等のレシーバは、DRAMのDQ端子から出力される読み出しデータを、DQSの両エッジ(立ち上がりエッジと立ち下がりエッジ)のタイミングで取り込む。

【0007】

DLL1−12において、入力された外部クロック信号(CK)をディレイラインで遅延させた信号を、さらに、入出力バッファ1−13の出力バッファ(出力回路)のレプリカ(Replica)(不図示)で遅延させたレプリカクロック信号(Repclk)と、外部クロック信号CKの位相を比較し、これらの位相が合うように、ディレイラインの遅延時間を可変させる。データ読み出し時、レプリカクロック信号(Repclk)と同位相のデータストローブ信号DQSを出力信号として外部(コントローラ等)に出力することができれば、当該DQSは外部クロック信号CKと同位相となる。

【0008】

図2に、DLLとその周辺回路(出力回路とレプリカ回路)の典型的な構成の一例を示す。図2に示すように、DRAM入力信号を入力するディレイライン100と、ディレイライン100の出力であるDLL出力信号を入力し、出力回路103の遅延時間Tを模した遅延T’を有するレプリカ回路104と、レプリカ回路104の出力信号であるレプリカクロック信号Repclkと、DLL入力信号(DRAM入力信号)を入力し両者の位相を比較する位相検出回路(PD:Phase Detector)105と、位相検出回路105での位相比較結果をディレイライン増減信号として入力するカウンタ回路102と、カウンタ回路102のカウント値をデコードしてディレイライン100の遅延時間を設定するデコーダ回路101を備えている。ディレイライン100は、単位遅延回路を複数段縦続形態に接続し、デコーダ回路101の出力に基づき、出力信号が取り出される段数が決定される(単位遅延回路の段数が増えれば、DLL出力信号の遅延時間は増大し、単位遅延回路の段数が減少すれば、DLL出力信号の遅延時間は減少する)。位相検出回路(PD)は、入力した2つの信号(Repclkと、DLL入力信号)の位相を比較し、どちらのエッジが時間的に進んでいるか(遅れているか)を検出するため、位相比較回路又は位相比較器とも呼ばれる。位相検出回路105での比較の結果、レプリカクロック信号Repclkの位相が、DRAM入力信号よりも遅れている場合、カウンタ回路102は、例えばカウンタダウンし、デコーダ回路101は、ディレイライン100の遅延時間を短縮させ、レプリカクロック信号Repclkの位相が、DRAM入力信号よりも進んでいる場合、カウンタ回路102は、例えばカウンタアップし、デコーダ回路101は、ディレイライン100の遅延時間を増加させる。

【0009】

ここで、DLLにおける位相の概念について、図3を参照して説明する。図3において、入力信号はDLLへの入力信号(外部クロック信号CK)、出力信号はDLLの出力信号である。図3には、未ロック状態のDLLにおける入出力信号の位相差が模式的に示されている。DLLは、ディレイラインの遅延時間を調整し、DLLの入力信号(図1の外部クロック信号CK)のエッジAと、DLLの出力信号(図2のレプリカクロック信号Repclk)のエッジBを合致させる。即ち、図3におけるc=b−a相当の時間、入力信号をディレイライン100で遅延させることで、入力信号のエッジAと、出力信号のエッジBをA=B(c=0)としている。c=0の状態を「ロック状態」という(あるいは「位相合致状態」ともいう)。

【0010】

図2において、レプリカ回路104の遅延(T’)は、出力回路103の固有遅延(T)を模しているため、一般的に、出力回路103と同一構成の回路をレプリカ回路104として搭載する。なお、出力回路103はDLL出力信号を受け、DLL出力信号のエッジに応答してDRAM出力信号(データ信号)を出力する。出力回路103とレプリカ回路104は、同一チップ内に設けられるため、半導体製造時のMOSFET(MOS電界効果トランジスタ)の閾値電圧(Vt)のばらつき等は同等である。よって、同一構造であれば、出力回路103とレプリカ回路104とは、同一の遅延時間であることが期待できる。また、出力回路103とレプリカ回路104において、閾値電圧(Vt)の温度特性は同等であるため、動作時の温度変化等によりMOSFETの閾値電圧(Vt)が変化した場合にも、出力回路103とレプリカ回路104において、同様に変化する。そのため、出力回路103とレプリカ回路104の遅延T、T’は同等と考えてよい。

【0011】

図2において、位相検出回路(PD)105は、DLL入力信号(DRAM入力信号)とレプリカクロック信号(Repclk)の位相の前後比較を行う。位相検出回路(PD)105の位相比較結果を「Rep位相前後情報」と呼ぶ場合もある。位相検出回路(PD)で得られた位相比較結果は、ディレイライン増減信号としてカウンタ回路102に送られる。レプリカクロック信号(Repclk)のエッジがDRAM入力信号(CK)のエッジよりも前の場合(レプリカクロック信号(Repclk)がDRAM入力信号(CK)よりも位相検出回路(PD)105に早く到達した場合)、カウンタ回路102のカウンタ値を増加させ、デコーダ回路101を介してディレイライン100の遅延段数を増加し、遅延時間を大とし、レプリカクロック信号(Repclk)がさらに遅延される。カウンタ回路102は、初期値(例えば零)を基準にカウントアップ/ダウンするアップダウンカウンタとして構成され、カウント値の正/負に応じて、遅延時間が基準(初期設定値)の遅延よりも長い/短い段数に位置する単位遅延回路の出力を選択する。なお、カウンタ回路102のカウント値のビット数、及び符号(コード)が、ディレイラインの複数の段数に対応し単位遅延の出力の1つを選択可能なコードとして構成されている場合、デコーダ回路は不用とされる。

【0012】

レプリカクロック信号(Repclk)のエッジがDLL入力信号(DRAM入力信号CK)のエッジよりも後の場合(したがって、RepclkがCKよりも遅くPDに到達した場合)、カウンタ回路102のカウンタ値を減少され、ディレイラインの遅延段の段数を減少し、Repclkのエッジを先行させる。

【0013】

上記一連の動作を継続することで、最終的に、図2のレプリカ回路104から出力されるレプリカクロック信号(Repclk)のエッジAがDRAM入力信号(CK)の位相の前後を横断し続ける状態に到達する。すなわち、図3において、c=0となり、エッジBがエッジAよりも位相が進む、又は遅れる状態を繰り返す。これが、前記ロック状態であり、Repclkの位相とCKの位相が合致するように、図2のディレイレイン100の遅延が調整された状態である。

【0014】

DLLのロック時において、レプリカ回路104から出力されるレプリカクロック信号(Repclk)と、DRAM入力信号(CK)間に発生する位相差を「ロック位相」(あるいは「ロック位相差」)という。Lock位相は、本来、0であることが望ましいが、回路形式・利用電圧等の条件により、一定量のシフトが発生する。そのため、一般的に、DLLのロックでは、ロック位相を考慮に入れ、本来ロック位相0が得られる値から、予め一定量のシフトを考慮して、ロックを行っている。

【0015】

なお、特許文献1には、位相検出回路を備えたDLLが開示されている(特許文献1の図2参照)。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2010−62937号公報

【発明の概要】

【発明が解決しようとする課題】

【0017】

以下、関連技術の分析を与える。

【0018】

位相検出回路(PD)において、当該位相検出回路(PD)を構成するMOSFETの閾値電圧(Vt)が変化すれば、位相検出回路(PD)の動作は変化する。位相検出回路(PD)動作の変化は、外部クロック信号CKとレプリカクロック信号(Repclk)の位相比較動作の変化として現れる。すなわち、サンプル(チップ)間に存在する閾値電圧(Vt)ばらつき(製造ばらつき)や、同一サンプル(同一チップ内)においても、動作温度等の変化により発生する閾値電圧(Vt)の変動に伴い、ロック位相(ロック時に、RepclkとCK間に発生する位相差)が変化する。閾値電圧(Vt)の変化に伴うロック位相の変化を以下に説明する。

【0019】

異なるサンプル(チップ)間で閾値電圧(Vt)が異なる。この場合、サンプル間でロック位相が異なる。

【0020】

同一サンプル(同一チップ内)であるが、動作温度により閾値電圧(Vt)が異なる。この場合、同一サンプルであるが、動作温度によって、ロック位相が変化する。

【0021】

図4は、DRAMデバイスにおける、ロック位相を示す図である。図4において、左側のY軸はロック位相を表している。白の四角(□)は位相検出回路(PD)の位相比較結果↑(アップ)、黒の菱型(◆)は位相検出回路(PD)の位相比較結果↓(ダウン)、右側のY軸=電流値、白の三角形(△)は電流を表している。

【0022】

X軸の1行目は温度であり、−5、110、25(一部条件のみ)℃。

【0023】

X軸の2行目は、位相検出回路(PD)の動作電圧(本例では1.1Vのみ)である。

【0024】

X軸の3行目は、入力信号リファレンスレベル(DRAM等の相補入力(相補クロックCK/CKB)を想定)している。

【0025】

入力VDD=1.3、1.5、1.7V、入力スイング=0.25Vにて、以下の分類となる。クロック波形のクロスポイント(相補クロック(CK、/CK)の立ち上がりと立ち下がりがクロスするポイント)として、

「低」は、CKと/CKBのクロスポイント=47.5[%]、

「普」は、CKと/CKBのクロスポイント=50.0[%](HighとLowの中央、Duty=50%の対称波形)、

「高」は、CKと/CKBのクロスポイント=52.5[%]。

【0026】

X軸の4行目は、電源電圧(VDD)、

X軸の5行目は、製造時の閾値電圧(Vt)

である。

【0027】

上記した区分けにて、温度・閾値電圧(Vt)変動に注目した場合、図3上のワーストケースとなる、丸で囲んだ1、2間のロック位相差は、50psである。他の状況にも、一様に、ロック位相差が存在することがわかる。このように、プロセス−閾値電圧(Vt)条件(P)、動作電圧条件(V)、温度条件(T)により、ロック位相にばらつきが見られる事がわかる。

【0028】

図4によれば、Lock位相は、PVT条件変動に伴い、例えば50ps程度の変動が起こり得る。以上のように、ロック位相の定常性は保たれていない。よって、サンプル・温度等の変位に伴い発生するロック位相の変動に対応し、補正するシステムの提案が求められている。

【0029】

また、近時の低電圧化の流れに伴い、上記の変動幅は、拡大していくものと考えられる。

【課題を解決するための手段】

【0030】

上記問題点の少なくとも1つを解決するため、本発明は概略以下の構成とされる(ただし以下に限定されない)。

【0031】

本発明によれば、DLLの位相検出回路を構成する複数のトランジスタのうち所定のトランジスタの閾値電圧を補正する補正回路を備えた半導体装置が提供される。

【発明の効果】

【0032】

本発明によれば、サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができる。

【図面の簡単な説明】

【0033】

【図1】DLLを備えた半導体装置の一例を示す図である。

【図2】DLLの構成の一例を示す図である。

【図3】未ロック状態のDLLにおける位相差を説明する図である。

【図4】PVT条件別のロック位相の変位を例示した図である。

【図5】本発明の一実施形態の構成を示す図である。

【図6】位相検出回路(PD)の構成を示す図である。

【図7】PDバックゲート電位変更回路の構成の一例を示す図である。

【発明を実施するための形態】

【0034】

本発明の課題を解決する技術思想(コンセプト)の代表的な一例は以下に示される。但し、本願の請求内容はこの技術思想に限られず、本願請求項に記載の内容であることは言うまでもない。いくつかの好ましい形態によれば、第1の信号と第2の信号の位相を比較する位相検出回路(105)と、前記位相検出回路(105)を構成する複数のトランジスタのうち所定のトランジスタの閾値電圧を補正する補正回路(例えば図5のPDバックゲート電位変更回路106)を備えている。位相検出回路(105)はDLLの入力信号と出力信号の位相を比較し、DLLのディレイラインの遅延時間を増減させるための信号を出力する。

【0035】

好ましい形態によれば、さらに、半導体装置内部の温度を検出するセンサ(図5の107)を備え、前記補正回路は、前記センサ(107)で検出された温度情報に基づき、前記位相検出回路を構成する前記所定のトランジスタの閾値電圧を補正する。あるいは、半導体装置毎又は半導体装置群単位(例えばウェハ単位、あるいはロット単位等)でのトランジスタの閾値電圧情報を記憶する記憶部(108)を備え、前記補正回路は、前記記憶部に記憶される前記半導体装置毎又は半導体装置群単位でのトランジスタの閾値電圧情報に基づき、前記位相検出回路を構成する前記所定のトランジスタの閾値電圧を補正する。

【0036】

好ましい形態によれば、前記補正回路が、前記位相検出回路(105)を構成する前記所定のトランジスタのバックゲートに与える電圧を生成する電圧源回路(図7の1064)を備え、前記センサからの前記温度情報、及び/又は、前記記憶部に記憶された前記トランジスタの閾値電圧情報に基づき、前記バックゲート電圧を可変に設定する。

【0037】

DLLの前記ディレイライン(100)から出力される前記信号に応答してデータ信号を出力端子に出力する出力バッファ回路(103)の遅延を模したレプリカ回路(104)を備え、前記ディレイライン(100)から出力された信号は、前記レプリカ回路(104)で遅延され、前記位相検出回路(105)に入力される。

【0038】

本発明によれば、温度及びサンプルの条件により、ダイナミックに位相検出回路のトランジスタの閾値電圧Vtを補正する。いくつかの好ましい形態(Preferred Modes)によれば、位相検出回路(PD)を構成するMOSトランジスタの閾値電圧(Vt)の変化の補正を行い、サンプル別、あるいは動作温度別に発生していたロック位相(ロック時にRepclkとCK間に発生する位相差)のばらつきを解消する。

【0039】

DLLは、レプリカクロック信号(Repclk)を用いて、外部クロックと位相比較し、ディレイラインの遅延時間をフィードバック制御する回路構成である。レプリカ回路の遅延が出力回路の遅延時間を模すこと(図2の遅延時間T=T’)で、ロック動作中にロック位相を読み取り、位相検出回路(PD)において、DLL入力信号の位相と、レプリカクロック信号(Repclk)の位相(どちらのエッジが時間的の前に位置するか)の前後を判断している。

【0040】

位相検出回路(PD)においては、前述したように、位相検出回路(PD)を構成するMOSFETの閾値電圧(Vt)に影響を受け、ロック位相が変化するという問題を持つが、本発明によれば、これを是正することができる。

【0041】

<実施形態>

図5は、本発明の一実施形態を説明するための図である。図2の構成に対して、位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ(ATCSR(Auto Temperature Compensated Self Refresh:自動温度補償セルフリフレッシュ)107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備えている。温度センサ107の温度情報、ヒューズ(Fuse)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出される。

【0042】

図5において、ディレイライン100、デコーダ回路101、カウンタ回路102、出力回路103、レプリカ回路104は、図2の構成と同様である。すなわち、図1及び図2に示した構成に、さらに、図5の温度センサ107、サンプル別閾値電圧(Vt)情報を記憶するヒューズ(Fuse)108、PDバックゲート電位変更回路106を備えた構成が、この実施形態に係る半導体装置の一例となる。なお、図5のFuse(ヒューズ)108は、ROM(Read Only Memory)等他の任意の不揮発性記憶装置であってもよいことは勿論である。なお、ヒューズ(Fuse)108等にはデバイス製造時(例えばウエハテスト時、あるいは製品出荷時等)に、サンプル別閾値電圧(Vt)情報が設定される。以下では、本実施形態において、図1について共通部分の説明の重複は回避する。

【0043】

特に制限されないが、本実施形態では、ATCSRが温度センサ107として用いられている。ATCSRは、DRAM製品に搭載される温度センサの一種であり、DRAMデバイス内部に組み込まれた温度センサで検出された周囲温度情報に応じて自動的にリフレッシュ間隔を変更する。DRAMの場合、例えばモバイル用途等の低電圧動作品、DDR3以降の高速動作品においてATCSR機能の搭載が一般化しつつある。なお、ATCSRを具備している低電圧動作品・高速動作品に、本発明を適用する場合、新たに温度計を搭載する必要はなく、ATCSRの組み込み温度センサから出力される温度情報を利用すればよい。また特に制限されないが、ATCSR機能により読み出された情報は、温度レジスタ等にデジタル情報として設定される。なお、図5の温度センサ107として、ダイオード素子等(PN接合素子)を半導体装置内に組み込み、ダイオード素子に定電流を流し、端子間電圧を例えばAD変換器でアナログデジタル変換し温度情報に換算する構成としてもよい。ダイオード素子に流す電流(順方向電流)I、アノード・カソード間電圧V、絶対温度Tとの間には、

I≒Isexp(qV/kT) ・・・(1)

の関係があり(ただし、Isは飽和電流(逆方向飽和電流)、qは単位電荷、kはボルツマン定数)、上式の両辺の対数をとると、

V=(kT/q)ln(I/Is) ・・・(2)

が得られ、電圧Vは絶対温度Tに比例する。

【0044】

MOSトランジスタ(MOSFET)の閾値電圧(Vt)は、MOSFETのバックゲート電位(基板電位)により変化するという基板バイアス効果を利用し、PDバックゲート電位変更回路106は、温度センサ107からの温度情報、及び/又は、ヒューズ(Fuse)等によるサンプル別の閾値電圧(Vt)情報108に基づき、MOSFETのバックゲート電位を制御する。なお、MOSFETの閾値電圧(Vt)は負の温度特性を有し、温度が上昇すると、閾値電圧(Vt)は下る。

【0045】

MOSFETの閾値電圧(Vt)は、次式(3)で与えられる。

ただし、

Vt0はNch−MOSFETの場合、界面がp基板と同程度にn型に反転したときのゲート電圧であり、γは基板バイアス効果係数(典型的には、0.3〜0.4V1/2)、φFは(kT/q)ln(Nsub/ni)(ただし、qは単位電荷、kはボルツマン定数、Nsubは基板の不純物濃度、niは真性半導体内のキャリア(電子)濃度)、Vsbはソース・基板間電圧(又は、ソース・ウェル間電圧)である。

【0046】

Nch−MOSFETの場合、バックゲート電位(基板電位、あるいは、Nch−MOSFETが形成されるPウエルの電位)をソース電位(例えばVSS)よりも下げる(負電位とする)とVsbが正値となり、式(3)から、Vtは、バックゲート電位=VSSのときの値Vt0よりも増大する。一方、バックゲート電位をソース電位(例えばVSS)よりも上げると、Vtはバックゲート電位=VSSのときの値Vt0よりも減少する。一方、Pch−MOSFETの場合、バックゲート電位を電源VDDよりも上げると、閾値電圧(Vt)の絶対値|Vt|はバックゲート電位=VDDのときの絶対値|Vt0|よりも増大し、バックゲート電位を電源VDDよりも下げると、閾値電圧(Vt)の絶対値Vtは、バックゲート電位=VDDのときの絶対値|Vt0|よりも減少する。

【0047】

PDバックゲート電位変更回路106は、例えば図7に示すように、温度センサ107の温度情報、ヒューズ(Fuse)108に記憶されたサンプル別閾値電圧(Vt)情報をそれぞれ読み出す第1、第2の入力回路1061、1062と、第1、第2の入力回路1061、1062の読み出し情報に基づき、位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を確定するバックゲート電位決定回路1063と、バックゲート電位決定回路1063で決定されたバックゲート電位を、MOSFETのバックゲートにそれぞれ出力する電圧源回路1064と、制御回路1065を備えている。制御回路1065は、第1、第2の入力回路1061、1062の読み出しの開始/停止を制御する制御信号(指示信号・タイミング信号)や、バックゲート電位決定回路1063の動作の開始/停止を制御する制御信号(指示信号、タイミング信号)、電圧源回路1064を制御する制御信号をそれぞれ供給する。なお、特に制限されないが、バックゲート電位決定回路1063は、測定された周囲温度情報と、Pch−MOSFET又はNch−MOSFETのバックゲート電圧の対応をテーブル形式で記憶したROM(Read Only Memory)を備え、例えば周囲温度に対応するアドレスをROMに入力しバックゲート電位を読み出す方式としてもよい。さらに、第2の入力回路1062で読み取られたサンプル別閾値電圧(Vt)情報と、第1の入力回路1061で読み取られた温度情報を合わせた情報からROMのアドレス情報を生成しバックゲート電圧情報を取得するようにしてもよい。この場合、サンプル依存且つ温度依存でPDのMOSFETの閾値電圧を制御することができる。電圧源回路1064は、出力電圧が可変に設定可能な定電圧源(programmable constant voltage source)で構成され、位相検出回路(PD)105の所定のMOSFETが形成されたウエルコンタクトにバックゲート電圧VBBを供給する。また、制御回路1065は、制御回路1065から指示がない場合には、例えばNch−MOSFETのバックゲート電位VBBとしてVSS(Pch−MOSFETのバックゲート電位としてVDD電位)を出力し、バックゲート電位決定回路1063から新たなバックゲート電位情報が決定された場合に、制御回路1065から指示に基づき、位相検出回路(PD)の例えばMOSFETのバックゲートに、新たなバックゲート電位VBBを出力する構成としてもよい。Nch−MOSFETの場合、閾値電圧(Vt)を、VBB=VSSの場合よりも高くするには、VBB<VSSとし、低くするには、VBB>VSSとする。サンプル別閾値電圧(Vt)情報は、チップ毎に、あるいは、当該チップが形成されたウエハ単位、あるいは、ロット単位(例えば1ロットは12又は25枚分のウエハ)等、チップの集合(チップ群)単位に、閾値電圧情報を設定するようにしてもよい。

【0048】

なお、本実施形態において、PDバックゲート電位変更回路106において、温度情報の取得のタイミングとして、特に制限されないが、例えばDRAMデバイスでのセルフリフレッシュに応答して温度情報を取得するようにしてもよい。あるいは、DRAMデバイス外部のCPUからコントローラを介してDRAMに設定されるコマンド等の内容に応じて温度情報を取得するようにしてもよい。また特に制限されないが、サンプル別閾値電圧(Vt)情報は、DRAMデバイスのパワーオン時等の初期設定時等に、Fuse108から第2の入力回路1062に設定され記憶保持する構成としてもよい。なお、セルフリフレッシュは、セルフリフレッシュ開始コマンド(SREコマンド)の入力時、クロックイネーブル信号CKE(図1参照)をHighからLowとしておくことでセルフリフレッシュモード(DRAM側でリフレッシュを自動で行う)が開始し、セルフリフレッシュ中、クロックイネーブル信号CLKはLowに保持される。なお、クロックイネーブル信号CLKがLowとされることで内部クロックは停止する。セルフリフレッシュのリフレッシュ周期は内部タイマー等によって制御される。クロックイネーブル信号CKEをLowからHighとすると、セルフリフレッシュモードの終了となる。また、セルフリフレッシュ開始時、DLLは一旦リセットされ、セルフリフレッシュ終了時、動作可となる。このため、セルフリフレッシュの開始等に同期して、PDバックゲート電位変更回路106が温度センサ107から温度情報を取得する場合、温度センサ107からの温度情報を第1の入力回路1061のレジスタ等に設定するためのタイミング信号は、例えばクロックイネーブル信号CKEのHighからLowへの遷移、内部タイマーのタイムアウト発生等に応答して制御回路1065内で生成されるパルス等(ワンショット又はマルチショットパルス)で行うようにしてもよい。

【0049】

位相検出回路(PD)105のNch−MOSFETにおける閾値電圧制御の動作例を説明する。

【0050】

(1)Nch−MOSFETの閾値電圧(Vt)が高めのウエハの場合、ヒューズ(Fuse)108に記憶されたサンプル別の閾値電圧(Vt)情報に基づき、PDバックゲート電位変更回路106は、Nch−MOSFETのバックゲート電位(Nch−MOSFETが形成されたPウエル電位)を上げ、閾値電圧(Vt)を下げる。Nch−MOSFETは、シリコン基板に設けられたPウエル内にN+拡散層(ソース・ドレイン)とその間のゲートが作成され、バックゲートはPウエルとなる。Nch−MOSFETが形成されたPウエルのウエル電位を上げる。

【0051】

閾値電圧(Vt)が低めのウエハの場合には、PDバックゲート電位変更回路106は、Nch−MOSFETのバックゲート電位(Nch−MOSFETが形成されたPウエル電位)を下げ、閾値電圧(Vt)を上げる。

【0052】

(2)閾値電圧(Vt)が高まる低温時は、閾値電圧(Vt)を下げる。すなわち、PDバックゲート電位変更回路106は、Nch−MOSFETが形成されたPウエルのウエル電位を上げる。

【0053】

閾値電圧(Vt)が低まる高温時には、閾値電圧(Vt)を上げる。PDバックゲート電位変更回路106は、Nch−MOSFETが形成されたPウエルのウエル電位を下げる。

【0054】

以上の最適値(温度とNch−MOSFETのバックゲート電位、サンプル別Vt情報とNch−MOSFETバックゲート電位)を事前にシミュレーション等で求めておき、ATCSR情報、閾値電圧(Vt)情報(ヒューズ108等で保持)にしたがって、PDバックゲート電位変更回路106にて動的に変更するようにしてもよい。

【0055】

次に、位相検出回路(PD)105のPch−MOSFETにおける閾値電圧制御の動作例を説明する。

(1)閾値電圧(Vt)が高めのウエハの場合、閾値電圧(Vt)を下げる。Pch−MOSFETは、シリコン基板に設けられたNウエル内にP+拡散層(ソース・ドレイン)とその間のゲートが作成され、バックゲートはNウエルとなる。PDバックゲート電位変更回路106は、Pch−MOSFETが形成されたNウエルのウエル電位を下げる。

【0056】

閾値電圧(Vt)が低めのウエハの場合、閾値電圧(Vt)を上げる(基板電位を上げる)。PDバックゲート電位変更回路106は、Pch−MOSFETが形成されたNウエルのウエル電位を上げる。

【0057】

(2)閾値電圧(Vt)が高まる低温時には、閾値電圧(Vt)を下げる。PDバックゲート電位変更回路106は、Pch−MOSFETが形成されたNウエルのウエル電位を下げる。

【0058】

閾値電圧(Vt)が低まる高温時には、閾値電圧(Vt)を上げる。PDバックゲート電位変更回路106は、Pch−MOSFETが形成されたNウエルのウエル電位を上げる。

【0059】

以上の最適値(温度とPch−MOSFETのバックゲート電位、サンプル別Vt情報とPch−MOSFETバックゲート電位)を事前にシミュレーション等で求めておき、ATCSR情報、閾値電圧(Vt)情報(Fuse等で保持)にしたがって動的に変更する。なお、Nch−MOSFET〜Pch−MOSFET間では、基板電位(ウエル電位)の上下が逆転する。

【0060】

上記(1)〜(2)の操作に伴って、位相検出回路(PD)105を構成するMOSFETの閾値電圧(Vt)は、常に一定に保たれる。したがって、従来サンプル別、同一サンプル動作温度別に、発生していたRep位相情報の変化が抑制される。よって、ロック位相の定常性が保たれる。

【0061】

なお、Nch−MOSFETとPch−MOSETのそれぞれのバックゲート電位を独立に制御する場合、シリコン基板上にPウエル、Nウエルを備えたツインウエルCMOSプロセスを用いてもよい。

【0062】

電流消費低減・低電圧動作のトレンドに対して、近時、半導体製品のトレンドとして、電流消費低減・低電圧動作が目標となっている。電流消費低減のためには、MOSFETの閾値電圧(Vt)を高め、リーク電流等を削減する手法が有効である。しかしながら、閾値電圧(Vt)の上昇に伴い、MOSFET動作におけるゲート・オーバードライブ(=Vgs(ゲート・ソース間電圧)−閾値電圧(Vt))が低下し、MOSFETの最低動作電圧を押し上げてしまう。閾値電圧(Vt)の上昇は、低電圧動作のトレンドに対して逆行するものといえる。そのため、現在は、同一チップ内の一部MOSFETのみ(設計・製造時の作り分け等により)、低閾値電圧(Vt)−MOSFETを採用する等して対処している。

【0063】

位相検出回路(PD)にも、低閾値電圧(Vt)−MOSFETが採用される例はあるが、本発明を適用することで、位相検出回路(PD)を構成するMOSFETの閾値電圧(Vt)を動的に変化させることができる。つまり、他要素と同一(あるいは、高めの)閾値電圧(Vt)を利用して製造しておき、動作時に、位相検出回路(PD)の基板電位変更回路106を用いて位相検出回路(PD)105の閾値電圧(Vt)のみを下げるといった対策が可能である。

【0064】

本実施形態により、MOSFETの閾値電圧(Vt)を動的に変更することで、位相検出回路(PD)に関しては、低閾値電圧(Vt)−MOSFETを用いずに、電流消費削減、低電圧動作というトレンドに対して、効果的な対応が可能といえる。

【0065】

また位相検出回路(PD)の低閾値電圧(Vt)化を動的に行えることから、半導体製品全体を、高閾値電圧(Vt)化して製造し、製品全体のリーク電流等の削減に注力しつつ、位相検出回路(PD)のMOSFETの閾値電圧(Vt)を変更することで、通常品と同様のロック位相を保つといった応用も可能である。

【0066】

本実施形態によれば、製造コスト低減を可能としている。すなわち、位相検出回路(PD)以外の各要素を通常閾値電圧(Vt)で設計できた場合、上記の低閾値電圧(Vt)−MOSFETは、位相検出回路(PD)のみのために導入せざるを得ず、製造コストの増加に繋がっていた。本発明を適用し、位相検出回路(PD)以外の各要素を、通常閾値電圧(Vt)−MOSFETにて製造できた場合には、低閾値電圧(Vt)−MOSFETの製造工程そのものを排除できるケースが想定できる。このため、製造工程の削減がコスト削減に結びつく事はいうまでも無い。

【0067】

本実施形態によれば、高周波動作への対応を可能としている。すなわち、上記述べてきたように、本発明によれば、ロック位相のサンプル間ばらつき、動作温度ばらつきを低減するものである。したがって高周波動作時に厳しいタイミングマージンを満たす上でも効果がある。高周波動作半導体は必然的にタイミングスペックが厳しくなるが、位相検出回路(PD)の形式が同じである場合、ロック位相のばらつき分布は変わらず、タイミングスペックへの影響が、相対的に大きくなっていく。ロック位相が、温度・閾値電圧(Vt)等により変化する事は、先に述べたとおりであるが、本発明を適用することにより、一定のロック位相を保つことで、タイミングスペックへの悪影響を抑える事が可能である。

【0068】

以上より、本実施形態の位相検出回路(PD)は高周波動作に対する利点をも兼ね備える。

【0069】

さらに、回路形式の柔軟さ、増幅回路つき位相検出回路(PD)への利用が可能となる。本発明によれば、MOSトランジスタの閾値電圧(Vt)の一定化を目的としたものである。したがって、閾値電圧(Vt)の変動がロック位相に対して大きな影響を及ぼし、従来、利用が見送られてきた形式の位相検出回路(PD)があれば、本発明を適用する事で、実現が容易となる。

【0070】

図6に示す回路例は、閾値電圧(Vt)変動に敏感なダイナミックアンプを利用した位相検出回路(PD)例である。ダイナミックアンプは、クロック信号の活性化時(例えばHighパルス)のときアンプを駆動する電流源が活性化されて増幅動作する。

【0071】

図6の位相比較回路は、CKと、CKBの電圧を比較する電圧コンパレータを構成するNch差動対(201、202)と、差動対の差動出力(DLSAT、DLSAB)を差動でラッチする差動型フリップフロップ(203、204、205、206)と、差動出力(DLSAT、DLSAB)をプリチャージ・イコライズする回路(211−213)と、クロック信号Repclkに基づき、差動対(201、202)の電流源(207)の活性化を制御する回路(210、208)を備えている。

【0072】

レプリカクロック信号Repclkの立ち上がりエッジの到来時に、相補のクロック信号CK、CKBの状態を把握するものである。レプリカクロック信号RepclkがLowからHighとなった時点でのクロック信号CK、CKBの状態をサンプルし、CKがHighであれば、比較結果を出力する正転端子COTにLowパルスを出力する。CKBがHighであれば、比較結果を出力する反転端子COBにLowパルスを出力する。レプリカクロック信号RepclkがHighからLowとなると、COT、COBはともHighとされ、次の比較動作(レプリカクロック信号RepclkのHighパルスの入力)までともにHighに保持される。なお、図6のCKBは、図1、図5の/CK(クロック信号CKの相補信号)を入力する。

【0073】

より詳しくは、図6に示すように、共通接続されたソースが、Nch−MOSFET207、208を介してVSSに接続され、ゲートにCK、CKB(/CK)を入力するNch−MOSFET201、202と、ソースが電源VPERIに接続されたPch−MOSFET204、206と、Pch−MOSFET204、206のドレインにそれぞれドレインが接続され、共通接続されたソースがNch−MOSFET209のドレインに接続されたNch−MOSFET203、205と、ソースが電源VPERIに接続されたPch−MOSFET212、213と、Pch−MOSFET212、213のドレイン間に接続されたPch−MOSFET211と、を備えている。Pch−MOSFET212のドレインは、DLSABノードにおいて、Nch−MOSFET201のドレインに接続され、さらにPch−MOSFET204とNch−MOSFET203のドレインの接続点に接続され、DLSABノードはインバータ214の入力に接続され、Pch−MOSFET213のドレインは、DLSATノードにおいて、Nch−MOSFET202のドレインに接続され、さらにPch−MOSFET206とNch−MOSFET205のドレインの接続点に接続され、DLSATノードはインバータ217の入力に接続され、Pch−MOSFET204とNch−MOSFET203と共通ドレインと共通ゲートは、Pch−MOSFET206とNch−MOSFET205の共通ゲートと共通ドレインに交差接続されている。インバータ217、214の出力信号は、インバータ(反転型出力バッファ)218、216でそれぞれ反転され、端子COT、COBに出力される。Pch−MOSFET211、212、213、Nch−MOSFET207、209は、レプリカクロック信号Repclkに接続され、Nch−MOSFET208のゲートは、レプリカクロック信号Repclkをインバータ210で反転した信号Repclk2が入力される。レプリカクロック信号RepclkがLowからHighとなると、Repclk2はインバータ210の伝播遅延時間経過後、HighからLowとなる。したがって、RepclkがLowからHighとなった後、Repclk2がHighからLowとなるまでの期間、Nch−MOSFET207、208がオンし、差動対トランジスタ201、202の共通ソースに定電流を供給する。特に制限されないが、Nch−MOSFET207が定電流源トランジスタ、Nch−MOSFET208は、Repclk2に基づき、定電流源トランジスタ207の活性化を制御するスイッチトランジスタとして構成される。Nch−MOSFET207、208、209はRepclkインプットディスチャージ回路、Nch−MOSFET201、202は、CK、CKBインプットディスチャージ回路、MOSFET203、204、205、206はダイナミックバッファ、211はイコライザ、Pch−MOSFET212、113はプリチャージ回路を構成している。電源VPERIは、図1のDRAMの周辺回路を駆動する電源である。図6において、VPERIの代わりに、内部電源電圧VDD等であってもよいとは勿論である。また位相検出回路の出力を差動出力COT、COBの代わりに、シングルエンデッド出力としてもよいことは勿論である。

【0074】

図6に示すように、本実施形態では、Nch−MOSFET201、202、207、208等のバックゲートは、VSSの変わりに、PDバックゲート電位変更回路106から出力されるバックゲートバイアス電圧VBBに接続されている。

【0075】

レプリカクロック(Repclk)の立ち上がりエッジ到来時のCK、CKBの電位極性を、インバータ214、217以降の情報として出力する。すなわち、Repclkの立ち上がりエッジのタイミングで、CK=Low、CKB=Highの場合、COT=High、COB=Lowとなる。すなわち、Repclkの位相がCKよりも進んでおり(Repclkの遅延不足である)、DLLのカウンタ回路102(図5参照)のカウンタ値を増加させてディレイライン100(図5参照)の遅延を増加させる。

【0076】

Repclkの立ち上がりエッジのタイミングで、CK=High、CKB=Lowの場合、COT=Low、COB=Highとなる。Repclkの位相がCKよりも遅れており(Repclkの遅延が過剰である)、DLLのカウンタ回路102(図5参照)のカウンタ値を減少させてディレイライン100(図5参照)の遅延を減少させる。

【0077】

レプリカクロック信号Repclkの立ち下がりエッジ以降から立ち上がりジ到来までのLow期間中、プリチャージ用のPch−MOSFET212、213およびイコライズ用のPch−MOSFET211がオン(導通状態)である。また、レプリカ・インプット・ディスチャージ220のNch−MOSFET208、209はオフ(非導通状態)となり、差動対(201、202)の出力ノードDLSAT、DLSAB共にHigh電位(VPERI)とされ(プリチャージ状態)、COT、COBはともにHigh電位とされる。なお、このプリチャージ状態においても、外部よりCK、CKBは入力される。Nch−MOSFET210、202は、一定程度のアナログゲートレベルであるが、レプリカ・インプットディスチャージ回路220=非活性状態とされ、Nch−MOSFET210、202の共通ソースの電位はほぼ一定に保たれる。

【0078】

レプリカクロック信号Repclkの立ち上がりエッジにて、DLSAB、および、Nch−MOSFET210、202のソースの電位が低下する。この際、Nch−MOSFET210、202のゲート電位は相補の関係であるため、両者には電位差が生じる(一方は他方よりも高電位である)。したがって、ノードDLSABとDLSAT間電位に差が生じる。DLSABとDLSATの間に電位差が生じた状態がダイナミックアンプ(入力と出力が交差接続された2つのCMOSインバータ((203、204)と(205、206)からなる)219に発生することからその電位差が差動増幅される。差動増幅されたDLSAT、DLSABノード間の電位差は、インバータ217、218、インバータ214、216を通って出力端子COT、COBから外部(図5のカウンタ回路102)に伝播する。

【0079】

位相検出回路(PD)に、ダイナミックアンプによる増幅動作が組み込まれているのは、半導体製品外部入力(CK、CKB)が、電源レベルの1/2などに設定されたリファレンスレベルVef付近の差動小振幅な信号となっているためである。すなわち、コモン電圧をVrefとして、Vref±ΔVとされる(振幅=2ΔV、Vref=VDD/2、Vref+ΔV<VDD)。小振幅による差動伝送は、信号伝播時の電力消費抑制などに効果が大きいものの、差動信号を受けるレシーバ(例えば位相検出回路(PD))にて増幅が必要である。

【0080】

この様な小振幅な差動信号を扱う回路では、特性に影響を及ぼす閾値電圧(Vt)の影響が相対的に大きい。サンプル別・動作温度別閾値電圧(Vt)の影響を抑えるため、従来、例えば以下の対策が行われていた。

【0081】

(A)インプット・ディスチャージトランジスタ(201、202、207−209)を低閾値電圧(Vt)とする。

【0082】

(B)インプット・ディスチャージトランジスタのサイズを拡大する。

【0083】

これらの対策は、レプリカクロック信号Repclkの立ち上がりの到来時のインプット・ディスチャージトランジスタの電流を増加し、ダイナミックアンプの増幅初期差電位の増加を目指すものである。本質的なサンプル・動作温度ばらつきを抑制できるものではないが、本来ならば増幅初期差電位が小さい状況下でも、ダイナミックアンプの動作の確実化がなされるため、相対的に動作の平準化に寄与できる。ただし、インプット・ディスチャージ・トランジスタの電流増加に伴い、位相検出回路(PD)全体の消費電流増加がおき、また本質的なばらつき低減策ではないなど問題が多い。

【0084】

これに対して、本実施形態による閾値電圧(Vt)の均一化は、図6に示した位相検出回路(PD)のような増幅回路を備える形式へ適用する。

【0085】

本実施形態によれば、Nch−MOSFT(201、202、207−209)のバックゲートは、PDバックゲート電位変更回路106からのバックゲートバイアス電圧VBBに接続され、例えばVBB>VSSとすることで、低閾値電圧化を達成する。また、従来のサンプル・温度別ばらつきを本質的に解消し、またインプット・ディスチャージトランジスタの大電流化も抑制することができる。

【0086】

さらに、本実施形態によれば以下のような作用効果を奏する。

【0087】

ATCSR(例えばDRAM等が標準的に備える温度計)、Fuse等によるサンプル別閾値電圧(Vt)情報を基に、位相検出回路(PD)の基板電位を変更する。基板電位の変更に伴い、位相検出回路(PD)の動作に由来するロック位相が補正され、平準化される。

【0088】

DLLへの適用にあたり、基板電位の変更は、位相検出回路(PD)にのみ適用すればよく、複雑化増大の程度が小さい。

【0089】

電流消費低減・低電圧動作のトレンドに対応可能である。

【0090】

製造コストの低減を可能としている。

【0091】

高周波動作への対応を可能としている。

【0092】

閾値電圧(Vt)変化に過敏な回路に適用することで、位相検出回路(PD)への実用可能性をさらに高めることができる。

【0093】

上記の通り、実施形態では、増幅回路(ダイナミックアンプ)付き位相検出回路(PD)への本発明の適用による、

・ロック位相の定常化、

・位相検出回路(PD)自体の消費電力の低減、

・位相検出回路(PD)を構成するMOSトランジスタサイズの小型化

等の作用について説明した。

【0094】

本発明の技術思想は、様々な半導体装置に適用することができる。例えば、CPU(Central Processing Unit)、MCU(Micro Control Unit)、DSP(Digital Signal Processor)、ASIC(Application Specific Integrated Circuit)、ASSP(Application Specific Standard Product)、メモリ(Memory)等の半導体装置全般に、本発明を適用することができる。このような本発明が適用された半導体装置の製品形態としては、例えば、SOC(システムオンチップ)、MCP(マルチチップパッケージ)やPOP(パッケージオンパッケージ)などが挙げられる。これらの任意の製品形態、パッケージ形態を有する半導体装置に対して本発明を適用することができる。また、トランジスタは、電界効果トランジスタ(Field Effect Transistor;FET)であれば良く、MOS(Metal Oxide Semiconductor)以外にもMIS(Metal−Insulator Semiconductor)、TFT(Thin Film Transistor)等の様々なFETに適用できる。トランジスタ等の様々なFETに適用できる。更に、装置内に一部のバイポーラ型トランジスタを有しても良い。更に、PMOSFET(P型チャネルMOSFET)は、第2導電型のトランジスタ、Nch−MOSFET(N型チャネルMOSFET)は、第1導電型のトランジスタの代表例である。

【0095】

本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0096】

1−1 メモリセルアレイ

1−2 センスアンプ

1−3 カラムデコーダ

1−4 ロウデコーダ

1−5 モードレジスタ

1−6 ロウアドレスバッファ及びリフレッシュカウンタ

1−7 カラムアドレスバッファ及びバーストカウンタ

1−8 データコントロール回路

1−9 コマンドデコーダ

1−10 コントロールロジック

1−11 ラッチ回路

1−12 DLL

1−13 入出力バッファ

1−14 クロックジェネレータ

100 ディレイライン

101 デコーダ回路

102 カウンタ回路

103 出力回路

104 レプリカ回路

105 位相検出回路(PD)

106 PDバックゲート電位変更回路(電源回路)

107 ATCSR(温度計)

108 ヒューズ(Fuse)等よるサンプル別Vt情報

204、206、211−213 Pch−MOSFET

201〜203、205、207−209 Nch−MOSFET

210、214、217 インバータ

216、218 出力バッファ(インバータ)

219 ダイナミックアンプ

220 レプリカクロック・インプットディスチャージ

1061、1062 入力回路

1063 バックゲート電位決定回路

1064 電圧源回路

1065 制御回路

【特許請求の範囲】

【請求項1】

第1の信号と第2の信号の位相を比較する位相検出回路と、

前記位相検出回路を構成する複数のトランジスタのうち所定のトランジスタの閾値電圧を補正する補正回路と、

を備えている半導体装置。

【請求項2】

半導体装置内部の温度を検出するセンサを備え、

前記補正回路が、前記センサで検出された温度情報に基づき、前記位相検出回路を構成する前記所定のトランジスタの閾値電圧を補正する請求項1記載の半導体装置。

【請求項3】

半導体装置毎又は半導体装置群単位でのトランジスタの閾値電圧情報を記憶する記憶部を備え、

前記補正回路は、前記記憶部に記憶される前記半導体装置毎又は半導体装置群単位でのトランジスタの閾値電圧情報に基づき、前記位相検出回路を構成する前記所定のトランジスタの閾値電圧を補正する請求項1又は2記載の半導体装置。

【請求項4】

前記補正回路が、

前記位相検出回路を構成する前記所定のトランジスタのバックゲートに与える電圧を生成する電圧源回路を備え、前記センサからの前記温度情報、及び/又は、前記記憶部に記憶された前記トランジスタの閾値電圧情報に基づき、前記バックゲート電圧を可変に設定する請求項3記載の半導体装置。

【請求項5】

半導体装置外部信号から入力された入力信号を遅延させるディレイラインと、前記位相検出回路と、カウンタ回路と、を含むDLL(Delay Lock Loop)を備え

前記位相検出回路は、前記ディレイラインから出力された信号を帰還入力し、前記帰還入力した前記信号と、前記半導体装置外部信号から入力された前記入力信号とを、前記第1及び第2の信号として入力して位相を比較し、

前記カウンタ回路は、前記位相検出回路での位相比較結果に基づきカウント値を可変させ、前記カウント値に基づき前記ディレイラインの遅延時間を可変させる、請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

前記ディレイラインから出力される前記信号に応答してデータ信号を出力端子に出力する出力バッファ回路の遅延を模したレプリカ回路を備え、

前記ディレイラインから出力された信号は前記レプリカ回路に入力され、前記レプリカ回路から出力される信号が前記位相検出回路に帰還入力される請求項5記載の半導体装置。

【請求項7】

前記位相検出回路は、

前記第1及び第2の信号の一方の信号を差動で入力する第1導電型の差動トランジスタ対と、

前記第1及び第2の信号の他方の信号の活性化のタイミングから所定期間、前記差動対に駆動電流を供給する第1導電型の電流源トランジスタと、

前記第1及び第2の信号の前記他方の信号に基づき、前記差動回路の差動出力を、所定の電位でプリチャージ・イコライズする受ける第2導電型のプリチャージ・イコライズ回路と、

入力と出力がそれぞれ交差接続され、前記差動回路の差動出力に接続された第1及び第2のインバータと、

前記第1及び第2のインバータの電源パスに挿入され、前記第1及び第2の信号の前記他方の信号に基づき、導通・非導通が制御される第1導電型のトランジスタスイッチと、

前記差動回路の差動出力をそれぞれ受ける第1及び第2の出力バッファ回路と、

を備え、

前記第1導電型の差動トランジスタ対、前記第1導電型のトランジスタスイッチ、前記第1導電型の電流源トランジスタのバックゲートが前記補正回路の出力に接続されている、請求項6記載の半導体装置。

【請求項8】

前記第1の信号が、半導体装置外部信号から入力された相補の外部クロック信号であり、

前記第2の信号が、前記レプリカ回路から出力される信号であり、

前記第2導電型のプリチャージ・イコライズ回路、前記第1導電型のトランジスタスイッチ、前記第1導電型の電流源トランジスタが、前記第2の信号に基づき、活性化と非活性化が制御される、請求項7記載の半導体装置。

【請求項9】

温度を検出する前記センサとして、前記半導体装置内部に組み込まれた自動温度補償セルフリフレッシュ機能の温度センサを用いる、請求項2記載の半導体装置。

【請求項1】

第1の信号と第2の信号の位相を比較する位相検出回路と、

前記位相検出回路を構成する複数のトランジスタのうち所定のトランジスタの閾値電圧を補正する補正回路と、

を備えている半導体装置。

【請求項2】

半導体装置内部の温度を検出するセンサを備え、

前記補正回路が、前記センサで検出された温度情報に基づき、前記位相検出回路を構成する前記所定のトランジスタの閾値電圧を補正する請求項1記載の半導体装置。

【請求項3】

半導体装置毎又は半導体装置群単位でのトランジスタの閾値電圧情報を記憶する記憶部を備え、

前記補正回路は、前記記憶部に記憶される前記半導体装置毎又は半導体装置群単位でのトランジスタの閾値電圧情報に基づき、前記位相検出回路を構成する前記所定のトランジスタの閾値電圧を補正する請求項1又は2記載の半導体装置。

【請求項4】

前記補正回路が、

前記位相検出回路を構成する前記所定のトランジスタのバックゲートに与える電圧を生成する電圧源回路を備え、前記センサからの前記温度情報、及び/又は、前記記憶部に記憶された前記トランジスタの閾値電圧情報に基づき、前記バックゲート電圧を可変に設定する請求項3記載の半導体装置。

【請求項5】

半導体装置外部信号から入力された入力信号を遅延させるディレイラインと、前記位相検出回路と、カウンタ回路と、を含むDLL(Delay Lock Loop)を備え

前記位相検出回路は、前記ディレイラインから出力された信号を帰還入力し、前記帰還入力した前記信号と、前記半導体装置外部信号から入力された前記入力信号とを、前記第1及び第2の信号として入力して位相を比較し、

前記カウンタ回路は、前記位相検出回路での位相比較結果に基づきカウント値を可変させ、前記カウント値に基づき前記ディレイラインの遅延時間を可変させる、請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

前記ディレイラインから出力される前記信号に応答してデータ信号を出力端子に出力する出力バッファ回路の遅延を模したレプリカ回路を備え、

前記ディレイラインから出力された信号は前記レプリカ回路に入力され、前記レプリカ回路から出力される信号が前記位相検出回路に帰還入力される請求項5記載の半導体装置。

【請求項7】

前記位相検出回路は、

前記第1及び第2の信号の一方の信号を差動で入力する第1導電型の差動トランジスタ対と、

前記第1及び第2の信号の他方の信号の活性化のタイミングから所定期間、前記差動対に駆動電流を供給する第1導電型の電流源トランジスタと、

前記第1及び第2の信号の前記他方の信号に基づき、前記差動回路の差動出力を、所定の電位でプリチャージ・イコライズする受ける第2導電型のプリチャージ・イコライズ回路と、

入力と出力がそれぞれ交差接続され、前記差動回路の差動出力に接続された第1及び第2のインバータと、

前記第1及び第2のインバータの電源パスに挿入され、前記第1及び第2の信号の前記他方の信号に基づき、導通・非導通が制御される第1導電型のトランジスタスイッチと、

前記差動回路の差動出力をそれぞれ受ける第1及び第2の出力バッファ回路と、

を備え、

前記第1導電型の差動トランジスタ対、前記第1導電型のトランジスタスイッチ、前記第1導電型の電流源トランジスタのバックゲートが前記補正回路の出力に接続されている、請求項6記載の半導体装置。

【請求項8】

前記第1の信号が、半導体装置外部信号から入力された相補の外部クロック信号であり、

前記第2の信号が、前記レプリカ回路から出力される信号であり、

前記第2導電型のプリチャージ・イコライズ回路、前記第1導電型のトランジスタスイッチ、前記第1導電型の電流源トランジスタが、前記第2の信号に基づき、活性化と非活性化が制御される、請求項7記載の半導体装置。

【請求項9】

温度を検出する前記センサとして、前記半導体装置内部に組み込まれた自動温度補償セルフリフレッシュ機能の温度センサを用いる、請求項2記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−38518(P2013−38518A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−171331(P2011−171331)

【出願日】平成23年8月4日(2011.8.4)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月4日(2011.8.4)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]