半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

【発明の詳細な説明】

【技術分野】

【0001】

発明の技術分野は、半導体装置に関する。ここで、半導体装置とは、半導体特性を利用す

ることで機能する素子および装置全般を指すものである。

【背景技術】

【0002】

金属酸化物は多様に存在し、さまざまな用途に用いられている。酸化インジウムはよく知

られた材料であり、液晶表示装置などに必要とされる透明電極の材料として用いられてい

る。

【0003】

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物としては

、例えば、酸化タングステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このよう

な金属酸化物をチャネル形成領域に用いた薄膜トランジスタが既に知られている(例えば

、特許文献1乃至特許文献4、非特許文献1等参照)。

【0004】

ところで、金属酸化物には、一元系酸化物のみでなく多元系酸化物も知られている。例え

ば、ホモロガス相を有するInGaO3(ZnO)m(m:自然数)は、In、Gaおよ

びZnを有する多元系酸化物半導体として知られている(例えば、非特許文献2乃至非特

許文献4等参照)。

【0005】

そして、上記のようなIn−Ga−Zn系酸化物で構成される酸化物半導体も、薄膜トラ

ンジスタのチャネル形成領域に適用可能であることが確認されている(例えば、特許文献

5、非特許文献5および非特許文献6等参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭60−198861号公報

【特許文献2】特開平8−264794号公報

【特許文献3】特表平11−505377号公報

【特許文献4】特開2000−150900号公報

【特許文献5】特開2004−103957号公報

【非特許文献】

【0007】

【非特許文献1】M. W. Prins, K. O. Grosse−Holz, G. Muller, J. F. M. Cillessen, J. B. Giesbers, R. P. Weening, and R. M. Wolf、「A ferroelectric transparent thin−film transistor」、 Appl. Phys. Lett.、17 June 1996、 Vol.68 p.3650−3652

【非特許文献2】M. Nakamura, N. Kimizuka, and T. Mohri、「The Phase Relations in the In2O3−Ga2ZnO4−ZnO System at 1350℃」、J. Solid State Chem.、1991、Vol.93, p.298−315

【非特許文献3】N. Kimizuka, M. Isobe, and M. Nakamura、「Syntheses and Single−Crystal Data of Homologous Compounds, In2O3(ZnO)m(m=3,4, and 5), InGaO3(ZnO)3, and Ga2O3(ZnO)m(m=7,8,9, and 16) in the In2O3−ZnGa2O4−ZnO System」、 J. Solid State Chem.、1995、Vol.116, p.170−178

【非特許文献4】中村真佐樹、君塚昇、毛利尚彦、磯部光正、「ホモロガス相、InFeO3(ZnO)m(m:自然数)とその同型化合物の合成および結晶構造」、固体物理、1993年、Vol.28、No.5、p.317−327

【非特許文献5】K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono、「Thin−film transistor fabricated in single−crystalline transparent oxide semiconductor」、SCIENCE、2003、Vol.300、p.1269−1272

【非特許文献6】K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono、「Room−temperature fabrication of transparent flexible thin−film transistors using amorphous oxide semiconductors」、NATURE、2004、Vol.432 p.488−492

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところで、トランジスタの動作の高速化、トランジスタの低消費電力化、低価格化、など

を達成するためには、トランジスタの微細化は必須である。

【0009】

トランジスタを微細化する場合には、製造工程において発生する不良が大きな問題となる

。例えば、トランジスタを微細化する場合には、短チャネル効果の問題も生じる。短チャ

ネル効果とは、トランジスタの微細化(チャネル長(L)の縮小)に伴って顕在化する電

気特性の劣化である。短チャネル効果は、ドレインの電界の効果がソースにまでおよぶこ

とに起因するものである。短チャネル効果の具体例としては、しきい値電圧の低下、S値

の増大、漏れ電流の増大などがある。特に、酸化物半導体を用いたトランジスタは、室温

においてシリコンを用いたトランジスタと比較してオフ電流が小さいことが知られており

、これは熱励起により生じるキャリアが少ない、つまりキャリア密度が小さいためと考え

られる。キャリア密度が小さい材料を用いたトランジスタでは、しきい値電圧の低下など

の短チャネル効果が現れやすい傾向にある。

【0010】

そこで、開示する発明の一態様は、不良を抑制しつつ微細化を達成した半導体装置の提供

を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供

を目的の一とする。

【課題を解決するための手段】

【0011】

本発明の一態様は、酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン

電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設

けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物

半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、

且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極

と重なる半導体装置である。

【0012】

本発明の他の一態様は、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲ

ート絶縁層と、ゲート絶縁層上に設けられた酸化物半導体層と、酸化物半導体層上に接し

て設けられた絶縁層と、絶縁層及びゲート絶縁層上に設けられたソース電極及びドレイン

電極と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極また

はドレイン電極と接し、酸化物半導体層の端面の上端と、絶縁層の端面の下端とは一致す

る半導体装置である。

【0013】

本発明の他の一態様は、基板上に設けられた酸化物半導体層と、酸化物半導体層上に接し

て設けられた絶縁層と、基板及び絶縁層上に設けられたソース電極及びドレイン電極と、

絶縁層、ソース電極及びドレイン電極上に設けられたゲート絶縁層と、ゲート絶縁層上に

設けられたゲート電極と、を有し、酸化物半導体層は、該酸化物半導体層の端面において

、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層

を介して、ソース電極またはドレイン電極と重なる半導体装置である。

【0014】

上記において、酸化物半導体層の端面の上端と、絶縁層の端面の下端とは一致するのが好

ましい。また、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層よりも高

抵抗である第2の導電層と、を含み、第2の導電層において、酸化物半導体層と接するの

が好ましい。

【0015】

本発明の他の一態様は、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲ

ート絶縁層と、ゲート絶縁層上に設けられた第1の導電層と、第1の導電層よりも高抵抗

である第2の導電層と、を含むソース電極及びドレイン電極と、ゲート電極と重畳し、か

つ第2の導電層に接して設けられた酸化物半導体層と、第1の導電層と、酸化物半導体層

との間に設けられた絶縁層と、を有する半導体装置である。

【0016】

上記において、第2の導電層は、第1の導電層の端面よりチャネル長方向に伸長した領域

を有するのが好ましい。また、上記において、第2の導電層の膜厚は、5nm乃至15n

mとすると良い。また、第2の導電層は、金属の窒化物とすると良い。

【0017】

ここで半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。例えば

、表示装置や記憶装置、集積回路などは半導体装置に含まれうる。

【0018】

また、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」また

は「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極

」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外し

ない。また、「上」「下」の用語は説明の便宜のために用いる表現に過ぎず、特に言及す

る場合を除き、その上下を入れ替えたものも含む。

【0019】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限

定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、

その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配

線」が一体となって形成されている場合などをも含む。

【0020】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や

、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため

、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることがで

きるものとする。

【0021】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの

」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの

」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタ

などのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有す

る素子などが含まれる。

【発明の効果】

【0022】

開示する発明の一態様によって、ソース電極またはドレイン電極が酸化物半導体層と接す

る界面の近傍を高抵抗領域とすることで、ソース電極とドレイン電極の間の電界を緩和す

ることができる。このため、しきい値電圧低下などの短チャネル効果を抑制させることが

できる。

【0023】

このような効果により、微細化に伴う問題点が解消されることになるため、結果として、

トランジスタサイズを十分に小さくすることが可能になる。トランジスタサイズを十分に

小さくすることで、半導体装置の占める面積が小さくなり、半導体装置の取り数が増大す

る。これにより、半導体装置あたりの製造コストは抑制される。また、半導体装置が小型

化されるため、従来の半導体装置と同程度の大きさで、さらに機能が高められた半導体装

置を実現することができる。また、チャネル長の縮小による、動作の高速化、低消費電力

化などの効果を得ることもできる。つまり、開示する発明の一態様により酸化物半導体を

用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ること

が可能である。

【0024】

このように、開示する発明の一態様によって、不良を抑制しつつ、または、良好な特性を

維持しつつ、微細化を達成した半導体装置を提供することができる。

【図面の簡単な説明】

【0025】

【図1】半導体装置の断面図

【図2】半導体装置の作製工程に係る断面図

【図3】半導体装置の断面図

【図4】半導体装置の作製工程に係る断面図

【図5】半導体装置の断面図

【図6】半導体装置の作製工程に係る断面図

【図7】半導体装置の断面図

【図8】半導体装置の作製工程に係る断面図

【図9】半導体装置の回路図の例

【図10】半導体装置の回路図の例

【図11】半導体装置の回路図の例

【図12】電子機器の例

【発明を実施するための形態】

【0026】

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下

の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および

詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下

に示す実施の形態の記載内容に限定して解釈されるものではない。

【0027】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実

際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必

ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0028】

なお、本明細書等における「第1」、「第2」、「第3」などの序数は、構成要素の混同

を避けるために付すものであり、数的に限定するものではないことを付記する。

【0029】

(実施の形態1)

本実施の形態では、開示する発明の一態様に係る半導体装置の構成およびその作製工程の

例について、図1及び図2を参照して説明する。

【0030】

〈半導体装置の構成例〉

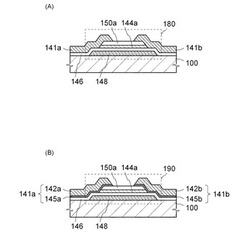

図1(A)及び図1(B)に、半導体装置の例として、トランジスタの断面構造を示す。

図1(A)及び図1(B)では、開示する発明の一態様に係るトランジスタとして、ボト

ムゲート型のトランジスタを示している。

【0031】

図1(A)に示すトランジスタ180は、基板100上に、ゲート電極148と、ゲート

電極148上に設けられたゲート絶縁層146と、ゲート絶縁層146上に設けられた酸

化物半導体層144aと、酸化物半導体層144a上に接して設けられた絶縁層150a

と、ゲート絶縁層146及び絶縁層150a上に設けられたソース電極141a及びドレ

イン電極141bと、を有している。

【0032】

図1(A)に示すトランジスタ180において、酸化物半導体層144aは、その端面に

おいてソース電極141a及びドレイン電極141bと接している。また、酸化物半導体

層144aの端面の上端と絶縁層150aの端面の下端とは一致しており、酸化物半導体

層144aは、その上方で絶縁層150aを介して、ソース電極141a及びドレイン電

極141bと重なっている。つまり、酸化物半導体層144aは、端面でのみ、ソース電

極141a及びドレイン電極141bと接している。

【0033】

本明細書中で、端面とは、例えば、酸化物半導体層および導電膜などを、基板表面に概略

垂直に切断したときの面を指す。または、基板表面に対して垂直方向から±30°以上6

0°以下の範囲で切断したときの面を指す。つまり、膜状の構造をエッチングすることに

より生じる切断面を指すものとする。また、本明細書中で、一致とは、概略一致も含むも

のとする。例えば、同じマスクを用いてエッチングした積層構造の層Aの端面と層Bの端

面は一致しているとみなす。

【0034】

また、図1(B)に示すトランジスタ190のように、ソース電極141aを、第2の導

電層145aと第1の導電層142aとを順に積層した構造とし、ドレイン電極141b

を、第2の導電層145bと第1の導電層142bとを順に積層した構造とすることもで

きる。

【0035】

〈トランジスタの作製工程の例〉

以下、図2を用いて、図1(A)に示すトランジスタの作製工程の例について説明する。

【0036】

まず、絶縁表面を有する基板100上に導電膜を成膜し、当該導電膜を選択的にエッチン

グしてゲート電極148を形成する(図2(A)参照)。ただし、基板100の表面は全

て絶縁表面とする必要はなく、一部に導電性の領域が形成されていてもよい。

【0037】

基板100に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処

理に耐えうる程度の耐熱性を有していることが必要となる。例えば、ガラス基板、セラミ

ック基板、石英基板、サファイア基板などの基板を用いることができる。また、絶縁表面

を有していれば、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、

シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能で

あり、これらの基板上に半導体素子が設けられていてもよい。また、基板100上に下地

膜が設けられていても良い。

【0038】

ゲート電極148となる導電膜は、スパッタ法をはじめとするPVD法や、プラズマCV

D法などのCVD法を用いて形成することができる。ゲート電極148となる導電膜の材

料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステン

から選ばれた元素やこれらの窒化物、上述した元素を成分とする合金等を用いることがで

きる。マンガン、マグネシウム、ジルコニウム、ベリリウムのいずれか、またはこれらを

複数組み合わせた材料を用いてもよい。また、アルミニウムに、チタン、タンタル、タン

グステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素、またはこれ

らを複数組み合わせた材料を用いてもよい。また、酸化インジウム(In2O3)、酸化

スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金(In2O3−S

nO2、ITOと略記する場合がある)、酸化インジウム酸化亜鉛合金(In2O3−Z

nO)、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させた

導電性の金属酸化物を用いても良い。

【0039】

ただし、ゲート電極148の材料の仕事関数が酸化物半導体層144aの電子親和力と同

程度、またはそれより小さいと、トランジスタを微細化した場合に、そのしきい値電圧が

マイナス側にシフトすることがある。よって、ゲート電極148には、酸化物半導体層1

44aの電子親和力より大きい仕事関数を有する材料を用いる事が好ましい。このような

材料としては、例えば、タングステン、白金、金、p型の導電性を付与したシリコンなど

がある。

【0040】

また、ゲート電極148は、単層構造としても良いし、2層以上の積層構造としても良い

。ゲート電極148の厚さは、10nm〜400nm、好ましくは100nm〜200n

mとする。

【0041】

また、ゲート電極148を形成するエッチングに用いるマスク形成時の露光には、紫外線

、KrFレーザ光、またはArFレーザ光を用いるのが好適である。特に、加工寸法が2

5nm未満の露光を行う場合には、数nm〜数10nmと極めて波長が短い超紫外線(E

xtreme Ultraviolet)を用いてマスク形成時の露光を行うのが好適で

ある。超紫外線による露光は、解像度が高く焦点深度も大きいため、微細化には適してい

る。

【0042】

導電膜をエッチングする際に、図2(A)に示すように、ゲート電極148の端部をテー

パー形状とすることが好ましい。後の工程で、ゲート電極148上にゲート絶縁層146

などを形成する際、ゲート絶縁層146などにおける段切れを生じさせないようにするた

めである。

【0043】

次に、ゲート電極148を覆うように、ゲート絶縁層146を形成する(図2(B)参照

)。

【0044】

ゲート絶縁層146は、CVD法やスパッタ法等を用いて形成することができる。また、

ゲート絶縁層146は、酸化シリコン、窒化シリコン、酸化窒化シリコン、酸化アルミニ

ウム、酸化タンタル、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート(Hf

SixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSix

Oy(x>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAlxOy

(x>0、y>0))、などを含むように形成するのが好適である。ゲート絶縁層146

は、単層構造としても良いし、積層構造としても良い。また、その厚さは特に限定されな

いが、半導体装置を微細化する場合には、トランジスタの動作を確保するために薄くする

のが望ましい。例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好

ましくは10nm以上50nm以下とすることができる。

【0045】

上述のように、ゲート絶縁層146を薄くすると、トンネル効果などに起因するゲートリ

ークが問題となる。ゲートリークの問題を解消するには、ゲート絶縁層146に、酸化ハ

フニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSixOy(

x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSixOy(x>0

、y>0))、窒素が添加されたハフニウムアルミネート(HfAlxOy(x>0、y

>0))、などの高誘電率(high−k)材料を用いると良い。高誘電率(high−

k)材料をゲート絶縁層146に用いることで、電気的特性を確保しつつ、ゲートリーク

を抑制させられるために膜厚を大きくすることが可能になる。なお、高誘電率(high

−k)材料を含む膜と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリ

コン、酸化アルミニウムなどのいずれかを含む膜との積層構造としてもよい。

【0046】

次に、スパッタ法を用いて、ゲート絶縁層146上に酸化物半導体層144を成膜し、当

該酸化物半導体層144上に絶縁層150を成膜する(図2(C)参照)。

【0047】

酸化物半導体層144は、四元系金属酸化物であるIn−Sn−Ga−Zn−O系や、三

元系金属酸化物であるIn−Ga−Zn−O系、In−Sn−Zn−O系、In−Al−

Zn−O系、Sn−Ga−Zn−O系、Al−Ga−Zn−O系、Sn−Al−Zn−O

系や、二元系金属酸化物であるIn−Zn−O系、Sn−Zn−O系、Al−Zn−O系

、Zn−Mg−O系、Sn−Mg−O系、In−Mg−O系や、In−O系、Sn−O系

、Zn−O系などを用いて形成することができる。

【0048】

中でも、In−Ga−Zn−O系の酸化物半導体材料は、無電界時の抵抗が十分に高くオ

フ電流を十分に小さくすることが可能であり、また、電界効果移動度も高いため、半導体

装置に用いる半導体材料としては好適である。

【0049】

In−Ga−Zn−O系の酸化物半導体材料の代表例としては、InGaO3(ZnO)

m(m>0)で表記されるものがある。また、Gaに代えてMを用い、InMO3(Zn

O)m(m>0)のように表記される酸化物半導体材料がある。ここで、Mは、ガリウム

(Ga)、アルミニウム(Al)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)、

コバルト(Co)などから選ばれた一の金属元素または複数の金属元素を示す。例えば、

Mとしては、Ga、GaおよびAl、GaおよびFe、GaおよびNi、GaおよびMn

、GaおよびCoなどを適用することができる。なお、上述の組成は結晶構造から導き出

されるものであり、あくまでも一例に過ぎないことを付記する。

【0050】

酸化物半導体層144をスパッタ法で作製するためのターゲットとしては、In:Ga:

Zn=1:x:y(xは0以上、yは0.5以上5以下)の組成比を有するものを用いる

のが好適である。例えば、In:Ga:Zn=1:1:1[atom比](x=1、y=

1)、(すなわち、In2O3:Ga2O3:ZnO=1:1:2[mol数比])の組

成比を有する金属酸化物ターゲットなどを用いることができる。また、In:Ga:Zn

=1:1:0.5[atom比](x=1、y=0.5)、(すなわち、In2O3:G

a2O3:ZnO=1:1:1[mol数比])の組成比を有する金属酸化物ターゲット

や、In:Ga:Zn=1:1:2[atom比](x=1、y=2)、(すなわち、I

n2O3:Ga2O3:ZnO=1:1:4[mol数比])の組成比を有する金属酸化

物ターゲットや、In:Ga:Zn=1:0:1[atom比](x=0、y=1)、(

すなわち、In2O3:ZnO=1:2[mol数比])の組成比を有する金属酸化物タ

ーゲットを用いることもできる。

【0051】

本実施の形態では、非晶質構造の酸化物半導体層144を、In−Ga−Zn−O系の金

属酸化物ターゲットを用いるスパッタ法により形成することとする。

【0052】

金属酸化物ターゲット中の金属酸化物の相対密度は80%以上、好ましくは95%以上、

さらに好ましくは99.9%以上である。相対密度の高い金属酸化物ターゲットを用いる

ことにより、緻密な構造の酸化物半導体層144を形成することが可能である。

【0053】

酸化物半導体層144の形成雰囲気は、希ガス(代表的にはアルゴン)雰囲気、酸素雰囲

気、または、希ガス(代表的にはアルゴン)と酸素との混合雰囲気とするのが好適である

。具体的には、例えば、水素、水、水酸基、水素化物などの不純物が、濃度1ppm以下

(望ましくは濃度10ppb以下)にまで除去された高純度ガス雰囲気を用いるのが好適

である。

【0054】

酸化物半導体層144の形成の際には、例えば、減圧状態に保持された処理室内に被処理

物(ここでは、基板100を含む構造体)を保持し、被処理物の温度が100℃以上55

0℃未満、好ましくは200℃以上400℃以下となるように被処理物を熱する。または

、酸化物半導体層144の形成の際の被処理物の温度は、室温としてもよい。そして、処

理室内の水分を除去しつつ、水素や水などが除去されたスパッタガスを導入し、上記金属

酸化物ターゲットを用いて酸化物半導体層144を形成する。被処理物を熱しながら酸化

物半導体層144を形成した際、酸化物半導体層144に含まれる不純物を低減させるこ

とができる。また、スパッタによる損傷を軽減することができる。処理室内の水分を除去

するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、

イオンポンプ、チタンサブリメーションポンプなどを用いることができる。また、ターボ

ポンプにコールドトラップを加えたものを用いてもよい。クライオポンプなどを用いて排

気することで、処理室から水素や水などを除去することができるため、酸化物半導体層1

44中の不純物濃度を低減できる。

【0055】

酸化物半導体層144の形成条件としては、例えば、被処理物とターゲットとの間の距離

が170mm、圧力が0.4Pa、直流(DC)電力が0.5kW、雰囲気が酸素(酸素

100%)雰囲気、またはアルゴン(アルゴン100%)雰囲気、または酸素とアルゴン

の混合雰囲気、といった条件を適用することができる。なお、パルス直流(DC)電源を

用いると、ごみ(成膜時に形成される粉状の物質など)を低減でき、膜厚分布も均一とな

るため好ましい。酸化物半導体層144の膜厚は、例えば、3nm以上30nm以下、好

ましくは5nm以上15nm以下とする。このような厚さの酸化物半導体層144を用い

ることで、後の工程で形成される、ソース電極141aと酸化物半導体層144aの接触

面積、及びドレイン電極141bと酸化物半導体層144aの接触面積を低減できるので

、微細化に伴う短チャネル効果を抑制させることが可能である。ただし、適用する酸化物

半導体材料や、半導体装置の用途などにより適切な厚さは異なるから、その厚さは、用い

る材料や用途などに応じて選択することもできる。

【0056】

なお、酸化物半導体層144をスパッタ法により形成する前には、アルゴンガスを導入し

てプラズマを発生させる逆スパッタを行い、処理表面(例えばゲート絶縁層146の表面

)の付着物を除去するのが好適である。ここで、逆スパッタとは、通常のスパッタにおい

ては、スパッタターゲットにイオンを衝突させるところを、逆に、処理表面にイオンを衝

突させることによってその表面を改質する方法のことをいう。処理表面にイオンを衝突さ

せる方法としては、アルゴン雰囲気下で処理表面側に高周波電圧を印加して、被処理物付

近にプラズマを生成する方法などがある。なお、アルゴン雰囲気に代えて窒素、ヘリウム

、酸素などによる雰囲気を適用してもよい。

【0057】

それから、酸化物半導体層144の上に絶縁層150を成膜する。絶縁層150は、例え

ば、膜厚1nm以上50nm以下、好ましくは、3nm以上10nm以下で形成する。本

実施の形態においては、絶縁層150として、酸化シリコン膜を形成するものとする。

【0058】

また、酸化物半導体層144及び絶縁層150は、大気に触れさせることなく連続的に成

膜しても良い。このように成膜することによって、大気成分や大気中に浮遊する汚染不純

物元素(例えば、水素や水など)に汚染されることなく、酸化物半導体層144と絶縁層

150の界面を形成することができるので、トランジスタ特性のばらつきを低減させるこ

とができる。

【0059】

次に、マスクを用いたエッチングなどの方法によって酸化物半導体層144及び絶縁層1

50を選択的にエッチングして、島状の酸化物半導体層144a及び島状の絶縁層150

aを形成する(図2(D)参照)。ここで、島状の酸化物半導体層144aは、ゲート電

極148と重畳する領域に形成する。

【0060】

島状の酸化物半導体層144a及び島状の絶縁層150aを形成するエッチングに用いる

マスク形成時の露光には、紫外線、KrFレーザ光、またはArFレーザ光を用いるのが

好適である。特に、チャネル長(L)が25nm未満の露光を行う場合には、数nm〜数

10nmと極めて波長が短い超紫外線(Extreme Ultraviolet)を用

いてマスク形成時の露光を行うのが好適である。超紫外線による露光は、解像度が高く焦

点深度も大きいため、微細化には適している。

【0061】

絶縁層150及び酸化物半導体層144のエッチングには、ウェットエッチングまたはド

ライエッチングを用いることができ、ウェットエッチングとドライエッチングを組み合わ

せて用いることもできる。絶縁層150及び酸化物半導体層144を所望の形状にエッチ

ングできるよう、材料に合わせてエッチング条件(エッチングガス、エッチング液、エッ

チング時間、温度等)を適宜設定する。ただし、トランジスタのチャネル長(L)を微細

に加工するためには、ドライエッチングを用いるのが好ましい。ドライエッチングに用い

るエッチングガスとしては、例えば、六フッ化硫黄(SF6)、三フッ化窒素(NF3)

、トリフルオロメタン(CHF3)、オクタフルオロシクロブタン(C4F8)などのフ

ッ素を含むガス、四フッ化メタン(CF4)と水素の混合ガス等を用いることができ、希

ガス(ヘリウム(He)、アルゴン(Ar)、キセノン(Xe))、一酸化炭素、二酸化

炭素等を添加しても良い。

【0062】

また、ドライエッチングとしては、平行平板型RIE(Reactive Ion Et

ching)法や、ICP(Inductively Coupled Plasma:

誘導結合型プラズマ)エッチング法などを用いることができる。この場合にも、エッチン

グ条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側

の電極温度等)は適宜設定する必要がある。

【0063】

また、酸化物半導体層144及び絶縁層150をエッチングする際に、図2(D)に示す

ように、酸化物半導体層144及び絶縁層150の端部をテーパー形状とすることが好ま

しい。後の工程で、酸化物半導体層144及び絶縁層150上に、ソース電極141a及

びドレイン電極141bを形成する際、ソース電極141a及びドレイン電極141bな

どにおける段切れを生じさせないようにするためである。

【0064】

このように、絶縁層150及び酸化物半導体層144を一括でエッチングすることにより

、酸化物半導体層144aの端面の上端と絶縁層150aの端面の下端を容易に一致させ

ることができる。

【0065】

ここで、トランジスタ180のチャネル長(L)は、酸化物半導体層144aの幅によっ

て決定される。チャネル長(L)は、トランジスタ180の用途によって異なるが、例え

ば10nm以上1000nm以下、好ましくは20nm以上400nm以下とすることが

できる。

【0066】

なお、本実施の形態では、絶縁層150及び酸化物半導体層144のエッチングを一括で

行ったが、これに限られることなく、絶縁層150と酸化物半導体層144のエッチング

を逐次行うこともできる。また、酸化物半導体層144を成膜し、選択的エッチングで島

状の酸化物半導体層144aを形成した後、絶縁層150を成膜し、選択的エッチングで

島状の絶縁層150aを形成することもできる。

【0067】

それから、酸化物半導体層144に対して、熱処理(第1の熱処理)を行うことが望まし

い。この第1の熱処理によって酸化物半導体層144中の、過剰な水素(水や水酸基を含

む)を除去し、酸化物半導体層144の構造を整え、エネルギーギャップ中の欠陥準位を

低減させることができる。第1の熱処理の温度は、例えば、300℃以上550℃未満、

または400℃以上500℃以下とする。

【0068】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、

450℃、1時間の条件で行うことができる。この間、酸化物半導体層144は大気に触

れさせず、水や水素の混入が生じないようにする。

【0069】

熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射

によって、被処理物を加熱する装置を用いても良い。例えば、GRTA(Gas Rap

id Thermal Anneal)装置、LRTA(Lamp Rapid The

rmal Anneal)装置等のRTA(Rapid Thermal Anneal

)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ

、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ラン

プなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。

GRTA装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴン

などの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が

用いられる。

【0070】

例えば、第1の熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分

間熱した後、当該不活性ガス雰囲気から被処理物を取り出すGRTA処理を行ってもよい

。GRTA処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温

度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素

を含むガスに切り替えても良い。酸素を含む雰囲気において第1の熱処理を行うことで、

酸素欠損に起因するエネルギーギャップ中の欠陥準位を低減させることができるためであ

る。

【0071】

なお、不活性ガス雰囲気としては、窒素、または希ガス(ヘリウム、ネオン、アルゴン等

)を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ま

しい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの

純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上(

すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とする。

【0072】

いずれにしても、第1の熱処理によって不純物を低減させ、i型(真性半導体)またはi

型に限りなく近い酸化物半導体層144を形成することで、極めて優れた特性のトランジ

スタを実現することができる。

【0073】

ところで、上述の熱処理(第1の熱処理)には水素や水などを除去する効果があるから、

当該熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。当該脱水化処理や

、当該脱水素化処理は、酸化物半導体層144の成膜後や絶縁層150の成膜後、ソース

電極141a及びドレイン電極141bの形成後、などのタイミングにおいて行うことも

可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行って

も良い。

【0074】

次に、ゲート絶縁層146及び絶縁層150a上に、酸化物半導体層144aの端面と接

するように導電膜を形成し、当該導電膜を選択的にエッチングすることにより、ソース電

極141a及びドレイン電極141bを形成する(図2(E)参照)。

【0075】

ソース電極141a及びドレイン電極141bとなる導電膜の膜厚は、例えば、50nm

以上500nm以下とする。ソース電極141a及びドレイン電極141bとなる導電膜

は、スパッタ法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて形

成することができる。

【0076】

ソース電極141a及びドレイン電極141bとなる導電膜の材料としては、アルミニウ

ム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素やこれ

らの窒化物、上述した元素を成分とする合金等を用いることができる。マンガン、マグネ

シウム、ジルコニウム、ベリリウムのいずれか、またはこれらを複数組み合わせた材料を

用いてもよい。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、

クロム、ネオジム、スカンジウムから選ばれた元素、またはこれらを複数組み合わせた材

料を用いてもよい。また、酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化

亜鉛(ZnO)、酸化インジウム酸化スズ合金(In2O3−SnO2、ITOと略記す

る場合がある)、酸化インジウム酸化亜鉛合金(In2O3−ZnO)、または、これら

の金属酸化物材料にシリコン若しくは酸化シリコンを含有させた導電性の金属酸化物を用

いても良い。

【0077】

なお、ソース電極141a及びドレイン電極141bとなる導電膜の材料として、酸化物

半導体層144aの電子親和力よりも仕事関数の大きい金属材料を用いると、酸化物半導

体層144aとの接触界面での抵抗を高めることができるため好ましい。このような金属

材料としては、例えば、金、白金、窒化タングステン、酸化インジウム酸化スズ合金等が

挙げられる。また、ソース電極141a及びドレイン電極141bとなる導電膜の材料と

しては、酸化物半導体層144aとの接触により化学反応しない材料を用いるのが好まし

い。

【0078】

ソース電極141a及びドレイン電極141bとなる導電膜のエッチングには、ウェット

エッチングまたはドライエッチングを用いることができる。また、ウェットエッチングと

ドライエッチングを組み合わせて用いることもできる。所望の形状にエッチングできるよ

う、材料に合わせてエッチング条件(エッチングガス、エッチング液、エッチング時間、

温度等)を適宜設定する。ソース電極141a及びドレイン電極141bとなる導電膜の

エッチングにドライエッチングを用いる場合、エッチングガスとしては、例えば、塩素(

Cl2)、三塩化ホウ素(BCl3)、四塩化ケイ素(SiCl4)、四フッ化メタン(

CF4)、六フッ化硫黄(SF6)、三フッ化窒素(NF3)等を用いることができ、こ

れらのうちから複数を選択した混合ガスを用いることもできる。また、これらに、希ガス

(ヘリウム(He)、アルゴン(Ar))、酸素等を添加しても良い。

【0079】

このように、ソース電極141a及びドレイン電極141bを形成することにより、酸化

物半導体層144aは、その端面においてソース電極141a及びドレイン電極141b

と接する。また、酸化物半導体層144aの端面の上端と絶縁層150aの端面の下端と

は一致しており、酸化物半導体層144aは、その上方で絶縁層150aを介して、ソー

ス電極141a及びドレイン電極141bと重なっている。つまり、酸化物半導体層14

4aは、端面でのみ、ソース電極141a及びドレイン電極141bと接している。

【0080】

このように、酸化物半導体層144aの端面においてソース電極141a及びドレイン電

極141bと接し、酸化物半導体層144aの上面を絶縁層150aで覆うことにより、

ソース電極141aと酸化物半導体層144aとの接触面積、及びドレイン電極141b

と酸化物半導体層144aとの接触面積を低減させることができる。このため、接触界面

におけるコンタクト抵抗を増大させることができる。

【0081】

本実施の形態で示すトランジスタ180は、ソース電極141aと酸化物半導体層144

aとのコンタクト抵抗、及びドレイン電極141bと酸化物半導体層144aとのコンタ

クト抵抗を高めることで、トランジスタ180のチャネル長(L)を短くしても、酸化物

半導体層144aに掛かる電界を緩和して短チャネル効果を抑制させることができる。

【0082】

ただし、酸化物半導体層144aは、必ずしも端面でのみソース電極141a及びドレイ

ン電極141bと接している必要はなく、ソース電極141aと酸化物半導体層144a

との接触面積、及びドレイン電極141bと酸化物半導体層144aとの接触面積を低減

させることができれば、酸化物半導体層144aの上面の一部とソース電極141a及び

ドレイン電極141bとが接しても良い。

【0083】

また、ソース電極141a及びドレイン電極141bとなる導電膜を、第1の導電膜と第

2の導電膜とを順に積層した構造とすることで、図1(B)に示すトランジスタ190の

ように、ソース電極141aを、第2の導電層145aと第1の導電層142aとを順に

積層した構造とし、ドレイン電極141bを、第2の導電層145bと第1の導電層14

2bとを順に積層した構造とすることもできる。その場合、第1の導電膜の膜厚は、50

nm以上500nm以下とし、第2の導電膜の膜厚は、3nm以上30nm以下、好まし

くは5nm以上15nm以下とする。

【0084】

第1の導電膜及び第2の導電膜は、上記のソース電極141a及びドレイン電極141b

となる導電膜と、同様の材料及び同様の成膜方法で形成することができる。また、第1の

導電膜は、単層構造であっても良いし、2層以上の積層構造であっても良い。例えば、チ

タン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタ

ン膜が積層された2層構造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構

造などが挙げられる。

【0085】

なお、第2の導電膜の材料として、酸化物半導体層144aの電子親和力よりも仕事関数

の大きい金属材料を用いると、酸化物半導体層144aとの接触界面での抵抗を高めるこ

とができるため好ましい。このような金属材料としては、例えば、金、白金、窒化タング

ステン、酸化インジウム酸化スズ合金等が挙げられる。また、第2の導電膜の材料として

第1の導電膜よりも高抵抗な材料を用いると、作製されるトランジスタ190のソース電

極及びドレイン電極において、酸化物半導体層144aのチャネル形成領域と接する領域

が、その他の領域よりも高抵抗となるため、ソース電極とドレイン電極の間の電界を緩和

して短チャネル効果を抑制させることができ、好ましい。また、第2の導電層145a、

145bは酸化物半導体層144aと接するから、第2の導電膜には、酸化物半導体層1

44aとの接触により化学反応しない材料を用いるのが好ましい。

【0086】

例えば、第2の導電膜として窒化モリブデン膜を形成し、第1の導電膜としてチタン膜を

形成するのが好ましい。

【0087】

第1の導電膜及び第2の導電膜のエッチングについては、上記のソース電極141a及び

ドレイン電極141bとなる導電膜と、同様の方法で行うことができる。

【0088】

ソース電極141a及びドレイン電極141bの形成後には、不活性ガス雰囲気下、また

は酸素雰囲気下で第2の熱処理を行うのが望ましい。熱処理の温度は、200℃以上45

0℃以下、望ましくは250℃以上350℃以下である。例えば、窒素雰囲気下で250

℃、1時間の熱処理を行えばよい。第2の熱処理を行うことによって、トランジスタの電

気的特性のばらつきを軽減させることができる。また、絶縁層150aが酸素を含む場合

、酸化物半導体層144aに酸素を供給し、当該酸化物半導体層144aの酸素欠損を補

填して、i型(真性半導体)またはi型に限りなく近い酸化物半導体層144aを形成す

ることもできる。

【0089】

なお、本実施の形態では、ソース電極141a及びドレイン電極141bの形成後に第2

の熱処理を行っているが、第2の熱処理のタイミングはこれに特に限定されない。例えば

、トランジスタ180上に保護絶縁層を形成した後に第2の熱処理を行っても良い。また

、第1の熱処理に続けて第2の熱処理を行っても良いし、第1の熱処理に第2の熱処理を

兼ねさせても良いし、第2の熱処理に第1の熱処理を兼ねさせても良い。

【0090】

上述のように、第1の熱処理と第2の熱処理の少なくとも一方を適用することで、酸化物

半導体層144aを、その主成分以外の不純物が極力含まれないように高純度化すること

ができる。これにより、酸化物半導体層144a中の水素濃度を、5×1019atom

s/cm3以下、望ましくは5×1018atoms/cm3以下、より望ましくは5×

1017atoms/cm3以下とすることができる。また、酸化物半導体層144aの

キャリア密度を、一般的なシリコンウェハにおけるキャリア密度(1×1014/cm3

程度)と比較して、十分に小さい値(例えば、1×1012/cm3未満、より好ましく

は、1.45×1010/cm3未満)とすることができる。そして、これにより、オフ

電流が十分に小さくなる。例えば、トランジスタ180の室温でのオフ電流(ここでは、

単位チャネル幅(1μm)あたりの値)は、100zA/μm(1zA(ゼプトアンペア

)は1×10−21A)以下、望ましくは、10zA/μm以下となる。

【0091】

以上により、酸化物半導体層144aを用いたトランジスタ180が完成する。

【0092】

このように、酸化物半導体層144aの端面においてのみソース電極141a及びドレイ

ン電極141bと接し、酸化物半導体層144aの上面を絶縁層150aで覆うことによ

り、ソース電極141aと酸化物半導体層144aとの接触面積、及びドレイン電極14

1bと酸化物半導体層144aとの接触面積を低減させることができる。このため、接触

界面におけるコンタクト抵抗を増大させることができる。

【0093】

本実施の形態で示すトランジスタ180は、酸化物半導体層144aの端面においてのみ

ソース電極141a及びドレイン電極141bと接しているため、ソース電極141aと

酸化物半導体層144aとのコンタクト抵抗、及びドレイン電極141bと酸化物半導体

層144aとのコンタクト抵抗を高めることで、酸化物半導体層144aに掛かる電界を

緩和して、しきい値電圧低下などの短チャネル効果を抑制させることができる。

【0094】

このように、開示する発明の一態様では、微細化に伴う問題点を解消することができるた

め、結果として、トランジスタサイズを十分に小さくすることが可能になる。トランジス

タサイズを十分に小さくすることで、半導体装置の占める面積が小さくなるため、半導体

装置の取り数が増大する。これにより、半導体装置あたりの製造コストは抑制される。ま

た、半導体装置が小型化されるため、同程度の大きさでさらに機能が高められた半導体装

置を実現することができる。また、チャネル長の縮小による、動作の高速化、低消費電力

化などの効果を得ることもできる。つまり、開示する発明の一態様により酸化物半導体を

用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ること

が可能である。

【0095】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適

宜組み合わせて用いることができる。

【0096】

(実施の形態2)

本実施の形態では、実施の形態1とは異なる、開示する発明の一態様に係る半導体装置の

構成およびその作製工程について、図3及び図4を参照して説明する。

【0097】

〈半導体装置の構成例〉

図3(A)に示すトランジスタ260は、半導体装置の構成の例である。トランジスタ2

60は、基板200上に設けられたゲート電極248と、ゲート電極248上に設けられ

たゲート絶縁層246と、ゲート絶縁層246上に設けられた第2の導電層245aと、

第2の導電層245aよりも低抵抗である第1の導電層242aと、を含むソース電極と

、ゲート絶縁層246上に設けられた第2の導電層245bと、第2の導電層245bよ

りも低抵抗である第1の導電層242bと、を含むドレイン電極と、ゲート電極248と

重畳し、かつ第2の導電層245a、245bに接して設けられた酸化物半導体層244

と、第1の導電層242aと、酸化物半導体層244との間に設けられた絶縁層243a

と、第1の導電層242bと、酸化物半導体層244との間に設けられた絶縁層243b

と、

を有している。

【0098】

図3(A)に示すトランジスタ260において、第2の導電層245aは、第1の導電層

242aの端面からチャネル長方向に伸長した領域を有しており、第2の導電層245a

と酸化物半導体層244の少なくともチャネル形成領域とは接している。また、第2の導

電層245bは、第1の導電層242bの端面からチャネル長方向に伸長した領域を有し

ており、第2の導電層245bと酸化物半導体層244の少なくともチャネル形成領域と

は接している。

【0099】

さらに、図3(A)に示すトランジスタ260は、第2の導電層245aにおいて、第1

の導電層242aの端面からチャネル長方向に伸長した領域上に、サイドウォール絶縁層

252aを有し、第2の導電層245bにおいて、第1の導電層242bの端面からチャ

ネル長方向に伸長した領域上に、サイドウォール絶縁層252bを有している。サイドウ

ォール絶縁層252aは、酸化物半導体層244、第2の導電層245a、第1の導電層

242a、及び絶縁層243aに接して設けられている。また、サイドウォール絶縁層2

52aにおいて、酸化物半導体層244と接する領域の少なくとも一部は湾曲形状を有し

ている。サイドウォール絶縁層252bは、酸化物半導体層244、第2の導電層245

b、第1の導電層242b、及び絶縁層243bに接して設けられている。また、サイド

ウォール絶縁層252bにおいて、酸化物半導体層244と接する領域の少なくとも一部

は湾曲形状を有している。

【0100】

なお、図3(A)に示すトランジスタ260において、第2の導電層245aと第1の導

電層242aとが順に積層し、第2の導電層245bと第1の導電層242bとが順に積

層する例について示したが、本発明の一態様はこれに限定されない。例えば、図3(B)

に示すトランジスタ270のように、第1の導電層242aと第2の導電層245aとが

順に積層し、第1の導電層242bと第2の導電層245bとが順に積層する構成とする

こともできる。この場合においても、第2の導電層245aは、第1の導電層242aの

端面からチャネル長方向に伸長した領域を有し、酸化物半導体層244の少なくともチャ

ネル形成領域と接していることが好ましい。同様に、第2の導電層245bは、第1の導

電層242bの端面からチャネル長方向に伸長した領域を有し、酸化物半導体層244の

少なくともチャネル形成領域と接していることが好ましい。また、この場合、絶縁層24

3aは第2の導電層245aと酸化物半導体層244との間に設けられ、絶縁層243b

は、第2の導電層245bと酸化物半導体層244との間に設けられることになる。

【0101】

また、図3(C)に示すトランジスタ280のように、絶縁層243a、243bにおい

て、酸化物半導体層244と接する領域の少なくとも一部は湾曲形状を有する構造とする

こともできる。

【0102】

ソース電極またはドレイン電極を第1の導電層242a、242bと第2の導電層245

a、245bの積層構造として、第2の導電層245a、245bに、第1の導電層24

2a、242bの端面よりチャネル長方向に伸長した領域を設けることで、当該領域にお

いて電圧降下が生じ、酸化物半導体層にかかる電界が緩和する。このため、短チャネル効

果を抑制させることができる。また、ソース電極またはドレイン電極上に酸化物半導体層

244を形成する際の被覆性が向上する。さらに、絶縁層において、酸化物半導体層24

4と接する領域の少なくとも一部を湾曲形状とすることにより、酸化物半導体層244を

形成する際の被覆性が向上する。このため、成膜不良などの発生が抑制される。

【0103】

〈トランジスタ260の作製工程の例〉

次に、上記トランジスタ260の作製工程の例について、図4(A)乃至図4(F)を参

照して説明する。

【0104】

まず、基板200上に導電膜を形成した後、当該導電膜を選択的にエッチングしてゲート

電極248を形成する。次に、ゲート電極248を覆うようにゲート絶縁層246を形成

する(図4(A)参照)。

【0105】

ここで、基板200は、実施の形態1で示した基板100と同様の基板を用いることがで

きる。また、ゲート電極248は、実施の形態1で示したゲート電極148と同様の材料

、成膜方法を用いて形成することができる。また、ゲート絶縁層246は、実施の形態1

に示したゲート絶縁層146と同様の材料、成膜方法を用いて形成することができる。以

上の詳細については、実施の形態1の記載を参酌することができる。

【0106】

次に、ゲート絶縁層246上に第2の導電膜245を形成した後、第2の導電膜245上

に第1の導電膜を形成し、当該第1の導電膜上に絶縁膜を形成する。次に、絶縁膜上にマ

スクを形成し、絶縁膜および第1の導電膜をエッチングすることにより、絶縁層243a

、243b、および第1の導電層242a、242bを形成する(図4(B)参照)。

【0107】

ここで、第2の導電膜、第1の導電膜、及び絶縁膜は、実施の形態1で示した第2の導電

膜、第1の導電膜、及び絶縁膜と同様の材料、成膜方法を用いて形成することができる。

以上の詳細については、実施の形態1の記載を参酌することができる。ただし、第1の導

電膜と第2の導電膜については、エッチングの選択比を確保できる材料を用いて形成する

ことが望ましい。本実施の形態においては、例えば、第2の導電膜として窒化モリブデン

膜を形成し、第1の導電膜としてチタン膜を形成するものとする。

【0108】

絶縁層243a、243bの形成は、絶縁膜上にマスクを形成し、当該マスクを用いたエ

ッチングにより行う。絶縁膜のエッチングには、ウェットエッチングまたはドライエッチ

ングを用いることができ、ウェットエッチングとドライエッチングを組み合わせて用いる

こともできる。絶縁膜を所望の形状にエッチングできるよう、材料に合わせてエッチング

条件(エッチングガス、エッチング液、エッチング時間、温度等)を適宜設定する。ただ

し、トランジスタのチャネル長(L)を微細に加工するためには、ドライエッチングを用

いるのが好ましい。ドライエッチングに用いるエッチングガスとしては、例えば、六フッ

化硫黄(SF6)、三フッ化窒素(NF3)、トリフルオロメタン(CHF3)、オクタ

フルオロシクロブタン(C4F8)などのフッ素を含むガス、又は、四フッ化メタン(C

F4)と水素の混合ガス等を用いることができ、希ガス(ヘリウム(He)、アルゴン(

Ar)、キセノン(Xe))、一酸化炭素、又は二酸化炭素等を添加しても良い。

【0109】

第1の導電層242a、242bの形成は、絶縁膜のエッチングに用いたマスクを用いて

、第1の導電膜をエッチングすることにより行う(図4(B)参照)。なお、第1の導電

膜をエッチングする際には、第2の導電膜とのエッチングの選択比が確保されるエッチン

グ材料(エッチャントまたはエッチングガス)を用いる。また、第1の導電膜をエッチン

グする前にマスクを除去し、絶縁層243a及び絶縁層243bをマスクとして用いて第

1の導電膜をエッチングしても良い。

【0110】

第1の導電膜のエッチングには、ウェットエッチングまたはドライエッチングを用いるこ

とができる。また、ウェットエッチングとドライエッチングを組み合わせて用いることも

できる。所望の形状にエッチングできるよう、材料に合わせてエッチング条件(エッチン

グガス、エッチング液、エッチング時間、温度等)を適宜設定する。ただし、トランジス

タのチャネル長(L)を微細に加工するためには、ドライエッチングを用いるのが好まし

い。本実施の形態においては、第1の導電膜をエッチングするためのエッチングガスとし

て四フッ化メタン(CF4)と塩素(Cl2)と酸素(O2)との混合ガス、四フッ化メ

タン(CF4)と酸素(O2)との混合ガス、六フッ化硫黄(SF6)と塩素(Cl2)

と酸素(O2)との混合ガス、または、六フッ化硫黄(SF6)と酸素(O2)との混合

ガスを用いるものとする。

【0111】

絶縁層243a、絶縁層243bを設けることで、ソース電極またはドレイン電極と、後

に形成される酸化物半導体層との接触領域(接触面積など)の制御が容易になる。つまり

、ソース電極またはドレイン電極の抵抗の制御が容易になり、短チャネル効果の抑制を効

果的に行うことができる。

【0112】

次に、絶縁層243a、絶縁層243b、および、露出した第2の導電膜245を覆うよ

うに絶縁膜252を形成する(図4(C)参照)。絶縁膜252は、CVD法やスパッタ

リング法を用いて形成することができる。また、絶縁膜252は、酸化シリコン、窒化シ

リコン、酸化窒化シリコン、酸化アルミニウムなどを含むように形成するのが好適である

。また、絶縁膜252は、単層構造としても良いし、積層構造としても良い。

【0113】

次に、第2の導電膜245上であって、第1の導電層242aと第1の導電層242bの

間の領域に、サイドウォール絶縁層252a、252bを形成する(図4(D)参照)。

サイドウォール絶縁層252a、252bは、絶縁膜252に異方性の高いエッチング処

理を行うことで、自己整合的に形成することができる。ここで、異方性の高いエッチング

としては、ドライエッチングが好ましく、例えば、エッチングガスとして、トリフルオロ

メタン(CHF3)、オクタフルオロシクロブタン(C4F8)などのフッ素を含むガス

を用いることができる。また、これらのガスに、ヘリウム(He)やアルゴン(Ar)な

どの希ガスを添加しても良い。さらに、ドライエッチングとして、基板に高周波電圧を印

加する反応性イオンエッチング法(RIE法)を用いるのが好ましい。

【0114】

次に、サイドウォール絶縁層252a、252bをマスクとして第2の導電膜245を選

択的にエッチングし、第2の導電層245a、245bを形成する(図4(E)参照)。

このエッチング工程によって、第2の導電層245a及び第1の導電層242aが積層し

たソース電極と、第2の導電層245b及び第1の導電層242bが積層したドレイン電

極とが形成される。なお、第2の導電膜245のエッチングは、サイドウォール絶縁層2

52a、252bをマスクとして用いること以外は、実施の形態1で示した方法と同様の

方法で行うことができる。

【0115】

トランジスタ260のチャネル長(L)は、第2の導電層245aの下端部と第2の導電

層245bの下端部との間隔によって決定される。チャネル長(L)は、トランジスタ2

60の用途によって異なるが、例えば10nm乃至1000nm、好ましくは20nm乃

至400nmとすることができる。

【0116】

なお、本実施の形態で示すトランジスタの作製工程では、サイドウォール絶縁層252a

またはサイドウォール絶縁層252bを用いて第2の導電膜245をエッチングしている

ため、第2の導電層245aにおいて、第1の導電層242aの端面からチャネル長方向

に伸長した領域のチャネル長方向の長さ(LS)と、サイドウォール絶縁層252aの底

面におけるチャネル長方向の長さは概略一致している。同様に、第2の導電層245bに

おいて、第1の導電層242bの端面からチャネル長方向に伸長した領域のチャネル長方

向の長さ(LD)と、サイドウォール絶縁層252bの底面におけるチャネル長方向の長

さは概略一致している。サイドウォール絶縁層252a、252bは、絶縁膜252のエ

ッチング処理によって自己整合的に形成されるため、上記(LS)または(LD)は、絶

縁膜252の膜厚によって決定される。つまり、絶縁膜252の膜厚を制御することで、

トランジスタ260のチャネル長(L)を微細に調整することができる。例えば、トラン

ジスタ260のチャネル長(L)を、マスク形成時の露光のための露光装置の最小加工寸

法より微細に調整することもできる。このため、絶縁膜252の膜厚は、トランジスタ2

60の所望のチャネル長(L)および、第2の導電層245a、245bの加工に用いる

露光装置の解像度等に応じて決定すればよい。

【0117】

次に、絶縁層243a、243b、サイドウォール絶縁層252a、252bを覆い、且

つ、第2の導電層245a及び第2の導電層245bに接するように酸化物半導体層24

4を形成する(図4(F)参照)。

【0118】

酸化物半導体層244は、実施の形態1で示した酸化物半導体層144と同様の材料、方

法により形成することができる。また、酸化物半導体層244に対しては、熱処理(第1

の熱処理)を行うことが望ましい。詳細については、実施の形態1の記載を参酌すること

ができる。また、第1の熱処理を行った後には、不活性ガス雰囲気下、または酸素雰囲気

下で熱処理(第2の熱処理)を行うのが望ましい。詳細については、実施の形態1の記載

を参酌することができる。

【0119】

なお、トランジスタ260のソース電極は、第2の導電層245aにおいて、第1の導電

層242aの端面よりもチャネル長方向に伸長した領域の端面で、酸化物半導体層244

と接している。また、ドレイン電極は、第2の導電層245bにおいて、第1の導電層2

42bの端面よりもチャネル長方向に伸長した領域の端面で、酸化物半導体層244と接

している。このように、第1の導電層242a、242bよりも膜厚の小さい第2の導電

層245a、245bの端面において酸化物半導体層244と接することで、ソース電極

またはドレイン電極と酸化物半導体層244との接触面積を低減させ、酸化物半導体層2

44の近傍において、ソース電極またはドレイン電極の抵抗を増大させることができる。

したがって、トランジスタ260のチャネル長(L)を短くしても、ソース電極とドレイ

ン電極の間の電界を緩和して短チャネル効果を抑制させることができる。加えて、第2の

導電層を第1の導電層よりも高抵抗な材料を用いて作製すると、より効果的に抵抗を高め

ることができるため、好ましい。なお、開示する発明の技術思想は、ソース電極またはド

レイン電極に高抵抗な領域を形成することにあるので、ソース電極またはドレイン電極は

、厳密に第2の導電層245a及び第2の導電層245bの端面においてのみ酸化物半導

体層244と接する必要はない。

【0120】

以上により、酸化物半導体層244を用いたトランジスタ260を作製することができる

。

【0121】

本実施の形態に示すトランジスタ260のチャネル長(L)は、サイドウォール絶縁層2

52a、252bを形成するための絶縁膜252の膜厚によって微細に制御することがで

きる。よって、当該絶縁膜252の膜厚を適宜設定することにより、トランジスタ260

のチャネル長(L)を縮小し、容易に半導体装置の微細化を図ることができる。

【0122】

本実施の形態に示すトランジスタ260は、第2の導電層245aにおいて、第1の導電

層242aの端面からチャネル長方向に伸長した領域の上、及び、第2の導電層245b

において、第1の導電層242bの端面からチャネル長方向に伸長した領域の上に、サイ

ドウォール絶縁層252a及びサイドウォール絶縁層252bがそれぞれ設けられること

により、酸化物半導体層244、ゲート絶縁層246の被覆性を向上させ、成膜不良など

の発生を抑制させることができる。

【0123】

さらに、本実施の形態に示すトランジスタ260は、第2の導電層245aに第1の導電

層242aの端面からチャネル長方向に伸長した領域を設け、且つ、第2の導電層245

bに第1の導電層242bの端面からチャネル長方向に伸長した領域を設けて、ソース電

極またはドレイン電極の、酸化物半導体層244のチャネル形成領域と接する領域の近傍

を高抵抗領域とすることで、ソース電極とドレイン電極の間の電界を緩和して、しきい値

電圧低下などの短チャネル効果を抑制させることができる。

【0124】

このように、開示する発明の一態様では、微細化に伴う問題点を解消することができるた

め、結果として、トランジスタサイズを十分に小さくすることが可能になる。トランジス

タサイズを十分に小さくすることで、半導体装置の占める面積が小さくなるため、半導体

装置の取り数が増大する。これにより、半導体装置あたりの製造コストは抑制される。ま

た、半導体装置が小型化されるため、同程度の大きさでさらに機能が高められた半導体装

置を実現することができる。また、チャネル長の縮小による、動作の高速化、低消費電力

化などの効果を得ることもできる。つまり、開示する発明の一態様により酸化物半導体を

用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ること

が可能である。

【0125】

〈トランジスタ270およびトランジスタ280の作製工程の例〉

次に、図3(B)に示すトランジスタ270の作製工程の一例について説明する。ここで

、各工程の詳細は、トランジスタ260の作製工程の場合と同様である。また、図3(C

)に示すトランジスタ280は、絶縁層243a、243bにおいて、酸化物半導体層2

44と接する領域の少なくとも一部に湾曲形状を有する領域を設ける点以外は、トランジ

スタ270の作製工程と同様である。

【0126】

まず、基板200上に導電膜を形成した後、当該導電膜をエッチングしてゲート電極24

8を形成する。次に、ゲート電極248を覆うようにゲート絶縁層246を形成する。

【0127】

次に、ゲート絶縁層246上に、第1の導電膜を形成した後、第1の導電膜上にマスクを

形成し、第1の導電膜をエッチングすることにより、第1の導電層242a、242bを

形成する。

【0128】

次に、第1の導電層242a、242b、及び、ゲート絶縁層246上に第2の導電膜を

形成した後、第2の導電膜上に絶縁膜を形成する。

【0129】

次に、絶縁膜上にマスクを形成し、当該マスクを用いて絶縁膜をエッチングすることによ

り、絶縁層243a、243bを形成する。

【0130】

ここで、図3(A)の構成と異なる点は、第1の導電層242a、242bを形成した後

に、第2の導電層245a、245bを形成する点にある。第1の導電層242a、24

2bを形成した後に、第2の導電膜を形成してエッチングすることにより、第1の導電膜

と第2の導電膜とのエッチングの選択比を確保する必要がないので、第1の導電膜と第2

の導電膜それぞれの材料の選択の幅を広げることができる。

【0131】

次に、絶縁層243a、243bを形成するために用いたマスクを用いて、第2の導電膜

をエッチングすることにより、第2の導電層245a、245bを形成する。第2の導電

膜のエッチングは、絶縁膜のエッチングと同じガスを用いて、絶縁膜及び第2の導電膜を

連続的にエッチングすることも可能である。または、マスクを剥離して、絶縁層243a

、243bをマスクとして第2の導電膜をエッチングしてもよい。

【0132】

次に、絶縁層243a、243b、及びゲート絶縁層246上に、酸化物半導体膜をスパ

ッタ法により形成する。そして、酸化物半導体膜上にマスクを形成し、当該マスクを用い

て酸化物半導体膜をエッチングすることにより、酸化物半導体層244を形成する。

【0133】

以上により、酸化物半導体層244を用いたトランジスタ270を作製することができる

。

【0134】

なお、第2の導電層245a、245bを形成した後、絶縁層243a、243bに対し

てArガスを用いた逆スパッタを行うことにより、絶縁層243a、243bにおいて、

後に形成される酸化物半導体層244と接する領域の少なくとも一部が湾曲形状を有する

構成とすることができる。絶縁層243a、243bにおいて、酸化物半導体層244と

接する領域の少なくとも一部が湾曲形状を有することにより、酸化物半導体層244の被

覆性を向上させ、段切れを防止することが可能である。

【0135】

これにより、図3(C)に示すトランジスタ280を作製することができる。

【0136】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適

宜組み合わせて用いることができる。

【0137】

(実施の形態3)

本実施の形態では、先の実施の形態で示した半導体装置の構成とは異なる、半導体装置の

構成およびその作製工程の例について、図5及び図6を参照して説明する。

【0138】

〈半導体装置の構成例〉

図5(A)及び図5(B)に、半導体装置の例として、トランジスタの断面構造を示す。

図5(A)及び図5(B)では、開示する発明の一態様に係るトランジスタとして、トッ

プゲート型のトランジスタを示している。

【0139】

図5(A)に示すトランジスタ380は、基板300上に、酸化物半導体層344aと、

酸化物半導体層344a上に接して設けられた絶縁層350aと、絶縁層350a上に設

けられたソース電極341a及びドレイン電極341bと、ソース電極341a及びドレ

イン電極341b上に設けられたゲート絶縁層346と、ゲート絶縁層346上に設けら

れたゲート電極348と、を有している。

【0140】

図5(A)に示すトランジスタ380において、酸化物半導体層344aは、その端面に

おいてソース電極341a及びドレイン電極341bと接している。また、酸化物半導体

層344aの端面の上端と絶縁層350aの端面の下端とは一致しており、酸化物半導体

層344aは、その上方で絶縁層350aを介して、ソース電極341a及びドレイン電

極341bと重なっている。つまり、酸化物半導体層344aは、端面でのみ、ソース電

極341a及びドレイン電極341bと接している。

【0141】

また、図5(B)に示すトランジスタ390のように、ソース電極341aを、第2の導

電層345aと第1の導電層342aとを順に積層した構造とし、ドレイン電極341b

を、第2の導電層345bと第1の導電層342bとを順に積層した構造とすることもで

きる。

【0142】

〈トランジスタの作製工程の例〉

以下、図6を用いて、図5(A)に示すトランジスタの作製工程の例について説明する。

【0143】

まず、絶縁表面を有する基板300上に酸化物半導体層344を、スパッタ法を用いて成

膜し、当該酸化物半導体層344上に絶縁層350を成膜する(図6(A)参照)。

【0144】

ここで、基板300は、実施の形態1で示した基板100と同様の材料を用いることがで

きる。また、酸化物半導体層344は、実施の形態1で示した酸化物半導体層144と同

様の材料、成膜方法を用いて形成することができる。また、絶縁層350は、実施の形態

1で示した絶縁層150と同様の材料、成膜方法を用いて形成することができる。以上の

詳細については、実施の形態1の記載を参酌することができる。

【0145】

次に、マスクを用いたエッチングなどの方法によって酸化物半導体層344及び絶縁層3

50を選択的にエッチングして、島状の酸化物半導体層344a及び島状の絶縁層350

aを形成する(図6(B)参照)。

【0146】

酸化物半導体層344a及び絶縁層350aは、実施の形態1で示した酸化物半導体層1

44a及び絶縁層150aと同様の方法でエッチングを用いて形成することができる。詳

細については、実施の形態1の記載を参酌することができる。

【0147】

次に、基板300及び絶縁層350a上に、酸化物半導体層344aの端面と接するよう

に導電膜を形成し、当該導電膜を選択的にエッチングすることにより、ソース電極341

a及びドレイン電極341bを形成する(図6(C)参照)。

【0148】

ソース電極341a及びドレイン電極341bは、実施の形態1で示したソース電極14

1a及びドレイン電極141bと同様の材料、成膜方法を用いて形成することができる。

詳細については、実施の形態1の記載を参酌することができる。

【0149】

ここで、ソース電極341aの端面と酸化物半導体層344aのソース電極341a側の

端面との、チャネル長方向の距離は、0.1μm以下とするのが好ましい。また、同様に

ドレイン電極341bの端面と酸化物半導体層344aのドレイン電極341b側の端面

との、チャネル長方向の距離は、0.1μm以下とするのが好ましい。このような構成と

することにより、ゲート電極348の電界を酸化物半導体層344aに十分に作用させる

ことができる。

【0150】

また、実施の形態1で示したように、ソース電極341a及びドレイン電極341bとな

る導電膜を、第1の導電膜と第2の導電膜とを順に積層した構造とすることで、図5(B

)に示すトランジスタ390のように、ソース電極341aを、第2の導電層345aと

第1の導電層342aとを順に積層した構造とし、ドレイン電極341bを、第2の導電

層345bと第1の導電層342bとを順に積層した構造とすることもできる。第1の導

電層342a、342b及び第2の導電層345a、345bは、実施の形態1で示した

第1の導電層142a、142b及び第2の導電層145a、145bと同様の材料、成

膜方法を用いて形成することができる。よって、詳細については、実施の形態1の記載を

参酌することができる。

【0151】

次に、絶縁層350a、ソース電極341a及びドレイン電極341bを覆うように、ゲ

ート絶縁層346を形成する(図6(D)参照)。

【0152】

ゲート絶縁層346は、実施の形態1で示したゲート絶縁層146と同様の材料、成膜方

法を用いて形成することができる。よって、詳細については、実施の形態1の記載を参酌

することができる。

【0153】

次に、ゲート絶縁層346上に導電膜を成膜し、当該導電膜を選択的にエッチングしてゲ

ート電極348を形成する(図6(E)参照)。ここで、ゲート電極348は、島状の酸

化物半導体層344aと重畳する領域に形成するようにする。

【0154】

ゲート電極348は、実施の形態1で示したゲート電極148と同様の材料、成膜方法を

用いて形成することができる。よって、詳細については、実施の形態1の記載を参酌する

ことができる。

【0155】

以上により、酸化物半導体層344aを用いたトランジスタ380が完成する。

【0156】

このように、酸化物半導体層344aの端面においてソース電極341a及びドレイン電

極341bと接することにより、ソース電極341aと酸化物半導体層344aとの接触

面積及びドレイン電極341bと酸化物半導体層344aとの接触面積を低減させること

ができる。このため、接触界面におけるコンタクト抵抗を増大させることができる。

【0157】

本実施の形態で示すトランジスタ380は、酸化物半導体層344aの端面においてのみ

ソース電極341a及びドレイン電極341bと接し、ソース電極341aと酸化物半導

体層344aとのコンタクト抵抗、及びドレイン電極341bと酸化物半導体層344a

とのコンタクト抵抗を高めることで、酸化物半導体層344aに掛かる電界を緩和して、

しきい値電圧低下などの短チャネル効果を抑制させることができる。

【0158】

このように、開示する発明の一態様では、微細化に伴う問題点を解消することができるた

め、結果として、トランジスタサイズを十分に小さくすることが可能になる。トランジス

タサイズを十分に小さくすることで、半導体装置の占める面積が小さくなるため、半導体

装置の取り数が増大する。これにより、半導体装置あたりの製造コストは抑制される。ま

た、半導体装置が小型化されるため、同程度の大きさでさらに機能が高められた半導体装

置を実現することができる。また、チャネル長の縮小による、動作の高速化、低消費電力

化などの効果を得ることもできる。つまり、開示する発明の一態様により酸化物半導体を

用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ること

が可能である。

【0159】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適

宜組み合わせて用いることができる。

【0160】

(実施の形態4)

本実施の形態では、先の実施の形態とは異なる、開示する発明の一態様に係る半導体装置

の構成およびその作製工程について、図7及び図8を参照して説明する。

【0161】

〈半導体装置の構成例〉

図7に示すトランジスタ460は、半導体装置の構成の例である。トランジスタ460は

、基板400上に設けられた酸化物半導体層444aと、酸化物半導体層444a上に設

けられたゲート絶縁層446aと、ゲート絶縁層446a上に設けられたゲート電極44

8と、酸化物半導体層444aと接して設けられたソース電極442aおよびドレイン電

極442bと、を有している。また、トランジスタ460を覆うように、層間絶縁層45

3が設けられている。

【0162】

図7に示すトランジスタ460において、ゲート電極448の上面に接して絶縁層450

が設けられている。また、ゲート電極448の側面に接してサイドウォール絶縁層452

a、452bが設けられている。

【0163】

また、図7に示すトランジスタ460において、酸化物半導体層444aの長さ(チャネ

ル形成領域においてキャリアが流れる方向)は、ゲート絶縁層446aの長さと比較して

長くなるように形成してもよいし、酸化物半導体層444aの長さとゲート絶縁層446

aの長さが概略一致するように形成してもよい。

【0164】

〈半導体装置の作製工程の例〉

次に、図7に示すトランジスタ460の作製工程の一例について説明する。各工程の詳細

は、他の実施の形態と同様である。

【0165】

まず、基板400上に酸化物半導体膜444、絶縁膜446、導電膜、絶縁膜を順に形成

する。そして、絶縁膜上にマスクを形成し、当該マスクを用いて導電膜および絶縁膜を選

択的にエッチングして、ゲート電極448および絶縁層450を形成する(図8(A)参

照)。詳細については先の実施の形態を参酌できる。なお、絶縁膜446と絶縁層450

は、エッチングによる選択比が取れる材料を用いて形成することが望ましい。

【0166】

次に、少なくともゲート電極448および絶縁層450を覆うように絶縁層を形成し、当

該絶縁層に異方性の高いエッチング処理を施して、サイドウォール絶縁層452a、45

2bを形成する(図8(B)参照)。なお、サイドウォール絶縁層452aおよびサイド

ウォール絶縁層452bは、絶縁膜446との間でエッチングによる選択比が取れる材料

を用いて形成することが望ましい。詳細については、先の実施の形態を参酌できる。

【0167】

次に、絶縁層450、サイドウォール絶縁層452a、452bをマスクとして用いて、

酸化物半導体膜444および絶縁膜446を選択的にエッチングし、酸化物半導体層44

4aおよびゲート絶縁層446aを形成する(図8(C)参照)。ここで、エッチング処

理は、絶縁膜446と酸化物半導体膜444とを一度にエッチングするエッチング処理で

あっても良いし、絶縁膜446のエッチングと、酸化物半導体膜444のエッチングとを

別に行うエッチング処理であっても良い。なお、当該エッチング処理の条件によっては、

サイドウォール絶縁層452a、452bが後退する場合もある。この場合、後に形成さ

れるソース電極442aおよびドレイン電極442bは、酸化物半導体層444aの上面

の一部においても接触することになる。詳細については、先の実施の形態を参酌できる。

【0168】

次に、酸化物半導体層444a、ゲート絶縁層446a、絶縁層450、サイドウォール

絶縁層452a、452b、などを覆うように、基板400上に層間絶縁層453を形成

する。そして、層間絶縁層453に、酸化物半導体層444aにまで達する開口を形成し

た後、酸化物半導体層444aと接続するソース電極442aおよびドレイン電極442

bを形成する(図8(D)参照)。なお、層間絶縁層453の表面はCMP処理などを用

いて平坦に形成することが望ましい。層間絶縁層453の表面を平坦にすることで、その

後に形成されるソース電極442aやドレイン電極442bを好適に形成することができ

るためである。なお、ここでは層間絶縁層453に開口を形成して、ソース電極442a

およびドレイン電極442bを形成しているが、層間絶縁層453を形成する前にソース

電極442aおよびドレイン電極442bを形成しても良い。層間絶縁層、ソース電極、

ドレイン電極などの詳細については、先の実施の形態を参酌できる。

【0169】

以上により、酸化物半導体層444aを用いたトランジスタ460を作製することができ

る。

【0170】

本実施の形態に示すような構成を採用することで、ソース電極またはドレイン電極と、酸

化物半導体層との接触領域(接触面積など)の制御が容易になる。つまり、ソース電極ま

たはドレイン電極の抵抗の制御が容易になり、短チャネル効果の抑制を効果的に行うこと

ができる。

【0171】

このように、開示する発明の一態様では、微細化に伴う問題点を解消することができるた

め、結果として、トランジスタサイズを十分に小さくすることが可能になる。トランジス

タサイズを十分に小さくすることで、半導体装置の占める面積が小さくなるため、半導体

装置の取り数が増大する。これにより、半導体装置あたりの製造コストは抑制される。ま

た、半導体装置が小型化されるため、同程度の大きさでさらに機能が高められた半導体装

置を実現することができる。また、チャネル長の縮小による、動作の高速化、低消費電力

化などの効果を得ることもできる。つまり、開示する発明の一態様により酸化物半導体を

用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ること

が可能である。

【0172】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み

合わせて用いることができる。

【0173】

(実施の形態5)

本実施の形態では、開示する発明の一態様に係る半導体装置の応用例について、図9を参

照して説明する。ここでは、記憶装置の一例について説明する。なお、回路図においては

、酸化物半導体を用いたトランジスタであることを示すために、OSの符号を併せて付す

場合がある。

【0174】

図9(A−1)に示す半導体装置において、第1の配線(1st Line)とトランジ

スタ500のソース電極とは、電気的に接続され、第2の配線(2nd Line)とト

ランジスタ500のドレイン電極とは、電気的に接続されている。また、第3の配線(3

rd Line)とトランジスタ510のソース電極またはドレイン電極の一方とは、電

気的に接続され、第4の配線(4th Line)と、トランジスタ510のゲート電極

とは、電気的に接続されている。そして、トランジスタ500のゲート電極と、トランジ

スタ510のソース電極またはドレイン電極の他方は、容量素子520の電極の一方と電

気的に接続され、第5の配線(5th Line)と、容量素子520の電極の他方は電

気的に接続されている。

【0175】

ここで、トランジスタ510には、上述の酸化物半導体を用いたトランジスタが適用され

る。酸化物半導体を用いたトランジスタは、オフ電流が極めて小さいという特徴を有して

いる。このため、トランジスタ510をオフ状態とすることで、トランジスタ500のゲ

ート電極の電位を極めて長時間にわたって保持することが可能である。そして、容量素子

520を有することにより、トランジスタ500のゲート電極に与えられた電荷の保持が

容易になり、また、保持された情報の読み出しが容易になる。

【0176】

なお、トランジスタ500については特に限定されない。情報の読み出し速度を向上させ

るという観点からは、例えば、単結晶シリコンを用いたトランジスタなど、スイッチング

速度の高いトランジスタを適用するのが好適である。

【0177】

また、図9(B)に示すように、容量素子520を設けない構成とすることも可能である

。

【0178】

図9(A−1)に示す半導体装置では、トランジスタ500のゲート電極の電位が保持可

能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能であ

る。

【0179】

はじめに、情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、ト

ランジスタ510がオン状態となる電位にして、トランジスタ510をオン状態とする。

これにより、第3の配線の電位が、トランジスタ500のゲート電極、および容量素子5

20に与えられる。すなわち、トランジスタ500のゲート電極には、所定の電荷が与え

られる(書き込み)。ここでは、異なる二つの電位を与える電荷(以下、低電位を与える

電荷を電荷QL、高電位を与える電荷を電荷QHという)のいずれかが与えられるものと

する。なお、異なる三つまたはそれ以上の電位を与える電荷を適用して、記憶容量を向上

させても良い。その後、第4の配線の電位を、トランジスタ510がオフ状態となる電位

にして、トランジスタ510をオフ状態とすることにより、トランジスタ500のゲート

電極に与えられた電荷が保持される(保持)。

【0180】

トランジスタ510のオフ電流は極めて小さいから、トランジスタ500のゲート電極の

電荷は長時間にわたって保持される。

【0181】

次に、情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状

態で、第5の配線に適切な電位(読み出し電位)を与えると、トランジスタ500のゲー

ト電極に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジ

スタ500をnチャネル型とすると、トランジスタ500のゲート電極にQHが与えられ

ている場合の見かけのしきい値電圧Vth_Hは、トランジスタ500のゲート電極にQ

Lが与えられている場合の見かけのしきい値電圧Vth_Lより低くなるためである。こ

こで、見かけのしきい値電圧とは、トランジスタ500を「オン状態」とするために必要

な第5の配線の電位をいうものとする。したがって、第5の配線の電位をVth_HとV

th_Lの中間の電位V0とすることにより、トランジスタ500のゲート電極に与えら

れた電荷を判別できる。例えば、書き込みにおいて、QHが与えられていた場合には、第

5の配線の電位がV0(>Vth_H)となれば、トランジスタ500は「オン状態」と

なる。QLが与えられていた場合には、第5の配線の電位がV0(<Vth_L)となっ

ても、トランジスタ500は「オフ状態」のままである。このため、第2の配線の電位を

見ることで、保持されている情報を読み出すことができる。

【0182】

なお、メモリセルをアレイ状に配置して用いる場合には、所望のメモリセルの情報のみを

読み出せることが必要になる。このように、所定のメモリセルの情報を読み出し、それ以

外のメモリセルの情報を読み出さないようにするには、各メモリセル間でトランジスタ5

00がそれぞれ並列に接続されている場合には、読み出しの対象ではないメモリセルの第

5の配線に対して、ゲート電極の状態にかかわらずトランジスタ500が「オフ状態」と

なるような電位、つまり、Vth_Hより小さい電位を与えればよい。また、各メモリセ

ル間でトランジスタ500がそれぞれ直列に接続されている場合には、ゲート電極の状態

にかかわらずトランジスタ500が「オン状態」となるような電位、つまり、Vth_L

より大きい電位を第5の配線に与えればよい。

【0183】

次に、情報の書き換えについて説明する。情報の書き換えは、上記情報の書き込みおよび

保持と同様に行われる。つまり、第4の配線の電位を、トランジスタ510がオン状態と

なる電位にして、トランジスタ510をオン状態とする。これにより、第3の配線の電位

(新たな情報に係る電位)が、トランジスタ500のゲート電極および容量素子520に

与えられる。その後、第4の配線の電位を、トランジスタ510がオフ状態となる電位に

して、トランジスタ510をオフ状態とすることにより、トランジスタ500のゲート電

極は、新たな情報に係る電荷が与えられた状態となる。

【0184】

このように、開示する発明に係る半導体装置は、再度の情報の書き込みによって直接的に

情報を書き換えることが可能である。このためフラッシュメモリなどにおいて必要とされ

る高電圧を用いてのフローティングゲートからの電荷の引き抜きが不要であり、消去動作

に起因する動作速度の低下を抑制させることができる。つまり、半導体装置の高速動作が

実現される。

【0185】

なお、トランジスタ510のソース電極またはドレイン電極は、トランジスタ500のゲ

ート電極と電気的に接続されることにより、不揮発性メモリ素子として用いられるフロー

ティングゲート型トランジスタのフローティングゲートと同等の作用を奏する。このため

、図中、トランジスタ510のソース電極またはドレイン電極とトランジスタ500のゲ

ート電極が電気的に接続される部位をフローティングゲート部FGと呼ぶ場合がある。ト

ランジスタ510がオフの場合、当該フローティングゲート部FGは絶縁体中に埋設され

たと見ることができ、フローティングゲート部FGには電荷が保持される。酸化物半導体

を用いたトランジスタ510のオフ電流は、シリコン半導体などで形成されるトランジス

タの10万分の1以下であるため、トランジスタ510のリークによる、フローティング

ゲート部FGに蓄積される電荷の消失を無視することが可能である。つまり、酸化物半導

体を用いたトランジスタ510により、電力の供給が無くても情報の保持が可能な不揮発

性の記憶装置を実現することができる。

【0186】

例えば、トランジスタ510の室温でのオフ電流が10zA(1zA(ゼプトアンペア)

は1×10−21A)以下であり、容量素子520の容量値が10fF程度である場合に

は、少なくとも104秒以上のデータ保持が可能である。なお、当該保持時間が、トラン

ジスタ特性や容量値によって変動することはいうまでもない。

【0187】

また、この場合、従来のフローティングゲート型トランジスタにおいて指摘されているゲ

ート絶縁膜(トンネル絶縁膜)の劣化という問題が存在しない。つまり、従来問題とされ

ていた、電子をフローティングゲートに注入する際のゲート絶縁膜の劣化という問題を解

消することができる。これは、原理的な書き込み回数の制限が存在しないことを意味する

ものである。また、従来のフローティングゲート型トランジスタにおいて書き込みや消去

の際に必要であった高電圧も不要である。

【0188】

図9(A−1)に示す半導体装置は、当該半導体装置を構成するトランジスタなどの要素

が抵抗および容量を含むものとして、図9(A−2)のように考えることが可能である。

つまり、図9(A−2)では、トランジスタ500および容量素子520が、それぞれ、

抵抗および容量を含んで構成されていると考えることができる。R1およびC1は、それ

ぞれ、容量素子520の抵抗値および容量値であり、抵抗値R1は、容量素子520を構

成する絶縁層による抵抗値に相当する。また、R2およびC2は、それぞれ、トランジス

タ500の抵抗値および容量値であり、抵抗値R2はトランジスタ500がオン状態の時

のゲート絶縁層による抵抗値に相当し、容量値C2はいわゆるゲート容量(ゲート電極と

、ソース電極またはドレイン電極との間に形成される容量、及び、ゲート電極とチャネル

形成領域との間に形成される容量)の容量値に相当する。

【0189】

トランジスタ510がオフ状態にある場合のソース電極とドレイン電極の間の抵抗値(実

効抵抗とも呼ぶ)をROSとすると、トランジスタ510のゲートリークが十分に小さい

条件において、R1およびR2が、ROSがR1以下かつ、ROSがR2以下を満たす場

合には、電荷の保持期間(情報の保持期間ということもできる)は、主としてトランジス

タ510のオフ電流によって決定されることになる。

【0190】

逆に、当該条件を満たさない場合には、トランジスタ510のオフ電流が十分に小さくと

も、保持期間を十分に確保することが困難になる。トランジスタ510のオフ電流以外の

リーク電流(例えば、ソース電極とゲート電極の間において生じるリーク電流等)が大き

いためである。このことから、本実施の形態において開示する半導体装置は、上述の関係

を満たすものであることが望ましいといえる。

【0191】

一方で、C1とC2は、C1はC2以上の関係を満たすことが望ましい。C1を大きくす

ることで、第5の配線によってフローティングゲート部FGの電位を制御する際に、第5

の配線の電位を効率よくフローティングゲート部FGに与えることができるようになり、

第5の配線に与える電位間(例えば、読み出しの電位と、非読み出しの電位)の電位差を

低く抑えることができるためである。

【0192】

上述の関係を満たすことで、より好適な半導体装置を実現することが可能である。なお、

R1およびR2は、トランジスタ500のゲート絶縁層や容量素子520の絶縁層によっ

て制御される。C1およびC2についても同様である。よって、ゲート絶縁層の材料や厚

さなどを適宜設定し、上述の関係を満たすようにすることが望ましい。

【0193】

本実施の形態で示す半導体装置においては、フローティングゲート部FGが、フラッシュ

メモリ等のフローティングゲート型のトランジスタのフローティングゲートと同等の作用

をするが、本実施の形態のフローティングゲート部FGは、フラッシュメモリ等のフロー

ティングゲートと本質的に異なる特徴を有する。フラッシュメモリでは、コントロールゲ

ートに印加される電圧が高いため、その電位の影響が、隣接するセルのフローティングゲ

ートにおよぶことを防ぐために、セルとセルとの間隔をある程度保つ必要が生じる。この

ことは、半導体装置の高集積化を阻害する要因の一つである。そして、当該要因は、高電

界をかけてトンネル電流を発生させるというフラッシュメモリの根本的な原理に起因する

ものである。

【0194】

また、フラッシュメモリの上記原理によって、絶縁膜の劣化が進行し、書き換え回数の限

界(104〜105回程度)という別の問題も生じる。

【0195】

開示する発明に係る半導体装置は、酸化物半導体を用いたトランジスタのスイッチングに

よって動作し、上述のようなトンネル電流による電荷注入の原理を用いない。すなわち、

フラッシュメモリのような、電荷を注入するための高電界が不要である。これにより、隣

接セルに対する、コントロールゲートによる高電界の影響を考慮する必要がないため、高

集積化が容易になる。

【0196】

また、トンネル電流による電荷注入の原理を用いないため、メモリセルの劣化の原因が存

在しない。つまり、フラッシュメモリと比較して高い耐久性および信頼性を有することに

なる。

【0197】

また、高電界が不要であり、大型の周辺回路(昇圧回路など)が不要である点も、フラッ

シュメモリに対するアドバンテージである。

【0198】

なお、容量素子520を構成する絶縁層の比誘電率εr1と、トランジスタ500におい

てゲート容量を構成する絶縁層の比誘電率εr2とを異ならせる場合には、容量素子52

0を構成する絶縁層の面積S1と、トランジスタ500においてゲート容量を構成する絶

縁層の面積S2とが、2・S2は、S1以上(望ましくはS2は、S1以上)を満たしつ

つ、C1は、C2以上を実現することが容易である。具体的には、例えば、容量素子52

0を構成する絶縁層においては、酸化ハフニウムなどの高誘電率(high−k)材料で

なる膜、または酸化ハフニウムなどの高誘電率(high−k)材料でなる膜と酸化物半

導体でなる膜との積層構造を採用してεr1を10以上、好ましくは15以上とし、トラ

ンジスタ500においてゲート容量を構成する絶縁層においては、酸化シリコンを採用し

て、εr2=3〜4とすることができる。

【0199】

このような構成を併せて用いることで、開示する発明に係る半導体装置の、より一層の高

集積化が可能である。

【0200】

なお、上記説明は、電子を多数キャリアとするn型トランジスタ(nチャネル型トランジ

スタ)を用いる場合についてのものであるが、n型トランジスタに代えて、正孔を多数キ

ャリアとするp型トランジスタ(pチャネル型トランジスタ)を用いることができるのは

いうまでもない。

【0201】

以上示したように、開示する発明の一態様の半導体装置は、オフ状態でのソースとドレイ

ン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ、当該書き込み用トラン

ジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性

のメモリセルを有している。

【0202】

書き込み用トランジスタのオフ電流は、使用時の温度(例えば、25℃)で100zA(

1×10−19A)以下、好ましくは10zA(1×10−20A)以下、さらに好まし

くは、1zA(1×10−21A)以下であることが望ましい。通常のシリコン半導体で

は、上述のように低いオフ電流を得ることは困難であるが、酸化物半導体を適切な条件で

加工して得られたトランジスタにおいては達成しうる。このため、書き込み用トランジス

タとして、酸化物半導体を含むトランジスタを用いることが好ましい。

【0203】

さらに酸化物半導体を用いたトランジスタはサブスレッショルドスイング値(S値)が小

さいため、比較的移動度が低くてもスイッチング速度を十分大きくすることが可能である

。よって、当該トランジスタを書き込み用トランジスタとして用いることで、フローティ

ングゲート部FGに与えられる書き込みパルスの立ち上がりを極めて急峻にすることがで

きる。また、オフ電流が小さいため、フローティングゲート部FGに保持させる電荷量を

少なくすることが可能である。つまり、酸化物半導体を用いたトランジスタを書き込み用

トランジスタとして用いることで、情報の書き換えを高速に行うことができる。

【0204】

読み出し用トランジスタとしては、オフ電流についての制限はないが、読み出しの速度を

高くするために、高速で動作するトランジスタを用いることが好ましい。例えば、読み出

し用トランジスタとしてスイッチング速度が1ナノ秒以下のトランジスタを用いることが

好ましい。

【0205】

メモリセルへの情報の書き込みは、書き込み用トランジスタをオン状態とすることにより

、書き込み用トランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の

一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたフローティングゲ

ート部FGに電位を供給し、その後、書き込み用トランジスタをオフ状態とすることによ

り、フローティングゲート部FGに所定量の電荷を保持させることで行う。ここで、書き

込み用トランジスタのオフ電流は極めて小さいため、フローティングゲート部FGに供給

された電荷は長時間にわたって保持される。オフ電流が例えば実質的に0であれば、従来

のDRAMで必要とされたリフレッシュ動作が不要となるか、または、リフレッシュ動作

の頻度を極めて低く(例えば、一ヶ月乃至一年に一度程度)することが可能となり、半導

体装置の消費電力を十分に低減させることができる。

【0206】

また、メモリセルへの再度の情報の書き込みによって、直接的に情報を書き換えることが

可能である。このためフラッシュメモリなどにおいて必要とされる消去動作が不要であり

、消去動作に起因する動作速度の低下を抑制させることができる。つまり、半導体装置の

高速動作が実現される。また、従来のフローティングゲート型トランジスタで書き込みや

消去の際に必要とされていた高い電圧を必要としないため、半導体装置の消費電力をさら

に低減させることができる。本実施の形態に係るメモリセルに印加される電圧(メモリセ

ルの各端子に同時に印加される電位の最大のものと最小のものの差)の最大値は、2段階

(1ビット)の情報を書き込む場合、一つのメモリセルにおいて、5V以下、好ましくは

3V以下である。

【0207】

開示する発明に係る半導体装置に配置されるメモリセルは、書き込み用トランジスタと、

読み出し用トランジスタと、容量素子とを少なくとも含んでいればよく、また、容量素子

の面積は小さくても動作可能である。したがって、メモリセルあたりの面積を、例えば、

1メモリセルあたり6つのトランジスタを必要とするSRAMと比較して、十分に小さく

することが可能であり、半導体装置においてメモリセルを高密度で配置することができる

。

【0208】

また、従来のフローティングゲート型トランジスタでは、書き込み時にゲート絶縁膜(ト

ンネル絶縁膜)中を電荷が移動するために、当該ゲート絶縁膜(トンネル絶縁膜)の劣化

が不可避であった。しかしながら、本発明の一態様に係るメモリセルにおいては、書き込

み用トランジスタのスイッチング動作により情報の書き込みがなされるため、従来問題と

されていたゲート絶縁膜の劣化を解消することができる。これは、原理的な書き込み回数

の制限が存在せず、書き換え耐性が極めて高いことを意味するものである。例えば、本発

明の一態様に係るメモリセルは、1×109回(10億回)以上の書き込み後であっても

、電流−電圧特性に劣化が見られない。

【0209】

さらに、メモリセルの書き込み用トランジスタとして酸化物半導体を用いたトランジスタ

を用いる場合、酸化物半導体は一般にエネルギーギャップが大きく(例えば、In−Ga

−Zn−O系の場合3.0〜3.5eV)、熱励起キャリアが極めて少ないこともあり、

例えば、150℃もの高温環境下でもメモリセルの電流−電圧特性に劣化が見られない。

【0210】

本発明者らは、鋭意研究の結果、酸化物半導体を用いたトランジスタは、150℃の高温

下であっても特性の劣化を起こさず、且つオフ電流が100zA以下と極めて小さいとい

う優れた特性を有することを見出した。本実施の形態では、このような優れた特性を有す

るトランジスタをメモリセルの書き込み用トランジスタとして適用し、従来にない特徴を

有する半導体装置を提供するものである。

【0211】

開示する発明の一態様により、酸化物半導体を用いたトランジスタにおいて、不良を抑制

しつつ、または良好な特性を維持しつつ、微細化を達成することができる。そして、この

ようなトランジスタを用いることにより、上述のような優れた記憶装置を、高度に集積化

することができる。

【0212】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適

宜組み合わせて用いることができる。

【0213】

(実施の形態6)

本実施の形態では、開示する発明の一態様に係る半導体装置の応用例について、図10お

よび図11を用いて説明する。

【0214】

図10(A)および図10(B)は、図9(A−1)に示す半導体装置(以下、メモリセ

ル550とも記載する。)を複数用いて形成される半導体装置の回路図である。図10(

A)は、メモリセル550が直列に接続された、いわゆるNAND型の半導体装置の回路

図であり、図10(B)は、メモリセル550が並列に接続された、いわゆるNOR型の

半導体装置の回路図である。

【0215】

図10(A)に示す半導体装置は、ソース線SL、ビット線BL、第1信号線S1、m本

の第2信号線S2、m本のワード線WLと、複数のメモリセル550(1、1)〜550

(m、1)が、縦m個(行)×横1個(列)に配置されている。なお、図10(A)では

、ソース線SLおよびビット線BLを1本ずつ有する構成となっているが、これに限られ

ない。ソース線SLおよびビット線BLをn本有することで、縦m個(行)×横n個(列

)のメモリセルアレイを有する構成としてもよい。

【0216】

各メモリセル550において、トランジスタ500のゲート電極と、トランジスタ510

のソース電極またはドレイン電極の一方と、容量素子520の電極の一方とは、電気的に

接続されている。また、第1信号線S1とトランジスタ510のソース電極またはドレイ

ン電極の他方とは、電気的に接続され、第2信号線S2と、トランジスタ510のゲート

電極とは、電気的に接続されている。そして、ワード線WLと、容量素子520の電極の

他方は電気的に接続されている。

【0217】

また、メモリセル550が有するトランジスタ500のソース電極は、隣接するメモリセ

ル550のトランジスタ500のドレイン電極と電気的に接続され、メモリセル550が

有するトランジスタ500のドレイン電極は、隣接するメモリセル550のトランジスタ

500のソース電極と電気的に接続される。ただし、直列に接続された複数のメモリセル

のうち、一方の端に設けられたメモリセル550が有するトランジスタ500のドレイン

電極は、ビット線と電気的に接続される。また、直列に接続された複数のメモリセルのう

ち、他方の端に設けられたメモリセル550が有するトランジスタ500のソース電極は

、ソース線と電気的に接続される。

【0218】

図10(A)に示す半導体装置では、行ごとの書き込み動作および読み出し動作を行う。

書き込み動作は次のように行われる。書き込みを行う行の第2の信号線S2にトランジス

タ510がオン状態となる電位を与え、書き込みを行う行のトランジスタ510をオン状

態にする。これにより、指定した行のトランジスタ500のゲート電極に第1の信号線S

1の電位が与えられ、当該ゲート電極に所定の電荷が与えられる。このようにして、指定

した行のメモリセルにデータを書き込むことができる。

【0219】

また、読み出し動作は次のように行われる。まず、読み出しを行う行以外のワード線WL

に、トランジスタ500のゲート電極に与えられた電荷によらず、トランジスタ500が

オン状態となるような電位を与え、読み出しを行う行以外のトランジスタ500をオン状

態とする。それから、読み出しを行う行のワード線WLに、トランジスタ500のゲート

電極が有する電荷によって、トランジスタ500のオン状態またはオフ状態が選択される

ような電位(読み出し電位)を与える。そして、ソース線SLに定電位を与え、ビット線

BLに接続されている読み出し回路(図示しない)を動作状態とする。ここで、ソース線

SL−ビット線BL間の複数のトランジスタ500は、読み出しを行う行を除いてオン状

態となっているため、ソース線SL−ビット線BL間のコンダクタンスは、読み出しを行

う行のトランジスタ500の状態(オン状態またはオフ状態)によって決定される。読み

出しを行う行のトランジスタ500のゲート電極が有する電荷によって、トランジスタの

コンダクタンスは異なるから、それに応じて、ビット線BLの電位は異なる値をとる。ビ

ット線の電位を読み出し回路によって読み出すことで、指定した行のメモリセルから情報

を読み出すことができる。

【0220】

図10(B)に示す半導体装置は、n本のソース線SL、ビット線BLおよび第1信号線

S1と、m本の第2信号線S2およびワード線WLと、複数のメモリセル550(1、1

)〜550(m、n)が、縦m個(行)×横n個(列)のマトリクス状に配置されたメモ

リセルアレイ560を有する。各トランジスタ500のゲート電極と、トランジスタ51

0のソース電極またはドレイン電極の一方と、容量素子520の電極の一方とは、電気的

に接続されている。また、ソース線SLとトランジスタ500のソース電極とは、電気的

に接続され、ビット線BLとトランジスタ500のドレイン電極とは、電気的に接続され

ている。また、第1信号線S1とトランジスタ510のソース電極またはドレイン電極の

他方とは、電気的に接続され、第2信号線S2と、トランジスタ510のゲート電極とは

、電気的に接続されている。そして、ワード線WLと、容量素子520の電極の他方は電

気的に接続されている。

【0221】

図10(B)に示す半導体装置では、行ごとの書き込み動作および読み出し動作を行う。

書き込み動作は、上述の図10(A)に示す半導体装置と同様の方法で行われる。読み出

し動作は次のように行われる。まず、読み出しを行う行以外のワード線WLに、トランジ

スタ500のゲート電極に与えられた電荷によらず、トランジスタ500がオフ状態とな

るような電位を与え、読み出しを行う行以外のトランジスタ500をオフ状態とする。そ

れから、読み出しを行う行のワード線WLに、トランジスタ500のゲート電極が有する

電荷によって、トランジスタ500のオン状態またはオフ状態が選択されるような電位(

読み出し電位)を与える。そして、ソース線SLに定電位を与え、ビット線BLに接続さ

れている読み出し回路(図示しない)を動作状態とする。ここで、ソース線SL−ビット

線BL間のコンダクタンスは、読み出しを行う行のトランジスタ500の状態(オン状態

またはオフ状態)によって決定される。つまり、読み出しを行う行のトランジスタ500

のゲート電極が有する電荷によって、ビット線BLの電位は異なる値をとる。ビット線の

電位を読み出し回路によって読み出すことで、指定した行のメモリセルから情報を読み出

すことができる。

【0222】

なお、上記においては、各メモリセル550に保持させる情報量を1ビットとしたが、本

実施の形態に示す記憶装置の構成はこれに限られない。トランジスタ500のゲート電極

に与える電位を3種類以上用意して、各メモリセル550が保持する情報量を増加させて

も良い。例えば、トランジスタ500のゲート電極に与える電位を4種類とする場合には

、各メモリセルに2ビットの情報を保持させることができる。

【0223】

次に、図10に示す半導体装置などに用いることができる読み出し回路の一例について図

11を用いて説明する。

【0224】

図11(A)には、読み出し回路の概略を示す。当該読み出し回路は、トランジスタとセ

ンスアンプ回路を有する。

【0225】

読み出し時には、端子Aは読み出しを行うメモリセルが接続されたビット線に接続される

。また、トランジスタのゲート電極にはバイアス電位Vbiasが印加され、端子Aの電

位が制御される。

【0226】

メモリセル550は、格納されるデータに応じて、異なる抵抗値を示す。具体的には、選

択したメモリセル550のトランジスタ500がオン状態の場合には低抵抗状態となり、

選択したメモリセル550のトランジスタ500がオフ状態の場合には高抵抗状態となる

。

【0227】

メモリセル550が高抵抗状態の場合、端子Aの電位が参照電位Vrefより高くなり、

センスアンプは端子Aの電位に対応する電位を出力する。一方、メモリセル550が低抵

抗状態の場合、端子Aの電位が参照電位Vrefより低くなり、センスアンプ回路は端子

Aの電位に対応する電位を出力する。

【0228】

このように、読み出し回路を用いることで、メモリセル550からデータを読み出すこと

ができる。なお、本実施の形態の読み出し回路は一例である。他の公知の回路を用いても

良い。また、読み出し回路は、プリチャージ回路を有しても良い。参照電位Vrefの代

わりに参照用のビット線が接続される構成としても良い。

【0229】

図11(B)に、センスアンプ回路の一例である差動型センスアンプを示す。差動型セン

スアンプは、入力端子Vin(+)と入力端子Vin(−)と出力端子Voutを有し、

Vin(+)とVin(−)の差を増幅する。Vin(+)>Vin(−)であればVo

utは、概ねHigh出力、Vin(+)<Vin(−)であればVoutは、概ねLo

w出力となる。当該差動型センスアンプを読み出し回路に用いる場合、Vin(+)とV

in(−)の一方は入力端子Aと接続し、Vin(+)とVin(−)の他方には参照電

位Vrefを与える。

【0230】

図11(C)に、センスアンプ回路の一例であるラッチ型センスアンプを示す。ラッチ型

センスアンプは、入出力端子V1および入出力端子V2と、制御用信号Spの入力端子、

制御用信号Snの入力端子を有する。まず、信号SpをHigh、信号SnをLowとし

て、電源電位(Vdd)を遮断する。そして、比較を行う電位をV1とV2に与える。そ

の後、信号SpをLow、信号SnをHighとして、電源電位(Vdd)を供給すると

、比較を行う電位V1inとV2inがV1in>V2inの関係にあれば、V1の出力

はHigh、V2の出力はLowとなり、V1in<V2inの関係にあれば、V1の出

力はLow、V2の出力はHighとなる。このような関係を利用して、V1inとV2

inの差を増幅することができる。当該ラッチ型センスアンプを読み出し回路に用いる場

合、V1とV2の一方は、スイッチを介して端子Aおよび出力端子と接続し、V1とV2

の他方には参照電位Vrefを与える。

【0231】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み

合わせて用いることができる。

【0232】

(実施の形態7)

本実施の形態では、上述の実施の形態で説明した半導体装置を電子機器に適用する場合に

ついて、図12を用いて説明する。本実施の形態では、コンピュータ、携帯電話機(携帯

電話、携帯電話装置ともいう)、携帯情報端末(携帯型ゲーム機、音響再生装置なども含

む)、デジタルカメラ、デジタルビデオカメラ、電子ペーパー、テレビジョン装置(テレ

ビ、またはテレビジョン受信機ともいう)などの電子機器に、上述の半導体装置を適用す

る場合について説明する。

【0233】

図12(A)は、ノート型のパーソナルコンピュータであり、筐体601、筐体602、

表示部603、キーボード604などによって構成されている。筐体601と筐体602

内には、先の実施の形態に示す微細化された半導体装置が設けられている。そのため、小

型、高速動作、低消費電力、といった特徴を備えたノート型のパーソナルコンピュータが

実現される。

【0234】

図12(B)は、携帯情報端末(PDA)であり、本体611には、表示部613と、外

部インターフェイス615と、操作ボタン614等が設けられている。また、携帯情報端

末を操作するスタイラス612などを備えている。本体611内には、先の実施の形態に

示す微細化された半導体装置が設けられている。そのため、小型、高速動作、低消費電力

、といった特徴を備えた携帯情報端末が実現される。

【0235】

図12(C)は、電子ペーパーを実装した電子書籍620であり、筐体621と筐体62

3の2つの筐体で構成されている。筐体621及び筐体623には、それぞれ表示部62

5及び表示部627が設けられている。筐体621と筐体623は、軸部637により接

続されており、当該軸部637を軸として開閉動作を行うことができる。また、筐体62

1は、電源631、操作キー633、スピーカー635などを備えている。筐体621、

筐体623の少なくとも一には、先の実施の形態に示す微細化された半導体装置が設けら

れている。そのため、小型、高速動作、低消費電力、といった特徴を備えた電子書籍が実

現される。

【0236】

図12(D)は、携帯電話機であり、筐体640と筐体641の2つの筐体で構成されて

いる。さらに、筐体640と筐体641は、スライドし、図12(D)のように展開して

いる状態から重なり合った状態とすることができ、携帯に適した小型化が可能である。ま

た、筐体641は、表示パネル642、スピーカー643、マイクロフォン644、ポイ

ンティングデバイス646、カメラ用レンズ647、外部接続端子648などを備えてい

る。また、筐体640は、携帯電話機の充電を行う太陽電池セル649、外部メモリスロ

ット650などを備えている。また、表示パネル642はタッチパネル機能を備えており

、図12(D)には映像表示されている複数の操作キー645を点線で示している。また

、アンテナは、筐体641に内蔵されている。筐体640と筐体641の少なくとも一に

は、先の実施の形態に示す微細化された半導体装置が設けられている。そのため、小型、

高速動作、低消費電力、といった特徴を備えた携帯電話機が実現される。

【0237】

図12(E)は、デジタルカメラであり、本体661、表示部667、接眼部663、操

作スイッチ664、表示部665、バッテリー666などによって構成されている。本体

661内には、先の実施の形態に示す微細化された半導体装置が設けられている。そのた

め、小型、高速動作、低消費電力、といった特徴を備えたデジタルカメラが実現される。

【0238】

図12(F)は、テレビジョン装置670であり、筐体671、表示部673、スタンド

675などで構成されている。テレビジョン装置670の操作は、筐体671が備えるス

イッチや、リモコン操作機680により行うことができる。筐体671及びリモコン操作

機680には、先の実施の形態に示す微細化された半導体装置が搭載されている。そのた

め、高速動作、低消費電力、といった特徴を備えたテレビジョン装置が実現される。

【0239】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置が搭

載されている。このため、小型、高速動作、低消費電力、といった特徴を備えた電子機器

が実現される。

【符号の説明】

【0240】

100 基板

144 酸化物半導体層

146 ゲート絶縁層

148 ゲート電極

150 絶縁層

180 トランジスタ

190 トランジスタ

141a ソース電極

141b ドレイン電極

142a 第1の導電層

142b 第1の導電層

144a 酸化物半導体層

145a 第2の導電層

145b 第2の導電層

150a 絶縁層

200 基板

242a 第1の導電層

242b 第1の導電層

243a 絶縁層

243b 絶縁層

244 酸化物半導体層

245 導電膜

245a 第2の導電層

245b 第2の導電層

246 ゲート絶縁層

248 ゲート電極

252 絶縁膜

252a サイドウォール絶縁層

252b サイドウォール絶縁層

260 トランジスタ

270 トランジスタ

280 トランジスタ

300 基板

344 酸化物半導体層

346 ゲート絶縁層

348 ゲート電極

350 絶縁層

380 トランジスタ

390 トランジスタ

341a ソース電極

341b ドレイン電極

342a 第1の導電層

342b 第1の導電層

344a 酸化物半導体層

345a 第2の導電層

345b 第2の導電層

350a 絶縁層

400 基板

444 酸化物半導体膜

446 絶縁膜

448 ゲート電極

450 絶縁層

453 層間絶縁層

460 トランジスタ

442a ソース電極

442b ドレイン電極

444a 酸化物半導体層

446a ゲート絶縁層

452a サイドウォール絶縁層

452b サイドウォール絶縁層

500 トランジスタ

510 トランジスタ

520 容量素子

550 メモリセル

560 メモリセルアレイ

601 筐体

602 筐体

603 表示部

604 キーボード

611 本体

612 スタイラス

613 表示部

614 操作ボタン

615 外部インターフェイス

620 電子書籍

621 筐体

623 筐体

625 表示部

627 表示部

631 電源

633 操作キー

635 スピーカー

637 軸部

640 筐体

641 筐体

642 表示パネル

643 スピーカー

644 マイクロフォン

645 操作キー

646 ポインティングデバイス

647 カメラ用レンズ

648 外部接続端子

649 太陽電池セル

650 外部メモリスロット

661 本体

663 接眼部

664 操作スイッチ

665 表示部

666 バッテリー

667 表示部

670 テレビジョン装置

671 筐体

673 表示部

675 スタンド

680 リモコン操作機

【技術分野】

【0001】

発明の技術分野は、半導体装置に関する。ここで、半導体装置とは、半導体特性を利用す

ることで機能する素子および装置全般を指すものである。

【背景技術】

【0002】

金属酸化物は多様に存在し、さまざまな用途に用いられている。酸化インジウムはよく知

られた材料であり、液晶表示装置などに必要とされる透明電極の材料として用いられてい

る。

【0003】

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物としては

、例えば、酸化タングステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このよう

な金属酸化物をチャネル形成領域に用いた薄膜トランジスタが既に知られている(例えば

、特許文献1乃至特許文献4、非特許文献1等参照)。

【0004】

ところで、金属酸化物には、一元系酸化物のみでなく多元系酸化物も知られている。例え

ば、ホモロガス相を有するInGaO3(ZnO)m(m:自然数)は、In、Gaおよ

びZnを有する多元系酸化物半導体として知られている(例えば、非特許文献2乃至非特

許文献4等参照)。

【0005】

そして、上記のようなIn−Ga−Zn系酸化物で構成される酸化物半導体も、薄膜トラ

ンジスタのチャネル形成領域に適用可能であることが確認されている(例えば、特許文献

5、非特許文献5および非特許文献6等参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭60−198861号公報

【特許文献2】特開平8−264794号公報

【特許文献3】特表平11−505377号公報

【特許文献4】特開2000−150900号公報

【特許文献5】特開2004−103957号公報

【非特許文献】

【0007】

【非特許文献1】M. W. Prins, K. O. Grosse−Holz, G. Muller, J. F. M. Cillessen, J. B. Giesbers, R. P. Weening, and R. M. Wolf、「A ferroelectric transparent thin−film transistor」、 Appl. Phys. Lett.、17 June 1996、 Vol.68 p.3650−3652

【非特許文献2】M. Nakamura, N. Kimizuka, and T. Mohri、「The Phase Relations in the In2O3−Ga2ZnO4−ZnO System at 1350℃」、J. Solid State Chem.、1991、Vol.93, p.298−315

【非特許文献3】N. Kimizuka, M. Isobe, and M. Nakamura、「Syntheses and Single−Crystal Data of Homologous Compounds, In2O3(ZnO)m(m=3,4, and 5), InGaO3(ZnO)3, and Ga2O3(ZnO)m(m=7,8,9, and 16) in the In2O3−ZnGa2O4−ZnO System」、 J. Solid State Chem.、1995、Vol.116, p.170−178

【非特許文献4】中村真佐樹、君塚昇、毛利尚彦、磯部光正、「ホモロガス相、InFeO3(ZnO)m(m:自然数)とその同型化合物の合成および結晶構造」、固体物理、1993年、Vol.28、No.5、p.317−327

【非特許文献5】K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono、「Thin−film transistor fabricated in single−crystalline transparent oxide semiconductor」、SCIENCE、2003、Vol.300、p.1269−1272

【非特許文献6】K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono、「Room−temperature fabrication of transparent flexible thin−film transistors using amorphous oxide semiconductors」、NATURE、2004、Vol.432 p.488−492

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところで、トランジスタの動作の高速化、トランジスタの低消費電力化、低価格化、など

を達成するためには、トランジスタの微細化は必須である。

【0009】

トランジスタを微細化する場合には、製造工程において発生する不良が大きな問題となる

。例えば、トランジスタを微細化する場合には、短チャネル効果の問題も生じる。短チャ

ネル効果とは、トランジスタの微細化(チャネル長(L)の縮小)に伴って顕在化する電

気特性の劣化である。短チャネル効果は、ドレインの電界の効果がソースにまでおよぶこ

とに起因するものである。短チャネル効果の具体例としては、しきい値電圧の低下、S値

の増大、漏れ電流の増大などがある。特に、酸化物半導体を用いたトランジスタは、室温

においてシリコンを用いたトランジスタと比較してオフ電流が小さいことが知られており

、これは熱励起により生じるキャリアが少ない、つまりキャリア密度が小さいためと考え

られる。キャリア密度が小さい材料を用いたトランジスタでは、しきい値電圧の低下など

の短チャネル効果が現れやすい傾向にある。

【0010】

そこで、開示する発明の一態様は、不良を抑制しつつ微細化を達成した半導体装置の提供

を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供

を目的の一とする。

【課題を解決するための手段】

【0011】

本発明の一態様は、酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン

電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設

けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物

半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、

且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極

と重なる半導体装置である。

【0012】

本発明の他の一態様は、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲ

ート絶縁層と、ゲート絶縁層上に設けられた酸化物半導体層と、酸化物半導体層上に接し

て設けられた絶縁層と、絶縁層及びゲート絶縁層上に設けられたソース電極及びドレイン

電極と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極また

はドレイン電極と接し、酸化物半導体層の端面の上端と、絶縁層の端面の下端とは一致す

る半導体装置である。

【0013】

本発明の他の一態様は、基板上に設けられた酸化物半導体層と、酸化物半導体層上に接し

て設けられた絶縁層と、基板及び絶縁層上に設けられたソース電極及びドレイン電極と、

絶縁層、ソース電極及びドレイン電極上に設けられたゲート絶縁層と、ゲート絶縁層上に

設けられたゲート電極と、を有し、酸化物半導体層は、該酸化物半導体層の端面において

、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層

を介して、ソース電極またはドレイン電極と重なる半導体装置である。

【0014】

上記において、酸化物半導体層の端面の上端と、絶縁層の端面の下端とは一致するのが好

ましい。また、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層よりも高

抵抗である第2の導電層と、を含み、第2の導電層において、酸化物半導体層と接するの

が好ましい。

【0015】

本発明の他の一態様は、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲ

ート絶縁層と、ゲート絶縁層上に設けられた第1の導電層と、第1の導電層よりも高抵抗

である第2の導電層と、を含むソース電極及びドレイン電極と、ゲート電極と重畳し、か

つ第2の導電層に接して設けられた酸化物半導体層と、第1の導電層と、酸化物半導体層

との間に設けられた絶縁層と、を有する半導体装置である。

【0016】

上記において、第2の導電層は、第1の導電層の端面よりチャネル長方向に伸長した領域

を有するのが好ましい。また、上記において、第2の導電層の膜厚は、5nm乃至15n

mとすると良い。また、第2の導電層は、金属の窒化物とすると良い。

【0017】

ここで半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。例えば

、表示装置や記憶装置、集積回路などは半導体装置に含まれうる。

【0018】

また、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」また

は「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極

」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外し

ない。また、「上」「下」の用語は説明の便宜のために用いる表現に過ぎず、特に言及す

る場合を除き、その上下を入れ替えたものも含む。

【0019】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限

定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、

その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配

線」が一体となって形成されている場合などをも含む。

【0020】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や

、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため

、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることがで

きるものとする。

【0021】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの

」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの

」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタ

などのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有す

る素子などが含まれる。

【発明の効果】

【0022】

開示する発明の一態様によって、ソース電極またはドレイン電極が酸化物半導体層と接す

る界面の近傍を高抵抗領域とすることで、ソース電極とドレイン電極の間の電界を緩和す

ることができる。このため、しきい値電圧低下などの短チャネル効果を抑制させることが

できる。

【0023】

このような効果により、微細化に伴う問題点が解消されることになるため、結果として、

トランジスタサイズを十分に小さくすることが可能になる。トランジスタサイズを十分に

小さくすることで、半導体装置の占める面積が小さくなり、半導体装置の取り数が増大す

る。これにより、半導体装置あたりの製造コストは抑制される。また、半導体装置が小型

化されるため、従来の半導体装置と同程度の大きさで、さらに機能が高められた半導体装

置を実現することができる。また、チャネル長の縮小による、動作の高速化、低消費電力

化などの効果を得ることもできる。つまり、開示する発明の一態様により酸化物半導体を

用いたトランジスタの微細化が達成されることで、これに付随する様々な効果を得ること

が可能である。

【0024】

このように、開示する発明の一態様によって、不良を抑制しつつ、または、良好な特性を

維持しつつ、微細化を達成した半導体装置を提供することができる。

【図面の簡単な説明】

【0025】

【図1】半導体装置の断面図

【図2】半導体装置の作製工程に係る断面図

【図3】半導体装置の断面図

【図4】半導体装置の作製工程に係る断面図

【図5】半導体装置の断面図

【図6】半導体装置の作製工程に係る断面図

【図7】半導体装置の断面図

【図8】半導体装置の作製工程に係る断面図

【図9】半導体装置の回路図の例

【図10】半導体装置の回路図の例

【図11】半導体装置の回路図の例

【図12】電子機器の例

【発明を実施するための形態】

【0026】

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下

の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および

詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下

に示す実施の形態の記載内容に限定して解釈されるものではない。

【0027】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実

際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必

ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0028】

なお、本明細書等における「第1」、「第2」、「第3」などの序数は、構成要素の混同

を避けるために付すものであり、数的に限定するものではないことを付記する。

【0029】

(実施の形態1)

本実施の形態では、開示する発明の一態様に係る半導体装置の構成およびその作製工程の

例について、図1及び図2を参照して説明する。

【0030】

〈半導体装置の構成例〉

図1(A)及び図1(B)に、半導体装置の例として、トランジスタの断面構造を示す。

図1(A)及び図1(B)では、開示する発明の一態様に係るトランジスタとして、ボト

ムゲート型のトランジスタを示している。

【0031】

図1(A)に示すトランジスタ180は、基板100上に、ゲート電極148と、ゲート

電極148上に設けられたゲート絶縁層146と、ゲート絶縁層146上に設けられた酸

化物半導体層144aと、酸化物半導体層144a上に接して設けられた絶縁層150a

と、ゲート絶縁層146及び絶縁層150a上に設けられたソース電極141a及びドレ

イン電極141bと、を有している。

【0032】

図1(A)に示すトランジスタ180において、酸化物半導体層144aは、その端面に

おいてソース電極141a及びドレイン電極141bと接している。また、酸化物半導体

層144aの端面の上端と絶縁層150aの端面の下端とは一致しており、酸化物半導体

層144aは、その上方で絶縁層150aを介して、ソース電極141a及びドレイン電

極141bと重なっている。つまり、酸化物半導体層144aは、端面でのみ、ソース電

極141a及びドレイン電極141bと接している。

【0033】

本明細書中で、端面とは、例えば、酸化物半導体層および導電膜などを、基板表面に概略

垂直に切断したときの面を指す。または、基板表面に対して垂直方向から±30°以上6

0°以下の範囲で切断したときの面を指す。つまり、膜状の構造をエッチングすることに

より生じる切断面を指すものとする。また、本明細書中で、一致とは、概略一致も含むも

のとする。例えば、同じマスクを用いてエッチングした積層構造の層Aの端面と層Bの端

面は一致しているとみなす。

【0034】

また、図1(B)に示すトランジスタ190のように、ソース電極141aを、第2の導

電層145aと第1の導電層142aとを順に積層した構造とし、ドレイン電極141b

を、第2の導電層145bと第1の導電層142bとを順に積層した構造とすることもで

きる。

【0035】

〈トランジスタの作製工程の例〉

以下、図2を用いて、図1(A)に示すトランジスタの作製工程の例について説明する。

【0036】

まず、絶縁表面を有する基板100上に導電膜を成膜し、当該導電膜を選択的にエッチン

グしてゲート電極148を形成する(図2(A)参照)。ただし、基板100の表面は全

て絶縁表面とする必要はなく、一部に導電性の領域が形成されていてもよい。

【0037】

基板100に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処

理に耐えうる程度の耐熱性を有していることが必要となる。例えば、ガラス基板、セラミ

ック基板、石英基板、サファイア基板などの基板を用いることができる。また、絶縁表面

を有していれば、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、

シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能で

あり、これらの基板上に半導体素子が設けられていてもよい。また、基板100上に下地

膜が設けられていても良い。

【0038】

ゲート電極148となる導電膜は、スパッタ法をはじめとするPVD法や、プラズマCV

D法などのCVD法を用いて形成することができる。ゲート電極148となる導電膜の材

料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステン

から選ばれた元素やこれらの窒化物、上述した元素を成分とする合金等を用いることがで

きる。マンガン、マグネシウム、ジルコニウム、ベリリウムのいずれか、またはこれらを

複数組み合わせた材料を用いてもよい。また、アルミニウムに、チタン、タンタル、タン

グステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素、またはこれ

らを複数組み合わせた材料を用いてもよい。また、酸化インジウム(In2O3)、酸化

スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金(In2O3−S

nO2、ITOと略記する場合がある)、酸化インジウム酸化亜鉛合金(In2O3−Z

nO)、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させた

導電性の金属酸化物を用いても良い。

【0039】

ただし、ゲート電極148の材料の仕事関数が酸化物半導体層144aの電子親和力と同

程度、またはそれより小さいと、トランジスタを微細化した場合に、そのしきい値電圧が

マイナス側にシフトすることがある。よって、ゲート電極148には、酸化物半導体層1

44aの電子親和力より大きい仕事関数を有する材料を用いる事が好ましい。このような

材料としては、例えば、タングステン、白金、金、p型の導電性を付与したシリコンなど

がある。

【0040】

また、ゲート電極148は、単層構造としても良いし、2層以上の積層構造としても良い

。ゲート電極148の厚さは、10nm〜400nm、好ましくは100nm〜200n

mとする。

【0041】

また、ゲート電極148を形成するエッチングに用いるマスク形成時の露光には、紫外線

、KrFレーザ光、またはArFレーザ光を用いるのが好適である。特に、加工寸法が2

5nm未満の露光を行う場合には、数nm〜数10nmと極めて波長が短い超紫外線(E

xtreme Ultraviolet)を用いてマスク形成時の露光を行うのが好適で

ある。超紫外線による露光は、解像度が高く焦点深度も大きいため、微細化には適してい

る。

【0042】

導電膜をエッチングする際に、図2(A)に示すように、ゲート電極148の端部をテー

パー形状とすることが好ましい。後の工程で、ゲート電極148上にゲート絶縁層146

などを形成する際、ゲート絶縁層146などにおける段切れを生じさせないようにするた

めである。

【0043】

次に、ゲート電極148を覆うように、ゲート絶縁層146を形成する(図2(B)参照

)。

【0044】

ゲート絶縁層146は、CVD法やスパッタ法等を用いて形成することができる。また、

ゲート絶縁層146は、酸化シリコン、窒化シリコン、酸化窒化シリコン、酸化アルミニ

ウム、酸化タンタル、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート(Hf

SixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSix

Oy(x>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAlxOy

(x>0、y>0))、などを含むように形成するのが好適である。ゲート絶縁層146

は、単層構造としても良いし、積層構造としても良い。また、その厚さは特に限定されな

いが、半導体装置を微細化する場合には、トランジスタの動作を確保するために薄くする

のが望ましい。例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好

ましくは10nm以上50nm以下とすることができる。

【0045】

上述のように、ゲート絶縁層146を薄くすると、トンネル効果などに起因するゲートリ

ークが問題となる。ゲートリークの問題を解消するには、ゲート絶縁層146に、酸化ハ

フニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSixOy(

x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSixOy(x>0

、y>0))、窒素が添加されたハフニウムアルミネート(HfAlxOy(x>0、y

>0))、などの高誘電率(high−k)材料を用いると良い。高誘電率(high−

k)材料をゲート絶縁層146に用いることで、電気的特性を確保しつつ、ゲートリーク

を抑制させられるために膜厚を大きくすることが可能になる。なお、高誘電率(high

−k)材料を含む膜と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリ

コン、酸化アルミニウムなどのいずれかを含む膜との積層構造としてもよい。

【0046】

次に、スパッタ法を用いて、ゲート絶縁層146上に酸化物半導体層144を成膜し、当

該酸化物半導体層144上に絶縁層150を成膜する(図2(C)参照)。

【0047】

酸化物半導体層144は、四元系金属酸化物であるIn−Sn−Ga−Zn−O系や、三

元系金属酸化物であるIn−Ga−Zn−O系、In−Sn−Zn−O系、In−Al−

Zn−O系、Sn−Ga−Zn−O系、Al−Ga−Zn−O系、Sn−Al−Zn−O

系や、二元系金属酸化物であるIn−Zn−O系、Sn−Zn−O系、Al−Zn−O系

、Zn−Mg−O系、Sn−Mg−O系、In−Mg−O系や、In−O系、Sn−O系

、Zn−O系などを用いて形成することができる。

【0048】

中でも、In−Ga−Zn−O系の酸化物半導体材料は、無電界時の抵抗が十分に高くオ

フ電流を十分に小さくすることが可能であり、また、電界効果移動度も高いため、半導体

装置に用いる半導体材料としては好適である。

【0049】

In−Ga−Zn−O系の酸化物半導体材料の代表例としては、InGaO3(ZnO)

m(m>0)で表記されるものがある。また、Gaに代えてMを用い、InMO3(Zn

O)m(m>0)のように表記される酸化物半導体材料がある。ここで、Mは、ガリウム

(Ga)、アルミニウム(Al)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)、

コバルト(Co)などから選ばれた一の金属元素または複数の金属元素を示す。例えば、

Mとしては、Ga、GaおよびAl、GaおよびFe、GaおよびNi、GaおよびMn

、GaおよびCoなどを適用することができる。なお、上述の組成は結晶構造から導き出

されるものであり、あくまでも一例に過ぎないことを付記する。

【0050】

酸化物半導体層144をスパッタ法で作製するためのターゲットとしては、In:Ga:

Zn=1:x:y(xは0以上、yは0.5以上5以下)の組成比を有するものを用いる

のが好適である。例えば、In:Ga:Zn=1:1:1[atom比](x=1、y=

1)、(すなわち、In2O3:Ga2O3:ZnO=1:1:2[mol数比])の組

成比を有する金属酸化物ターゲットなどを用いることができる。また、In:Ga:Zn

=1:1:0.5[atom比](x=1、y=0.5)、(すなわち、In2O3:G

a2O3:ZnO=1:1:1[mol数比])の組成比を有する金属酸化物ターゲット

や、In:Ga:Zn=1:1:2[atom比](x=1、y=2)、(すなわち、I

n2O3:Ga2O3:ZnO=1:1:4[mol数比])の組成比を有する金属酸化

物ターゲットや、In:Ga:Zn=1:0:1[atom比](x=0、y=1)、(

すなわち、In2O3:ZnO=1:2[mol数比])の組成比を有する金属酸化物タ

ーゲットを用いることもできる。

【0051】

本実施の形態では、非晶質構造の酸化物半導体層144を、In−Ga−Zn−O系の金

属酸化物ターゲットを用いるスパッタ法により形成することとする。

【0052】

金属酸化物ターゲット中の金属酸化物の相対密度は80%以上、好ましくは95%以上、

さらに好ましくは99.9%以上である。相対密度の高い金属酸化物ターゲットを用いる

ことにより、緻密な構造の酸化物半導体層144を形成することが可能である。

【0053】

酸化物半導体層144の形成雰囲気は、希ガス(代表的にはアルゴン)雰囲気、酸素雰囲

気、または、希ガス(代表的にはアルゴン)と酸素との混合雰囲気とするのが好適である

。具体的には、例えば、水素、水、水酸基、水素化物などの不純物が、濃度1ppm以下

(望ましくは濃度10ppb以下)にまで除去された高純度ガス雰囲気を用いるのが好適

である。

【0054】

酸化物半導体層144の形成の際には、例えば、減圧状態に保持された処理室内に被処理

物(ここでは、基板100を含む構造体)を保持し、被処理物の温度が100℃以上55

0℃未満、好ましくは200℃以上400℃以下となるように被処理物を熱する。または

、酸化物半導体層144の形成の際の被処理物の温度は、室温としてもよい。そして、処

理室内の水分を除去しつつ、水素や水などが除去されたスパッタガスを導入し、上記金属

酸化物ターゲットを用いて酸化物半導体層144を形成する。被処理物を熱しながら酸化

物半導体層144を形成した際、酸化物半導体層144に含まれる不純物を低減させるこ

とができる。また、スパッタによる損傷を軽減することができる。処理室内の水分を除去

するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、

イオンポンプ、チタンサブリメーションポンプなどを用いることができる。また、ターボ

ポンプにコールドトラップを加えたものを用いてもよい。クライオポンプなどを用いて排

気することで、処理室から水素や水などを除去することができるため、酸化物半導体層1

44中の不純物濃度を低減できる。

【0055】

酸化物半導体層144の形成条件としては、例えば、被処理物とターゲットとの間の距離

が170mm、圧力が0.4Pa、直流(DC)電力が0.5kW、雰囲気が酸素(酸素

100%)雰囲気、またはアルゴン(アルゴン100%)雰囲気、または酸素とアルゴン

の混合雰囲気、といった条件を適用することができる。なお、パルス直流(DC)電源を

用いると、ごみ(成膜時に形成される粉状の物質など)を低減でき、膜厚分布も均一とな

るため好ましい。酸化物半導体層144の膜厚は、例えば、3nm以上30nm以下、好

ましくは5nm以上15nm以下とする。このような厚さの酸化物半導体層144を用い

ることで、後の工程で形成される、ソース電極141aと酸化物半導体層144aの接触

面積、及びドレイン電極141bと酸化物半導体層144aの接触面積を低減できるので

、微細化に伴う短チャネル効果を抑制させることが可能である。ただし、適用する酸化物

半導体材料や、半導体装置の用途などにより適切な厚さは異なるから、その厚さは、用い

る材料や用途などに応じて選択することもできる。

【0056】

なお、酸化物半導体層144をスパッタ法により形成する前には、アルゴンガスを導入し

てプラズマを発生させる逆スパッタを行い、処理表面(例えばゲート絶縁層146の表面

)の付着物を除去するのが好適である。ここで、逆スパッタとは、通常のスパッタにおい

ては、スパッタターゲットにイオンを衝突させるところを、逆に、処理表面にイオンを衝

突させることによってその表面を改質する方法のことをいう。処理表面にイオンを衝突さ

せる方法としては、アルゴン雰囲気下で処理表面側に高周波電圧を印加して、被処理物付

近にプラズマを生成する方法などがある。なお、アルゴン雰囲気に代えて窒素、ヘリウム

、酸素などによる雰囲気を適用してもよい。

【0057】

それから、酸化物半導体層144の上に絶縁層150を成膜する。絶縁層150は、例え

ば、膜厚1nm以上50nm以下、好ましくは、3nm以上10nm以下で形成する。本

実施の形態においては、絶縁層150として、酸化シリコン膜を形成するものとする。

【0058】

また、酸化物半導体層144及び絶縁層150は、大気に触れさせることなく連続的に成

膜しても良い。このように成膜することによって、大気成分や大気中に浮遊する汚染不純

物元素(例えば、水素や水など)に汚染されることなく、酸化物半導体層144と絶縁層

150の界面を形成することができるので、トランジスタ特性のばらつきを低減させるこ

とができる。

【0059】

次に、マスクを用いたエッチングなどの方法によって酸化物半導体層144及び絶縁層1

50を選択的にエッチングして、島状の酸化物半導体層144a及び島状の絶縁層150

aを形成する(図2(D)参照)。ここで、島状の酸化物半導体層144aは、ゲート電

極148と重畳する領域に形成する。

【0060】

島状の酸化物半導体層144a及び島状の絶縁層150aを形成するエッチングに用いる

マスク形成時の露光には、紫外線、KrFレーザ光、またはArFレーザ光を用いるのが

好適である。特に、チャネル長(L)が25nm未満の露光を行う場合には、数nm〜数

10nmと極めて波長が短い超紫外線(Extreme Ultraviolet)を用

いてマスク形成時の露光を行うのが好適である。超紫外線による露光は、解像度が高く焦

点深度も大きいため、微細化には適している。

【0061】

絶縁層150及び酸化物半導体層144のエッチングには、ウェットエッチングまたはド

ライエッチングを用いることができ、ウェットエッチングとドライエッチングを組み合わ

せて用いることもできる。絶縁層150及び酸化物半導体層144を所望の形状にエッチ

ングできるよう、材料に合わせてエッチング条件(エッチングガス、エッチング液、エッ

チング時間、温度等)を適宜設定する。ただし、トランジスタのチャネル長(L)を微細

に加工するためには、ドライエッチングを用いるのが好ましい。ドライエッチングに用い

るエッチングガスとしては、例えば、六フッ化硫黄(SF6)、三フッ化窒素(NF3)

、トリフルオロメタン(CHF3)、オクタフルオロシクロブタン(C4F8)などのフ

ッ素を含むガス、四フッ化メタン(CF4)と水素の混合ガス等を用いることができ、希

ガス(ヘリウム(He)、アルゴン(Ar)、キセノン(Xe))、一酸化炭素、二酸化

炭素等を添加しても良い。

【0062】

また、ドライエッチングとしては、平行平板型RIE(Reactive Ion Et

ching)法や、ICP(Inductively Coupled Plasma:

誘導結合型プラズマ)エッチング法などを用いることができる。この場合にも、エッチン

グ条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側

の電極温度等)は適宜設定する必要がある。

【0063】

また、酸化物半導体層144及び絶縁層150をエッチングする際に、図2(D)に示す

ように、酸化物半導体層144及び絶縁層150の端部をテーパー形状とすることが好ま

しい。後の工程で、酸化物半導体層144及び絶縁層150上に、ソース電極141a及

びドレイン電極141bを形成する際、ソース電極141a及びドレイン電極141bな

どにおける段切れを生じさせないようにするためである。

【0064】

このように、絶縁層150及び酸化物半導体層144を一括でエッチングすることにより

、酸化物半導体層144aの端面の上端と絶縁層150aの端面の下端を容易に一致させ

ることができる。

【0065】

ここで、トランジスタ180のチャネル長(L)は、酸化物半導体層144aの幅によっ

て決定される。チャネル長(L)は、トランジスタ180の用途によって異なるが、例え

ば10nm以上1000nm以下、好ましくは20nm以上400nm以下とすることが

できる。

【0066】

なお、本実施の形態では、絶縁層150及び酸化物半導体層144のエッチングを一括で

行ったが、これに限られることなく、絶縁層150と酸化物半導体層144のエッチング

を逐次行うこともできる。また、酸化物半導体層144を成膜し、選択的エッチングで島

状の酸化物半導体層144aを形成した後、絶縁層150を成膜し、選択的エッチングで

島状の絶縁層150aを形成することもできる。

【0067】

それから、酸化物半導体層144に対して、熱処理(第1の熱処理)を行うことが望まし

い。この第1の熱処理によって酸化物半導体層144中の、過剰な水素(水や水酸基を含

む)を除去し、酸化物半導体層144の構造を整え、エネルギーギャップ中の欠陥準位を

低減させることができる。第1の熱処理の温度は、例えば、300℃以上550℃未満、

または400℃以上500℃以下とする。

【0068】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、

450℃、1時間の条件で行うことができる。この間、酸化物半導体層144は大気に触

れさせず、水や水素の混入が生じないようにする。

【0069】

熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射