半導体装置

【課題】出力信号を高速に変化させかつオーバーシュートやアンダーシュートを抑制できるようにする。

【解決手段】入力信号を反転して出力する主ドライバ11に加えて、補助ドライバ12を設け、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、変化開始から主ドライバの出力信号がある電圧レベルを超えるまでの期間では信号変化を補助するように制御部15により補助ドライバの動作を制御し、主ドライバの出力信号がある電圧レベルを超えてから第2の電圧レベルになるまでの期間に信号変化を抑制するように制御部により補助ドライバの動作を制御するようにして、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制できるようにする。

【解決手段】入力信号を反転して出力する主ドライバ11に加えて、補助ドライバ12を設け、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、変化開始から主ドライバの出力信号がある電圧レベルを超えるまでの期間では信号変化を補助するように制御部15により補助ドライバの動作を制御し、主ドライバの出力信号がある電圧レベルを超えてから第2の電圧レベルになるまでの期間に信号変化を抑制するように制御部により補助ドライバの動作を制御するようにして、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制できるようにする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、半導体装置からの信号出力に係る制御技術に関する。

【背景技術】

【0002】

半導体装置を構成する通常のCMOS回路において、信号の電圧レベルは、ハイレベルとしての電源電圧レベル又はローレベルとしての接地電圧レベルの2つの状態があり、その電圧レベルにて信号を伝送する。信号の変化は、接地電圧レベルから電源電圧レベルに、もしくは電源電圧レベルから接地電圧レベルに信号の電圧レベルを変化させることで行う。しかし、伝送回路に寄生する容量の影響により、目的とする電源電圧レベルや接地電圧レベルを超えた電圧レベルに達する、いわゆるオーバーシュートやアンダーシュートが発生することがあり、その信号波形の乱れがノイズとなり伝送品質を低下させる。また、信号の変化を高速に行うために駆動能力を大きくするなどして高速性を重視すると、オーバーシュートやアンダーシュートが大きくなる。

【0003】

オーバーシュートやアンダーシュートを抑制する方法として、例えば図8に示すような回路構成が用いられる。図8(A)は、出力回路の一例を示す図である。図8(A)において、ドライバ(出力バッファ)81は、例えばCMOSトランジスタで構成されるインバータであり、電源電圧Vdd及び接地電圧Gndがそれぞれ供給される配線間に接続されたPチャネルトランジスタ82及びNチャネルトランジスタ83を有する。出力回路に入力された入力信号は、ドライバ81を介して出力端子OUTより出力信号として出力される。

【0004】

また、図8(A)に示す出力回路においては、出力信号の信号線に終端抵抗84、85が接続されている。このように終端抵抗84、85を設けることで伝送回路の寄生容量による影響を抑えて、信号の電圧レベルが電源電圧レベルや接地電圧レベルを超えることを抑制し、オーバーシュートやアンダーシュートを軽減している。図8(B)は、図8(A)に示したように終端抵抗を接続した場合における出力信号の波形を示す図である。図8(B)において、実線で示す信号波形86が終端抵抗を接続した場合の出力信号を示し、破線で示す信号波形87が終端抵抗を接続しなかったとした場合の出力波形を示している。

【0005】

また、出力信号を出力する2つのドライバのうちの1つのドライバの動作を、信号の電圧レベルが目的とする電源電圧レベル又は接地電圧レベルになる直前に停止させることで、オーバーシュートやアンダーシュートを軽減する方法が提案されている(例えば、特許文献1参照。)。また、出力信号の変化時に、信号の電圧レベルがある電圧レベルになるまでは1つのドライバを動作させ、その電圧レベルに達すると2つのドライバを動作させる方法が提案されている(例えば、特許文献2、3参照。)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平3−242020号公報

【特許文献2】特開平5−243958号公報

【特許文献3】特開平3−89624号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

前述のように出力信号の信号線に終端抵抗を接続すると、図8(B)に示したように、オーバーシュートやアンダーシュートは軽減するが、定常時の電圧レベルが終端抵抗の影響により電源電圧レベルや接地電圧レベルに達せず、信号の振幅レベルが小さくなる。また、出力信号の信号線に対して、終端抵抗を介して接続される電源又は接地電圧(グランド)から信号変化とは逆の電圧レベルがかかることで、出力信号の変化を開始してから終了するまでの時間が増大し、信号変化が遅くなる。また、終端抵抗を介して電源及び接地電圧(グランド)に接続されることで、定常的にリーク電流が発生し、消費電力が増大する。

【0008】

また、特許文献1に記載の技術では、1つのドライバの動作を停止させることでオーバーシュートやアンダーシュートは軽減する。しかし、もう1つのドライバは動作し続けるために、伝送回路に寄生する容量の影響を受けてオーバーシュートやアンダーシュートが発生する。なお、オーバーシュートやアンダーシュートを抑制する方法として、時間当たりの電圧変化量を小さくすることも考えられるが、出力信号の変化に要する時間が増大し高速動作が不可能になる。

【0009】

本発明の目的は、出力信号の変化を高速に行い、かつ出力信号におけるオーバーシュートやアンダーシュートを抑制する半導体装置を提供することにある。

【課題を解決するための手段】

【0010】

半導体装置の一態様は、入力信号の電圧に応じた出力信号を出力信号線に出力する第1の駆動回路と、出力信号線に出力端が接続された第2の駆動回路と、第2の駆動回路を制御する制御部とを備える。制御部は、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、出力信号の電圧レベルが第3の電圧レベルに達するまでは出力信号の変化を補助し、出力信号の電圧レベルが第3の電圧レベルに達した後に出力信号の変化を抑制するよう第2の駆動回路を制御する。

【発明の効果】

【0011】

入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、出力信号の電圧レベルが第3の電圧レベルに達するまで出力信号の変化を補助し、その後、出力信号の変化を抑制するよう第2の駆動回路を制御するので、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制することができる。

【図面の簡単な説明】

【0012】

【図1】本発明の実施形態における半導体装置の構成例を示す図である。

【図2】本実施形態における半導体装置の構成例を示す図である。

【図3】本実施形態における半導体装置の動作を説明するための信号波形図である。

【図4】本実施形態における第1の検出部の構成例を示す図である。

【図5】本実施形態における第2の検出部の構成例を示す図である。

【図6】本実施形態における制御部の構成例を示す図である。

【図7】本実施形態における半導体装置による出力波形の一例を示す図である。

【図8】出力回路の一例を示す図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施形態を図面に基づいて説明する。

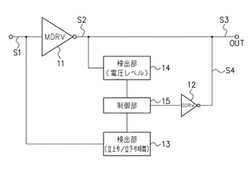

図1は、本発明の一実施形態における半導体装置の構成例を示す図である。図1において、11は主ドライバ(出力バッファ)であり、12は補助ドライバ(補助出力バッファ)である。また、13は第1の検出部であり、14は第2の検出部であり、15は制御部である。

【0014】

主ドライバ11は、入力端より入力される入力信号S1を受け、それを反転して出力信号S2として出力する。補助ドライバ12は、その駆動能力が主ドライバ11の駆動能力より小さいドライバであり、制御部15から出力される制御信号により動作が制御される。補助ドライバ12は、制御部15からの制御信号に応じた出力を出力信号S4として出力する。出力信号S2と出力信号S4を合成したものが、半導体装置の出力端OUTより出力される出力信号S3に対応する。なお、補助ドライバ12の駆動能力は、主ドライバ11の駆動能力と同じであっても良い。

【0015】

第1の検出部13は、主ドライバ11の入力信号S1を入力とし、入力信号S1に基づいて主ドライバ11における出力信号S2の変化及びそれに係る時間を検出する。第1の検出部13は、検出結果に応じて制御信号を制御部15に出力する。第2の検出部14は、主ドライバ11の出力信号S2を入力とし、出力信号S2の電圧レベルを検出する。第2の検出部14は、検出結果を制御信号により制御部15に出力する。制御部15は、第1の検出部13の出力(制御信号)及び第2の検出部14の出力(制御信号)を入力とし、それらの出力(制御信号)に基づいて補助ドライバ12の動作を制御するための制御信号を生成し出力する。

【0016】

図2は、本実施形態における半導体装置の詳細な構成例を示す図である。この図2において、図1に示した構成要素と同一の機能を有する構成要素には同一の符号を付している。

【0017】

図2に示すように、主ドライバ11は、電源電圧Vdd及び接地電圧Gndがそれぞれ供給される配線間に接続されたPチャネル型電界効果トランジスタ21及びNチャネル型電界効果トランジスタ22を有する。Pチャネルトランジスタ21は、ソースに電源電圧Vddが供給され、ドレインがNチャネルトランジスタ22のドレインに接続される。Nチャネルトランジスタ22は、ソースに接地電圧Gndが供給される。また、Pチャネルトランジスタ21及びNチャネルトランジスタ22のゲートには、入力信号S1が供給される。Pチャネルトランジスタ21及びNチャネルトランジスタ22のドレインの相互接続点の電位が、主ドライバ11の出力信号S2として、出力信号S3の信号線に対して出力される。

【0018】

補助ドライバ12は、電源電圧Vdd及び接地電圧Gndがそれぞれ供給される配線間に接続されたPチャネル型電界効果トランジスタ23及びNチャネル型電界効果トランジスタ24を有する。Pチャネルトランジスタ23は、ソースに電源電圧Vddが供給され、ドレインがNチャネルトランジスタ24のドレインに接続される。Nチャネルトランジスタ24は、ソースに接地電圧Gndが供給される。また、Pチャネルトランジスタ23のゲートには、制御部15から出力される制御信号SW1が供給され、Nチャネルトランジスタ24のゲートには、制御部15から出力される制御信号SW2が供給される。Pチャネルトランジスタ23及びNチャネルトランジスタ24のドレインの相互接続点は、出力信号S3の信号線に接続される。

【0019】

第1の検出部13は、主ドライバ11への入力信号S1を受けて、制御信号t1、t2を出力する。第1の検出部13は、入力信号S1に基づいて、主ドライバ11における出力信号S2の電圧レベルが、電源電圧レベルから接地電圧レベルに変化するか(立ち下がり)、接地電圧レベルから電源電圧レベルに変化するか(立ち上がり)を検出する。また、第1の検出部13は、主ドライバ11による立ち下がり動作の開始及び終了のタイミング又は立ち上がり動作の開始及び終了のタイミングを検出する。そして、第1の検出部13は、検出結果に応じて、主ドライバ11における立ち下がり動作時に(詳細には、立ち下がり動作の開始から動作終了後の安定期間までの期間において)制御信号t1をアサートする。また、第1の検出部13は、検出結果に応じて、主ドライバ11における立ち上がり動作時に(詳細には、立ち上がり動作の開始から動作終了後の安定期間までの期間において)制御信号t2をアサートする。

【0020】

第2の検出部14は、主ドライバ11の出力信号S2を受けて出力信号S2の電圧レベルを検出し、検出された電圧レベルに応じて制御信号A、Bを出力する。第2の検出部14は、出力信号S2の電圧レベルが接地電圧レベルの近傍の第1の電圧レベルより低いか否かを検出し、第1の電圧レベルより低いときには制御信号Aをアサートし、そうでないときには制御信号Aをネゲートする。また、第2の検出部14は、出力信号S2の電圧レベルが電源電圧レベルの近傍の第2の電圧レベルより高いか否かを検出し、第2の電圧レベルより高いときには制御信号Bをアサートし、そうでないときには制御信号Bをネゲートする。

【0021】

ここで、第1の電圧レベル及び第2の電圧レベルは、電源電圧Vddと接地電圧Gndとの間の電圧レベルであって、(接地電圧Gnd)<(第1の電圧レベル)<(第2の電圧レベル)<(電源電圧Vdd)の関係を満たす。例えば、第1の電圧レベルは0.05×(Vdd−Gnd)〜0.20×(Vdd−Gnd)の範囲内の任意の電圧レベルであり、第2の電圧レベルは0.80×(Vdd−Gnd)〜0.95×(Vdd−Gnd)の範囲内の任意の電圧レベルである。

【0022】

制御部15は、第1の検出部13から出力される制御信号t1、t2、及び第2の検出部14から出力される制御信号A、Bを受けて、補助ドライバ12の動作を制御する制御信号SW1、SW2を出力する。すなわち、制御部15は、制御信号t1、t2、及び制御信号A、Bに基づいて、図3に示すように制御信号SW1、SW2を出力し補助ドライバ12のトランジスタ23、24をオン/オフ制御する。

【0023】

図3は、本実施形態における半導体装置の動作を説明するための信号波形図である。図3において、t1、t2は、第1の検出部13から制御部15に出力される制御信号であり、A、Bは、第2の検出部14から制御部15に出力される制御信号である。なお、制御信号t1、t2及び制御信号A、Bは、アサートされているときにハイレベルにされ、ネゲートされているときにローレベルにされるとする。SW1、SW2は、制御部15から補助ドライバ12に出力される制御信号である。図3には、補助ドライバ12のPチャネルトランジスタ23及びNチャネルトランジスタ24がオン状態とされる期間をハイレベルに対応させて示すために制御信号SW1についてはその反転信号を示している。また、LVVは電源電圧レベル、LVGは接地電圧レベル、LVAは接地電圧レベルLVGの近傍の第1の電圧レベル、LVBは電源電圧レベルLVVの近傍の第2の電圧レベルである。

【0024】

まず、図3において最初の状態は、主ドライバ11への入力信号S1がローレベルの状態で十分な時間が経過し、主ドライバ11の出力信号S2の電圧レベルが電源電圧レベルLVVで安定しているものとする。このとき、制御信号t1、t2及び制御信号Aはローレベルであり、制御信号Bはハイレベルである。また、制御信号t1、t2及び制御信号A、Bがこの状態であるとき、制御部15から出力される制御信号SW1はハイレベルであり、制御部15から出力される制御信号SW2はローレベルである。したがって、補助ドライバ12のトランジスタ23、24はともにオフ状態(非導通状態)であり、補助ドライバ12はオフ状態である。

【0025】

時刻T11にて、入力信号S1がローレベルからハイレベルに変化すると、主ドライバ11は、出力信号S2の電圧レベルを電源電圧レベルから接地電圧レベルに変化させるための立ち下がり動作を開始する。また、第1の検出部13は、入力信号S1のローレベルからハイレベルへの変化を検出し、制御信号t1をハイレベルにする。制御部15は、ハイレベルの制御信号t1を受けると、制御信号Aがハイレベルになるまで制御信号SW2をハイレベルにする。すなわち、制御信号t1がハイレベルであり、かつ制御信号Aがローレベルである期間中は、制御部15により制御信号SW1、SW2がハイレベルとされ、補助ドライバ12のNチャネルトランジスタ24がオン状態(導通状態)となる。

【0026】

このように、主ドライバ11で立ち下がり動作が開始されると、補助ドライバ12は、接地電圧側のトランジスタをオン状態にして電圧レベルが下がる方向に電圧をかけるように制御され、出力信号S3の電源電圧レベルから接地電圧レベルへの変化を補助する。したがって、出力信号S3における電源電圧レベルから接地電圧レベルへの変化の高速性が向上される。

【0027】

続いて、主ドライバ11の出力信号S2の電圧レベルが第1の電圧レベルLVAより低くなる時刻T12にて、第2の検出部14は、出力信号S2の電圧レベルが第1の電圧レベルLVAより低くなったことを検出し、制御信号Aをハイレベルにする。なお、出力信号S2の電圧レベルが第1の電圧レベルLVAより低くなる前に、第2の検出部14は、出力信号S2の電圧レベルが第2の電圧レベルLVBより高くないことを検出して制御信号Bをローレベルにしている。

【0028】

制御部15は、制御信号t1がハイレベルの状態で、ハイレベルの制御信号Aを受けると、制御信号SW2をハイレベルからローレベルにして、補助ドライバ12のNチャネルトランジスタ24をオン状態からオフ状態に変化させる。また、制御部15は、制御信号SW2をハイレベルからローレベルにした後に(同時であっても良い)、制御信号t1がローレベルになるまで制御信号SW1をローレベルにする。すなわち、制御信号t1がハイレベルであり、かつ制御信号Aがハイレベルである期間中は、制御部15により制御信号SW1、SW2がローレベルとされ、補助ドライバ12のPチャネルトランジスタ23がオン状態(導通状態)となる。

【0029】

このように、主ドライバ11の出力信号S2の電圧レベルが第1の電圧レベルLVAより低くなると、補助ドライバ12は、電源電圧側のトランジスタをオン状態にして電圧レベルが上がる方向に電圧をかけるように制御される。これにより、出力信号S3の電圧レベルが接地電圧を超えることを抑制し、アンダーシュートを軽減することができる。

【0030】

続いて、主ドライバ11の出力信号S2の電圧レベルが接地電圧レベルLVGに到達した後に所定の遅延時間が経過した時刻T13にて、第1の検出部13は、出力信号S2の電圧レベルが安定したと判定し、制御信号t1をローレベルにする。制御部15は、制御信号t1がローレベルになると、制御信号SW1をローレベルからハイレベルにして、補助ドライバ12のPチャネルトランジスタ23をオン状態からオフ状態に変化させる。すなわち、制御信号t1、t2がともにローレベルである期間中は、制御部15により制御信号SW1がハイレベル、制御信号SW2がローレベルとされ、補助ドライバ12のトランジスタ23、24がオフ状態となる。このようにして、主ドライバ11での立ち下がり動作が終了すると、補助ドライバ12はオフ状態となるよう制御される。これにより、補助ドライバ12を介した定常的なリーク電流の発生を抑制し、消費電力を低減することができる。

【0031】

出力信号が電源電圧レベルLVGで安定している状態で、時刻T14にて、入力信号S1がハイレベルからローレベルに変化すると、主ドライバ11は、出力信号S2の電圧レベルを接地電圧レベルから電源電圧レベルに変化させるための立ち上がり動作を開始する。第1の検出部13は、入力信号S1のハイレベルからローレベルへの変化を検出し、制御信号t2をハイレベルにする。制御部15は、ハイレベルの制御信号t2を受けると、制御信号Bがハイレベルになるまで制御信号SW1をローレベルにする。すなわち、制御信号t2がハイレベルであり、かつ制御信号Bがローレベルである期間中は、制御部15により制御信号SW1、SW2がローレベルとされ、補助ドライバ12のPチャネルトランジスタ23がオン状態となる。

【0032】

このように、主ドライバ11で立ち上がり動作が開始されると、補助ドライバ12は、電源電圧側のトランジスタをオン状態にして電圧レベルが上がる方向に電圧をかけるように制御され、出力信号S3の接地電圧レベルから電源電圧レベルへの変化を補助する。したがって、出力信号S3における接地電圧レベルから電源電圧レベルへの変化の高速性が向上される。

【0033】

続いて、主ドライバ11の出力信号S2の電圧レベルが第2の電圧レベルLVBより高くなる時刻T15にて、第2の検出部14は、出力信号S2の電圧レベルが第2の電圧レベルLVBより高くなったことを検出し、制御信号Bをハイレベルにする。なお、出力信号S2の電圧レベルが第2の電圧レベルLVBより高くなる前に、第2の検出部14は、出力信号S2の電圧レベルが第1の電圧レベルLVAより低くないことを検出して制御信号Aをローレベルにしている。

【0034】

制御部15は、制御信号t2がハイレベルの状態で、ハイレベルの制御信号Bを受けると、制御信号SW1をローレベルからハイレベルにして、補助ドライバ12のPチャネルトランジスタ23をオフ状態にする。また、制御部15は、制御信号SW1をローレベルからハイレベルにした後に(同時であっても良い)、制御信号t2がローレベルになるまで制御信号SW2をハイレベルにする。すなわち、制御信号t2がハイレベルであり、かつ制御信号Bがハイレベルである期間中は、制御部15により制御信号SW1、SW2がハイレベルとされ、補助ドライバ12のNチャネルトランジスタ24がオン状態となる。

【0035】

このように、主ドライバ11の出力信号S2の電圧レベルが第2の電圧レベルLVBより高くなると、補助ドライバ12は、接地電圧側のトランジスタをオン状態にして電圧レベルが下がる方向に電圧をかけるように制御される。これにより、出力信号S3の電圧レベルが電源電圧を超えることを抑制し、オーバーシュートを軽減することができる。

【0036】

続いて、主ドライバ11の出力信号S2の電圧レベルが電源電圧レベルLVVに到達した後に所定の遅延時間が経過した時刻T16にて、第1の検出部13は、出力信号S2の電圧レベルが安定したと判定し、制御信号t2をローレベルにする。制御部15は、制御信号t2がローレベルになると、制御信号SW2をハイレベルからローレベルにして、補助ドライバ12のNチャネルトランジスタ24をオン状態からオフ状態に変化させる。このようにして、主ドライバ11での立ち上がり動作が終了すると、補助ドライバ12はオフ状態となるよう制御され、補助ドライバ12を介した定常的なリーク電流の発生を抑制し、消費電力を低減することができる。

【0037】

なお、出力信号S2の電圧レベルが電源電圧レベルLVVや接地電圧レベルLVGに到達した後に補助ドライバ12をオフ状態にするための所定の遅延時間は、例えば使用する主ドライバ11に応じて予め設定される。

【0038】

以上のように、主ドライバ11(出力信号S2)の状態に応じて補助ドライバ12を制御することで、半導体装置の出力端子OUTより出力される出力信号S3の波形は、図7に一例を示すように改善される。図7に示す信号波形において、71、74に示す箇所は、主ドライバ11だけが動作しており、補助ドライバ12がオフ状態であるときの波形を示している。また、72、75に示す箇所は、主ドライバ11が出力信号の電圧レベルを変化させようとする方向に対して、同方向の電圧が出力信号にかかるように補助ドライバ12が制御されている期間である。この期間においては、主ドライバ11及び補助ドライバ12の2つのドライバによって出力信号が駆動されるので、出力信号S3の信号変化が加速されて速やかな信号変化を実現でき高速性を向上させることができる。また、73、76に示す箇所は、主ドライバ11が出力信号の電圧レベルを変化させようとする方向に対して、逆方向の電圧が出力信号にかかるように補助ドライバ12が制御されている期間である。この期間においては、主ドライバ11による出力信号の変化を抑制するように補助ドライバ12が動作することで、出力信号S3の信号変化を緩和しオーバーシュートやアンダーシュートを軽減することできる。

【0039】

以下に、本実施形態における半導体装置が有する第1の検出部13、第2の検出部14、及び制御部15のそれぞれの構成例を示す。なお、以下に示す構成は一例であって、これに限定されるものではない。

【0040】

図4(A)は、第1の検出部13の第1の構成例を示す図である。図4(A)に示す第1の検出部13は、論理積演算回路(AND回路)31、33、及び遅延回路32、34を有する。

【0041】

2入力のAND回路31は、入力信号S1が第1の入力端に入力され、遅延回路32により所定の時間だけ遅延された入力信号S1が反転されて第2の入力端に入力される。なお、入力信号S1を反転した後に遅延回路32により遅延させた信号をAND回路31の第2の入力端に入力するようにしても良い。2入力のAND回路31の出力が制御信号t1として出力される。また、2入力のAND回路33は、入力信号S1が反転されて第1の入力端に入力され、遅延回路34により所定の時間だけ遅延された入力信号S1が第2の入力端に入力される。2入力のAND回路32の出力が制御信号t2として出力される。

【0042】

図4(A)に示す第1の検出部13は、入力信号S1がローレベルからハイレベルに変化するとき(出力信号S2が立ち下がるとき)に、入力信号S1の変化開始から遅延回路32による遅延時間が経過するまで、制御信号t1がハイレベルになる。同様に、入力信号S1がハイレベルからローレベルに変化するとき(出力信号S2が立ち上がるとき)に、入力信号S1の変化開始から遅延回路34による遅延時間が経過するまで、制御信号t2がハイレベルになる。図4(A)に示す第1の検出部13では、例えば使用する主ドライバ11に応じた遅延時間を有する遅延回路32、34を用いることで、図3に示した動作を実現する制御信号t1、t2を生成することが可能である。

【0043】

図4(B)は、第1の検出部13の第2の構成例を示す図である。図4(B)に示す第1の検出部13は、フリップフロップ35、36、否定論理和演算回路(NOR回路)37、38、AND回路39、40、42、及びインバータ(遅延回路)41を有する。

【0044】

フリップフロップ35、36は同じクロック信号で動作し、フリップフロップ35の出力がフリップフロップ36の入力端に入力される。フリップフロップ35の出力が主ドライバ11への入力信号S1に対応する。2入力のNOR回路37は、フリップフロップ35の出力が第1の入力端に入力され、フリップフロップ36の出力が第2の入力端に反転入力される。また、2入力のNOR回路38は、フリップフロップ35の出力が第1の入力端に反転入力され、フリップフロップ36の出力が第2の入力端に入力される。

【0045】

2入力のAND回路39は、NOR回路37の出力が第1の入力端に入力され、AND回路42の出力が第2の入力端に入力される。2入力のAND回路40は、NOR回路38の出力が第1の入力端に入力され、AND回路42の出力が第2の入力端に入力される。インバータ41には、フリップフロップ35、36の動作に用いられるクロック信号が入力される。2入力のAND回路42は、インバータ41の出力が第1の入力端に入力され、フリップフロップ35、36の動作に用いられるクロック信号が第2の入力端に入力される。2入力のAND回路39の出力が制御信号t2として出力され、2入力のAND回路40の出力が制御信号t1として出力される。

【0046】

図5(A)は、第2の検出部14の第1の構成例を示す図である。この図5(A)において、図2に示した構成要素と同一の構成要素には同一の符号を付している。図5(A)に示す第2の検出部14は、インバータ51及びバッファ52を有する。

【0047】

インバータ51は、入力端が主ドライバ11の出力端に接続され、出力が制御信号Aとして出力される。インバータ51は、その閾値(Vth)が接地電圧レベルLVGの近傍の第1の電圧レベルLVAである。したがって、制御信号Aとして出力されるインバータ51の出力は、主ドライバ11の出力端の電位が第1の電圧レベルLVAより低いときにはハイレベルとなり、そうでないときにはローレベルとなる。

【0048】

バッファ52は、入力端が主ドライバ11の出力端に接続され、出力が制御信号Bとして出力される。バッファ52は、その閾値(Vth)が電源電圧レベルLVVの近傍の第2の電圧レベルLVBである。したがって、制御信号Bとして出力されるバッファ52の出力は、主ドライバ11の出力端の電位が第2の電圧レベルLVBより高いときにはハイレベルとなり、そうでないときにはローレベルとなる。

【0049】

図5(B)は、第2の検出部14の第2の構成例を示す図である。この図5(B)において、図2に示した構成要素と同一の構成要素には同一の符号を付している。図5(B)に示す第2の検出部14は、コンパレータ(比較器)54、55を有する。コンパレータ53は、供給される主ドライバ11の出力端の電位が第1の電圧レベルLVAより低いか否かを判定し、判定結果を制御信号Aとして出力する。同様に、コンパレータ54は、供給される主ドライバ11の出力端の電位が第2の電圧レベルLVBより高いか否かを判定し、判定結果を制御信号Bとして出力する。

【0050】

図6(A)は、制御部15の構成例を示す図である。図6(A)に示す制御部15は、否定論理積演算回路(NAND回路)61、63、インバータ62、64、セレクタ65、66、及びNOR回路67、68を有する。

【0051】

2入力のNAND回路61は、制御信号Aが入力されるとともに、制御信号t2がインバータ62を介して入力され、その演算結果を出力する。2入力のNAND回路63は、制御信号Bが入力されるとともに、制御信号t1がインバータ64を介して入力され、その演算結果を出力する。セレクタ65は、制御信号t2がインバータ62を介して入力されるとともに、NAND回路61の出力が入力される。また、セレクタ65は、選択信号として制御信号t1がインバータ64を介して入力される。セレクタ65は、選択信号が“1”(制御信号t1が“0”)の場合にはインバータ62を介して入力される制御信号t2を出力し、選択信号が“0”(制御信号t1が“1”)の場合にはNAND回路61の出力を出力する。また、セレクタ66は、制御信号t1がインバータ64を介して入力されるとともに、NAND回路63の出力が入力される。また、セレクタ66は、選択信号として制御信号t2がインバータ62を介して入力される。セレクタ66は、選択信号が“1”(制御信号t2が“0”)の場合にはインバータ64を介して入力される制御信号t1を出力し、選択信号が“0”(制御信号t2が“1”)の場合にはNAND回路63の出力を出力する。

【0052】

2入力のNOR回路67は、制御信号B及びセレクタ65の出力が入力され、その演算結果を信号SW1として出力する。また、2入力のNOR回路68は、制御信号A及びセレクタ66の出力が入力され、その演算結果を信号SW2として出力する。ここで、信号SW1、SW2は、図6(B)に示す動作論理(真理値表)において、OFFと示される場合に“0”であり、ONと示される場合に“1”である。

【0053】

図6(A)に示した制御部15は、図6(B)に示す動作論理(真理値表)に従って入力信号(制御信号t1、t2、A、B)に応じた出力信号(制御信号SW1、SW2)を出力する。図6(B)において、t1、t2の欄は第1の検出部13から出力される制御信号t1、t2の値を示し、A、Bの欄は第2の検出部14から出力される制御信号A、Bの値を示す。また、SW1の欄は、制御信号SW1により制御されるPチャネルトランジスタ23の状態を示し、SW2の欄は、制御信号SW2により制御されるNチャネルトランジスタ24の状態を示している。すなわち、“ON”とは対応するトランジスタが導通状態であることを示し、“OFF”とは対応するトランジスタが非導通状態であることを示す。図6(B)中、“X”は任意(Don't care)であることを示す。

【0054】

図6(B)に示すように、制御部15は、制御信号t1が“1”(ハイレベル)、かつ制御信号t2及びAが“0”(ローレベル)であるとき(図3での時刻T11〜時刻T12に相当)、補助ドライバ12において電源電圧側トランジスタがオフ状態となり、接地電圧側トランジスタがオン状態となるよう制御信号SW1、SW2を出力する。制御部15は、制御信号t1及びAが“1”、かつ制御信号t2及びBが“0”であるとき(図3での時刻T12〜時刻T13に相当)、補助ドライバ12において電源電圧側トランジスタがオン状態となり、接地電圧側トランジスタがオフ状態となるよう制御信号SW1、SW2を出力する。

【0055】

また、制御部15は、制御信号t1及びBが“0”、かつ制御信号t2が“1”であるとき(図3での時刻T14〜時刻T15に相当)、補助ドライバ12において電源電圧側トランジスタがオン状態となり、接地電圧側トランジスタがオフ状態となるよう制御信号SW1、SW2を出力する。制御部15は、制御信号t1及びAが“0”、かつ制御信号t2及びBが“1”であるとき(図3での時刻T15〜時刻T16に相当)、補助ドライバ12において電源電圧側トランジスタがオフ状態となり、接地電圧側トランジスタがオン状態となるよう制御信号SW1、SW2を出力する。

【0056】

また、制御部15は、制御信号t1及びt2が“0”であるとき(図3での時刻T13〜時刻T14などに相当)、補助ドライバ12において電源電圧側トランジスタ及び接地電圧側トランジスタがともにオフ状態となるよう制御信号SW1、SW2を出力する。

【0057】

なお、図6(A)に示した制御部15の構成は一例であって、これに限定されるものではない。制御部15は、図6(B)に示した動作論理(真理値表)に従って入力信号に応じた出力信号を出力できれば良く、その回路構成等は任意である。

【0058】

なお、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

本発明の諸態様を付記として以下に示す。

【0059】

(付記1)

入力信号の電圧に応じた出力信号を出力信号線に出力する第1の駆動回路と、

前記出力信号線に出力端が接続された第2の駆動回路と、

前記第2の駆動回路を制御する制御部とを備え、

前記制御部は、前記入力信号の電圧変化に応じて前記出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、前記出力信号の電圧レベルが前記第1の電圧レベルと前記第2の電圧レベルとの間に設定された第3の電圧レベルに達するまでは前記第1の電圧レベルから前記第2の電圧レベルへの前記出力信号の変化を補助し、前記出力信号の電圧レベルが前記第3の電圧レベルに達した後に前記第1の電圧レベルから前記第2の電圧レベルへの前記出力信号の変化を抑制するよう前記第2の駆動回路を制御することを特徴とする半導体装置。

(付記2)

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルへ変化するときに、前記出力信号の電圧レベルが前記第3の電圧レベルに達するまでは前記第2の電圧レベルの側に変化させる電圧を前記第2の駆動回路により前記出力信号線に供給させ、前記出力信号の電圧レベルが前記第3の電圧レベルに達してから前記第2の電圧レベルになるまでの期間に前記第1の電圧レベルの側に変化させる電圧を前記第2の駆動回路により前記出力信号線に供給させることを特徴とする付記1記載の半導体装置。

(付記3)

前記入力信号の電圧変化を検出する第1の検出部と、

前記出力信号の電圧レベルが前記第3の電圧レベルに達したか否かを検出する第2の検出部とを備え、

前記制御部は、前記第1の検出部及び前記第2の検出部での検出結果に基づいて前記第2の駆動回路を制御することを特徴とする付記1記載の半導体装置。

(付記4)

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルに変化した後に、前記第2の駆動回路の動作を止めることを特徴とする付記1記載の半導体装置。

(付記5)

前記第3の電圧レベルは、前記第2の電圧レベルに到達直前の電圧レベルであることを特徴とする付記1記載の半導体装置。

(付記6)

前記第1の電圧レベルは接地電圧レベルであり、前記第2の電圧レベルは電源電圧レベルであり、前記第3の電圧レベルは0.80×(電源電圧レベル−接地電圧レベル)から0.95×(電源電圧レベル−接地電圧レベル)の間の任意の電圧レベルであることを特徴とする付記1記載の半導体装置。

(付記7)

前記第1の電圧レベルは電源電圧レベルであり、前記第2の電圧レベルは接地電圧レベルであり、前記第3の電圧レベルは0.05×(電源電圧レベル−接地電圧レベル)から0.20×(電源電圧レベル−接地電圧レベル)の間の任意の電圧レベルであることを特徴とする付記1記載の半導体装置。

(付記8)

前記入力信号の電圧変化に応じて前記出力信号が接地電圧レベルから電源電圧レベルへ変化する場合には、前記第1の電圧レベルを前記接地電圧レベルとし、前記第2の電圧レベルを前記電源電圧レベルとし、前記第3の電圧レベルを前記電源電圧レベルの近傍の電圧レベルとして動作するとともに、

前記入力信号の電圧変化に応じて前記出力信号が前記電源電圧レベルから前記接地電圧レベルへ変化する場合には、前記第1の電圧レベルを前記電源電圧レベルとし、前記第2の電圧レベルを前記接地電圧レベルとし、前記第3の電圧レベルを前記接地電圧レベルの近傍の電圧レベルとして動作することを特徴とする付記1記載の半導体装置。

(付記9)

入力信号の電圧に応じた出力信号を出力信号線に出力する駆動回路と、

ソースに第1の電圧レベルの電圧が供給され、ドレインが前記出力信号線に接続された第1のトランジスタと、

ソースに第2の電圧レベルの電圧が供給され、ドレインが前記出力信号線に接続された第2のトランジスタと、

前記入力信号の電圧変化に応じて前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルへ変化する場合に、前記出力信号の電圧レベルが前記第1の電圧レベルと前記第2の電圧レベルとの間に設定された第3の電圧レベルに達するまでは前記第1のトランジスタをオフ状態とするとともに前記第2のトランジスタをオン状態とし、前記出力信号の電圧レベルが前記第3の電圧レベルに達した後に前記第1のトランジスタをオン状態とするとともに前記第2のトランジスタをオフ状態とする制御部とを備えることを特徴とする半導体装置。

(付記10)

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルに変化した後に、前記第1のトランジスタ及び前記第2のトランジスタをともにオフ状態とすることを特徴とする付記9記載の半導体装置。

(付記11)

前記入力信号の電圧変化を検出し、検出結果に応じた第1の制御信号を前記制御部に出力する第1の検出部と、

前記出力信号の電圧レベルが前記第3の電圧レベルを超えているか否かを検出し、検出結果に応じた第2の制御信号を前記制御部に出力する第2の検出部とを備え、

前記制御部は、前記第1の制御信号及び前記第2の制御信号に基づいて、前記第1のトランジスタ及び前記第2のトランジスタを制御することを特徴とする付記9記載の半導体装置。

(付記12)

前記第1の検出部は、前記第1の制御信号を、前記入力信号の電圧変化の検出時にアサートして前記出力信号が前記第2の電圧レベルに変化した後にネゲートし、

前記第2の検出部は、前記第2の制御信号を、前記出力信号の電圧レベルが前記第3の電圧レベルを境界として前記第2の電圧レベル側である場合にはアサートして前記第1の電圧レベル側である場合にはネゲートし、

前記制御部は、前記第1の制御信号がアサートされ、かつ前記第2の制御信号がネゲートされている期間は、前記第1のトランジスタをオフ状態とするとともに前記第2のトランジスタをオン状態とし、前記第1の制御信号がアサートされ、かつ前記第2の制御信号がアサートされている期間は、前記第1のトランジスタをオン状態とするとともに前記第2のトランジスタをオフ状態とすることを特徴とする付記9記載の半導体装置。

(付記13)

前記入力信号の電圧変化に応じて前記出力信号が接地電圧レベルから電源電圧レベルへ変化する場合には、前記第1の電圧レベルを前記接地電圧レベルとし、前記第2の電圧レベルを前記電源電圧レベルとし、前記第3の電圧レベルを前記電源電圧レベルの近傍の電圧レベルとして動作するとともに、

前記入力信号の電圧変化に応じて前記出力信号が前記電源電圧レベルから前記接地電圧レベルへ変化する場合には、前記第1の電圧レベルを前記電源電圧レベルとし、前記第2の電圧レベルを前記接地電圧レベルとし、前記第3の電圧レベルを前記接地電圧レベルの近傍の電圧レベルとして動作することを特徴とする付記9記載の半導体装置。

【符号の説明】

【0060】

11 主ドライバ

12 補助ドライバ

13 第1の検出部(立上り/立下り検出)

14 第2の検出部(電圧レベル検出)

15 制御部

【技術分野】

【0001】

本発明は、半導体装置に関し、半導体装置からの信号出力に係る制御技術に関する。

【背景技術】

【0002】

半導体装置を構成する通常のCMOS回路において、信号の電圧レベルは、ハイレベルとしての電源電圧レベル又はローレベルとしての接地電圧レベルの2つの状態があり、その電圧レベルにて信号を伝送する。信号の変化は、接地電圧レベルから電源電圧レベルに、もしくは電源電圧レベルから接地電圧レベルに信号の電圧レベルを変化させることで行う。しかし、伝送回路に寄生する容量の影響により、目的とする電源電圧レベルや接地電圧レベルを超えた電圧レベルに達する、いわゆるオーバーシュートやアンダーシュートが発生することがあり、その信号波形の乱れがノイズとなり伝送品質を低下させる。また、信号の変化を高速に行うために駆動能力を大きくするなどして高速性を重視すると、オーバーシュートやアンダーシュートが大きくなる。

【0003】

オーバーシュートやアンダーシュートを抑制する方法として、例えば図8に示すような回路構成が用いられる。図8(A)は、出力回路の一例を示す図である。図8(A)において、ドライバ(出力バッファ)81は、例えばCMOSトランジスタで構成されるインバータであり、電源電圧Vdd及び接地電圧Gndがそれぞれ供給される配線間に接続されたPチャネルトランジスタ82及びNチャネルトランジスタ83を有する。出力回路に入力された入力信号は、ドライバ81を介して出力端子OUTより出力信号として出力される。

【0004】

また、図8(A)に示す出力回路においては、出力信号の信号線に終端抵抗84、85が接続されている。このように終端抵抗84、85を設けることで伝送回路の寄生容量による影響を抑えて、信号の電圧レベルが電源電圧レベルや接地電圧レベルを超えることを抑制し、オーバーシュートやアンダーシュートを軽減している。図8(B)は、図8(A)に示したように終端抵抗を接続した場合における出力信号の波形を示す図である。図8(B)において、実線で示す信号波形86が終端抵抗を接続した場合の出力信号を示し、破線で示す信号波形87が終端抵抗を接続しなかったとした場合の出力波形を示している。

【0005】

また、出力信号を出力する2つのドライバのうちの1つのドライバの動作を、信号の電圧レベルが目的とする電源電圧レベル又は接地電圧レベルになる直前に停止させることで、オーバーシュートやアンダーシュートを軽減する方法が提案されている(例えば、特許文献1参照。)。また、出力信号の変化時に、信号の電圧レベルがある電圧レベルになるまでは1つのドライバを動作させ、その電圧レベルに達すると2つのドライバを動作させる方法が提案されている(例えば、特許文献2、3参照。)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平3−242020号公報

【特許文献2】特開平5−243958号公報

【特許文献3】特開平3−89624号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

前述のように出力信号の信号線に終端抵抗を接続すると、図8(B)に示したように、オーバーシュートやアンダーシュートは軽減するが、定常時の電圧レベルが終端抵抗の影響により電源電圧レベルや接地電圧レベルに達せず、信号の振幅レベルが小さくなる。また、出力信号の信号線に対して、終端抵抗を介して接続される電源又は接地電圧(グランド)から信号変化とは逆の電圧レベルがかかることで、出力信号の変化を開始してから終了するまでの時間が増大し、信号変化が遅くなる。また、終端抵抗を介して電源及び接地電圧(グランド)に接続されることで、定常的にリーク電流が発生し、消費電力が増大する。

【0008】

また、特許文献1に記載の技術では、1つのドライバの動作を停止させることでオーバーシュートやアンダーシュートは軽減する。しかし、もう1つのドライバは動作し続けるために、伝送回路に寄生する容量の影響を受けてオーバーシュートやアンダーシュートが発生する。なお、オーバーシュートやアンダーシュートを抑制する方法として、時間当たりの電圧変化量を小さくすることも考えられるが、出力信号の変化に要する時間が増大し高速動作が不可能になる。

【0009】

本発明の目的は、出力信号の変化を高速に行い、かつ出力信号におけるオーバーシュートやアンダーシュートを抑制する半導体装置を提供することにある。

【課題を解決するための手段】

【0010】

半導体装置の一態様は、入力信号の電圧に応じた出力信号を出力信号線に出力する第1の駆動回路と、出力信号線に出力端が接続された第2の駆動回路と、第2の駆動回路を制御する制御部とを備える。制御部は、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、出力信号の電圧レベルが第3の電圧レベルに達するまでは出力信号の変化を補助し、出力信号の電圧レベルが第3の電圧レベルに達した後に出力信号の変化を抑制するよう第2の駆動回路を制御する。

【発明の効果】

【0011】

入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、出力信号の電圧レベルが第3の電圧レベルに達するまで出力信号の変化を補助し、その後、出力信号の変化を抑制するよう第2の駆動回路を制御するので、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制することができる。

【図面の簡単な説明】

【0012】

【図1】本発明の実施形態における半導体装置の構成例を示す図である。

【図2】本実施形態における半導体装置の構成例を示す図である。

【図3】本実施形態における半導体装置の動作を説明するための信号波形図である。

【図4】本実施形態における第1の検出部の構成例を示す図である。

【図5】本実施形態における第2の検出部の構成例を示す図である。

【図6】本実施形態における制御部の構成例を示す図である。

【図7】本実施形態における半導体装置による出力波形の一例を示す図である。

【図8】出力回路の一例を示す図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施形態を図面に基づいて説明する。

図1は、本発明の一実施形態における半導体装置の構成例を示す図である。図1において、11は主ドライバ(出力バッファ)であり、12は補助ドライバ(補助出力バッファ)である。また、13は第1の検出部であり、14は第2の検出部であり、15は制御部である。

【0014】

主ドライバ11は、入力端より入力される入力信号S1を受け、それを反転して出力信号S2として出力する。補助ドライバ12は、その駆動能力が主ドライバ11の駆動能力より小さいドライバであり、制御部15から出力される制御信号により動作が制御される。補助ドライバ12は、制御部15からの制御信号に応じた出力を出力信号S4として出力する。出力信号S2と出力信号S4を合成したものが、半導体装置の出力端OUTより出力される出力信号S3に対応する。なお、補助ドライバ12の駆動能力は、主ドライバ11の駆動能力と同じであっても良い。

【0015】

第1の検出部13は、主ドライバ11の入力信号S1を入力とし、入力信号S1に基づいて主ドライバ11における出力信号S2の変化及びそれに係る時間を検出する。第1の検出部13は、検出結果に応じて制御信号を制御部15に出力する。第2の検出部14は、主ドライバ11の出力信号S2を入力とし、出力信号S2の電圧レベルを検出する。第2の検出部14は、検出結果を制御信号により制御部15に出力する。制御部15は、第1の検出部13の出力(制御信号)及び第2の検出部14の出力(制御信号)を入力とし、それらの出力(制御信号)に基づいて補助ドライバ12の動作を制御するための制御信号を生成し出力する。

【0016】

図2は、本実施形態における半導体装置の詳細な構成例を示す図である。この図2において、図1に示した構成要素と同一の機能を有する構成要素には同一の符号を付している。

【0017】

図2に示すように、主ドライバ11は、電源電圧Vdd及び接地電圧Gndがそれぞれ供給される配線間に接続されたPチャネル型電界効果トランジスタ21及びNチャネル型電界効果トランジスタ22を有する。Pチャネルトランジスタ21は、ソースに電源電圧Vddが供給され、ドレインがNチャネルトランジスタ22のドレインに接続される。Nチャネルトランジスタ22は、ソースに接地電圧Gndが供給される。また、Pチャネルトランジスタ21及びNチャネルトランジスタ22のゲートには、入力信号S1が供給される。Pチャネルトランジスタ21及びNチャネルトランジスタ22のドレインの相互接続点の電位が、主ドライバ11の出力信号S2として、出力信号S3の信号線に対して出力される。

【0018】

補助ドライバ12は、電源電圧Vdd及び接地電圧Gndがそれぞれ供給される配線間に接続されたPチャネル型電界効果トランジスタ23及びNチャネル型電界効果トランジスタ24を有する。Pチャネルトランジスタ23は、ソースに電源電圧Vddが供給され、ドレインがNチャネルトランジスタ24のドレインに接続される。Nチャネルトランジスタ24は、ソースに接地電圧Gndが供給される。また、Pチャネルトランジスタ23のゲートには、制御部15から出力される制御信号SW1が供給され、Nチャネルトランジスタ24のゲートには、制御部15から出力される制御信号SW2が供給される。Pチャネルトランジスタ23及びNチャネルトランジスタ24のドレインの相互接続点は、出力信号S3の信号線に接続される。

【0019】

第1の検出部13は、主ドライバ11への入力信号S1を受けて、制御信号t1、t2を出力する。第1の検出部13は、入力信号S1に基づいて、主ドライバ11における出力信号S2の電圧レベルが、電源電圧レベルから接地電圧レベルに変化するか(立ち下がり)、接地電圧レベルから電源電圧レベルに変化するか(立ち上がり)を検出する。また、第1の検出部13は、主ドライバ11による立ち下がり動作の開始及び終了のタイミング又は立ち上がり動作の開始及び終了のタイミングを検出する。そして、第1の検出部13は、検出結果に応じて、主ドライバ11における立ち下がり動作時に(詳細には、立ち下がり動作の開始から動作終了後の安定期間までの期間において)制御信号t1をアサートする。また、第1の検出部13は、検出結果に応じて、主ドライバ11における立ち上がり動作時に(詳細には、立ち上がり動作の開始から動作終了後の安定期間までの期間において)制御信号t2をアサートする。

【0020】

第2の検出部14は、主ドライバ11の出力信号S2を受けて出力信号S2の電圧レベルを検出し、検出された電圧レベルに応じて制御信号A、Bを出力する。第2の検出部14は、出力信号S2の電圧レベルが接地電圧レベルの近傍の第1の電圧レベルより低いか否かを検出し、第1の電圧レベルより低いときには制御信号Aをアサートし、そうでないときには制御信号Aをネゲートする。また、第2の検出部14は、出力信号S2の電圧レベルが電源電圧レベルの近傍の第2の電圧レベルより高いか否かを検出し、第2の電圧レベルより高いときには制御信号Bをアサートし、そうでないときには制御信号Bをネゲートする。

【0021】

ここで、第1の電圧レベル及び第2の電圧レベルは、電源電圧Vddと接地電圧Gndとの間の電圧レベルであって、(接地電圧Gnd)<(第1の電圧レベル)<(第2の電圧レベル)<(電源電圧Vdd)の関係を満たす。例えば、第1の電圧レベルは0.05×(Vdd−Gnd)〜0.20×(Vdd−Gnd)の範囲内の任意の電圧レベルであり、第2の電圧レベルは0.80×(Vdd−Gnd)〜0.95×(Vdd−Gnd)の範囲内の任意の電圧レベルである。

【0022】

制御部15は、第1の検出部13から出力される制御信号t1、t2、及び第2の検出部14から出力される制御信号A、Bを受けて、補助ドライバ12の動作を制御する制御信号SW1、SW2を出力する。すなわち、制御部15は、制御信号t1、t2、及び制御信号A、Bに基づいて、図3に示すように制御信号SW1、SW2を出力し補助ドライバ12のトランジスタ23、24をオン/オフ制御する。

【0023】

図3は、本実施形態における半導体装置の動作を説明するための信号波形図である。図3において、t1、t2は、第1の検出部13から制御部15に出力される制御信号であり、A、Bは、第2の検出部14から制御部15に出力される制御信号である。なお、制御信号t1、t2及び制御信号A、Bは、アサートされているときにハイレベルにされ、ネゲートされているときにローレベルにされるとする。SW1、SW2は、制御部15から補助ドライバ12に出力される制御信号である。図3には、補助ドライバ12のPチャネルトランジスタ23及びNチャネルトランジスタ24がオン状態とされる期間をハイレベルに対応させて示すために制御信号SW1についてはその反転信号を示している。また、LVVは電源電圧レベル、LVGは接地電圧レベル、LVAは接地電圧レベルLVGの近傍の第1の電圧レベル、LVBは電源電圧レベルLVVの近傍の第2の電圧レベルである。

【0024】

まず、図3において最初の状態は、主ドライバ11への入力信号S1がローレベルの状態で十分な時間が経過し、主ドライバ11の出力信号S2の電圧レベルが電源電圧レベルLVVで安定しているものとする。このとき、制御信号t1、t2及び制御信号Aはローレベルであり、制御信号Bはハイレベルである。また、制御信号t1、t2及び制御信号A、Bがこの状態であるとき、制御部15から出力される制御信号SW1はハイレベルであり、制御部15から出力される制御信号SW2はローレベルである。したがって、補助ドライバ12のトランジスタ23、24はともにオフ状態(非導通状態)であり、補助ドライバ12はオフ状態である。

【0025】

時刻T11にて、入力信号S1がローレベルからハイレベルに変化すると、主ドライバ11は、出力信号S2の電圧レベルを電源電圧レベルから接地電圧レベルに変化させるための立ち下がり動作を開始する。また、第1の検出部13は、入力信号S1のローレベルからハイレベルへの変化を検出し、制御信号t1をハイレベルにする。制御部15は、ハイレベルの制御信号t1を受けると、制御信号Aがハイレベルになるまで制御信号SW2をハイレベルにする。すなわち、制御信号t1がハイレベルであり、かつ制御信号Aがローレベルである期間中は、制御部15により制御信号SW1、SW2がハイレベルとされ、補助ドライバ12のNチャネルトランジスタ24がオン状態(導通状態)となる。

【0026】

このように、主ドライバ11で立ち下がり動作が開始されると、補助ドライバ12は、接地電圧側のトランジスタをオン状態にして電圧レベルが下がる方向に電圧をかけるように制御され、出力信号S3の電源電圧レベルから接地電圧レベルへの変化を補助する。したがって、出力信号S3における電源電圧レベルから接地電圧レベルへの変化の高速性が向上される。

【0027】

続いて、主ドライバ11の出力信号S2の電圧レベルが第1の電圧レベルLVAより低くなる時刻T12にて、第2の検出部14は、出力信号S2の電圧レベルが第1の電圧レベルLVAより低くなったことを検出し、制御信号Aをハイレベルにする。なお、出力信号S2の電圧レベルが第1の電圧レベルLVAより低くなる前に、第2の検出部14は、出力信号S2の電圧レベルが第2の電圧レベルLVBより高くないことを検出して制御信号Bをローレベルにしている。

【0028】

制御部15は、制御信号t1がハイレベルの状態で、ハイレベルの制御信号Aを受けると、制御信号SW2をハイレベルからローレベルにして、補助ドライバ12のNチャネルトランジスタ24をオン状態からオフ状態に変化させる。また、制御部15は、制御信号SW2をハイレベルからローレベルにした後に(同時であっても良い)、制御信号t1がローレベルになるまで制御信号SW1をローレベルにする。すなわち、制御信号t1がハイレベルであり、かつ制御信号Aがハイレベルである期間中は、制御部15により制御信号SW1、SW2がローレベルとされ、補助ドライバ12のPチャネルトランジスタ23がオン状態(導通状態)となる。

【0029】

このように、主ドライバ11の出力信号S2の電圧レベルが第1の電圧レベルLVAより低くなると、補助ドライバ12は、電源電圧側のトランジスタをオン状態にして電圧レベルが上がる方向に電圧をかけるように制御される。これにより、出力信号S3の電圧レベルが接地電圧を超えることを抑制し、アンダーシュートを軽減することができる。

【0030】

続いて、主ドライバ11の出力信号S2の電圧レベルが接地電圧レベルLVGに到達した後に所定の遅延時間が経過した時刻T13にて、第1の検出部13は、出力信号S2の電圧レベルが安定したと判定し、制御信号t1をローレベルにする。制御部15は、制御信号t1がローレベルになると、制御信号SW1をローレベルからハイレベルにして、補助ドライバ12のPチャネルトランジスタ23をオン状態からオフ状態に変化させる。すなわち、制御信号t1、t2がともにローレベルである期間中は、制御部15により制御信号SW1がハイレベル、制御信号SW2がローレベルとされ、補助ドライバ12のトランジスタ23、24がオフ状態となる。このようにして、主ドライバ11での立ち下がり動作が終了すると、補助ドライバ12はオフ状態となるよう制御される。これにより、補助ドライバ12を介した定常的なリーク電流の発生を抑制し、消費電力を低減することができる。

【0031】

出力信号が電源電圧レベルLVGで安定している状態で、時刻T14にて、入力信号S1がハイレベルからローレベルに変化すると、主ドライバ11は、出力信号S2の電圧レベルを接地電圧レベルから電源電圧レベルに変化させるための立ち上がり動作を開始する。第1の検出部13は、入力信号S1のハイレベルからローレベルへの変化を検出し、制御信号t2をハイレベルにする。制御部15は、ハイレベルの制御信号t2を受けると、制御信号Bがハイレベルになるまで制御信号SW1をローレベルにする。すなわち、制御信号t2がハイレベルであり、かつ制御信号Bがローレベルである期間中は、制御部15により制御信号SW1、SW2がローレベルとされ、補助ドライバ12のPチャネルトランジスタ23がオン状態となる。

【0032】

このように、主ドライバ11で立ち上がり動作が開始されると、補助ドライバ12は、電源電圧側のトランジスタをオン状態にして電圧レベルが上がる方向に電圧をかけるように制御され、出力信号S3の接地電圧レベルから電源電圧レベルへの変化を補助する。したがって、出力信号S3における接地電圧レベルから電源電圧レベルへの変化の高速性が向上される。

【0033】

続いて、主ドライバ11の出力信号S2の電圧レベルが第2の電圧レベルLVBより高くなる時刻T15にて、第2の検出部14は、出力信号S2の電圧レベルが第2の電圧レベルLVBより高くなったことを検出し、制御信号Bをハイレベルにする。なお、出力信号S2の電圧レベルが第2の電圧レベルLVBより高くなる前に、第2の検出部14は、出力信号S2の電圧レベルが第1の電圧レベルLVAより低くないことを検出して制御信号Aをローレベルにしている。

【0034】

制御部15は、制御信号t2がハイレベルの状態で、ハイレベルの制御信号Bを受けると、制御信号SW1をローレベルからハイレベルにして、補助ドライバ12のPチャネルトランジスタ23をオフ状態にする。また、制御部15は、制御信号SW1をローレベルからハイレベルにした後に(同時であっても良い)、制御信号t2がローレベルになるまで制御信号SW2をハイレベルにする。すなわち、制御信号t2がハイレベルであり、かつ制御信号Bがハイレベルである期間中は、制御部15により制御信号SW1、SW2がハイレベルとされ、補助ドライバ12のNチャネルトランジスタ24がオン状態となる。

【0035】

このように、主ドライバ11の出力信号S2の電圧レベルが第2の電圧レベルLVBより高くなると、補助ドライバ12は、接地電圧側のトランジスタをオン状態にして電圧レベルが下がる方向に電圧をかけるように制御される。これにより、出力信号S3の電圧レベルが電源電圧を超えることを抑制し、オーバーシュートを軽減することができる。

【0036】

続いて、主ドライバ11の出力信号S2の電圧レベルが電源電圧レベルLVVに到達した後に所定の遅延時間が経過した時刻T16にて、第1の検出部13は、出力信号S2の電圧レベルが安定したと判定し、制御信号t2をローレベルにする。制御部15は、制御信号t2がローレベルになると、制御信号SW2をハイレベルからローレベルにして、補助ドライバ12のNチャネルトランジスタ24をオン状態からオフ状態に変化させる。このようにして、主ドライバ11での立ち上がり動作が終了すると、補助ドライバ12はオフ状態となるよう制御され、補助ドライバ12を介した定常的なリーク電流の発生を抑制し、消費電力を低減することができる。

【0037】

なお、出力信号S2の電圧レベルが電源電圧レベルLVVや接地電圧レベルLVGに到達した後に補助ドライバ12をオフ状態にするための所定の遅延時間は、例えば使用する主ドライバ11に応じて予め設定される。

【0038】

以上のように、主ドライバ11(出力信号S2)の状態に応じて補助ドライバ12を制御することで、半導体装置の出力端子OUTより出力される出力信号S3の波形は、図7に一例を示すように改善される。図7に示す信号波形において、71、74に示す箇所は、主ドライバ11だけが動作しており、補助ドライバ12がオフ状態であるときの波形を示している。また、72、75に示す箇所は、主ドライバ11が出力信号の電圧レベルを変化させようとする方向に対して、同方向の電圧が出力信号にかかるように補助ドライバ12が制御されている期間である。この期間においては、主ドライバ11及び補助ドライバ12の2つのドライバによって出力信号が駆動されるので、出力信号S3の信号変化が加速されて速やかな信号変化を実現でき高速性を向上させることができる。また、73、76に示す箇所は、主ドライバ11が出力信号の電圧レベルを変化させようとする方向に対して、逆方向の電圧が出力信号にかかるように補助ドライバ12が制御されている期間である。この期間においては、主ドライバ11による出力信号の変化を抑制するように補助ドライバ12が動作することで、出力信号S3の信号変化を緩和しオーバーシュートやアンダーシュートを軽減することできる。

【0039】

以下に、本実施形態における半導体装置が有する第1の検出部13、第2の検出部14、及び制御部15のそれぞれの構成例を示す。なお、以下に示す構成は一例であって、これに限定されるものではない。

【0040】

図4(A)は、第1の検出部13の第1の構成例を示す図である。図4(A)に示す第1の検出部13は、論理積演算回路(AND回路)31、33、及び遅延回路32、34を有する。

【0041】

2入力のAND回路31は、入力信号S1が第1の入力端に入力され、遅延回路32により所定の時間だけ遅延された入力信号S1が反転されて第2の入力端に入力される。なお、入力信号S1を反転した後に遅延回路32により遅延させた信号をAND回路31の第2の入力端に入力するようにしても良い。2入力のAND回路31の出力が制御信号t1として出力される。また、2入力のAND回路33は、入力信号S1が反転されて第1の入力端に入力され、遅延回路34により所定の時間だけ遅延された入力信号S1が第2の入力端に入力される。2入力のAND回路32の出力が制御信号t2として出力される。

【0042】

図4(A)に示す第1の検出部13は、入力信号S1がローレベルからハイレベルに変化するとき(出力信号S2が立ち下がるとき)に、入力信号S1の変化開始から遅延回路32による遅延時間が経過するまで、制御信号t1がハイレベルになる。同様に、入力信号S1がハイレベルからローレベルに変化するとき(出力信号S2が立ち上がるとき)に、入力信号S1の変化開始から遅延回路34による遅延時間が経過するまで、制御信号t2がハイレベルになる。図4(A)に示す第1の検出部13では、例えば使用する主ドライバ11に応じた遅延時間を有する遅延回路32、34を用いることで、図3に示した動作を実現する制御信号t1、t2を生成することが可能である。

【0043】

図4(B)は、第1の検出部13の第2の構成例を示す図である。図4(B)に示す第1の検出部13は、フリップフロップ35、36、否定論理和演算回路(NOR回路)37、38、AND回路39、40、42、及びインバータ(遅延回路)41を有する。

【0044】

フリップフロップ35、36は同じクロック信号で動作し、フリップフロップ35の出力がフリップフロップ36の入力端に入力される。フリップフロップ35の出力が主ドライバ11への入力信号S1に対応する。2入力のNOR回路37は、フリップフロップ35の出力が第1の入力端に入力され、フリップフロップ36の出力が第2の入力端に反転入力される。また、2入力のNOR回路38は、フリップフロップ35の出力が第1の入力端に反転入力され、フリップフロップ36の出力が第2の入力端に入力される。

【0045】

2入力のAND回路39は、NOR回路37の出力が第1の入力端に入力され、AND回路42の出力が第2の入力端に入力される。2入力のAND回路40は、NOR回路38の出力が第1の入力端に入力され、AND回路42の出力が第2の入力端に入力される。インバータ41には、フリップフロップ35、36の動作に用いられるクロック信号が入力される。2入力のAND回路42は、インバータ41の出力が第1の入力端に入力され、フリップフロップ35、36の動作に用いられるクロック信号が第2の入力端に入力される。2入力のAND回路39の出力が制御信号t2として出力され、2入力のAND回路40の出力が制御信号t1として出力される。

【0046】

図5(A)は、第2の検出部14の第1の構成例を示す図である。この図5(A)において、図2に示した構成要素と同一の構成要素には同一の符号を付している。図5(A)に示す第2の検出部14は、インバータ51及びバッファ52を有する。

【0047】

インバータ51は、入力端が主ドライバ11の出力端に接続され、出力が制御信号Aとして出力される。インバータ51は、その閾値(Vth)が接地電圧レベルLVGの近傍の第1の電圧レベルLVAである。したがって、制御信号Aとして出力されるインバータ51の出力は、主ドライバ11の出力端の電位が第1の電圧レベルLVAより低いときにはハイレベルとなり、そうでないときにはローレベルとなる。

【0048】

バッファ52は、入力端が主ドライバ11の出力端に接続され、出力が制御信号Bとして出力される。バッファ52は、その閾値(Vth)が電源電圧レベルLVVの近傍の第2の電圧レベルLVBである。したがって、制御信号Bとして出力されるバッファ52の出力は、主ドライバ11の出力端の電位が第2の電圧レベルLVBより高いときにはハイレベルとなり、そうでないときにはローレベルとなる。

【0049】

図5(B)は、第2の検出部14の第2の構成例を示す図である。この図5(B)において、図2に示した構成要素と同一の構成要素には同一の符号を付している。図5(B)に示す第2の検出部14は、コンパレータ(比較器)54、55を有する。コンパレータ53は、供給される主ドライバ11の出力端の電位が第1の電圧レベルLVAより低いか否かを判定し、判定結果を制御信号Aとして出力する。同様に、コンパレータ54は、供給される主ドライバ11の出力端の電位が第2の電圧レベルLVBより高いか否かを判定し、判定結果を制御信号Bとして出力する。

【0050】

図6(A)は、制御部15の構成例を示す図である。図6(A)に示す制御部15は、否定論理積演算回路(NAND回路)61、63、インバータ62、64、セレクタ65、66、及びNOR回路67、68を有する。

【0051】

2入力のNAND回路61は、制御信号Aが入力されるとともに、制御信号t2がインバータ62を介して入力され、その演算結果を出力する。2入力のNAND回路63は、制御信号Bが入力されるとともに、制御信号t1がインバータ64を介して入力され、その演算結果を出力する。セレクタ65は、制御信号t2がインバータ62を介して入力されるとともに、NAND回路61の出力が入力される。また、セレクタ65は、選択信号として制御信号t1がインバータ64を介して入力される。セレクタ65は、選択信号が“1”(制御信号t1が“0”)の場合にはインバータ62を介して入力される制御信号t2を出力し、選択信号が“0”(制御信号t1が“1”)の場合にはNAND回路61の出力を出力する。また、セレクタ66は、制御信号t1がインバータ64を介して入力されるとともに、NAND回路63の出力が入力される。また、セレクタ66は、選択信号として制御信号t2がインバータ62を介して入力される。セレクタ66は、選択信号が“1”(制御信号t2が“0”)の場合にはインバータ64を介して入力される制御信号t1を出力し、選択信号が“0”(制御信号t2が“1”)の場合にはNAND回路63の出力を出力する。

【0052】

2入力のNOR回路67は、制御信号B及びセレクタ65の出力が入力され、その演算結果を信号SW1として出力する。また、2入力のNOR回路68は、制御信号A及びセレクタ66の出力が入力され、その演算結果を信号SW2として出力する。ここで、信号SW1、SW2は、図6(B)に示す動作論理(真理値表)において、OFFと示される場合に“0”であり、ONと示される場合に“1”である。

【0053】

図6(A)に示した制御部15は、図6(B)に示す動作論理(真理値表)に従って入力信号(制御信号t1、t2、A、B)に応じた出力信号(制御信号SW1、SW2)を出力する。図6(B)において、t1、t2の欄は第1の検出部13から出力される制御信号t1、t2の値を示し、A、Bの欄は第2の検出部14から出力される制御信号A、Bの値を示す。また、SW1の欄は、制御信号SW1により制御されるPチャネルトランジスタ23の状態を示し、SW2の欄は、制御信号SW2により制御されるNチャネルトランジスタ24の状態を示している。すなわち、“ON”とは対応するトランジスタが導通状態であることを示し、“OFF”とは対応するトランジスタが非導通状態であることを示す。図6(B)中、“X”は任意(Don't care)であることを示す。

【0054】

図6(B)に示すように、制御部15は、制御信号t1が“1”(ハイレベル)、かつ制御信号t2及びAが“0”(ローレベル)であるとき(図3での時刻T11〜時刻T12に相当)、補助ドライバ12において電源電圧側トランジスタがオフ状態となり、接地電圧側トランジスタがオン状態となるよう制御信号SW1、SW2を出力する。制御部15は、制御信号t1及びAが“1”、かつ制御信号t2及びBが“0”であるとき(図3での時刻T12〜時刻T13に相当)、補助ドライバ12において電源電圧側トランジスタがオン状態となり、接地電圧側トランジスタがオフ状態となるよう制御信号SW1、SW2を出力する。

【0055】

また、制御部15は、制御信号t1及びBが“0”、かつ制御信号t2が“1”であるとき(図3での時刻T14〜時刻T15に相当)、補助ドライバ12において電源電圧側トランジスタがオン状態となり、接地電圧側トランジスタがオフ状態となるよう制御信号SW1、SW2を出力する。制御部15は、制御信号t1及びAが“0”、かつ制御信号t2及びBが“1”であるとき(図3での時刻T15〜時刻T16に相当)、補助ドライバ12において電源電圧側トランジスタがオフ状態となり、接地電圧側トランジスタがオン状態となるよう制御信号SW1、SW2を出力する。

【0056】

また、制御部15は、制御信号t1及びt2が“0”であるとき(図3での時刻T13〜時刻T14などに相当)、補助ドライバ12において電源電圧側トランジスタ及び接地電圧側トランジスタがともにオフ状態となるよう制御信号SW1、SW2を出力する。

【0057】

なお、図6(A)に示した制御部15の構成は一例であって、これに限定されるものではない。制御部15は、図6(B)に示した動作論理(真理値表)に従って入力信号に応じた出力信号を出力できれば良く、その回路構成等は任意である。

【0058】

なお、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

本発明の諸態様を付記として以下に示す。

【0059】

(付記1)

入力信号の電圧に応じた出力信号を出力信号線に出力する第1の駆動回路と、

前記出力信号線に出力端が接続された第2の駆動回路と、

前記第2の駆動回路を制御する制御部とを備え、

前記制御部は、前記入力信号の電圧変化に応じて前記出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、前記出力信号の電圧レベルが前記第1の電圧レベルと前記第2の電圧レベルとの間に設定された第3の電圧レベルに達するまでは前記第1の電圧レベルから前記第2の電圧レベルへの前記出力信号の変化を補助し、前記出力信号の電圧レベルが前記第3の電圧レベルに達した後に前記第1の電圧レベルから前記第2の電圧レベルへの前記出力信号の変化を抑制するよう前記第2の駆動回路を制御することを特徴とする半導体装置。

(付記2)

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルへ変化するときに、前記出力信号の電圧レベルが前記第3の電圧レベルに達するまでは前記第2の電圧レベルの側に変化させる電圧を前記第2の駆動回路により前記出力信号線に供給させ、前記出力信号の電圧レベルが前記第3の電圧レベルに達してから前記第2の電圧レベルになるまでの期間に前記第1の電圧レベルの側に変化させる電圧を前記第2の駆動回路により前記出力信号線に供給させることを特徴とする付記1記載の半導体装置。

(付記3)

前記入力信号の電圧変化を検出する第1の検出部と、

前記出力信号の電圧レベルが前記第3の電圧レベルに達したか否かを検出する第2の検出部とを備え、

前記制御部は、前記第1の検出部及び前記第2の検出部での検出結果に基づいて前記第2の駆動回路を制御することを特徴とする付記1記載の半導体装置。

(付記4)

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルに変化した後に、前記第2の駆動回路の動作を止めることを特徴とする付記1記載の半導体装置。

(付記5)

前記第3の電圧レベルは、前記第2の電圧レベルに到達直前の電圧レベルであることを特徴とする付記1記載の半導体装置。

(付記6)

前記第1の電圧レベルは接地電圧レベルであり、前記第2の電圧レベルは電源電圧レベルであり、前記第3の電圧レベルは0.80×(電源電圧レベル−接地電圧レベル)から0.95×(電源電圧レベル−接地電圧レベル)の間の任意の電圧レベルであることを特徴とする付記1記載の半導体装置。

(付記7)

前記第1の電圧レベルは電源電圧レベルであり、前記第2の電圧レベルは接地電圧レベルであり、前記第3の電圧レベルは0.05×(電源電圧レベル−接地電圧レベル)から0.20×(電源電圧レベル−接地電圧レベル)の間の任意の電圧レベルであることを特徴とする付記1記載の半導体装置。

(付記8)

前記入力信号の電圧変化に応じて前記出力信号が接地電圧レベルから電源電圧レベルへ変化する場合には、前記第1の電圧レベルを前記接地電圧レベルとし、前記第2の電圧レベルを前記電源電圧レベルとし、前記第3の電圧レベルを前記電源電圧レベルの近傍の電圧レベルとして動作するとともに、

前記入力信号の電圧変化に応じて前記出力信号が前記電源電圧レベルから前記接地電圧レベルへ変化する場合には、前記第1の電圧レベルを前記電源電圧レベルとし、前記第2の電圧レベルを前記接地電圧レベルとし、前記第3の電圧レベルを前記接地電圧レベルの近傍の電圧レベルとして動作することを特徴とする付記1記載の半導体装置。

(付記9)

入力信号の電圧に応じた出力信号を出力信号線に出力する駆動回路と、

ソースに第1の電圧レベルの電圧が供給され、ドレインが前記出力信号線に接続された第1のトランジスタと、

ソースに第2の電圧レベルの電圧が供給され、ドレインが前記出力信号線に接続された第2のトランジスタと、

前記入力信号の電圧変化に応じて前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルへ変化する場合に、前記出力信号の電圧レベルが前記第1の電圧レベルと前記第2の電圧レベルとの間に設定された第3の電圧レベルに達するまでは前記第1のトランジスタをオフ状態とするとともに前記第2のトランジスタをオン状態とし、前記出力信号の電圧レベルが前記第3の電圧レベルに達した後に前記第1のトランジスタをオン状態とするとともに前記第2のトランジスタをオフ状態とする制御部とを備えることを特徴とする半導体装置。

(付記10)

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルに変化した後に、前記第1のトランジスタ及び前記第2のトランジスタをともにオフ状態とすることを特徴とする付記9記載の半導体装置。

(付記11)

前記入力信号の電圧変化を検出し、検出結果に応じた第1の制御信号を前記制御部に出力する第1の検出部と、

前記出力信号の電圧レベルが前記第3の電圧レベルを超えているか否かを検出し、検出結果に応じた第2の制御信号を前記制御部に出力する第2の検出部とを備え、

前記制御部は、前記第1の制御信号及び前記第2の制御信号に基づいて、前記第1のトランジスタ及び前記第2のトランジスタを制御することを特徴とする付記9記載の半導体装置。

(付記12)

前記第1の検出部は、前記第1の制御信号を、前記入力信号の電圧変化の検出時にアサートして前記出力信号が前記第2の電圧レベルに変化した後にネゲートし、

前記第2の検出部は、前記第2の制御信号を、前記出力信号の電圧レベルが前記第3の電圧レベルを境界として前記第2の電圧レベル側である場合にはアサートして前記第1の電圧レベル側である場合にはネゲートし、

前記制御部は、前記第1の制御信号がアサートされ、かつ前記第2の制御信号がネゲートされている期間は、前記第1のトランジスタをオフ状態とするとともに前記第2のトランジスタをオン状態とし、前記第1の制御信号がアサートされ、かつ前記第2の制御信号がアサートされている期間は、前記第1のトランジスタをオン状態とするとともに前記第2のトランジスタをオフ状態とすることを特徴とする付記9記載の半導体装置。

(付記13)

前記入力信号の電圧変化に応じて前記出力信号が接地電圧レベルから電源電圧レベルへ変化する場合には、前記第1の電圧レベルを前記接地電圧レベルとし、前記第2の電圧レベルを前記電源電圧レベルとし、前記第3の電圧レベルを前記電源電圧レベルの近傍の電圧レベルとして動作するとともに、

前記入力信号の電圧変化に応じて前記出力信号が前記電源電圧レベルから前記接地電圧レベルへ変化する場合には、前記第1の電圧レベルを前記電源電圧レベルとし、前記第2の電圧レベルを前記接地電圧レベルとし、前記第3の電圧レベルを前記接地電圧レベルの近傍の電圧レベルとして動作することを特徴とする付記9記載の半導体装置。

【符号の説明】

【0060】

11 主ドライバ

12 補助ドライバ

13 第1の検出部(立上り/立下り検出)

14 第2の検出部(電圧レベル検出)

15 制御部

【特許請求の範囲】

【請求項1】

入力信号の電圧に応じた出力信号を出力信号線に出力する第1の駆動回路と、

前記出力信号線に出力端が接続された第2の駆動回路と、

前記第2の駆動回路を制御する制御部とを備え、

前記制御部は、前記入力信号の電圧変化に応じて前記出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、前記出力信号の電圧レベルが前記第1の電圧レベルと前記第2の電圧レベルとの間に設定された第3の電圧レベルに達するまでは前記第1の電圧レベルから前記第2の電圧レベルへの前記出力信号の変化を補助し、前記出力信号の電圧レベルが前記第3の電圧レベルに達した後に前記第1の電圧レベルから前記第2の電圧レベルへの前記出力信号の変化を抑制するよう前記第2の駆動回路を制御することを特徴とする半導体装置。

【請求項2】

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルへ変化するときに、前記出力信号の電圧レベルが前記第3の電圧レベルに達するまでは前記第2の電圧レベルの側に変化させる電圧を前記第2の駆動回路により前記出力信号線に供給させ、前記出力信号の電圧レベルが前記第3の電圧レベルに達してから前記第2の電圧レベルになるまでの期間に前記第1の電圧レベルの側に変化させる電圧を前記第2の駆動回路により前記出力信号線に供給させることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記入力信号の電圧変化を検出する第1の検出部と、

前記出力信号の電圧レベルが前記第3の電圧レベルに達したか否かを検出する第2の検出部とを備え、

前記制御部は、前記第1の検出部及び前記第2の検出部での検出結果に基づいて前記第2の駆動回路を制御することを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルに変化した後に、前記第2の駆動回路の動作を止めることを特徴とする請求項1〜3の何れか1項に記載の半導体装置。

【請求項5】

前記第3の電圧レベルは、前記第2の電圧レベルに到達直前の電圧レベルであることを特徴とする請求項1〜4の何れか1項に記載の半導体装置。

【請求項6】

前記入力信号の電圧変化に応じて前記出力信号が接地電圧レベルから電源電圧レベルへ変化する場合には、前記第1の電圧レベルを前記接地電圧レベルとし、前記第2の電圧レベルを前記電源電圧レベルとし、前記第3の電圧レベルを前記電源電圧レベルの近傍の電圧レベルとして動作するとともに、

前記入力信号の電圧変化に応じて前記出力信号が前記電源電圧レベルから前記接地電圧レベルへ変化する場合には、前記第1の電圧レベルを前記電源電圧レベルとし、前記第2の電圧レベルを前記接地電圧レベルとし、前記第3の電圧レベルを前記接地電圧レベルの近傍の電圧レベルとして動作することを特徴とする請求項1〜5の何れか1項に記載の半導体装置。

【請求項7】

入力信号の電圧に応じた出力信号を出力信号線に出力する駆動回路と、

ソースに第1の電圧レベルの電圧が供給され、ドレインが前記出力信号線に接続された第1のトランジスタと、

ソースに第2の電圧レベルの電圧が供給され、ドレインが前記出力信号線に接続された第2のトランジスタと、

前記入力信号の電圧変化に応じて前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルへ変化する場合に、前記出力信号の電圧レベルが前記第1の電圧レベルと前記第2の電圧レベルとの間に設定された第3の電圧レベルに達するまでは前記第1のトランジスタをオフ状態とするとともに前記第2のトランジスタをオン状態とし、前記出力信号の電圧レベルが前記第3の電圧レベルに達した後に前記第1のトランジスタをオン状態とするとともに前記第2のトランジスタをオフ状態とする制御部とを備えることを特徴とする半導体装置。

【請求項8】

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルに変化した後に、前記第1のトランジスタ及び前記第2のトランジスタをともにオフ状態とすることを特徴とする請求項7記載の半導体装置。

【請求項9】

前記入力信号の電圧変化を検出し、検出結果に応じた第1の制御信号を前記制御部に出力する第1の検出部と、

前記出力信号の電圧レベルが前記第3の電圧レベルを超えているか否かを検出し、検出結果に応じた第2の制御信号を前記制御部に出力する第2の検出部とを備え、

前記制御部は、前記第1の制御信号及び前記第2の制御信号に基づいて、前記第1のトランジスタ及び前記第2のトランジスタを制御することを特徴とする請求項7又は8記載の半導体装置。

【請求項10】

前記第1の検出部は、前記第1の制御信号を、前記入力信号の電圧変化の検出時にアサートして前記出力信号が前記第2の電圧レベルに変化した後にネゲートし、

前記第2の検出部は、前記第2の制御信号を、前記出力信号の電圧レベルが前記第3の電圧レベルを境界として前記第2の電圧レベル側である場合にはアサートして前記第1の電圧レベル側である場合にはネゲートし、

前記制御部は、前記第1の制御信号がアサートされ、かつ前記第2の制御信号がネゲートされている期間は、前記第1のトランジスタをオフ状態とするとともに前記第2のトランジスタをオン状態とし、前記第1の制御信号がアサートされ、かつ前記第2の制御信号がアサートされている期間は、前記第1のトランジスタをオン状態とするとともに前記第2のトランジスタをオフ状態とすることを特徴とする請求項9記載の半導体装置。

【請求項1】

入力信号の電圧に応じた出力信号を出力信号線に出力する第1の駆動回路と、

前記出力信号線に出力端が接続された第2の駆動回路と、

前記第2の駆動回路を制御する制御部とを備え、

前記制御部は、前記入力信号の電圧変化に応じて前記出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、前記出力信号の電圧レベルが前記第1の電圧レベルと前記第2の電圧レベルとの間に設定された第3の電圧レベルに達するまでは前記第1の電圧レベルから前記第2の電圧レベルへの前記出力信号の変化を補助し、前記出力信号の電圧レベルが前記第3の電圧レベルに達した後に前記第1の電圧レベルから前記第2の電圧レベルへの前記出力信号の変化を抑制するよう前記第2の駆動回路を制御することを特徴とする半導体装置。

【請求項2】

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルへ変化するときに、前記出力信号の電圧レベルが前記第3の電圧レベルに達するまでは前記第2の電圧レベルの側に変化させる電圧を前記第2の駆動回路により前記出力信号線に供給させ、前記出力信号の電圧レベルが前記第3の電圧レベルに達してから前記第2の電圧レベルになるまでの期間に前記第1の電圧レベルの側に変化させる電圧を前記第2の駆動回路により前記出力信号線に供給させることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記入力信号の電圧変化を検出する第1の検出部と、

前記出力信号の電圧レベルが前記第3の電圧レベルに達したか否かを検出する第2の検出部とを備え、

前記制御部は、前記第1の検出部及び前記第2の検出部での検出結果に基づいて前記第2の駆動回路を制御することを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルに変化した後に、前記第2の駆動回路の動作を止めることを特徴とする請求項1〜3の何れか1項に記載の半導体装置。

【請求項5】

前記第3の電圧レベルは、前記第2の電圧レベルに到達直前の電圧レベルであることを特徴とする請求項1〜4の何れか1項に記載の半導体装置。

【請求項6】

前記入力信号の電圧変化に応じて前記出力信号が接地電圧レベルから電源電圧レベルへ変化する場合には、前記第1の電圧レベルを前記接地電圧レベルとし、前記第2の電圧レベルを前記電源電圧レベルとし、前記第3の電圧レベルを前記電源電圧レベルの近傍の電圧レベルとして動作するとともに、

前記入力信号の電圧変化に応じて前記出力信号が前記電源電圧レベルから前記接地電圧レベルへ変化する場合には、前記第1の電圧レベルを前記電源電圧レベルとし、前記第2の電圧レベルを前記接地電圧レベルとし、前記第3の電圧レベルを前記接地電圧レベルの近傍の電圧レベルとして動作することを特徴とする請求項1〜5の何れか1項に記載の半導体装置。

【請求項7】

入力信号の電圧に応じた出力信号を出力信号線に出力する駆動回路と、

ソースに第1の電圧レベルの電圧が供給され、ドレインが前記出力信号線に接続された第1のトランジスタと、

ソースに第2の電圧レベルの電圧が供給され、ドレインが前記出力信号線に接続された第2のトランジスタと、

前記入力信号の電圧変化に応じて前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルへ変化する場合に、前記出力信号の電圧レベルが前記第1の電圧レベルと前記第2の電圧レベルとの間に設定された第3の電圧レベルに達するまでは前記第1のトランジスタをオフ状態とするとともに前記第2のトランジスタをオン状態とし、前記出力信号の電圧レベルが前記第3の電圧レベルに達した後に前記第1のトランジスタをオン状態とするとともに前記第2のトランジスタをオフ状態とする制御部とを備えることを特徴とする半導体装置。

【請求項8】

前記制御部は、前記出力信号が前記第1の電圧レベルから前記第2の電圧レベルに変化した後に、前記第1のトランジスタ及び前記第2のトランジスタをともにオフ状態とすることを特徴とする請求項7記載の半導体装置。

【請求項9】

前記入力信号の電圧変化を検出し、検出結果に応じた第1の制御信号を前記制御部に出力する第1の検出部と、

前記出力信号の電圧レベルが前記第3の電圧レベルを超えているか否かを検出し、検出結果に応じた第2の制御信号を前記制御部に出力する第2の検出部とを備え、

前記制御部は、前記第1の制御信号及び前記第2の制御信号に基づいて、前記第1のトランジスタ及び前記第2のトランジスタを制御することを特徴とする請求項7又は8記載の半導体装置。

【請求項10】

前記第1の検出部は、前記第1の制御信号を、前記入力信号の電圧変化の検出時にアサートして前記出力信号が前記第2の電圧レベルに変化した後にネゲートし、

前記第2の検出部は、前記第2の制御信号を、前記出力信号の電圧レベルが前記第3の電圧レベルを境界として前記第2の電圧レベル側である場合にはアサートして前記第1の電圧レベル側である場合にはネゲートし、

前記制御部は、前記第1の制御信号がアサートされ、かつ前記第2の制御信号がネゲートされている期間は、前記第1のトランジスタをオフ状態とするとともに前記第2のトランジスタをオン状態とし、前記第1の制御信号がアサートされ、かつ前記第2の制御信号がアサートされている期間は、前記第1のトランジスタをオン状態とするとともに前記第2のトランジスタをオフ状態とすることを特徴とする請求項9記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−42222(P2013−42222A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2011−176140(P2011−176140)

【出願日】平成23年8月11日(2011.8.11)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成23年8月11日(2011.8.11)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]