半導体装置

【課題】セキュリティ情報を格納した領域への物理的な破壊攻撃を、従来よりも簡単な手法で検知する。

【解決手段】半導体装置1において、第1の機能モジュール3は、正常に動作しているか否かのテスト対象となる。第2の機能モジュール2は、第1の機能モジュール3にテストデータを出力し、テストデータに応じて第1の機能モジュールから出力された出力信号が正常なデータパターンと一致するか否かを判定する。第3の機能モジュール7は、耐タンパ性を必要とする。シールド配線SLは、基板に対して垂直方向から見たときに第3の機能モジュール7が設けられた領域を覆うように設けられ、その両端部は第1の機能モジュール3と接続される。シールド配線SLが断線しているとき、上記の出力信号は正常なデータパターンと一致しなくなる。

【解決手段】半導体装置1において、第1の機能モジュール3は、正常に動作しているか否かのテスト対象となる。第2の機能モジュール2は、第1の機能モジュール3にテストデータを出力し、テストデータに応じて第1の機能モジュールから出力された出力信号が正常なデータパターンと一致するか否かを判定する。第3の機能モジュール7は、耐タンパ性を必要とする。シールド配線SLは、基板に対して垂直方向から見たときに第3の機能モジュール7が設けられた領域を覆うように設けられ、その両端部は第1の機能モジュール3と接続される。シールド配線SLが断線しているとき、上記の出力信号は正常なデータパターンと一致しなくなる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、基板上に形成された集積回路を含む半導体装置に関し、特に外部からの物理的手段による不正侵入を検知する機構を備えた半導体装置に関する。

【背景技術】

【0002】

機密データを処理したり保存したりする機能モジュールは、容易に外部から解析できないよう、防御策を講じる必要がある。非正規な手段による機密データの読み取りを防ぐ能力を耐タンパ性(tamper resistant)という。物理的に耐タンパ性を高める手段として、たとえば、パッシブシールドとアクティブシールドとが知られている。

【0003】

パッシブシールドとは、半導体チップの最上層近くの金属配線層を用いて形成された金属薄膜であり、パッシブシールドよりも下層に設けられた回路の配線を外部から観察できないようにしたものである。しかしながら、FIB(集束イオンビーム:Focused Ion Beam)やレーザ光などの物理的手段によってパッシブシールドを貫通する穴を形成すれば、プローブ針やEB(電子ビーム:Electron Beam)テスタなどによって容易に情報が読み取られてしまう。

【0004】

これに対して、アクティブシールドは、半導体チップ全体を覆うように複雑に張り巡らされている配線パターンと、その配線が何らかの手段によって切断されたとき、その断線を検知するセンサとで構成される。センサは配線パターンの電位や容量などを検出する。

【0005】

特開2006−293921号公報(特許文献1)は、POP(Package On Package)構造の半導体装置に対してアクティブシールドによって耐タンパ性を高める手段を開示する。具体的に、この文献の半導体装置は、セキュリティチップと、積層された複数のパッケージの上に取り付けられたセキュリティカバーと、セキュリティ信号伝播用のデータ保護配線とを備えている。セキュリティチップでは、データ保護配線に信号を送信し、データ保護配線を経由して戻ってきた信号をもとの信号と比較する。そして、その比較結果に基づいて、複数のパッケージ内の素子を停止させる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−293921号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記のようにアクティブシールドは、耐タンパ性が必要な半導体チップに対する物理的な破壊攻撃をある程度有効に防御することができる。しかしながら、センサを含めたアクティブシールドの設計に手間がかかるという問題がある。

【0008】

この発明の目的は、物理的な破壊攻撃を従来よりも簡単な手法で検知することによって耐タンパ性を高めた半導体装置を提供することである。

【課題を解決するための手段】

【0009】

この発明による半導体装置は、オンチップのテスト回路を有し、当該テスト回路による被テスト回路の信号経路の一部としてシールド配線を含むものである。

【発明の効果】

【0010】

上記の実施の形態によれば、半導体装置に備えられたテスト機能を用いてシールド配線の断線が検知されるので、物理的な破壊攻撃を従来よりも簡単な手法で検知することができる。

【図面の簡単な説明】

【0011】

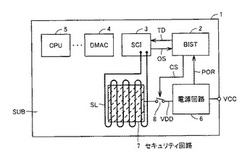

【図1】この発明の実施の一形態による半導体装置1の構成を示す機能ブロック図である。

【図2】被テスト回路3にスキャンテスト回路が付加された場合の構成を模式的に示すブロック図である。

【図3】図1のシールド配線SLの構造の一例を模式的に示す平面図である。

【図4】図3のシールド配線SLをY方向から見た側面断面図である。

【図5】シールド配線SLの他の配置例を模式的に示す側面断面図である。

【図6】シールド配線SLのさらに他の配置例を模式的に示す側面断面図である。

【発明を実施するための形態】

【0012】

この発明の実施の一形態による半導体装置は、基板と、この基板上に設けられた第1〜第3の機能モジュールと、1または複数のシールド配線とを備える。第1の機能モジュールは、正常に動作しているか否かのテスト対象となる。第2の機能モジュールは、第1の機能モジュールにテストデータを出力し、テストデータに応じて第1の機能モジュールから出力された出力信号が正常なデータパターンと一致するか否かを判定する。第3の機能モジュールは、耐タンパ性を必要とする。1または複数のシールド配線は、基板に対して垂直方向から見たときに第3の機能モジュールが設けられた領域を覆うように、第3の機能モジュールの上方および第3の機能モジュールと反対側の基板面のうち少なくとも一方に設けられる。1または複数のシールド配線の各々の両端部は、第1の機能モジュールと接続される。1または複数のシールド配線の少なくとも1つが断線しているとき、上記の出力信号は正常なデータパターンと一致しなくなる。

【0013】

以下、この発明の実施の形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰返さない。

【0014】

[半導体装置の構成]

図1は、この発明の実施の一形態による半導体装置1の構成を示す機能ブロック図である。図1の半導体装置1は、セルフテスト機能を有するマイクロコンピュータチップである。

【0015】

図1を参照して、半導体装置1は、シリコンなどの半導体の基板SUB上に形成された複数の機能モジュールを含む。図1には、複数の機能モジュールとして、BIST(Built-In Self Test)2、SCI(Serial Communication Interface)3、DMAC(Direct Memory Access Controller)4、CPU(Central Processing Unit)5、電源回路6、およびセキュリティ回路7などが示されている。ここで、セキュリティ回路7は、機密データを処理したり保存したりする機能モジュールであり、耐タンパ性を必要とする。セキュリティ回路7を覆うようにシールド配線SL(いわゆる「ラーメン配線」)が設けられている。

【0016】

電源回路6は、外部電源電圧VCCに基づいて内部電源電圧VDDを生成し、生成した内部電源電圧VDDを各機能モジュールに供給する。図1では、図解を容易にするために、セキュリティ回路7に至る内部電源電圧VDDの供給経路のみが代表的に示されている。なお、セキュリティ回路7に至る内部電源電圧VDDの供給経路上には、電源スイッチ8が設けられている。電源スイッチ8は、BIST2から出力された制御信号CSに応答してオンまたはオフに切替わる。

【0017】

電源回路6は、さらに、パワーオンリセット信号PORを生成して各機能モジュールに出力する。電源回路6は、外部電源電圧VCCの立上がり時に、外部電源電圧VCCの大きさが所定の基準電圧を超えたときにパワーオンリセット信号PORを活性状態に切替える。各機能モジュールは、パワーオンリセット信号PORが活性状態に切替わったとき、所定の初期化動作を行なう。なお、図1では、図解を容易にするために、電源回路6からBIST2に至るパワーオンリセット信号PORの経路のみが代表的に示されている。

【0018】

BIST2は、機能モジュールが正常に動作するか否かをテストするための回路である。具体的に、BIST2は、テスト対象の機能モジュール(「被テスト回路」とも称する)にテストデータTDを入力し、テストデータTDに応じて被テスト回路から出力された出力信号OSが正常なデータパターンと一致するか否かを判定する。図1では、一例として被テスト回路がSCI3である場合が示されている(以下、「SCI3」に代えて「被テスト回路3」とも記載する)。この実施の形態のBIST2は、パワーオンリセット信号PORが活性状態に切替わったときにテストを実行する。

【0019】

シールド配線SLは、基板SUBに対して垂直方向から見たときにセキュリティ回路7の設けられている領域全体を覆うように、セキュリティ回路7用の信号配線が形成された金属配線層よりも上層の金属配線層を用いて形成される。シールド配線SLの形状は、たとえば、図1に示したミアンダ(meander)形状や、スパイラル形状などに加工されている。

【0020】

シールド配線SLの両端部は、被テスト回路3のテストを実行するときにシールド配線SLの断線も検出できるように、被テスト回路3と接続されている。具体的な被テスト回路3の設計方法として以下のような方法を採用することができる。

【0021】

第1の方法は、スキャンテストやバウンダリ・スキャンなどのテスト容易化設計手法を、被テスト回路3の設計に適用するものである。この場合、被テスト回路3にテスト容易化のための新たな回路要素を付加するのに併せて、シールド配線SLに接続された回路要素も付加する。これによって、スキャンテストやバウンダリ・スキャンなどを実行するときに、シールド配線SLの断線も併せて検出できるようにする。

【0022】

第2の方法は、被テスト回路3の内部配線の一部をシールド配線SLに置換するものである。言い換えると、被テスト回路3の内部配線の一部がセキュリティ回路7の上部にまで引き伸ばされたような形状となるように被テスト回路3を設計する。この場合、被テスト回路3のテスト時にはシールド配線SLの断線故障の検出率がほぼ100%になるようにするとともに、被テスト回路3の通常動作時に被テスト回路3の動作に影響を及ぼさないようにする必要がある。このようなテスト時の故障検出率と通常時の回路動作との両方の条件を満足するようにシールド配線SLの接続箇所が決定される。

【0023】

上記の方法で設計された被テスト回路3にテストを行なった結果、出力信号OSが正常なデータパターンに一致しないことが検知された場合には、セキュリティ回路7にアクセス出来ないようにする。セキュリティ回路7へのアクセス遮断の例を以下に記す。上記のデータパターンの不一致を検知した場合には、BIST2は、制御信号CSによって電源スイッチ8をオフ状態にする。この結果、セキュリティ回路7への内部電源電圧VDDの供給が停止するので、セキュリティ回路7の動作が停止することになる。これによって、セキュリティ回路7から機密データが不正な手段で読み出されるのを防止することができる。内部電源電圧VDDの供給を停止するのに代えて、セキュリティ回路7へのクロック信号の入力を停止することによって、セキュリティ回路7の動作を停止させてもよい。

【0024】

なお、図1において、シールド配線SLは、セキュリティ回路7が形成された基板面側(以下、「主面側」もしくは「回路面側」とも称する)に形成されているが、セキュリティ回路7と反対側の基板裏面側に形成してもよい。シールド配線SLを基板裏面側に形成する場合には、基板SUBを貫通するコンタクトホールを介してシールド配線SLの両端部と被テスト回路3とが接続される。

【0025】

シールド配線SLは、必ずしも半導体装置1の最上層の金属配線層を用いて形成する必要はない。たとえば、セキュリティ回路7の内部動作と直接関係のない電源配線や接地配線は、シールド配線SLよりも上方に設けられていてもよい。

【0026】

シールド配線SLの本数は1本には限られない。基板主面側に複数のシールド配線SLを立体的に交差するように配線してもよいし、基板主面側と裏面側の両方にシールド配線を設けてもよい。

【0027】

[スキャンテストによるシールド配線の断線検出]

以下、被テスト回路3にスキャンテストを行なうための回路を付加する場合において、シールド配線SLの接続部分の設計方法と、シールド配線SLの断線を検出する方法について説明する。

【0028】

図2は、被テスト回路3にスキャンテスト回路が付加された場合の構成を模式的に示すブロック図である。図2を参照して、被テスト回路3は、スキャンフリップフロップ11〜16と(図2では、代表的に6個のスキャンフリップフロップのみが示されている)、組合せ論理回路17,18とを含む。

【0029】

(スキャンチェーンの構成)

スキャンテストでは、被テスト回路3内の通常のフリップフロップが、スキャンフリップフロップに置換される。図2の場合、スキャンフリップフロップ13,14は、通常のフリップフロップを置換したものである。図2の場合には、さらに、シールド配線SL1,SL2の断線を検出するために、シールド配線SL1,SL2に接続されたスキャンフリップフロップ11,12,15,16が付加されている。

【0030】

各スキャンフリップフロップは、通常のフリップフロップが有するデータ入力端子D、出力端子Qおよびクロック端子CKの他に、スキャン入力端子SI、スキャン出力端子SO、およびスキャンイネーブル端子SEを含む。スキャンイネーブル端子SEに入力された信号(以下、「スキャンイネーブル信号」と称する)が“0”のとき、各スキャンフリップフロップは、クロックの立上がりまたは立下がりエッジに同期してデータ入力端子Dに入力された信号を取込んで保持する通常のフリップフロップの動作を行なう。スキャンイネーブル信号が“1”のとき、各スキャンフリップフロップは、クロック信号の立上がりエッジに同期してスキャン入力端子SIに入力された信号を取込んで保持する。なお、出力端子Qとスキャン出力端子SOはスキャンフリップフロップの内部で接続されている。

【0031】

被テスト回路3内に設けられたスキャンフリップフロップ11〜16は、スキャン入力端子SIとスキャン出力端子SOとが相互に接続されることによって、シフトレジスタ(「スキャンチェーン」と称する)20を構成する。このシフトレジスタ20を用いてスキャンテストが実行される。

【0032】

具体的に被テスト回路3のスキャンテストを行なう場合には、まず、第1ステップで、図1のBIST2は、スキャンイネーブル信号を“1”に設定して、スキャンチェーンの入力端子21にテストデータを入力することによってシフトレジスタ20に初期値を設定する。

【0033】

次の第2ステップで、BIST2は、スキャンイネーブル信号を“0”に設定して、被テスト回路3を1クロック動作させる。このとき、BIST2は、被テスト回路3の入力端子23〜25からテストパターンを入力し、出力端子26〜28から出力される信号を検出することによって、組合せ論理回路17,18のテストを行なう。

【0034】

次の第3ステップで、BIST2は、スキャンイネーブル信号を“1”に設定して、スキャンチェーンの出力端子22からテスト結果を受取る。以上の第1〜第3ステップを繰り返すことによって、組合せ論理回路17,18の全テストパターンでのテストが完了する。

【0035】

(シールド配線の接続と断線検出)

次に、シールド配線の接続箇所とその断線検出方法について説明する。図2では、被テスト回路3に2本のシールド配線SL1,SL2が接続されている。具体的に、第1のシールド配線SL1は、その一端がスキャンフリップフロップ11の出力端子Qに接続され、他端がスキャンフリップフロップ12のデータ入力端子Dに接続される。第2のシールド配線SL2は、その一端がスキャンフリップフロップ15の出力端子Qに接続され、他端がスキャンフリップフロップ16のデータ入力端子Dに接続される。

【0036】

シールド配線SL1,SL2が断線していない場合には、上記の第2のステップで1クロック動作させたとき、スキャンフリップフロップ12の記憶データがスキャンフリップフロップ11の記憶データに置換わり、スキャンフリップフロップ16の記憶データがスキャンフリップフロップ15の記憶データに置換わる。これに対して、シールド配線SL1,SL2が断線している場合には、上記の第2ステップで1クロック動作させても、スキャンフリップフロップ12,16の記憶データが置換されなくなる。この結果、図1のBIST2は、前述の第3ステップで、スキャンフリップフロップ11〜16から出力されたデータが、正常な場合に期待されるパターンデータに一致するか否かを判定することよって、シールド配線L1,L2の断線を検知することができる。

【0037】

(変形例−バウンダリ・スキャンテストによる場合)

被テスト回路3のテスト方法として、上記のスキャンテストに代えてバウンダリ・スキャンテストを用いてもよい。バウンダリ・スキャンテストでは、被テスト回路のI/Oバッファ(入出力バッファ)が、バウンダリ・スキャンセルに置き換えられる。バウンダリ・スキャンセルは、通常のI/Oバッファの機能に加えてシフトレジスタの機能を有し、これらの機能は制御信号によって切替えることができる。

【0038】

シールド配線SL1,SL2の断線を検出するためには、図2の場合と同様に、チェーン状に接続されたバウンダリ・スキャンセルと直列にスキャンフリップフロップ11,12,15,16を接続する。これらのスキャンフリップフロップ11,12,15,16の出力端子およびデータ入力端子には、シールド配線SL1,SL2が接続される。これによって、バウンダリ・スキャンテストを行なう際にシールド配線SL1,SL2の断線検出も併せて行なうことができる。

【0039】

[シールド配線の構成の詳細]

図3は、図1のシールド配線SLの構造の一例を模式的に示す平面図である。図3では、基板SUB上に形成された、シールド配線SL、被テスト回路3、およびセキュリティ回路7とが示されている。これらの構成要素には、図解を容易にするためにハッチングを付している。

【0040】

図4は、図3のシールド配線SLをY方向から見た側面断面図である。図4において、図3と対応する要素には同一のハッチングを付している。

【0041】

図3、図4を参照して、被テスト回路3およびセキュリティ回路7の各々は、基板上に形成された複数のMOS(Metal Oxide Semiconductor)トランジスタ、およびこれらのMOSトランジスタを接続するための複数の金属配線層などによって構成される。シールド配線SLは、これらの被テスト回路3およびセキュリティ回路7で用いられる金属配線層よりもさらに上層の金属配線層Ma,Mbを用いて形成される。

【0042】

具体的に、最上層の金属配線層Mbに形成された配線32の第1端部32AがコンタクトホールCHを介して被テスト回路3と接続され、それより下層の金属配線層Maに形成された配線35の第1端部35AがコンタクトホールCHを介して被テスト回路3と接続される。配線35の第2端部35Bは、コンタクトホールを介して上層の金属配線層Mbに形成された配線31の第1端部31Aと接続される。セキュリティ回路7の上方には、金属配線層Mbを用いて複数の配線36が形成されている。これらの複数の配線36ならびに前述の配線31および32が、下層の金属配線層Maに形成された複数の配線33,34とコンタクトホールCHを介して接続されることによって、ミアンダ状のシールド配線SLが構成される。

【0043】

図5は、シールド配線SLの他の配置例を模式的に示す側面断面図である。図5において、図4の場合と同一または相当する部分には同一の参照符号を付して説明を繰り返さない。

【0044】

図5に示す例では、シールド配線SLは、基板SUBの裏面側(機能モジュール3,7の形成面と反対側)に形成される。ミアンダ状のシールド配線SLの端部51,52は、それぞれ基板SUBを貫通するコンタクトホールSCHを介して被テスト回路3と接続される。

【0045】

フリップチップ構造の場合には、シールド配線SLを基板裏面側に配置するのが望ましい。図5に示すように、フリップチップ構造では、半導体チップの回路面側に形成された絶縁層40Aの表面に突起状の端子(バンプ)41が多数形成される。半導体チップをパッケージに実装する際には、半導体チップを上下逆さにし、これらの突起状の端子41とパッケージ基板とを半田接続する。このような構成では、基板SUBの裏面側からの物理的手段による攻撃を防御する必要があるので、基板SUBの裏面側にシールド配線SLが形成されている。

【0046】

図6は、シールド配線SLのさらに他の配置例を模式的に示す側面断面図である。図6において、図4、図5の場合と同一または相当する部分には同一の参照符号を付して説明を繰り返さない。

【0047】

図6では、基板SUBの両面にシールド配線SL1,SL2が形成された例が示されている。回路面側に形成されたシールド配線SL1の構成は、図4の場合と同一であり、基板裏面側に形成されたシールド配線SL2の構成は、図5の場合と同一である。図6の場合、基板裏面側に設けられたシールド配線SL2を覆うように絶縁層40Bが形成され、絶縁層40Bの表面にパッケージ基板と接続するための突起状の端子(バンプ)41が形成される。

【0048】

今回開示された実施の形態はすべての点で例示であって制限的なものでないと考えられるべきである。この発明の範囲は上記した説明ではなくて請求の範囲によって示され、請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0049】

1 半導体装置、2 BIST(第2の機能モジュール)、3 被テスト回路(第1の機能モジュール)、6 電源回路、7 セキュリティ回路(第3の機能モジュール)、8 電源スイッチ、11〜16 スキャンフリップフロップ、20 シフトレジスタ(スキャンチェーン)、21 スキャンチェーンの入力端子、22 スキャンチェーンの出力端子、OS 出力信号、POR パワーオンリセット信号、SL,SL1,SL2 シールド配線、SUB 基板、TD テストデータ。

【技術分野】

【0001】

この発明は、基板上に形成された集積回路を含む半導体装置に関し、特に外部からの物理的手段による不正侵入を検知する機構を備えた半導体装置に関する。

【背景技術】

【0002】

機密データを処理したり保存したりする機能モジュールは、容易に外部から解析できないよう、防御策を講じる必要がある。非正規な手段による機密データの読み取りを防ぐ能力を耐タンパ性(tamper resistant)という。物理的に耐タンパ性を高める手段として、たとえば、パッシブシールドとアクティブシールドとが知られている。

【0003】

パッシブシールドとは、半導体チップの最上層近くの金属配線層を用いて形成された金属薄膜であり、パッシブシールドよりも下層に設けられた回路の配線を外部から観察できないようにしたものである。しかしながら、FIB(集束イオンビーム:Focused Ion Beam)やレーザ光などの物理的手段によってパッシブシールドを貫通する穴を形成すれば、プローブ針やEB(電子ビーム:Electron Beam)テスタなどによって容易に情報が読み取られてしまう。

【0004】

これに対して、アクティブシールドは、半導体チップ全体を覆うように複雑に張り巡らされている配線パターンと、その配線が何らかの手段によって切断されたとき、その断線を検知するセンサとで構成される。センサは配線パターンの電位や容量などを検出する。

【0005】

特開2006−293921号公報(特許文献1)は、POP(Package On Package)構造の半導体装置に対してアクティブシールドによって耐タンパ性を高める手段を開示する。具体的に、この文献の半導体装置は、セキュリティチップと、積層された複数のパッケージの上に取り付けられたセキュリティカバーと、セキュリティ信号伝播用のデータ保護配線とを備えている。セキュリティチップでは、データ保護配線に信号を送信し、データ保護配線を経由して戻ってきた信号をもとの信号と比較する。そして、その比較結果に基づいて、複数のパッケージ内の素子を停止させる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−293921号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記のようにアクティブシールドは、耐タンパ性が必要な半導体チップに対する物理的な破壊攻撃をある程度有効に防御することができる。しかしながら、センサを含めたアクティブシールドの設計に手間がかかるという問題がある。

【0008】

この発明の目的は、物理的な破壊攻撃を従来よりも簡単な手法で検知することによって耐タンパ性を高めた半導体装置を提供することである。

【課題を解決するための手段】

【0009】

この発明による半導体装置は、オンチップのテスト回路を有し、当該テスト回路による被テスト回路の信号経路の一部としてシールド配線を含むものである。

【発明の効果】

【0010】

上記の実施の形態によれば、半導体装置に備えられたテスト機能を用いてシールド配線の断線が検知されるので、物理的な破壊攻撃を従来よりも簡単な手法で検知することができる。

【図面の簡単な説明】

【0011】

【図1】この発明の実施の一形態による半導体装置1の構成を示す機能ブロック図である。

【図2】被テスト回路3にスキャンテスト回路が付加された場合の構成を模式的に示すブロック図である。

【図3】図1のシールド配線SLの構造の一例を模式的に示す平面図である。

【図4】図3のシールド配線SLをY方向から見た側面断面図である。

【図5】シールド配線SLの他の配置例を模式的に示す側面断面図である。

【図6】シールド配線SLのさらに他の配置例を模式的に示す側面断面図である。

【発明を実施するための形態】

【0012】

この発明の実施の一形態による半導体装置は、基板と、この基板上に設けられた第1〜第3の機能モジュールと、1または複数のシールド配線とを備える。第1の機能モジュールは、正常に動作しているか否かのテスト対象となる。第2の機能モジュールは、第1の機能モジュールにテストデータを出力し、テストデータに応じて第1の機能モジュールから出力された出力信号が正常なデータパターンと一致するか否かを判定する。第3の機能モジュールは、耐タンパ性を必要とする。1または複数のシールド配線は、基板に対して垂直方向から見たときに第3の機能モジュールが設けられた領域を覆うように、第3の機能モジュールの上方および第3の機能モジュールと反対側の基板面のうち少なくとも一方に設けられる。1または複数のシールド配線の各々の両端部は、第1の機能モジュールと接続される。1または複数のシールド配線の少なくとも1つが断線しているとき、上記の出力信号は正常なデータパターンと一致しなくなる。

【0013】

以下、この発明の実施の形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰返さない。

【0014】

[半導体装置の構成]

図1は、この発明の実施の一形態による半導体装置1の構成を示す機能ブロック図である。図1の半導体装置1は、セルフテスト機能を有するマイクロコンピュータチップである。

【0015】

図1を参照して、半導体装置1は、シリコンなどの半導体の基板SUB上に形成された複数の機能モジュールを含む。図1には、複数の機能モジュールとして、BIST(Built-In Self Test)2、SCI(Serial Communication Interface)3、DMAC(Direct Memory Access Controller)4、CPU(Central Processing Unit)5、電源回路6、およびセキュリティ回路7などが示されている。ここで、セキュリティ回路7は、機密データを処理したり保存したりする機能モジュールであり、耐タンパ性を必要とする。セキュリティ回路7を覆うようにシールド配線SL(いわゆる「ラーメン配線」)が設けられている。

【0016】

電源回路6は、外部電源電圧VCCに基づいて内部電源電圧VDDを生成し、生成した内部電源電圧VDDを各機能モジュールに供給する。図1では、図解を容易にするために、セキュリティ回路7に至る内部電源電圧VDDの供給経路のみが代表的に示されている。なお、セキュリティ回路7に至る内部電源電圧VDDの供給経路上には、電源スイッチ8が設けられている。電源スイッチ8は、BIST2から出力された制御信号CSに応答してオンまたはオフに切替わる。

【0017】

電源回路6は、さらに、パワーオンリセット信号PORを生成して各機能モジュールに出力する。電源回路6は、外部電源電圧VCCの立上がり時に、外部電源電圧VCCの大きさが所定の基準電圧を超えたときにパワーオンリセット信号PORを活性状態に切替える。各機能モジュールは、パワーオンリセット信号PORが活性状態に切替わったとき、所定の初期化動作を行なう。なお、図1では、図解を容易にするために、電源回路6からBIST2に至るパワーオンリセット信号PORの経路のみが代表的に示されている。

【0018】

BIST2は、機能モジュールが正常に動作するか否かをテストするための回路である。具体的に、BIST2は、テスト対象の機能モジュール(「被テスト回路」とも称する)にテストデータTDを入力し、テストデータTDに応じて被テスト回路から出力された出力信号OSが正常なデータパターンと一致するか否かを判定する。図1では、一例として被テスト回路がSCI3である場合が示されている(以下、「SCI3」に代えて「被テスト回路3」とも記載する)。この実施の形態のBIST2は、パワーオンリセット信号PORが活性状態に切替わったときにテストを実行する。

【0019】

シールド配線SLは、基板SUBに対して垂直方向から見たときにセキュリティ回路7の設けられている領域全体を覆うように、セキュリティ回路7用の信号配線が形成された金属配線層よりも上層の金属配線層を用いて形成される。シールド配線SLの形状は、たとえば、図1に示したミアンダ(meander)形状や、スパイラル形状などに加工されている。

【0020】

シールド配線SLの両端部は、被テスト回路3のテストを実行するときにシールド配線SLの断線も検出できるように、被テスト回路3と接続されている。具体的な被テスト回路3の設計方法として以下のような方法を採用することができる。

【0021】

第1の方法は、スキャンテストやバウンダリ・スキャンなどのテスト容易化設計手法を、被テスト回路3の設計に適用するものである。この場合、被テスト回路3にテスト容易化のための新たな回路要素を付加するのに併せて、シールド配線SLに接続された回路要素も付加する。これによって、スキャンテストやバウンダリ・スキャンなどを実行するときに、シールド配線SLの断線も併せて検出できるようにする。

【0022】

第2の方法は、被テスト回路3の内部配線の一部をシールド配線SLに置換するものである。言い換えると、被テスト回路3の内部配線の一部がセキュリティ回路7の上部にまで引き伸ばされたような形状となるように被テスト回路3を設計する。この場合、被テスト回路3のテスト時にはシールド配線SLの断線故障の検出率がほぼ100%になるようにするとともに、被テスト回路3の通常動作時に被テスト回路3の動作に影響を及ぼさないようにする必要がある。このようなテスト時の故障検出率と通常時の回路動作との両方の条件を満足するようにシールド配線SLの接続箇所が決定される。

【0023】

上記の方法で設計された被テスト回路3にテストを行なった結果、出力信号OSが正常なデータパターンに一致しないことが検知された場合には、セキュリティ回路7にアクセス出来ないようにする。セキュリティ回路7へのアクセス遮断の例を以下に記す。上記のデータパターンの不一致を検知した場合には、BIST2は、制御信号CSによって電源スイッチ8をオフ状態にする。この結果、セキュリティ回路7への内部電源電圧VDDの供給が停止するので、セキュリティ回路7の動作が停止することになる。これによって、セキュリティ回路7から機密データが不正な手段で読み出されるのを防止することができる。内部電源電圧VDDの供給を停止するのに代えて、セキュリティ回路7へのクロック信号の入力を停止することによって、セキュリティ回路7の動作を停止させてもよい。

【0024】

なお、図1において、シールド配線SLは、セキュリティ回路7が形成された基板面側(以下、「主面側」もしくは「回路面側」とも称する)に形成されているが、セキュリティ回路7と反対側の基板裏面側に形成してもよい。シールド配線SLを基板裏面側に形成する場合には、基板SUBを貫通するコンタクトホールを介してシールド配線SLの両端部と被テスト回路3とが接続される。

【0025】

シールド配線SLは、必ずしも半導体装置1の最上層の金属配線層を用いて形成する必要はない。たとえば、セキュリティ回路7の内部動作と直接関係のない電源配線や接地配線は、シールド配線SLよりも上方に設けられていてもよい。

【0026】

シールド配線SLの本数は1本には限られない。基板主面側に複数のシールド配線SLを立体的に交差するように配線してもよいし、基板主面側と裏面側の両方にシールド配線を設けてもよい。

【0027】

[スキャンテストによるシールド配線の断線検出]

以下、被テスト回路3にスキャンテストを行なうための回路を付加する場合において、シールド配線SLの接続部分の設計方法と、シールド配線SLの断線を検出する方法について説明する。

【0028】

図2は、被テスト回路3にスキャンテスト回路が付加された場合の構成を模式的に示すブロック図である。図2を参照して、被テスト回路3は、スキャンフリップフロップ11〜16と(図2では、代表的に6個のスキャンフリップフロップのみが示されている)、組合せ論理回路17,18とを含む。

【0029】

(スキャンチェーンの構成)

スキャンテストでは、被テスト回路3内の通常のフリップフロップが、スキャンフリップフロップに置換される。図2の場合、スキャンフリップフロップ13,14は、通常のフリップフロップを置換したものである。図2の場合には、さらに、シールド配線SL1,SL2の断線を検出するために、シールド配線SL1,SL2に接続されたスキャンフリップフロップ11,12,15,16が付加されている。

【0030】

各スキャンフリップフロップは、通常のフリップフロップが有するデータ入力端子D、出力端子Qおよびクロック端子CKの他に、スキャン入力端子SI、スキャン出力端子SO、およびスキャンイネーブル端子SEを含む。スキャンイネーブル端子SEに入力された信号(以下、「スキャンイネーブル信号」と称する)が“0”のとき、各スキャンフリップフロップは、クロックの立上がりまたは立下がりエッジに同期してデータ入力端子Dに入力された信号を取込んで保持する通常のフリップフロップの動作を行なう。スキャンイネーブル信号が“1”のとき、各スキャンフリップフロップは、クロック信号の立上がりエッジに同期してスキャン入力端子SIに入力された信号を取込んで保持する。なお、出力端子Qとスキャン出力端子SOはスキャンフリップフロップの内部で接続されている。

【0031】

被テスト回路3内に設けられたスキャンフリップフロップ11〜16は、スキャン入力端子SIとスキャン出力端子SOとが相互に接続されることによって、シフトレジスタ(「スキャンチェーン」と称する)20を構成する。このシフトレジスタ20を用いてスキャンテストが実行される。

【0032】

具体的に被テスト回路3のスキャンテストを行なう場合には、まず、第1ステップで、図1のBIST2は、スキャンイネーブル信号を“1”に設定して、スキャンチェーンの入力端子21にテストデータを入力することによってシフトレジスタ20に初期値を設定する。

【0033】

次の第2ステップで、BIST2は、スキャンイネーブル信号を“0”に設定して、被テスト回路3を1クロック動作させる。このとき、BIST2は、被テスト回路3の入力端子23〜25からテストパターンを入力し、出力端子26〜28から出力される信号を検出することによって、組合せ論理回路17,18のテストを行なう。

【0034】

次の第3ステップで、BIST2は、スキャンイネーブル信号を“1”に設定して、スキャンチェーンの出力端子22からテスト結果を受取る。以上の第1〜第3ステップを繰り返すことによって、組合せ論理回路17,18の全テストパターンでのテストが完了する。

【0035】

(シールド配線の接続と断線検出)

次に、シールド配線の接続箇所とその断線検出方法について説明する。図2では、被テスト回路3に2本のシールド配線SL1,SL2が接続されている。具体的に、第1のシールド配線SL1は、その一端がスキャンフリップフロップ11の出力端子Qに接続され、他端がスキャンフリップフロップ12のデータ入力端子Dに接続される。第2のシールド配線SL2は、その一端がスキャンフリップフロップ15の出力端子Qに接続され、他端がスキャンフリップフロップ16のデータ入力端子Dに接続される。

【0036】

シールド配線SL1,SL2が断線していない場合には、上記の第2のステップで1クロック動作させたとき、スキャンフリップフロップ12の記憶データがスキャンフリップフロップ11の記憶データに置換わり、スキャンフリップフロップ16の記憶データがスキャンフリップフロップ15の記憶データに置換わる。これに対して、シールド配線SL1,SL2が断線している場合には、上記の第2ステップで1クロック動作させても、スキャンフリップフロップ12,16の記憶データが置換されなくなる。この結果、図1のBIST2は、前述の第3ステップで、スキャンフリップフロップ11〜16から出力されたデータが、正常な場合に期待されるパターンデータに一致するか否かを判定することよって、シールド配線L1,L2の断線を検知することができる。

【0037】

(変形例−バウンダリ・スキャンテストによる場合)

被テスト回路3のテスト方法として、上記のスキャンテストに代えてバウンダリ・スキャンテストを用いてもよい。バウンダリ・スキャンテストでは、被テスト回路のI/Oバッファ(入出力バッファ)が、バウンダリ・スキャンセルに置き換えられる。バウンダリ・スキャンセルは、通常のI/Oバッファの機能に加えてシフトレジスタの機能を有し、これらの機能は制御信号によって切替えることができる。

【0038】

シールド配線SL1,SL2の断線を検出するためには、図2の場合と同様に、チェーン状に接続されたバウンダリ・スキャンセルと直列にスキャンフリップフロップ11,12,15,16を接続する。これらのスキャンフリップフロップ11,12,15,16の出力端子およびデータ入力端子には、シールド配線SL1,SL2が接続される。これによって、バウンダリ・スキャンテストを行なう際にシールド配線SL1,SL2の断線検出も併せて行なうことができる。

【0039】

[シールド配線の構成の詳細]

図3は、図1のシールド配線SLの構造の一例を模式的に示す平面図である。図3では、基板SUB上に形成された、シールド配線SL、被テスト回路3、およびセキュリティ回路7とが示されている。これらの構成要素には、図解を容易にするためにハッチングを付している。

【0040】

図4は、図3のシールド配線SLをY方向から見た側面断面図である。図4において、図3と対応する要素には同一のハッチングを付している。

【0041】

図3、図4を参照して、被テスト回路3およびセキュリティ回路7の各々は、基板上に形成された複数のMOS(Metal Oxide Semiconductor)トランジスタ、およびこれらのMOSトランジスタを接続するための複数の金属配線層などによって構成される。シールド配線SLは、これらの被テスト回路3およびセキュリティ回路7で用いられる金属配線層よりもさらに上層の金属配線層Ma,Mbを用いて形成される。

【0042】

具体的に、最上層の金属配線層Mbに形成された配線32の第1端部32AがコンタクトホールCHを介して被テスト回路3と接続され、それより下層の金属配線層Maに形成された配線35の第1端部35AがコンタクトホールCHを介して被テスト回路3と接続される。配線35の第2端部35Bは、コンタクトホールを介して上層の金属配線層Mbに形成された配線31の第1端部31Aと接続される。セキュリティ回路7の上方には、金属配線層Mbを用いて複数の配線36が形成されている。これらの複数の配線36ならびに前述の配線31および32が、下層の金属配線層Maに形成された複数の配線33,34とコンタクトホールCHを介して接続されることによって、ミアンダ状のシールド配線SLが構成される。

【0043】

図5は、シールド配線SLの他の配置例を模式的に示す側面断面図である。図5において、図4の場合と同一または相当する部分には同一の参照符号を付して説明を繰り返さない。

【0044】

図5に示す例では、シールド配線SLは、基板SUBの裏面側(機能モジュール3,7の形成面と反対側)に形成される。ミアンダ状のシールド配線SLの端部51,52は、それぞれ基板SUBを貫通するコンタクトホールSCHを介して被テスト回路3と接続される。

【0045】

フリップチップ構造の場合には、シールド配線SLを基板裏面側に配置するのが望ましい。図5に示すように、フリップチップ構造では、半導体チップの回路面側に形成された絶縁層40Aの表面に突起状の端子(バンプ)41が多数形成される。半導体チップをパッケージに実装する際には、半導体チップを上下逆さにし、これらの突起状の端子41とパッケージ基板とを半田接続する。このような構成では、基板SUBの裏面側からの物理的手段による攻撃を防御する必要があるので、基板SUBの裏面側にシールド配線SLが形成されている。

【0046】

図6は、シールド配線SLのさらに他の配置例を模式的に示す側面断面図である。図6において、図4、図5の場合と同一または相当する部分には同一の参照符号を付して説明を繰り返さない。

【0047】

図6では、基板SUBの両面にシールド配線SL1,SL2が形成された例が示されている。回路面側に形成されたシールド配線SL1の構成は、図4の場合と同一であり、基板裏面側に形成されたシールド配線SL2の構成は、図5の場合と同一である。図6の場合、基板裏面側に設けられたシールド配線SL2を覆うように絶縁層40Bが形成され、絶縁層40Bの表面にパッケージ基板と接続するための突起状の端子(バンプ)41が形成される。

【0048】

今回開示された実施の形態はすべての点で例示であって制限的なものでないと考えられるべきである。この発明の範囲は上記した説明ではなくて請求の範囲によって示され、請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0049】

1 半導体装置、2 BIST(第2の機能モジュール)、3 被テスト回路(第1の機能モジュール)、6 電源回路、7 セキュリティ回路(第3の機能モジュール)、8 電源スイッチ、11〜16 スキャンフリップフロップ、20 シフトレジスタ(スキャンチェーン)、21 スキャンチェーンの入力端子、22 スキャンチェーンの出力端子、OS 出力信号、POR パワーオンリセット信号、SL,SL1,SL2 シールド配線、SUB 基板、TD テストデータ。

【特許請求の範囲】

【請求項1】

基板と、

前記基板上に設けられ、正常に動作しているか否かのテスト対象となる第1の機能モジュールと、

前記基板上に設けられ、前記第1の機能モジュールにテストデータを出力し、前記テストデータに応じて前記第1の機能モジュールから出力された出力信号が正常なデータパターンと一致するか否かを判定する第2の機能モジュールと、

前記基板上に設けられ、耐タンパ性を必要とする第3の機能モジュールと、

前記基板に対して垂直方向から見たときに前記第3の機能モジュールが設けられた領域を覆うように、前記第3の機能モジュールの上方および前記第3の機能モジュールと反対側の基板面のうち少なくとも一方に設けられた1または複数のシールド配線とを備え、

前記1または複数のシールド配線の各々の両端部は、前記第1の機能モジュールと接続され、

前記1または複数のシールド配線の少なくとも1つが断線しているとき、前記出力信号は前記正常なデータパターンと一致しなくなる、半導体装置。

【請求項2】

前記第2の機能モジュールは、前記出力信号が前記正常なデータパターンと一致しないことを検知した場合、前記第3の機能モジュールへのアクセスを遮断させる、請求項1に記載の半導体装置。

【請求項3】

前記第2の機能モジュールは、パワーオンリセット時に前記第1の機能モジュールに前記テストデータを入力し、前記出力信号が前記正常なデータパターンと一致するか否かを判定する、請求項1または2に記載の半導体装置。

【請求項4】

前記第1の機能モジュールは、スキャンテストのためのスキャンチェーンを構成する複数のフリップフリップ回路を含み、

前記第2の機能モジュールは、前記スキャンチェーンの入力端子に前記テストデータを入力し、前記スキャンチェーンの出力端子から出力された前記出力信号が前記正常なデータパターンと一致するか否かを判定し、

前記1または複数のシールド配線のうちの1つのシールド配線の一端は、前記スキャンチェーンを構成する1つのフリップフロップ回路の出力端子と接続され、他端は、前記スキャンチェーンを構成する別の1つのフリップフロップのデータ入力端子と接続される、請求項1に記載の半導体装置。

【請求項1】

基板と、

前記基板上に設けられ、正常に動作しているか否かのテスト対象となる第1の機能モジュールと、

前記基板上に設けられ、前記第1の機能モジュールにテストデータを出力し、前記テストデータに応じて前記第1の機能モジュールから出力された出力信号が正常なデータパターンと一致するか否かを判定する第2の機能モジュールと、

前記基板上に設けられ、耐タンパ性を必要とする第3の機能モジュールと、

前記基板に対して垂直方向から見たときに前記第3の機能モジュールが設けられた領域を覆うように、前記第3の機能モジュールの上方および前記第3の機能モジュールと反対側の基板面のうち少なくとも一方に設けられた1または複数のシールド配線とを備え、

前記1または複数のシールド配線の各々の両端部は、前記第1の機能モジュールと接続され、

前記1または複数のシールド配線の少なくとも1つが断線しているとき、前記出力信号は前記正常なデータパターンと一致しなくなる、半導体装置。

【請求項2】

前記第2の機能モジュールは、前記出力信号が前記正常なデータパターンと一致しないことを検知した場合、前記第3の機能モジュールへのアクセスを遮断させる、請求項1に記載の半導体装置。

【請求項3】

前記第2の機能モジュールは、パワーオンリセット時に前記第1の機能モジュールに前記テストデータを入力し、前記出力信号が前記正常なデータパターンと一致するか否かを判定する、請求項1または2に記載の半導体装置。

【請求項4】

前記第1の機能モジュールは、スキャンテストのためのスキャンチェーンを構成する複数のフリップフリップ回路を含み、

前記第2の機能モジュールは、前記スキャンチェーンの入力端子に前記テストデータを入力し、前記スキャンチェーンの出力端子から出力された前記出力信号が前記正常なデータパターンと一致するか否かを判定し、

前記1または複数のシールド配線のうちの1つのシールド配線の一端は、前記スキャンチェーンを構成する1つのフリップフロップ回路の出力端子と接続され、他端は、前記スキャンチェーンを構成する別の1つのフリップフロップのデータ入力端子と接続される、請求項1に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−45407(P2013−45407A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2011−184856(P2011−184856)

【出願日】平成23年8月26日(2011.8.26)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成23年8月26日(2011.8.26)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]