半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

【発明の詳細な説明】

【技術分野】

【0001】

トランジスタなどの半導体素子を含む回路を有する半導体装置及びその作製方法に関する。例えば、電源回路に搭載されるパワーデバイス、メモリ、サイリスタ、コンバータ、イメージセンサなどを含む半導体集積回路、液晶表示パネルに代表される電気光学装置、発光素子を有する発光表示装置等を部品として搭載した電子機器に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、発光表示装置、半導体回路及び電子機器は全て半導体装置である。

【背景技術】

【0003】

液晶表示装置に代表されるように、ガラス基板等に形成されるトランジスタはアモルファスシリコン、多結晶シリコンなどによって構成されている。アモルファスシリコンを用いたトランジスタは電界効果移動度が低いもののガラス基板の大面積化に対応することができる。また、多結晶シリコンを用いたトランジスタの電界効果移動度は高いがガラス基板の大面積化には適していないという欠点を有している。

【0004】

シリコンを用いたトランジスタに対して、酸化物半導体を用いてトランジスタを作製し、電子デバイスや光デバイスに応用する技術が注目されている。例えば、酸化物半導体として、酸化亜鉛、In−Ga−Zn−O系酸化物を用いてトランジスタを作製し、表示装置の画素のスイッチング素子などに用いる技術が特許文献1及び特許文献2で開示されている。

【0005】

ところで、特に酸化物半導体においては、水素がキャリアの供給源となることが指摘されている。そのため、酸化物半導体の形成時に水素が混入しないような措置を講じることが求められる。また、酸化物半導体のみならず、酸化物半導体に接するゲート絶縁膜の水素を低減することで、しきい値電圧の変動を低減している(特許文献3参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−123861号公報

【特許文献2】特開2007−96055号公報

【特許文献3】特開2009−224479号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、酸化物半導体を用いたトランジスタにおいて、高い電界効果移動度及びオン電流が大きいと共に、ゲート電圧が負のときの電流が小さいトランジスタを作製することは困難である。このため、電界効果移動度が高くオン電流が大きいトランジスタを用いて作製された半導体装置は、トランジスタのゲート電圧が負のときの電流起因による消費電力が上昇してしまうという問題がある。一方、ゲート電圧が負のときの電流が小さいトランジスタを用いて作製された半導体装置は、トランジスタの電界効果移動度が低くオン電流が小さいため、高速動作が困難である、という問題がある。

【0008】

そこで、本発明の一態様は、高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供することを課題の一とする。

【課題を解決するための手段】

【0009】

本発明の一態様は、酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流の低いトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタを作り分けることを特徴とする。代表的には、ゲート電圧が負のときの電流が小さいトランジスタで構成される回路と、電界効果移動度が高くオン電流が大きいトランジスタで構成される回路とを有する。電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタは、酸化物半導体膜、該酸化物半導体膜と重畳するゲート電極、及び酸化物半導体膜及びゲート電極の間に設けられるゲート絶縁膜を有する。また、それぞれの酸化物半導体膜において、ゲート電極と重畳する第1の領域を有する。ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜における第1の領域と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜における第1の領域とが、酸素濃度が異なることを特徴とする。好ましくは、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜における第1の領域と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜における第1の領域は、酸素濃度が低いことを特徴とする。

【0010】

なお、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜には酸素が添加され、その酸化物半導体膜中に添加された酸素濃度は5×1019/cm3以上5×1021/cm3以下である。

【0011】

また、電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタにおける酸化物半導体膜は、ゲート電極と重畳する第1の領域と、該第1の領域を挟む一対の第2の領域とを有する。または、ゲート電極と重畳する第1の領域と、該第1の領域を挟む一対の第2の領域と、該一対の第2の領域を挟む一対の第3の領域とを有する。

【0012】

上記一対の第2の領域及び上記一対の第3の領域には、ドーパントが含まれており、該ドーパントの濃度は、5×1018atoms/cm3以上1×1022atoms/cm3以下、好ましくは5×1018atoms/cm3以上5×1019atoms/cm3未満である。

【0013】

電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタはそれぞれ、シングルゲート構造であってもよい。または、ゲート電圧が負のときの電流が小さいトランジスタは、シングルゲート構造であり、電界効果移動度が高くオン電流が大きいトランジスタは、デュアルゲート構造であってもよい。デュアルゲート構造のトランジスタは、2つの電極に異なる電圧を印加することで、しきい値電圧を制御することができる。

【0014】

電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタは、酸化物半導体膜に接する一対の電極を有する。また、電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタは、スタガ型であってもよい。または、電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタは、コプレナー型であってもよい。

【0015】

また、酸化物半導体膜は、In、Ga、Sn及びZnから選ばれた一種以上の元素を含む。

【0016】

酸化物半導体膜を有するトランジスタにおいて、ゲート電極と重畳する第1の領域の酸素濃度が異なるトランジスタを作製する。第1の領域の酸素濃度が高いトランジスタ、即ち、化学量論的組成比より多くの酸素を含む酸化物半導体膜を有するトランジスタは、酸化物半導体膜に含まれる酸素欠損量が少ない。このため、酸素欠損に起因するエネルギーギャップ中のドナー準位が低い、または実質的にない。この結果、オフ状態において、リーク電流が発生しにくく、トランジスタのゲート電圧が負のときの電流を低減することができる。一方、第1の領域の酸素濃度が低いトランジスタ、即ち、化学量論的組成比より少ない酸素を含む酸化物半導体膜を有するトランジスタは、酸化物半導体膜の酸素欠損量が含まれるため、オン状態においてキャリアが発生しやすくなり、トランジスタの電界効果移動度を高く、オン電流を大きくすることができる。このため、半導体装置を構成する回路の特性に合わせて、トランジスタを作り分けることで、具体的には高速動作が必要な回路においては、電界効果移動度が高くオン電流が大きいトランジスタを用い、リーク電流の少ない回路においては、ゲート電圧が負のときの電流が小さいトランジスタを用いることで、高速動作が可能であり、且つ消費電力の低い半導体装置を作製することができる。

【発明の効果】

【0017】

本発明の一態様によって、酸化物半導体膜の酸素欠損量の多いトランジスタ及び酸素欠損量の少ないトランジスタをそれぞれ作製することができる。この結果、電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタを作製することができる。更には、当該トランジスタを回路の機能に合わせて作り分けることで、高速動作が可能であり、且つ消費電力の低い半導体装置を作製することができる。

【図面の簡単な説明】

【0018】

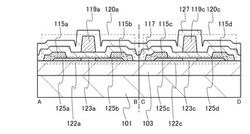

【図1】本発明の一態様に係る半導体装置を説明する断面図である。

【図2】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図3】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図4】本発明の一態様に係る半導体装置を説明する断面図である。

【図5】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図6】本発明の一態様に係る半導体装置を説明する断面図である。

【図7】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図8】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図9】本発明の一態様に係る半導体装置を説明する断面図である。

【図10】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図11】本発明の一態様に係る半導体装置を説明する断面図である。

【図12】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図13】本発明の一態様に係る半導体装置を説明する断面図である。

【図14】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図15】本発明の一態様に係る半導体装置を説明する断面図である。

【図16】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図17】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図18】本発明の一態様に係るトランジスタの電気特性を説明する図である。

【図19】本発明の一態様に係る記憶装置の構成を示すブロック図である。

【図20】本発明の一態様に係る記憶装置を説明する回路図である。

【図21】本発明の一態様に係る記憶装置を説明する回路図である。

【図22】本発明の一態様を示すアクティブマトリクス型表示装置を説明する図である。

【図23】本発明の一態様を示す電子機器の外観図である。

【発明を実施するための形態】

【0019】

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分または同様な機能を有する部分には、同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0020】

なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0021】

また、本明細書にて用いる第1、第2、第3などの用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。

【0022】

(実施の形態1)

本実施の形態では、ゲート電圧が負のときの電流が小さいトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタとを有する半導体装置の構造及び作製方法について、図1乃至図3を用いて説明する。本実施の形態のトランジスタは、コプレナー型のトップゲートトランジスタであって、一対の電極が酸化物半導体膜の側面及び表面の一部を覆うことを特徴とする。

【0023】

図1は、本実施の形態に示す半導体装置の断面図である。図1に示す半導体装置は、ゲート電圧が負のときの電流が小さいトランジスタ120aと、電界効果移動度が高くオン電流が大きいトランジスタ120cとを有する。

【0024】

ゲート電圧が負のときの電流が小さいトランジスタ120aは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜122aと、酸化物半導体膜122aに接する、ソース電極及びドレイン電極として機能する一対の電極115a、115bと、酸化物半導体膜122aを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜122aと重畳するゲート電極119aとを有する。酸化物半導体膜122aは、ゲート電極119aと重畳する第1の領域123aと、第1の領域123aを挟むドーパントを含む一対の第2の領域125a、125bとを有する。なお、酸化物半導体膜122aにおいて、第1の領域123aはチャネル領域として機能し、ドーパントを含む一対の第2の領域125a、125bにおいて、一対の電極115a、115bと接する領域はソース領域及びドレイン領域として機能する。また、一対の電極115a、115bと接しない領域により、ソース−ドレイン耐圧を高めることができる。

【0025】

電界効果移動度が高くオン電流が大きいトランジスタ120cは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜122cと、酸化物半導体膜122cに接する、ソース電極及びドレイン電極として機能する一対の電極115c、115dと、酸化物半導体膜122cを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜122cと重畳するゲート電極119cとを有する。酸化物半導体膜122cは、ゲート電極119cと重畳する第1の領域123cと、第1の領域123cを挟むドーパントを含む一対の第2の領域125c、125dとを有する。なお、酸化物半導体膜122cにおいて、第1の領域123cはチャネル領域として機能し、ドーパントを含む一対の第2の領域125c、125dにおいて、一対の電極115c、115dと接する領域はソース領域及びドレイン領域として機能する。また、一対の電極115c、115dと接しない領域により、ソース−ドレイン耐圧を高めることができる。

【0026】

また、トランジスタ120a、120cを覆う絶縁膜127を有することが好ましい。

【0027】

本実施の形態においては、トランジスタ120aを構成する酸化物半導体膜122aには、化学量論的組成比に対し過剰な酸素が含まれている。この場合、過剰な酸素は、酸化物半導体の格子間に存在する場合もある。酸化物半導体膜122aに添加された酸素濃度は、5×1019/cm3以上5×1021/cm3以下である。

【0028】

酸化物半導体膜122aに含まれる酸素欠損は、酸化物半導体膜122cと比較して少ない。このため、酸素欠損に起因するエネルギーギャップ中のドナー準位が低い、または実質的にない。この結果、トランジスタ120aはゲート電圧が負のときの電流が小さいトランジスタである。一方、酸化物半導体膜122cは、酸素欠損を含む。このため、トランジスタ120cでは、オン状態において、キャリアが発生しやすい。このため、トランジスタ120cは、電界効果移動度が高くオン電流が大きいトランジスタである。

【0029】

基板101の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板101として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板101として用いてもよい。

【0030】

また、基板101として、可撓性基板を用いてもよい。基板101と絶縁膜103の間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板101より分離し、他の基板に転載するのに用いることができる。その際、半導体装置は耐熱性の劣る基板や可撓性の基板にも転載できる。

【0031】

絶縁膜103は、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム等を適宜用いることができる。

【0032】

また、絶縁膜103は、加熱により酸素の一部が脱離する酸化絶縁膜を用いて形成してもよい。加熱により酸素の一部が脱離する酸化絶縁膜としては、化学量論比を満たす酸素よりも多くの酸素を含む酸化絶縁膜を用いることが好ましい。加熱により酸素の一部が脱離する酸化絶縁膜は、加熱により酸素が脱離するため、加熱により酸化物半導体膜に酸素を拡散させることができる。加熱により酸素の一部が脱離する酸化絶縁膜の代表例としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム等がある。

【0033】

絶縁膜103は、50nm以上、好ましくは200nm以上500nm以下とする。絶縁膜103を厚くすることで、絶縁膜として加熱により酸素の一部が脱離する酸化絶縁膜を用いる場合、絶縁膜103の酸素脱離量を増加させることができると共に、絶縁膜103及び後に形成される酸化物半導体膜との界面における界面準位を低減することが可能である。

【0034】

ここで、「加熱により酸素の一部が脱離する」とは、TDS(Thermal Desorption Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の放出量が1.0×1018atoms/cm3以上、好ましくは3.0×1020atoms/cm3以上であることをいう。

【0035】

ここで、TDS分析にて、酸素原子に換算しての酸素の脱離量の測定方法について、以下に説明する。

【0036】

TDS分析したときの気体の脱離量は、スペクトルの積分値に比例する。このため、絶縁膜のスペクトルの積分値と、標準試料の基準値に対する比とにより、気体の放出量を計算することができる。標準試料の基準値とは、所定の原子を含む試料の、スペクトルの積分値に対する原子の密度の割合である。

【0037】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、及び絶縁膜のTDS分析結果から、絶縁膜の酸素分子の脱離量(NO2)は、数式1で求めることができる。ここで、TDS分析で得られる質量数32で検出されるスペクトルの全てが酸素分子由来と仮定する。質量数32のものとしてCH3OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子及び質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0038】

【数1】

【0039】

NH2は、標準試料から脱離した水素分子を密度で換算した値である。SH2は、標準試料をTDS分析したときのスペクトルの積分値である。ここで、標準試料の基準値を、NH2/SH2とする。SO2は、絶縁膜をTDS分析したときのスペクトルの積分値である。αは、TDS分析におけるスペクトル強度に影響する係数である。数式1の詳細に関しては、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の脱離量は、電子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料として1×1016atoms/cm3の水素原子を含むシリコンウェハを用いて測定する。

【0040】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の脱離量についても見積もることができる。

【0041】

なお、NO2は酸素分子の脱離量である。絶縁膜においては、酸素原子に換算したときの酸素の放出量は、酸素分子の脱離量の2倍となる。

【0042】

上記構成において、加熱により酸素放出される絶縁膜は、酸素が過剰な酸化シリコン(SiOX(X>2))であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2))とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数及び酸素原子数は、ラザフォード後方散乱法により測定した値である。

【0043】

絶縁膜103から酸化物半導体膜122a、122cに酸素が供給されることで、絶縁膜103及び酸化物半導体膜122a、122cの界面準位を低減できる。この結果、トランジスタの動作などに起因して生じうる電荷などが、上述の絶縁膜103及び酸化物半導体膜122a、122cの界面に捕獲されることを抑制することができ、電気特性の劣化の少ないトランジスタを得ることができる。

【0044】

さらに、酸化物半導体膜122a、122cの酸素欠損に起因して電荷が生じる場合がある。一般に、酸化物半導体膜の酸素欠損は、一部がドナーとなりキャリアである電子を生じる。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。この傾向はバックチャネル側で生じる酸素欠損において顕著である。なお、本明細書におけるバックチャネルとは、図1に示す酸化物半導体膜122a、122cの第1の領域123a、123cにおいて絶縁膜103との界面近傍を指す。絶縁膜103から酸化物半導体膜122a、122cに酸素が十分に供給されることにより、しきい値電圧がマイナス方向へシフトする要因である、酸化物半導体膜122a、122cの酸素欠損を低減することができる。

【0045】

酸化物半導体膜122a、122cとしては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてジルコニウム(Zr)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0046】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0047】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する。)、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−Zr−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0048】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0049】

また、酸化物半導体として、InMO3(ZnO)m(m>0、且つ、mは整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In2SnO5(ZnO)n(n>0、且つ、nは整数)で表記される材料を用いてもよい。

【0050】

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)あるいはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子数比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子数比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

【0051】

しかし、これらに限られず、必要とする半導体特性及び電気特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0052】

なお、酸化物半導体膜122a、122cに形成することが可能な金属の酸化物は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタがオフ状態のときに流れる電流(オフ電流)を低減することができる。

【0053】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0054】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0055】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0056】

なお、Raとは、JIS B0601:2001(ISO4287:1997)で定義されている算術平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」で表現でき、以下の式にて定義される。

【0057】

【数2】

【0058】

ここで、指定面とは、粗さ計測の対象となる面であり、座標(x1,y1,f(x1,y1)),(x1,y2,f(x1,y2)),(x2,y1,f(x2,y1)),(x2,y2,f(x2,y2))の4点で表される四角形の領域とし、指定面をxy平面に投影した長方形の面積をS0、基準面の高さ(指定面の平均高さ)をZ0とする。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて測定可能である。

【0059】

また、酸化物半導体膜122a、122cとして、結晶化した部分を有するCAAC(C Axis Aligned Crystalline Oxide Semiconductorともいう。)膜を用いてもよい。

【0060】

CAAC膜とは、c軸配向し、かつab面、表面または界面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て、金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面(あるいは表面または界面)においては、a軸またはb軸の向きが異なる(c軸を中心に回転した)結晶を含む酸化物半導体膜のことである。

【0061】

広義に、CAAC膜とは、非単結晶であって、そのab面に垂直な方向から見て、三角形もしくは六角形、または正三角形もしくは正六角形の原子配列を有し、かつc軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子が層状に配列した相を含む膜をいう。

【0062】

CAAC膜は単結晶ではないが、非晶質のみから形成されているものでもない。また、CAAC膜は結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

【0063】

CAAC膜を構成する酸素の一部は窒素で置換されてもよい。また、CAAC膜を構成する個々の結晶部分のc軸は一定の方向(例えば、CAAC膜が形成される基板面やCAAC膜の表面や膜面、界面等に垂直な方向)に揃っていてもよい。あるいは、CAAC膜を構成する個々の結晶部分のab面の法線は一定の方向(例えば、基板面、表面、膜面、界面等に垂直な方向)を向いていてもよい。

【0064】

CAAC膜は、その組成等に応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成等に応じて、可視光に対して透明であったり不透明であったりする。

【0065】

ここでは、酸化物半導体膜122a、122cとして非晶質構造の酸化物半導体膜を形成する。

【0066】

酸化物半導体膜122a、122cの厚さは、1nm以上50nm以下、更に好ましくは1nm以上30nm以下、更に好ましくは1nm以上10nm以下、更に好ましくは3nm以上7nm以下とすることが好ましい。酸化物半導体膜122a、122cの厚さを上記厚さとすることで、トランジスタのしきい値電圧のマイナス方向へのシフトを抑制することができる。

【0067】

酸化物半導体膜122a、122cにおいて、アルカリ金属またはアルカリ土類金属の濃度は、1×1018atoms/cm3以下、さらに好ましくは2×1016atoms/cm3以下であることが望ましい。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアが生成されることがあり、トランジスタのオフ電流の上昇の原因となるためである。

【0068】

酸化物半導体膜122a、122cの第1の領域123a、123cには、5×1018atoms/cm3以下の窒素が含まれてもよい。

【0069】

酸化物半導体膜122a、122cの第1の領域123a、123cは、水素濃度を5×1018atoms/cm3未満、好ましくは1×1018atoms/cm3以下、より好ましくは5×1017atoms/cm3以下、さらに好ましくは1×1016atoms/cm3以下とすることが好ましい。酸化物半導体及び水素の結合により、水素の一部がドナーとなり、キャリアである電子が生じてしまう。これらのため、酸化物半導体膜122a、122cの第1の領域123a、123c中の水素濃度を低減することで、しきい値電圧のマイナス方向へのシフトを低減することができる。

【0070】

ドーパントを含む一対の第2の領域125a〜125dは、ドーパントとして、ホウ素、窒素、リン、及びヒ素の少なくとも一以上が含まれる。または、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノンの少なくとも一以上が含まれる。または、ドーパントとしてフッ素が含まれる。なお、ドーパントとして、ホウ素、窒素、リン、及びヒ素の一以上と、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノンの一以上と、フッ素とが適宜組み合わされて含まれていてもよい。

【0071】

ドーパントを含む一対の第2の領域125a〜125dに含まれるドーパントの濃度は、5×1018atoms/cm3以上1×1022atoms/cm3以下、好ましくは5×1018atoms/cm3以上5×1019atoms/cm3未満とする。

【0072】

ドーパントを含む一対の第2の領域125a〜125dはドーパントを含むため、キャリア密度または欠陥を増加させることができる。このため、ドーパントを含まない第1の領域123a、123cと比較して導電性を高めることができる。なお、ドーパント濃度を増加させすぎると、ドーパントがキャリアの移動を阻害することになり、ドーパントを含む一対の第2の領域125a〜125dの導電性を低下させることになる。

【0073】

ドーパントを含む一対の第2の領域125a〜125dは、導電率が0.1S/cm以上1000S/cm以下、好ましくは10S/cm以上1000S/cm以下とすることが好ましい。

【0074】

一対の電極115a〜115dは導電材料として、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタングステンからなる単体金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、タングステン膜上にチタン膜を積層する二層構造、銅−マグネシウム−アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などがある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。なお、一対の電極115a〜115dは配線としても機能させてもよい。

【0075】

電極115a〜115dは、酸化物半導体膜122a、122cの表面の一部及び側面、特にチャネル幅方向と平行な側面を覆うため、酸化物半導体膜122a、122cとの接触面積を広くすることができる。このため、酸化物半導体膜122a、122cと、一対の電極115a〜115dとの接触抵抗を低減でき、またチャネル幅を広げることが可能であり、トランジスタのオン電流を大きくすることができる。

【0076】

ゲート絶縁膜117は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa−Zn−O系金属酸化物膜などを用いればよく、積層または単層で設ける。また、ゲート絶縁膜117は、絶縁膜103に示すような、加熱により酸素が脱離する酸化絶縁膜を用いてもよい。ゲート絶縁膜117に加熱により酸素が脱離する膜を用いることで、酸化物半導体膜122a、122cに生じる酸素欠損を修復することができ、トランジスタの電気特性の劣化を抑制できる。

【0077】

また、ゲート絶縁膜117として、ハフニウムシリケート(HfSiOx)、窒素が添加されたハフニウムシリケート(HfSixOyNz)、窒素が添加されたハフニウムアルミネート(HfAlxOyNz)、酸化ハフニウム、酸化イットリウムなどのhigh−k材料を用いることでゲート絶縁膜の厚さを薄くしてもゲートリークを低減できる。

【0078】

ゲート絶縁膜117の厚さは、10nm以上300nm以下、より好ましくは5nm以上50nm以下、より好ましくは10nm以上30nm以下とするとよい。

【0079】

ゲート電極119a、119cは、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金などを用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属元素を用いてもよい。また、ゲート電極119a、119cは、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタングステン膜を積層する二層構造、窒化タンタル膜上にタングステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などがある。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の膜、または複数組み合わせた合金膜、もしくは窒化膜を用いてもよい。

【0080】

また、ゲート電極119a、119cは、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

【0081】

また、ゲート電極119a、119cとゲート絶縁膜117との間に、ゲート絶縁膜117に接する材料層として、窒素を含むIn−Ga−Zn−O膜や、窒素を含むIn−Sn−O膜や、窒素を含むIn−Ga−O膜や、窒素を含むIn−Zn−O膜や、窒素を含むSn−O膜や、窒素を含むIn−O膜や、金属窒化膜(InN、ZnNなど)を設けることが好ましい。これらの膜は仕事関数が5eV、好ましくは5.5eV以上であり、トランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。例えば、窒素を含むIn−Ga−Zn−O膜を用いる場合、少なくとも酸化物半導体膜122a、122cより高い窒素濃度、具体的には7原子%以上の窒素を含むIn−Ga−Zn−O膜を用いる。

【0082】

絶縁膜127は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層または単層で設ける。なお、絶縁膜127として、絶縁膜103と同様に、加熱により酸素の一部が脱離する酸化絶縁膜を用いて形成してもよい。また、絶縁膜127として、外部への酸素の拡散を防ぐ酸化絶縁膜を用いることで、ゲート絶縁膜117から脱離する酸素を酸化物半導体膜122a、122cに供給することができる。また、絶縁膜127として、外部からの水素の拡散を防ぐ酸化絶縁膜を用いることで、外部から酸化物半導体膜122a、122cへの水素の拡散を低減することが可能であり、酸化物半導体膜122a、122cの欠損を低減することができる。外部からの水素の拡散を防ぐ酸化絶縁膜の代表例としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。

【0083】

なお、本実施の形態においては、一対の電極115a〜115dの対向領域を、直線状、U字状、C字状等とすることができる。一対の電極115a〜115dの対向領域を、U字状、C字状等とすることで、チャネル幅を大きくすることが可能であり、オン電流を大きくすることができる。

【0084】

次に、図1に示すトランジスタの作製方法について、図2及び図3を用いて説明する。なお、各図においてA−B断面図は、図1に示すA−B断面図の作製工程を説明し、C−D断面図は、図1に示すC−D断面図の作製工程を説明する。

【0085】

図2(A)に示すように、基板101上に絶縁膜103及び酸化物半導体膜105を積層形成する。

【0086】

絶縁膜103は、スパッタリング法、CVD法等により形成する。なお、加熱により酸素の一部が脱離する酸化絶縁膜は、スパッタリング法を用いることで形成しやすいため好ましい。

【0087】

加熱により酸素の一部が脱離する酸化絶縁膜をスパッタリング法により形成する場合は、成膜ガス中の酸素量が高いことが好ましく、酸素、または酸素及び希ガスの混合ガス等を用いることができる。代表的には、成膜ガス中の酸素濃度を6%以上100%以下にすることが好ましい。

【0088】

加熱により酸素の一部が脱離する酸化絶縁膜の代表例として酸化シリコン膜を形成する場合、石英(好ましくは合成石英)をターゲットに用い、基板温度30℃以上450℃以下(好ましくは70℃以上200℃以下)、基板とターゲットの間の距離(T−S間距離)を20mm以上400mm以下(好ましくは40mm以上200mm以下)、圧力を0.1Pa以上4Pa以下(好ましくは0.2Pa以上1.2Pa以下)、高周波電源を0.5kW以上12kW以下(好ましくは1kW以上5kW以下)、成膜ガス中のO2/(O2+Ar)割合を1%以上100%以下(好ましくは6%以上100%以下)として、RFスパッタリング法により酸化シリコン膜を形成することが好ましい。なお、石英(好ましくは合成石英)ターゲットに代えてシリコンターゲットを用いることもできる。なお、成膜ガスとしては、酸素のみを用いてもよい。

【0089】

なお、絶縁膜103を形成する前に、加熱処理またはプラズマ処理により、基板に含まれる水素を脱離させることが好ましい。この結果、後の加熱処理において、絶縁膜103及び酸化物半導体膜105中に水素が拡散することを防ぐことができる。なお、加熱処理は、不活性雰囲気、減圧雰囲気または乾燥空気雰囲気にて、100℃以上基板の歪み点未満で行う。また、プラズマ処理は、希ガス、酸素、窒素または酸化窒素(亜酸化窒素、一酸化窒素、二酸化窒素など)を用いる。

【0090】

また、絶縁膜103を平坦化することで、後に形成する酸化物半導体膜105の断切れ防止が可能であるため好ましい。

【0091】

酸化物半導体膜105は、スパッタリング法、塗布法、印刷法、パルスレーザー蒸着法等により形成した後、加熱処理を行うことで形成することができる。

【0092】

ここで、酸化物半導体膜105を成膜するスパッタリング装置について、以下に詳細を説明する。

【0093】

酸化物半導体膜105を成膜する処理室は、リークレートを1×10−10Pa・m3/秒以下とすることが好ましく、それによりスパッタリング法により成膜する際、膜中への不純物の混入を低減することができる。

【0094】

リークレートを低くするには、外部リークのみならず内部リークを低減する必要がある。外部リークとは、微小な穴やシール不良などによって真空系の外から気体が流入することである。内部リークとは、真空系内のバルブなどの仕切りからの漏れや内部の部材からの放出ガスに起因する。リークレートを1×10−10Pa・m3/秒以下とするためには、外部リーク及び内部リークの両面から対策をとる必要がある。

【0095】

外部リークを減らすには、処理室の開閉部分はメタルガスケットでシールするとよい。メタルガスケットは、フッ化鉄、酸化アルミニウム、または酸化クロムによって被覆された金属材料を用いると好ましい。メタルガスケットはOリングと比べ密着性が高く、外部リークを低減できる。また、フッ化鉄、酸化アルミニウム、酸化クロムなどの不動態によって被覆された金属材料を用いることで、メタルガスケットから生じる水素を含む放出ガスが抑制され、内部リークも低減することができる。

【0096】

処理室の内壁を構成する部材として、水素を含む放出ガスの少ないアルミニウム、クロム、チタン、ジルコニウム、ニッケルまたはバナジウムを用いる。また、前述の材料を鉄、クロム及びニッケルなどを含む合金材料に被覆して用いてもよい。鉄、クロム及びニッケルなどを含む合金材料は、剛性があり、熱に強く、また加工に適している。ここで、表面積を小さくするために部材の表面凹凸を研磨などによって低減しておくと、放出ガスを低減できる。あるいは、前述の成膜装置の部材をフッ化鉄、酸化アルミニウム、酸化クロムなどの不動態で被覆してもよい。

【0097】

さらに、スパッタガスを処理室に導入する直前に、スパッタガスの精製機を設けることが好ましい。このとき、精製機から処理室までの配管の長さを5m以下、好ましくは1m以下とする。配管の長さを5m以下または1m以下とすることで、配管からの放出ガスの影響を長さに応じて低減できる。

【0098】

処理室の排気は、ドライポンプなどの粗引きポンプと、スパッタイオンポンプ、ターボ分子ポンプ及びクライオポンプなどの高真空ポンプとを適宜組み合わせて行うとよい。ターボ分子ポンプは大きいサイズの分子の排気が優れる一方、水素や水の排気能力が低い。さらに、水の排気能力の高いクライオポンプまたは水素の排気能力の高いスパッタイオンポンプを組み合わせることが有効となる。

【0099】

処理室の内側に存在する吸着物は、内壁に吸着しているために処理室の圧力に影響しないが、処理室を排気した際のガス放出の原因となる。そのため、リークレートと排気速度に相関はないが、排気能力の高いポンプを用いて、処理室に存在する吸着物をできる限り脱離し、予め排気しておくことが重要である。なお、吸着物の脱離を促すために、処理室をベーキングしてもよい。ベーキングすることで吸着物の脱離速度を10倍程度大きくすることができる。ベーキングは100℃以上450℃以下で行えばよい。このとき、不活性ガスを導入しながら吸着物の除去を行うと、排気するだけでは脱離しにくい水などの脱離速度をさらに大きくすることができる。

【0100】

このように、酸化物半導体膜の成膜工程において、更に好ましくは絶縁膜の成膜工程において、処理室の圧力、処理室のリークレートなどを制御して、不純物の混入を極力抑えることによって、酸化物半導体膜に含まれる水素を含む不純物の混入を低減することができる。また、絶縁膜から酸化物半導体膜への水素などの不純物の拡散を低減することができる。

【0101】

酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水となると共に、酸素が脱離した格子(あるいは酸素が脱離した部分)には欠損が形成されてしまう。このため、酸化物半導体膜の成膜工程において、水素を含む不純物を極めて減らすことにより、酸化物半導体膜の欠損を低減することが可能である。このため、不純物をできるだけ除去し、高純度化させた酸化物半導体膜をチャネル領域とすることにより、トランジスタの信頼性を高めることができる。

【0102】

スパッタリング法において、プラズマを発生させるための電源装置は、RF電源装置、AC電源装置、DC電源装置等を適宜用いることができる。

【0103】

ターゲットとしては、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属酸化物であるIn−Ga−Zn系酸化物、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−Zr−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物などのターゲットを用いることができる。

【0104】

ターゲットの一例として、In、Ga、及びZnを含む金属酸化物ターゲットを、In2O3:Ga2O3:ZnO=1:1:1[mol数比]の組成比とする。また、In2O3:Ga2O3:ZnO=1:1:2[mol数比]の組成比を有するターゲット、またはIn2O3:Ga2O3:ZnO=1:1:4[mol数比]の組成比を有するターゲット、In2O3:Ga2O3:ZnO=2:1:8[mol数比]の組成比を有するターゲットを用いることもできる。また、In2O3:ZnO=25:1〜1:4[mol数比]の組成比を有するターゲットを用いることもできる。

【0105】

なお、スパッタリングガスは、希ガス(代表的にはアルゴン)雰囲気、酸素雰囲気、希ガス及び酸素の混合ガスを適宜用いる。なお、希ガス及び酸素の混合ガスの場合、希ガスに対して酸素のガス比を高めることが好ましい。また、スパッタリングガスには、水素を含む不純物が除去された高純度ガスを用いることが好ましい。

【0106】

また、スパッタリング法を用いる場合、基板温度を150℃以上450℃以下、好ましくは200℃以上350℃以下とすることで、酸化物半導体膜中への水分(水素を含む)などの混入を低減しつつ、CAAC膜を形成することができる。

【0107】

また、絶縁膜103において、酸化物半導体膜と接する領域を酸化アルミニウム膜で形成し、酸化物半導体膜105を形成した後、酸化物半導体膜105にレーザ光を照射してもよい。当該工程により、絶縁膜103との界面からCAAC膜を形成することができる。

【0108】

なお、酸化物半導体膜をスパッタリング装置で成膜する前に、スパッタリング装置にダミー基板を搬入し、ダミー基板上に酸化物半導体膜を成膜して、ターゲット表面、または防着板に付着した水素、水分を取り除く工程を行ってもよい。

【0109】

基板101上に上記方法により酸化物半導体膜を形成した後、基板101に加熱処理を施して、該酸化物半導体膜より水素を放出させることができる。なお、当該加熱処理においては、酸化物半導体膜から酸素も脱離し、酸化物半導体膜中には酸素欠損が残存する場合がある。

【0110】

なお、絶縁膜103として、加熱により酸素の一部が脱離する酸化絶縁膜を用いる場合、基板101上に上記方法により酸化物半導体膜を形成した後、基板101に加熱処理を施して、該酸化物半導体膜より水素を放出させると共に、絶縁膜103に含まれる酸素の一部を、酸化物半導体膜と、絶縁膜103及び酸化物半導体膜の界面近傍とに拡散させる。当該加熱処理において、絶縁膜103に含まれる酸素が、酸化物半導体膜へ拡散し、酸化物半導体膜において絶縁膜と接する界面の近傍とにおける酸素欠損を低減することができる。なお、当該加熱条件によっては、絶縁膜103から酸化物半導体膜へ酸素が拡散するが、これと同時に酸化物半導体膜から外部へ酸素が脱離してしまい、酸化物半導体膜において、酸素欠損が残存してしまう場合がある。当該酸素欠損は、トランジスタのチャネル長がサブミクロンである微細構造のトランジスタの場合、特に影響が大きく、しきい値電圧がマイナス方向にシフトしてしまう。

【0111】

酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水となると共に、酸素が脱離した格子(あるいは酸素が脱離した部分)には欠損が形成されてしまう。このため、当該加熱処理により、水素を含む不純物を極めて減らすことにより、酸化物半導体膜の水素由来の欠損を低減することが可能である。

【0112】

以上のことから、図2(A)に示すように、少なくとも水素濃度が低減された酸化物半導体膜105を形成することができる。

【0113】

該加熱処理の温度は、少なくとも酸化物半導体膜から水素を放出させる温度が好ましく、更には酸化物半導体膜から水素を放出させると共に、絶縁膜103に含まれる酸素の一部を脱離させ、さらには酸化物半導体膜に拡散させる温度が好ましく、代表的には、150℃以上基板歪み点未満、好ましくは250℃以上450℃以下、更に好ましくは300℃以上450℃以下とする。

【0114】

また、該加熱処理は、RTA(Rapid Thermal Anneal)装置を用いることができる。RTAを用いることで、短時間に限り、基板の歪み点以上の温度で熱処理を行うことができる。そのため、酸化物半導体膜からの水素の放出、更には絶縁膜103から酸化物半導体膜への酸素拡散の時間を短縮することができる。

【0115】

加熱処理は、不活性ガス雰囲気で行うことができ、代表的には、ヘリウム、ネオン、アルゴン、キセノン、クリプトン等の希ガス、または窒素雰囲気で行うことが好ましい。また、酸素雰囲気及び減圧雰囲気で行ってもよい。処理時間は3分〜24時間とする。

【0116】

次に、図2(B)に示すように、酸化物半導体膜107a、107cを形成する。酸化物半導体膜107a、107cは、酸化物半導体膜105上にマスクを形成し、酸化物半導体膜105の一部を選択的にエッチングすることで形成する。

【0117】

次に、図2(C)に示すように、後に電界効果移動度が高くオン電流が大きいトランジスタの一部となる酸化物半導体膜107c上にマスク109を形成した後、酸化物半導体膜107aに酸素111を添加する。この結果、酸化物半導体膜107cより酸素欠損を低減した酸化物半導体膜113a(図2(D)参照。)を形成する。この後、マスク109を除去する。

【0118】

酸化物半導体膜107aに酸素を添加する方法として、イオンドーピング法またはイオンインプランテーション法を用いることができる。または、酸素の添加方法として、プラズマイマージョンイオンインプランテーション法を用いてもよい。プラズマイマージョンイオンインプランテーション法は、酸化物半導体膜107aが凹凸のある形状であっても酸素の添加を効率よく行うことができる。さらに、酸素の添加はイオンドーピング法またはイオンインプランテーション法などによる注入する以外の方法でも行うことができる。例えば、酸素雰囲気にてプラズマを発生させて、酸化物半導体膜107aに対してプラズマ処理を行うことによって、酸素を添加することができる。上記プラズマを発生させる装置としては、ドライエッチング装置やプラズマCVD装置、高密度プラズマCVD装置などを用いることができる。

【0119】

酸化物半導体膜107aに添加する酸素111は、酸素ラジカル、酸素原子、及び酸素イオンの一以上である。また、酸素111は、酸化物半導体膜107aの少なくとも一部、代表的には、酸化物半導体膜107aの表面、酸化物半導体膜107a中、及び酸化物半導体膜107a及び絶縁膜103の界面のいずれかに添加されればよい。

【0120】

イオンドーピング法またはイオンインプランテーション法を用いて酸素を酸化物半導体膜107aに添加する際の酸素添加量は、5×1019/cm3以上5×1021/cm3以下である。この際、酸素111のエネルギーが高いと、酸化物半導体膜にダメージが入り、物理的に欠陥が生じてしまうため、酸素111のエネルギーは酸化物半導体膜にダメージを与えない程度とすることが好ましい。

【0121】

また、酸素が添加された酸化物半導体膜113aは、化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている。この場合、過剰な酸素は、酸化物半導体の格子間に存在する場合もある。このような酸化物半導体の組成は、InGaZnmO(m+3x)(x>1、m≧1)で表すことができる。

【0122】

なお、酸化物半導体において、酸素は主たる成分材料の一つである。このため、酸化物半導体膜中の酸素濃度を、SIMS(Secondary Ion Mass Spectrometry)などの方法を用いて、正確に見積もることは難しい。つまり、酸化物半導体膜に酸素が意図的に添加されたか否かを判別することは困難であるといえる。

【0123】

ところで、酸素には17Oや18Oといった同位体が存在し、自然界におけるこれらの存在比率はそれぞれ酸素原子全体の0.037%、0.204%程度であることが知られている。つまり、酸化物半導体膜中におけるこれら同位体の濃度は、SIMSなどの方法によって見積もることができる程度になるから、これらの濃度を測定することで、酸化物半導体膜中の酸素濃度をより正確に見積もることが可能な場合がある。よって、これらの濃度を測定することで、酸化物半導体膜に意図的に酸素が添加されたか否かを判別してもよい。

【0124】

酸化物半導体膜107aに酸素を添加することで、酸化物半導体膜113a中の酸素欠損を低減することができる。一方、酸化物半導体膜107cには、酸素を添加していなため、酸化物半導体膜113aと比較して酸素欠損の残存量が多い。

【0125】

次に、酸化物半導体膜113a上に一対の電極115a、115bを形成すると共に、酸化物半導体膜107c上に一対の電極115c、115dを形成する。次に、一対の電極115a〜115d及び酸化物半導体膜113a、107cを覆うゲート絶縁膜117を形成する。

【0126】

一対の電極115a〜115dは、印刷法またはインクジェット法を用いて形成する。または、スパッタリング法、CVD法、蒸着法等で導電膜を形成した後、該導電膜上にマスクを形成して導電膜をエッチングして、一対の電極115a〜115dを形成する。導電膜上に形成するマスクは、印刷法、インクジェット法、フォトリソグラフィ法を適宜用いることができる。なお、マスクを用いて一対の電極115a〜115dを形成した場合は、この後マスクを除去する。

【0127】

ゲート絶縁膜117は、スパッタリング法、CVD法等により形成する。

【0128】

次に、図3(A)に示すように、ゲート絶縁膜117上にゲート電極119a、119cを形成する。

【0129】

ゲート電極119a、119cは、印刷法またはインクジェット法により形成する。若しくは、スパッタリング法、CVD法、蒸着法等で導電膜を形成した後、該導電膜上にマスクを形成して導電膜をエッチングして、ゲート電極119a、119cを形成する。導電膜上に形成するマスクは、印刷法、インクジェット法、フォトリソグラフィ法を適宜用いることができる。なお、マスクを用いてゲート電極119a、119cを形成した場合は、この後マスクを除去する。

【0130】

次に、図3(B)に示すように、ゲート電極119a、119cをマスクとして、酸化物半導体膜113a、107cにドーパント121を添加する処理を行う。この結果、図3(C)に示すように、A−B断面においては、ドーパントを含む一対の第2の領域125a、125bを形成する。ゲート電極119aをマスクにしてドーパントを添加するため、セルフアラインでドーパントを含む一対の第2の領域125a、125b、及びドーパントが添加されない第1の領域123aを形成することができる。なお、ゲート電極119aと重畳する第1の領域123aはチャネル領域として機能する。また、ドーパントを含む一対の第2の領域125a、125bにおいて、一対の電極115a、115bと接する領域はソース領域及びドレイン領域として機能する。また、一対の電極115a、115bと接しない領域により、ソース−ドレイン耐圧を高めることができる。また、第1の領域123a、及びドーパントを含む一対の第2の領域125a、125bを酸化物半導体膜122aと示す。

【0131】

また、C−D断面においては、ドーパントを含む一対の第2の領域125c、125dを形成する。ゲート電極119cをマスクにしてドーパントを添加するため、セルフアラインでドーパントを含む一対の第2の領域125c、125d、及びドーパントが添加されない第1の領域123cを形成することができる。なお、ゲート電極119cと重畳する第1の領域123cはチャネル領域として機能する。また、ドーパントを含む一対の第2の領域125c、125dにおいて、一対の電極115c、115dと接する領域はソース領域及びドレイン領域として機能する。また、一対の電極115c、115dと接しない領域により、ソース−ドレイン耐圧を高めることができる。また、第1の領域123c、及びドーパントを含む一対の第2の領域125c、125dを酸化物半導体膜122cと示す。

【0132】

一対の第2の領域125a〜125dのそれぞれ一部には、一対の電極115a〜115dを透過したドーパントが添加される。一対の第2の領域125a〜125dにおいて、ドーパントのエネルギーによるダメージが原因の欠陥が生じても、当該欠陥がキャリアの発生源となり、膜抵抗が低減するため、図2(C)に示す酸素111の添加と比較して、ドーパントのエネルギーを高めることができる。

【0133】

酸化物半導体膜113a、107cにドーパントを添加する方法として、イオンドーピング法またはイオンインプランテーション法を用いることができる。また、添加するドーパントとしては、ホウ素、窒素、リン、及びヒ素の少なくとも一以上がある。または、ドーパントとしては、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノンの少なくとも一以上がある。または、ドーパントとしてフッ素が含まれる。なお、ドーパントとして、ホウ素、窒素、リン、及びヒ素の一以上と、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノンの一以上と、フッ素とを適宜組み合わしてもよい。

【0134】

また、酸化物半導体膜113a、107cへのドーパントの添加は、酸化物半導体膜113a、107cを覆って、絶縁膜などが形成されている状態を示したが、酸化物半導体膜113a、107cが露出している状態でドーパントの添加を行ってもよい。

【0135】

さらに、上記ドーパントの添加はイオンドーピング法またはイオンインプランテーション法などによる注入する以外の方法でも行うことができる。例えば、添加する元素を含むガス雰囲気にてプラズマを発生させて、被添加物に対してプラズマ処理を行うことによって、ドーパントを添加することができる。上記プラズマを発生させる装置としては、ドライエッチング装置やプラズマCVD装置などを用いることができる。

【0136】

この後、加熱処理を行ってもよい。当該加熱処理の温度は、代表的には、150℃以上450℃以下、好ましくは300℃以上450℃以下とする。または、150℃から450℃まで徐々に温度上昇させながら加熱してもよい。

【0137】

当該加熱処理により、ドーパントを含む一対の第2の領域125a〜125dの抵抗を低減することができる。なお、当該加熱処理において、ドーパントを含む一対の第2の領域125a〜125dは、結晶状態でも非晶質状態でもよい。また、ゲート絶縁膜117から酸素が酸化物半導体膜に拡散し、酸化物半導体膜に含まれる酸素欠損を低減することができる。なお、当該工程における酸化物半導体膜への酸素拡散量は図2(C)に示す酸素添加と比べると少ない。このため、酸化物半導体膜122cにおいては、酸素欠損が低減されるもの、酸素欠損は残存する。

【0138】

絶縁膜127は、ゲート絶縁膜117と同様に形成することができる。

【0139】

以上の工程により、図1に示すトランジスタ120a、120cを作製することができる。

【0140】

トランジスタ120a、120cは、脱水素化を目的とする熱処理によって、水素を酸化物半導体膜より意図的に排除し、その後酸化物半導体膜に酸素を選択的に添加することによって、酸化物半導体膜を構成する主成分材料の一つである酸素を供給することができる。これによって、酸化物半導体膜を高純度化及び電気的にi型(真性)化することができる。

【0141】

また、酸素を選択的に添加することで、上記加熱処理において残存する酸化物半導体膜中または界面の酸素欠損を低減し、酸素欠損に起因するエネルギーギャップ中のドナー準位を低減する、または実質的になくすことができる。よって、トランジスタ120aは、ゲート電圧が負のときの電流を低減することができる。

【0142】

本実施の形態に示すトランジスタ120aを構成する酸化物半導体膜122aは、酸素が添加されており、酸素欠損が少ない。このため、トランジスタ120aはゲート電圧が負のときの電流が小さいトランジスタである。一方、トランジスタ120cを構成する酸化物半導体膜122cは、酸素が添加されておらず、酸素欠損を含む。このため、トランジスタ120cでは、オン状態において、キャリアが発生しやすい。このため、トランジスタ120cは、電界効果移動度が高くオン電流が大きいトランジスタである。以上のことから、選択的に酸化物半導体膜へ酸素を添加することで、同一基板上に、ゲート電圧が負のときの電流が小さいトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタを作製することができる。

【0143】

(実施の形態2)

本実施の形態では、実施の形態1と異なる構造のトランジスタ及びのその作製方法について、図2、図4及び図5を用いて説明する。本実施の形態では、コプレナー型のトップゲートトランジスタについて説明する。

【0144】

図4は、本実施の形態に示す半導体装置の断面図である。図4に示す半導体装置は、ゲート電圧が負のときの電流が小さいトランジスタ130aと、電界効果移動度が高くオン電流が大きいトランジスタ130cとを有する。

【0145】

ゲート電圧が負のときの電流が小さいトランジスタ130aは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜122aと、酸化物半導体膜122aを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜122aと重畳するゲート電極119aとを有する。また、ゲート絶縁膜117及びゲート電極119a上に絶縁膜127及び絶縁膜131が積層され、ゲート絶縁膜117、絶縁膜127、及び絶縁膜131の開口部に形成され、且つ酸化物半導体膜122aと接する一対の電極133a、133bを有する。なお、酸化物半導体膜122aの構造は、実施の形態1と同様であり、ゲート電極119aと重畳する第1の領域123aと、第1の領域123aを挟むドーパントを含む一対の第2の領域125a、125bとを有する。

【0146】

電界効果移動度が高くオン電流が大きいトランジスタ130cは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜122cと、酸化物半導体膜122cを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜122cと重畳するゲート電極119cとを有する。また、ゲート絶縁膜117及びゲート電極119c上に絶縁膜127及び絶縁膜131が積層され、ゲート絶縁膜117、絶縁膜127、及び絶縁膜131の開口部に形成され、且つ酸化物半導体膜122cと接する一対の電極133c、133dを有する。なお、酸化物半導体膜122cの構造は、実施の形態1と同様であり、ゲート電極119cと重畳する第1の領域123cと、第1の領域123cを挟むドーパントを含む一対の第2の領域125c、125dとを有する。

【0147】

酸化物半導体膜122aは酸素が添加されており、酸化物半導体膜122cは、酸素が添加されない。即ち、酸化物半導体膜122aは酸化物半導体膜122cより酸素欠損の含有量が少ない。

【0148】

また、トランジスタ130a、130cを覆う絶縁膜127を有することが好ましい。

【0149】

本実施の形態で示すトランジスタはコプレナー型であるため、トランジスタの微細化が可能である。

【0150】

絶縁膜131は、絶縁膜127と同様に形成することができる。または、絶縁膜131として、BPSG(Boron Phosphorus Silicate Glass)などの無機材料、または、ポリイミド、アクリルなどの有機材料を用いて形成することで、絶縁膜131の平坦性を高めることができる。

【0151】

一対の電極133a〜133dは、実施の形態1に示す一対の電極115a〜115dと同様の材料を適宜用いることができる。

【0152】

次に、図4に示すトランジスタ130a、130cの作製方法について、図2及び図5を用いて説明する。なお、各図においてA−B断面図は、図4に示すA−B断面図の作製工程を説明し、C−D断面図は、図4に示すC−D断面図の作製工程を説明する。

【0153】

図2(A)乃至図2(C)の工程を経て、図5(A)に示すように、基板101上に絶縁膜103を形成する。また、絶縁膜103上に酸化物半導体膜113a、107cを形成する。なお、酸化物半導体膜113a、107cは、加熱処理が施され脱水素化処理された酸化物半導体膜である。

【0154】

次に、酸化物半導体膜113a、107c上に、実施の形態1と同様の方法により、ゲート絶縁膜117を形成した後、ゲート絶縁膜117上にゲート電極119a、119cを形成する。

【0155】

ゲート電極119a、119cをマスクとして、酸化物半導体膜113a、107cにドーパント121を添加する処理を行う。この結果、図5(B)に示すように、A−B断面においては、ドーパントを含む一対の第2の領域125a、125bを形成する。ゲート電極119aをマスクにしてドーパントを添加するため、セルフアラインでドーパントを含む一対の第2の領域125a、125b、及びドーパントが添加されない第1の領域123aを形成することができる。なお、ゲート電極119aと重畳する第1の領域123aはチャネル領域として機能する。また、第1の領域123a、及びドーパントを含む一対の第2の領域125a、125bを酸化物半導体膜122aと示す。

【0156】

また、C−D断面においては、ドーパントを含む一対の第2の領域125c、125dを形成する。ゲート電極119cをマスクにしてドーパントを添加するため、セルフアラインでドーパントを含む一対の第2の領域125c、125d、及びドーパントが添加されない第1の領域123cを形成することができる。なお、ゲート電極119cと重畳する第1の領域123cはチャネル領域として機能する。また、第1の領域123c、及びドーパントを含む一対の第2の領域125c、125dを酸化物半導体膜122cと示す。

【0157】

この後、加熱処理を行ってもよい。

【0158】

次に、図5(C)に示すように、ゲート絶縁膜117及びゲート電極119a、119c上に、絶縁膜127及び絶縁膜131を形成する。絶縁膜131の形成方法は、スパッタリング法、CVD法、塗布法、印刷法等を適宜用いることができる。

【0159】

次に、ゲート絶縁膜117、絶縁膜127、及び絶縁膜131の一部を除去し、開口部を形成した後、当該開口部において、酸化物半導体膜122a、122cの一対の第2の領域125a〜125dに接する電極133a〜133dを形成する。一対の電極133a〜133dは、一対の電極115a〜115dと同様に形成することができる。

【0160】

本実施の形態により、脱水素化工程の後、選択的に酸化物半導体膜へ酸素を添加することで、同一基板上に、ゲート電圧が負のときの電流が小さいトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタを作製することができる。

【0161】

(実施の形態3)

本実施の形態では、実施の形態1及び実施の形態2と異なる構造のトランジスタの構造及び作製方法について、図2、図6乃至図8を用いて説明する。本実施の形態に示すトランジスタは、実施の形態1と比較して、酸化物半導体膜の構造が異なる。

【0162】

図6は、本実施の形態に示す半導体装置の断面図である。図6に示す半導体装置は、ゲート電圧が負のときの電流が小さいトランジスタ150aと、電界効果移動度が高くオン電流が大きいトランジスタ150cとを有する。

【0163】

ゲート電圧が負のときの電流が小さいトランジスタ150aは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜146aと、酸化物半導体膜146aに接する、ソース電極及びドレイン電極として機能する一対の電極115a、115bと、酸化物半導体膜146aを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜146aと重畳するゲート電極119aとを有する。酸化物半導体膜146aは、ゲート電極119aと重畳する第1の領域147aと、第1の領域147aを挟むドーパントを含む一対の第2の領域149a、149bと、一対の第2の領域を挟むドーパントを含む一対の第3の領域151a、151bを有する。なお、酸化物半導体膜146aにおいて、第1の領域147aはチャネル領域として機能し、ドーパントを含む一対の第2の領域149a、149bは、電界緩和領域として機能し、ドーパントを含む一対の第3の領域151a、151bは、ソース領域及びドレイン領域として機能する。

【0164】

電界効果移動度が高くオン電流が大きいトランジスタ150cは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜146cと、酸化物半導体膜146cに接する、ソース電極及びドレイン電極として機能する一対の電極115c、115dと、酸化物半導体膜146cを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜146cと重畳するゲート電極119cとを有する。酸化物半導体膜146cは、ゲート電極119cと重畳する第1の領域147cと、第1の領域147cを挟むドーパントを含む一対の第2の領域149c、149dと、一対の第2の領域を挟むドーパントを含む一対の第3の領域151c、151dを有する。なお、酸化物半導体膜146cにおいて、第1の領域147cはチャネル領域として機能し、ドーパントを含む一対の第2の領域149c、149dは、電界緩和領域として機能し、ドーパントを含む一対の第3の領域151c、151dは、ソース領域及びドレイン領域として機能する。

【0165】

また、トランジスタ150a、150cを覆う絶縁膜127を有することが好ましい。

【0166】

酸化物半導体膜146aにおいて、第1の領域147a及び一対の第2の領域149a、149bは、一対の第3の領域151a、151bと比較して、酸素濃度が高い。即ち、これは、一対の電極115a〜115dを形成した後、酸化物半導体膜107a、107cに酸素を添加することで、このような構造となる。

【0167】

即ち、第1の領域147aは、5×1019/cm3以上5×1021/cm3以下の酸素が添加されている。また、一対の第2の領域149a、149bは、1×1018/cm3以上5×1021/cm3以下の酸素が添加されており、且つドーパント濃度が5×1018atoms/cm3以上1×1022atoms/cm3以下、好ましくは5×1018atoms/cm3以上5×1019atoms/cm3未満である。また、一対の第3の領域151a、151bは、ドーパント濃度が5×1018atoms/cm3以上1×1022atoms/cm3以下、好ましくは5×1018atoms/cm3以上5×1019atoms/cm3未満である。

【0168】

一方、酸化物半導体膜146cにおいて、第1の領域147c、一対の第2の領域149c、149d、及び一対の第3の領域151c、151dには酸素が添加されない。即ち、酸化物半導体膜146aの第1の領域147a、一対の第2の領域149a、149bと比較して、酸素濃度が低い。また、一対の第2の領域149c、149d、及び一対の第3の領域151c、151dは、ドーパント濃度が5×1018atoms/cm3以上1×1022atoms/cm3以下、好ましくは5×1018atoms/cm3以上5×1019atoms/cm3未満である。

【0169】

本実施の形態に示すトランジスタ150aにおいて、ソース領域及びドレイン領域となる一対の第3の領域151a、151bには酸素が添加されない。即ち、当該領域においては、酸素欠損が残存する。この結果、一対の第3の領域151a、151bにおいては、キャリアが発生しやすく、膜抵抗を低減することができる。一方、第1の領域147a及び一対の第2の領域149a、149bには酸素が添加されるため、酸素欠損が低減されている。これらのため、トランジスタ150aは、ゲート電圧が負のときの電流が小さく、且つ実施の形態1及び実施の形態2に示すトランジスタ120a、130aと比較して、オン電流の大きいトランジスタとなる。

【0170】

次に、図6に示すトランジスタ150a、150cの作製方法について、図2、図7及び図8を用いて説明する。なお、各図においてA−B断面図は、図6に示すA−B断面図の作製工程を説明し、C−D断面図は、図6に示すC−D断面図の作製工程を説明する。

【0171】

図2(A)及び図2(B)の工程を経て、図7(A)に示すように、基板101上に絶縁膜103を形成する。また、絶縁膜103上に酸化物半導体膜107a、107cを形成する。なお、酸化物半導体膜107a、107cは、加熱処理が施され脱水素化処理された酸化物半導体膜である。

【0172】

次に、酸化物半導体膜107a、107c上に、実施の形態1と同様の方法により、一対の電極115a〜115dを形成する。次に、酸化物半導体膜107a、107c、及び一対の電極115a〜115d上に、実施の形態1と同様の方法によりゲート絶縁膜117を形成する。

【0173】

次に、図7(B)に示すように、後に電界効果移動度が高くオン電流が大きいトランジスタの一部となる酸化物半導体膜107c上にマスク109を形成した後、酸化物半導体膜107aに酸素141を添加する。酸素141は、実施の形態1に示す酸素111と同様に添加することができる。この後、マスク109を除去する。

【0174】

本実施の形態では、ゲート絶縁膜117を介して、酸化物半導体膜107aに酸素を添加するため、酸素の添加領域(酸素の注入深さ)をより制御しやすくなり、酸化物半導体膜107aへ効率よく酸素を添加することができる。

【0175】

この結果、図7(C)に示すように、酸化物半導体膜107aにおいて、一対の電極115a、115bと重畳しない領域においては酸素が添加される。この結果、酸素が添加された領域143aと、酸素が添加されない領域145a、145bを形成することができる。即ち、酸化物半導体膜107c及び領域145a、145bより酸素欠損の少ない領域143aを形成することができる。

【0176】

次に、図8(A)に示すように、ゲート電極119a、119cを形成する。次に、ゲート電極119a、119cをマスクとして、酸素が添加された酸化物半導体膜の領域143a及び領域145a、145b、並びに酸化物半導体膜107cに、実施の形態1と同様にドーパント121を添加する。

【0177】

この結果、図8(B)に示すように、A−B断面においては、ドーパントを含む一対の第2の領域149a、149b、及び一対の第3の領域151a、151bを形成する。ゲート電極119aをマスクにしてドーパントを添加するため、セルフアラインでドーパントを含む一対の第2の領域149a、149b及び一対の第3の領域151a、151b、並びにドーパントが添加されない第1の領域147aを形成することができる。なお、ゲート電極119aと重畳する第1の領域147aはチャネル領域として機能する。また、ドーパントを含む一対の第2の領域149a、149bは電界緩和領域として機能する。また、ドーパントを含む一対の第3の領域151a、151bはソース領域及びドレイン領域として機能する。また、第1の領域147a、ドーパントを含む一対の第2の領域149a、149b、及びドーパントを含む一対の第3の領域151a、151bを酸化物半導体膜146aと示す。

【0178】

また、C−D断面においては、ドーパントを含む一対の第2の領域149c、149d、及び一対の第3の領域151c、151dを形成する。ゲート電極119cをマスクにしてドーパントを添加するため、セルフアラインでドーパントを含む一対の第2の領域149c、149d及び一対の第3の領域151c、151d、並びにドーパントが添加されない第1の領域147cを形成することができる。なお、ゲート電極119cと重畳する第1の領域147cはチャネル領域として機能する。また、ドーパントを含む一対の第2の領域149c、149dは電界緩和領域として機能する。また、ドーパントを含む一対の第3の領域151c、151dはソース領域及びドレイン領域として機能する。また、第1の領域147c、ドーパントを含む一対の第2の領域149c、149d、及びドーパントを含む一対の第3の領域151c、151dを酸化物半導体膜146cと示す。

【0179】

この後、加熱処理を行ってもよい。

【0180】

以上の工程により、図6に示すトランジスタ150a、150cを作製することができる。

【0181】

なお、この後、図8(C)に示すように、実施の形態2と同様に、ゲート絶縁膜117及びゲート電極119a、119c上に絶縁膜127及び絶縁膜131を形成する。次に、ゲート絶縁膜117、絶縁膜127、及び絶縁膜131の一部を除去し、開口部を形成した後、当該開口部において、一対の電極115a〜115dに接する一対の電極133a〜133dを形成してもよい。

【0182】

本実施の形態により、脱水素化工程の後、選択的に酸化物半導体膜へ酸素を添加することで、同一基板上に、ゲート電圧が負のときの電流が小さいトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタを作製することができる。

【0183】

(実施の形態4)

本実施の形態は、実施の形態1乃至実施の形態3と異なる構造のトランジスタの構造及び作製方法について、図2、図9及び図10を用いて説明する。本実施の形態に示すトランジスタは、ゲート電極の側面にサイドウォール絶縁膜を有する点が実施の形態1乃至実施の形態3と異なる。

【0184】

図9は、本実施の形態に示す半導体装置の断面図である。図9に示す半導体装置は、ゲート電圧が負のときの電流が小さいトランジスタ160aと、電界効果移動度が高くオン電流が大きいトランジスタ160cとを有する。

【0185】

ゲート電圧が負のときの電流が小さいトランジスタ160aは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜122aと、酸化物半導体膜122aに接する、ソース電極及びドレイン電極として機能する一対の電極165a、165bと、酸化物半導体膜122aの一部を覆うゲート絶縁膜163aと、ゲート絶縁膜163a上であって、且つ酸化物半導体膜122aと重畳するゲート電極119a及びゲート電極119aの側面に設けられるサイドウォール絶縁膜161a、161bとを有する。トランジスタ160aにおいては、一対の電極165a、165bは、酸化物半導体膜122aの側面及び表面の一部、並びにサイドウォール絶縁膜161a、161bの側面に接する。このため、一対の第2の領域125a、125bにおいて、一対の電極165a、165bと接する領域がソース領域及びドレイン領域として機能する。また、ゲート絶縁膜163aと接する領域により、ソース−ドレイン耐圧を高めることができる。

【0186】

電界効果移動度が高くオン電流が大きいトランジスタ160cは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜122cと、酸化物半導体膜122cに接する、ソース電極及びドレイン電極として機能する一対の電極165c、165dと、酸化物半導体膜122cの一部を覆うゲート絶縁膜163cと、ゲート絶縁膜163c上であって、且つ酸化物半導体膜122cと重畳するゲート電極119c及びゲート電極119cの側面に設けられるサイドウォール絶縁膜161c、161dとを有する。トランジスタ160cにおいては、一対の電極165c、165dは、酸化物半導体膜122cの側面及び表面の一部、並びにサイドウォール絶縁膜161c、161dの側面に接する。このため、一対の第2の領域125c、125dにおいて、一対の電極165c、165dと接する領域がソース領域及びドレイン領域として機能する。また、ゲート絶縁膜163cと接する領域により、ソース−ドレイン耐圧を高めることができる。

【0187】

酸化物半導体膜122aは酸素が添加された領域であり、酸化物半導体膜122cは、酸素が添加されない領域である。即ち、酸化物半導体膜122aは酸化物半導体膜122cより酸素欠損の含有量が少ない。

【0188】

また、トランジスタ160a、160cを覆う絶縁膜127を有することが好ましい。

【0189】

トランジスタ160a、160cはサイドウォール絶縁膜161a〜161dを有する。サイドウォール絶縁膜161a〜161dの幅が制御できるため、一対の電極165a〜165dを形成するためのマスク合わせの精度を緩和することができる。よって、複数のトランジスタにおけるばらつきを低減することができる。

【0190】

次に、図9に示すトランジスタ160a、160cの作製方法について、図2、図5及び図10を用いて説明する。なお、各図においてA−B断面図は、図9に示すA−B断面図の作製工程を説明し、C−D断面図は、図9に示すC−D断面図の作製工程を説明する。

【0191】

図2(A)乃至図2(C)の工程、並びに図5(A)及び図5(B)の工程を経て、基板101上に絶縁膜103を形成する。また、絶縁膜103上に、酸化物半導体膜122a、122cを形成する。また、酸化物半導体膜122a、122c上にゲート絶縁膜117及びゲート電極119a、119cを形成する。なお、酸化物半導体膜122a、122cは、加熱処理が施され脱水素化処理された酸化物半導体膜である。

【0192】

次に、ゲート絶縁膜117およびゲート電極119a、119c上に、後にサイドウォール絶縁膜161a〜161dとなる絶縁膜を形成する。絶縁膜は、スパッタリング法、CVD法等により形成する。また、当該絶縁膜の厚さは特に限定はないが、ゲート電極119a、119cの形状に応じる被覆性を考慮して、適宜選択すればよい。

【0193】

次に、絶縁膜をエッチングすることによりサイドウォール絶縁膜161a〜161dを形成する。該エッチングは、異方性の高いエッチングであり、サイドウォール絶縁膜161a〜161dは、絶縁膜に異方性の高いエッチング工程を行うことでセルフアラインに形成することができる。ここで、異方性の高いエッチングとしては、ドライエッチングが好ましく、例えば、エッチングガスとして、トリフルオロメタン(CHF3)、オクタフルオロシクロブタン(C4F8)、テトラフルオロメタン(CF4)などのフッ素を含むガスを用いることができ、ヘリウム(He)やアルゴン(Ar)などの希ガスまたは水素(H2)を添加しても良い。さらに、ドライエッチングとして、基板に高周波電圧を印加する、反応性イオンエッチング法(RIE法)を用いるのが好ましい。

【0194】

また、ドーパントを含む一対の第2の領域125a〜125dにおいて、ソースまたはドレインとチャネルとの距離は、サイドウォール絶縁膜161a〜161dの幅に対応し、またサイドウォール絶縁膜161a〜161dの幅は、ゲート電極119a、119cの厚さにも対応することから、サイドウォール絶縁膜161a〜161dの幅が、所望の範囲となるように、ゲート電極119a、119cの厚さを決めればよい。

【0195】

また、サイドウォール絶縁膜161a〜161dの形成工程と共に、異方性の高いエッチングを用いてゲート絶縁膜117をエッチングし、酸化物半導体膜122a、122cを露出させることで、ゲート絶縁膜163a、163cを形成することができる(図10(A)参照。)。

【0196】

次に、図10(B)に示すように、一対の電極165a〜165dを形成する。

【0197】

一対の電極165a〜165dは、実施の形態1に示す一対の電極115a〜115dと同様に形成することができる。一対の電極165a〜165dは、サイドウォール絶縁膜161a〜161d及びゲート絶縁膜163a、163cの側面と接するように、形成することが好ましい。即ち、トランジスタの一対の電極165a〜165dの端部がサイドウォール絶縁膜161a〜161d上に位置し、酸化物半導体膜122a、122cにおいて、ドーパントを含む一対の第2の領域125a〜125dの露出部を全て覆っていることが好ましい。この結果、ドーパントが含まれる一対の第2の領域125a〜125dにおいて、一対の電極165a〜165dと接する領域がソース領域及びドレイン領域として機能する。また、サイドウォール絶縁膜161a〜161d及びゲート絶縁膜163a、163cと重なる領域により、ソース−ドレイン耐圧を高めることができる。また、サイドウォール絶縁膜161a〜161dの長さによりソースまたはドレインとチャネルとの距離が制御できるため、一対の電極165a〜165dを形成するためのマスク合わせの精度を緩和することができる。よって、複数のトランジスタにおけるばらつきを低減することができる。

【0198】

次に、ゲート電極119a、119c、サイドウォール絶縁膜161a〜161d、及び一対の電極165a〜165d上に、絶縁膜127を形成してもよい。

【0199】

以上の工程により、図9に示すトランジスタ160a、160cを作製することができる。

【0200】

なお、この後、図10(C)に示すように、絶縁膜167を形成し、絶縁膜127及び絶縁膜167の一部をエッチングして開口部を形成した後、当該開口部において、一対の電極165a〜165dに接する一対の電極169a〜169dを形成する。一対の電極169a〜169dは、一対の電極115a〜115dと同様に形成することができる。

【0201】

本実施の形態により、脱水素化工程の後、選択的に酸化物半導体膜へ酸素を添加することで、同一基板上に、ゲート電圧が負のときの電流が小さいトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタを作製することができる。

【0202】

(実施の形態5)

本実施の形態では、実施の形態1及び実施の形態3において、酸化物半導体膜、一対の電極、及びゲート電極の構造の異なるトランジスタについて、図11を用いて説明する。

【0203】

図11は、本実施の形態に示す半導体装置の断面図である。図11に示す半導体装置は、ゲート電圧が負のときの電流が小さいトランジスタ170aと、電界効果移動度が高くオン電流が大きいトランジスタ170cとを有する。

【0204】

ゲート電圧が負のときの電流が小さいトランジスタ170aは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸素が添加された酸化物半導体膜142aと、酸化物半導体膜142aに接する、ソース電極及びドレイン電極として機能する一対の電極115a、115bと、酸化物半導体膜142aを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜142a及び一対の電極115a、115bの一部と重畳するゲート電極171aとを有する。なお、酸化物半導体膜142aは、酸素が添加された領域143aと、酸素が添加されない領域145a、145bを有する。

【0205】

電界効果移動度が高くオン電流が大きいトランジスタ170cは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜107cと、酸化物半導体膜107cに接する、ソース電極及びドレイン電極として機能する一対の電極115c、115dと、酸化物半導体膜107cを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜107c及び一対の電極115c、115dの一部と重畳するゲート電極171cとを有する。

【0206】

また、トランジスタ170a、170cを覆う絶縁膜127を有することが好ましい。

【0207】

次に、図11に示すトランジスタ170a、170cの作製方法について、図2、図7及び図12を用いて説明する。

【0208】

図2(A)、図2(B)、図7(A)、及び図7(B)の工程を経て、図12(A)に示すように、基板101上に絶縁膜103を形成する。また、絶縁膜103上に酸化物半導体膜142a、107cを形成する。なお、酸化物半導体膜142a、107cは、加熱処理が施され脱水素化処理された酸化物半導体膜である。また、一対の電極115a〜115dを形成する。また、ゲート絶縁膜117を形成する。なお、酸化物半導体膜142aは、酸素が添加された領域143aと、酸素が添加されない領域145a、145bを有する。即ち、酸化物半導体膜107c及び領域145a、145bと比較して、領域143aは酸素欠損が少ない。

【0209】

次に、図12(B)に示すように、ゲート絶縁膜117上にゲート電極171a、171cを形成する。ゲート電極171a、171cは、ゲート電極119a、119cと同様に形成する。なお、ゲート電極171a、171cの端部はそれぞれ、一対の電極115a〜115dと一部重畳するように形成する。この後、絶縁膜127を形成してもよい。

【0210】

以上の工程により、図11に示すトランジスタ170a、170cを作製することができる。

【0211】

なお、この後、実施の形態2と同様に、絶縁膜127上に、図5(C)に示す絶縁膜131を形成する。次に、ゲート絶縁膜117、絶縁膜127、及び絶縁膜131の一部を除去し、開口部を形成した後、当該開口部において、一対の電極115a〜115dに接する一対の電極133a〜133dを形成してもよい。

【0212】

また、ここでは、酸化物半導体膜107a、107c上に一対の電極115a〜115dを形成した後に、酸化物半導体膜107aに酸素を添加したが、この代わりに、酸化物半導体膜107a、107c上に一対の電極115a〜115dを形成する前に、酸化物半導体膜107aに酸素を添加してもよい。

【0213】

本実施の形態に示すトランジスタは、ゲート電極と、一対の電極とが一部重畳しているため、酸化物半導体膜にオフセット領域が無く、ドーパントを添加しなくとも、酸化物半導体膜において一対の電極と接する領域がソース領域及びドレイン領域となる。このため、工程数を削減することができる。

【0214】

本実施の形態により、脱水素化工程の後、選択的に酸化物半導体膜へ酸素を添加することで、同一基板上に、ゲート電圧が負のときの電流が小さいトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタを作製することができる。

【0215】

(実施の形態6)

本実施の形態では、実施の形態1、実施の形態3、及び実施の形態5において、一対の電極の構造の異なるトランジスタについて、説明する。

【0216】

実施の形態1、実施の形態3、及び実施の形態5において、トランジスタ120a、120c、150a、150c、170a、170cの一対の電極115a〜115dは、それぞれ酸化物半導体膜122a、122c、146a、146c、142a、107cと、ゲート絶縁膜117との間に設けられているが、当該構造の代わりに、一対の電極がそれぞれ、絶縁膜103と酸化物半導体膜122a、122c、146a、146c、142a、107cとの間に設けられてもよい。

【0217】

(実施の形態7)

本実施の形態では、実施の形態1乃至実施の形態6と異なる構造のトランジスタの構造及び作製方法について、図13及び図14を用いて説明する。本実施の形態では、逆スタガ型のボトムゲートトランジスタについて説明する。

【0218】

図13は、本実施の形態に示す半導体装置の断面図である。図13に示す半導体装置は、ゲート電圧が負のときの電流が小さいトランジスタ210aと、電界効果移動度が高くオン電流が大きいトランジスタ210cとを有する。

【0219】

ゲート電圧が負のときの電流が小さいトランジスタ210aは、基板201上に設けられる絶縁膜203と、絶縁膜203上に設けられるゲート電極205aと、絶縁膜203及びゲート電極205aを覆うゲート絶縁膜207と、ゲート絶縁膜207上であって、且つゲート電極205aと重畳する酸化物半導体膜217aと、酸化物半導体膜217aに接する一対の電極219a、219bとを有する。

【0220】

電界効果移動度が高くオン電流が大きいトランジスタ210cは、基板201上に設けられる絶縁膜203と、絶縁膜203上に設けられるゲート電極205cと、絶縁膜203及びゲート電極205cを覆うゲート絶縁膜207と、ゲート絶縁膜207上であって、且つゲート電極205cと重畳する酸化物半導体膜211cと、酸化物半導体膜211cに接する一対の電極219c、219dとを有する。

【0221】

また、トランジスタ210a、210cを覆う絶縁膜221を有することが好ましい。なお、絶縁膜203は設けなくともよい。

【0222】

基板201、絶縁膜203、ゲート電極205a、205c、及びゲート絶縁膜207は、それぞれ実施の形態1に示す基板101、絶縁膜103、ゲート電極119a、119c、及びゲート絶縁膜117を適宜用いることができる。

【0223】

酸化物半導体膜217aは、実施の形態1に示す酸化物半導体膜122aに含まれる第1の領域123aと同様に、酸素が添加された領域であり、酸化物半導体膜217cより酸素欠損の含有量が少ない。一方、酸化物半導体膜217cは、実施の形態1に示す酸化物半導体膜122cと同様に、酸素が添加されない領域である。

【0224】

一対の電極219a〜219d及び絶縁膜221はそれぞれ、実施の形態1に示す一対の電極115a〜115d、絶縁膜127と同様に形成することができる。

【0225】

次に、図13に示すトランジスタ210a、210cの作製方法について、図14を用いて説明する。なお、図14においてA−B断面図は、図13に示すA−B断面図の作製工程を説明し、C−D断面図は、図13に示すC−D断面図の作製工程を説明する。

【0226】

図14(A)に示すように、基板201上に絶縁膜203を形成する。次に、絶縁膜203上にゲート電極205a、205cを形成する。ゲート電極205a、205c上にゲート絶縁膜207を形成する。ゲート絶縁膜207上に酸化物半導体膜209を形成する。

【0227】

絶縁膜203は、実施の形態1に示す絶縁膜103と同様に形成することができる。

【0228】

ゲート電極205a、205cは、実施の形態1に示すゲート電極119a、119cと同様に形成することができる。

【0229】

ゲート絶縁膜207及び酸化物半導体膜209はそれぞれ、実施の形態1に示すゲート絶縁膜117及び酸化物半導体膜105と同様に形成することができる。即ち、酸化物半導体膜209は、加熱処理が施され脱水素化処理された酸化物半導体膜である。

【0230】

次に、酸化物半導体膜209を選択的にエッチングして、図14(B)に示すように、酸化物半導体膜211a、211cを形成する。次に、後に電界効果移動度が高くオン電流が大きいトランジスタの一部となる酸化物半導体膜211c上にマスク213を形成した後、酸化物半導体膜211aに酸素215を添加する。この結果、酸素欠損を酸化物半導体膜211cより低減した酸化物半導体膜217a(図14(C)参照。)を形成する。この後、マスク213を除去する。なお、酸素215の添加方法に関しては、実施の形態1に示す酸素111の添加方法と同様にすればよい。

【0231】

次に、図14(D)に示すように、ゲート絶縁膜207及び酸化物半導体膜217a、211c上に一対の電極219a〜219dを形成する。次に、ゲート絶縁膜207、酸化物半導体膜217a、211c、及び一対の電極219a〜219d上に絶縁膜221を形成する。一対の電極219a〜219dは、実施の形態1に示す一対の電極115a〜115dと同様に形成する。また、絶縁膜221は、実施の形態1に示す絶縁膜127と同様に形成する。

【0232】

この後、加熱処理を行うことで、トランジスタの信頼性を高めることができる。

【0233】

以上の工程により、図13に示すトランジスタ210a、210cを作製することができる。

【0234】

なお、図13に示すトランジスタ210a、210cは、絶縁膜221及び酸化物半導体膜217a、211cの間にそれぞれ一対の電極219a〜219dを設けたが、この代わりに、ゲート絶縁膜207及び酸化物半導体膜217a、211cの間にそれぞれ一対の電極219a〜219dを設けてもよい。

【0235】

本実施の形態により、脱水素化工程の後、選択的に酸化物半導体膜へ酸素を添加することで、同一基板上に、ゲート電圧が負のときの電流が小さいトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタを作製することができる。

【0236】

(実施の形態8)

本実施の形態では、実施の形態1乃至実施の形態7と異なる構造のトランジスタの構造及び作製方法について、図15乃至図17を用いて説明する。本実施の形態では、コプレナー型のトップゲートトランジスタ、及びスタガ型のデュアルゲートトランジスタを有する半導体装置について説明する。

【0237】

図15は、本実施の形態に示す半導体装置の断面図である。図15に示す半導体装置は、ゲート電圧が負のときの電流が小さいトランジスタ310aと、電界効果移動度が高くオン電流が大きいトランジスタ310cとを有する。

【0238】

ゲート電圧が負のときの電流が小さいトランジスタ310aは、シングルゲート構造で、コプレナー型のトップゲートトランジスタである。なお、トランジスタ310aは、実施の形態1乃至実施の形態7に示す、ゲート電圧が負のときの電流が小さいトランジスタ120a、130a、150a、160a、170a、210aを適宜選択して用いることができる。ここでは、実施の形態1に示すトランジスタ120aと同様の構造のトランジスタを用いて説明する。

【0239】

ゲート電圧が負のときの電流が小さいトランジスタ310aは、基板301上に設けられる絶縁膜303及び絶縁膜307と、絶縁膜307に設けられる酸化物半導体膜326aと、酸化物半導体膜326aに接する、ソース電極及びドレイン電極として機能する一対の電極317a、317bと、酸化物半導体膜326aを覆う絶縁膜319と、絶縁膜319上であって、且つ酸化物半導体膜326aと重畳するゲート電極321aとを有する。酸化物半導体膜326aは、ゲート電極321aと重畳する第1の領域327aと、第1の領域327aを挟むドーパントを含む一対の第2の領域329a、329bとを有する。絶縁膜319は、ゲート絶縁膜として機能する。また、酸化物半導体膜326aにおいて、第1の領域327aはチャネル領域として機能し、ドーパントを含む一対の第2の領域329a、329bにおいて、一対の電極317a、317bと接する領域はソース領域及びドレイン領域として機能する。また、一対の電極317a、317bと接しない領域により、ソース−ドレイン耐圧を高めることができる。

【0240】

電界効果移動度が高くオン電流が大きいトランジスタ310cは、デュアルゲート構造であることを特徴とする。なお、トランジスタ310cは、実施の形態1乃至実施の形態7に示す、電界効果移動度が高くオン電流が大きいトランジスタ120c、130c、150c、160c、170c、210cを適宜選択し、デュアルゲート構造とすることで、用いることができる。ここでは、実施の形態7に示すトランジスタ210aの変形構造を用いて説明する。

【0241】

電界効果移動度が高くオン電流が大きいトランジスタ310cは、基板301上に設けられる絶縁膜303と、絶縁膜303上に設けられる第1のゲート電極305cと、絶縁膜303及び第1のゲート電極305cを覆う絶縁膜307と、絶縁膜307上であって、且つ第1のゲート電極305cと重畳する酸化物半導体膜309cと、酸化物半導体膜309cに接する一対の電極317c、317dと、酸化物半導体膜309c、一対の電極317c、317dを覆う絶縁膜319と、絶縁膜319上に形成される第2のゲート電極321cとを有する。絶縁膜307は、第1のゲート絶縁膜として機能し、絶縁膜319は、第2のゲート絶縁膜として機能する。

【0242】

また、トランジスタ310a、310cを覆う絶縁膜331を有することが好ましい。なお、絶縁膜303は設けなくともよい。

【0243】

基板301、絶縁膜303、第1のゲート電極305c、及び絶縁膜307は、それぞれ実施の形態1に示す基板101、絶縁膜103、ゲート電極119c、及びゲート絶縁膜117と同様に形成することができる。

【0244】

酸化物半導体膜326aは、実施の形態1に示す酸化物半導体膜122aに含まれる第1の領域123aと同様に、酸素が添加された領域である。一方、酸化物半導体膜309cは、実施の形態1に示す酸化物半導体膜122cと同様に、酸素が添加されない領域である。また、酸化物半導体膜326aにおいて、一対の第2の領域329a、329bは、実施の形態1に示す一対の第2の領域125a、125bと同様にドーパントが添加されている。

【0245】

一対の電極317a〜317d、絶縁膜319、ゲート電極321a、第2のゲート電極321c、絶縁膜331はそれぞれ、実施の形態1に示す一対の電極115a〜115d、ゲート絶縁膜117、ゲート電極119a、119c、絶縁膜127と同様に形成することができる。

【0246】

ゲート電圧が負のときの電流が小さいトランジスタ310aは、酸化物半導体膜326aに酸素が添加されており、酸化物半導体膜326aにおいて酸素欠損が少ない。このため、しきい値電圧がプラスシフトしており、ノーマリーオフのトランジスタである。一方、電界効果移動度が高くオン電流が大きいトランジスタ310cは、デュアルゲート構造であるため、第1のゲート電極305c及び第2のゲート電極321cに印加する電圧を異ならせることで、しきい値電圧を制御することができる。即ち、しきい値電圧がプラスシフトするノーマリーオフのトランジスタ、しきい値電圧がマイナス方向へシフトするノーマリーオンのトランジスタのしきい値電圧を、半導体装置の回路に合わせて適宜設定することができる。

【0247】

次に、図15に示すトランジスタ310a、310cの作製方法について、図16及び図17を用いて説明する。なお、各図においてA−B断面図は、図15に示すA−B断面図の作製工程を説明し、C−D断面図は、図15に示すC−D断面図の作製工程を説明する。

【0248】

図16(A)に示すように、基板301上に絶縁膜303を形成する。次に、絶縁膜303上に第1のゲート電極305cを形成する。

【0249】

絶縁膜303は、実施の形態1に示す絶縁膜103と同様に形成することができる。

【0250】

第1のゲート電極305cは、実施の形態1に示すゲート電極119cと同様に形成することができる。

【0251】

次に、図16(B)に示すように、第1のゲート電極305c上に絶縁膜307を形成する。絶縁膜307上に、分離された酸化物半導体膜309a、309cを形成する。

【0252】

絶縁膜307及び酸化物半導体膜309a、309cはそれぞれ、実施の形態1に示すゲート絶縁膜117及び酸化物半導体膜107a、107cと同様に形成することができる。

【0253】

次に、後に電界効果移動度が高くオン電流が大きいトランジスタの一部となる酸化物半導体膜309c上にマスク311を形成した後、酸化物半導体膜309aに酸素313を添加する。この結果、酸素欠損を酸化物半導体膜309cより低減した酸化物半導体膜315a(図16(C)参照。)を形成する。この後、マスク311を除去する。なお、酸素313の添加方法に関しては、実施の形態1に示す酸素111の添加方法と同様にすればよい。

【0254】

次に、図16(D)に示すように、絶縁膜307及び酸化物半導体膜315a、309c上に一対の電極317a〜317dを形成する。次に、絶縁膜307、酸化物半導体膜315a、309c、及び一対の電極317a〜317d上に絶縁膜319を形成する。一対の電極317a〜317dは、実施の形態1に示す一対の電極115a〜115dと同様に形成することができる。絶縁膜319は、実施の形態1に示すゲート絶縁膜117と同様に形成する。

【0255】

次に、絶縁膜319上であって、且つ酸化物半導体膜315a、309cと重畳する領域にゲート電極321a、第2のゲート電極321cを形成する。ゲート電極321a、第2のゲート電極321cは、実施の形態1に示すゲート電極119a、119cと同様に形成することができる。

【0256】

次に、図17(A)に示すように、後に電界効果移動度が高くオン電流が大きいトランジスタの一部となる酸化物半導体膜309c上にマスク323を形成した後、ゲート電極321aをマスクとして、酸化物半導体膜315aにドーパント325を添加する処理を行う。この結果、図17(B)に示すように、A−B断面においては、ドーパントを含む一対の第2の領域329a、329bを形成する。ゲート電極321aをマスクにしてドーパントを添加するため、セルフアラインでドーパントを含む一対の第2の領域329a、329b、及びドーパントが添加されない第1の領域327aを形成することができる。また、第1の領域327a、及びドーパントを含む一対の第2の領域329a、329bを酸化物半導体膜326aと示す。

【0257】

この後、加熱処理を行ってもよい。

【0258】

次に、図17(C)に示すように、絶縁膜319、ゲート電極321a、及び第2のゲート電極321c上に、絶縁膜331を形成する。この後、加熱処理を行うことが好ましい。

【0259】

以上の工程により、図15に示すトランジスタ310a、310cを作製することができる。

【0260】

本実施の形態により、脱水素化工程の後、選択的に酸化物半導体膜へ酸素を添加することで、同一基板上に、ゲート電圧が負のときの電流が小さいトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタを作製することができる。

【0261】

(実施の形態9)

本実施の形態では、先の実施の形態に示す半導体装置の一例として、記憶装置を示す。

【0262】

図19に、記憶装置の具体的な構成の一例をブロック図で示す。なお、図19に示すブロック図では、記憶装置内の回路を機能ごとに分類し、互いに独立したブロックとして示しているが、実際の回路は機能ごとに完全に切り分けることが難しく、一つの回路が複数の機能に係わることもあり得る。

【0263】

図19に示す記憶装置901は、メモリセルアレイ903と、駆動回路905とを有する。駆動回路905は、入出力バッファ907と、ワード線の電位を制御するワード線駆動回路909と、メモリセルにおけるデータの書き込み及び読み出しを制御するデータ線駆動回路911と、入出力バッファ907、ワード線駆動回路909、及びデータ線駆動回路911の動作を制御する制御回路913を有している。

【0264】

また、ワード線駆動回路909は、ローデコーダ915を有する。なお、ワード線駆動回路909は、ローデコーダ915の他に、レベルシフタ及びバッファを有している。また、データ線駆動回路911は、カラムデコーダ917及び読み出し回路919を有する。なお、データ線駆動回路911は、カラムデコーダ917及び読み出し回路919の他に、セレクタ及びレベルシフタを有している。

【0265】

なお、メモリセルアレイ903、入出力バッファ907、ワード線駆動回路909、データ線駆動回路911、制御回路913は、全て一の基板を用いて形成されていてもよいし、いずれか1つ又は全てが互いに異なる基板を用いて形成されていても良い。

【0266】

異なる基板を用いている場合、FPC(Flexible Printed Circuit)などを介して電気的な接続を確保することができる。この場合、駆動回路905の一部がFPCにCOF(Chip On Film)法を用いて接続されていてもよい。或いは、COG(Chip On Glass)法を用いて、電気的な接続を確保することができる。

【0267】

記憶装置901に、メモリセルアレイ903のアドレスAx、アドレスAyを情報として含む信号ADが入力されると、制御回路913は、列方向のアドレスAxをデータ線駆動回路911に送り、行方向のアドレスAyをワード線駆動回路909に送る。また、制御回路913は、入出力バッファ907を介して記憶装置901に入力されたデータを情報として含む信号DATAを、データ線駆動回路911に送る。

【0268】

メモリセルアレイ903におけるデータの書き込み動作、読み出し動作の選択は、制御回路913に供給される信号RE(Read enable)、信号WE(Write enable)などによって選択される。更に、メモリセルアレイ903が複数存在する場合、制御回路913に、メモリセルアレイ903を選択するための信号CE(Chip enable)が入力されていても良い。この場合、信号RE、信号WEにより選択される動作が、信号CEにより選択されたメモリセルアレイ903において実行される。

【0269】

メモリセルアレイ903では、信号WEによって書き込み動作が選択されると、制御回路913からの指示に従って、ワード線駆動回路909が有するローデコーダ915において、アドレスAyに対応するメモリセルを選択するための信号が生成される。当該信号は、レベルシフタによって振幅が調整された後、バッファを介してメモリセルアレイ903に入力される。一方、データ線駆動回路911では、制御回路913からの指示に従って、カラムデコーダ917において選択されたメモリセルのうち、アドレスAxに対応するメモリセルを選択するための信号が生成される。当該信号は、レベルシフタによって振幅が調整された後、セレクタに入力される。セレクタでは、入力された信号に従って信号DATAをサンプリングし、アドレスAx、アドレスAyに対応するメモリセルにサンプリングした信号を入力する。

【0270】

また、メモリセルアレイ903では、信号REによって読み出し動作が選択されると、制御回路913からの指示に従って、ワード線駆動回路909が有するローデコーダ915において、アドレスAyに対応するメモリセルを選択するための信号が生成される。当該信号は、レベルシフタによって振幅が調整された後、バッファを介してメモリセルアレイ903に入力される。一方、読み出し回路919では、制御回路913からの指示に従って、ローデコーダ915により選択されたメモリセルのうち、アドレスAxに対応するメモリセルを選択する。そして、アドレスAx、アドレスAyに対応するメモリセルに記憶されているデータを読み出し、該データを情報として含む信号を生成する。

【0271】

なお、データ線駆動回路911は、信号DATAを一時的に記憶することができるページバッファ、データの読み出し時においてデータ線に電位VRを予め与えるプリチャージ回路などを有していても良い。

【0272】

次に、ローデコーダ及びカラムデコーダの構成について、図20を用いて説明する。ここでは、カラムデコーダ917を用いて説明する。ここでは、一例として4本のビット線及び4本のワード線で構成される256ビットの記憶装置のカラムデコーダ917について説明する。なお、ビット数に合わせてビット線及びワード線の本数を適宜選択することが可能である。

【0273】

カラムデコーダ917はアドレス線S1、S1B、S2、S2B、S3、S3B、S4、S4Bよりアドレス信号をNAND回路931a、931bに入力する。なお、S1B、S2B、S3B、S4Bにはそれぞれ、S1、S2、S3、S4の反転信号が入力される。また、NAND回路931a、931bから出力される信号を、NOR回路933を通して出力端子out1〜out16(図示せず)に出力する。図20の構成により、カラムデコーダ917において選択されたメモリセルのうち、アドレスAxに対応するメモリセルを選択するための信号が生成される。当該信号は、レベルシフタによって振幅が調整された後、セレクタに入力される。セレクタでは、入力された信号に従って信号DATAをサンプリングし、アドレスAx、アドレスAyに対応するメモリセルにサンプリングした信号を入力する。

【0274】

なお、ローデコーダ915もカラムデコーダ917と同様の回路構成とすることが可能であり、ローデコーダ915において、アドレスAyに対応するメモリセルを選択するための信号が生成される。当該信号は、レベルシフタによって振幅が調整された後、バッファを介してメモリセルアレイ903に入力される。

【0275】

図19に示す駆動回路905、更にはローデコーダ915及びカラムデコーダ917は、メモリセルアレイ903のビット線及びワード線への信号書込のために高速処理が必要である。このため、先の実施の形態において、トランジスタ120c、130c、150c、160c、170c、210c、310cに示すような、電界効果移動度が高くオン電流が大きいトランジスタを用いて駆動回路905、更にはローデコーダ915及びカラムデコーダ917を構成することで、記憶装置の高速動作が可能である。

【0276】

次に、メモリセルアレイ903の構造について、図21を用いて説明する。

【0277】

図21には、いわゆるDRAM(Dynamic Random Access Memory)に相当する構成の記憶装置におけるメモリセルアレイを示す。図21に示すメモリセルアレイ903は、m(m≧2)本のビット線BL、及びn(n≧2)本のワード線WLを有する。また、m×n個のメモリセル921がマトリクス状に配列されている。

【0278】

メモリセル921は、トランジスタ923及び容量素子925で構成されている。トランジスタ923のゲート電極は、ワード線WLと接続されている。また、トランジスタ923のソース電極又はドレイン電極の一方は、ビット線BLと接続されており、トランジスタ923のソース電極又はドレイン電極の他方は、容量素子925の電極の一方と接続されている。また、容量素子925の電極の他方は容量線と接続され、一定の電位が与えられている。

【0279】

メモリセル921に含まれるトランジスタ923として、先の実施の形態に示すゲート電圧が負のときの電流が小さいトランジスタ120a、130a、150a、160a、170a、210a、310aを適宜用いることで、容量素子925に書き込まれたデータを長時間の保持することが可能であり、記憶装置を実質的な不揮発性記憶装置として使用することが可能になる。

【0280】

なお、図21においては、半導体装置としてDRAMを用いて説明したが、先の実施の形態に示すゲート電圧が負のときの電流が小さいトランジスタ120a、130a、150a、160a、170a、210a、310aを適宜用いて作製したメモリ素子を用いれば、SRAM(Static Random Access Memory)やその他の記憶装置とすることができる。

【0281】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0282】

(実施の形態10)

本実施の形態では、半導体装置の一例である表示装置において、同一基板上に少なくとも駆動回路の一部と、画素部に配置するトランジスタを作製する例について以下に説明する。

【0283】

画素部に配置するトランジスタは、画素を構成する画素電極の電位を保つため、リーク電流が小さいことが好ましい。このため、画素部に配置するトランジスタを先の実施の形態に示すゲート電圧が負のときの電流が小さいトランジスタ120a、130a、150a、160a、170a、210a、310aを適宜用いる。また、駆動回路のうち、nチャネル型TFTで構成することができる駆動回路の一部を、先の実施の形態に示す電界効果移動度が高くオン電流が大きいトランジスタ120c、130c、150c、160c、170c、210c、310cを適宜用いると共に、画素部のトランジスタと同一基板上に形成する。このように、画素部や駆動回路に先の実施の形態に示すトランジスタを用いることにより、信頼性の高いと共に、高速動作が可能であり、消費電力の低い表示装置を提供することができる。

【0284】

アクティブマトリクス型表示装置の一例を図22に示す。表示装置の基板600上には、画素部601、第1の走査線駆動回路602、第2の走査線駆動回路603、信号線駆動回路604を有する。画素部601には、複数の信号線が信号線駆動回路604から延伸して配置され、複数の走査線が第1の走査線駆動回路602、及び第2の走査線駆動回路603から延伸して配置されている。なお、走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に設けられている。また、表示装置の基板600はFPC(Flexible Printed Circuit)等の接続部を介して、タイミング制御回路(コントローラ、制御ICともいう)に接続されている。

【0285】

図22では、第1の走査線駆動回路602、第2の走査線駆動回路603、信号線駆動回路604は、画素部601と同じ基板600上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板600外部に駆動回路を設けた場合、配線を延伸させる必要が生じ、配線間の接続数が増える。同じ基板600上に駆動回路を設けた場合、その配線間の接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。

【0286】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0287】

(実施の形態11)

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、又はテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。先の実施の形態で説明した半導体装置を具備する電子機器の例について説明する。

【0288】

図23は、携帯型の情報端末であり、本体1001、筐体1002、表示部1003a、1003bなどによって構成されている。表示部1003bはタッチパネルとなっており、表示部1003bに表示されるキーボードボタン1004を触れることで画面操作や、文字入力を行うことができる。勿論、表示部1003aをタッチパネルとして構成してもよい。先の実施の形態で示したトランジスタをスイッチング素子として液晶パネルや有機発光パネルを作製して表示部1003a、1003bに適用することにより、携帯型の情報端末の表示部の信頼性を向上させることができる。

【0289】

図23は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。

【0290】

また、図23に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0291】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【実施例1】

【0292】

本実施例では、酸素が添加された酸化物半導体膜を有するトランジスタ(以下、トランジスタ1と示す。)と、酸素が添加されない酸化物半導体膜を有するトランジスタ(以下、トランジスタ2と示す。)の電気特性について、図2、図7、図12、図17、及び図18を用いて説明する。本実施例では、実施の形態5に示すトランジスタを作製した。

【0293】

はじめに、トランジスタ1、トランジスタ2の作製工程について、説明する。

【0294】

図2(A)に示すように基板101上に絶縁膜103を形成した。

【0295】

基板101としては、シリコンウェハを用いた。

【0296】

塩化水素を含む酸素雰囲気において、950度で基板101を加熱して、基板101表面に、厚さ100nmの塩素を含む酸化シリコン膜を形成した後、基板101の一方の面の塩素を含む酸化シリコン膜を除去した。次に、基板101の他方の面、即ち塩素を含む酸化シリコン膜表面に逆スパッタ処理をした後、塩素を含む酸化シリコン膜上に厚さ330nmの酸化シリコン膜をスパッタリング法により形成した。このとき、スパッタリング条件としては、酸化シリコンターゲットを用い、スパッタガスとして50sccmの酸素を圧力0.4Paのチャンバーに導入し、基板温度を100度とし、基板とターゲット間隔を60mmとして、供給電力を1.5kWとした。以上の工程により、基板101上に絶縁膜103を形成した。

【0297】

次に、絶縁膜103の表面を平坦化処理した。ここでは、CMP処理により絶縁膜103の表面を30nm研磨した。

【0298】

次に、スパッタリング法により、厚さ15nmのIn−Sn−Zn系酸化物膜を形成した後、加熱処理を行って、絶縁膜103から酸素をIn−Sn−Zn系酸化物膜に拡散させ、酸素欠損を低減した酸化物半導体膜105を形成した。しかしながら、当該加熱処理だけでは、酸化物半導体膜105には酸素欠損が残存する。このときのスパッタリング条件としては、In:Sn:Zn=1:1:1のターゲットを用い、スパッタガスとして流量15sccmの酸素を圧力0.4Paのチャンバーに導入し、基板温度を200度とし、供給電力を0.1kWとした。また、加熱処理としては、250度のチャンバーにおいて窒素雰囲気で加熱した後、酸素雰囲気で加熱した。

【0299】

次に、酸化物半導体膜105上にフォトリソグラフィ工程によりマスクを形成した後、酸化物半導体膜105を選択的にエッチングして、図2(B)に示すように、酸化物半導体膜107a、107cを形成した。ここでは、ICPエッチング装置を用いてエッチングを行った。エッチング条件として、ICP電極に450Wの電力を供給し、バイアス電極に100Wの電力を供給し、チャンバー圧力を1.9Paとし、流量60sccmの三塩化ボロン及び流量20sccmの塩素をエッチングガスとして用いた。

【0300】

次に、図7(A)に示すように、酸化物半導体膜107a、107c上に一対の電極115a〜115dを形成した。ここでは、酸化物半導体膜107a、107c上に厚さ100nmのタングステン膜をスパッタリング法により形成した後、タングステン膜上にフォトリソグラフィ工程によりマスクを形成し、タングステン膜を選択的にエッチングして、一対の電極115a〜115dを形成した。この後、マスクを除去した。

【0301】

なお、タングステン膜の成膜に用いたスパッタリング条件としては、タングステンターゲットを用い、スパッタガスとして流量80sccmの加熱したアルゴンを圧力0.8Paのチャンバーに導入し、基板温度を230度とし、供給電力を1kWとした。

【0302】

また、タングステン膜をエッチングするエッチング条件としては、ICP電極に500Wの電力を供給し、バイアス電極に150Wの電力を供給し、チャンバー圧力を1.0Paとし、流量25sccmの四塩化炭素、流量25sccmの塩素、及び流量10sccmの酸素をエッチングガスとして用いた。

【0303】

次に、酸化物半導体膜107a、107c及び一対の電極115a〜115d上にゲート絶縁膜117を形成した。ここでは、ゲート絶縁膜117として厚さ100nmの酸化窒化シリコン膜をCVD法により形成した。このときのプラズマCVD法の成膜条件は、流量1sccmのシラン、流量800sccmの一酸化二窒素を原料ガスとして、圧力40Paのチャンバーに導入し、60MHzの高周波電源の電力を150Wとし、基板温度を400度とし、電極間隔距離を28mmとした。

【0304】

次に、図7(B)に示すように、フォトリソグラフィ工程によりマスク109を形成した後、後にトランジスタ1となる酸化物半導体膜107aに酸素を添加した。ここでは、イオン注入装置を用い、電子エネルギーを25kV、酸素ドーズ量を1×1015cm−2とした。なお、後にトランジスタ2となる酸化物半導体膜107cには酸素を添加しなかった。この結果、図12(A)に示すように、後にトランジスタ1となる領域においては、酸素が添加された領域143aと、一対の電極115a、115bと重畳し、酸素が添加されない一対の領域145a、145bとを有する酸化物半導体膜142aを形成した。

【0305】

次に、図12(B)に示すように、ゲート絶縁膜117上にゲート電極171a、171cを形成した後、絶縁膜127を形成した。

【0306】

ゲート電極171a、171cは、ゲート絶縁膜117上に、スパッタリング方法により厚さ30nmの窒化タンタル膜と、厚さ135nmのタングステン膜を積層形成した後、タングステン膜上にフォトリソグラフィ工程によりマスクを形成し、窒化タンタル膜及びタングステン膜を選択的にエッチングして形成した。

【0307】

なお、窒化タンタル膜の成膜に用いたスパッタリング条件としては、窒化タンタルターゲットを用い、スパッタガスとして流量50sccmのアルゴン及び流量10sccmの窒素を圧力0.6Paのチャンバーに導入し、供給電力を1kWの電力とした。また、タングステン膜の成膜に用いたスパッタリング条件としては、タングステンターゲットを用い、スパッタガスとして流量100sccmの加熱したアルゴンを圧力2Paのチャンバーに導入し、基板温度を230度とし、供給電力を4kWとした。

【0308】

タングステン膜のエッチング条件として、ICP電極に3000Wの電力を供給し、バイアス電極に110Wの電力を供給し、チャンバー圧力を0.67Paとし、流量45sccmの塩素、流量55sccmの四フッ化メタン、流量55sccmの酸素をエッチングガスとして用いた。また、窒化タンタル膜のエッチング条件として、ICP電極に2000Wの電力を供給し、バイアス電極に50Wの電力を供給し、チャンバー圧力を1Paとし、流量100sccmの塩素をエッチングガスとして第1のエッチングを行った後、ICP電極に1000Wの電力を供給し、バイアス電極に25Wの電力を供給し、チャンバー圧力を2Paに変更して第2のエッチングを行った。

【0309】

絶縁膜127は、厚さ50nmの酸化アルミニウム膜と、厚さ300nmの酸化窒化シリコン膜を積層形成した。

【0310】

なお、酸化アルミニウム膜の成膜に用いたスパッタリング条件としては、酸化アルミニウムターゲットを用い、スパッタガスとして流量25sccmのアルゴン及び流量25sccmの酸素を圧力0.4Paのチャンバーに導入し、ターゲット及び基板間隔を60mm、基板温度を250度、供給電力を2.5kWとした。また、酸化窒化シリコン膜のプラズマCVD法の成膜条件は、流量5sccmのシラン、流量1000sccmの一酸化二窒素を原料ガスとして、圧力133Paのチャンバーに導入し、13.56MHzの高周波電源の電力を35Wとし、基板温度を325度とし、電極間隔距離を20mmとした。

【0311】

この後、絶縁膜127上にフォトリソグラフィ工程によりマスクを形成した後、ゲート絶縁膜117及び絶縁膜127を選択的にエッチングして、開口部を形成した。次に、当該開口部に一対の電極を形成した。

【0312】

ゲート絶縁膜117及び絶縁膜127をエッチングするエッチング条件としては、ICP電極に475Wの電力を供給し、バイアス電極に300Wの電力を供給し、チャンバー圧力を3.5Paとし、流量22.5sccmの三フッ化メタン、流量127.5sccmのヘリウム、及び流量5sccmのメタンをエッチングガスとして用いた。

【0313】

一対の電極は、厚さ50nmのチタン膜、厚さ100nmのアルミニウム膜、及び厚さ50nmのチタン膜を順に積層形成した後、フォトリソグラフィ工程によりマスクを形成し、当該マスクを用いて選択的にエッチングして形成した。

【0314】

なお、チタン膜の成膜に用いたスパッタリング条件としては、チタンターゲットを用い、スパッタガスとして流量20sccmのアルゴンを圧力0.1Paのチャンバーに導入し、基板温度を室温とし、供給電力を12kWの電力とした。また、アルミニウム膜の成膜に用いたスパッタリング条件としては、アルミニウムターゲットを用い、スパッタガスとして流量50sccmのアルゴンを圧力0.4Paのチャンバーに導入し、基板温度を室温とし、供給電力を1kWの電力とした。

【0315】

チタン膜、アルミニウム膜、及びチタン膜のエッチング条件としては、ICP電極に450Wの電力を供給し、バイアス電極に100Wの電力を供給し、チャンバー圧力を1.9Paとし、流量60sccmの三塩化ボロン、流量20sccmの塩素をエッチングガスとして用いた。

【0316】

以上の工程により、トランジスタ1及びトランジスタ2を作製した。

【0317】

図18(A)は、トランジスタ1の電気特性であり、図18(B)は、トランジスタ2の電気特性である。図18において、左縦軸はドレイン電流を表し、右縦軸は電界効果移動度を表し、横軸はゲート電圧を表す。

【0318】

本実施例の薄膜トランジスタの一対の電極115a、115b、及び一対の電極115c、115dの対向間隔(即ち、チャネル長方向における一対の電極の距離)を9.9μm、一対の電極115a、115b、及び一対の電極115c、115dの対向幅(即ち、チャネル幅方向において一対の電極が対向する距離)を10.3μmとした。また、ゲート絶縁膜117の厚さを100nm、平均誘電率を4.1として電界効果移動度を計算した。

【0319】

また、ドレイン電圧(Vd)が0.1Vで、ゲート電圧(Vg)が3Vのときのオン電流(Ion_0.1と示す。)、ドレイン電圧(Vd)が3Vで、ゲート電圧(Vg)が3Vのときのオン電流(Ion_3と示す。)、ドレイン電圧(Vd)が0.1Vで、ゲート電圧(Vg)が−3Vのときの電流(Ioff_0.1と示す。)、ドレイン電圧(Vd)が3Vで、ゲート電圧(Vg)が−3Vのときの電流(Ioff_3と示す。)、しきい値電圧(Vthと示す。)、ドレイン電圧(Vd)が0.1Vのときの電界効果移動度(μFE_linと示す。)、ドレイン電圧(Vd)が3Vのときの電界効果移動度(μFE_satと示す。)を表1に示す。

【0320】

【表1】

【0321】

図18及び表1より、酸素が添加された酸化物半導体膜を有するトランジスタ(トランジスタ1)は、ゲート電圧が0V以下における電流が小さいことが分かる。また、しきい値電圧がプラスであることが分かる。即ち、ノーマリーオフのトランジスタである。一方、酸素が添加されない酸化物半導体膜を有するトランジスタ(トランジスタ2)は、トランジスタ1と比較して、オン電流が大きく電界効果移動度(Vd=3Vを除く)が高いことが分かる。

【技術分野】

【0001】

トランジスタなどの半導体素子を含む回路を有する半導体装置及びその作製方法に関する。例えば、電源回路に搭載されるパワーデバイス、メモリ、サイリスタ、コンバータ、イメージセンサなどを含む半導体集積回路、液晶表示パネルに代表される電気光学装置、発光素子を有する発光表示装置等を部品として搭載した電子機器に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、発光表示装置、半導体回路及び電子機器は全て半導体装置である。

【背景技術】

【0003】

液晶表示装置に代表されるように、ガラス基板等に形成されるトランジスタはアモルファスシリコン、多結晶シリコンなどによって構成されている。アモルファスシリコンを用いたトランジスタは電界効果移動度が低いもののガラス基板の大面積化に対応することができる。また、多結晶シリコンを用いたトランジスタの電界効果移動度は高いがガラス基板の大面積化には適していないという欠点を有している。

【0004】

シリコンを用いたトランジスタに対して、酸化物半導体を用いてトランジスタを作製し、電子デバイスや光デバイスに応用する技術が注目されている。例えば、酸化物半導体として、酸化亜鉛、In−Ga−Zn−O系酸化物を用いてトランジスタを作製し、表示装置の画素のスイッチング素子などに用いる技術が特許文献1及び特許文献2で開示されている。

【0005】

ところで、特に酸化物半導体においては、水素がキャリアの供給源となることが指摘されている。そのため、酸化物半導体の形成時に水素が混入しないような措置を講じることが求められる。また、酸化物半導体のみならず、酸化物半導体に接するゲート絶縁膜の水素を低減することで、しきい値電圧の変動を低減している(特許文献3参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−123861号公報

【特許文献2】特開2007−96055号公報

【特許文献3】特開2009−224479号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、酸化物半導体を用いたトランジスタにおいて、高い電界効果移動度及びオン電流が大きいと共に、ゲート電圧が負のときの電流が小さいトランジスタを作製することは困難である。このため、電界効果移動度が高くオン電流が大きいトランジスタを用いて作製された半導体装置は、トランジスタのゲート電圧が負のときの電流起因による消費電力が上昇してしまうという問題がある。一方、ゲート電圧が負のときの電流が小さいトランジスタを用いて作製された半導体装置は、トランジスタの電界効果移動度が低くオン電流が小さいため、高速動作が困難である、という問題がある。

【0008】

そこで、本発明の一態様は、高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供することを課題の一とする。

【課題を解決するための手段】

【0009】

本発明の一態様は、酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流の低いトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタを作り分けることを特徴とする。代表的には、ゲート電圧が負のときの電流が小さいトランジスタで構成される回路と、電界効果移動度が高くオン電流が大きいトランジスタで構成される回路とを有する。電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタは、酸化物半導体膜、該酸化物半導体膜と重畳するゲート電極、及び酸化物半導体膜及びゲート電極の間に設けられるゲート絶縁膜を有する。また、それぞれの酸化物半導体膜において、ゲート電極と重畳する第1の領域を有する。ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜における第1の領域と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜における第1の領域とが、酸素濃度が異なることを特徴とする。好ましくは、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜における第1の領域と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜における第1の領域は、酸素濃度が低いことを特徴とする。

【0010】

なお、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜には酸素が添加され、その酸化物半導体膜中に添加された酸素濃度は5×1019/cm3以上5×1021/cm3以下である。

【0011】

また、電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタにおける酸化物半導体膜は、ゲート電極と重畳する第1の領域と、該第1の領域を挟む一対の第2の領域とを有する。または、ゲート電極と重畳する第1の領域と、該第1の領域を挟む一対の第2の領域と、該一対の第2の領域を挟む一対の第3の領域とを有する。

【0012】

上記一対の第2の領域及び上記一対の第3の領域には、ドーパントが含まれており、該ドーパントの濃度は、5×1018atoms/cm3以上1×1022atoms/cm3以下、好ましくは5×1018atoms/cm3以上5×1019atoms/cm3未満である。

【0013】

電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタはそれぞれ、シングルゲート構造であってもよい。または、ゲート電圧が負のときの電流が小さいトランジスタは、シングルゲート構造であり、電界効果移動度が高くオン電流が大きいトランジスタは、デュアルゲート構造であってもよい。デュアルゲート構造のトランジスタは、2つの電極に異なる電圧を印加することで、しきい値電圧を制御することができる。

【0014】

電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタは、酸化物半導体膜に接する一対の電極を有する。また、電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタは、スタガ型であってもよい。または、電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタは、コプレナー型であってもよい。

【0015】

また、酸化物半導体膜は、In、Ga、Sn及びZnから選ばれた一種以上の元素を含む。

【0016】

酸化物半導体膜を有するトランジスタにおいて、ゲート電極と重畳する第1の領域の酸素濃度が異なるトランジスタを作製する。第1の領域の酸素濃度が高いトランジスタ、即ち、化学量論的組成比より多くの酸素を含む酸化物半導体膜を有するトランジスタは、酸化物半導体膜に含まれる酸素欠損量が少ない。このため、酸素欠損に起因するエネルギーギャップ中のドナー準位が低い、または実質的にない。この結果、オフ状態において、リーク電流が発生しにくく、トランジスタのゲート電圧が負のときの電流を低減することができる。一方、第1の領域の酸素濃度が低いトランジスタ、即ち、化学量論的組成比より少ない酸素を含む酸化物半導体膜を有するトランジスタは、酸化物半導体膜の酸素欠損量が含まれるため、オン状態においてキャリアが発生しやすくなり、トランジスタの電界効果移動度を高く、オン電流を大きくすることができる。このため、半導体装置を構成する回路の特性に合わせて、トランジスタを作り分けることで、具体的には高速動作が必要な回路においては、電界効果移動度が高くオン電流が大きいトランジスタを用い、リーク電流の少ない回路においては、ゲート電圧が負のときの電流が小さいトランジスタを用いることで、高速動作が可能であり、且つ消費電力の低い半導体装置を作製することができる。

【発明の効果】

【0017】

本発明の一態様によって、酸化物半導体膜の酸素欠損量の多いトランジスタ及び酸素欠損量の少ないトランジスタをそれぞれ作製することができる。この結果、電界効果移動度が高くオン電流が大きいトランジスタ、並びにゲート電圧が負のときの電流が小さいトランジスタを作製することができる。更には、当該トランジスタを回路の機能に合わせて作り分けることで、高速動作が可能であり、且つ消費電力の低い半導体装置を作製することができる。

【図面の簡単な説明】

【0018】

【図1】本発明の一態様に係る半導体装置を説明する断面図である。

【図2】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図3】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図4】本発明の一態様に係る半導体装置を説明する断面図である。

【図5】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図6】本発明の一態様に係る半導体装置を説明する断面図である。

【図7】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図8】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図9】本発明の一態様に係る半導体装置を説明する断面図である。

【図10】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図11】本発明の一態様に係る半導体装置を説明する断面図である。

【図12】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図13】本発明の一態様に係る半導体装置を説明する断面図である。

【図14】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図15】本発明の一態様に係る半導体装置を説明する断面図である。

【図16】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図17】本発明の一態様に係る半導体装置の作製方法を説明する断面図である。

【図18】本発明の一態様に係るトランジスタの電気特性を説明する図である。

【図19】本発明の一態様に係る記憶装置の構成を示すブロック図である。

【図20】本発明の一態様に係る記憶装置を説明する回路図である。

【図21】本発明の一態様に係る記憶装置を説明する回路図である。

【図22】本発明の一態様を示すアクティブマトリクス型表示装置を説明する図である。

【図23】本発明の一態様を示す電子機器の外観図である。

【発明を実施するための形態】

【0019】

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分または同様な機能を有する部分には、同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0020】

なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0021】

また、本明細書にて用いる第1、第2、第3などの用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。

【0022】

(実施の形態1)

本実施の形態では、ゲート電圧が負のときの電流が小さいトランジスタと、電界効果移動度が高くオン電流が大きいトランジスタとを有する半導体装置の構造及び作製方法について、図1乃至図3を用いて説明する。本実施の形態のトランジスタは、コプレナー型のトップゲートトランジスタであって、一対の電極が酸化物半導体膜の側面及び表面の一部を覆うことを特徴とする。

【0023】

図1は、本実施の形態に示す半導体装置の断面図である。図1に示す半導体装置は、ゲート電圧が負のときの電流が小さいトランジスタ120aと、電界効果移動度が高くオン電流が大きいトランジスタ120cとを有する。

【0024】

ゲート電圧が負のときの電流が小さいトランジスタ120aは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜122aと、酸化物半導体膜122aに接する、ソース電極及びドレイン電極として機能する一対の電極115a、115bと、酸化物半導体膜122aを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜122aと重畳するゲート電極119aとを有する。酸化物半導体膜122aは、ゲート電極119aと重畳する第1の領域123aと、第1の領域123aを挟むドーパントを含む一対の第2の領域125a、125bとを有する。なお、酸化物半導体膜122aにおいて、第1の領域123aはチャネル領域として機能し、ドーパントを含む一対の第2の領域125a、125bにおいて、一対の電極115a、115bと接する領域はソース領域及びドレイン領域として機能する。また、一対の電極115a、115bと接しない領域により、ソース−ドレイン耐圧を高めることができる。

【0025】

電界効果移動度が高くオン電流が大きいトランジスタ120cは、基板101上に設けられる絶縁膜103と、絶縁膜103上に設けられる酸化物半導体膜122cと、酸化物半導体膜122cに接する、ソース電極及びドレイン電極として機能する一対の電極115c、115dと、酸化物半導体膜122cを覆うゲート絶縁膜117と、ゲート絶縁膜117上であって、且つ酸化物半導体膜122cと重畳するゲート電極119cとを有する。酸化物半導体膜122cは、ゲート電極119cと重畳する第1の領域123cと、第1の領域123cを挟むドーパントを含む一対の第2の領域125c、125dとを有する。なお、酸化物半導体膜122cにおいて、第1の領域123cはチャネル領域として機能し、ドーパントを含む一対の第2の領域125c、125dにおいて、一対の電極115c、115dと接する領域はソース領域及びドレイン領域として機能する。また、一対の電極115c、115dと接しない領域により、ソース−ドレイン耐圧を高めることができる。

【0026】

また、トランジスタ120a、120cを覆う絶縁膜127を有することが好ましい。

【0027】

本実施の形態においては、トランジスタ120aを構成する酸化物半導体膜122aには、化学量論的組成比に対し過剰な酸素が含まれている。この場合、過剰な酸素は、酸化物半導体の格子間に存在する場合もある。酸化物半導体膜122aに添加された酸素濃度は、5×1019/cm3以上5×1021/cm3以下である。

【0028】

酸化物半導体膜122aに含まれる酸素欠損は、酸化物半導体膜122cと比較して少ない。このため、酸素欠損に起因するエネルギーギャップ中のドナー準位が低い、または実質的にない。この結果、トランジスタ120aはゲート電圧が負のときの電流が小さいトランジスタである。一方、酸化物半導体膜122cは、酸素欠損を含む。このため、トランジスタ120cでは、オン状態において、キャリアが発生しやすい。このため、トランジスタ120cは、電界効果移動度が高くオン電流が大きいトランジスタである。

【0029】

基板101の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板101として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板101として用いてもよい。

【0030】

また、基板101として、可撓性基板を用いてもよい。基板101と絶縁膜103の間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板101より分離し、他の基板に転載するのに用いることができる。その際、半導体装置は耐熱性の劣る基板や可撓性の基板にも転載できる。

【0031】

絶縁膜103は、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム等を適宜用いることができる。

【0032】

また、絶縁膜103は、加熱により酸素の一部が脱離する酸化絶縁膜を用いて形成してもよい。加熱により酸素の一部が脱離する酸化絶縁膜としては、化学量論比を満たす酸素よりも多くの酸素を含む酸化絶縁膜を用いることが好ましい。加熱により酸素の一部が脱離する酸化絶縁膜は、加熱により酸素が脱離するため、加熱により酸化物半導体膜に酸素を拡散させることができる。加熱により酸素の一部が脱離する酸化絶縁膜の代表例としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム等がある。

【0033】

絶縁膜103は、50nm以上、好ましくは200nm以上500nm以下とする。絶縁膜103を厚くすることで、絶縁膜として加熱により酸素の一部が脱離する酸化絶縁膜を用いる場合、絶縁膜103の酸素脱離量を増加させることができると共に、絶縁膜103及び後に形成される酸化物半導体膜との界面における界面準位を低減することが可能である。

【0034】

ここで、「加熱により酸素の一部が脱離する」とは、TDS(Thermal Desorption Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の放出量が1.0×1018atoms/cm3以上、好ましくは3.0×1020atoms/cm3以上であることをいう。

【0035】

ここで、TDS分析にて、酸素原子に換算しての酸素の脱離量の測定方法について、以下に説明する。

【0036】

TDS分析したときの気体の脱離量は、スペクトルの積分値に比例する。このため、絶縁膜のスペクトルの積分値と、標準試料の基準値に対する比とにより、気体の放出量を計算することができる。標準試料の基準値とは、所定の原子を含む試料の、スペクトルの積分値に対する原子の密度の割合である。

【0037】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、及び絶縁膜のTDS分析結果から、絶縁膜の酸素分子の脱離量(NO2)は、数式1で求めることができる。ここで、TDS分析で得られる質量数32で検出されるスペクトルの全てが酸素分子由来と仮定する。質量数32のものとしてCH3OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子及び質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0038】

【数1】

【0039】

NH2は、標準試料から脱離した水素分子を密度で換算した値である。SH2は、標準試料をTDS分析したときのスペクトルの積分値である。ここで、標準試料の基準値を、NH2/SH2とする。SO2は、絶縁膜をTDS分析したときのスペクトルの積分値である。αは、TDS分析におけるスペクトル強度に影響する係数である。数式1の詳細に関しては、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の脱離量は、電子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料として1×1016atoms/cm3の水素原子を含むシリコンウェハを用いて測定する。

【0040】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の脱離量についても見積もることができる。

【0041】

なお、NO2は酸素分子の脱離量である。絶縁膜においては、酸素原子に換算したときの酸素の放出量は、酸素分子の脱離量の2倍となる。

【0042】

上記構成において、加熱により酸素放出される絶縁膜は、酸素が過剰な酸化シリコン(SiOX(X>2))であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2))とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数及び酸素原子数は、ラザフォード後方散乱法により測定した値である。

【0043】

絶縁膜103から酸化物半導体膜122a、122cに酸素が供給されることで、絶縁膜103及び酸化物半導体膜122a、122cの界面準位を低減できる。この結果、トランジスタの動作などに起因して生じうる電荷などが、上述の絶縁膜103及び酸化物半導体膜122a、122cの界面に捕獲されることを抑制することができ、電気特性の劣化の少ないトランジスタを得ることができる。

【0044】

さらに、酸化物半導体膜122a、122cの酸素欠損に起因して電荷が生じる場合がある。一般に、酸化物半導体膜の酸素欠損は、一部がドナーとなりキャリアである電子を生じる。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。この傾向はバックチャネル側で生じる酸素欠損において顕著である。なお、本明細書におけるバックチャネルとは、図1に示す酸化物半導体膜122a、122cの第1の領域123a、123cにおいて絶縁膜103との界面近傍を指す。絶縁膜103から酸化物半導体膜122a、122cに酸素が十分に供給されることにより、しきい値電圧がマイナス方向へシフトする要因である、酸化物半導体膜122a、122cの酸素欠損を低減することができる。

【0045】

酸化物半導体膜122a、122cとしては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてジルコニウム(Zr)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0046】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0047】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属酸化物であるIn−Ga−Zn系酸化物(IGZOとも表記する。)、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−Zr−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0048】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0049】

また、酸化物半導体として、InMO3(ZnO)m(m>0、且つ、mは整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In2SnO5(ZnO)n(n>0、且つ、nは整数)で表記される材料を用いてもよい。

【0050】

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)あるいはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子数比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子数比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

【0051】

しかし、これらに限られず、必要とする半導体特性及び電気特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0052】

なお、酸化物半導体膜122a、122cに形成することが可能な金属の酸化物は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタがオフ状態のときに流れる電流(オフ電流)を低減することができる。

【0053】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0054】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0055】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0056】

なお、Raとは、JIS B0601:2001(ISO4287:1997)で定義されている算術平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」で表現でき、以下の式にて定義される。

【0057】

【数2】

【0058】

ここで、指定面とは、粗さ計測の対象となる面であり、座標(x1,y1,f(x1,y1)),(x1,y2,f(x1,y2)),(x2,y1,f(x2,y1)),(x2,y2,f(x2,y2))の4点で表される四角形の領域とし、指定面をxy平面に投影した長方形の面積をS0、基準面の高さ(指定面の平均高さ)をZ0とする。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて測定可能である。

【0059】

また、酸化物半導体膜122a、122cとして、結晶化した部分を有するCAAC(C Axis Aligned Crystalline Oxide Semiconductorともいう。)膜を用いてもよい。

【0060】

CAAC膜とは、c軸配向し、かつab面、表面または界面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て、金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面(あるいは表面または界面)においては、a軸またはb軸の向きが異なる(c軸を中心に回転した)結晶を含む酸化物半導体膜のことである。

【0061】

広義に、CAAC膜とは、非単結晶であって、そのab面に垂直な方向から見て、三角形もしくは六角形、または正三角形もしくは正六角形の原子配列を有し、かつc軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子が層状に配列した相を含む膜をいう。

【0062】

CAAC膜は単結晶ではないが、非晶質のみから形成されているものでもない。また、CAAC膜は結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

【0063】

CAAC膜を構成する酸素の一部は窒素で置換されてもよい。また、CAAC膜を構成する個々の結晶部分のc軸は一定の方向(例えば、CAAC膜が形成される基板面やCAAC膜の表面や膜面、界面等に垂直な方向)に揃っていてもよい。あるいは、CAAC膜を構成する個々の結晶部分のab面の法線は一定の方向(例えば、基板面、表面、膜面、界面等に垂直な方向)を向いていてもよい。

【0064】

CAAC膜は、その組成等に応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成等に応じて、可視光に対して透明であったり不透明であったりする。

【0065】

ここでは、酸化物半導体膜122a、122cとして非晶質構造の酸化物半導体膜を形成する。

【0066】

酸化物半導体膜122a、122cの厚さは、1nm以上50nm以下、更に好ましくは1nm以上30nm以下、更に好ましくは1nm以上10nm以下、更に好ましくは3nm以上7nm以下とすることが好ましい。酸化物半導体膜122a、122cの厚さを上記厚さとすることで、トランジスタのしきい値電圧のマイナス方向へのシフトを抑制することができる。

【0067】

酸化物半導体膜122a、122cにおいて、アルカリ金属またはアルカリ土類金属の濃度は、1×1018atoms/cm3以下、さらに好ましくは2×1016atoms/cm3以下であることが望ましい。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアが生成されることがあり、トランジスタのオフ電流の上昇の原因となるためである。

【0068】

酸化物半導体膜122a、122cの第1の領域123a、123cには、5×1018atoms/cm3以下の窒素が含まれてもよい。

【0069】

酸化物半導体膜122a、122cの第1の領域123a、123cは、水素濃度を5×1018atoms/cm3未満、好ましくは1×1018atoms/cm3以下、より好ましくは5×1017atoms/cm3以下、さらに好ましくは1×1016atoms/cm3以下とすることが好ましい。酸化物半導体及び水素の結合により、水素の一部がドナーとなり、キャリアである電子が生じてしまう。これらのため、酸化物半導体膜122a、122cの第1の領域123a、123c中の水素濃度を低減することで、しきい値電圧のマイナス方向へのシフトを低減することができる。

【0070】

ドーパントを含む一対の第2の領域125a〜125dは、ドーパントとして、ホウ素、窒素、リン、及びヒ素の少なくとも一以上が含まれる。または、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノンの少なくとも一以上が含まれる。または、ドーパントとしてフッ素が含まれる。なお、ドーパントとして、ホウ素、窒素、リン、及びヒ素の一以上と、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノンの一以上と、フッ素とが適宜組み合わされて含まれていてもよい。

【0071】

ドーパントを含む一対の第2の領域125a〜125dに含まれるドーパントの濃度は、5×1018atoms/cm3以上1×1022atoms/cm3以下、好ましくは5×1018atoms/cm3以上5×1019atoms/cm3未満とする。

【0072】

ドーパントを含む一対の第2の領域125a〜125dはドーパントを含むため、キャリア密度または欠陥を増加させることができる。このため、ドーパントを含まない第1の領域123a、123cと比較して導電性を高めることができる。なお、ドーパント濃度を増加させすぎると、ドーパントがキャリアの移動を阻害することになり、ドーパントを含む一対の第2の領域125a〜125dの導電性を低下させることになる。

【0073】

ドーパントを含む一対の第2の領域125a〜125dは、導電率が0.1S/cm以上1000S/cm以下、好ましくは10S/cm以上1000S/cm以下とすることが好ましい。

【0074】

一対の電極115a〜115dは導電材料として、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタングステンからなる単体金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、タングステン膜上にチタン膜を積層する二層構造、銅−マグネシウム−アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などがある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。なお、一対の電極115a〜115dは配線としても機能させてもよい。

【0075】

電極115a〜115dは、酸化物半導体膜122a、122cの表面の一部及び側面、特にチャネル幅方向と平行な側面を覆うため、酸化物半導体膜122a、122cとの接触面積を広くすることができる。このため、酸化物半導体膜122a、122cと、一対の電極115a〜115dとの接触抵抗を低減でき、またチャネル幅を広げることが可能であり、トランジスタのオン電流を大きくすることができる。

【0076】

ゲート絶縁膜117は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa−Zn−O系金属酸化物膜などを用いればよく、積層または単層で設ける。また、ゲート絶縁膜117は、絶縁膜103に示すような、加熱により酸素が脱離する酸化絶縁膜を用いてもよい。ゲート絶縁膜117に加熱により酸素が脱離する膜を用いることで、酸化物半導体膜122a、122cに生じる酸素欠損を修復することができ、トランジスタの電気特性の劣化を抑制できる。

【0077】

また、ゲート絶縁膜117として、ハフニウムシリケート(HfSiOx)、窒素が添加されたハフニウムシリケート(HfSixOyNz)、窒素が添加されたハフニウムアルミネート(HfAlxOyNz)、酸化ハフニウム、酸化イットリウムなどのhigh−k材料を用いることでゲート絶縁膜の厚さを薄くしてもゲートリークを低減できる。

【0078】

ゲート絶縁膜117の厚さは、10nm以上300nm以下、より好ましくは5nm以上50nm以下、より好ましくは10nm以上30nm以下とするとよい。

【0079】

ゲート電極119a、119cは、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金などを用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属元素を用いてもよい。また、ゲート電極119a、119cは、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタングステン膜を積層する二層構造、窒化タンタル膜上にタングステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などがある。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の膜、または複数組み合わせた合金膜、もしくは窒化膜を用いてもよい。

【0080】

また、ゲート電極119a、119cは、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

【0081】

また、ゲート電極119a、119cとゲート絶縁膜117との間に、ゲート絶縁膜117に接する材料層として、窒素を含むIn−Ga−Zn−O膜や、窒素を含むIn−Sn−O膜や、窒素を含むIn−Ga−O膜や、窒素を含むIn−Zn−O膜や、窒素を含むSn−O膜や、窒素を含むIn−O膜や、金属窒化膜(InN、ZnNなど)を設けることが好ましい。これらの膜は仕事関数が5eV、好ましくは5.5eV以上であり、トランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。例えば、窒素を含むIn−Ga−Zn−O膜を用いる場合、少なくとも酸化物半導体膜122a、122cより高い窒素濃度、具体的には7原子%以上の窒素を含むIn−Ga−Zn−O膜を用いる。

【0082】

絶縁膜127は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層または単層で設ける。なお、絶縁膜127として、絶縁膜103と同様に、加熱により酸素の一部が脱離する酸化絶縁膜を用いて形成してもよい。また、絶縁膜127として、外部への酸素の拡散を防ぐ酸化絶縁膜を用いることで、ゲート絶縁膜117から脱離する酸素を酸化物半導体膜122a、122cに供給することができる。また、絶縁膜127として、外部からの水素の拡散を防ぐ酸化絶縁膜を用いることで、外部から酸化物半導体膜122a、122cへの水素の拡散を低減することが可能であり、酸化物半導体膜122a、122cの欠損を低減することができる。外部からの水素の拡散を防ぐ酸化絶縁膜の代表例としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。

【0083】