半導体装置

【課題】端子部のコンタクトホールのテーパー形状を高い精度で制御する。

【解決手段】酸化物半導体層7a、ソース配線13as、ドレイン電極13adを備えた薄膜トランジスタと、第1接続部3c、第2接続部13cおよび第2接続部上に形成された第3接続部19cを備えた端子部とからなる薄膜トランジスタである。第2接続部は、第1および第2絶縁膜5,9に設けられた第1開口部内で第1接続部と接し、第3接続部19cは、保護膜に設けられた第2開口部内で第2接続部と接する。第1開口部は、第1絶縁膜5および第2絶縁膜9を同時にエッチングすることによって形成、第2開口部は、保護膜15を前記第1および第2絶縁膜とは別個にエッチングすることによって形成される。第2接続部13cは、第1開口部における第1および第2絶縁膜の端面を覆い、かつ、第2開口部における保護膜15の端面を覆っていない。

【解決手段】酸化物半導体層7a、ソース配線13as、ドレイン電極13adを備えた薄膜トランジスタと、第1接続部3c、第2接続部13cおよび第2接続部上に形成された第3接続部19cを備えた端子部とからなる薄膜トランジスタである。第2接続部は、第1および第2絶縁膜5,9に設けられた第1開口部内で第1接続部と接し、第3接続部19cは、保護膜に設けられた第2開口部内で第2接続部と接する。第1開口部は、第1絶縁膜5および第2絶縁膜9を同時にエッチングすることによって形成、第2開口部は、保護膜15を前記第1および第2絶縁膜とは別個にエッチングすることによって形成される。第2接続部13cは、第1開口部における第1および第2絶縁膜の端面を覆い、かつ、第2開口部における保護膜15の端面を覆っていない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタを備える半導体装置およびその製造方法に関する。

【背景技術】

【0002】

アクティブマトリクス型の液晶表示装置や有機EL表示装置は、一般に、画素毎にスイッチング素子として薄膜トランジスタ(Thin Film Transistor;以下、「TFT」)が形成された基板(以下、「TFT基板」)と、対向電極およびカラーフィルターなどが形成された対向基板と、TFT基板と対向基板との間に設けられた液晶層などの光変調層とを備えている。

【0003】

TFT基板には、複数のソース配線と、複数のゲート配線と、これらの交差部にそれぞれ配置された複数のTFTと、液晶層などの光変調層に電圧を印加するための画素電極と、補助容量配線および補助容量電極などが形成されている。また、TFT基板の端部には、ソース配線およびゲート配線を、駆動回路の入力端子にそれぞれ接続するための端子部が設けられている。駆動回路は、TFT基板上に形成されていてもよいし、別個の基板(回路基板)上に形成されていてもよい。

【0004】

TFT基板の構成は、例えば特許文献1に開示されている。以下、図面を参照しながら、特許文献1に開示されたTFT基板の構成を説明する。

【0005】

図12(a)は、TFT基板の概略を示す模式的な平面図であり、図12(b)は、TFT基板における1個の画素を示す拡大平面図である。また、図13は、図12に示す半導体装置におけるTFTおよび端子部の断面図である。

【0006】

図12(a)に示すように、TFT基板は、複数のゲート配線2016と、複数のソース配線2017とを有している。これらの配線2016、2017で包囲されたそれぞれの領域2021が「画素」となる。TFT基板のうち画素が形成される領域(表示領域)以外の領域2040には、複数のゲート配線2016およびソース配線2017のそれぞれを駆動回路に接続するための複数の接続部2041が配置されている。各接続部2041は、外部配線と接続するための端子部を構成する。なお、本明細書では、複数の端子部が配置されるTFT基板の領域2040を「端子配置領域」と呼ぶ。

【0007】

図12(b)および図13に示すように、画素となる各領域2021を覆うように画素電極2020が設けられている。また、各領域2021にはTFTが形成されている。TFTは、ゲート電極Gと、ゲート電極Gを覆うゲート絶縁膜2025、2026と、ゲート絶縁膜2026上に配置された半導体層2019と、半導体層2019の両端部にそれぞれ接続されたソース電極Sおよびドレイン電極Dとを有している。TFTは保護膜2028で覆われている。保護膜2028と画素電極2020との間には、層間絶縁膜2029が形成されている。TFTのソース電極Sはソース配線2017に、ゲート電極Gはゲート配線2016に接続されている。また、ドレイン電極Dは、コンタクトホール2030内で画素電極2020に接続されている。

【0008】

また、ゲート配線2016と平行に補助容量配線2018が形成されている。補助容量配線2018は補助容量に接続されている。ここでは、補助容量は、ドレイン電極と同じ導電膜から形成された補助容量電極2018bと、ゲート配線と同じ導電膜から形成された補助容量電極2018aと、それらの間に位置するゲート絶縁膜2026とから構成されている。

【0009】

各ゲート配線2016またはソース配線2017から延びた接続部2041上には、ゲート絶縁膜2025、2026および保護膜2028が形成されておらず、接続部2041の上面と接するように接続配線2044が形成されている。これにより、接続部2041と接続配線2044との電気的な接続が確保されている。

【0010】

なお、図13に示すように、液晶表示装置では、TFT基板2013は、液晶層2015を挟んで、対向電極やカラーフィルターが形成された基板2014と対向するように配置される。

【0011】

このようなTFT基板を製造する際には、画素となる領域2021(「画素部」ともいう。)と、端子部とを共通のプロセスで形成し、マスク数や工程数の増大を抑えることが好ましい。

【0012】

上記のTFT基板を製造しようとすると、ゲート絶縁膜2025、2026および保護膜2028のうち端子配置領域2040に位置する部分、および、ゲート絶縁膜2025および保護膜2028のうち補助容量が形成される領域に位置する部分をエッチングする必要がある。特許文献1では、有機絶縁膜を用いて層間絶縁膜2029を形成し、これをマスクとして、これらの絶縁膜2025、2026および保護膜2028をエッチングすることが開示されている。

【0013】

一方、近年、シリコン半導体膜の代わりに、酸化亜鉛などの酸化物半導体膜を用いてTFTの活性層を形成することが提案されている。このようなTFTを「酸化物半導体TFT」と称する。酸化物半導体は、アモルファスシリコンよりも高い移動度を有している。このため、酸化物半導体TFTは、アモルファスシリコンTFTよりも高速で動作することが可能である。また、酸化物半導体膜は、多結晶シリコン膜よりも簡便なプロセスで形成されるため、大面積が必要とされる装置にも適用できる。

【0014】

しかしながら、ボトムゲート構造を有する酸化物半導体TFTでは、TFTの製造プロセス中、例えば熱処理工程などにおいて、酸素欠陥によってキャリア電子が生じ、抵抗が低くなるおそれがある。また、ソース・ドレイン電極のエッチング工程や層間絶縁膜の形成工程において、その下方にある酸化物半導体膜がダメージを受けやすいという問題がある。

【0015】

これに対し、半導体層のうちチャネルが形成される領域(チャネル形成領域)を覆うようにチャネル保護膜を設ける構造(チャネル保護型)が提案されている。TFTの製造プロセスにおいて、半導体層上にチャネル保護膜を形成した後、ソース・ドレイン電極を形成すると、ソース・ドレイン電極を形成するためのエッチングを行う際に、チャネル保護膜がエッチストップとして機能する。このため、チャネル形成領域がエッチングによって受けるダメージを低減できる。

【0016】

特許文献2には、チャネル保護型のTFTを有するTFT基板の画素部の構成が記載されている。ただし、特許文献2のTFTは、シリコン膜を用いて形成されている。

【0017】

図14は、特許文献2に記載されたTFT基板の一部を示す断面図である。TFT基板の各画素には、薄膜トランジスタ1141および補助容量1142が設けられている。薄膜トランジスタ1141には、ゲート配線1102、ゲート絶縁膜1104、チャネル形成領域を有する半導体層1113、チャネル保護膜1108、ソース領域1118、ドレイン領域1117、ドレイン電極1121およびソース配線1122が形成されている。薄膜トランジスタ1141は保護膜1127で覆われており、保護膜1127上には画素電極1131が設けられている。画素電極1131は、保護膜1127に形成されたコンタクトホール内でドレイン電極1121と接続されている。補助容量1142は、ゲート配線1102と同じ導電膜から形成された容量配線1151と、画素電極1131を電極とし、電極間に挟まれたゲート絶縁膜1104および保護膜1127を誘電体として構成されている。

【0018】

なお、本明細書では、半導体層のチャネル形成領域とソース・ドレイン電極との間に形成された絶縁膜を「チャネル保護膜」または「エッチストッパ」と呼び、TFTを覆う絶縁膜、ボトムゲート構造の場合にはソース・ドレイン電極上に設けられる絶縁膜を、単に「保護膜」と呼んで両者を区別する。

【0019】

図示されていないが、このTFT基板における端子部では、ゲート配線1102上のゲート絶縁膜1104および保護膜1127に形成されたコンタクトホール内で、ゲート配線1102と、保護膜1127上に設けられる外部配線とを電気的に接続させることができる。

【0020】

上記の半導体装置の製造方法では、チャネル保護膜1108を形成するためのエッチングと、ソース・ドレイン電極1121、1122を形成するためのエッチングと、保護膜1127にコンタクトホールを形成するためのエッチングとが行われる(特許文献2の図7〜図9)。端子部のコンタクトホールは、保護膜1127のエッチングを行う際に、保護膜1127およびゲート絶縁膜1104を一括してエッチングすることによって形成されると考えられる。

【0021】

なお、特許文献3には、チャネル保護型のTFTを備えたTFT基板の製造方法において、ハーフトーンマスクを利用することによって、使用するマスクの数を低減することが提案されている。しかしながら、特許文献3の方法は、製造プロセスが複雑で、量産性が低くなるおそれがある。また、ゲート電極とソース・ドレイン電極との間に絶縁膜が1層しか形成されていないため、これらの電極間で短絡が生じる可能性がある。

【先行技術文献】

【特許文献】

【0022】

【特許文献1】特開2008−170664号公報

【特許文献2】特開2009−157354号公報

【特許文献3】特開2007−258675号公報

【発明の概要】

【発明が解決しようとする課題】

【0023】

特許文献1、2に開示された方法によると、TFT基板の端子部において、ゲート絶縁膜および保護膜を同時にエッチングする必要がある。本発明者が検討したところ、このような方法を酸化物半導体TFTを備えるTFT基板に適用すると、次のような問題があることを見出した。

【0024】

一般に、酸化物半導体TFTでは、ゲート絶縁膜や保護膜としてSiO2膜などの酸化物膜が用いられることが多い。これは、酸化物半導体層に酸素欠損が生じた場合に、酸化物膜に含まれる酸素によって酸素欠損を回復できるからである。

【0025】

特許文献1によると、TFT基板(図12、図13)を製造する際には、有機絶縁膜を用いて層間絶縁膜2029を形成し、これをマスクとして、ゲート絶縁膜2025、2026および保護膜2028のうち端子配置領域2040に位置する部分をエッチングすることにより、端子部のコンタクトホールが形成される。このとき、ゲート絶縁膜2025、2026および保護膜2028のうち何れかの材料としてSiO2が用いられていれば、SiO2のエッチレートが非常に低いために、エッチング時間が長くなる。この結果、マスクである有機絶縁膜(層間絶縁膜)2029がダメージを受けるおそれがある。

【0026】

特許文献2では、端子部のコンタクトホールは、レジストマスクを用いて、保護膜1127およびゲート絶縁膜1104を一括してエッチングすることによって形成されると考えられる。このとき、保護膜1127およびゲート絶縁膜1104の何れかの材料としてSiO2が用いられていれば、SiO2のエッチレートが非常に低いために、エッチング工程でレジストマスクがダメージを受けて、レジストマスクの剥離不良が生じる可能性がある。また、エッチレートが低いと、端子部のコンタクトホールの壁面に所望のテーパー形状を形成し難くなり、壁面が基板に対して略垂直になる可能性がある。このような場合、端子部のコンタクトホール内に形成される配線に切れが生じやすくなるという問題もある。

【0027】

このように、従来は、ソース端子やゲート端子を形成するためのエッチング工程において、エッチングマスクがダメージを受けたり、あるいは、コンタクトホールのテーパー形状を最適化できずに配線の断切れを生じさせるおそれがあり、TFT基板の信頼性を低下させる可能性があった。

【0028】

本発明は、上記事情を解決するためになされたものであり、その主な目的は、酸化物半導体TFTと、TFTの電極と外部配線とを接続する端子部とを備える半導体装置において、端子部のコンタクトホールを形成する際に、マスクへのダメージを低減するとともに、高い精度でコンタクトホールの壁面のテーパー形状を制御することにある。

【課題を解決するための手段】

【0029】

本発明の半導体装置は、基板と、前記基板上に形成された薄膜トランジスタと、前記薄膜トランジスタと外部配線とを電気的に接続する端子部とを備えた半導体装置であって、前記薄膜トランジスタは、前記基板上に設けられたゲート配線と、前記ゲート配線上に形成された第1絶縁膜と、前記第1絶縁膜上に形成され、チャネル領域と、前記チャネル領域の両側にそれぞれ位置するソース領域およびドレイン領域とを有する島状の酸化物半導体層と、前記酸化物半導体層上に接して設けられた第2絶縁膜と、前記第2絶縁膜上に設けられ、前記ソース領域と電気的に接続されたソース配線と、前記第2絶縁膜上に設けられ、前記ドレイン領域と電気的に接続されたドレイン電極と、前記ソース配線および前記ドレイン電極上に設けられ、前記薄膜トランジスタを覆う保護膜とを備え、前記端子部は、前記ゲート配線と同一の導電膜から形成された第1接続部と、前記第1接続部上に形成され、前記ソース配線および前記ドレイン電極と同一の導電膜から形成された第2接続部と、前記第2接続部上に形成された第3接続部とを備え、前記第2接続部は、前記第1絶縁膜および前記第2絶縁膜に設けられた第1開口部内で、前記第1接続部と接しており、前記第3接続部は、前記保護膜に設けられた第2開口部内で、前記第2接続部と接しており、前記第2接続部は、前記第1開口部における前記第1絶縁膜および前記第2絶縁膜の端面を覆い、かつ、前記第2開口部における前記保護膜の端面を覆っていない。

【0030】

ある好ましい実施形態において、前記基板の表面の法線方向から見て、前記第2開口部は、前記第1開口部の内部に位置する。

【0031】

前記ドレイン電極と電気的に接続された画素電極をさらに備え、前記第3接続部は、前記画素電極と同一の導電膜から形成されていてもよい。

【0032】

ある好ましい実施形態において、前記基板に形成された補助容量をさらに備え、前記補助容量は、前記ゲート配線と同一の導電膜から形成された補助容量配線と、前記補助容量配線を覆う前記第1絶縁膜と、前記酸化物半導体層と同一の酸化物半導体膜から形成された補助容量形成用半導体層と、前記補助容量形成用半導体層上に設けられた補助容量電極とを有しており、前記補助容量電極は、前記第2絶縁膜に形成された開口部内で前記補助容量形成用半導体層と接している。

【0033】

ある好ましい実施形態において、前記補助容量電極は、前記ドレイン電極の一部であり、前記画素電極は、前記保護膜に形成された開口部内で前記補助容量電極に接している。

【0034】

ある好ましい実施形態において、前記補助容量電極は、前記画素電極の一部である。

【0035】

前記ゲート配線と前記ソース配線とを電気的に接続するゲート・ソース接続部をさらに備え、前記ゲート・ソース接続部では、前記ソース配線は、前記第1絶縁膜および前記第2絶縁膜に設けられた前記第1開口部内で前記ゲート配線に接していてもよい。

【0036】

前記保護膜と前記画素電極との間に、有機絶縁膜をさらに備えていてもよい。

【0037】

前記第1絶縁膜および前記保護膜のうち少なくとも一方はSiO2を含むことが好ましい。

【0038】

前記第1絶縁膜は、SiO2膜およびSiNx膜を含む積層構造を有しており、前記SiO2膜は前記積層構造の最上層であり、前記酸化物半導体層の下面と接していてもよい。

【0039】

前記保護膜は、SiO2膜およびSiNx膜を含む積層構造を有しており、前記SiO2膜は前記積層構造の最下層であってもよい。

【0040】

ある好ましい実施形態において、前記ゲート配線の上面および側壁と前記ソース配線との間、および、前記ゲート配線の上面および側壁と前記ドレイン電極との間には、少なくとも前記第1絶縁膜および前記酸化物半導体層が設けられている。

【0041】

前記ゲート配線の上面および側壁と前記ソース配線との間、および、前記ゲート配線の上面および側壁と前記ドレイン電極との間に、前記第2絶縁膜がさらに設けられていてもよい。

【0042】

前記第2絶縁膜は、前記酸化物半導体層の表面のうち前記ソース領域および前記ドレイン領域を除く全ての上面および側壁を覆っており、かつ、前記酸化物半導体層の側壁近傍で前記第1絶縁膜の上面と接していてもよい。

【0043】

前記酸化物半導体層のチャネル長方向に沿った幅は、前記ゲート配線のチャネル長方向に沿った幅よりも大きくてもよい。

【0044】

本発明の半導体装置の製造方法は、上記のいずれかに記載の半導体装置の製造方法であって、(A)基板上にゲート配線用導電膜を形成し、これをパターニングすることによって、ゲート配線および第1接続部を形成する工程と、(B)前記ゲート配線および前記第1接続部上に、第1絶縁膜を形成する工程と、(C)前記第1絶縁膜上に、薄膜トランジスタの活性層となる酸化物半導体層を形成する工程と、(D)前記酸化物半導体層および前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(E)前記酸化物半導体層をエッチストップとして前記第1および第2絶縁膜のエッチングを行うことにより、前記第2絶縁膜に、前記酸化物半導体層を露出するソースコンタクト形成用開口部およびドレインコンタクト形成用開口部を形成するとともに、前記第2絶縁膜および前記第1絶縁膜に、前記第1接続部の表面を露出する第1開口部を形成する工程と、(F)前記第2絶縁膜上にソース・ドレイン電極用導電膜を形成し、これをパターニングすることによって、前記ソースコンタクト形成用開口部内で前記酸化物半導体層に接するソース配線と、前記ドレインコンタクト形成用開口部内で前記酸化物半導体層に接するドレイン電極と、前記第1開口部内で前記第1接続部に接する第2接続部を形成する工程と、(G)前記ソース配線、前記ドレイン電極および前記第2接続部上に保護膜を形成する工程と、(H)前記保護膜に、前記第2接続部を露出する第2開口部を形成する工程と、(I)前記保護膜上に、前記第2開口部内で前記第2接続部に接する第3接続部を形成する工程とを包含する。

【0045】

前記工程(H)は、前記保護膜に、前記ドレイン電極を露出する開口部を形成する工程を含み、前記工程(I)は、前記保護膜上に透明導電膜を形成し、これをパターニングすることによって、前記第3接続部と画素電極とを形成する工程であって、前記画素電極は、前記ドレイン電極を露出する前記開口部内で前記ドレイン電極と接する工程であってもよい。

【発明の効果】

【0046】

本発明によると、酸化物半導体TFTと、TFTの電極と外部配線とを接続する端子部とを備える半導体装置において、端子部のコンタクトホールを形成する際に、エッチング時間を短縮してマスクへのダメージを低減するとともに、高い精度でコンタクトホールの壁面のテーパー形状を制御できる。よって、半導体装置の信頼性を高めることができる。

【0047】

また、上記半導体装置を、製造工程を複雑化することなく簡便に製造できる。

【図面の簡単な説明】

【0048】

【図1】(a)〜(f)は、それぞれ、本発明による実施形態1の半導体装置の製造方法の一例を示す工程断面図である。

【図2】本発明による実施形態1の半導体装置の平面図であり、(a)は、半導体装置における画素部101の平面図であり、(b)〜(d)は、それぞれ、半導体装置におけるゲート端子、ソース端子およびゲート・ソース接続部の平面図である。

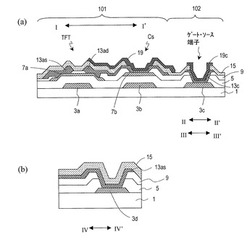

【図3】(a)は、図2(a)に示すI−I’線と、図2(b)に示すII−II’線または図2(c)に示すIII−III’線とに沿った断面図である。(b)は、図2(d)に示すIV−IV’線に沿った断面図である。

【図4】(a)〜(f)は、それぞれ、本発明による実施形態2の半導体装置の製造方法の一例を示す工程断面図である。

【図5】本発明による実施形態2の半導体装置の平面図であり、(a)は、半導体装置における画素部201の平面図であり、(b)〜(d)は、それぞれ、半導体装置におけるゲート端子、ソース端子およびゲート・ソース接続部の平面図である。

【図6】(a)は、図5(a)に示すI−I’線と、図5(b)に示すII−II’線または図5(c)に示すIII−III’線とに沿った断面図である。(b)は、図5(d)に示すIV−IV’線に沿った断面図である。

【図7】(a)〜(c)は、それぞれ、本発明による実施形態3の半導体装置の製造方法の一例を示す工程断面図である。

【図8】実施形態3の半導体装置において、接続部23cに断切れが生じた場合の端子部を例示する拡大断面図である。

【図9】本発明による実施形態3の他の半導体装置の構成を例示する断面図である。

【図10】本発明による実施形態3のさらに他の半導体装置の構成を例示する断面図である。

【図11】(a)〜(c)は、それぞれ、本発明による実施形態4の半導体装置の製造方法の一例を示す工程断面図である。

【図12】(a)は、従来のTFT基板の概略を示す模式的な平面図であり、(b)は、(a)のTFT基板における1個の画素を示す拡大平面図である。

【図13】図12に示す従来のTFT基板におけるTFTおよび端子部の断面図である。

【図14】従来のTFT基板の一部を示す断面図である。

【発明を実施するための形態】

【0049】

(実施形態1)

以下、図面を参照しながら、本発明による実施形態1の半導体装置の製造方法を説明する。

【0050】

本実施形態の半導体装置は、少なくとも1つの酸化物半導体TFTが形成されたTFT基板を備えていればよく、各種表示装置やTFT基板、電子機器などを広く含む。

【0051】

ここでは、酸化物半導体TFTをスイッチング素子として備えた、液晶表示装置のTFT基板の製造方法を例に説明する。TFT基板は、複数の画素部を含む表示領域と、表示領域以外の領域に形成された端子配置領域とを有している。本実施形態では、表示領域の各画素部に、酸化物半導体TFTおよび補助容量が形成され、端子配置領域に、複数の端子部が形成される。

【0052】

図1(a)〜(f)は、本実施形態の半導体装置の製造方法を説明するための模式的な工程断面図である。

【0053】

まず、図1(a)に示すように、基板1のうちTFTを形成しようとする領域(TFT形成領域)Aにゲート配線3a、補助容量を形成しようとする領域(補助容量形成領域)Bに補助容量配線3b、およびゲート・ソース端子部を形成しようとする領域(端子部形成領域)Cに、ゲート配線の接続部3cを形成する。

【0054】

なお、TFT形成領域Aおよび補助容量形成領域Bは、表示領域内の各画素部101にそれぞれ位置し、端子部形成領域Cは、表示領域以外の領域、例えば基板1の周縁に配置された端子配置領域102内に位置する。通常、端子配置領域102には多数のソース端子部およびゲート端子部が形成されるが、ここでは1個のゲートまたはソース端子部の形成領域Cのみを示す。

【0055】

ゲート配線3a、補助容量配線3bおよび接続部3cは、基板1上にスパッタ法などにより金属膜(例えばTi/Al/Ti膜)を形成した後、金属膜をパターニングすることによって形成される。金属膜のパターニングは、公知のフォトリソグラフィによりレジストマスクを形成し、レジストマスクで覆われていない部分を除去することによって行われる。この後、レジストマスクを基板1から剥離する。

【0056】

次に、図1(b)に示すように、ゲート配線3a、補助容量配線3bおよび接続部3cを覆うように絶縁膜5を形成する。続いて、TFT形成領域AにTFTのチャネル層となる島状の酸化物半導体層7a、補助容量形成領域Bに島状の酸化物半導体層7bを形成する。

【0057】

本実施形態では、絶縁膜5として、例えば厚さが約400nmのSiO2膜をCVD法を用いて形成する。なお、絶縁膜5は、例えばSiO2膜からなる単層であってもよいし、SiNx膜を下層とし、SiO2膜を上層とする積層構造を有していてもよい。SiO2膜からなる単層の場合、SiO2膜の厚さは300nm以上500nm以下であることが好ましい。SiNx膜(下層)およびSiO2膜(上層)からなる積層構造を有する場合、SiNx膜の厚さは200nm以上500nm以下、SiO2膜の厚さは20nm以上150nm以下であることが好ましい。

【0058】

酸化物半導体層7a、7bは、以下のようにして形成できる。まず、スパッタ法を用いて、例えば厚さが30nm以上300nm以下のIn−Ga−Zn−O系半導体(IGZO)膜を絶縁膜5の上に形成する。この後、フォトリソグラフィにより、IGZO膜の所定の領域を覆うレジストマスクを形成する。次いで、IGZO膜のうちレジストマスクで覆われていない部分をウェットエッチングにより除去する。この後、レジストマスクを剥離する。このようにして、島状の酸化物半導体層7a、7bを得る。なお、IGZO膜の代わりに、他の酸化物半導体膜を用いて酸化物半導体層7a、7bを形成してもよい。

【0059】

次いで、図1(c)に示すように、基板1の表面全体に絶縁膜9を堆積させた後、絶縁膜9をパターニングする。

【0060】

具体的には、まず、絶縁膜5および酸化物半導体層7a、7bの上に、絶縁膜9として例えばSiO2膜(厚さ:例えば約150nm)をCVD法によって形成する。

【0061】

絶縁膜9は、SiOyなどの酸化物膜を含むことが好ましい。酸化物膜を用いると、酸化物半導体層7a、7bに酸素欠損が生じた場合に、酸化物膜に含まれる酸素によって酸素欠損を回復することが可能となるので、酸化物半導体層7a、7bの酸化欠損をより効果的に低減できる。ここでは、絶縁膜9としてSiO2膜からなる単層を用いているが、絶縁膜9は、SiO2膜を下層とし、SiNx膜を上層とする積層構造を有していてもよい。絶縁膜9の厚さ(積層構造を有する場合には各層の合計厚さ)は50nm以上200nm以下であることが好ましい。50nm以上であれば、ソース・ドレイン電極のパターニング工程などにおいて、酸化物半導体層7aの表面をより確実に保護できる。一方、200nmを超えると、ソース電極やドレイン電極により大きい段差が生じるので、断線などを引き起こすおそれがある。

【0062】

この後、フォトリソグラフィにより、絶縁膜9の所定の領域を覆うレジストマスクを形成する。次いで、絶縁膜9のうちレジストマスクで覆われていない部分をウェットエッチングにより除去する。このとき、端子部形成領域Cでは、絶縁膜9だけでなく、その下の絶縁膜5もエッチングされ、TFT形成領域Aおよび補助容量形成領域Bでは、絶縁膜9の下の酸化物半導体層7a、7bはエッチングされないように、エッチング条件を選択する。ここでは、エッチングガスとしてCF4/O2(流量:475sccm/25sccm)を用い、基板1の温度を60℃として、チャンバー内でドライエッチングを行う。チャンバー内の真空度を15mTとする。また、印加パワーを1000W、エッチング時間を7分とする。

【0063】

これにより、TFT形成領域Aでは、絶縁膜9のうちソースコンタクトおよびドレインコンタクトを形成する部分がエッチングされて、酸化物半導体層7aを露出する2つの開口部11as、11adが形成される。絶縁膜9は、酸化物半導体層7aのうちチャネルとなる領域を覆っており、チャネル保護膜9aとして機能する。補助容量形成領域Bでは、絶縁膜9のうち酸化物半導体層7b上に位置する部分がエッチングされて、酸化物半導体層7bを露出する開口部11bが形成される。端子部形成領域Cでは、絶縁膜9のうち接続部3c上に位置する部分、および、その下の絶縁膜5が連続してエッチングされて、接続部3cの表面を露出する開口部11cが得られる。開口部11cの直径は例えば20μmである。

【0064】

本工程では、酸化物半導体層7a、7bをエッチストップとして、絶縁膜5および絶縁膜9のエッチングが行われるように、絶縁膜5、9の材料などに応じて、エッチング条件が選択されていることが好ましい。これにより、端子部形成領域Cでは絶縁膜9および絶縁膜5が一括してエッチング(GI/ES同時エッチング)されるとともに、TFT形成領域Aおよび補助容量形成領域Bでは絶縁膜9のみをエッチングできる。ここでいうエッチング条件とは、ドライエッチングを用いる場合、エッチングガスの種類、基板1の温度、チャンバー内の真空度などを含む。また、ウェットエッチングを用いる場合、エッチング液の種類やエッチング時間などを含む。

【0065】

続いて、図1(d)に示すように、基板1の表面全体に導電膜を形成する。本実施形態では、例えばスパッタ法によりTi/Al/Ti膜などの金属膜を形成する。この後、例えばフォトリソグラフィにより、金属膜のパターニングを行う。

【0066】

これにより、TFT形成領域Aでは、開口部11as、11adの内部および絶縁膜9上に、酸化物半導体層7aのうちチャネル領域となる領域の両側に位置する領域とそれぞれ接するように、ソース配線13asおよびドレイン電極13adを形成する。ドレイン電極13adは、補助容量形成領域Bにおける補助容量配線3b上まで延び、開口部11bを介して酸化物半導体層7bと接している。ドレイン電極13adのうち酸化物半導体層7bと接する部分は、補助容量電極としても機能する。また、端子部形成領域Cでは、開口部11cの内部および絶縁膜9上に、接続部3cと電気的に接続された接続部13cが形成される。

【0067】

なお、本明細書では、酸化物半導体層7aのうちソース配線13asと接する領域を「ソース領域」、ドレイン電極13adと接する領域を「ドレイン領域」と称する。また、酸化物半導体層7aのうちゲート配線3a上に位置し、かつ、ソース領域とドレイン領域とによって挟まれた領域を「チャネル領域」と称する。

【0068】

このようにして、TFT形成領域Aに酸化物半導体TFTが形成され、補助容量形成領域Bに補助容量Csが形成される。なお、酸化物半導体層7bはドライダメージにより導電体となる可能性が高い。その場合、補助容量Csは、補助容量配線3bと、ドレイン電極13adおよび酸化物半導体層7bとを電極とし、絶縁膜5を誘電体として構成される。

【0069】

この後、図1(e)に示すように、酸化物半導体TFTおよび補助容量Csを覆うように、基板1の表面全体に保護膜15を堆積させる。本実施形態では、保護膜15として、SiO2膜などの酸化物膜(厚さ:例えば約265nm)をCVD法によって形成する。なお、保護膜15は、例えばSiO2膜からなる単層であってもよいし、SiO2膜を下層とし、SiNx膜を上層とする積層構造を有していてもよい。SiO2膜からなる単層の場合、SiO2膜の厚さは50nm以上300nm以下であることが好ましい。SiO2膜(下層)およびSiNx膜(上層)からなる積層構造を有する場合、SIO2膜の厚さは50nm以上150nm以下、SiNx膜の厚さは50nm以上200nm以下であることが好ましい。

【0070】

次いで、フォトリソグラフィにより保護膜15のパターニングを行う。これにより、補助容量形成領域Bにおいて、保護膜15に、ドレイン電極13adを露出する開口部17bを形成する。開口部17bは、補助容量Cs上に形成される。また、端子部形成領域Cにおいて、保護膜15に、接続部13cを露出する開口部17cを形成する。なお、図示するように、開口部11cおよび開口部17cの幅は略等しくてもよいが、基板1の表面の法線方向から見て、開口部17cは開口部11cよりも一回り小さく、開口部11c内に配置されることが好ましい。これにより、基板の法線方向から見て、開口部11c、17cが重なり合うように配置されるので、開口部11c、17cによって端子部のコンタクトホールを構成できる。

【0071】

次いで、図1(f)に示すように、保護膜15の上および開口部17b、17c内に透明導電膜を形成し、透明導電膜のパターニングを行う。これにより、ドレイン電極13adの露出した表面と接する画素電極19と、接続部13cの露出した表面と接する接続部19cを形成する。画素電極19は、画素ごとに分離して配置される。

【0072】

本実施形態では、例えばスパッタ法により透明導電膜を堆積する。透明導電膜として、例えばITO膜(厚さ:50〜200nm)を用いる。次いで、公知のフォトリソグラフィによってITO膜のパターニングを行う。

【0073】

なお、図1では、簡単のため、画素電極19、補助容量Csおよび薄膜トランジスタTFTを1個ずつ示しているが、TFT基板は、通常、複数の画素部101を有しており、複数の画素部101のそれぞれに画素電極19、補助容量Csおよび薄膜トランジスタTFTが配置される。また、端子配置領域102においては、ソース配線13asおよびゲート配線3aと同数の端子部が形成される。

【0074】

図示していないが、端子配置領域102には、ソース配線とゲート配線とを接続するゲート・ソース接続部を形成する場合がある。その場合には、端子部の開口部11cを形成する際に、ゲート配線上の絶縁膜9および絶縁膜5を同時にエッチングして、ゲート配線(またはその接続部)を露出する開口部を形成することが好ましい。この開口部内にソース配線を形成することによって、ソース配線とゲート配線とが直接接する構成を有するゲート・ソース接続部が得られる。

【0075】

図2および図3は、本実施形態の半導体装置を模式的に示す図である。図2(a)は、半導体装置における画素部101の平面図であり、図2(b)〜(d)は、それぞれ、半導体装置における端子配置領域102のゲート端子、ソース端子およびゲート・ソース接続部の平面図である。図3(a)は、図2(a)に示すI−I’線と、図2(b)に示すII−II’線または図2(c)に示すIII−III’線とに沿った断面図である。図3(b)は、図2(d)に示すIV−IV’線に沿った断面図である。

【0076】

これらの図からわかるように、各画素部101では、画素の行方向に沿って延びるソース配線13asと、画素の列方向に沿って延びるゲート配線3aおよび補助容量配線3bとが形成されている。

【0077】

ソース配線13asとゲート配線3aとの交差する点の近傍には、薄膜トランジスタTFTが形成され、補助容量配線3b上には補助容量Csが形成されている。

【0078】

TFTの酸化物半導体層7aは、絶縁膜9の開口部11as、11adを介して、ソース配線13asおよびドレイン電極13adとそれぞれ接続されている。また、ドレイン電極13adは、補助容量配線3b上まで延伸されており、補助容量Cs上で、保護膜15の開口部17b内で画素電極19と接続されている。

【0079】

補助容量Csの酸化物半導体層7bは、絶縁膜9の開口部11b内で補助容量電極(ここではドレイン電極13ad)と接続され、保護膜15の開口部17b内で画素電極19と接続されている。基板1の表面の法線方向から見て、開口部17bは、開口部11b内に配置されている。

【0080】

ゲート端子部およびソース端子部では、接続部3cは、絶縁膜5および絶縁膜9を同時にエッチングして得られた開口部11c内で接続部13cと接続され、保護膜15の開口部17c内で接続部19cと接続されている。本実施形態では、開口部11c内に接続部3cが形成された後に、保護膜15に開口部17cが形成されるので、接続部3cは開口部11cにおける絶縁膜5、9の端面(開口部11cの壁面)を覆い、かつ、開口部17cにおける保護膜15の端面(開口部17cの壁面)を覆っていない。また、基板1の表面の法線方向から見て、開口部17cは、開口部11c内に配置されている。

【0081】

また、ゲート・ソース接続部では、ゲート配線の接続部3dは、絶縁膜5および絶縁膜9を同時にエッチングして得られた開口部11d内で、ソース配線13asと直接接続されている。ソース配線13as上は保護膜15で覆われている。

【0082】

本実施形態の半導体装置は、図1を参照しながら前述した方法を用いて製造されるので、従来と比べて、以下のような利点を有する。

【0083】

特許文献1に開示された従来の方法では、チャネル保護膜のみを先にエッチングし、ソース・ドレイン電極を形成した後に、保護膜のエッチングを行う。このため、端子部に形成するコンタクトホールは、保護膜のエッチングを行う際に、ゲート絶縁膜および保護膜を一括でエッチングすることにより形成される(GI/Pass同時エッチング)。しかしながら、この方法によると、前述したように、SiO2を用いてゲート絶縁膜や保護膜が形成されている場合には、エッチング時間が非常に長くなり、エッチングマスクとして用いるレジスト膜の表面がダメージを受けて、レジスト膜を基板から良好に剥離できないおそれがある。

【0084】

あるいは、特許文献2に開示された方法では、有機絶縁膜を上層、無機絶縁膜を下層とする積層構造の保護膜を形成し、有機絶縁膜をマスクとして、無機絶縁膜およびゲート絶縁膜をエッチングすることにより、端子部のコンタクトホールを形成していた(GI/Pass同時エッチング)。この方法でも、SiO2を用いて無機絶縁膜や保護膜が形成されている場合、エッチング時間が非常に長くなる。このため、エッチングの際に、マスクとして用いる有機絶縁膜の表面がダメージを受けるおそれがある。

【0085】

これに対し、本実施形態では、端子部のコンタクトホールは2段階に分けて形成される。すなわち、ゲート絶縁膜となる絶縁膜5と、チャネル保護膜(エッチストップ)形成用の絶縁膜9とに対するエッチングを同時に行い、開口部11cを形成する(GI/ES同時エッチング)。続いて、ソース・ドレイン電極形成後、上記のGI/ES同時エッチングとは別個に、保護膜15のエッチングを行い、保護膜15に開口部17cを形成する(Passエッチング)。一般に、保護膜15の厚さは、チャネル保護膜形成用の絶縁膜9の厚さよりも大きい。このため、本実施形態におけるGI/ES同時エッチングでは、従来のゲート絶縁膜と保護膜とを同時にエッチングするGI/Pass同時エッチングと比べて、エッチングされる膜(被エッチング膜)の合計厚さを小さくできる。従って、エッチング時間を大幅に短縮できるので、エッチングマスクへのダメージを低減できる。

【0086】

また、従来の方法によると、コンタクトホールのテーパー形状を制御することが困難となるおそれがある。端子部のコンタクトホールのテーパー形状は、従来の方法ではGI/Pass同時エッチングにおけるエッチング条件によって制御される。これに対し、本実施形態では主に保護膜15のみのエッチング(Passエッチング)におけるエッチング条件によって制御される。一般に、被エッチング膜の材料が同じ場合、被エッチング膜が薄い方が、エッチングマスク(レジスト膜)に与えるダメージを考慮する必要がないので、エッチング条件を選択しやすい。従って、本実施形態によると、従来の方法よりも被エッチング膜を薄くできるので、より高い精度でコンタクトホールの壁面のテーパー形状を制御することが可能となる。

【0087】

特に、ゲート絶縁膜および保護膜が何れも積層構造(例えば2層構造)を有する場合には、従来の方法では4層の膜に対してエッチングを行うことになり、テーパー形状の制御が非常に困難となる。本実施形態では、そのような場合でも、保護膜を構成する2層の膜に対するエッチングによってテーパー形状を制御できるので、テーパー形状の制御性を大幅に向上できる。

【0088】

このように、本実施形態によると、より確実に、コンタクトホールの壁面を基板の法線に対して所定の角度(テーパー角)で傾斜させることができるので、コンタクトホール上に形成される配線に切れが生じることを防止できる。よって、端子部におけるソース配線またはゲート配線と、駆動回路の入力部との電気的な接続を確保できる。

【0089】

さらに、従来は、ゲート・ソース接続部において、画素電極を形成するための透明導電膜を介して、ゲート配線とソース配線とを電気的に接続していた(例えば特許文献2の図4)。このため、ゲート・ソース接続部のコンタクトホールの壁面が基板の法線に対して十分に傾斜していないと、壁面を構成するソース配線と、壁面上に形成される透明導電膜とを電気的に接続できないという問題がある。

【0090】

これに対し、本実施形態によると、絶縁膜(ゲート絶縁膜)5と絶縁膜9とが同時にエッチングされるため、ゲート配線の接続部3dとソース配線13asとが直接接する構成のゲート・ソース接続部を形成できる。従って、たとえコンタクトホールの壁面がほとんど傾斜していなくても、コンタクトホールの壁面のテーパー形状に関わらず、ゲート配線3aとソース配線13asとをより確実に電気的に接続できる。

【0091】

さらに、本実施形態は、特許文献3に開示された構成と比べて、次のようなメリットも有している。

【0092】

特許文献3に開示された構成では、ゲート電極、ゲート絶縁膜および酸化物半導体層は、同一のマスクを用いてパターニングされている。これらの層の側壁は、エッチストップとして機能する絶縁膜で覆われている。この構成では、ゲート電極の側壁とソース電極との間には、エッチストップとして機能する絶縁膜しか設けられておらず、これらの電極間で短絡が生じる可能性があった。これに対し、本実施形態によると、ゲート絶縁膜となる絶縁膜5、酸化物半導体層7aおよびエッチストップとして機能する絶縁膜9は、チャネル長方向にゲート配線3aよりも長いので、ゲート配線3aの側壁は絶縁膜5、酸化物半導体層7aおよび絶縁膜9で覆われている。したがって、ゲート配線3aの上面および側壁とソース配線13asとの間、および、ゲート配線3aの上面および側壁とドレイン電極13adとの間には、少なくとも2層の絶縁膜(絶縁膜5および絶縁膜9)が存在する。このため、上述したような短絡を防止できる。また、絶縁膜5、特に絶縁膜5のうちゲート配線3aとソース・ドレイン電極13as、13adとの間に位置する部分に穴が開いているような場合でも、絶縁膜9でカバーできるので、これらの間に点欠陥が生じることを抑制できる。

【0093】

本実施形態では、絶縁膜5、絶縁膜9および保護膜15のうち少なくとも1つがSiO2を含むことが好ましい。これにより、これらの膜からTFTの活性層となる酸化物半導体層7aに酸素が供給されるので、酸化物半導体層7aに生じる酸素欠損をより低減できる。このため、酸素欠陥に起因して酸化物半導体層7aが低抵抗化されることを抑制できるので、リーク電流やヒステリシスを低減できる。特に、これらの絶縁膜のうち酸化物半導体層7a側の表面(すなわち絶縁膜5の上面、絶縁膜9の下面、保護膜15の下面)がSiO2から形成されているとより効果的である。

【0094】

また、チャネル保護膜9aを含む絶縁膜9は、島状の酸化物半導体層7aの上面全体(ただしソース・ドレイン領域を除く)および側壁全体を覆っていることが好ましい。このような構成によると、図1(d)に示すソース・ドレイン電極を形成するためのパターニング工程において、酸化物半導体層7aのチャネル領域およびその近傍に、酸化還元反応によって酸素欠陥が形成されることを抑制できる。この結果、酸素欠陥に起因して酸化物半導体層7aが低抵抗化されることを抑制できるので、リーク電流やヒステリシスを低減できる。また、絶縁膜9は、チャネル幅方向に酸化物半導体層7aよりも長く、酸化物半導体層7aの側壁の近傍に位置する絶縁膜5の上面とも接することが好ましい。これにより、絶縁膜9によって酸化物半導体層7aの上面のみでなく側壁もより確実に保護できる。

【0095】

本実施形態における酸化物半導体層7a、7bは、例えばZn−O系半導体(ZnO)、In−Ga−Zn−O系半導体(IGZO)、In−Zn−O系半導体(IZO)、またはZn−Ti−O系半導体(ZTO)からなる層であることが好ましい。

【0096】

(実施形態2)

以下、図面を参照しながら、本発明による実施形態2の半導体装置の製造方法を説明する。本実施形態は、補助容量電極として、ドレイン電極の代わりに画素電極を用いる点で、実施形態1と異なっている。

【0097】

図4(a)〜(f)は、本実施形態の半導体装置の製造方法を説明するための模式的な工程断面図である。簡単のため、図1と同様の構成要素には同じ参照符号を付し、説明を省略する。

【0098】

まず、図4(a)に示すように、基板1のうちTFTを形成しようとするTFT形成領域Aにゲート配線3a、補助容量を形成しようとする補助容量形成領域Bに補助容量配線3b、およびゲート・ソース端子を形成しようとする端子部形成領域Cに、ゲート配線の接続部3cを形成する。配線3a、3bおよび接続部3cの形成方法や材料は、図1(a)を参照しながら前述した方法および材料と同様である。

【0099】

次に、図4(b)に示すように、ゲート配線3a、補助容量配線3bおよび接続部3cを覆うように絶縁膜5を形成する。続いて、TFT形成領域AにTFTのチャネル層となる島状の酸化物半導体層7a、補助容量形成領域Bに島状の酸化物半導体層7bを形成する。絶縁膜5および酸化物半導体層7a、7bの形成方法や材料は、図1(b)を参照しながら前述した方法および材料と同様である。

【0100】

次いで、図4(c)に示すように、基板1の表面全体に絶縁膜9を堆積させた後、絶縁膜9をパターニングする。これにより、TFT形成領域Aでは、絶縁膜9のうちソースコンタクトおよびドレインコンタクトを形成する部分がエッチングされて、酸化物半導体層7aを露出する2つの開口部11as、11adが形成される。絶縁膜9は、酸化物半導体層7aのうちチャネルとなる領域を覆い、チャネル保護膜9aとして機能する。補助容量形成領域Bでは、絶縁膜9のうち酸化物半導体層7b上に位置する部分がエッチングされて、酸化物半導体層7bを露出する開口部11bが形成される。端子部形成領域Cでは、絶縁膜9のうち接続部3c上に位置する部分、および、その下の絶縁膜5が連続してエッチングされて、接続部3cの表面を露出する開口部11cが得られる。絶縁膜9の形成方法、材料およびエッチング方法は、図1(c)を参照しながら前述した方法および材料と同様である。

【0101】

続いて、図4(d)に示すように、基板1の表面全体に導電膜を堆積させた後、これをパターニングする。これにより、TFT形成領域Aでは、開口部11as、11adの内部および絶縁膜9上に、酸化物半導体層7aのうちチャネル領域となる領域の両側に位置する領域とそれぞれ接するように、ソース配線23asおよびドレイン電極23adをそれぞれ形成する。本実施形態におけるドレイン電極23adは、酸化物半導体層7aの一部を覆う島状のパターンを有しており、実施形態1のように補助容量形成領域Bまで延びていない。端子部形成領域Cでは、開口部11cの内部および絶縁膜9上に、接続部3cに接するように接続部23cを形成する。なお、本実施形態では、本エッチング工程によって、導電膜のうち、補助容量形成領域Bの酸化物半導体層7bの表面上(すなわち開口部11bの内部)に位置する部分も除去される。このようにして、TFT形成領域Aに酸化物半導体TFTが形成される。導電膜の材料や形成方法は、図1(d)を参照しながら前述した材料および方法と同様である。

【0102】

この後、図4(e)に示すように、基板1の表面全体に保護膜25を堆積させる。次いで、フォトリソグラフィ、ウェットエッチングおよびレジスト剥離洗浄工程により、保護膜25のパターニングを行う。これにより、TFT形成領域Aにおいて、保護膜25に、ドレイン電極23adの表面を露出する開口部27aを形成する。また、補助容量形成領域Bにおいて、酸化物半導体層7bの表面を露出する開口部27bを形成する。さらに、端子部形成領域Cにおいて、接続部23cを露出する開口部27cを形成する。保護膜25の材料、形成方法およびエッチング方法は、図1(e)を参照しながら前述した材料および方法と同様である。

【0103】

この後、図4(f)に示すように、保護膜25の上および開口部27a、27b、27c内に透明導電膜(例えばITO膜)を形成し、透明導電膜のパターニングを行う。これにより、ドレイン電極23adの露出した表面および酸化物半導体層7bと接する画素電極29と、接続部23cの露出した表面と接する接続部29cを形成する。

【0104】

本実施形態では、この工程によって、補助容量形成領域Bに補助容量Csが形成される。補助容量Csは、補助容量配線3bと、酸化物半導体層7bおよび画素電極29とを電極とし、絶縁膜5を誘電体として構成されている。

【0105】

図5および図6は、本実施形態の半導体装置を模式的に示す図である。図5(a)は、半導体装置における画素部201の平面図であり、図5(b)〜(d)は、それぞれ、半導体装置における端子配置領域202のゲート端子、ソース端子およびゲート・ソース接続部の平面図である。図6(a)は、図5(a)に示すI−I’線と、図5(b)に示すII−II’線または図5(c)に示すIII−III’線とに沿った断面図である。図6(b)は、図5(d)に示すIV−IV’線に沿った断面図である。

【0106】

これらの図からわかるように、各画素部201では、画素の行方向に沿って延びるソース配線23asと、画素の列方向に沿って延びるゲート配線3aおよび補助容量配線3bとが形成されている。ソース配線23asとゲート配線3aとの交差する点の近傍には、薄膜トランジスタTFTが形成されている。TFTの酸化物半導体層7aは、絶縁膜9の開口部11as、11ad内で、ソース配線23asおよびドレイン電極23adとそれぞれ接続されている。ドレイン電極23adは、保護膜25の開口部27a内で画素電極29と電気的に接続されている。

【0107】

補助容量配線3b上には補助容量Csが形成されている。補助容量Csの酸化物半導体層7bは、絶縁膜9の開口部11bおよび保護膜25の開口部27bからなるコンタクトホール内で、画素電極29と接続されている。従って、画素電極29は補助容量電極としても機能する。基板1の表面の法線方向から見て、開口部27bは、開口部11bの内部に配置されている。

【0108】

ゲート端子部およびソース端子部では、接続部3cは、絶縁膜5および絶縁膜9を同時にエッチングして得られた開口部11c内で、接続部23cと接続されている。接続部23cは、保護膜25の開口部27c内で接続部29cと接続されている。本実施形態でも、実施形態1と同様に、開口部11c内に接続部23cが形成された後に、保護膜25に開口部27cが形成されるので、接続部23cは開口部11cにおける絶縁膜5、9の端面(開口部11cの壁面)を覆い、かつ、開口部27cにおける保護膜25の端面(開口部27cの壁面)を覆っていない。また、基板1の表面の法線方向から見て、開口部27cは、開口部11c内に配置されている。

【0109】

本実施形態でも、基板1の端子配置領域202にゲート・ソース接続部が形成される場合がある。ゲート・ソース接続部では、ゲート配線の接続部3dは、絶縁膜5および絶縁膜9を同時にエッチングして得られた開口部11c内で、ソース配線23asと直接接続されている。ソース配線23asは保護膜25で覆われている。

【0110】

本実施形態によると、ゲート絶縁膜となる絶縁膜5およびチャネル保護膜(エッチストップ)形成用の絶縁膜9に対するエッチング(GI/ES同時エッチング)と、保護膜25のエッチング(Passエッチング)とによって、端子部のコンタクトホールを形成する。このため、ゲート絶縁膜および保護膜を同時にエッチングする従来の方法よりも、エッチング時間を大幅に短縮できる。従って、実施形態1と同様に、エッチングマスクへのダメージを低減できる。また、より高い精度でコンタクトホールの壁面のテーパー形状を制御することが可能となる。さらに、ゲート・ソース接続部において、ゲート配線の接続部3dとソース配線23asとを直接接続させることが可能になるので、ゲート・ソース接続部のコンタクトホールの壁面のテーパー形状に関わらず、ゲート配線の接続部3dとソース配線23asとをより確実に電気的に接続することができる。

【0111】

その上、本実施形態によると、実施形態1と異なり、次のようなメリットもある。実施形態1では、ドレイン電極の島状パターンが補助容量Csまで延びて、補助容量電極として用いられる。これに対し、本実施形態では、補助容量Csにドレイン電極が形成されていない。この構造は、ソース配線23as、ドレイン電極23adおよび接続部23cを形成するための導電膜のパターニング工程(図4(d))において、補助容量形成領域Bの酸化物半導体層7bがエッチストップとして機能することによって実現できる。

【0112】

通常、実施形態1のようにドレイン電極を補助容量電極として用いる場合、ドレイン電極と補助容量配線とが確実に重なるようにマージンを設ける必要がある。このため、補助容量配線およびドレイン電極のうち何れか一方の平面形状が大きくなるように設計される。例えば実施形態1では、補助容量配線の幅よりも、その上のドレイン電極の幅が大きくなるように設計されている。ドレイン電極および補助容量電極は何れも金属膜などから形成されており、これらの平面形状が大きくなると、開口率が低下する要因となる。

【0113】

一方、本実施形態でも、補助容量配線3bと、酸化物半導体層7bおよび画素電極29とが確実に重なるようにマージンを設ける必要がある。このため、酸化物半導体層7bおよび画素電極29の幅が、補助容量配線3bの幅よりも大きくなるように設計されている。しかしながら、酸化物半導体層7bおよび画素電極29は何れも透明であり、これらのパターンを拡大しても、開口率を低下させる要因とはならない。従って、実施形態1よりも、開口率を高めることができる。

【0114】

(実施形態3)

以下、図面を参照しながら、本発明による実施形態3の半導体装置の製造方法を説明する。本実施形態は、保護膜と画素電極との間に有機絶縁膜を形成する点で、前述の実施形態と異なっている。

【0115】

図7(a)〜(c)は、本実施形態の半導体装置の製造方法を説明するための模式的な工程断面図である。簡単のため、図4と同様の構成要素には同じ参照符号を付し、説明を省略する。

【0116】

まず、図7(a)に示すように、実施形態2と同様の方法(図4(a)〜(d))により、基板1上に、ゲート配線3a、補助容量配線3b、接続部3c、絶縁膜5、酸化物半導体層7a、7b、絶縁膜9、ソース配線23as、ドレイン電極23adおよび接続部23cを形成する。

【0117】

次に、図7(b)に示すように、基板1の表面に、保護膜25および有機絶縁膜36をこの順で形成する。ここでは、保護膜25として、例えば厚さが50nm〜300nmの酸化物膜をCVD法により形成する。また、有機絶縁膜36として、例えば厚さが1μm以上4μm以下のアクリル系樹脂膜を塗布することにより形成する。有機絶縁膜36によって基板1の表面は平坦化されることが好ましい。

【0118】

次いで、フォトリソグラフィにより有機絶縁膜36のパターニングを行った後、有機絶縁膜36をマスクとして、保護膜25をドライエッチングによってパターニングする。これにより、TFT形成領域Aにおいて、保護膜25および有機絶縁膜36に、ドレイン電極23adの表面を露出する開口部37aを形成する。また、補助容量形成領域Bにおいて、酸化物半導体層7bの表面を露出する開口部37bを形成する。さらに、端子部形成領域Cにおいて、接続部23cを露出する開口部37cを形成する。

【0119】

この後、図7(c)に示すように、保護膜25の上および開口部37a、37b、37c内に透明導電膜(例えばITO膜)を形成し、透明導電膜のパターニングを行う。これにより、ドレイン電極23adの露出した表面および酸化物半導体層7bと接する画素電極29と、接続部23cの露出した表面と接する接続部29cとを形成する。画素電極29は、補助容量Csの電極としても機能する。このようにして、本実施形態の半導体装置を得る。

【0120】

本実施形態の半導体装置の平面図は、図5を参照しながら前述した実施形態2の半導体装置の平面図と同様である。ただし、図5に示す保護膜25の開口部27a、27b、27cは、本実施形態では、保護膜25および有機絶縁膜36の開口部37a、37b、37cとなる。また、本実施形態におけるゲート・ソース接続部の断面図は、図6(b)に示す実施形態2のゲート・ソース接続部の断面図と同様である。

【0121】

本実施形態によると、ゲート絶縁膜となる絶縁膜5およびチャネル保護膜(エッチストップ)形成用の絶縁膜9に対するエッチング(GI/ES同時エッチング)と、有機絶縁膜36のエッチングおよび保護膜25のエッチング(Passエッチング)とによって、端子部のコンタクトホールを形成する。このため、ゲート絶縁膜および保護膜を同時にエッチングする従来の方法よりも、エッチング時間を大幅に短縮できる。従って、前述の実施形態と同様に、エッチングマスクへのダメージを低減できる。また、より高い精度でコンタクトホールの壁面のテーパー形状を制御することが可能となる。さらに、ゲート・ソース接続部において、ゲート配線の接続部3dとソース配線23asとをより確実に電気的に接続することができる。その上、実施形態2と同様に、開口率を低下させることなく、補助容量配線3bと、酸化物半導体層7bおよび画素電極29との重なりマージンを設けることができる。

【0122】

また、本実施形態によると、端子部のコンタクトホール内部で接続部23cに断切れが生じた場合であっても、ゲート配線3cと接続部29cとの電気的接続をより確実に確保できるというメリットもある。

【0123】

図8は、接続部23cに断切れが生じた場合の端子部を例示する拡大断面図である。図示するように、絶縁膜5および絶縁膜9からなる開口部11cの壁面が所望のテーパー形状を有していない場合(例えば開口部11cの壁面が基板1の表面に略垂直になるような場合)、開口部11cの内部に形成された接続部23cに断切れが生じることがある。接続部23cに断切れが生じると、保護膜25は、断切れを生じた接続部23c上のみにCVD法などによって堆積される。一方、有機絶縁膜36は、開口部11cの壁面を覆うように塗布されるので、断切れによって生じた空間が埋められて、より滑らかな壁面を有する開口部37cが得られる。このため、開口部37c内に堆積される接続部29cには断切れが生じにくい。この結果、図示するように、たとえ接続部23cに断切れが生じても、接続部23cを介して、接続部29cとゲート配線3cとを電気的に接続することができる。

【0124】

なお、特許文献1に開示された方法のように、保護膜上に有機絶縁膜を設けた場合でも、無機絶縁膜およびゲート絶縁膜を同時にエッチング(Pass/GI同時エッチング)すると、図8を参照して説明したようなメリットは得られないと考えられる。前述したように、酸化物半導体TFTでは、ゲート絶縁膜、チャネル保護膜および保護膜としてSiO2膜を用いることが好ましい。SiO2膜はSiNx膜よりもエッチレートが低いので、Pass/GI同時エッチングの際に、エッチングマスクである有機絶縁膜の表面状態やテーパー形状を制御することが困難だからである。

【0125】

本実施形態の半導体装置の構成は、図7を参照しながら上述した構成に限定されない。図9および図10は、本実施形態の半導体装置の他の例を示す断面図である。

【0126】

図7に示す例では、保護膜25上に有機絶縁膜36を形成しているが、代わりに、図9に示すように、実施形態1の半導体装置における保護膜15上に有機絶縁膜36を形成してもよい。図9に示す半導体装置の平面図は、図2に示す実施形態1の半導体装置の平面図と同様である。ただし、図2に示す保護膜15の開口部17b、17cは、本実施形態では、保護膜15および有機絶縁膜36の開口部となる。また、ゲート・ソース接続部の断面図は、図3(b)に示す実施形態1のゲート・ソース接続部の断面図と同様である。図9に示す半導体装置によると、実施形態1と同様の効果が得られる。また、図8を参照しながら前述したように、接続部13cに断切れが生じても、端子部における配線間の電気的な接続を確保できる。

【0127】

また、図7に示す例では、端子部形成領域Cにも保護膜25および有機絶縁膜36が形成されているが、図10に示すように、端子部形成領域Cに保護膜25および有機絶縁膜36を形成しなくてもよい。さらに、図9に示すように、保護膜15上に有機絶縁膜36を形成する場合でも、端子部形成領域Cに保護膜15および有機絶縁膜36を形成しなくてもよい。

【0128】

(実施形態4)

以下、図面を参照しながら、本発明による実施形態4の半導体装置の製造方法を説明する。本実施形態は、ゲート絶縁膜として、SiNx膜を下層とし、SiO2膜を上層とする積層膜を形成し、保護膜として、SiO2膜を下層とし、SiNx膜を上層とする積層膜を形成する点で、前述の実施形態と異なっている。

【0129】

図11(a)〜(c)は、本実施形態の半導体装置の製造方法を説明するための模式的な工程断面図である。簡単のため、図4と同様の構成要素には同じ参照符号を付し、説明を省略する。

【0130】

まず、図11(a)に示すように、基板1上に、ゲート配線3a、補助容量配線3b、接続部3cを形成する。ゲート配線3a、補助容量配線3b、接続部3cの形成方法は、図1(a)を参照しながら前述した方法と同様である。

【0131】

次いで、図11(b)に示すように、ゲート配線3a、補助容量配線3bおよび接続部3cを覆うように、SiNx膜5LおよびSiO2膜5Uをこの順で形成することにより、絶縁膜5を得る。この後、絶縁膜5の上に、酸化物半導体層7a、7bを形成する。

【0132】

ここでは、CVD法により、厚さが例えば200nm以上500nm以下のSiNx膜5L、および、厚さが例えば20nm以上150nm以下のSiO2膜5Uを形成する。酸化物半導体層7a、7bは、スパッタ法により、厚さが例えば30nm以上300nm以下のIGZO膜を形成し、これをパターニングすることによって得られる。酸化物半導体層7a、7bの形成方法は、図1(b)を参照しながら前述した方法と同様である。

【0133】

続いて、図示しないが、図1(c)を参照しながら前述した方法で、基板1の表面に絶縁膜9を堆積する。この後、TFT形成領域Aにおいて、絶縁膜9にソースコンタクト形成用の開口部、ドレインコンタクト形成用の開口部を形成し、補助容量形成領域Bにおいて、絶縁膜9に酸化物半導体層7bを露出する開口部を形成する。これと同時に、端子部形成領域Cにおいて、絶縁膜9および絶縁膜5をエッチングして開口部を形成する。次いで、図4(d)を参照しながら前述した方法で、絶縁膜9上および絶縁膜9の開口部内に金属膜を形成し、これをパターニングすることにより、ソース配線23as、ドレイン電極23adおよび接続部23cを形成する。

【0134】

この後、図11(c)に示すように、基板1の表面に、SiO2膜25LおよびSiNx膜25Uをこの順で形成することにより、保護膜25を形成する。本実施形態では、ここでは、CVD法により、厚さが例えば50nm以上150nm以下のSiO2膜25L、および、厚さが例えば50nm以上200nm以下のSiNx膜25Uを形成する。

【0135】

次いで、フォトリソグラフィ、ウェットエッチングおよびレジスト剥離洗浄工程により、保護膜25のパターニングを行う。これにより、TFT形成領域Aにおいて、保護膜25に、ドレイン電極23adの表面を露出する開口部27aを形成する。また、補助容量形成領域Bにおいて、酸化物半導体層7bの表面を露出する開口部27bを形成する。さらに、端子部形成領域Cにおいて、接続部23cを露出する開口部27cを形成する。

【0136】

図示しないが、この後、図4(f)を参照しながら前述したように、保護膜25の上および開口部27a、27b、27c内に透明導電膜(例えばITO膜)を形成し、透明導電膜のパターニングを行う。これにより、ドレイン電極23adの露出した表面および酸化物半導体層7bと接する画素電極29と、接続部23cの露出した表面と接する接続部29cとを形成する。

【0137】

本実施形態の半導体装置の平面図は、図5を参照しながら前述した実施形態2の半導体装置の平面図と同様である。また、本実施形態におけるゲート・ソース接続部の断面図は、図6(b)に示す実施形態2のゲート・ソース接続部の断面図と同様である。

【0138】

本実施形態によると、実施形態2と同様の効果が得られる。また、絶縁膜(ゲート絶縁膜)5および保護膜25として、SiO2膜およびSiNx膜からなる積層膜を用いると、次のようなメリットが得られる。

【0139】

酸化物半導体TFTでは、ゲート絶縁膜および保護膜としてSiNx膜を単層で用いると、製造プロセスにおいて、酸化物半導体層がSiNxと触れた状態で加熱処理が行われるので、酸化物半導体層中の酸素が還元される可能性がある。また、SiNx膜を形成する際に酸化物半導体層がプラズマダメージを受けやすい。この結果、酸化物半導体TFTの特性が低下するおそれがある。一方、ゲート絶縁膜および保護膜としてSiO2膜を単層で用いると、上記のような問題は生じないが、SiO2膜はSiNx膜よりも誘電率が低いために、ソース−ゲート間の耐圧を確保するためには、SiO2膜を厚くする必要がある。このため、TFTのオン電流の低下を引き起こす要因となる。

【0140】

これに対し、ゲート絶縁膜および保護膜として、SiO2膜およびSiNx膜からなる積層膜を用いると、SiO2膜のみからなるゲート絶縁膜や保護膜より薄くても、十分な耐圧を確保できる。従って、ゲート絶縁膜および保護膜によるTFTのオン電流の低下を抑制できる。さらに、積層膜のうち酸化物半導体層に接する膜、または酸化物半導体層に最も近接する膜にSiO2膜を配置することにより、酸化物半導体層の酸素がSiNxによって還元されたり、SiNx膜を形成する際に酸化物半導体層がプラズマダメージを受けることを防止できる。

【0141】

本実施形態における絶縁膜5は、SiO2膜およびSiNx膜を含む積層構造を有し、かつ、積層構造の最上層、すなわち酸化物半導体層の下面と接する層がSiO2膜であればよい。同様に、保護膜25は、SiO2膜およびSiNx膜を含む積層構造を有し、かつ、積層構造の最下層、すなわち最も酸化物半導体層側に位置する層がSiO2膜であればよい。図11に示す例では、絶縁膜5および保護膜25が何れも積層構造を有するが、これらのうち一方のみが上記のような積層構造を有していれば、上記の効果を得ることができる。ただし、これらの膜5、25が両方とも上記のような積層構造を有していればより顕著な効果が得られる。

【0142】

なお、従来の方法では、保護膜およびゲート絶縁膜に対するエッチングを同時に行うので(Pass/GI同時エッチング)、これらの膜が上記のような積層膜であると、SiNx/SiO2/SiO2/SiNxからなる膜を一括してエッチングする。言い換えると、ドライエッチレートが互いに異なる3層(SiNx/SiO2/SiNx)を一括してエッチングする。このため、エッチングの際のテーパー制御は極めて難しい。SiNx膜の方がSiO2膜よりもドライエッチレートが数倍高いため、これらの積層膜をエッチングすると、SiNx膜がシフトしてかさ状になることがある。また、特許文献1のように保護膜上に有機絶縁膜を設けると、Pass/GI同時エッチングの際に、エッチングマスクである有機絶縁膜の表面ダメージも制御することが必要となるため、テーパー制御はほとんど不可能となる。

【0143】

これに対し、本実施形態によると、ES/GI同時エッチングにおいてSiO2/SiNx、保護膜(Passエッチング)においてSiNx/SiO2の2層のみに対してエッチングを行うので、SiNx/SiO2/SiNxの3層をエッチングする従来方法よりも高い精度でテーパー制御を行うことができる。

【0144】

なお、実施形態3で説明したように、本実施形態の半導体装置においても保護膜25と画素電極29との間に有機絶縁膜を設けてもよい。この場合でも、絶縁膜5、9の同時エッチングとは別個に、有機絶縁膜をエッチングマスクとして保護膜(SINx/SiO2)25のエッチングを行ってもよい(Passエッチング)。これにより、有機絶縁膜の表面ダメージを抑えつつ、保護膜25の開口部のテーパー形状を制御できる。

【0145】

なお、図11に示す例では、実施形態2の半導体装置における絶縁膜5および保護膜25として、SiNx膜およびSiO2膜からなる積層膜を用いているが、実施形態1の半導体装置における絶縁膜5および保護膜15として、SiO2およびSiNxからなる積層膜を用いてもよい。これにより、上記と同様の効果が得られる。すなわち、テーパー形状の制御性を低下させることなく、TFT特性の低下を抑制できる。この場合でも、保護膜15と画素電極19との間に、実施形態3で説明したような有機絶縁膜を設けてもよい。

【産業上の利用可能性】

【0146】

本発明は、アクティブマトリクス基板等の回路基板、液晶表示装置、有機エレクトロルミネセンス(EL)表示装置および無機エレクトロルミネセンス表示装置等の表示装置、イメージセンサー装置等の撮像装置、画像入力装置や指紋読み取り装置等の電子装置などの薄膜トランジスタを備えた装置に広く適用できる。特に、大型の液晶表示装置等に好適に適用され得る。

【符号の説明】

【0147】

1 基板

3a ゲート配線

3b 補助容量配線

3c 接続部

3d 接続部

5 絶縁膜(ゲート絶縁膜)

5L ゲート絶縁膜の下層

5U ゲート絶縁膜の上層

7a、7b 酸化物半導体層(活性層)

9 絶縁膜(保護膜、エッチストッパ)

11as、11ad、11b、11c、11d、17b、17c、27a、27b、27c、37a、37b、37c 開口部

13as、23as ソース配線

13ad、23ad ドレイン電極

13c、23c、19c、29c 接続部

15、25 保護膜

19、29 画素電極

36 有機絶縁膜

25L 保護膜の下層

25U 保護膜の上層

101、201 表示領域における1個の画素部

102、202 端子配置領域

【技術分野】

【0001】

本発明は、薄膜トランジスタを備える半導体装置およびその製造方法に関する。

【背景技術】

【0002】

アクティブマトリクス型の液晶表示装置や有機EL表示装置は、一般に、画素毎にスイッチング素子として薄膜トランジスタ(Thin Film Transistor;以下、「TFT」)が形成された基板(以下、「TFT基板」)と、対向電極およびカラーフィルターなどが形成された対向基板と、TFT基板と対向基板との間に設けられた液晶層などの光変調層とを備えている。

【0003】

TFT基板には、複数のソース配線と、複数のゲート配線と、これらの交差部にそれぞれ配置された複数のTFTと、液晶層などの光変調層に電圧を印加するための画素電極と、補助容量配線および補助容量電極などが形成されている。また、TFT基板の端部には、ソース配線およびゲート配線を、駆動回路の入力端子にそれぞれ接続するための端子部が設けられている。駆動回路は、TFT基板上に形成されていてもよいし、別個の基板(回路基板)上に形成されていてもよい。

【0004】

TFT基板の構成は、例えば特許文献1に開示されている。以下、図面を参照しながら、特許文献1に開示されたTFT基板の構成を説明する。

【0005】

図12(a)は、TFT基板の概略を示す模式的な平面図であり、図12(b)は、TFT基板における1個の画素を示す拡大平面図である。また、図13は、図12に示す半導体装置におけるTFTおよび端子部の断面図である。

【0006】

図12(a)に示すように、TFT基板は、複数のゲート配線2016と、複数のソース配線2017とを有している。これらの配線2016、2017で包囲されたそれぞれの領域2021が「画素」となる。TFT基板のうち画素が形成される領域(表示領域)以外の領域2040には、複数のゲート配線2016およびソース配線2017のそれぞれを駆動回路に接続するための複数の接続部2041が配置されている。各接続部2041は、外部配線と接続するための端子部を構成する。なお、本明細書では、複数の端子部が配置されるTFT基板の領域2040を「端子配置領域」と呼ぶ。

【0007】

図12(b)および図13に示すように、画素となる各領域2021を覆うように画素電極2020が設けられている。また、各領域2021にはTFTが形成されている。TFTは、ゲート電極Gと、ゲート電極Gを覆うゲート絶縁膜2025、2026と、ゲート絶縁膜2026上に配置された半導体層2019と、半導体層2019の両端部にそれぞれ接続されたソース電極Sおよびドレイン電極Dとを有している。TFTは保護膜2028で覆われている。保護膜2028と画素電極2020との間には、層間絶縁膜2029が形成されている。TFTのソース電極Sはソース配線2017に、ゲート電極Gはゲート配線2016に接続されている。また、ドレイン電極Dは、コンタクトホール2030内で画素電極2020に接続されている。

【0008】

また、ゲート配線2016と平行に補助容量配線2018が形成されている。補助容量配線2018は補助容量に接続されている。ここでは、補助容量は、ドレイン電極と同じ導電膜から形成された補助容量電極2018bと、ゲート配線と同じ導電膜から形成された補助容量電極2018aと、それらの間に位置するゲート絶縁膜2026とから構成されている。

【0009】

各ゲート配線2016またはソース配線2017から延びた接続部2041上には、ゲート絶縁膜2025、2026および保護膜2028が形成されておらず、接続部2041の上面と接するように接続配線2044が形成されている。これにより、接続部2041と接続配線2044との電気的な接続が確保されている。

【0010】

なお、図13に示すように、液晶表示装置では、TFT基板2013は、液晶層2015を挟んで、対向電極やカラーフィルターが形成された基板2014と対向するように配置される。

【0011】

このようなTFT基板を製造する際には、画素となる領域2021(「画素部」ともいう。)と、端子部とを共通のプロセスで形成し、マスク数や工程数の増大を抑えることが好ましい。

【0012】

上記のTFT基板を製造しようとすると、ゲート絶縁膜2025、2026および保護膜2028のうち端子配置領域2040に位置する部分、および、ゲート絶縁膜2025および保護膜2028のうち補助容量が形成される領域に位置する部分をエッチングする必要がある。特許文献1では、有機絶縁膜を用いて層間絶縁膜2029を形成し、これをマスクとして、これらの絶縁膜2025、2026および保護膜2028をエッチングすることが開示されている。

【0013】

一方、近年、シリコン半導体膜の代わりに、酸化亜鉛などの酸化物半導体膜を用いてTFTの活性層を形成することが提案されている。このようなTFTを「酸化物半導体TFT」と称する。酸化物半導体は、アモルファスシリコンよりも高い移動度を有している。このため、酸化物半導体TFTは、アモルファスシリコンTFTよりも高速で動作することが可能である。また、酸化物半導体膜は、多結晶シリコン膜よりも簡便なプロセスで形成されるため、大面積が必要とされる装置にも適用できる。

【0014】

しかしながら、ボトムゲート構造を有する酸化物半導体TFTでは、TFTの製造プロセス中、例えば熱処理工程などにおいて、酸素欠陥によってキャリア電子が生じ、抵抗が低くなるおそれがある。また、ソース・ドレイン電極のエッチング工程や層間絶縁膜の形成工程において、その下方にある酸化物半導体膜がダメージを受けやすいという問題がある。

【0015】

これに対し、半導体層のうちチャネルが形成される領域(チャネル形成領域)を覆うようにチャネル保護膜を設ける構造(チャネル保護型)が提案されている。TFTの製造プロセスにおいて、半導体層上にチャネル保護膜を形成した後、ソース・ドレイン電極を形成すると、ソース・ドレイン電極を形成するためのエッチングを行う際に、チャネル保護膜がエッチストップとして機能する。このため、チャネル形成領域がエッチングによって受けるダメージを低減できる。

【0016】

特許文献2には、チャネル保護型のTFTを有するTFT基板の画素部の構成が記載されている。ただし、特許文献2のTFTは、シリコン膜を用いて形成されている。

【0017】

図14は、特許文献2に記載されたTFT基板の一部を示す断面図である。TFT基板の各画素には、薄膜トランジスタ1141および補助容量1142が設けられている。薄膜トランジスタ1141には、ゲート配線1102、ゲート絶縁膜1104、チャネル形成領域を有する半導体層1113、チャネル保護膜1108、ソース領域1118、ドレイン領域1117、ドレイン電極1121およびソース配線1122が形成されている。薄膜トランジスタ1141は保護膜1127で覆われており、保護膜1127上には画素電極1131が設けられている。画素電極1131は、保護膜1127に形成されたコンタクトホール内でドレイン電極1121と接続されている。補助容量1142は、ゲート配線1102と同じ導電膜から形成された容量配線1151と、画素電極1131を電極とし、電極間に挟まれたゲート絶縁膜1104および保護膜1127を誘電体として構成されている。

【0018】

なお、本明細書では、半導体層のチャネル形成領域とソース・ドレイン電極との間に形成された絶縁膜を「チャネル保護膜」または「エッチストッパ」と呼び、TFTを覆う絶縁膜、ボトムゲート構造の場合にはソース・ドレイン電極上に設けられる絶縁膜を、単に「保護膜」と呼んで両者を区別する。

【0019】

図示されていないが、このTFT基板における端子部では、ゲート配線1102上のゲート絶縁膜1104および保護膜1127に形成されたコンタクトホール内で、ゲート配線1102と、保護膜1127上に設けられる外部配線とを電気的に接続させることができる。

【0020】

上記の半導体装置の製造方法では、チャネル保護膜1108を形成するためのエッチングと、ソース・ドレイン電極1121、1122を形成するためのエッチングと、保護膜1127にコンタクトホールを形成するためのエッチングとが行われる(特許文献2の図7〜図9)。端子部のコンタクトホールは、保護膜1127のエッチングを行う際に、保護膜1127およびゲート絶縁膜1104を一括してエッチングすることによって形成されると考えられる。

【0021】

なお、特許文献3には、チャネル保護型のTFTを備えたTFT基板の製造方法において、ハーフトーンマスクを利用することによって、使用するマスクの数を低減することが提案されている。しかしながら、特許文献3の方法は、製造プロセスが複雑で、量産性が低くなるおそれがある。また、ゲート電極とソース・ドレイン電極との間に絶縁膜が1層しか形成されていないため、これらの電極間で短絡が生じる可能性がある。

【先行技術文献】

【特許文献】

【0022】

【特許文献1】特開2008−170664号公報

【特許文献2】特開2009−157354号公報

【特許文献3】特開2007−258675号公報

【発明の概要】

【発明が解決しようとする課題】

【0023】

特許文献1、2に開示された方法によると、TFT基板の端子部において、ゲート絶縁膜および保護膜を同時にエッチングする必要がある。本発明者が検討したところ、このような方法を酸化物半導体TFTを備えるTFT基板に適用すると、次のような問題があることを見出した。

【0024】

一般に、酸化物半導体TFTでは、ゲート絶縁膜や保護膜としてSiO2膜などの酸化物膜が用いられることが多い。これは、酸化物半導体層に酸素欠損が生じた場合に、酸化物膜に含まれる酸素によって酸素欠損を回復できるからである。

【0025】

特許文献1によると、TFT基板(図12、図13)を製造する際には、有機絶縁膜を用いて層間絶縁膜2029を形成し、これをマスクとして、ゲート絶縁膜2025、2026および保護膜2028のうち端子配置領域2040に位置する部分をエッチングすることにより、端子部のコンタクトホールが形成される。このとき、ゲート絶縁膜2025、2026および保護膜2028のうち何れかの材料としてSiO2が用いられていれば、SiO2のエッチレートが非常に低いために、エッチング時間が長くなる。この結果、マスクである有機絶縁膜(層間絶縁膜)2029がダメージを受けるおそれがある。

【0026】

特許文献2では、端子部のコンタクトホールは、レジストマスクを用いて、保護膜1127およびゲート絶縁膜1104を一括してエッチングすることによって形成されると考えられる。このとき、保護膜1127およびゲート絶縁膜1104の何れかの材料としてSiO2が用いられていれば、SiO2のエッチレートが非常に低いために、エッチング工程でレジストマスクがダメージを受けて、レジストマスクの剥離不良が生じる可能性がある。また、エッチレートが低いと、端子部のコンタクトホールの壁面に所望のテーパー形状を形成し難くなり、壁面が基板に対して略垂直になる可能性がある。このような場合、端子部のコンタクトホール内に形成される配線に切れが生じやすくなるという問題もある。

【0027】

このように、従来は、ソース端子やゲート端子を形成するためのエッチング工程において、エッチングマスクがダメージを受けたり、あるいは、コンタクトホールのテーパー形状を最適化できずに配線の断切れを生じさせるおそれがあり、TFT基板の信頼性を低下させる可能性があった。

【0028】

本発明は、上記事情を解決するためになされたものであり、その主な目的は、酸化物半導体TFTと、TFTの電極と外部配線とを接続する端子部とを備える半導体装置において、端子部のコンタクトホールを形成する際に、マスクへのダメージを低減するとともに、高い精度でコンタクトホールの壁面のテーパー形状を制御することにある。

【課題を解決するための手段】

【0029】

本発明の半導体装置は、基板と、前記基板上に形成された薄膜トランジスタと、前記薄膜トランジスタと外部配線とを電気的に接続する端子部とを備えた半導体装置であって、前記薄膜トランジスタは、前記基板上に設けられたゲート配線と、前記ゲート配線上に形成された第1絶縁膜と、前記第1絶縁膜上に形成され、チャネル領域と、前記チャネル領域の両側にそれぞれ位置するソース領域およびドレイン領域とを有する島状の酸化物半導体層と、前記酸化物半導体層上に接して設けられた第2絶縁膜と、前記第2絶縁膜上に設けられ、前記ソース領域と電気的に接続されたソース配線と、前記第2絶縁膜上に設けられ、前記ドレイン領域と電気的に接続されたドレイン電極と、前記ソース配線および前記ドレイン電極上に設けられ、前記薄膜トランジスタを覆う保護膜とを備え、前記端子部は、前記ゲート配線と同一の導電膜から形成された第1接続部と、前記第1接続部上に形成され、前記ソース配線および前記ドレイン電極と同一の導電膜から形成された第2接続部と、前記第2接続部上に形成された第3接続部とを備え、前記第2接続部は、前記第1絶縁膜および前記第2絶縁膜に設けられた第1開口部内で、前記第1接続部と接しており、前記第3接続部は、前記保護膜に設けられた第2開口部内で、前記第2接続部と接しており、前記第2接続部は、前記第1開口部における前記第1絶縁膜および前記第2絶縁膜の端面を覆い、かつ、前記第2開口部における前記保護膜の端面を覆っていない。

【0030】

ある好ましい実施形態において、前記基板の表面の法線方向から見て、前記第2開口部は、前記第1開口部の内部に位置する。

【0031】

前記ドレイン電極と電気的に接続された画素電極をさらに備え、前記第3接続部は、前記画素電極と同一の導電膜から形成されていてもよい。

【0032】

ある好ましい実施形態において、前記基板に形成された補助容量をさらに備え、前記補助容量は、前記ゲート配線と同一の導電膜から形成された補助容量配線と、前記補助容量配線を覆う前記第1絶縁膜と、前記酸化物半導体層と同一の酸化物半導体膜から形成された補助容量形成用半導体層と、前記補助容量形成用半導体層上に設けられた補助容量電極とを有しており、前記補助容量電極は、前記第2絶縁膜に形成された開口部内で前記補助容量形成用半導体層と接している。

【0033】

ある好ましい実施形態において、前記補助容量電極は、前記ドレイン電極の一部であり、前記画素電極は、前記保護膜に形成された開口部内で前記補助容量電極に接している。

【0034】

ある好ましい実施形態において、前記補助容量電極は、前記画素電極の一部である。

【0035】

前記ゲート配線と前記ソース配線とを電気的に接続するゲート・ソース接続部をさらに備え、前記ゲート・ソース接続部では、前記ソース配線は、前記第1絶縁膜および前記第2絶縁膜に設けられた前記第1開口部内で前記ゲート配線に接していてもよい。

【0036】

前記保護膜と前記画素電極との間に、有機絶縁膜をさらに備えていてもよい。

【0037】

前記第1絶縁膜および前記保護膜のうち少なくとも一方はSiO2を含むことが好ましい。

【0038】

前記第1絶縁膜は、SiO2膜およびSiNx膜を含む積層構造を有しており、前記SiO2膜は前記積層構造の最上層であり、前記酸化物半導体層の下面と接していてもよい。

【0039】

前記保護膜は、SiO2膜およびSiNx膜を含む積層構造を有しており、前記SiO2膜は前記積層構造の最下層であってもよい。

【0040】

ある好ましい実施形態において、前記ゲート配線の上面および側壁と前記ソース配線との間、および、前記ゲート配線の上面および側壁と前記ドレイン電極との間には、少なくとも前記第1絶縁膜および前記酸化物半導体層が設けられている。

【0041】

前記ゲート配線の上面および側壁と前記ソース配線との間、および、前記ゲート配線の上面および側壁と前記ドレイン電極との間に、前記第2絶縁膜がさらに設けられていてもよい。

【0042】

前記第2絶縁膜は、前記酸化物半導体層の表面のうち前記ソース領域および前記ドレイン領域を除く全ての上面および側壁を覆っており、かつ、前記酸化物半導体層の側壁近傍で前記第1絶縁膜の上面と接していてもよい。

【0043】

前記酸化物半導体層のチャネル長方向に沿った幅は、前記ゲート配線のチャネル長方向に沿った幅よりも大きくてもよい。

【0044】

本発明の半導体装置の製造方法は、上記のいずれかに記載の半導体装置の製造方法であって、(A)基板上にゲート配線用導電膜を形成し、これをパターニングすることによって、ゲート配線および第1接続部を形成する工程と、(B)前記ゲート配線および前記第1接続部上に、第1絶縁膜を形成する工程と、(C)前記第1絶縁膜上に、薄膜トランジスタの活性層となる酸化物半導体層を形成する工程と、(D)前記酸化物半導体層および前記第1絶縁膜を覆う第2絶縁膜を形成する工程と、(E)前記酸化物半導体層をエッチストップとして前記第1および第2絶縁膜のエッチングを行うことにより、前記第2絶縁膜に、前記酸化物半導体層を露出するソースコンタクト形成用開口部およびドレインコンタクト形成用開口部を形成するとともに、前記第2絶縁膜および前記第1絶縁膜に、前記第1接続部の表面を露出する第1開口部を形成する工程と、(F)前記第2絶縁膜上にソース・ドレイン電極用導電膜を形成し、これをパターニングすることによって、前記ソースコンタクト形成用開口部内で前記酸化物半導体層に接するソース配線と、前記ドレインコンタクト形成用開口部内で前記酸化物半導体層に接するドレイン電極と、前記第1開口部内で前記第1接続部に接する第2接続部を形成する工程と、(G)前記ソース配線、前記ドレイン電極および前記第2接続部上に保護膜を形成する工程と、(H)前記保護膜に、前記第2接続部を露出する第2開口部を形成する工程と、(I)前記保護膜上に、前記第2開口部内で前記第2接続部に接する第3接続部を形成する工程とを包含する。

【0045】

前記工程(H)は、前記保護膜に、前記ドレイン電極を露出する開口部を形成する工程を含み、前記工程(I)は、前記保護膜上に透明導電膜を形成し、これをパターニングすることによって、前記第3接続部と画素電極とを形成する工程であって、前記画素電極は、前記ドレイン電極を露出する前記開口部内で前記ドレイン電極と接する工程であってもよい。

【発明の効果】

【0046】

本発明によると、酸化物半導体TFTと、TFTの電極と外部配線とを接続する端子部とを備える半導体装置において、端子部のコンタクトホールを形成する際に、エッチング時間を短縮してマスクへのダメージを低減するとともに、高い精度でコンタクトホールの壁面のテーパー形状を制御できる。よって、半導体装置の信頼性を高めることができる。

【0047】

また、上記半導体装置を、製造工程を複雑化することなく簡便に製造できる。

【図面の簡単な説明】

【0048】

【図1】(a)〜(f)は、それぞれ、本発明による実施形態1の半導体装置の製造方法の一例を示す工程断面図である。

【図2】本発明による実施形態1の半導体装置の平面図であり、(a)は、半導体装置における画素部101の平面図であり、(b)〜(d)は、それぞれ、半導体装置におけるゲート端子、ソース端子およびゲート・ソース接続部の平面図である。

【図3】(a)は、図2(a)に示すI−I’線と、図2(b)に示すII−II’線または図2(c)に示すIII−III’線とに沿った断面図である。(b)は、図2(d)に示すIV−IV’線に沿った断面図である。

【図4】(a)〜(f)は、それぞれ、本発明による実施形態2の半導体装置の製造方法の一例を示す工程断面図である。

【図5】本発明による実施形態2の半導体装置の平面図であり、(a)は、半導体装置における画素部201の平面図であり、(b)〜(d)は、それぞれ、半導体装置におけるゲート端子、ソース端子およびゲート・ソース接続部の平面図である。

【図6】(a)は、図5(a)に示すI−I’線と、図5(b)に示すII−II’線または図5(c)に示すIII−III’線とに沿った断面図である。(b)は、図5(d)に示すIV−IV’線に沿った断面図である。

【図7】(a)〜(c)は、それぞれ、本発明による実施形態3の半導体装置の製造方法の一例を示す工程断面図である。

【図8】実施形態3の半導体装置において、接続部23cに断切れが生じた場合の端子部を例示する拡大断面図である。

【図9】本発明による実施形態3の他の半導体装置の構成を例示する断面図である。

【図10】本発明による実施形態3のさらに他の半導体装置の構成を例示する断面図である。

【図11】(a)〜(c)は、それぞれ、本発明による実施形態4の半導体装置の製造方法の一例を示す工程断面図である。

【図12】(a)は、従来のTFT基板の概略を示す模式的な平面図であり、(b)は、(a)のTFT基板における1個の画素を示す拡大平面図である。

【図13】図12に示す従来のTFT基板におけるTFTおよび端子部の断面図である。

【図14】従来のTFT基板の一部を示す断面図である。

【発明を実施するための形態】

【0049】

(実施形態1)

以下、図面を参照しながら、本発明による実施形態1の半導体装置の製造方法を説明する。

【0050】

本実施形態の半導体装置は、少なくとも1つの酸化物半導体TFTが形成されたTFT基板を備えていればよく、各種表示装置やTFT基板、電子機器などを広く含む。

【0051】

ここでは、酸化物半導体TFTをスイッチング素子として備えた、液晶表示装置のTFT基板の製造方法を例に説明する。TFT基板は、複数の画素部を含む表示領域と、表示領域以外の領域に形成された端子配置領域とを有している。本実施形態では、表示領域の各画素部に、酸化物半導体TFTおよび補助容量が形成され、端子配置領域に、複数の端子部が形成される。

【0052】

図1(a)〜(f)は、本実施形態の半導体装置の製造方法を説明するための模式的な工程断面図である。

【0053】

まず、図1(a)に示すように、基板1のうちTFTを形成しようとする領域(TFT形成領域)Aにゲート配線3a、補助容量を形成しようとする領域(補助容量形成領域)Bに補助容量配線3b、およびゲート・ソース端子部を形成しようとする領域(端子部形成領域)Cに、ゲート配線の接続部3cを形成する。

【0054】

なお、TFT形成領域Aおよび補助容量形成領域Bは、表示領域内の各画素部101にそれぞれ位置し、端子部形成領域Cは、表示領域以外の領域、例えば基板1の周縁に配置された端子配置領域102内に位置する。通常、端子配置領域102には多数のソース端子部およびゲート端子部が形成されるが、ここでは1個のゲートまたはソース端子部の形成領域Cのみを示す。

【0055】

ゲート配線3a、補助容量配線3bおよび接続部3cは、基板1上にスパッタ法などにより金属膜(例えばTi/Al/Ti膜)を形成した後、金属膜をパターニングすることによって形成される。金属膜のパターニングは、公知のフォトリソグラフィによりレジストマスクを形成し、レジストマスクで覆われていない部分を除去することによって行われる。この後、レジストマスクを基板1から剥離する。

【0056】

次に、図1(b)に示すように、ゲート配線3a、補助容量配線3bおよび接続部3cを覆うように絶縁膜5を形成する。続いて、TFT形成領域AにTFTのチャネル層となる島状の酸化物半導体層7a、補助容量形成領域Bに島状の酸化物半導体層7bを形成する。

【0057】

本実施形態では、絶縁膜5として、例えば厚さが約400nmのSiO2膜をCVD法を用いて形成する。なお、絶縁膜5は、例えばSiO2膜からなる単層であってもよいし、SiNx膜を下層とし、SiO2膜を上層とする積層構造を有していてもよい。SiO2膜からなる単層の場合、SiO2膜の厚さは300nm以上500nm以下であることが好ましい。SiNx膜(下層)およびSiO2膜(上層)からなる積層構造を有する場合、SiNx膜の厚さは200nm以上500nm以下、SiO2膜の厚さは20nm以上150nm以下であることが好ましい。

【0058】

酸化物半導体層7a、7bは、以下のようにして形成できる。まず、スパッタ法を用いて、例えば厚さが30nm以上300nm以下のIn−Ga−Zn−O系半導体(IGZO)膜を絶縁膜5の上に形成する。この後、フォトリソグラフィにより、IGZO膜の所定の領域を覆うレジストマスクを形成する。次いで、IGZO膜のうちレジストマスクで覆われていない部分をウェットエッチングにより除去する。この後、レジストマスクを剥離する。このようにして、島状の酸化物半導体層7a、7bを得る。なお、IGZO膜の代わりに、他の酸化物半導体膜を用いて酸化物半導体層7a、7bを形成してもよい。

【0059】

次いで、図1(c)に示すように、基板1の表面全体に絶縁膜9を堆積させた後、絶縁膜9をパターニングする。

【0060】

具体的には、まず、絶縁膜5および酸化物半導体層7a、7bの上に、絶縁膜9として例えばSiO2膜(厚さ:例えば約150nm)をCVD法によって形成する。

【0061】

絶縁膜9は、SiOyなどの酸化物膜を含むことが好ましい。酸化物膜を用いると、酸化物半導体層7a、7bに酸素欠損が生じた場合に、酸化物膜に含まれる酸素によって酸素欠損を回復することが可能となるので、酸化物半導体層7a、7bの酸化欠損をより効果的に低減できる。ここでは、絶縁膜9としてSiO2膜からなる単層を用いているが、絶縁膜9は、SiO2膜を下層とし、SiNx膜を上層とする積層構造を有していてもよい。絶縁膜9の厚さ(積層構造を有する場合には各層の合計厚さ)は50nm以上200nm以下であることが好ましい。50nm以上であれば、ソース・ドレイン電極のパターニング工程などにおいて、酸化物半導体層7aの表面をより確実に保護できる。一方、200nmを超えると、ソース電極やドレイン電極により大きい段差が生じるので、断線などを引き起こすおそれがある。

【0062】

この後、フォトリソグラフィにより、絶縁膜9の所定の領域を覆うレジストマスクを形成する。次いで、絶縁膜9のうちレジストマスクで覆われていない部分をウェットエッチングにより除去する。このとき、端子部形成領域Cでは、絶縁膜9だけでなく、その下の絶縁膜5もエッチングされ、TFT形成領域Aおよび補助容量形成領域Bでは、絶縁膜9の下の酸化物半導体層7a、7bはエッチングされないように、エッチング条件を選択する。ここでは、エッチングガスとしてCF4/O2(流量:475sccm/25sccm)を用い、基板1の温度を60℃として、チャンバー内でドライエッチングを行う。チャンバー内の真空度を15mTとする。また、印加パワーを1000W、エッチング時間を7分とする。

【0063】

これにより、TFT形成領域Aでは、絶縁膜9のうちソースコンタクトおよびドレインコンタクトを形成する部分がエッチングされて、酸化物半導体層7aを露出する2つの開口部11as、11adが形成される。絶縁膜9は、酸化物半導体層7aのうちチャネルとなる領域を覆っており、チャネル保護膜9aとして機能する。補助容量形成領域Bでは、絶縁膜9のうち酸化物半導体層7b上に位置する部分がエッチングされて、酸化物半導体層7bを露出する開口部11bが形成される。端子部形成領域Cでは、絶縁膜9のうち接続部3c上に位置する部分、および、その下の絶縁膜5が連続してエッチングされて、接続部3cの表面を露出する開口部11cが得られる。開口部11cの直径は例えば20μmである。

【0064】

本工程では、酸化物半導体層7a、7bをエッチストップとして、絶縁膜5および絶縁膜9のエッチングが行われるように、絶縁膜5、9の材料などに応じて、エッチング条件が選択されていることが好ましい。これにより、端子部形成領域Cでは絶縁膜9および絶縁膜5が一括してエッチング(GI/ES同時エッチング)されるとともに、TFT形成領域Aおよび補助容量形成領域Bでは絶縁膜9のみをエッチングできる。ここでいうエッチング条件とは、ドライエッチングを用いる場合、エッチングガスの種類、基板1の温度、チャンバー内の真空度などを含む。また、ウェットエッチングを用いる場合、エッチング液の種類やエッチング時間などを含む。

【0065】

続いて、図1(d)に示すように、基板1の表面全体に導電膜を形成する。本実施形態では、例えばスパッタ法によりTi/Al/Ti膜などの金属膜を形成する。この後、例えばフォトリソグラフィにより、金属膜のパターニングを行う。

【0066】

これにより、TFT形成領域Aでは、開口部11as、11adの内部および絶縁膜9上に、酸化物半導体層7aのうちチャネル領域となる領域の両側に位置する領域とそれぞれ接するように、ソース配線13asおよびドレイン電極13adを形成する。ドレイン電極13adは、補助容量形成領域Bにおける補助容量配線3b上まで延び、開口部11bを介して酸化物半導体層7bと接している。ドレイン電極13adのうち酸化物半導体層7bと接する部分は、補助容量電極としても機能する。また、端子部形成領域Cでは、開口部11cの内部および絶縁膜9上に、接続部3cと電気的に接続された接続部13cが形成される。

【0067】

なお、本明細書では、酸化物半導体層7aのうちソース配線13asと接する領域を「ソース領域」、ドレイン電極13adと接する領域を「ドレイン領域」と称する。また、酸化物半導体層7aのうちゲート配線3a上に位置し、かつ、ソース領域とドレイン領域とによって挟まれた領域を「チャネル領域」と称する。

【0068】

このようにして、TFT形成領域Aに酸化物半導体TFTが形成され、補助容量形成領域Bに補助容量Csが形成される。なお、酸化物半導体層7bはドライダメージにより導電体となる可能性が高い。その場合、補助容量Csは、補助容量配線3bと、ドレイン電極13adおよび酸化物半導体層7bとを電極とし、絶縁膜5を誘電体として構成される。

【0069】

この後、図1(e)に示すように、酸化物半導体TFTおよび補助容量Csを覆うように、基板1の表面全体に保護膜15を堆積させる。本実施形態では、保護膜15として、SiO2膜などの酸化物膜(厚さ:例えば約265nm)をCVD法によって形成する。なお、保護膜15は、例えばSiO2膜からなる単層であってもよいし、SiO2膜を下層とし、SiNx膜を上層とする積層構造を有していてもよい。SiO2膜からなる単層の場合、SiO2膜の厚さは50nm以上300nm以下であることが好ましい。SiO2膜(下層)およびSiNx膜(上層)からなる積層構造を有する場合、SIO2膜の厚さは50nm以上150nm以下、SiNx膜の厚さは50nm以上200nm以下であることが好ましい。

【0070】

次いで、フォトリソグラフィにより保護膜15のパターニングを行う。これにより、補助容量形成領域Bにおいて、保護膜15に、ドレイン電極13adを露出する開口部17bを形成する。開口部17bは、補助容量Cs上に形成される。また、端子部形成領域Cにおいて、保護膜15に、接続部13cを露出する開口部17cを形成する。なお、図示するように、開口部11cおよび開口部17cの幅は略等しくてもよいが、基板1の表面の法線方向から見て、開口部17cは開口部11cよりも一回り小さく、開口部11c内に配置されることが好ましい。これにより、基板の法線方向から見て、開口部11c、17cが重なり合うように配置されるので、開口部11c、17cによって端子部のコンタクトホールを構成できる。

【0071】

次いで、図1(f)に示すように、保護膜15の上および開口部17b、17c内に透明導電膜を形成し、透明導電膜のパターニングを行う。これにより、ドレイン電極13adの露出した表面と接する画素電極19と、接続部13cの露出した表面と接する接続部19cを形成する。画素電極19は、画素ごとに分離して配置される。

【0072】

本実施形態では、例えばスパッタ法により透明導電膜を堆積する。透明導電膜として、例えばITO膜(厚さ:50〜200nm)を用いる。次いで、公知のフォトリソグラフィによってITO膜のパターニングを行う。

【0073】

なお、図1では、簡単のため、画素電極19、補助容量Csおよび薄膜トランジスタTFTを1個ずつ示しているが、TFT基板は、通常、複数の画素部101を有しており、複数の画素部101のそれぞれに画素電極19、補助容量Csおよび薄膜トランジスタTFTが配置される。また、端子配置領域102においては、ソース配線13asおよびゲート配線3aと同数の端子部が形成される。

【0074】

図示していないが、端子配置領域102には、ソース配線とゲート配線とを接続するゲート・ソース接続部を形成する場合がある。その場合には、端子部の開口部11cを形成する際に、ゲート配線上の絶縁膜9および絶縁膜5を同時にエッチングして、ゲート配線(またはその接続部)を露出する開口部を形成することが好ましい。この開口部内にソース配線を形成することによって、ソース配線とゲート配線とが直接接する構成を有するゲート・ソース接続部が得られる。

【0075】

図2および図3は、本実施形態の半導体装置を模式的に示す図である。図2(a)は、半導体装置における画素部101の平面図であり、図2(b)〜(d)は、それぞれ、半導体装置における端子配置領域102のゲート端子、ソース端子およびゲート・ソース接続部の平面図である。図3(a)は、図2(a)に示すI−I’線と、図2(b)に示すII−II’線または図2(c)に示すIII−III’線とに沿った断面図である。図3(b)は、図2(d)に示すIV−IV’線に沿った断面図である。

【0076】

これらの図からわかるように、各画素部101では、画素の行方向に沿って延びるソース配線13asと、画素の列方向に沿って延びるゲート配線3aおよび補助容量配線3bとが形成されている。

【0077】

ソース配線13asとゲート配線3aとの交差する点の近傍には、薄膜トランジスタTFTが形成され、補助容量配線3b上には補助容量Csが形成されている。

【0078】

TFTの酸化物半導体層7aは、絶縁膜9の開口部11as、11adを介して、ソース配線13asおよびドレイン電極13adとそれぞれ接続されている。また、ドレイン電極13adは、補助容量配線3b上まで延伸されており、補助容量Cs上で、保護膜15の開口部17b内で画素電極19と接続されている。

【0079】

補助容量Csの酸化物半導体層7bは、絶縁膜9の開口部11b内で補助容量電極(ここではドレイン電極13ad)と接続され、保護膜15の開口部17b内で画素電極19と接続されている。基板1の表面の法線方向から見て、開口部17bは、開口部11b内に配置されている。

【0080】

ゲート端子部およびソース端子部では、接続部3cは、絶縁膜5および絶縁膜9を同時にエッチングして得られた開口部11c内で接続部13cと接続され、保護膜15の開口部17c内で接続部19cと接続されている。本実施形態では、開口部11c内に接続部3cが形成された後に、保護膜15に開口部17cが形成されるので、接続部3cは開口部11cにおける絶縁膜5、9の端面(開口部11cの壁面)を覆い、かつ、開口部17cにおける保護膜15の端面(開口部17cの壁面)を覆っていない。また、基板1の表面の法線方向から見て、開口部17cは、開口部11c内に配置されている。

【0081】

また、ゲート・ソース接続部では、ゲート配線の接続部3dは、絶縁膜5および絶縁膜9を同時にエッチングして得られた開口部11d内で、ソース配線13asと直接接続されている。ソース配線13as上は保護膜15で覆われている。

【0082】

本実施形態の半導体装置は、図1を参照しながら前述した方法を用いて製造されるので、従来と比べて、以下のような利点を有する。

【0083】

特許文献1に開示された従来の方法では、チャネル保護膜のみを先にエッチングし、ソース・ドレイン電極を形成した後に、保護膜のエッチングを行う。このため、端子部に形成するコンタクトホールは、保護膜のエッチングを行う際に、ゲート絶縁膜および保護膜を一括でエッチングすることにより形成される(GI/Pass同時エッチング)。しかしながら、この方法によると、前述したように、SiO2を用いてゲート絶縁膜や保護膜が形成されている場合には、エッチング時間が非常に長くなり、エッチングマスクとして用いるレジスト膜の表面がダメージを受けて、レジスト膜を基板から良好に剥離できないおそれがある。

【0084】

あるいは、特許文献2に開示された方法では、有機絶縁膜を上層、無機絶縁膜を下層とする積層構造の保護膜を形成し、有機絶縁膜をマスクとして、無機絶縁膜およびゲート絶縁膜をエッチングすることにより、端子部のコンタクトホールを形成していた(GI/Pass同時エッチング)。この方法でも、SiO2を用いて無機絶縁膜や保護膜が形成されている場合、エッチング時間が非常に長くなる。このため、エッチングの際に、マスクとして用いる有機絶縁膜の表面がダメージを受けるおそれがある。

【0085】

これに対し、本実施形態では、端子部のコンタクトホールは2段階に分けて形成される。すなわち、ゲート絶縁膜となる絶縁膜5と、チャネル保護膜(エッチストップ)形成用の絶縁膜9とに対するエッチングを同時に行い、開口部11cを形成する(GI/ES同時エッチング)。続いて、ソース・ドレイン電極形成後、上記のGI/ES同時エッチングとは別個に、保護膜15のエッチングを行い、保護膜15に開口部17cを形成する(Passエッチング)。一般に、保護膜15の厚さは、チャネル保護膜形成用の絶縁膜9の厚さよりも大きい。このため、本実施形態におけるGI/ES同時エッチングでは、従来のゲート絶縁膜と保護膜とを同時にエッチングするGI/Pass同時エッチングと比べて、エッチングされる膜(被エッチング膜)の合計厚さを小さくできる。従って、エッチング時間を大幅に短縮できるので、エッチングマスクへのダメージを低減できる。

【0086】

また、従来の方法によると、コンタクトホールのテーパー形状を制御することが困難となるおそれがある。端子部のコンタクトホールのテーパー形状は、従来の方法ではGI/Pass同時エッチングにおけるエッチング条件によって制御される。これに対し、本実施形態では主に保護膜15のみのエッチング(Passエッチング)におけるエッチング条件によって制御される。一般に、被エッチング膜の材料が同じ場合、被エッチング膜が薄い方が、エッチングマスク(レジスト膜)に与えるダメージを考慮する必要がないので、エッチング条件を選択しやすい。従って、本実施形態によると、従来の方法よりも被エッチング膜を薄くできるので、より高い精度でコンタクトホールの壁面のテーパー形状を制御することが可能となる。

【0087】

特に、ゲート絶縁膜および保護膜が何れも積層構造(例えば2層構造)を有する場合には、従来の方法では4層の膜に対してエッチングを行うことになり、テーパー形状の制御が非常に困難となる。本実施形態では、そのような場合でも、保護膜を構成する2層の膜に対するエッチングによってテーパー形状を制御できるので、テーパー形状の制御性を大幅に向上できる。

【0088】

このように、本実施形態によると、より確実に、コンタクトホールの壁面を基板の法線に対して所定の角度(テーパー角)で傾斜させることができるので、コンタクトホール上に形成される配線に切れが生じることを防止できる。よって、端子部におけるソース配線またはゲート配線と、駆動回路の入力部との電気的な接続を確保できる。

【0089】

さらに、従来は、ゲート・ソース接続部において、画素電極を形成するための透明導電膜を介して、ゲート配線とソース配線とを電気的に接続していた(例えば特許文献2の図4)。このため、ゲート・ソース接続部のコンタクトホールの壁面が基板の法線に対して十分に傾斜していないと、壁面を構成するソース配線と、壁面上に形成される透明導電膜とを電気的に接続できないという問題がある。

【0090】

これに対し、本実施形態によると、絶縁膜(ゲート絶縁膜)5と絶縁膜9とが同時にエッチングされるため、ゲート配線の接続部3dとソース配線13asとが直接接する構成のゲート・ソース接続部を形成できる。従って、たとえコンタクトホールの壁面がほとんど傾斜していなくても、コンタクトホールの壁面のテーパー形状に関わらず、ゲート配線3aとソース配線13asとをより確実に電気的に接続できる。

【0091】

さらに、本実施形態は、特許文献3に開示された構成と比べて、次のようなメリットも有している。

【0092】

特許文献3に開示された構成では、ゲート電極、ゲート絶縁膜および酸化物半導体層は、同一のマスクを用いてパターニングされている。これらの層の側壁は、エッチストップとして機能する絶縁膜で覆われている。この構成では、ゲート電極の側壁とソース電極との間には、エッチストップとして機能する絶縁膜しか設けられておらず、これらの電極間で短絡が生じる可能性があった。これに対し、本実施形態によると、ゲート絶縁膜となる絶縁膜5、酸化物半導体層7aおよびエッチストップとして機能する絶縁膜9は、チャネル長方向にゲート配線3aよりも長いので、ゲート配線3aの側壁は絶縁膜5、酸化物半導体層7aおよび絶縁膜9で覆われている。したがって、ゲート配線3aの上面および側壁とソース配線13asとの間、および、ゲート配線3aの上面および側壁とドレイン電極13adとの間には、少なくとも2層の絶縁膜(絶縁膜5および絶縁膜9)が存在する。このため、上述したような短絡を防止できる。また、絶縁膜5、特に絶縁膜5のうちゲート配線3aとソース・ドレイン電極13as、13adとの間に位置する部分に穴が開いているような場合でも、絶縁膜9でカバーできるので、これらの間に点欠陥が生じることを抑制できる。

【0093】

本実施形態では、絶縁膜5、絶縁膜9および保護膜15のうち少なくとも1つがSiO2を含むことが好ましい。これにより、これらの膜からTFTの活性層となる酸化物半導体層7aに酸素が供給されるので、酸化物半導体層7aに生じる酸素欠損をより低減できる。このため、酸素欠陥に起因して酸化物半導体層7aが低抵抗化されることを抑制できるので、リーク電流やヒステリシスを低減できる。特に、これらの絶縁膜のうち酸化物半導体層7a側の表面(すなわち絶縁膜5の上面、絶縁膜9の下面、保護膜15の下面)がSiO2から形成されているとより効果的である。

【0094】

また、チャネル保護膜9aを含む絶縁膜9は、島状の酸化物半導体層7aの上面全体(ただしソース・ドレイン領域を除く)および側壁全体を覆っていることが好ましい。このような構成によると、図1(d)に示すソース・ドレイン電極を形成するためのパターニング工程において、酸化物半導体層7aのチャネル領域およびその近傍に、酸化還元反応によって酸素欠陥が形成されることを抑制できる。この結果、酸素欠陥に起因して酸化物半導体層7aが低抵抗化されることを抑制できるので、リーク電流やヒステリシスを低減できる。また、絶縁膜9は、チャネル幅方向に酸化物半導体層7aよりも長く、酸化物半導体層7aの側壁の近傍に位置する絶縁膜5の上面とも接することが好ましい。これにより、絶縁膜9によって酸化物半導体層7aの上面のみでなく側壁もより確実に保護できる。

【0095】

本実施形態における酸化物半導体層7a、7bは、例えばZn−O系半導体(ZnO)、In−Ga−Zn−O系半導体(IGZO)、In−Zn−O系半導体(IZO)、またはZn−Ti−O系半導体(ZTO)からなる層であることが好ましい。

【0096】

(実施形態2)

以下、図面を参照しながら、本発明による実施形態2の半導体装置の製造方法を説明する。本実施形態は、補助容量電極として、ドレイン電極の代わりに画素電極を用いる点で、実施形態1と異なっている。

【0097】

図4(a)〜(f)は、本実施形態の半導体装置の製造方法を説明するための模式的な工程断面図である。簡単のため、図1と同様の構成要素には同じ参照符号を付し、説明を省略する。

【0098】

まず、図4(a)に示すように、基板1のうちTFTを形成しようとするTFT形成領域Aにゲート配線3a、補助容量を形成しようとする補助容量形成領域Bに補助容量配線3b、およびゲート・ソース端子を形成しようとする端子部形成領域Cに、ゲート配線の接続部3cを形成する。配線3a、3bおよび接続部3cの形成方法や材料は、図1(a)を参照しながら前述した方法および材料と同様である。

【0099】

次に、図4(b)に示すように、ゲート配線3a、補助容量配線3bおよび接続部3cを覆うように絶縁膜5を形成する。続いて、TFT形成領域AにTFTのチャネル層となる島状の酸化物半導体層7a、補助容量形成領域Bに島状の酸化物半導体層7bを形成する。絶縁膜5および酸化物半導体層7a、7bの形成方法や材料は、図1(b)を参照しながら前述した方法および材料と同様である。

【0100】

次いで、図4(c)に示すように、基板1の表面全体に絶縁膜9を堆積させた後、絶縁膜9をパターニングする。これにより、TFT形成領域Aでは、絶縁膜9のうちソースコンタクトおよびドレインコンタクトを形成する部分がエッチングされて、酸化物半導体層7aを露出する2つの開口部11as、11adが形成される。絶縁膜9は、酸化物半導体層7aのうちチャネルとなる領域を覆い、チャネル保護膜9aとして機能する。補助容量形成領域Bでは、絶縁膜9のうち酸化物半導体層7b上に位置する部分がエッチングされて、酸化物半導体層7bを露出する開口部11bが形成される。端子部形成領域Cでは、絶縁膜9のうち接続部3c上に位置する部分、および、その下の絶縁膜5が連続してエッチングされて、接続部3cの表面を露出する開口部11cが得られる。絶縁膜9の形成方法、材料およびエッチング方法は、図1(c)を参照しながら前述した方法および材料と同様である。

【0101】

続いて、図4(d)に示すように、基板1の表面全体に導電膜を堆積させた後、これをパターニングする。これにより、TFT形成領域Aでは、開口部11as、11adの内部および絶縁膜9上に、酸化物半導体層7aのうちチャネル領域となる領域の両側に位置する領域とそれぞれ接するように、ソース配線23asおよびドレイン電極23adをそれぞれ形成する。本実施形態におけるドレイン電極23adは、酸化物半導体層7aの一部を覆う島状のパターンを有しており、実施形態1のように補助容量形成領域Bまで延びていない。端子部形成領域Cでは、開口部11cの内部および絶縁膜9上に、接続部3cに接するように接続部23cを形成する。なお、本実施形態では、本エッチング工程によって、導電膜のうち、補助容量形成領域Bの酸化物半導体層7bの表面上(すなわち開口部11bの内部)に位置する部分も除去される。このようにして、TFT形成領域Aに酸化物半導体TFTが形成される。導電膜の材料や形成方法は、図1(d)を参照しながら前述した材料および方法と同様である。

【0102】

この後、図4(e)に示すように、基板1の表面全体に保護膜25を堆積させる。次いで、フォトリソグラフィ、ウェットエッチングおよびレジスト剥離洗浄工程により、保護膜25のパターニングを行う。これにより、TFT形成領域Aにおいて、保護膜25に、ドレイン電極23adの表面を露出する開口部27aを形成する。また、補助容量形成領域Bにおいて、酸化物半導体層7bの表面を露出する開口部27bを形成する。さらに、端子部形成領域Cにおいて、接続部23cを露出する開口部27cを形成する。保護膜25の材料、形成方法およびエッチング方法は、図1(e)を参照しながら前述した材料および方法と同様である。

【0103】

この後、図4(f)に示すように、保護膜25の上および開口部27a、27b、27c内に透明導電膜(例えばITO膜)を形成し、透明導電膜のパターニングを行う。これにより、ドレイン電極23adの露出した表面および酸化物半導体層7bと接する画素電極29と、接続部23cの露出した表面と接する接続部29cを形成する。

【0104】

本実施形態では、この工程によって、補助容量形成領域Bに補助容量Csが形成される。補助容量Csは、補助容量配線3bと、酸化物半導体層7bおよび画素電極29とを電極とし、絶縁膜5を誘電体として構成されている。

【0105】

図5および図6は、本実施形態の半導体装置を模式的に示す図である。図5(a)は、半導体装置における画素部201の平面図であり、図5(b)〜(d)は、それぞれ、半導体装置における端子配置領域202のゲート端子、ソース端子およびゲート・ソース接続部の平面図である。図6(a)は、図5(a)に示すI−I’線と、図5(b)に示すII−II’線または図5(c)に示すIII−III’線とに沿った断面図である。図6(b)は、図5(d)に示すIV−IV’線に沿った断面図である。

【0106】

これらの図からわかるように、各画素部201では、画素の行方向に沿って延びるソース配線23asと、画素の列方向に沿って延びるゲート配線3aおよび補助容量配線3bとが形成されている。ソース配線23asとゲート配線3aとの交差する点の近傍には、薄膜トランジスタTFTが形成されている。TFTの酸化物半導体層7aは、絶縁膜9の開口部11as、11ad内で、ソース配線23asおよびドレイン電極23adとそれぞれ接続されている。ドレイン電極23adは、保護膜25の開口部27a内で画素電極29と電気的に接続されている。

【0107】

補助容量配線3b上には補助容量Csが形成されている。補助容量Csの酸化物半導体層7bは、絶縁膜9の開口部11bおよび保護膜25の開口部27bからなるコンタクトホール内で、画素電極29と接続されている。従って、画素電極29は補助容量電極としても機能する。基板1の表面の法線方向から見て、開口部27bは、開口部11bの内部に配置されている。

【0108】

ゲート端子部およびソース端子部では、接続部3cは、絶縁膜5および絶縁膜9を同時にエッチングして得られた開口部11c内で、接続部23cと接続されている。接続部23cは、保護膜25の開口部27c内で接続部29cと接続されている。本実施形態でも、実施形態1と同様に、開口部11c内に接続部23cが形成された後に、保護膜25に開口部27cが形成されるので、接続部23cは開口部11cにおける絶縁膜5、9の端面(開口部11cの壁面)を覆い、かつ、開口部27cにおける保護膜25の端面(開口部27cの壁面)を覆っていない。また、基板1の表面の法線方向から見て、開口部27cは、開口部11c内に配置されている。

【0109】

本実施形態でも、基板1の端子配置領域202にゲート・ソース接続部が形成される場合がある。ゲート・ソース接続部では、ゲート配線の接続部3dは、絶縁膜5および絶縁膜9を同時にエッチングして得られた開口部11c内で、ソース配線23asと直接接続されている。ソース配線23asは保護膜25で覆われている。

【0110】

本実施形態によると、ゲート絶縁膜となる絶縁膜5およびチャネル保護膜(エッチストップ)形成用の絶縁膜9に対するエッチング(GI/ES同時エッチング)と、保護膜25のエッチング(Passエッチング)とによって、端子部のコンタクトホールを形成する。このため、ゲート絶縁膜および保護膜を同時にエッチングする従来の方法よりも、エッチング時間を大幅に短縮できる。従って、実施形態1と同様に、エッチングマスクへのダメージを低減できる。また、より高い精度でコンタクトホールの壁面のテーパー形状を制御することが可能となる。さらに、ゲート・ソース接続部において、ゲート配線の接続部3dとソース配線23asとを直接接続させることが可能になるので、ゲート・ソース接続部のコンタクトホールの壁面のテーパー形状に関わらず、ゲート配線の接続部3dとソース配線23asとをより確実に電気的に接続することができる。

【0111】

その上、本実施形態によると、実施形態1と異なり、次のようなメリットもある。実施形態1では、ドレイン電極の島状パターンが補助容量Csまで延びて、補助容量電極として用いられる。これに対し、本実施形態では、補助容量Csにドレイン電極が形成されていない。この構造は、ソース配線23as、ドレイン電極23adおよび接続部23cを形成するための導電膜のパターニング工程(図4(d))において、補助容量形成領域Bの酸化物半導体層7bがエッチストップとして機能することによって実現できる。

【0112】

通常、実施形態1のようにドレイン電極を補助容量電極として用いる場合、ドレイン電極と補助容量配線とが確実に重なるようにマージンを設ける必要がある。このため、補助容量配線およびドレイン電極のうち何れか一方の平面形状が大きくなるように設計される。例えば実施形態1では、補助容量配線の幅よりも、その上のドレイン電極の幅が大きくなるように設計されている。ドレイン電極および補助容量電極は何れも金属膜などから形成されており、これらの平面形状が大きくなると、開口率が低下する要因となる。

【0113】

一方、本実施形態でも、補助容量配線3bと、酸化物半導体層7bおよび画素電極29とが確実に重なるようにマージンを設ける必要がある。このため、酸化物半導体層7bおよび画素電極29の幅が、補助容量配線3bの幅よりも大きくなるように設計されている。しかしながら、酸化物半導体層7bおよび画素電極29は何れも透明であり、これらのパターンを拡大しても、開口率を低下させる要因とはならない。従って、実施形態1よりも、開口率を高めることができる。

【0114】

(実施形態3)

以下、図面を参照しながら、本発明による実施形態3の半導体装置の製造方法を説明する。本実施形態は、保護膜と画素電極との間に有機絶縁膜を形成する点で、前述の実施形態と異なっている。

【0115】

図7(a)〜(c)は、本実施形態の半導体装置の製造方法を説明するための模式的な工程断面図である。簡単のため、図4と同様の構成要素には同じ参照符号を付し、説明を省略する。

【0116】

まず、図7(a)に示すように、実施形態2と同様の方法(図4(a)〜(d))により、基板1上に、ゲート配線3a、補助容量配線3b、接続部3c、絶縁膜5、酸化物半導体層7a、7b、絶縁膜9、ソース配線23as、ドレイン電極23adおよび接続部23cを形成する。

【0117】

次に、図7(b)に示すように、基板1の表面に、保護膜25および有機絶縁膜36をこの順で形成する。ここでは、保護膜25として、例えば厚さが50nm〜300nmの酸化物膜をCVD法により形成する。また、有機絶縁膜36として、例えば厚さが1μm以上4μm以下のアクリル系樹脂膜を塗布することにより形成する。有機絶縁膜36によって基板1の表面は平坦化されることが好ましい。

【0118】

次いで、フォトリソグラフィにより有機絶縁膜36のパターニングを行った後、有機絶縁膜36をマスクとして、保護膜25をドライエッチングによってパターニングする。これにより、TFT形成領域Aにおいて、保護膜25および有機絶縁膜36に、ドレイン電極23adの表面を露出する開口部37aを形成する。また、補助容量形成領域Bにおいて、酸化物半導体層7bの表面を露出する開口部37bを形成する。さらに、端子部形成領域Cにおいて、接続部23cを露出する開口部37cを形成する。

【0119】

この後、図7(c)に示すように、保護膜25の上および開口部37a、37b、37c内に透明導電膜(例えばITO膜)を形成し、透明導電膜のパターニングを行う。これにより、ドレイン電極23adの露出した表面および酸化物半導体層7bと接する画素電極29と、接続部23cの露出した表面と接する接続部29cとを形成する。画素電極29は、補助容量Csの電極としても機能する。このようにして、本実施形態の半導体装置を得る。

【0120】

本実施形態の半導体装置の平面図は、図5を参照しながら前述した実施形態2の半導体装置の平面図と同様である。ただし、図5に示す保護膜25の開口部27a、27b、27cは、本実施形態では、保護膜25および有機絶縁膜36の開口部37a、37b、37cとなる。また、本実施形態におけるゲート・ソース接続部の断面図は、図6(b)に示す実施形態2のゲート・ソース接続部の断面図と同様である。

【0121】

本実施形態によると、ゲート絶縁膜となる絶縁膜5およびチャネル保護膜(エッチストップ)形成用の絶縁膜9に対するエッチング(GI/ES同時エッチング)と、有機絶縁膜36のエッチングおよび保護膜25のエッチング(Passエッチング)とによって、端子部のコンタクトホールを形成する。このため、ゲート絶縁膜および保護膜を同時にエッチングする従来の方法よりも、エッチング時間を大幅に短縮できる。従って、前述の実施形態と同様に、エッチングマスクへのダメージを低減できる。また、より高い精度でコンタクトホールの壁面のテーパー形状を制御することが可能となる。さらに、ゲート・ソース接続部において、ゲート配線の接続部3dとソース配線23asとをより確実に電気的に接続することができる。その上、実施形態2と同様に、開口率を低下させることなく、補助容量配線3bと、酸化物半導体層7bおよび画素電極29との重なりマージンを設けることができる。

【0122】

また、本実施形態によると、端子部のコンタクトホール内部で接続部23cに断切れが生じた場合であっても、ゲート配線3cと接続部29cとの電気的接続をより確実に確保できるというメリットもある。

【0123】

図8は、接続部23cに断切れが生じた場合の端子部を例示する拡大断面図である。図示するように、絶縁膜5および絶縁膜9からなる開口部11cの壁面が所望のテーパー形状を有していない場合(例えば開口部11cの壁面が基板1の表面に略垂直になるような場合)、開口部11cの内部に形成された接続部23cに断切れが生じることがある。接続部23cに断切れが生じると、保護膜25は、断切れを生じた接続部23c上のみにCVD法などによって堆積される。一方、有機絶縁膜36は、開口部11cの壁面を覆うように塗布されるので、断切れによって生じた空間が埋められて、より滑らかな壁面を有する開口部37cが得られる。このため、開口部37c内に堆積される接続部29cには断切れが生じにくい。この結果、図示するように、たとえ接続部23cに断切れが生じても、接続部23cを介して、接続部29cとゲート配線3cとを電気的に接続することができる。

【0124】

なお、特許文献1に開示された方法のように、保護膜上に有機絶縁膜を設けた場合でも、無機絶縁膜およびゲート絶縁膜を同時にエッチング(Pass/GI同時エッチング)すると、図8を参照して説明したようなメリットは得られないと考えられる。前述したように、酸化物半導体TFTでは、ゲート絶縁膜、チャネル保護膜および保護膜としてSiO2膜を用いることが好ましい。SiO2膜はSiNx膜よりもエッチレートが低いので、Pass/GI同時エッチングの際に、エッチングマスクである有機絶縁膜の表面状態やテーパー形状を制御することが困難だからである。

【0125】

本実施形態の半導体装置の構成は、図7を参照しながら上述した構成に限定されない。図9および図10は、本実施形態の半導体装置の他の例を示す断面図である。

【0126】

図7に示す例では、保護膜25上に有機絶縁膜36を形成しているが、代わりに、図9に示すように、実施形態1の半導体装置における保護膜15上に有機絶縁膜36を形成してもよい。図9に示す半導体装置の平面図は、図2に示す実施形態1の半導体装置の平面図と同様である。ただし、図2に示す保護膜15の開口部17b、17cは、本実施形態では、保護膜15および有機絶縁膜36の開口部となる。また、ゲート・ソース接続部の断面図は、図3(b)に示す実施形態1のゲート・ソース接続部の断面図と同様である。図9に示す半導体装置によると、実施形態1と同様の効果が得られる。また、図8を参照しながら前述したように、接続部13cに断切れが生じても、端子部における配線間の電気的な接続を確保できる。

【0127】

また、図7に示す例では、端子部形成領域Cにも保護膜25および有機絶縁膜36が形成されているが、図10に示すように、端子部形成領域Cに保護膜25および有機絶縁膜36を形成しなくてもよい。さらに、図9に示すように、保護膜15上に有機絶縁膜36を形成する場合でも、端子部形成領域Cに保護膜15および有機絶縁膜36を形成しなくてもよい。

【0128】

(実施形態4)

以下、図面を参照しながら、本発明による実施形態4の半導体装置の製造方法を説明する。本実施形態は、ゲート絶縁膜として、SiNx膜を下層とし、SiO2膜を上層とする積層膜を形成し、保護膜として、SiO2膜を下層とし、SiNx膜を上層とする積層膜を形成する点で、前述の実施形態と異なっている。

【0129】

図11(a)〜(c)は、本実施形態の半導体装置の製造方法を説明するための模式的な工程断面図である。簡単のため、図4と同様の構成要素には同じ参照符号を付し、説明を省略する。

【0130】

まず、図11(a)に示すように、基板1上に、ゲート配線3a、補助容量配線3b、接続部3cを形成する。ゲート配線3a、補助容量配線3b、接続部3cの形成方法は、図1(a)を参照しながら前述した方法と同様である。

【0131】

次いで、図11(b)に示すように、ゲート配線3a、補助容量配線3bおよび接続部3cを覆うように、SiNx膜5LおよびSiO2膜5Uをこの順で形成することにより、絶縁膜5を得る。この後、絶縁膜5の上に、酸化物半導体層7a、7bを形成する。

【0132】

ここでは、CVD法により、厚さが例えば200nm以上500nm以下のSiNx膜5L、および、厚さが例えば20nm以上150nm以下のSiO2膜5Uを形成する。酸化物半導体層7a、7bは、スパッタ法により、厚さが例えば30nm以上300nm以下のIGZO膜を形成し、これをパターニングすることによって得られる。酸化物半導体層7a、7bの形成方法は、図1(b)を参照しながら前述した方法と同様である。

【0133】

続いて、図示しないが、図1(c)を参照しながら前述した方法で、基板1の表面に絶縁膜9を堆積する。この後、TFT形成領域Aにおいて、絶縁膜9にソースコンタクト形成用の開口部、ドレインコンタクト形成用の開口部を形成し、補助容量形成領域Bにおいて、絶縁膜9に酸化物半導体層7bを露出する開口部を形成する。これと同時に、端子部形成領域Cにおいて、絶縁膜9および絶縁膜5をエッチングして開口部を形成する。次いで、図4(d)を参照しながら前述した方法で、絶縁膜9上および絶縁膜9の開口部内に金属膜を形成し、これをパターニングすることにより、ソース配線23as、ドレイン電極23adおよび接続部23cを形成する。

【0134】

この後、図11(c)に示すように、基板1の表面に、SiO2膜25LおよびSiNx膜25Uをこの順で形成することにより、保護膜25を形成する。本実施形態では、ここでは、CVD法により、厚さが例えば50nm以上150nm以下のSiO2膜25L、および、厚さが例えば50nm以上200nm以下のSiNx膜25Uを形成する。

【0135】

次いで、フォトリソグラフィ、ウェットエッチングおよびレジスト剥離洗浄工程により、保護膜25のパターニングを行う。これにより、TFT形成領域Aにおいて、保護膜25に、ドレイン電極23adの表面を露出する開口部27aを形成する。また、補助容量形成領域Bにおいて、酸化物半導体層7bの表面を露出する開口部27bを形成する。さらに、端子部形成領域Cにおいて、接続部23cを露出する開口部27cを形成する。

【0136】

図示しないが、この後、図4(f)を参照しながら前述したように、保護膜25の上および開口部27a、27b、27c内に透明導電膜(例えばITO膜)を形成し、透明導電膜のパターニングを行う。これにより、ドレイン電極23adの露出した表面および酸化物半導体層7bと接する画素電極29と、接続部23cの露出した表面と接する接続部29cとを形成する。

【0137】

本実施形態の半導体装置の平面図は、図5を参照しながら前述した実施形態2の半導体装置の平面図と同様である。また、本実施形態におけるゲート・ソース接続部の断面図は、図6(b)に示す実施形態2のゲート・ソース接続部の断面図と同様である。

【0138】

本実施形態によると、実施形態2と同様の効果が得られる。また、絶縁膜(ゲート絶縁膜)5および保護膜25として、SiO2膜およびSiNx膜からなる積層膜を用いると、次のようなメリットが得られる。

【0139】

酸化物半導体TFTでは、ゲート絶縁膜および保護膜としてSiNx膜を単層で用いると、製造プロセスにおいて、酸化物半導体層がSiNxと触れた状態で加熱処理が行われるので、酸化物半導体層中の酸素が還元される可能性がある。また、SiNx膜を形成する際に酸化物半導体層がプラズマダメージを受けやすい。この結果、酸化物半導体TFTの特性が低下するおそれがある。一方、ゲート絶縁膜および保護膜としてSiO2膜を単層で用いると、上記のような問題は生じないが、SiO2膜はSiNx膜よりも誘電率が低いために、ソース−ゲート間の耐圧を確保するためには、SiO2膜を厚くする必要がある。このため、TFTのオン電流の低下を引き起こす要因となる。

【0140】

これに対し、ゲート絶縁膜および保護膜として、SiO2膜およびSiNx膜からなる積層膜を用いると、SiO2膜のみからなるゲート絶縁膜や保護膜より薄くても、十分な耐圧を確保できる。従って、ゲート絶縁膜および保護膜によるTFTのオン電流の低下を抑制できる。さらに、積層膜のうち酸化物半導体層に接する膜、または酸化物半導体層に最も近接する膜にSiO2膜を配置することにより、酸化物半導体層の酸素がSiNxによって還元されたり、SiNx膜を形成する際に酸化物半導体層がプラズマダメージを受けることを防止できる。

【0141】

本実施形態における絶縁膜5は、SiO2膜およびSiNx膜を含む積層構造を有し、かつ、積層構造の最上層、すなわち酸化物半導体層の下面と接する層がSiO2膜であればよい。同様に、保護膜25は、SiO2膜およびSiNx膜を含む積層構造を有し、かつ、積層構造の最下層、すなわち最も酸化物半導体層側に位置する層がSiO2膜であればよい。図11に示す例では、絶縁膜5および保護膜25が何れも積層構造を有するが、これらのうち一方のみが上記のような積層構造を有していれば、上記の効果を得ることができる。ただし、これらの膜5、25が両方とも上記のような積層構造を有していればより顕著な効果が得られる。

【0142】

なお、従来の方法では、保護膜およびゲート絶縁膜に対するエッチングを同時に行うので(Pass/GI同時エッチング)、これらの膜が上記のような積層膜であると、SiNx/SiO2/SiO2/SiNxからなる膜を一括してエッチングする。言い換えると、ドライエッチレートが互いに異なる3層(SiNx/SiO2/SiNx)を一括してエッチングする。このため、エッチングの際のテーパー制御は極めて難しい。SiNx膜の方がSiO2膜よりもドライエッチレートが数倍高いため、これらの積層膜をエッチングすると、SiNx膜がシフトしてかさ状になることがある。また、特許文献1のように保護膜上に有機絶縁膜を設けると、Pass/GI同時エッチングの際に、エッチングマスクである有機絶縁膜の表面ダメージも制御することが必要となるため、テーパー制御はほとんど不可能となる。

【0143】

これに対し、本実施形態によると、ES/GI同時エッチングにおいてSiO2/SiNx、保護膜(Passエッチング)においてSiNx/SiO2の2層のみに対してエッチングを行うので、SiNx/SiO2/SiNxの3層をエッチングする従来方法よりも高い精度でテーパー制御を行うことができる。

【0144】

なお、実施形態3で説明したように、本実施形態の半導体装置においても保護膜25と画素電極29との間に有機絶縁膜を設けてもよい。この場合でも、絶縁膜5、9の同時エッチングとは別個に、有機絶縁膜をエッチングマスクとして保護膜(SINx/SiO2)25のエッチングを行ってもよい(Passエッチング)。これにより、有機絶縁膜の表面ダメージを抑えつつ、保護膜25の開口部のテーパー形状を制御できる。

【0145】

なお、図11に示す例では、実施形態2の半導体装置における絶縁膜5および保護膜25として、SiNx膜およびSiO2膜からなる積層膜を用いているが、実施形態1の半導体装置における絶縁膜5および保護膜15として、SiO2およびSiNxからなる積層膜を用いてもよい。これにより、上記と同様の効果が得られる。すなわち、テーパー形状の制御性を低下させることなく、TFT特性の低下を抑制できる。この場合でも、保護膜15と画素電極19との間に、実施形態3で説明したような有機絶縁膜を設けてもよい。

【産業上の利用可能性】

【0146】

本発明は、アクティブマトリクス基板等の回路基板、液晶表示装置、有機エレクトロルミネセンス(EL)表示装置および無機エレクトロルミネセンス表示装置等の表示装置、イメージセンサー装置等の撮像装置、画像入力装置や指紋読み取り装置等の電子装置などの薄膜トランジスタを備えた装置に広く適用できる。特に、大型の液晶表示装置等に好適に適用され得る。

【符号の説明】

【0147】

1 基板

3a ゲート配線

3b 補助容量配線

3c 接続部

3d 接続部

5 絶縁膜(ゲート絶縁膜)

5L ゲート絶縁膜の下層

5U ゲート絶縁膜の上層

7a、7b 酸化物半導体層(活性層)

9 絶縁膜(保護膜、エッチストッパ)

11as、11ad、11b、11c、11d、17b、17c、27a、27b、27c、37a、37b、37c 開口部

13as、23as ソース配線

13ad、23ad ドレイン電極

13c、23c、19c、29c 接続部

15、25 保護膜

19、29 画素電極

36 有機絶縁膜

25L 保護膜の下層

25U 保護膜の上層

101、201 表示領域における1個の画素部

102、202 端子配置領域

【特許請求の範囲】

【請求項1】

基板と、前記基板上に形成された薄膜トランジスタと、前記薄膜トランジスタと外部配線とを電気的に接続する端子部とを備えた半導体装置であって、

前記薄膜トランジスタは、

前記基板上に設けられたゲート配線と、

前記ゲート配線上に形成された第1絶縁膜と、

前記第1絶縁膜上に形成され、チャネル領域と、前記チャネル領域の両側にそれぞれ位置するソース領域およびドレイン領域とを有する島状の酸化物半導体層と、

前記酸化物半導体層上に接して設けられた第2絶縁膜と、

前記第2絶縁膜上に設けられ、前記ソース領域と電気的に接続されたソース配線と、

前記第2絶縁膜上に設けられ、前記ドレイン領域と電気的に接続されたドレイン電極と、

前記ソース配線およびドレイン電極上に設けられ、前記薄膜トランジスタを覆う保護膜と

を備え、

前記端子部は、

前記ゲート配線と同一の導電膜から形成された第1接続部と、

前記第1接続部上に形成され、前記ソース配線およびドレイン電極と同一の導電膜から形成された第2接続部と、

前記第2接続部上に形成された第3接続部と

を備え、

前記第2接続部は、前記第1絶縁膜および前記第2絶縁膜に設けられた第1開口部内で、前記第1接続部と接しており、

前記第3接続部は、前記保護膜に設けられた第2開口部内で、前記第2接続部と接しており、

前記第1開口部は、前記第1絶縁膜および前記第2絶縁膜を同時にエッチングすることによって形成されており、前記第2開口部は、前記保護膜を前記第1および第2絶縁膜とは別個にエッチングすることによって形成されており、

前記第2接続部は、前記第1開口部における前記第1絶縁膜および前記第2絶縁膜の端面を覆い、かつ、前記第2開口部における前記保護膜の端面を覆っておらず、前記第2接続部の一部は前記第2絶縁膜と前記保護膜との間に配置されている半導体装置。

【請求項2】

前記基板の表面の法線方向から見て、前記第2開口部は、前記第1開口部の内部に位置する請求項1に記載の半導体装置。

【請求項3】

前記ドレイン電極と電気的に接続された画素電極をさらに備え、

前記第3接続部は、前記画素電極と同一の導電膜から形成されている請求項1または2に記載の半導体装置。

【請求項4】

前記基板に形成された補助容量をさらに備え、

前記補助容量は、

前記ゲート配線と同一の導電膜から形成された補助容量配線と、

前記補助容量配線を覆う前記第1絶縁膜と、

前記酸化物半導体層と同一の酸化物半導体膜から形成された補助容量形成用半導体層と、

前記補助容量形成用半導体層上に設けられた補助容量電極と

を有しており、

前記補助容量電極は、前記第2絶縁膜に形成された開口部内で前記補助容量形成用半導体層と接している請求項3に記載の半導体装置。

【請求項5】

前記補助容量電極は、前記ドレイン電極の一部であり、

前記画素電極は、前記保護膜に形成された開口部内で前記補助容量電極に接している請求項4に記載の半導体装置。

【請求項6】

前記補助容量電極は、前記画素電極の一部である請求項4に記載の半導体装置。

【請求項7】

前記ゲート配線と前記ソース配線とを電気的に接続するゲート・ソース接続部をさらに備え、

前記ゲート・ソース接続部では、前記ソース配線は、前記第1絶縁膜および前記第2絶縁膜に設けられた前記第1開口部内で前記ゲート配線に接している請求項1から6のいずれかに記載の半導体装置。

【請求項8】

前記保護膜と前記画素電極との間に、有機絶縁膜をさらに備える請求項1から7のいずれかに記載の半導体装置。

【請求項9】

前記第1絶縁膜および前記保護膜のうち少なくとも一方はSiO2を含む請求項1から8のいずれかに記載の半導体装置。

【請求項10】

前記第1絶縁膜は、SiO2膜およびSiNx膜を含む積層構造を有しており、前記SiO2膜は前記積層構造の最上層であり、前記酸化物半導体層の下面と接している請求項9に記載の半導体装置。

【請求項11】

前記保護膜は、SiO2膜およびSiNx膜を含む積層構造を有しており、前記SiO2膜は前記積層構造の最下層である請求項9または10に記載の半導体装置。

【請求項12】

前記ゲート配線の上面および側壁と前記ソース配線との間、および、前記ゲート配線の上面および側壁と前記ドレイン電極との間には、少なくとも前記第1絶縁膜および前記酸化物半導体層が設けられている請求項1から11のいずれかに記載の半導体装置。

【請求項13】

前記ゲート配線の上面および側壁と前記ソース配線との間、および、前記ゲート配線の上面および側壁と前記ドレイン電極との間に、前記第2絶縁膜がさらに設けられている請求項12に記載の半導体装置。

【請求項14】

前記第2絶縁膜は、前記酸化物半導体層の表面のうち前記ソース領域および前記ドレイン領域を除く全ての上面および側壁を覆っており、かつ、前記酸化物半導体層の側壁近傍で前記第1絶縁膜の上面と接している請求項1から13のいずれかに記載の半導体装置。

【請求項15】

前記酸化物半導体層のチャネル長方向に沿った幅は、前記ゲート配線のチャネル長方向に沿った幅よりも大きい請求項1から14のいずれかに記載の半導体装置。

【請求項16】

前記開口部の周縁において、前記第2接続部と前記第3接続部との間に前記保護膜が存在する請求項1から15のいずれかに記載の半導体装置。

【請求項17】

前記第2絶縁膜は、前記酸化物半導体層の前記ソース領域に達するソースコンタクト形成用開口部と、前記酸化物半導体層の前記ドレイン領域に達するドレインコンタクト形成用開口部とを有し、前記ソース配線は前記ソースコンタクト形成用開口部内で前記酸化物半導体層と接し、前記ドレイン電極は前記ドレインコンタクト形成用開口部内で前記酸化物半導体層と接している請求項1から16のいずれかに記載の半導体装置。

【請求項18】

前記ソースコンタクト形成用開口部および前記ドレインコンタクト形成用開口部と、前記第1開口部とは、エッチングにより同時に形成されている請求項17に記載の半導体装置。

【請求項19】

前記ソース配線は、前記ソースコンタクト形成用開口部の側壁、および、前記第2絶縁膜の上面のうち前記ソースコンタクト形成用開口部の周縁に位置する部分と接しており、

前記ドレイン電極は、前記ドレインコンタクト形成用開口部の側壁、および、前記第2絶縁膜の上面のうち前記ドレインコンタクト形成用開口部の周縁に位置する部分と接している請求項17または18に記載の半導体装置。

【請求項20】

前記第2開口部は、前記有機絶縁膜をマスクとして前記保護層をエッチングすることによって形成されている請求項8に記載の半導体装置。

【請求項21】

前記酸化物半導体層はIGZO層である請求項1から20のいずれかに記載の半導体装置。

【請求項1】

基板と、前記基板上に形成された薄膜トランジスタと、前記薄膜トランジスタと外部配線とを電気的に接続する端子部とを備えた半導体装置であって、

前記薄膜トランジスタは、

前記基板上に設けられたゲート配線と、

前記ゲート配線上に形成された第1絶縁膜と、

前記第1絶縁膜上に形成され、チャネル領域と、前記チャネル領域の両側にそれぞれ位置するソース領域およびドレイン領域とを有する島状の酸化物半導体層と、

前記酸化物半導体層上に接して設けられた第2絶縁膜と、

前記第2絶縁膜上に設けられ、前記ソース領域と電気的に接続されたソース配線と、

前記第2絶縁膜上に設けられ、前記ドレイン領域と電気的に接続されたドレイン電極と、

前記ソース配線およびドレイン電極上に設けられ、前記薄膜トランジスタを覆う保護膜と

を備え、

前記端子部は、

前記ゲート配線と同一の導電膜から形成された第1接続部と、

前記第1接続部上に形成され、前記ソース配線およびドレイン電極と同一の導電膜から形成された第2接続部と、

前記第2接続部上に形成された第3接続部と

を備え、

前記第2接続部は、前記第1絶縁膜および前記第2絶縁膜に設けられた第1開口部内で、前記第1接続部と接しており、

前記第3接続部は、前記保護膜に設けられた第2開口部内で、前記第2接続部と接しており、

前記第1開口部は、前記第1絶縁膜および前記第2絶縁膜を同時にエッチングすることによって形成されており、前記第2開口部は、前記保護膜を前記第1および第2絶縁膜とは別個にエッチングすることによって形成されており、

前記第2接続部は、前記第1開口部における前記第1絶縁膜および前記第2絶縁膜の端面を覆い、かつ、前記第2開口部における前記保護膜の端面を覆っておらず、前記第2接続部の一部は前記第2絶縁膜と前記保護膜との間に配置されている半導体装置。

【請求項2】

前記基板の表面の法線方向から見て、前記第2開口部は、前記第1開口部の内部に位置する請求項1に記載の半導体装置。

【請求項3】

前記ドレイン電極と電気的に接続された画素電極をさらに備え、

前記第3接続部は、前記画素電極と同一の導電膜から形成されている請求項1または2に記載の半導体装置。

【請求項4】

前記基板に形成された補助容量をさらに備え、

前記補助容量は、

前記ゲート配線と同一の導電膜から形成された補助容量配線と、

前記補助容量配線を覆う前記第1絶縁膜と、

前記酸化物半導体層と同一の酸化物半導体膜から形成された補助容量形成用半導体層と、

前記補助容量形成用半導体層上に設けられた補助容量電極と

を有しており、

前記補助容量電極は、前記第2絶縁膜に形成された開口部内で前記補助容量形成用半導体層と接している請求項3に記載の半導体装置。

【請求項5】

前記補助容量電極は、前記ドレイン電極の一部であり、

前記画素電極は、前記保護膜に形成された開口部内で前記補助容量電極に接している請求項4に記載の半導体装置。

【請求項6】

前記補助容量電極は、前記画素電極の一部である請求項4に記載の半導体装置。

【請求項7】

前記ゲート配線と前記ソース配線とを電気的に接続するゲート・ソース接続部をさらに備え、

前記ゲート・ソース接続部では、前記ソース配線は、前記第1絶縁膜および前記第2絶縁膜に設けられた前記第1開口部内で前記ゲート配線に接している請求項1から6のいずれかに記載の半導体装置。

【請求項8】

前記保護膜と前記画素電極との間に、有機絶縁膜をさらに備える請求項1から7のいずれかに記載の半導体装置。

【請求項9】

前記第1絶縁膜および前記保護膜のうち少なくとも一方はSiO2を含む請求項1から8のいずれかに記載の半導体装置。

【請求項10】

前記第1絶縁膜は、SiO2膜およびSiNx膜を含む積層構造を有しており、前記SiO2膜は前記積層構造の最上層であり、前記酸化物半導体層の下面と接している請求項9に記載の半導体装置。

【請求項11】

前記保護膜は、SiO2膜およびSiNx膜を含む積層構造を有しており、前記SiO2膜は前記積層構造の最下層である請求項9または10に記載の半導体装置。

【請求項12】

前記ゲート配線の上面および側壁と前記ソース配線との間、および、前記ゲート配線の上面および側壁と前記ドレイン電極との間には、少なくとも前記第1絶縁膜および前記酸化物半導体層が設けられている請求項1から11のいずれかに記載の半導体装置。

【請求項13】

前記ゲート配線の上面および側壁と前記ソース配線との間、および、前記ゲート配線の上面および側壁と前記ドレイン電極との間に、前記第2絶縁膜がさらに設けられている請求項12に記載の半導体装置。

【請求項14】

前記第2絶縁膜は、前記酸化物半導体層の表面のうち前記ソース領域および前記ドレイン領域を除く全ての上面および側壁を覆っており、かつ、前記酸化物半導体層の側壁近傍で前記第1絶縁膜の上面と接している請求項1から13のいずれかに記載の半導体装置。

【請求項15】

前記酸化物半導体層のチャネル長方向に沿った幅は、前記ゲート配線のチャネル長方向に沿った幅よりも大きい請求項1から14のいずれかに記載の半導体装置。

【請求項16】

前記開口部の周縁において、前記第2接続部と前記第3接続部との間に前記保護膜が存在する請求項1から15のいずれかに記載の半導体装置。

【請求項17】

前記第2絶縁膜は、前記酸化物半導体層の前記ソース領域に達するソースコンタクト形成用開口部と、前記酸化物半導体層の前記ドレイン領域に達するドレインコンタクト形成用開口部とを有し、前記ソース配線は前記ソースコンタクト形成用開口部内で前記酸化物半導体層と接し、前記ドレイン電極は前記ドレインコンタクト形成用開口部内で前記酸化物半導体層と接している請求項1から16のいずれかに記載の半導体装置。

【請求項18】

前記ソースコンタクト形成用開口部および前記ドレインコンタクト形成用開口部と、前記第1開口部とは、エッチングにより同時に形成されている請求項17に記載の半導体装置。

【請求項19】

前記ソース配線は、前記ソースコンタクト形成用開口部の側壁、および、前記第2絶縁膜の上面のうち前記ソースコンタクト形成用開口部の周縁に位置する部分と接しており、

前記ドレイン電極は、前記ドレインコンタクト形成用開口部の側壁、および、前記第2絶縁膜の上面のうち前記ドレインコンタクト形成用開口部の周縁に位置する部分と接している請求項17または18に記載の半導体装置。

【請求項20】

前記第2開口部は、前記有機絶縁膜をマスクとして前記保護層をエッチングすることによって形成されている請求項8に記載の半導体装置。

【請求項21】

前記酸化物半導体層はIGZO層である請求項1から20のいずれかに記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−51421(P2013−51421A)

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願番号】特願2012−206132(P2012−206132)

【出願日】平成24年9月19日(2012.9.19)

【分割の表示】特願2011−545195(P2011−545195)の分割

【原出願日】平成22年12月3日(2010.12.3)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願日】平成24年9月19日(2012.9.19)

【分割の表示】特願2011−545195(P2011−545195)の分割

【原出願日】平成22年12月3日(2010.12.3)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]