半導体装置

【課題】接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供する。

【解決手段】第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、溝の内側に埋め込まれた電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである。

【解決手段】第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、溝の内側に埋め込まれた電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、高耐圧化のための構造に特徴を有する半導体装置に関する。

【背景技術】

【0002】

従来技術として、深い拡散層を形成することなく、高耐圧の半導体素子を提供する技術が開示されている(例えば、特許文献1参照。)。

【0003】

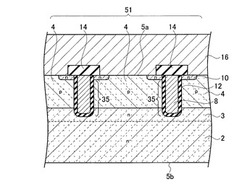

特許文献1に記載された高耐圧半導体装置は、図11に示すように、素子領域51とその周囲に配置された接合終端領域52とを有する。素子領域51および接合終端領域52において、高抵抗のn型ベース層31の表面内にp型ベース層34が拡散形成される。素子領域51には、ゲート電極を埋め込んだ複数のトレンチ35が形成される。素子領域51を囲んで、接合終端領域52には連続或いは不連続なリング形状を有する複数の終端トレンチ55が形成される。終端トレンチ55はp型ベース層34を貫通し、n型ベース層31の途中まで達する深さを有する。接合終端領域52において、p型ベース層34は終端トレンチ55により電気的に分離された複数の部分に分割される。

【0004】

特許文献1に記載された高耐圧半導体装置においては、図11に示すように、各トレンチ(35、55)の深さが、隣り合うトレンチ(35、55)の間隔(p型ベース層34の幅)よりも大きくなるように設定されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平9−283754号公報(第2−3頁、第1図)

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明者は、図11に示す従来型構造に基づいて、電位分布をシミュレーションした。その結果を図11中に、10V/本の等電位面で示す。特許文献1に記載された高耐圧半導体装置においては、図11に示すように、トレンチ35、55の深さが、トレンチ35、55の幅よりも大きくなるように設定されているが、図11中に示すシミュレーション結果によれば、接合終端領域52における電界緩和の効果は少なく所望の耐圧を得ることができない。

【0007】

特許文献1に記載された高耐圧半導体装置においては、各トレンチ(35、55)の深さが、隣り合うトレンチ(35、55)の間隔(p型ベース層34の幅)よりも大きくなるように設定されているが、本発明者は、逆に各トレンチ(35、55)の深さが、隣り合うトレンチ(35、55)の間隔(p型ベース層34の幅)よりも小さく設定した方が、接合終端領域52における電界緩和効果があり、高耐圧が得られることを見出した。

【0008】

本発明の目的は、接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供することにある。

【課題を解決するための手段】

【0009】

上記目的を達成するための本発明の一態様によれば、第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである半導体装置が提供される。

【発明の効果】

【0010】

本発明の半導体装置によれば、接合終端領域における電界を緩和し、高耐圧化することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の第1の実施の形態に係る半導体装置の素子領域の模式的断面構造図。

【図2】本発明の第1の実施の形態に係る半導体装置の接合終端領域の模式的断面構造図。

【図3】本発明の第1の実施の形態に係る半導体装置の接合終端領域の各部のキャパシタのモデル図。

【図4】本発明の第1の実施の形態に係る半導体装置において、トレンチ深さを浅く設定した場合の電位分布シミュレーション結果を示す模式図(10V/本)。

【図5】本発明の第1の実施の形態に係る半導体装置において、トレンチ深さを浅く設定し、かつp型ベース層の間隔を最適化した場合の電位分布シミュレーション結果を示す模式図(20V/本)。

【図6】耐圧相対値とトレンチ深さ/ベース深さ(WT/WB)の関係を表す特性図。

【図7】図3に対応する容量C1〜C4とコレクタ電圧VCE(V)との関係を示す特性図。

【図8】本発明の第1の実施の形態に係る半導体装置の接合終端領域において、フィールドプレート電極構造の模式的断面構造図。

【図9】本発明の第1の実施の形態に係る半導体装置の接合終端領域において、第2導電層からなるゲート電極と接続する取り出し電極および当該取り出し電極と接続されたフィールドプレート電極構造の模式的断面構造図。

【図10】本発明の第1の実施の形態に係る半導体装置の接合終端領域において、複数の第2導電層と接続されかつフローティング状態になされている取り出し電極構造の模式的断面構造図。

【図11】従来例に係る半導体装置において、電位分布シミュレーション結果を示す模式図(10V/本)。

【発明を実施するための形態】

【0012】

次に、図面を参照して、本発明の実施の形態を説明する。以下の図面の記載において、同一または類似の部分には同一または類似の符号を付している。ただし、図面は模式的なものであり、現実のものとは異なることに留意すべきである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0013】

また、以下に示す実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の技術的思想は、各構成部品の配置などを下記のものに特定するものでない。この発明の技術的思想は、特許請求の範囲において、種々の変更を加えることができる。

【0014】

[第1の実施の形態]

図1は、本発明の第1の実施の形態に係る半導体装置の素子領域51の模式的断面構造図を示す。また、図2は、本発明の第1の実施の形態に係る半導体装置の接合終端領域52の模式的断面構造図を示す。上記において、素子領域51、接合終端領域52は一部分を拡大して模式的に示したものであり、紙面左右方向および表裏方向に連続して形成され、配置されている。また、上面から見て、素子領域51を取り囲むように、接合終端領域52は配置されている。

【0015】

本発明の第1の実施の形態に係る半導体装置の素子領域51は、一方の主面5aと他方の主面5bを有する半導体基体に配置されている。当該半導体基体には、図1に示すように、第1導電型の不純物を有する第1半導体領域(n-型ベース層)2と、第1半導体領域2の上面と接し、一方の主面5aにおいて一部が露出し、かつ第1導電型と異なる第2導電型の第2半導体領域(p型ベース層)4と、第2半導体領域4の上面と接し、一方の主面5aにおいて一部が露出し、かつ第1導電型の第3半導体領域(n型エミッタ領域)10と、一方の主面5aから第2半導体領域4および第3半導体領域10を貫通し、底面が第1半導体領域2に達するトレンチ35と、トレンチ35の側面および底面に形成されたゲート絶縁膜12と、ゲート絶縁膜12の内側に埋め込まれたゲート電極(第1導電層)8と、ゲート電極8と電気的に接続された制御電極(図示省略)と、第1半導体領域2と電気的に接続された第1の電極(コレクタ電極)(図示省略)と、第2半導体領域4および第3半導体領域10と電気的に接続された第3の電極16(エミッタ電極)とを備える。

【0016】

図1に示される半導体装置において、絶縁ゲートバイポーラトランジスタ(IGBT:Insulated Gate Bipolar Transistor)として構成される場合には、第1半導体領域2の他方の主面5bには、さらに第2導電型の第4半導体領域(コレクタ領域)が配置される。IGBTの場合、第2半導体領域4および第3半導体領域10はそれぞれベース領域、エミッタ領域となる。

【0017】

一方、図1に示される半導体装置において、絶縁ゲート電界効果トランジスタ(MISFET:Metal Insulator Semiconductor Field Effect Transistor)として構成される場合には、第1半導体領域2の他方の主面5bには、さらに第1導電型の第4半導体領域(ドレイン領域)が配置されることが望ましい。MISFETの場合、第2半導体領域4および第3半導体領域10はそれぞれベース領域、ソース領域となる。

【0018】

ゲート電極(8)/ゲート絶縁膜(12)/p型ベース層(4)からなるMIS構造のp型ベース層4の界面近傍にnチャネル領域が導通状態において形成される点は、IGBTの場合もMISFETの場合も同様である。

【0019】

また、図1に示すように、n型バッファ層3をp型ベース層4とn-型ベース層2との間に介在させて、隣り合うp型ベース層4間のパンチングスルーを防止し、nチャネルMIS構造のチャネル長を明確に規定する構成としても良い。

【0020】

また、図1に示すように、トレンチ35の上部において、n型エミッタ(ソース)領域10とゲート絶縁膜12とゲート電極8の上部には層間絶縁膜14が配置されている。層間絶縁膜14は後述する接合終端領域52における層間絶縁膜18と同一材料で、同時プロセスで形成することもできる。

【0021】

本発明の第1の実施の形態に係る半導体装置の上方から見て、素子領域51を取り囲むように形成された接合終端領域52は、図2に示すように、第1導電型の不純物を有する第1半導体領域(n-型ベース層)2と、第1半導体領域2の上面と接し、かつ第1導電型と異なる第2導電型の第2半導体領域(p型ベース層)4と、第2半導体領域4の上面(一方の主面5a)から深さ方向に形成された溝からなる終端トレンチ55と、終端トレンチ55の側壁および底面に形成されたゲート絶縁膜12と、ゲート絶縁膜12を介して終端トレンチ55の内側に埋め込まれたゲート電極(第2導電層)8とを有し、第2半導体領域4の上面から終端トレンチ55の溝の底面までの深さWTが第2半導体領域の厚みWBの0.9〜2.0倍であることを特徴とする。

【0022】

さらに、本発明の第1の実施の形態に係る半導体装置の接合終端領域52には、図2に示すように、第2半導体領域4の上面(一方の主面5a)上に配置された層間絶縁膜18と、層間絶縁膜18上に配置されたフィールドプレート電極20を備える。

【0023】

本発明の第1の実施の形態に係る半導体装置において、素子領域51内の第1導電層からなるゲート電極8、および接合終端領域52内の第2導電層からなるゲート電極8は、図1、2に示すように、同時プロセスによって、ポリシリコンが充填されたトレンチ構造によって形成されていても良い。

【0024】

本発明の第1の実施の形態に係る半導体装置において、素子領域51内のp型ベース層4と、接合終端領域52内のp型ベース層4は、同時プロセスによって形成することができる。

【0025】

また、本発明の第1の実施の形態に係る半導体装置において、接合終端領域52内の終端トレンチ55は、図2に示すように、紙面上垂直にまた素子表面に素子領域51を囲みながらリング状に形成されている。さらに、接合終端領域52において、外周に拡散形成されたp型ベース層4はリング状に分断形成されている。

【0026】

図3は、本発明の第1の実施の形態に係る半導体装置の接合終端領域52の構造における各部のキャパシタのモデル図を示す。

【0027】

p型ベース層4がリング状に分断形成されている外周構造の素子に電圧印加した場合、各部位の電位は、図3に示すように、容量の分布定数回路としても解析することができる。

【0028】

本発明の第1の実施の形態に係る半導体装置として、図1に示すようなIGBT若しくはMISFETにおいて、所定の耐圧限界近くまでコレクタ電圧若しくはドレイン電圧を印加されている場合、図3内に模式的に示すように、n-型ベース層2(n-ドレイン領域)に空乏層が形成される。また、p型ベース層4と終端トレンチ55内のゲート電極8間には薄いゲート絶縁膜12が形成されているため、C3,C4,C1,C2間には、後述するように、(1)式の関係が成立することが望ましい。

【0029】

この場合、表面近傍の電位分布は、直列接続されたp型ベース層4と終端トレンチ55内のポリシリコン(ゲート電極8)間の容量結合によって決定される。

【0030】

この性質を利用すると外周の電位分布は任意に調整が可能となる。

【0031】

図3に示すように、p型ベース層4の厚さを示すベース深さはWBで定義され、トレンチ深さはWTで定義される。C1はp型ベース層4とn-型ベース層2間のキャパシタを表す。C2はトレンチ構造におけるゲート電極8とn-型ベース層2間のキャパシタを表す。C3,C4は、トレンチ構造におけるゲート電極8とp型ベース層4間のキャパシタを表す。上述した各部のキャパシタの間には、

C3,C4>>C1,C2 …(1)

の関係が成立していることが望ましい。

【0032】

また、図4は、本発明の第1の実施の形態に係る半導体装置において、トレンチ深さを浅く設定した場合の電位分布シミュレーション結果の模式図を示す。すなわち、図4においては、p型ベース層4の間隔を最適化せず、各トレンチ(35、55)の深さが、隣り合うトレンチ(35、55)の間隔(p型ベース層4の幅)よりも浅く設定しただけでも、接合終端領域52における電界緩和効果があり、高耐圧が得られる。図4において、各ラインは10V/本で示されている。

【0033】

さらに、図5は、本発明の第1の実施の形態に係る半導体装置において、各トレンチ(35、55)の深さを、隣り合うトレンチ(35、55)の間隔(p型ベース層4の幅)よりも浅く設定し、かつp型ベース層4の間隔を最適化した場合の電位分布シミュレーション結果の模式図を示す。すなわち、図5においては、高耐圧を得られるように外周各部のp型ベース層4の分断幅を最適化して設定したシミュレーション結果を示す。

【0034】

図5において、各ラインは20V/本で示されている。図5から明らかなように、各トレンチ(35、55)の深さを、隣り合うトレンチ(35、55)の間隔(p型ベース層4の幅)よりも浅く設定し、かつp型ベース層4の間隔を最適化した場合には、素子領域51近傍の電界緩和効果が顕著に得られ、かつ等電位面は、素子領域51から離隔した接合終端領域52まで均一に延伸している。

【0035】

図6は、耐圧相対値とトレンチ深さ/ベース深さ(WT/WB)の関係を表す。図6から明らかなように、トレンチ深さ/ベース深さ(WT/WB)の値は、例えば約0.9〜2.0の範囲において、所望の耐圧相対値が得られることがわかる。

【0036】

図7は、本発明の第1の実施の形態に係る半導体装置において、各トレンチ(35、55)の深さを、隣り合うトレンチ(35、55)の間隔(p型ベース層4の幅)よりも浅く設定し、かつp型ベース層4の間隔を最適化した場合における図3に対応する容量C1〜C4とコレクタ電圧VCE(V)との関係を示す。IGBT構造において、コレクタ電圧VCE=600Vを印加した場合、WT/WB=1.3において、

C1:C2:C3:C4=1:1.5:79:79 …(2)

の結果が得られている。すなわち、(1)式の関係が成立している。

【0037】

図5において示した、高耐圧を得られるように外周各部のp型ベース層4の分断幅を最適化して設定したシミュレーション結果を引き出すためにはp型ベース層4の拡散深さWBとトレンチ深さWTの比を、WB:WT=1:0.9〜1:2.0程度に抑える必要がある。

【0038】

終端トレンチ55の深さWTが深いと、終端トレンチ55の側面の面積が増加するためゲート電極8とn-型ベース層2間の容量(C2)が大きくなり、電位分布制御可能の前提となる(1)式の条件(C3,C4>>C1,C2)が満たされなくなるためである。

【0039】

また、WB:WT=1:0.9の場合、すなわちトレンチ深さWTがp型ベース層4の深さWBより浅い場合においても、コレクタ電圧VCE(V)の印加によって、p型ベース層4/n-型ベース層2間のpn接合からの空乏層の広がりにより、p型ベース層4が分断され、同等の効果が期待できる。ただし、本発明の第1の実施の形態に係る半導体装置の効果を十分に得るためには、WT/WB>1であることが望ましい。

【0040】

(外周構造)

本発明の第1の実施の形態に係る半導体装置において、外周構造は、以下の複数の構成を複数組み合わせて実施して、最適化し調整することができる。

【0041】

(a)接合終端領域52のp型ベース層4の分断寸法を適切に設定する。すなわち、素子領域51に近い場所はp型ベース層4の幅を相対的に広く設定し、素子領域51から離隔するに従い、p型ベース層4の幅を相対的に狭く設定して、大きな耐圧が確保することができる。

【0042】

(b)トレンチ側壁のゲート絶縁膜12の厚みが2種類以上使用可能な場合、例えば素子領域51に近いトレンチは薄いゲート絶縁膜12を用い、素子領域51から離隔するに従い、相対的に厚いゲート絶縁膜12を用いると、接合終端領域52において、素子領域51に近いほど容量C1は大きくなり、一方、素子領域51から離隔方向への位置変化に対して素子領域51に近い場所の電位変化は小さくなり電界は緩和される。

【0043】

素子領域51から離隔した場所の電位変化は大きく電界は高まるが、p型ベース層4とn-ベース層2との間の電位差は小さいため、素子領域51から離隔した場所における耐圧破壊は生じない。

【0044】

(c)図8は、本発明の第1の実施の形態に係る半導体装置の接合終端領域において、フィールドプレート電極構造の模式的断面構造を示す。すなわち、図8に示すように、少なくとも素子領域51近傍の接合終端領域52上に配置された層間絶縁膜18と、層間絶縁膜18上に延在して配置されたフィールドプレート電極20とを備えることを特徴とする。

【0045】

フィールドプレート電極20は、エミッタ領域(ソース領域)10に接続された第3の電極と等電位になされていてもよく、或いはまた、素子領域51内の第1導電層からなるゲート電極8と等電位になされていても良い。

【0046】

層間絶縁膜18は、例えばリン・ケイ酸ガラス(PSG:Phospho Silicate Glasses)膜、ホウ素・リン・ケイ酸ガラス(BPSG:Boro−Phospho Silicate Glasses)膜、ノンドープ・ケイ酸ガラス膜、窒化シリコン膜、ポリシリコン膜などを用いることができる。

【0047】

フィールドプレート電極20は、例えばアルミニウム電極で形成し、PSG膜などからなる層間絶縁膜18上にフィールドプレート電極20を作成することで素子領域51に近い場所の電位変化を小さくし、電界を緩和することができる。

【0048】

(d)図9は、本発明の第1の実施の形態に係る半導体装置の接合終端領域52において、第2導電層からなるゲート電極8と接続する取り出し電極22および当該取り出し電極22と接続されたフィールドプレート電極20からなる構造の模式的断面構造を示す。

【0049】

すなわち、接合終端領域52上に配置された層間絶縁膜18と、接合終端領域52上に層間絶縁膜18を介して配置され、第2導電層からなるゲート電極8と接続する取り出し電極22と、層間絶縁膜18上に延在して配置され、取り出し電極22と接続されたフィールドプレート電極20とを備えることを特徴とする。

【0050】

層間絶縁膜18は、例えばPSG膜、BPSG膜、ノンドープ・ケイ酸ガラス膜、窒化シリコン膜、ポリシリコン膜などを用いて形成することができる。フィールドプレート電極20は、例えばアルミニウム電極で形成し、PSG膜などからなる層間絶縁膜18上にフィールドプレート電極20を作成することで、フィールドプレート電極20の下側のp型ベース層4近傍の電位変化を小さくし、電界を緩和することができる。

【0051】

(e)図10は、本発明の第1の実施の形態に係る半導体装置の接合終端領域において、複数の第2導電層からなるゲート電極8と接続され、かつフローティング状態になされている取り出し電極22の構造の模式的断面構造を示す。

【0052】

すなわち、接合終端領域52上に配置された層間絶縁膜18と、接合終端領域52上に層間絶縁膜18を介して配置され、複数の第2導電層からなるゲート電極8と接続する取り出し電極22とを備え、当該取り出し電極22はフローティング状態になされていることを特徴とする。例えば、複数の第2導電層からなるゲート電極8は、フローティング状態になされているポリシリコン層で形成される。

【0053】

取り出し電極22は、図10に示すように、フローティング状態になされてポリシリコン層同士を共通接続することで形成することができる。

【0054】

(f)最外周部には空乏層の延びを止めるため、高不純物密度層を拡散形成しても良い。

【0055】

(g)最外周部の複数の終端トレンチ55を形成するゲート電極8を、n-ベース層2若しくはドレイン電極(コレクタ電極)と接続した等電位ポテンシャルリング(EQR:EQui-potential Ring)として使用する構成を備えていてもよい。

【0056】

(h)素子領域51と接合終端領域52の境界の素子領域51側にもトレンチを数列作成して、電界緩和を図る構成を備えていてもよい。

【0057】

(i)あるいはまた、接合終端領域52において、終端トレンチ55の幅を場所によって変えることによって、電界緩和を図る構成を備えていてもよい。

【0058】

本発明の第1の実施の形態に係る半導体装置によれば、接合終端領域における電界を緩和し、高耐圧化することができる。

【0059】

[その他の実施の形態]

上記のように、本発明は第1の実施の形態によって記載したが、この開示の一部をなす論述および図面はこの発明を限定するものでないと理解すべきである。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0060】

本発明は第1の実施の形態に係る半導体装置としては、トレンチ構造を有するIGBT、MISFETなどの例を開示したが、これらに限定されるものではなく、トレンチ構造を有するIEGT、SIT、SIサイリスタなどのデバイス構造においても適用可能である。

【0061】

さらに、半導体材料としては、シリコンに限定されるものではなく、SiC、GaN系、GaAs系、InP系などの化合物半導体、或いはヘテロ接合のベース構造、或いはHEMT構造のチャネル構造を適用することもできる。

【0062】

このように、本発明はここでは記載していない様々な実施の形態などを含むことは勿論である。したがって、本発明の技術的範囲は上記の説明から妥当な特許請求の範囲に係る発明特定事項によってのみ定められるものである。

【符号の説明】

【0063】

2…n-型ベース層(第1半導体領域)

3…n型バッファ層

4、34…p型ベース層(第2半導体領域)

5a…一方の主面

5b…他方の主面

8…ゲート電極(第1導電層、第2導電層)

10…n型エミッタ(ソース)領域(第3半導体領域)

12…ゲート絶縁膜

14、18…層間絶縁膜

16…エミッタ(ソース)電極

20…フィールドプレート電極

22…取り出し電極

31…n型ベース層

35…トレンチ

51…素子領域

52…接合終端領域

55…終端トレンチ

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、高耐圧化のための構造に特徴を有する半導体装置に関する。

【背景技術】

【0002】

従来技術として、深い拡散層を形成することなく、高耐圧の半導体素子を提供する技術が開示されている(例えば、特許文献1参照。)。

【0003】

特許文献1に記載された高耐圧半導体装置は、図11に示すように、素子領域51とその周囲に配置された接合終端領域52とを有する。素子領域51および接合終端領域52において、高抵抗のn型ベース層31の表面内にp型ベース層34が拡散形成される。素子領域51には、ゲート電極を埋め込んだ複数のトレンチ35が形成される。素子領域51を囲んで、接合終端領域52には連続或いは不連続なリング形状を有する複数の終端トレンチ55が形成される。終端トレンチ55はp型ベース層34を貫通し、n型ベース層31の途中まで達する深さを有する。接合終端領域52において、p型ベース層34は終端トレンチ55により電気的に分離された複数の部分に分割される。

【0004】

特許文献1に記載された高耐圧半導体装置においては、図11に示すように、各トレンチ(35、55)の深さが、隣り合うトレンチ(35、55)の間隔(p型ベース層34の幅)よりも大きくなるように設定されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平9−283754号公報(第2−3頁、第1図)

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明者は、図11に示す従来型構造に基づいて、電位分布をシミュレーションした。その結果を図11中に、10V/本の等電位面で示す。特許文献1に記載された高耐圧半導体装置においては、図11に示すように、トレンチ35、55の深さが、トレンチ35、55の幅よりも大きくなるように設定されているが、図11中に示すシミュレーション結果によれば、接合終端領域52における電界緩和の効果は少なく所望の耐圧を得ることができない。

【0007】

特許文献1に記載された高耐圧半導体装置においては、各トレンチ(35、55)の深さが、隣り合うトレンチ(35、55)の間隔(p型ベース層34の幅)よりも大きくなるように設定されているが、本発明者は、逆に各トレンチ(35、55)の深さが、隣り合うトレンチ(35、55)の間隔(p型ベース層34の幅)よりも小さく設定した方が、接合終端領域52における電界緩和効果があり、高耐圧が得られることを見出した。

【0008】

本発明の目的は、接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供することにある。

【課題を解決するための手段】

【0009】

上記目的を達成するための本発明の一態様によれば、第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである半導体装置が提供される。

【発明の効果】

【0010】

本発明の半導体装置によれば、接合終端領域における電界を緩和し、高耐圧化することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の第1の実施の形態に係る半導体装置の素子領域の模式的断面構造図。

【図2】本発明の第1の実施の形態に係る半導体装置の接合終端領域の模式的断面構造図。

【図3】本発明の第1の実施の形態に係る半導体装置の接合終端領域の各部のキャパシタのモデル図。

【図4】本発明の第1の実施の形態に係る半導体装置において、トレンチ深さを浅く設定した場合の電位分布シミュレーション結果を示す模式図(10V/本)。

【図5】本発明の第1の実施の形態に係る半導体装置において、トレンチ深さを浅く設定し、かつp型ベース層の間隔を最適化した場合の電位分布シミュレーション結果を示す模式図(20V/本)。

【図6】耐圧相対値とトレンチ深さ/ベース深さ(WT/WB)の関係を表す特性図。

【図7】図3に対応する容量C1〜C4とコレクタ電圧VCE(V)との関係を示す特性図。

【図8】本発明の第1の実施の形態に係る半導体装置の接合終端領域において、フィールドプレート電極構造の模式的断面構造図。

【図9】本発明の第1の実施の形態に係る半導体装置の接合終端領域において、第2導電層からなるゲート電極と接続する取り出し電極および当該取り出し電極と接続されたフィールドプレート電極構造の模式的断面構造図。

【図10】本発明の第1の実施の形態に係る半導体装置の接合終端領域において、複数の第2導電層と接続されかつフローティング状態になされている取り出し電極構造の模式的断面構造図。

【図11】従来例に係る半導体装置において、電位分布シミュレーション結果を示す模式図(10V/本)。

【発明を実施するための形態】

【0012】

次に、図面を参照して、本発明の実施の形態を説明する。以下の図面の記載において、同一または類似の部分には同一または類似の符号を付している。ただし、図面は模式的なものであり、現実のものとは異なることに留意すべきである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0013】

また、以下に示す実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の技術的思想は、各構成部品の配置などを下記のものに特定するものでない。この発明の技術的思想は、特許請求の範囲において、種々の変更を加えることができる。

【0014】

[第1の実施の形態]

図1は、本発明の第1の実施の形態に係る半導体装置の素子領域51の模式的断面構造図を示す。また、図2は、本発明の第1の実施の形態に係る半導体装置の接合終端領域52の模式的断面構造図を示す。上記において、素子領域51、接合終端領域52は一部分を拡大して模式的に示したものであり、紙面左右方向および表裏方向に連続して形成され、配置されている。また、上面から見て、素子領域51を取り囲むように、接合終端領域52は配置されている。

【0015】

本発明の第1の実施の形態に係る半導体装置の素子領域51は、一方の主面5aと他方の主面5bを有する半導体基体に配置されている。当該半導体基体には、図1に示すように、第1導電型の不純物を有する第1半導体領域(n-型ベース層)2と、第1半導体領域2の上面と接し、一方の主面5aにおいて一部が露出し、かつ第1導電型と異なる第2導電型の第2半導体領域(p型ベース層)4と、第2半導体領域4の上面と接し、一方の主面5aにおいて一部が露出し、かつ第1導電型の第3半導体領域(n型エミッタ領域)10と、一方の主面5aから第2半導体領域4および第3半導体領域10を貫通し、底面が第1半導体領域2に達するトレンチ35と、トレンチ35の側面および底面に形成されたゲート絶縁膜12と、ゲート絶縁膜12の内側に埋め込まれたゲート電極(第1導電層)8と、ゲート電極8と電気的に接続された制御電極(図示省略)と、第1半導体領域2と電気的に接続された第1の電極(コレクタ電極)(図示省略)と、第2半導体領域4および第3半導体領域10と電気的に接続された第3の電極16(エミッタ電極)とを備える。

【0016】

図1に示される半導体装置において、絶縁ゲートバイポーラトランジスタ(IGBT:Insulated Gate Bipolar Transistor)として構成される場合には、第1半導体領域2の他方の主面5bには、さらに第2導電型の第4半導体領域(コレクタ領域)が配置される。IGBTの場合、第2半導体領域4および第3半導体領域10はそれぞれベース領域、エミッタ領域となる。

【0017】

一方、図1に示される半導体装置において、絶縁ゲート電界効果トランジスタ(MISFET:Metal Insulator Semiconductor Field Effect Transistor)として構成される場合には、第1半導体領域2の他方の主面5bには、さらに第1導電型の第4半導体領域(ドレイン領域)が配置されることが望ましい。MISFETの場合、第2半導体領域4および第3半導体領域10はそれぞれベース領域、ソース領域となる。

【0018】

ゲート電極(8)/ゲート絶縁膜(12)/p型ベース層(4)からなるMIS構造のp型ベース層4の界面近傍にnチャネル領域が導通状態において形成される点は、IGBTの場合もMISFETの場合も同様である。

【0019】

また、図1に示すように、n型バッファ層3をp型ベース層4とn-型ベース層2との間に介在させて、隣り合うp型ベース層4間のパンチングスルーを防止し、nチャネルMIS構造のチャネル長を明確に規定する構成としても良い。

【0020】

また、図1に示すように、トレンチ35の上部において、n型エミッタ(ソース)領域10とゲート絶縁膜12とゲート電極8の上部には層間絶縁膜14が配置されている。層間絶縁膜14は後述する接合終端領域52における層間絶縁膜18と同一材料で、同時プロセスで形成することもできる。

【0021】

本発明の第1の実施の形態に係る半導体装置の上方から見て、素子領域51を取り囲むように形成された接合終端領域52は、図2に示すように、第1導電型の不純物を有する第1半導体領域(n-型ベース層)2と、第1半導体領域2の上面と接し、かつ第1導電型と異なる第2導電型の第2半導体領域(p型ベース層)4と、第2半導体領域4の上面(一方の主面5a)から深さ方向に形成された溝からなる終端トレンチ55と、終端トレンチ55の側壁および底面に形成されたゲート絶縁膜12と、ゲート絶縁膜12を介して終端トレンチ55の内側に埋め込まれたゲート電極(第2導電層)8とを有し、第2半導体領域4の上面から終端トレンチ55の溝の底面までの深さWTが第2半導体領域の厚みWBの0.9〜2.0倍であることを特徴とする。

【0022】

さらに、本発明の第1の実施の形態に係る半導体装置の接合終端領域52には、図2に示すように、第2半導体領域4の上面(一方の主面5a)上に配置された層間絶縁膜18と、層間絶縁膜18上に配置されたフィールドプレート電極20を備える。

【0023】

本発明の第1の実施の形態に係る半導体装置において、素子領域51内の第1導電層からなるゲート電極8、および接合終端領域52内の第2導電層からなるゲート電極8は、図1、2に示すように、同時プロセスによって、ポリシリコンが充填されたトレンチ構造によって形成されていても良い。

【0024】

本発明の第1の実施の形態に係る半導体装置において、素子領域51内のp型ベース層4と、接合終端領域52内のp型ベース層4は、同時プロセスによって形成することができる。

【0025】

また、本発明の第1の実施の形態に係る半導体装置において、接合終端領域52内の終端トレンチ55は、図2に示すように、紙面上垂直にまた素子表面に素子領域51を囲みながらリング状に形成されている。さらに、接合終端領域52において、外周に拡散形成されたp型ベース層4はリング状に分断形成されている。

【0026】

図3は、本発明の第1の実施の形態に係る半導体装置の接合終端領域52の構造における各部のキャパシタのモデル図を示す。

【0027】

p型ベース層4がリング状に分断形成されている外周構造の素子に電圧印加した場合、各部位の電位は、図3に示すように、容量の分布定数回路としても解析することができる。

【0028】

本発明の第1の実施の形態に係る半導体装置として、図1に示すようなIGBT若しくはMISFETにおいて、所定の耐圧限界近くまでコレクタ電圧若しくはドレイン電圧を印加されている場合、図3内に模式的に示すように、n-型ベース層2(n-ドレイン領域)に空乏層が形成される。また、p型ベース層4と終端トレンチ55内のゲート電極8間には薄いゲート絶縁膜12が形成されているため、C3,C4,C1,C2間には、後述するように、(1)式の関係が成立することが望ましい。

【0029】

この場合、表面近傍の電位分布は、直列接続されたp型ベース層4と終端トレンチ55内のポリシリコン(ゲート電極8)間の容量結合によって決定される。

【0030】

この性質を利用すると外周の電位分布は任意に調整が可能となる。

【0031】

図3に示すように、p型ベース層4の厚さを示すベース深さはWBで定義され、トレンチ深さはWTで定義される。C1はp型ベース層4とn-型ベース層2間のキャパシタを表す。C2はトレンチ構造におけるゲート電極8とn-型ベース層2間のキャパシタを表す。C3,C4は、トレンチ構造におけるゲート電極8とp型ベース層4間のキャパシタを表す。上述した各部のキャパシタの間には、

C3,C4>>C1,C2 …(1)

の関係が成立していることが望ましい。

【0032】

また、図4は、本発明の第1の実施の形態に係る半導体装置において、トレンチ深さを浅く設定した場合の電位分布シミュレーション結果の模式図を示す。すなわち、図4においては、p型ベース層4の間隔を最適化せず、各トレンチ(35、55)の深さが、隣り合うトレンチ(35、55)の間隔(p型ベース層4の幅)よりも浅く設定しただけでも、接合終端領域52における電界緩和効果があり、高耐圧が得られる。図4において、各ラインは10V/本で示されている。

【0033】

さらに、図5は、本発明の第1の実施の形態に係る半導体装置において、各トレンチ(35、55)の深さを、隣り合うトレンチ(35、55)の間隔(p型ベース層4の幅)よりも浅く設定し、かつp型ベース層4の間隔を最適化した場合の電位分布シミュレーション結果の模式図を示す。すなわち、図5においては、高耐圧を得られるように外周各部のp型ベース層4の分断幅を最適化して設定したシミュレーション結果を示す。

【0034】

図5において、各ラインは20V/本で示されている。図5から明らかなように、各トレンチ(35、55)の深さを、隣り合うトレンチ(35、55)の間隔(p型ベース層4の幅)よりも浅く設定し、かつp型ベース層4の間隔を最適化した場合には、素子領域51近傍の電界緩和効果が顕著に得られ、かつ等電位面は、素子領域51から離隔した接合終端領域52まで均一に延伸している。

【0035】

図6は、耐圧相対値とトレンチ深さ/ベース深さ(WT/WB)の関係を表す。図6から明らかなように、トレンチ深さ/ベース深さ(WT/WB)の値は、例えば約0.9〜2.0の範囲において、所望の耐圧相対値が得られることがわかる。

【0036】

図7は、本発明の第1の実施の形態に係る半導体装置において、各トレンチ(35、55)の深さを、隣り合うトレンチ(35、55)の間隔(p型ベース層4の幅)よりも浅く設定し、かつp型ベース層4の間隔を最適化した場合における図3に対応する容量C1〜C4とコレクタ電圧VCE(V)との関係を示す。IGBT構造において、コレクタ電圧VCE=600Vを印加した場合、WT/WB=1.3において、

C1:C2:C3:C4=1:1.5:79:79 …(2)

の結果が得られている。すなわち、(1)式の関係が成立している。

【0037】

図5において示した、高耐圧を得られるように外周各部のp型ベース層4の分断幅を最適化して設定したシミュレーション結果を引き出すためにはp型ベース層4の拡散深さWBとトレンチ深さWTの比を、WB:WT=1:0.9〜1:2.0程度に抑える必要がある。

【0038】

終端トレンチ55の深さWTが深いと、終端トレンチ55の側面の面積が増加するためゲート電極8とn-型ベース層2間の容量(C2)が大きくなり、電位分布制御可能の前提となる(1)式の条件(C3,C4>>C1,C2)が満たされなくなるためである。

【0039】

また、WB:WT=1:0.9の場合、すなわちトレンチ深さWTがp型ベース層4の深さWBより浅い場合においても、コレクタ電圧VCE(V)の印加によって、p型ベース層4/n-型ベース層2間のpn接合からの空乏層の広がりにより、p型ベース層4が分断され、同等の効果が期待できる。ただし、本発明の第1の実施の形態に係る半導体装置の効果を十分に得るためには、WT/WB>1であることが望ましい。

【0040】

(外周構造)

本発明の第1の実施の形態に係る半導体装置において、外周構造は、以下の複数の構成を複数組み合わせて実施して、最適化し調整することができる。

【0041】

(a)接合終端領域52のp型ベース層4の分断寸法を適切に設定する。すなわち、素子領域51に近い場所はp型ベース層4の幅を相対的に広く設定し、素子領域51から離隔するに従い、p型ベース層4の幅を相対的に狭く設定して、大きな耐圧が確保することができる。

【0042】

(b)トレンチ側壁のゲート絶縁膜12の厚みが2種類以上使用可能な場合、例えば素子領域51に近いトレンチは薄いゲート絶縁膜12を用い、素子領域51から離隔するに従い、相対的に厚いゲート絶縁膜12を用いると、接合終端領域52において、素子領域51に近いほど容量C1は大きくなり、一方、素子領域51から離隔方向への位置変化に対して素子領域51に近い場所の電位変化は小さくなり電界は緩和される。

【0043】

素子領域51から離隔した場所の電位変化は大きく電界は高まるが、p型ベース層4とn-ベース層2との間の電位差は小さいため、素子領域51から離隔した場所における耐圧破壊は生じない。

【0044】

(c)図8は、本発明の第1の実施の形態に係る半導体装置の接合終端領域において、フィールドプレート電極構造の模式的断面構造を示す。すなわち、図8に示すように、少なくとも素子領域51近傍の接合終端領域52上に配置された層間絶縁膜18と、層間絶縁膜18上に延在して配置されたフィールドプレート電極20とを備えることを特徴とする。

【0045】

フィールドプレート電極20は、エミッタ領域(ソース領域)10に接続された第3の電極と等電位になされていてもよく、或いはまた、素子領域51内の第1導電層からなるゲート電極8と等電位になされていても良い。

【0046】

層間絶縁膜18は、例えばリン・ケイ酸ガラス(PSG:Phospho Silicate Glasses)膜、ホウ素・リン・ケイ酸ガラス(BPSG:Boro−Phospho Silicate Glasses)膜、ノンドープ・ケイ酸ガラス膜、窒化シリコン膜、ポリシリコン膜などを用いることができる。

【0047】

フィールドプレート電極20は、例えばアルミニウム電極で形成し、PSG膜などからなる層間絶縁膜18上にフィールドプレート電極20を作成することで素子領域51に近い場所の電位変化を小さくし、電界を緩和することができる。

【0048】

(d)図9は、本発明の第1の実施の形態に係る半導体装置の接合終端領域52において、第2導電層からなるゲート電極8と接続する取り出し電極22および当該取り出し電極22と接続されたフィールドプレート電極20からなる構造の模式的断面構造を示す。

【0049】

すなわち、接合終端領域52上に配置された層間絶縁膜18と、接合終端領域52上に層間絶縁膜18を介して配置され、第2導電層からなるゲート電極8と接続する取り出し電極22と、層間絶縁膜18上に延在して配置され、取り出し電極22と接続されたフィールドプレート電極20とを備えることを特徴とする。

【0050】

層間絶縁膜18は、例えばPSG膜、BPSG膜、ノンドープ・ケイ酸ガラス膜、窒化シリコン膜、ポリシリコン膜などを用いて形成することができる。フィールドプレート電極20は、例えばアルミニウム電極で形成し、PSG膜などからなる層間絶縁膜18上にフィールドプレート電極20を作成することで、フィールドプレート電極20の下側のp型ベース層4近傍の電位変化を小さくし、電界を緩和することができる。

【0051】

(e)図10は、本発明の第1の実施の形態に係る半導体装置の接合終端領域において、複数の第2導電層からなるゲート電極8と接続され、かつフローティング状態になされている取り出し電極22の構造の模式的断面構造を示す。

【0052】

すなわち、接合終端領域52上に配置された層間絶縁膜18と、接合終端領域52上に層間絶縁膜18を介して配置され、複数の第2導電層からなるゲート電極8と接続する取り出し電極22とを備え、当該取り出し電極22はフローティング状態になされていることを特徴とする。例えば、複数の第2導電層からなるゲート電極8は、フローティング状態になされているポリシリコン層で形成される。

【0053】

取り出し電極22は、図10に示すように、フローティング状態になされてポリシリコン層同士を共通接続することで形成することができる。

【0054】

(f)最外周部には空乏層の延びを止めるため、高不純物密度層を拡散形成しても良い。

【0055】

(g)最外周部の複数の終端トレンチ55を形成するゲート電極8を、n-ベース層2若しくはドレイン電極(コレクタ電極)と接続した等電位ポテンシャルリング(EQR:EQui-potential Ring)として使用する構成を備えていてもよい。

【0056】

(h)素子領域51と接合終端領域52の境界の素子領域51側にもトレンチを数列作成して、電界緩和を図る構成を備えていてもよい。

【0057】

(i)あるいはまた、接合終端領域52において、終端トレンチ55の幅を場所によって変えることによって、電界緩和を図る構成を備えていてもよい。

【0058】

本発明の第1の実施の形態に係る半導体装置によれば、接合終端領域における電界を緩和し、高耐圧化することができる。

【0059】

[その他の実施の形態]

上記のように、本発明は第1の実施の形態によって記載したが、この開示の一部をなす論述および図面はこの発明を限定するものでないと理解すべきである。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0060】

本発明は第1の実施の形態に係る半導体装置としては、トレンチ構造を有するIGBT、MISFETなどの例を開示したが、これらに限定されるものではなく、トレンチ構造を有するIEGT、SIT、SIサイリスタなどのデバイス構造においても適用可能である。

【0061】

さらに、半導体材料としては、シリコンに限定されるものではなく、SiC、GaN系、GaAs系、InP系などの化合物半導体、或いはヘテロ接合のベース構造、或いはHEMT構造のチャネル構造を適用することもできる。

【0062】

このように、本発明はここでは記載していない様々な実施の形態などを含むことは勿論である。したがって、本発明の技術的範囲は上記の説明から妥当な特許請求の範囲に係る発明特定事項によってのみ定められるものである。

【符号の説明】

【0063】

2…n-型ベース層(第1半導体領域)

3…n型バッファ層

4、34…p型ベース層(第2半導体領域)

5a…一方の主面

5b…他方の主面

8…ゲート電極(第1導電層、第2導電層)

10…n型エミッタ(ソース)領域(第3半導体領域)

12…ゲート絶縁膜

14、18…層間絶縁膜

16…エミッタ(ソース)電極

20…フィールドプレート電極

22…取り出し電極

31…n型ベース層

35…トレンチ

51…素子領域

52…接合終端領域

55…終端トレンチ

【特許請求の範囲】

【請求項1】

第1導電型の不純物を有する第1半導体領域と、

前記第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域と、

を有する半導体基体には、

コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、

上方から見て前記半導体基体の最外周部に形成された、前記第2半導体領域の上面から前記第1半導体領域に達する終端トレンチと、

前記終端トレンチの側壁および底面に形成された絶縁膜と、

前記絶縁膜を介して前記溝の内側に埋め込まれた電極と

を有し、

前記電極が、前記第1半導体領域又は前記コレクタ電極若しくは前記ドレイン電極と接続された等電位リングであることを特徴とする半導体装置。

【請求項2】

前記最外周部に拡散により形成された高不純物密度層を有することを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記素子領域を取り囲むように形成された終端領域と、

前記終端領域上に配置された層間絶縁膜と、

前記終端領域上に前記層間絶縁膜を介して配置されたフィールドプレートと

を更に有し、前記フィールドプレートが前記素子領域側に延伸していることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記素子領域を取り囲むように形成された終端領域と、

前記終端領域上に配置された層間絶縁膜と、

前記終端領域上に前記層間絶縁膜を介して配置され、前記層間絶縁膜に設けられた開口部において複数の前記電極と接続する取り出し電極を更に有することを特徴とする請求項1又は2に記載の半導体装置。

【請求項1】

第1導電型の不純物を有する第1半導体領域と、

前記第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域と、

を有する半導体基体には、

コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、

上方から見て前記半導体基体の最外周部に形成された、前記第2半導体領域の上面から前記第1半導体領域に達する終端トレンチと、

前記終端トレンチの側壁および底面に形成された絶縁膜と、

前記絶縁膜を介して前記溝の内側に埋め込まれた電極と

を有し、

前記電極が、前記第1半導体領域又は前記コレクタ電極若しくは前記ドレイン電極と接続された等電位リングであることを特徴とする半導体装置。

【請求項2】

前記最外周部に拡散により形成された高不純物密度層を有することを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記素子領域を取り囲むように形成された終端領域と、

前記終端領域上に配置された層間絶縁膜と、

前記終端領域上に前記層間絶縁膜を介して配置されたフィールドプレートと

を更に有し、前記フィールドプレートが前記素子領域側に延伸していることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記素子領域を取り囲むように形成された終端領域と、

前記終端領域上に配置された層間絶縁膜と、

前記終端領域上に前記層間絶縁膜を介して配置され、前記層間絶縁膜に設けられた開口部において複数の前記電極と接続する取り出し電極を更に有することを特徴とする請求項1又は2に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−55347(P2013−55347A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2012−246283(P2012−246283)

【出願日】平成24年11月8日(2012.11.8)

【分割の表示】特願2007−192161(P2007−192161)の分割

【原出願日】平成19年7月24日(2007.7.24)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成24年11月8日(2012.11.8)

【分割の表示】特願2007−192161(P2007−192161)の分割

【原出願日】平成19年7月24日(2007.7.24)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

[ Back to top ]