半導体装置

【課題】消費電力の低減と、製造コストの低減とを両立する発振回路を提供する。

【解決手段】本発明の半導体装置によれば、直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタを用いて、発振回路部を駆動させる電圧を生成する。このとき、複数のMOSトランジスタで生成される電圧の値は、電源電圧と、各MOSトランジスタのスレッショルド電圧の比率とに基づいて得られる。したがって、各MOSトランジスタのスレッショルド電圧を小さく抑えることが出来て、各MOSトランジスタの面積を節約することが出来て、発振回路部の消費電力を削減することが出来る。

【解決手段】本発明の半導体装置によれば、直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタを用いて、発振回路部を駆動させる電圧を生成する。このとき、複数のMOSトランジスタで生成される電圧の値は、電源電圧と、各MOSトランジスタのスレッショルド電圧の比率とに基づいて得られる。したがって、各MOSトランジスタのスレッショルド電圧を小さく抑えることが出来て、各MOSトランジスタの面積を節約することが出来て、発振回路部の消費電力を削減することが出来る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に係り、特に、発振回路を有する半導体装置に係る。

【背景技術】

【0002】

モバイル情報端末や、DSC(Digital Still Camera:デジタルカメラ)などにおいて、サイズの小型化が進んでいる。端末の小型化に伴い、バッテリの小型化も進んでおり、また、容量の小さいボタン電池を使用するケースも増加している。このため、LSI(Large Scale Integration:大規模集積回路)内部で常時動作する発振回路でも、低消費電力化の要求が高まっている。

【0003】

このような発振回路に電力を供給する方法として、定電圧回路を用いて、電源電圧から一定の幅で電圧を降下させて、発振回路に供給する従来技術が知られている。しかし、このような従来技術では、降下される電圧の幅が大きければ大きいほど、抵抗値のより高い抵抗素子が必要となる。そして、抵抗素子の抵抗値が高ければ高いほど、LSIの中でより広い面積を占有する。

【0004】

そこで、LSI内部の占有面積の節約と、低消費電力化との両立が求められている。

【0005】

上記に関連して、特許文献1(特開2005−159786号公報)には、発振回路に係る記載が開示されている。この発振回路は、消費電流の削減を目的として掲げている。この発振回路は、発振ゲートへの供給電圧を抑制する機能部を具備している。この発振回路は、ダイオード接続されたトランジスタのスレショルド電圧を用いて電圧を抑制する動作を行う。

【0006】

図1は、特許文献1に記載の発振回路の構成を示す回路図である。図1の発振回路の構成要素について説明する。この発振回路は、発振ゲート回路部120と、第1および第2の振幅抑制回路151および152と、振幅増幅回路109と、入力側コンデンサC101と、出力側コンデンサC102と、帰還抵抗103と、発振子104とを具備している。発振ゲート回路部120は、PMOSトランジスタ101と、NMOSトランジスタ102とを具備している。第1の振幅抑制回路151は、PMOSトランジスタ107を具備している。第1の振幅抑制回路151は、ダイオード130や、他のPMOSトランジスタ132や、第1の電流源134などをさらに具備しても良いが、ここではその詳細を省略する。第2の振幅抑制回路152は、NMOSトランジスタ108を具備している。第2の信服抑制回路152は、第2のダイオード132や、他のNMOSトランジスタ133や、第2の電流源135などをさらに具備しても良いが、ここではその詳細を省略する。振幅増幅回路109は、PMOSトランジスタ111と、NMOSトランジスタ112とを具備している。

【0007】

図1の発振回路の構成要素の接続関係について説明する。PMOSトランジスタ107のソースは、電源VCCに接続されている。PMOSトランジスタ107におけるゲートおよびドレインは、PMOSトランジスタ101のソースに共通接続されている。PMOSトランジスタ101のゲートは、NMOSトランジスタ102のゲートと、帰還抵抗103における一方の端部と、発振子104における一方の端部と、入力側コンデンサC101における一方の端部とに共通接続されている。PMOSトランジスタ101のドレインは、NMOSトランジスタ102のドレインと、帰還抵抗103における他方の端部と、発振子104における他方の端部と、出力側コンデンサC102における他方の端部と、PMOSトランジスタ111のゲートと、NMOSトランジスタ112のゲートとに共通接続されている。NMOSトランジスタ102のソースは、NMOSトランジスタ108におけるゲートおよびドレインに共通接続されている。NMOSトランジスタ108のソースは、接地されている。入力側コンデンサC101における他方の端部は、接地されている。出力側コンデンサC102における他方の端部は、接地されている。PMOSトランジスタ111のソースは、電源VCCに接続されている。PMOSトランジスタ111のドレインは、NMOSトランジスタ112のドレインと、出力部CKOUTとに共通接続されている。NMOSトランジスタ112のソースは、接地されている。

【0008】

図1の発振回路の動作について説明する。第1の振幅抑制回路151において、PMOSトランジスタ107は、ゲートおよびドレインが短絡されており、すなわちいわゆる「ダイオード接続」がされている。したがって、PMOSトランジスタ107のドレインにおける電圧の値は、電源VCCの電圧からPMOSトランジスタ107のスレッショルド電圧だけ下降した値に等しい。以下、PMOSトランジスタ107のスレッショルド電圧をVt107と記す。

【0009】

同様に、第2の振幅抑制回路152において、NMOSトランジスタ108もダイオード接続されている。したがって、NMOSトランジスタ108のドレインにおける電圧の値は、グランドの電圧からNMOSトランジスタ108のスレッショルド電圧だけ上昇した値に等しい。以下、NMOSトランジスタ108のスレッショルド電圧をVt108と記す。

【0010】

発振ゲート回路部120において、PMOSトランジスタ101と、NMOSトランジスタ102とは、第1の振幅抑制回路151におけるPMOSトランジスタ107のドレインと、第2の振幅抑制回路152におけるNMOSトランジスタ108のドレインとの間に、直列に接続されている。したがって、発振ゲート回路部120が生成する発振信号の電圧は、電源電圧VCCからスレッショルド電圧Vt107だけ下降した電圧と、グランド電圧からスレッショルド電圧Vt108だけ上昇した電圧との間で振幅する。

【0011】

ここで、発振ゲート回路部120の出力信号は、帰還抵抗103および振動子104を介して入力側に帰還することで発振する。なお、発振ゲート回路部120の発振信号が生成される際、入力側コンデンサC101と、出力側コンデンサC102とにおいて充放電が発生する。この充放電に伴う電流は、発振回路としての消費電力につながる。特許文献1では、発振信号の振幅を小さくすることで、発振回路の消費電力を低減している。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2005−159786号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

特許文献1の発振回路には、その動作が、トランジスタの製造時に発生するプロセスばらつきに影響されてしまうという問題がある。プロセスばらつきが発生する方向には、大きく分けて2種類の場合がある。

【0014】

まず、第1の場合では、PMOSトランジスタおよびNMOSトランジスタのスレッショルド電圧が設計値よりも高くなる方向にプロセスばらつきが発生する。このとき、発振ゲート回路部120が生成する発振信号の振幅は、設計値よりも大きくなる。また、発振ゲート回路部120の駆動能力は設計値よりも小さくなる。したがって、第1の場合では、発振ゲート回路部120において、PMOSトランジスタ101のソースと、NMOSトランジスタ102のソースとの間の電圧は、より大きいことが望ましい。

【0015】

次に、第2の場合では、PMOSトランジスタおよびNMOSトランジスタのスレッショルド電圧が設計値よりも低くなる方向にプロセスばらつきが発生する。このとき、発振ゲート回路部120が生成する発振信号の振幅は、設計値よりも小さくなる。また、発振ゲート回路部120の駆動能力は設計値よりも大きくなる。したがって、第2の場合では、発振ゲート回路部120において、PMOSトランジスタ101のソースと、NMOSトランジスタ102のソースとの間の電圧は、より小さいことが望ましい。

【0016】

しかし、トランジスタの製造時に、プロセスばらつきがどちらの方向に発生するのかは、予測不可能である。そこで、プロセスばらつきがいずれの方向に発生しても発振ゲート回路部120が確実に動作する電圧範囲が確保できるように、設計時の段階で十分なマージンを用意しておく必要がある。その結果、発振ゲート回路部120において、PMOSトランジスタ101のソースと、NMOSトランジスタ102のソースとの間に供給される電圧範囲は、消費電力の低減に寄与しないマージンを含んでしまう。

【0017】

また、ダイオード接続されたMOSトランジスタにおけるスレッショルド電圧は、一般的に0.6V〜0.7V程度である。より大きいスレッショルド電圧を得るためには、MOSトランジスタのゲート長Lをより大きくして、ドレインおよびソースの間を流れる電流IDSを小さくする必要がある。ただし、電流IDSは、ゲート長Lの逆数に比例する。図5Aは、一般的なMOSトランジスタにおける、ゲート長Lと、ドレインおよびソースの間を流れる電流IDSとの関係を示すグラフである。特許文献1の発振回路の場合、十分に小さい電流IDSを得るためには、ゲート長Lを数十μm(マイクロメートル)まで大きくする必要があると考えられる。このようなゲート長Lを有するMOSトランジスタを用いることは、発振回路の面積が大きくなる原因となる。このように、特許文献1の発振回路では、消費電力の低減と、製造コストの低減とを両立することが出来ない。

【課題を解決するための手段】

【0018】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0019】

半導体装置は、第1の電源部(VDD)と、第2の電源部(GND)と、振幅制御回路部(10)と、発振回路部(20、3、4、C1、C2)とを具備する。ここで、第1の電源部(VDD)は、第1の電源電圧を供給する。第2の電源部(GND)は、第2の電源電圧を供給する。振幅制御回路部(10)は、第1および第2の電源電圧(VDD、GND)を入力して第1および第2の供給電圧(V11、V12)を生成する。発振回路部(20、3、4、C1、C2)は、第1および第2の入力部(11、12)から第1および第2の供給電圧(V11、V12)をそれぞれ入力して発振する。振幅制御回路部(10)は、複数のMOSトランジスタ(5〜8)と、第1の出力部(11)と、第2の出力部(12)とを具備する。ここで、複数のMOSトランジスタ(5〜8)は、第1および第2の電源部(VDD、GND)の間に直列に接続されて、かつ、それぞれがダイオード接続されている。第1の出力部(11)は、複数のMOSトランジスタ(5〜8)のドレインまたはソースに接続されて、第1の供給電圧(V11)を出力する。第2の出力部(12)は、複数のMOSトランジスタ(5〜8)の他のドレインまたは他のソースに接続されて、第2の供給電圧(V12)を出力する。

【発明の効果】

【0020】

本発明の半導体装置によれば、直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタを用いて、発振回路部を駆動させる電圧を生成する。このとき、複数のMOSトランジスタで生成される電圧の値は、電源電圧と、各MOSトランジスタのスレッショルド電圧の比率とに基づいて得られる。したがって、各MOSトランジスタのスレッショルド電圧を小さく抑えることが出来て、各MOSトランジスタの面積を節約することが出来て、発振回路部の消費電力を削減することが出来る。

【図面の簡単な説明】

【0021】

【図1】図1は、特許文献1に記載の発振回路の構成を示す回路図である。

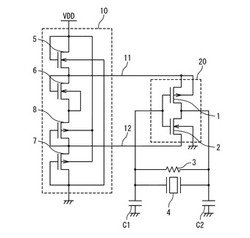

【図2】図2は、本発明の第1の実施形態による半導体装置の構成を示す回路図である。

【図3A】図3Aは、従来技術による半導体装置におけるMOSトランジスタ群のレイアウト図の一例である。

【図3B】図3Bは、本発明の第1の実施形態による半導体装置におけるMOSトランジスタ群のレイアウト図の一例である。

【図4A】図4Aは、従来技術による半導体装置の全体的なレイアウト図の一例である。

【図4B】図4Bは、本発明の第1の実施形態による半導体装置の全体的なレイアウト図の一例である。

【図5】図5は、NMOSトランジスタの長さLと、ドレイン・ソース間電流IDSとの関係を概略的に示すグラフである。

【図6】図6は、本発明の第2の実施形態による半導体装置の構成を示す回路図である。

【図7】図7は、本発明の第3の実施形態による半導体装置の構成を示す回路図である。

【図8】図8は、本発明の第4の実施形態による半導体装置の構成を示す回路図である。

【発明を実施するための形態】

【0022】

添付図面を参照して、本発明による半導体装置を実施するための形態を以下に説明する。

【0023】

(第1の実施形態)

図2は、本発明の第1の実施形態による半導体装置の構成を示す回路図である。図2に示した半導体装置の構成要素について説明する。図2に示した半導体装置は、電源VDDと、グランドGNDと、振幅制御回路部10と、発振ゲート回路部20と、帰還抵抗3と、振動子4と、入力側コンデンサC1と、出力側コンデンサC2とを具備している。振幅制御回路部10は、第1、第2のNMOSトランジスタ5、6と、第1、第2のPMOSトランジスタ7、8とを具備している。発振ゲート回路部20は、PMOSトランジスタ1と、NMOSトランジスタ2とを具備している。ここで、発振ゲート回路部20と、帰還抵抗3と、振動子4と、入力側コンデンサC1と、出力側コンデンサC2とをまとめて発振回路部と呼んでも良い。

【0024】

図2に示した半導体装置の構成要素の接続関係について説明する。電源VDDは、第1のNMOSトランジスタ5におけるドレインおよびゲートと、第1のPMOSトランジスタ7のバックゲートとに共通接続されている。ノード11は、第1のNMOSトランジスタ5のソースと、第2のNMOSトランジスタ6におけるソースおよびゲートと、PMOSトランジスタ1におけるソースおよびバックゲートとに共通接続されている。ノード12は、第1のPMOSトランジスタ7におけるソースと、第2のPMOSトランジスタ8におけるドレインおよびゲートと、NMOSトランジスタ2のソースとに共通接続されている。第2のNMOSトランジスタ6のソースは、第2のNMOSトランジスタ8におけるソースおよびバックゲートに共通接続されている。第1のNMOSトランジスタ5のバックゲートと、第2のNMOSトランジスタ6のバックゲートと、第1のPMOSトランジスタ7のゲートと、NMOSトランジスタ2のバックゲートと、入力側コンデンサC1における一方の端部と、出力側コンデンサC2における一方の端部とは、接地されている。入力側コンデンサC1における他方の端部は、PMOSトランジスタ1のゲートと、NMOSトランジスタ2のゲートと、帰還抵抗3における一方の端部と、振動子4における一方の端部とに共通接続されている。出力側コンデンサC2における他方の端部は、PMOSトランジスタ1のドレインと、NMOSトランジスタ2のドレインと、帰還抵抗3における他方の端部と、振動子4における他方の端部とに共通接続されている。

【0025】

図2に示した半導体装置の動作について説明する。まず、発振ゲート回路部20、入力側コンデンサC1、出力側コンデンサC2、帰還抵抗3および振動子4の動作について、前述した従来技術の場合と同様であるが、再度説明する。

【0026】

電源VDDは、第1の電源電圧VDDを供給する第1の電源部として動作する。同様に、グランドGNDは、第2の電源電圧として基準電圧を供給する第2の電源部として動作する。発振ゲート回路部20において、PMOSトランジスタ1と、NMOSトランジスタ2とは、ノード11と、ノード12との間に、直列に接続されている。したがって、発振ゲート回路部20が生成する発振信号の電圧は、ノード11における電圧と、ノード12における電圧との間で振幅する。ここで、ノード11と、ノード12とは、発振ゲート回路部20における第1、第2の入力部として機能する。また、発振ゲート回路部20の出力信号は、帰還抵抗3および振動子4を介して入力側に帰還することで発振する。なお、発振ゲート回路部20の発振信号が生成される際、入力側コンデンサC1と、出力側コンデンサC2とにおいて充放電が発生する。この充放電に伴う電流は、発振回路としての消費電力につながる。

【0027】

次に、ダイオード接続されたMOSトランジスタの動作について説明する。MOSトランジスタにおいて、ゲートがドレインに接続されていることを、ダイオード接続されていると言う。ダイオード接続されたMOSトランジスタでは、ゲート・ソース間電圧VGSがそのままスレッショルド電圧Vtとなる。図2の半導体装置では、第1、第2のNMOSトランジスタ5、6と、第1のPMOSトランジスタ7とがダイオード接続されている。したがって、MOSトランジスタ5〜7のスレッショルド電圧Vt5〜Vt7は、MOSトランジスタ5〜7のゲート・ソース間電圧VGS5〜VGS7に、それぞれ等しい。

【0028】

MOSトランジスタは、バックゲート・ソース間の電圧VBSの絶対値がゼロ以上である場合に、ソースからドレインへの電流が流れにくくなる。この場合、MOSトランジスタのスレッショルド電圧Vtは、バックゲート・ソース間電圧VBSがゼロに等しい場合よりも高くなる。図2に示した半導体装置において、第2のPMOSトランジスタ8は、ダイオード接続されているが、バックゲートがソースに接続されているので、バックゲート・ソース間電圧VBS8がゼロに等しい。そのため、第2のPMOSトランジスタ8のスレッショルド電圧Vt8は、他のMOSトランジスタ5〜7のスレッショルド電圧Vt5〜Vt7よりも低い。

【0029】

次に、図2に示した半導体装置の、発振が開始するまでの動作を説明する。まず、初期状態において、全てのトランジスタがオフ状態になっている。第1のNMOSトランジスタ5は、ゲートが電源VDDに接続されているため、電源投入後にドレイン・ソース間電流(以下「IDS」と記す)が発生する。第2のNMOSトランジスタ6は、ドレインおよびゲートに電圧が印加されて、IDSが発生する。第2のPMOSトランジスタ8は、ソースに電圧が印加される。第1のNMOSトランジスタ7は、ソースに電圧が印加される。ここで、ゲートがドレインに接続されており、ソース電圧に対してゲート電圧の方が低いため、IDSが発生する。振幅制御回路部10に含まれるMOSトランジスタ5〜8は、その全てがダイオード接続されているので、本来ならそれぞれのスレッショルド電圧Vt5〜Vt8で動作するはずである。しかし、これら4つのMOSトランジスタ5〜8は、直列に接続されていて、かつ、その両端が電源電圧VDDで印加されている。したがって、振幅制御回路10に含まれるMOSトランジスタ5〜8のドレイン・ソース間電圧VDS5〜VDS8は、電源電圧VDDと、これらのMOSトランジスタ5〜8のそれぞれにおけるスレッショルド電圧Vt5〜Vt8の比率とで決定する。具体的には、MOSトランジスタ5〜8のそれぞれにおける実際のドレイン・ソース間電圧VDS5〜VDS8は、本来のスレッショルド電圧Vt5〜Vt8の比率に応じて、次の式のように求められる。

VDS5=VDD×Vt5/(Vt5+Vt6+Vt7+Vt8)

VDS6=VDD×Vt6/(Vt5+Vt6+Vt7+Vt8)

VDS7=VDD×Vt7/(Vt5+Vt6+Vt7+Vt8)

VDS8=VDD×Vt8/(Vt5+Vt6+Vt7+Vt8)

【0030】

上記に示した、MOSトランジスタ5〜8のドレイン・ソース間電圧VDS5〜VDS8から、ノード11に供給される電圧V11と、ノード12に供給される電圧V12とは、次の式のように決定される。

V11=VDD×(Vt6+Vt7+Vt8)/(Vt5+Vt6+Vt7+Vt8)

V12=VDS7=VDD×Vt7/(Vt5+Vt6+Vt7+Vt8)

【0031】

上記に示した、ノード11、12の電圧V11、V12の差を駆動電圧ΔVとおくと、次の式のように求められる。

ΔV=V11−V12=VDD×(Vt6+Vt8)/(Vt5+Vt6+Vt7+Vt8)

発振ゲート回路部20に含まれる2つのMOSトランジスタ1、2が上記の駆動電圧ΔVを印加されることによって、発振ゲート回路部20は発振動作を開始する。

【0032】

なお、ノード11と、ノード12とは、振幅制御回路部10が第1、第2の供給電圧V11、V12を出力する第1、第2の出力部としても機能する。

【0033】

ここでもし、第2のPMOSトランジスタ8のバックゲートが電源VDDに接続されていたら、トランジスタ8のスレッショルド電圧Vt8は、図2のように接続されていない場合よりも大きくなる。その結果、振幅制御回路部10に含まれる4つのトランジスタ5〜8におけるスレッショルド電圧Vt5〜Vt8の比率が変わる。具体的には、ノード11の電圧V11がより高くなり、ノード12の電圧V12はより低くなり、その差である駆動電圧ΔVは高くなる。

【0034】

言い換えれば、図2のように、第2のPMOSトランジスタ8のバックゲートをそのソースに接続することで、本実施形態による半導体装置では、駆動電圧ΔVをさらに低くすることが出来る。

【0035】

発振ゲート回路部20への電源供給は、電源電圧VDDから下げたノード11の電圧V11と、グランドGNDの基準電圧から上げたノード12の電圧V12とで行われる。そのため、発振ゲート回路部20の出力波形は、その発振が定常状態にまで成長しきった後の最大振幅が、ノード11の電圧V11と、ノード12の電圧V12との間で小さく収まる。したがって、入力側コンデンサC1と、出力側コンデンサC2に充放電される電流もそれだけ小さくなる。結果的に、発振器全体としての消費電力を削減することが可能となる。

【0036】

ここで、半導体プロセスによる製造ばらつきの問題について考える。実際に製造された半導体装置では、製品ごとにトランジスタのスレッショルド電圧Vtがばらつくのが一般的である。このばらつきが、従来技術の場合には発振ゲート回路部の供給される電圧に直接的に影響するが、本発明によればこの影響が小さくなることを説明する。

【0037】

図1に示した従来技術の場合では、発振ゲート回路部120に供給される電圧は、PMOSトランジスタ107から供給されるハイ側の電圧と、NMOSトランジスタ108から供給されるロー側の電圧との差に等しい。ここで、PMOSトランジスタ107は、ダイオード接続されており、かつ、ソースが電源VCCに接続されている。したがって、ハイ側の電圧は、電源電圧VCCから、PMOSトランジスタ107のスレッショルド電圧Vt107だけ下げた電圧に等しい。同様に、NMOSトランジスタ108は、ダイオード接続されており、かつ、ソースが接地されている。したがって、ロー側の電圧は、グランドの基準電圧から、NMOSトランジスタ108のスレッショルド電圧Vt108だけ上げた電圧に等しい。このような構成では、発振ゲート回路部120に供給される電圧が、製造ばらつきの影響を直接的に受けてしまい、すなわち製造ばらつきと同じ比率でばらついてしまう。

【0038】

しかし、本実施形態による半導体装置では、直列に接続されたMOSトランジスタ5〜8のスレッショルド電圧Vt5〜Vt8に製造ばらつきが生じても、その比率は変わらない場合がある。これは、同じ半導体基板上の、比較的近い場所に形成される複数のトランジスタにおいて、発生する製造ばらつきは同様であると期待されるからである。この場合は、発振ゲート回路部20に供給される駆動電圧ΔVは、スレッショルド電圧の比率によって決定されるので、製造ばらつきの影響を受けずに済む。

【0039】

その一方で、PMOSトランジスタと、NMOSトランジスタとでは、製造ばらつきが逆方向に働く場合もある。この場合は、直列に接続されたMOSトランジスタ5〜8のそれぞれにおけるスレッショルド電圧Vt5〜Vt8の比率が変わってしまう。したがって、この場合は、発振ゲート回路部20に供給される駆動電圧ΔVが製造ばらつきの影響を受けてしまう。

【0040】

ただし、この場合は、発振ゲート回路部20に含まれるPMOSトランジスタ1と、NMOSトランジスタ2も、逆方向に働く製造ばらつきの影響を、MOSトランジスタ5〜8と同様に受けているはずである。すなわち、発振ゲート回路部20が動作する上で実際に必要な駆動電圧も、製造ばらつきの影響を、振幅制御回路部10から供給される駆動電圧ΔVと同様に受けているはずである。したがって、本実施形態による半導体装置では、製造ばらつきを考慮するにあたって、過剰なマージンを必要としない。その結果、従来技術では必要とされたマージンに纏わる余分な消費電力を、本発明では低減することが可能となっている。

【0041】

なお、直列に接続されているMOSトランジスタ5〜8について、チャネル極性を入れ替えたり、接続する順番を入れ替えたりしても、上記と同様の動作および効果が得られることは当然である。

【0042】

上記に説明したように、本実施形態による半導体装置では、発振ゲート回路部20に供給される駆動電圧ΔVを、複数のMOSトランジスタ5〜8のスレッショルド電圧Vt5〜Vt8の比率として決定している。したがって、これらのMOSトランジスタ5〜8の実効的なスレッショルド電圧Vt5〜Vt8を従来技術のように大きくする必要が無い。その結果、半導体装置全体としてのレイアウト面積を節約することが可能となっている。

【0043】

図3Aは、従来技術による半導体装置におけるMOSトランジスタ群のレイアウト図の一例である。図3Bは、本発明の第1の実施形態による半導体装置におけるMOSトランジスタ群のレイアウト図の一例である。図3A、図3Bを参照して、本発明による半導体装置ではMOSトランジスタのレイアウト面積を大幅に節約できることを説明する。

【0044】

図3Aには、PMOSトランジスタ42と、NMOSトランジスタ43とが描かれている。図3Bには、NMOSトランジスタ61、62と、PMOSトランジスタ63、64とが描かれている。図3AのPMOSトランジスタ42は、図1のPMOSトランジスタ151に対応する。図3AのNMOSトランジスタ43は、図1のNMOSトランジスタ152に対応する。図3BのNMOSトランジスタ61は、図2のNMOSトランジスタ5に対応する。図3BのNMOSトランジスタ62は、図2のNMOSトランジスタ6に対応する。図3BのPMOSトランジスタ63は、図2のNMOSトランジスタ7に対応する。図3BのPMOSトランジスタ64は、図2のNMOSトランジスタ8に対応する。ここで、図3Aおよび図3Bに描かれた全てのMOSトランジスタの縮尺は同じである。

【0045】

図1に示した従来技術では、十分に大きなスレッショルド電圧Vtを確保するために、MOSトランジスタのレイアウト面積を、図3Aに示したように大きくする必要があった。しかし、図2に示した本発明の場合は、スレッショルド電圧Vtの比率が重要なので、MOSトランジスタのレイアウト面積を、図3Bに示したように最小限に抑えることが可能である。

【0046】

図4Aは、従来技術による半導体装置の全体的なレイアウト図の一例である。図4Bは、本発明の第1の実施形態による半導体装置の全体的なレイアウト図の一例である。図4A、図4Bを参照して、本発明による半導体装置では、全体的なレイアウト面積を大幅に節約できることを説明する。

【0047】

図4Aには、半導体装置71のレイアウトが描かれている。半導体装置71は、PMOSトランジスタ42と、NMOSトランジスタ43と、PMOSトランジスタ101と、NMOSトランジスタ102と、帰還抵抗103と、回路部73とを含んでいる。図4AのPMOSトランジスタ42は、図1のPMOSトランジスタ151に対応する。図4AのNMOSトランジスタ43は、図1のNMOSトランジスタ152に対応する。図4AのPMOSトランジスタ101は、図1のPMOSトランジスタ101に対応する。図4AのNMOSトランジスタ102は、図1のNMOSトランジスタ102に対応する。図4Aの帰還抵抗103は、図1の帰還抵抗103に対応する。図4Aの回路部73は、図1のその他の構成要素、例えば入力側コンデンサC101、出力側コンデンサC102、振動子104、などに対応するものとする。

【0048】

図4Bには、半導体装置72のレイアウトが描かれている。半導体装置72は、PMOSトランジスタ61、62と、NMOSトランジスタ63、64と、PMOSトランジスタ1と、NMOSトランジスタ2と、帰還抵抗3と、回路部74とを含んでいる。図4BのPMOSトランジスタ61、62は、図2のPMOSトランジスタ7、8に対応する。図4BのNMOSトランジスタ63、64は、図2のNMOSトランジスタ5、6に対応する。図4BのPMOSトランジスタ1は、図2のPMOSトランジスタ1に対応する。図4BのNMOSトランジスタ2は、図2のNMOSトランジスタ2に対応する。図4Bの帰還抵抗3は、図2の帰還抵抗3に対応する。図4Bの回路部74は、図2のその他の構成要素、例えば入力側コンデンサC1、出力側コンデンサC2、振動子4、などに対応するものとする。

【0049】

ここで、図4A、図4Bのレイアウトの縮尺は同じである。それでも、図4Aの半導体装置71の全体的なレイアウト面積が、図4Bの半導体装置72の全体的なレイアウト面積の2倍近く大きくなってしまう最大の原因は、NMOSトランジスタ43の長さにあると言える。NMOSトランジスタ43の長さが、半導体装置71の大半を占めるデッドスペースが発生する原因となっているからである。

【0050】

なお、本実施形態と同等の性能を有する半導体装置を、図1に示した従来技術で構成するなら、NMOSトランジスタ43の長さLとして数十μm程度を確保する必要がある。この長さLは、十分なスレッショルド電圧Vtを確保し、かつ、ドレイン・ソース間電流IDSを低く抑えるために必要となる。

【0051】

図5は、NMOSトランジスタの長さLと、ドレイン・ソース間電流IDSとの関係を概略的に示すグラフである。図5において、横軸はNMOSトランジスタの長さLを示し、縦軸はドレイン・ソース間電流IDSを示す。図5のグラフから、ドレイン・ソース間電流IDSを低く抑えるためには、NMOSトランジスタの長さLを大きく確保する必要があることが読み取れる。

【0052】

上記に説明したように、本発明の第1の実施形態による半導体装置は、レイアウト面積の縮小に伴う製造コストの節約と、消費電力の節約とによる、2つの面でのコスト削減を可能とする。

【0053】

(第2の実施形態)

図6は、本発明の第2の実施形態による半導体装置の構成を示す回路図である。本実施形態による半導体装置は、図2に示した本発明の第1の実施形態による半導体装置に、以下の変更を加えたものに等しい。すなわち、図2の半導体装置では、第2のPMOSトランジスタ8のバックゲートが、第2のPMOSトランジスタ8のソースと、第2のNMOSトランジスタ6のソースとに共通接続されている。また、図2の半導体装置では、第2のNMOSトランジスタ6のバックゲートは、接地されている。しかし、本実施形態による半導体装置では、第2のNMOSトランジスタ6のバックゲートが、第2のPMOSトランジスタ8のソースと、第2のNMOSトランジスタ6のソースとに共通接続されている。また、本実施形態による半導体装置では、第2のPMOSトランジスタ8のバックゲートが接地されている。

【0054】

本実施形態による半導体装置のその他の構成については、図2に示した本発明の第1の実施形態の場合と同様であるので、さらなる詳細な説明を省略する。

【0055】

本実施形態による半導体装置の動作について説明する。本実施形態による半導体装置では、第2のNMOSトランジスタ6のスレッショルド電圧Vt6が、MOSトランジスタ5、7、8のスレッショルド電圧Vt5、Vt7、Vt8よりも低くなる。しかし、結果として、発振ゲート回路部20に供給される駆動電圧ΔVは、図2に示した本発明の第1の実施形態の場合と同じとなる。

【0056】

本実施形態による半導体装置のその他の動作および効果については、図2に示した本発明の第1の実施形態の場合と同様であるので、さらなる詳細な説明を省略する。

【0057】

(第3の実施形態)

図7は、本発明の第3の実施形態による半導体装置の構成を示す回路図である。図7の半導体装置は、図2に示した本発明の第1の実施形態による半導体装置に、以下の変更を加えたものに等しい。すなわち、制御回路部36と、セレクタ回路部40とを追加する。

【0058】

回路構成(トランジスタサイズを含む)の決まっている発振回路の増幅率は、発振回路を流れる電流(あるいは発振回路にかかる電圧)によって変化する。一般的に、発振回路は、発振開始時に必要な増幅率が、発振の持続に必要な増幅率よりも高い。言い換えれば、発振ゲート回路部20を流れる電流(あるいは発振ゲート回路部20にかかる電圧)が何らかの原因により低すぎた場合に、発振ゲート回路部20の増幅率が低くなり発振が開始しない恐れがある。本実施形態では、制御回路部36と、セレクタ回路部40とを追加することでこの問題を解決出来ることを説明する。

【0059】

図7に示した半導体装置の構成要素について説明する。セレクタ回路部40は、PMOSトランジスタ37と、インバータ回路部38と、NMOSトランジスタ39とを具備している。

【0060】

図7に示した半導体装置の構成要素の接続関係について説明する。制御回路部36の入力部は、発振ゲート回路部20の出力部に接続されている。制御回路部36の出力部は、PMOSトランジスタ37のゲートと、インバータ回路部38の入力部とに接続されている。インバータ回路部38の出力部は、NMOSトランジスタ39のゲートに接続されている。PMOSトランジスタ37のドレインは、ノード11に接続されている。PMOSトランジスタ37のソースおよびバックゲートは、電源VDDに接続されている。NMOSトランジスタ39のドレインは、ノード12に接続されている。NMOSトランジスタ39のソースおよびバックゲートは、接地されている。

【0061】

図7に示した半導体装置のその他の構成は、図2に示した本発明の第1の実施形態による半導体装置の場合と同様であるので、さらなる詳細な説明を省略する。

【0062】

図7に示した半導体装置の動作について説明する。まず、制御回路部36は、入力する信号に基づいて論理信号を出力する。このとき、制御回路部36の出力信号は、初期状態ではロー状態であって、発振ゲート回路部20の出力信号に発振が始まってから所定の時間が経過した後にハイ状態に変わるものとする。より具体的には、制御回路部36として、タイマ回路やカウンタ回路などを用いても良い。

【0063】

次に、セレクタ回路部40は、初期状態において、制御回路部36からロー状態の信号を入力する。このとき、PMOSトランジスタ37はオン状態になり、ノード11の電圧V11は電源電圧VDDに等しくなる。また、インバータ回路部38を介して、NMOSトランジスタ39もオン状態になり、ノード12の電圧V12はグランドの基準電圧に等しくなる。すなわち、初期状態において、発振ゲート回路部20には、電源電圧VDDが供給される。

【0064】

なお、PMOSトランジスタ37は、ゲートに供給される電圧に応じてドレイン・ソース間を導通または遮断する第1のスイッチ回路部として動作する。同様に、NMOSトランジスタ39は、ゲートに供給される電圧に応じてドレイン・ソース間を導通または遮断する第2のスイッチ回路部として動作する。したがって、PMOSトランジスタ37と、NMOSトランジスタ39とは、それぞれ、スイッチ回路部として動作可能な他の構成に置き換えることが可能である。

【0065】

その後、所定の時間が経過して、制御回路部36の出力信号がハイ状態に転じると、PMOSトランジスタ37およびNMOSトランジスタ39は両方ともオフ状態となる。このとき、ノード11の電圧V11と、ノード12の電圧V12とは、本発明の第1の実施形態の場合と同様に、振幅制御回路部10によって決定される。

【0066】

上記に説明したように、本実施形態の半導体装置によれば、発振ゲート回路部20に供給される電圧が、最初の期間では高く、その後は低く抑えられる。その結果、発振ゲート回路部20の発振開始時における駆動能力不足による未発振を防ぎ、かつ、発振開始後の消費電力を抑制することが可能となる。

【0067】

(第4の実施形態)

図8は、本発明の第4の実施形態による半導体装置の構成を示す回路図である。本実施形態による半導体装置は、図2に示した本発明の第1の実施形態による半導体装置に、以下の変更を加えたものに等しい。すなわち、検知回路部46と、第1、第2のセレクタ回路部44、45と、第3のNMOSトランジスタ6aと、第3のPMOSトランジスタ8aと、合計6個のノード11a、11b、11c、12a、12b、12cを追加する。ここで、検知回路部46は、入力部と、第1、第2の入力部とを具備している。また、第1、第2のセレクタ回路部44、45のそれぞれは、第1〜第3の入力部と、出力部と、制御信号入力部とを具備している。

【0068】

本実施形態による半導体装置の構成要素の接続関係について説明する。第3のNMOSトランジスタ6aは、第1のNMOSトランジスタ5と、第2のNMOSトランジスタ6との間に、直列に接続されている。すなわち、第3のNMOSトランジスタ6aのドレインは、第1のNMOSトランジスタ5のソースに接続されており、第3のNMOSトランジスタ6aのソースは、第2のNMOSトランジスタ6のドレインに接続されている。さらに、第3のNMOSトランジスタ6aのゲートは、第3のNMOSトランジスタ6aのドレインと、第1のNMOSトランジスタ5のソースとに共通接続されている。第3のNMOSトランジスタ6aのバックゲートは、接地されている。

【0069】

第3のPMOSトランジスタ8aは、第1のPMOSトランジスタ7と、第2のPMOSトランジスタ8との間に、直列に接続されている。すなわち、第3のPMOSトランジスタ8aのドレインは、第1のPMOSトランジスタ7のソースに接続されており、第3のPMOSトランジスタ8aのソースは、第2のPMOSトランジスタ8のドレインに接続されている。さらに、第3のPMOSトランジスタ8aのゲートは、第3のPMOSトランジスタ8aのドレインと、第1のPMOSトランジスタ7のソースとに共通接続されている。第3のPMOSトランジスタ8aのバックゲートは、第3のPMOSトランジスタ8aのソースと、第2のPMOSトランジスタ8におけるゲートおよびドレインとに、共通接続されている。

【0070】

検知回路部46の入力部は、発振ゲート回路部20の出力部に接続されている。検知回路部46における第1の出力部は、第1のセレクタ回路部44の制御信号入力部に接続されている。検知回路部46における第2の出力部は、第2のセレクタ回路部45の制御信号入力部に接続されている。第1のセレクタ回路部44における第1の入力部は、ノード11aに接続されている。第1のセレクタ回路部44における第2の入力部は、ノード11bに接続されている。第1のセレクタ回路部44における第3の入力部は、ノード11cに接続されている。第2のセレクタ回路部45における第1の入力部は、ノード12aに接続されている。第2のセレクタ回路部45における第2の入力部は、ノード12bに接続されている。第2のセレクタ回路部45における第3の入力部は、ノード12cに接続されている。第1のセレクタ回路部44の出力部は、ノード11に接続されている。第2のセレクタ回路部45の出力部は、ノード12に接続されている。

【0071】

ノード11aは、電源VDDと、第1のNMOSトランジスタ5におけるドレインおよびゲートとに共通接続されている。ノード11bは、第1のNMOSトランジスタ5のソースと、第3のNMOSトランジスタ6aにおけるドレインおよびソースとに共通接続されている。ノード11cは、第3のNMOSトランジスタ6aのソースと、第2のNMOSトランジスタ6におけるドレインおよびゲートとに共通接続されている。

【0072】

ノード12aは、第2のPMOSトランジスタ8におけるソースおよびゲートと、第3のPMOSトランジスタ8aにおけるソースおよびバックゲートとに共通接続されている。ノード12bは、第1のPMOSトランジスタ7におけるソースおよびバックゲートと、第3のPMOSトランジスタ8aにおけるドレインおよびゲートとに共通接続されている。ノード12cは、第1のPMOSトランジスタ7におけるドレインおよびゲートと、第1〜第3のNMOSトランジスタ5、6、6aのそれぞれにおけるバックゲートとに共通接続されており、かつ、接地されている。

【0073】

図8に示した本実施形態による半導体装置のその他の構成は、図2に示した本発明の第1の実施形態による半導体装置の場合と同様であるので、さらなる詳細な説明を省略する。

【0074】

図8に示した本実施形態による半導体装置の動作について説明する。まず、振幅制御回路部10は、直列に接続されたMOSトランジスタの総数が増えているものの、基本的には本発明の第1〜第3の実施形態の場合と同様に動作する。すなわち、振幅制御回路部10は、電源電圧VDDと、MOSトランジスタ5、6、6a、7、8、8aのスレッショルド電圧Vt5、Vt6、Vt6a、Vt7、Vt8、Vt8aの比率とに応じた電圧を、ノード11a、11b、11c、12a、12b、12cからそれぞれ出力する。

【0075】

より具体的には、ノード11aの電圧V11a、ノード11bの電圧V11b、ノード11cの電圧V11c、ノード12aの電圧V12a、ノード12bの電圧V12b、ノード12cの電圧V12cは、次の式のように求められる。

V11a=VDD

V11b=VDD×(Vt6+Vt6a+Vt7+Vt8+Vt8a)/ΣVt

V11c=VDD×(Vt6+Vt7+Vt8+Vt8a)/ΣVt

V12a=VDD×(Vt7+Vt8a)/ΣVt

V12b=VDD×(Vt7)/ΣVt

V12c=0

ただし、

ΣVt=Vt5+Vt6+Vt6a+Vt7+Vt8+Vt8a

とする。ここで、例えば、電圧V11bは、電圧11aと、電圧11cとの中間程度であり、電圧V12bは、電圧12aと、電圧12cとの中間程度であるものとする。

【0076】

次に、検知回路部46は、発振ゲート回路部20が出力する電圧の振幅に基づいて第1、第2の制御信号を生成する。第1のセレクタ回路部44は、第1の制御信号に基づいて、ノード11a、11b、11cからいずれか1つを選択してノード11に接続する。同様に、第2のセレクタ回路部45は、第2の制御信号に基づいて、ノード12a、12b、12cからいずれか1つを選択してノード12に接続する。

【0077】

本実施形態による半導体装置の初期状態では、すなわち発振ゲート回路部20の発振が開始する直前までは、第1のセレクタ回路部44がノード11aをノード11に接続するような第1の制御信号を、検知回路部46が生成するものとする。同様に、初期状態では、第2のセレクタ回路部45がノード12cをノード12に接続するような第2の制御信号を、検知回路部46が生成するものとする。こうすることで、図7に示した本発明の第3の実施形態の場合と同様に、発振ゲート回路部20に対して、電源電圧VDDにほぼ等しい電圧を供給することが出来る。すなわち、発振ゲート回路部20が高い電圧を供給されることで、発振の開始をより確実にすることが出来る。

【0078】

本実施形態による半導体装置の発振安定状態では、すなわち発振ゲート回路部20の発振が安定して持続している間は、第1のセレクタ回路部44がノード11cをノード11に接続するような第1の制御信号を、検知回路部46が生成するものとする。同様に、定常状態では、第2のセレクタ回路部45がノード12aをノード12に接続するような第2の制御信号を、検知回路部46が生成するものとする。こうすることで、本発明の他の実施形態の場合と同様に、発振ゲート回路部20に供給する電圧を削減することが可能となる。

【0079】

さらに、本実施形態の特徴として、電源電圧VDDが何らかの原因によって降下するなどして、発振ゲート回路部20が出力する電圧の振幅が減少した発振不安定状態では、発振ゲート回路部20に供給する電圧を一時的に上昇させることが可能である。発振不安定状態では、第1のセレクタ回路部44がノード11bノード11に接続するような第1の制御信号を、検知回路部46が生成するものとする。同様に、発振不安定状態では、第2のセレクタ回路部45がノード12bをノード12に接続するような第2の制御信号を、検知回路部46が生成するものとする。こうすることで、発振ゲート回路部20への供給電圧をなるべく節約しつつ、半導体装置を発振安定状態に戻すことが可能となる。

【0080】

なお、本実施形態による振幅制御回路部10は、合計6個のMOSトランジスタを直列に接続して具備しているが、これらMOSトランジスタの総数は本発明を限定するものではない。これらのMOSトランジスタの総数をさらに増やし、ノード11、ノード12に印加する電圧をさらに細かく制御しても良い。こうすることで、発振ゲート回路部20の安定性を確保しながら、必要最小限な供給電圧の値をさらに柔軟に制御することが可能となる。

【0081】

以上に説明した、本発明による第1〜第4の実施形態による半導体装置の特徴は、技術的に矛盾しない範囲において、自由に組み合わせることが可能である。

【符号の説明】

【0082】

1 PMOSトランジスタ

2 NMOSトランジスタ

3 帰還抵抗

4 振動子

5 NMOSトランジスタ

6 NMOSトランジスタ

6a NMOSトランジスタ

7 PMOSトランジスタ

8 PMOSトランジスタ

8a PMOSトランジスタ

10 振幅制御回路部

11 ノード

11a〜11c ノード

12 ノード

12a〜12c ノード

20 発振ゲート回路部

36 制御回路部

37 PMOSトランジスタ

38 インバータ回路部

39 NMOSトランジスタ

40 セレクタ回路部

42、43 レイアウト

44 セレクタ回路部

45 セレクタ回路部

46 検知回路部

61〜64 レイアウト

71 半導体装置

72 半導体装置

73 回路部

74 回路部

101 PMOSトランジスタ

102 NMOSトランジスタ

103 帰還抵抗

104 振動子

107 PMOSトランジスタ

108 NMOSトランジスタ

109 振幅増幅回路

111 PMOSトランジスタ

112 NMOSトランジスタ

120 発振ゲート回路部

130 ダイオード

131 ダイオード

132 PMOSトランジスタ

133 NMOSトランジスタ

134 電流源

135 電流源

151 振幅制御回路

152 振幅制御回路

C1 入力側コンデンサ

C2 出力側コンデンサ

C101 入力側コンデンサ

C102 出力側コンデンサ

VCC 電源

VDD 電源

【技術分野】

【0001】

本発明は、半導体装置に係り、特に、発振回路を有する半導体装置に係る。

【背景技術】

【0002】

モバイル情報端末や、DSC(Digital Still Camera:デジタルカメラ)などにおいて、サイズの小型化が進んでいる。端末の小型化に伴い、バッテリの小型化も進んでおり、また、容量の小さいボタン電池を使用するケースも増加している。このため、LSI(Large Scale Integration:大規模集積回路)内部で常時動作する発振回路でも、低消費電力化の要求が高まっている。

【0003】

このような発振回路に電力を供給する方法として、定電圧回路を用いて、電源電圧から一定の幅で電圧を降下させて、発振回路に供給する従来技術が知られている。しかし、このような従来技術では、降下される電圧の幅が大きければ大きいほど、抵抗値のより高い抵抗素子が必要となる。そして、抵抗素子の抵抗値が高ければ高いほど、LSIの中でより広い面積を占有する。

【0004】

そこで、LSI内部の占有面積の節約と、低消費電力化との両立が求められている。

【0005】

上記に関連して、特許文献1(特開2005−159786号公報)には、発振回路に係る記載が開示されている。この発振回路は、消費電流の削減を目的として掲げている。この発振回路は、発振ゲートへの供給電圧を抑制する機能部を具備している。この発振回路は、ダイオード接続されたトランジスタのスレショルド電圧を用いて電圧を抑制する動作を行う。

【0006】

図1は、特許文献1に記載の発振回路の構成を示す回路図である。図1の発振回路の構成要素について説明する。この発振回路は、発振ゲート回路部120と、第1および第2の振幅抑制回路151および152と、振幅増幅回路109と、入力側コンデンサC101と、出力側コンデンサC102と、帰還抵抗103と、発振子104とを具備している。発振ゲート回路部120は、PMOSトランジスタ101と、NMOSトランジスタ102とを具備している。第1の振幅抑制回路151は、PMOSトランジスタ107を具備している。第1の振幅抑制回路151は、ダイオード130や、他のPMOSトランジスタ132や、第1の電流源134などをさらに具備しても良いが、ここではその詳細を省略する。第2の振幅抑制回路152は、NMOSトランジスタ108を具備している。第2の信服抑制回路152は、第2のダイオード132や、他のNMOSトランジスタ133や、第2の電流源135などをさらに具備しても良いが、ここではその詳細を省略する。振幅増幅回路109は、PMOSトランジスタ111と、NMOSトランジスタ112とを具備している。

【0007】

図1の発振回路の構成要素の接続関係について説明する。PMOSトランジスタ107のソースは、電源VCCに接続されている。PMOSトランジスタ107におけるゲートおよびドレインは、PMOSトランジスタ101のソースに共通接続されている。PMOSトランジスタ101のゲートは、NMOSトランジスタ102のゲートと、帰還抵抗103における一方の端部と、発振子104における一方の端部と、入力側コンデンサC101における一方の端部とに共通接続されている。PMOSトランジスタ101のドレインは、NMOSトランジスタ102のドレインと、帰還抵抗103における他方の端部と、発振子104における他方の端部と、出力側コンデンサC102における他方の端部と、PMOSトランジスタ111のゲートと、NMOSトランジスタ112のゲートとに共通接続されている。NMOSトランジスタ102のソースは、NMOSトランジスタ108におけるゲートおよびドレインに共通接続されている。NMOSトランジスタ108のソースは、接地されている。入力側コンデンサC101における他方の端部は、接地されている。出力側コンデンサC102における他方の端部は、接地されている。PMOSトランジスタ111のソースは、電源VCCに接続されている。PMOSトランジスタ111のドレインは、NMOSトランジスタ112のドレインと、出力部CKOUTとに共通接続されている。NMOSトランジスタ112のソースは、接地されている。

【0008】

図1の発振回路の動作について説明する。第1の振幅抑制回路151において、PMOSトランジスタ107は、ゲートおよびドレインが短絡されており、すなわちいわゆる「ダイオード接続」がされている。したがって、PMOSトランジスタ107のドレインにおける電圧の値は、電源VCCの電圧からPMOSトランジスタ107のスレッショルド電圧だけ下降した値に等しい。以下、PMOSトランジスタ107のスレッショルド電圧をVt107と記す。

【0009】

同様に、第2の振幅抑制回路152において、NMOSトランジスタ108もダイオード接続されている。したがって、NMOSトランジスタ108のドレインにおける電圧の値は、グランドの電圧からNMOSトランジスタ108のスレッショルド電圧だけ上昇した値に等しい。以下、NMOSトランジスタ108のスレッショルド電圧をVt108と記す。

【0010】

発振ゲート回路部120において、PMOSトランジスタ101と、NMOSトランジスタ102とは、第1の振幅抑制回路151におけるPMOSトランジスタ107のドレインと、第2の振幅抑制回路152におけるNMOSトランジスタ108のドレインとの間に、直列に接続されている。したがって、発振ゲート回路部120が生成する発振信号の電圧は、電源電圧VCCからスレッショルド電圧Vt107だけ下降した電圧と、グランド電圧からスレッショルド電圧Vt108だけ上昇した電圧との間で振幅する。

【0011】

ここで、発振ゲート回路部120の出力信号は、帰還抵抗103および振動子104を介して入力側に帰還することで発振する。なお、発振ゲート回路部120の発振信号が生成される際、入力側コンデンサC101と、出力側コンデンサC102とにおいて充放電が発生する。この充放電に伴う電流は、発振回路としての消費電力につながる。特許文献1では、発振信号の振幅を小さくすることで、発振回路の消費電力を低減している。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2005−159786号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

特許文献1の発振回路には、その動作が、トランジスタの製造時に発生するプロセスばらつきに影響されてしまうという問題がある。プロセスばらつきが発生する方向には、大きく分けて2種類の場合がある。

【0014】

まず、第1の場合では、PMOSトランジスタおよびNMOSトランジスタのスレッショルド電圧が設計値よりも高くなる方向にプロセスばらつきが発生する。このとき、発振ゲート回路部120が生成する発振信号の振幅は、設計値よりも大きくなる。また、発振ゲート回路部120の駆動能力は設計値よりも小さくなる。したがって、第1の場合では、発振ゲート回路部120において、PMOSトランジスタ101のソースと、NMOSトランジスタ102のソースとの間の電圧は、より大きいことが望ましい。

【0015】

次に、第2の場合では、PMOSトランジスタおよびNMOSトランジスタのスレッショルド電圧が設計値よりも低くなる方向にプロセスばらつきが発生する。このとき、発振ゲート回路部120が生成する発振信号の振幅は、設計値よりも小さくなる。また、発振ゲート回路部120の駆動能力は設計値よりも大きくなる。したがって、第2の場合では、発振ゲート回路部120において、PMOSトランジスタ101のソースと、NMOSトランジスタ102のソースとの間の電圧は、より小さいことが望ましい。

【0016】

しかし、トランジスタの製造時に、プロセスばらつきがどちらの方向に発生するのかは、予測不可能である。そこで、プロセスばらつきがいずれの方向に発生しても発振ゲート回路部120が確実に動作する電圧範囲が確保できるように、設計時の段階で十分なマージンを用意しておく必要がある。その結果、発振ゲート回路部120において、PMOSトランジスタ101のソースと、NMOSトランジスタ102のソースとの間に供給される電圧範囲は、消費電力の低減に寄与しないマージンを含んでしまう。

【0017】

また、ダイオード接続されたMOSトランジスタにおけるスレッショルド電圧は、一般的に0.6V〜0.7V程度である。より大きいスレッショルド電圧を得るためには、MOSトランジスタのゲート長Lをより大きくして、ドレインおよびソースの間を流れる電流IDSを小さくする必要がある。ただし、電流IDSは、ゲート長Lの逆数に比例する。図5Aは、一般的なMOSトランジスタにおける、ゲート長Lと、ドレインおよびソースの間を流れる電流IDSとの関係を示すグラフである。特許文献1の発振回路の場合、十分に小さい電流IDSを得るためには、ゲート長Lを数十μm(マイクロメートル)まで大きくする必要があると考えられる。このようなゲート長Lを有するMOSトランジスタを用いることは、発振回路の面積が大きくなる原因となる。このように、特許文献1の発振回路では、消費電力の低減と、製造コストの低減とを両立することが出来ない。

【課題を解決するための手段】

【0018】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0019】

半導体装置は、第1の電源部(VDD)と、第2の電源部(GND)と、振幅制御回路部(10)と、発振回路部(20、3、4、C1、C2)とを具備する。ここで、第1の電源部(VDD)は、第1の電源電圧を供給する。第2の電源部(GND)は、第2の電源電圧を供給する。振幅制御回路部(10)は、第1および第2の電源電圧(VDD、GND)を入力して第1および第2の供給電圧(V11、V12)を生成する。発振回路部(20、3、4、C1、C2)は、第1および第2の入力部(11、12)から第1および第2の供給電圧(V11、V12)をそれぞれ入力して発振する。振幅制御回路部(10)は、複数のMOSトランジスタ(5〜8)と、第1の出力部(11)と、第2の出力部(12)とを具備する。ここで、複数のMOSトランジスタ(5〜8)は、第1および第2の電源部(VDD、GND)の間に直列に接続されて、かつ、それぞれがダイオード接続されている。第1の出力部(11)は、複数のMOSトランジスタ(5〜8)のドレインまたはソースに接続されて、第1の供給電圧(V11)を出力する。第2の出力部(12)は、複数のMOSトランジスタ(5〜8)の他のドレインまたは他のソースに接続されて、第2の供給電圧(V12)を出力する。

【発明の効果】

【0020】

本発明の半導体装置によれば、直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタを用いて、発振回路部を駆動させる電圧を生成する。このとき、複数のMOSトランジスタで生成される電圧の値は、電源電圧と、各MOSトランジスタのスレッショルド電圧の比率とに基づいて得られる。したがって、各MOSトランジスタのスレッショルド電圧を小さく抑えることが出来て、各MOSトランジスタの面積を節約することが出来て、発振回路部の消費電力を削減することが出来る。

【図面の簡単な説明】

【0021】

【図1】図1は、特許文献1に記載の発振回路の構成を示す回路図である。

【図2】図2は、本発明の第1の実施形態による半導体装置の構成を示す回路図である。

【図3A】図3Aは、従来技術による半導体装置におけるMOSトランジスタ群のレイアウト図の一例である。

【図3B】図3Bは、本発明の第1の実施形態による半導体装置におけるMOSトランジスタ群のレイアウト図の一例である。

【図4A】図4Aは、従来技術による半導体装置の全体的なレイアウト図の一例である。

【図4B】図4Bは、本発明の第1の実施形態による半導体装置の全体的なレイアウト図の一例である。

【図5】図5は、NMOSトランジスタの長さLと、ドレイン・ソース間電流IDSとの関係を概略的に示すグラフである。

【図6】図6は、本発明の第2の実施形態による半導体装置の構成を示す回路図である。

【図7】図7は、本発明の第3の実施形態による半導体装置の構成を示す回路図である。

【図8】図8は、本発明の第4の実施形態による半導体装置の構成を示す回路図である。

【発明を実施するための形態】

【0022】

添付図面を参照して、本発明による半導体装置を実施するための形態を以下に説明する。

【0023】

(第1の実施形態)

図2は、本発明の第1の実施形態による半導体装置の構成を示す回路図である。図2に示した半導体装置の構成要素について説明する。図2に示した半導体装置は、電源VDDと、グランドGNDと、振幅制御回路部10と、発振ゲート回路部20と、帰還抵抗3と、振動子4と、入力側コンデンサC1と、出力側コンデンサC2とを具備している。振幅制御回路部10は、第1、第2のNMOSトランジスタ5、6と、第1、第2のPMOSトランジスタ7、8とを具備している。発振ゲート回路部20は、PMOSトランジスタ1と、NMOSトランジスタ2とを具備している。ここで、発振ゲート回路部20と、帰還抵抗3と、振動子4と、入力側コンデンサC1と、出力側コンデンサC2とをまとめて発振回路部と呼んでも良い。

【0024】

図2に示した半導体装置の構成要素の接続関係について説明する。電源VDDは、第1のNMOSトランジスタ5におけるドレインおよびゲートと、第1のPMOSトランジスタ7のバックゲートとに共通接続されている。ノード11は、第1のNMOSトランジスタ5のソースと、第2のNMOSトランジスタ6におけるソースおよびゲートと、PMOSトランジスタ1におけるソースおよびバックゲートとに共通接続されている。ノード12は、第1のPMOSトランジスタ7におけるソースと、第2のPMOSトランジスタ8におけるドレインおよびゲートと、NMOSトランジスタ2のソースとに共通接続されている。第2のNMOSトランジスタ6のソースは、第2のNMOSトランジスタ8におけるソースおよびバックゲートに共通接続されている。第1のNMOSトランジスタ5のバックゲートと、第2のNMOSトランジスタ6のバックゲートと、第1のPMOSトランジスタ7のゲートと、NMOSトランジスタ2のバックゲートと、入力側コンデンサC1における一方の端部と、出力側コンデンサC2における一方の端部とは、接地されている。入力側コンデンサC1における他方の端部は、PMOSトランジスタ1のゲートと、NMOSトランジスタ2のゲートと、帰還抵抗3における一方の端部と、振動子4における一方の端部とに共通接続されている。出力側コンデンサC2における他方の端部は、PMOSトランジスタ1のドレインと、NMOSトランジスタ2のドレインと、帰還抵抗3における他方の端部と、振動子4における他方の端部とに共通接続されている。

【0025】

図2に示した半導体装置の動作について説明する。まず、発振ゲート回路部20、入力側コンデンサC1、出力側コンデンサC2、帰還抵抗3および振動子4の動作について、前述した従来技術の場合と同様であるが、再度説明する。

【0026】

電源VDDは、第1の電源電圧VDDを供給する第1の電源部として動作する。同様に、グランドGNDは、第2の電源電圧として基準電圧を供給する第2の電源部として動作する。発振ゲート回路部20において、PMOSトランジスタ1と、NMOSトランジスタ2とは、ノード11と、ノード12との間に、直列に接続されている。したがって、発振ゲート回路部20が生成する発振信号の電圧は、ノード11における電圧と、ノード12における電圧との間で振幅する。ここで、ノード11と、ノード12とは、発振ゲート回路部20における第1、第2の入力部として機能する。また、発振ゲート回路部20の出力信号は、帰還抵抗3および振動子4を介して入力側に帰還することで発振する。なお、発振ゲート回路部20の発振信号が生成される際、入力側コンデンサC1と、出力側コンデンサC2とにおいて充放電が発生する。この充放電に伴う電流は、発振回路としての消費電力につながる。

【0027】

次に、ダイオード接続されたMOSトランジスタの動作について説明する。MOSトランジスタにおいて、ゲートがドレインに接続されていることを、ダイオード接続されていると言う。ダイオード接続されたMOSトランジスタでは、ゲート・ソース間電圧VGSがそのままスレッショルド電圧Vtとなる。図2の半導体装置では、第1、第2のNMOSトランジスタ5、6と、第1のPMOSトランジスタ7とがダイオード接続されている。したがって、MOSトランジスタ5〜7のスレッショルド電圧Vt5〜Vt7は、MOSトランジスタ5〜7のゲート・ソース間電圧VGS5〜VGS7に、それぞれ等しい。

【0028】

MOSトランジスタは、バックゲート・ソース間の電圧VBSの絶対値がゼロ以上である場合に、ソースからドレインへの電流が流れにくくなる。この場合、MOSトランジスタのスレッショルド電圧Vtは、バックゲート・ソース間電圧VBSがゼロに等しい場合よりも高くなる。図2に示した半導体装置において、第2のPMOSトランジスタ8は、ダイオード接続されているが、バックゲートがソースに接続されているので、バックゲート・ソース間電圧VBS8がゼロに等しい。そのため、第2のPMOSトランジスタ8のスレッショルド電圧Vt8は、他のMOSトランジスタ5〜7のスレッショルド電圧Vt5〜Vt7よりも低い。

【0029】

次に、図2に示した半導体装置の、発振が開始するまでの動作を説明する。まず、初期状態において、全てのトランジスタがオフ状態になっている。第1のNMOSトランジスタ5は、ゲートが電源VDDに接続されているため、電源投入後にドレイン・ソース間電流(以下「IDS」と記す)が発生する。第2のNMOSトランジスタ6は、ドレインおよびゲートに電圧が印加されて、IDSが発生する。第2のPMOSトランジスタ8は、ソースに電圧が印加される。第1のNMOSトランジスタ7は、ソースに電圧が印加される。ここで、ゲートがドレインに接続されており、ソース電圧に対してゲート電圧の方が低いため、IDSが発生する。振幅制御回路部10に含まれるMOSトランジスタ5〜8は、その全てがダイオード接続されているので、本来ならそれぞれのスレッショルド電圧Vt5〜Vt8で動作するはずである。しかし、これら4つのMOSトランジスタ5〜8は、直列に接続されていて、かつ、その両端が電源電圧VDDで印加されている。したがって、振幅制御回路10に含まれるMOSトランジスタ5〜8のドレイン・ソース間電圧VDS5〜VDS8は、電源電圧VDDと、これらのMOSトランジスタ5〜8のそれぞれにおけるスレッショルド電圧Vt5〜Vt8の比率とで決定する。具体的には、MOSトランジスタ5〜8のそれぞれにおける実際のドレイン・ソース間電圧VDS5〜VDS8は、本来のスレッショルド電圧Vt5〜Vt8の比率に応じて、次の式のように求められる。

VDS5=VDD×Vt5/(Vt5+Vt6+Vt7+Vt8)

VDS6=VDD×Vt6/(Vt5+Vt6+Vt7+Vt8)

VDS7=VDD×Vt7/(Vt5+Vt6+Vt7+Vt8)

VDS8=VDD×Vt8/(Vt5+Vt6+Vt7+Vt8)

【0030】

上記に示した、MOSトランジスタ5〜8のドレイン・ソース間電圧VDS5〜VDS8から、ノード11に供給される電圧V11と、ノード12に供給される電圧V12とは、次の式のように決定される。

V11=VDD×(Vt6+Vt7+Vt8)/(Vt5+Vt6+Vt7+Vt8)

V12=VDS7=VDD×Vt7/(Vt5+Vt6+Vt7+Vt8)

【0031】

上記に示した、ノード11、12の電圧V11、V12の差を駆動電圧ΔVとおくと、次の式のように求められる。

ΔV=V11−V12=VDD×(Vt6+Vt8)/(Vt5+Vt6+Vt7+Vt8)

発振ゲート回路部20に含まれる2つのMOSトランジスタ1、2が上記の駆動電圧ΔVを印加されることによって、発振ゲート回路部20は発振動作を開始する。

【0032】

なお、ノード11と、ノード12とは、振幅制御回路部10が第1、第2の供給電圧V11、V12を出力する第1、第2の出力部としても機能する。

【0033】

ここでもし、第2のPMOSトランジスタ8のバックゲートが電源VDDに接続されていたら、トランジスタ8のスレッショルド電圧Vt8は、図2のように接続されていない場合よりも大きくなる。その結果、振幅制御回路部10に含まれる4つのトランジスタ5〜8におけるスレッショルド電圧Vt5〜Vt8の比率が変わる。具体的には、ノード11の電圧V11がより高くなり、ノード12の電圧V12はより低くなり、その差である駆動電圧ΔVは高くなる。

【0034】

言い換えれば、図2のように、第2のPMOSトランジスタ8のバックゲートをそのソースに接続することで、本実施形態による半導体装置では、駆動電圧ΔVをさらに低くすることが出来る。

【0035】

発振ゲート回路部20への電源供給は、電源電圧VDDから下げたノード11の電圧V11と、グランドGNDの基準電圧から上げたノード12の電圧V12とで行われる。そのため、発振ゲート回路部20の出力波形は、その発振が定常状態にまで成長しきった後の最大振幅が、ノード11の電圧V11と、ノード12の電圧V12との間で小さく収まる。したがって、入力側コンデンサC1と、出力側コンデンサC2に充放電される電流もそれだけ小さくなる。結果的に、発振器全体としての消費電力を削減することが可能となる。

【0036】

ここで、半導体プロセスによる製造ばらつきの問題について考える。実際に製造された半導体装置では、製品ごとにトランジスタのスレッショルド電圧Vtがばらつくのが一般的である。このばらつきが、従来技術の場合には発振ゲート回路部の供給される電圧に直接的に影響するが、本発明によればこの影響が小さくなることを説明する。

【0037】

図1に示した従来技術の場合では、発振ゲート回路部120に供給される電圧は、PMOSトランジスタ107から供給されるハイ側の電圧と、NMOSトランジスタ108から供給されるロー側の電圧との差に等しい。ここで、PMOSトランジスタ107は、ダイオード接続されており、かつ、ソースが電源VCCに接続されている。したがって、ハイ側の電圧は、電源電圧VCCから、PMOSトランジスタ107のスレッショルド電圧Vt107だけ下げた電圧に等しい。同様に、NMOSトランジスタ108は、ダイオード接続されており、かつ、ソースが接地されている。したがって、ロー側の電圧は、グランドの基準電圧から、NMOSトランジスタ108のスレッショルド電圧Vt108だけ上げた電圧に等しい。このような構成では、発振ゲート回路部120に供給される電圧が、製造ばらつきの影響を直接的に受けてしまい、すなわち製造ばらつきと同じ比率でばらついてしまう。

【0038】

しかし、本実施形態による半導体装置では、直列に接続されたMOSトランジスタ5〜8のスレッショルド電圧Vt5〜Vt8に製造ばらつきが生じても、その比率は変わらない場合がある。これは、同じ半導体基板上の、比較的近い場所に形成される複数のトランジスタにおいて、発生する製造ばらつきは同様であると期待されるからである。この場合は、発振ゲート回路部20に供給される駆動電圧ΔVは、スレッショルド電圧の比率によって決定されるので、製造ばらつきの影響を受けずに済む。

【0039】

その一方で、PMOSトランジスタと、NMOSトランジスタとでは、製造ばらつきが逆方向に働く場合もある。この場合は、直列に接続されたMOSトランジスタ5〜8のそれぞれにおけるスレッショルド電圧Vt5〜Vt8の比率が変わってしまう。したがって、この場合は、発振ゲート回路部20に供給される駆動電圧ΔVが製造ばらつきの影響を受けてしまう。

【0040】

ただし、この場合は、発振ゲート回路部20に含まれるPMOSトランジスタ1と、NMOSトランジスタ2も、逆方向に働く製造ばらつきの影響を、MOSトランジスタ5〜8と同様に受けているはずである。すなわち、発振ゲート回路部20が動作する上で実際に必要な駆動電圧も、製造ばらつきの影響を、振幅制御回路部10から供給される駆動電圧ΔVと同様に受けているはずである。したがって、本実施形態による半導体装置では、製造ばらつきを考慮するにあたって、過剰なマージンを必要としない。その結果、従来技術では必要とされたマージンに纏わる余分な消費電力を、本発明では低減することが可能となっている。

【0041】

なお、直列に接続されているMOSトランジスタ5〜8について、チャネル極性を入れ替えたり、接続する順番を入れ替えたりしても、上記と同様の動作および効果が得られることは当然である。

【0042】

上記に説明したように、本実施形態による半導体装置では、発振ゲート回路部20に供給される駆動電圧ΔVを、複数のMOSトランジスタ5〜8のスレッショルド電圧Vt5〜Vt8の比率として決定している。したがって、これらのMOSトランジスタ5〜8の実効的なスレッショルド電圧Vt5〜Vt8を従来技術のように大きくする必要が無い。その結果、半導体装置全体としてのレイアウト面積を節約することが可能となっている。

【0043】

図3Aは、従来技術による半導体装置におけるMOSトランジスタ群のレイアウト図の一例である。図3Bは、本発明の第1の実施形態による半導体装置におけるMOSトランジスタ群のレイアウト図の一例である。図3A、図3Bを参照して、本発明による半導体装置ではMOSトランジスタのレイアウト面積を大幅に節約できることを説明する。

【0044】

図3Aには、PMOSトランジスタ42と、NMOSトランジスタ43とが描かれている。図3Bには、NMOSトランジスタ61、62と、PMOSトランジスタ63、64とが描かれている。図3AのPMOSトランジスタ42は、図1のPMOSトランジスタ151に対応する。図3AのNMOSトランジスタ43は、図1のNMOSトランジスタ152に対応する。図3BのNMOSトランジスタ61は、図2のNMOSトランジスタ5に対応する。図3BのNMOSトランジスタ62は、図2のNMOSトランジスタ6に対応する。図3BのPMOSトランジスタ63は、図2のNMOSトランジスタ7に対応する。図3BのPMOSトランジスタ64は、図2のNMOSトランジスタ8に対応する。ここで、図3Aおよび図3Bに描かれた全てのMOSトランジスタの縮尺は同じである。

【0045】

図1に示した従来技術では、十分に大きなスレッショルド電圧Vtを確保するために、MOSトランジスタのレイアウト面積を、図3Aに示したように大きくする必要があった。しかし、図2に示した本発明の場合は、スレッショルド電圧Vtの比率が重要なので、MOSトランジスタのレイアウト面積を、図3Bに示したように最小限に抑えることが可能である。

【0046】

図4Aは、従来技術による半導体装置の全体的なレイアウト図の一例である。図4Bは、本発明の第1の実施形態による半導体装置の全体的なレイアウト図の一例である。図4A、図4Bを参照して、本発明による半導体装置では、全体的なレイアウト面積を大幅に節約できることを説明する。

【0047】

図4Aには、半導体装置71のレイアウトが描かれている。半導体装置71は、PMOSトランジスタ42と、NMOSトランジスタ43と、PMOSトランジスタ101と、NMOSトランジスタ102と、帰還抵抗103と、回路部73とを含んでいる。図4AのPMOSトランジスタ42は、図1のPMOSトランジスタ151に対応する。図4AのNMOSトランジスタ43は、図1のNMOSトランジスタ152に対応する。図4AのPMOSトランジスタ101は、図1のPMOSトランジスタ101に対応する。図4AのNMOSトランジスタ102は、図1のNMOSトランジスタ102に対応する。図4Aの帰還抵抗103は、図1の帰還抵抗103に対応する。図4Aの回路部73は、図1のその他の構成要素、例えば入力側コンデンサC101、出力側コンデンサC102、振動子104、などに対応するものとする。

【0048】

図4Bには、半導体装置72のレイアウトが描かれている。半導体装置72は、PMOSトランジスタ61、62と、NMOSトランジスタ63、64と、PMOSトランジスタ1と、NMOSトランジスタ2と、帰還抵抗3と、回路部74とを含んでいる。図4BのPMOSトランジスタ61、62は、図2のPMOSトランジスタ7、8に対応する。図4BのNMOSトランジスタ63、64は、図2のNMOSトランジスタ5、6に対応する。図4BのPMOSトランジスタ1は、図2のPMOSトランジスタ1に対応する。図4BのNMOSトランジスタ2は、図2のNMOSトランジスタ2に対応する。図4Bの帰還抵抗3は、図2の帰還抵抗3に対応する。図4Bの回路部74は、図2のその他の構成要素、例えば入力側コンデンサC1、出力側コンデンサC2、振動子4、などに対応するものとする。

【0049】

ここで、図4A、図4Bのレイアウトの縮尺は同じである。それでも、図4Aの半導体装置71の全体的なレイアウト面積が、図4Bの半導体装置72の全体的なレイアウト面積の2倍近く大きくなってしまう最大の原因は、NMOSトランジスタ43の長さにあると言える。NMOSトランジスタ43の長さが、半導体装置71の大半を占めるデッドスペースが発生する原因となっているからである。

【0050】

なお、本実施形態と同等の性能を有する半導体装置を、図1に示した従来技術で構成するなら、NMOSトランジスタ43の長さLとして数十μm程度を確保する必要がある。この長さLは、十分なスレッショルド電圧Vtを確保し、かつ、ドレイン・ソース間電流IDSを低く抑えるために必要となる。

【0051】

図5は、NMOSトランジスタの長さLと、ドレイン・ソース間電流IDSとの関係を概略的に示すグラフである。図5において、横軸はNMOSトランジスタの長さLを示し、縦軸はドレイン・ソース間電流IDSを示す。図5のグラフから、ドレイン・ソース間電流IDSを低く抑えるためには、NMOSトランジスタの長さLを大きく確保する必要があることが読み取れる。

【0052】

上記に説明したように、本発明の第1の実施形態による半導体装置は、レイアウト面積の縮小に伴う製造コストの節約と、消費電力の節約とによる、2つの面でのコスト削減を可能とする。

【0053】

(第2の実施形態)

図6は、本発明の第2の実施形態による半導体装置の構成を示す回路図である。本実施形態による半導体装置は、図2に示した本発明の第1の実施形態による半導体装置に、以下の変更を加えたものに等しい。すなわち、図2の半導体装置では、第2のPMOSトランジスタ8のバックゲートが、第2のPMOSトランジスタ8のソースと、第2のNMOSトランジスタ6のソースとに共通接続されている。また、図2の半導体装置では、第2のNMOSトランジスタ6のバックゲートは、接地されている。しかし、本実施形態による半導体装置では、第2のNMOSトランジスタ6のバックゲートが、第2のPMOSトランジスタ8のソースと、第2のNMOSトランジスタ6のソースとに共通接続されている。また、本実施形態による半導体装置では、第2のPMOSトランジスタ8のバックゲートが接地されている。

【0054】

本実施形態による半導体装置のその他の構成については、図2に示した本発明の第1の実施形態の場合と同様であるので、さらなる詳細な説明を省略する。

【0055】

本実施形態による半導体装置の動作について説明する。本実施形態による半導体装置では、第2のNMOSトランジスタ6のスレッショルド電圧Vt6が、MOSトランジスタ5、7、8のスレッショルド電圧Vt5、Vt7、Vt8よりも低くなる。しかし、結果として、発振ゲート回路部20に供給される駆動電圧ΔVは、図2に示した本発明の第1の実施形態の場合と同じとなる。

【0056】

本実施形態による半導体装置のその他の動作および効果については、図2に示した本発明の第1の実施形態の場合と同様であるので、さらなる詳細な説明を省略する。

【0057】

(第3の実施形態)

図7は、本発明の第3の実施形態による半導体装置の構成を示す回路図である。図7の半導体装置は、図2に示した本発明の第1の実施形態による半導体装置に、以下の変更を加えたものに等しい。すなわち、制御回路部36と、セレクタ回路部40とを追加する。

【0058】

回路構成(トランジスタサイズを含む)の決まっている発振回路の増幅率は、発振回路を流れる電流(あるいは発振回路にかかる電圧)によって変化する。一般的に、発振回路は、発振開始時に必要な増幅率が、発振の持続に必要な増幅率よりも高い。言い換えれば、発振ゲート回路部20を流れる電流(あるいは発振ゲート回路部20にかかる電圧)が何らかの原因により低すぎた場合に、発振ゲート回路部20の増幅率が低くなり発振が開始しない恐れがある。本実施形態では、制御回路部36と、セレクタ回路部40とを追加することでこの問題を解決出来ることを説明する。

【0059】

図7に示した半導体装置の構成要素について説明する。セレクタ回路部40は、PMOSトランジスタ37と、インバータ回路部38と、NMOSトランジスタ39とを具備している。

【0060】

図7に示した半導体装置の構成要素の接続関係について説明する。制御回路部36の入力部は、発振ゲート回路部20の出力部に接続されている。制御回路部36の出力部は、PMOSトランジスタ37のゲートと、インバータ回路部38の入力部とに接続されている。インバータ回路部38の出力部は、NMOSトランジスタ39のゲートに接続されている。PMOSトランジスタ37のドレインは、ノード11に接続されている。PMOSトランジスタ37のソースおよびバックゲートは、電源VDDに接続されている。NMOSトランジスタ39のドレインは、ノード12に接続されている。NMOSトランジスタ39のソースおよびバックゲートは、接地されている。

【0061】

図7に示した半導体装置のその他の構成は、図2に示した本発明の第1の実施形態による半導体装置の場合と同様であるので、さらなる詳細な説明を省略する。

【0062】

図7に示した半導体装置の動作について説明する。まず、制御回路部36は、入力する信号に基づいて論理信号を出力する。このとき、制御回路部36の出力信号は、初期状態ではロー状態であって、発振ゲート回路部20の出力信号に発振が始まってから所定の時間が経過した後にハイ状態に変わるものとする。より具体的には、制御回路部36として、タイマ回路やカウンタ回路などを用いても良い。

【0063】

次に、セレクタ回路部40は、初期状態において、制御回路部36からロー状態の信号を入力する。このとき、PMOSトランジスタ37はオン状態になり、ノード11の電圧V11は電源電圧VDDに等しくなる。また、インバータ回路部38を介して、NMOSトランジスタ39もオン状態になり、ノード12の電圧V12はグランドの基準電圧に等しくなる。すなわち、初期状態において、発振ゲート回路部20には、電源電圧VDDが供給される。

【0064】

なお、PMOSトランジスタ37は、ゲートに供給される電圧に応じてドレイン・ソース間を導通または遮断する第1のスイッチ回路部として動作する。同様に、NMOSトランジスタ39は、ゲートに供給される電圧に応じてドレイン・ソース間を導通または遮断する第2のスイッチ回路部として動作する。したがって、PMOSトランジスタ37と、NMOSトランジスタ39とは、それぞれ、スイッチ回路部として動作可能な他の構成に置き換えることが可能である。

【0065】

その後、所定の時間が経過して、制御回路部36の出力信号がハイ状態に転じると、PMOSトランジスタ37およびNMOSトランジスタ39は両方ともオフ状態となる。このとき、ノード11の電圧V11と、ノード12の電圧V12とは、本発明の第1の実施形態の場合と同様に、振幅制御回路部10によって決定される。

【0066】

上記に説明したように、本実施形態の半導体装置によれば、発振ゲート回路部20に供給される電圧が、最初の期間では高く、その後は低く抑えられる。その結果、発振ゲート回路部20の発振開始時における駆動能力不足による未発振を防ぎ、かつ、発振開始後の消費電力を抑制することが可能となる。

【0067】

(第4の実施形態)

図8は、本発明の第4の実施形態による半導体装置の構成を示す回路図である。本実施形態による半導体装置は、図2に示した本発明の第1の実施形態による半導体装置に、以下の変更を加えたものに等しい。すなわち、検知回路部46と、第1、第2のセレクタ回路部44、45と、第3のNMOSトランジスタ6aと、第3のPMOSトランジスタ8aと、合計6個のノード11a、11b、11c、12a、12b、12cを追加する。ここで、検知回路部46は、入力部と、第1、第2の入力部とを具備している。また、第1、第2のセレクタ回路部44、45のそれぞれは、第1〜第3の入力部と、出力部と、制御信号入力部とを具備している。

【0068】

本実施形態による半導体装置の構成要素の接続関係について説明する。第3のNMOSトランジスタ6aは、第1のNMOSトランジスタ5と、第2のNMOSトランジスタ6との間に、直列に接続されている。すなわち、第3のNMOSトランジスタ6aのドレインは、第1のNMOSトランジスタ5のソースに接続されており、第3のNMOSトランジスタ6aのソースは、第2のNMOSトランジスタ6のドレインに接続されている。さらに、第3のNMOSトランジスタ6aのゲートは、第3のNMOSトランジスタ6aのドレインと、第1のNMOSトランジスタ5のソースとに共通接続されている。第3のNMOSトランジスタ6aのバックゲートは、接地されている。

【0069】

第3のPMOSトランジスタ8aは、第1のPMOSトランジスタ7と、第2のPMOSトランジスタ8との間に、直列に接続されている。すなわち、第3のPMOSトランジスタ8aのドレインは、第1のPMOSトランジスタ7のソースに接続されており、第3のPMOSトランジスタ8aのソースは、第2のPMOSトランジスタ8のドレインに接続されている。さらに、第3のPMOSトランジスタ8aのゲートは、第3のPMOSトランジスタ8aのドレインと、第1のPMOSトランジスタ7のソースとに共通接続されている。第3のPMOSトランジスタ8aのバックゲートは、第3のPMOSトランジスタ8aのソースと、第2のPMOSトランジスタ8におけるゲートおよびドレインとに、共通接続されている。

【0070】

検知回路部46の入力部は、発振ゲート回路部20の出力部に接続されている。検知回路部46における第1の出力部は、第1のセレクタ回路部44の制御信号入力部に接続されている。検知回路部46における第2の出力部は、第2のセレクタ回路部45の制御信号入力部に接続されている。第1のセレクタ回路部44における第1の入力部は、ノード11aに接続されている。第1のセレクタ回路部44における第2の入力部は、ノード11bに接続されている。第1のセレクタ回路部44における第3の入力部は、ノード11cに接続されている。第2のセレクタ回路部45における第1の入力部は、ノード12aに接続されている。第2のセレクタ回路部45における第2の入力部は、ノード12bに接続されている。第2のセレクタ回路部45における第3の入力部は、ノード12cに接続されている。第1のセレクタ回路部44の出力部は、ノード11に接続されている。第2のセレクタ回路部45の出力部は、ノード12に接続されている。

【0071】

ノード11aは、電源VDDと、第1のNMOSトランジスタ5におけるドレインおよびゲートとに共通接続されている。ノード11bは、第1のNMOSトランジスタ5のソースと、第3のNMOSトランジスタ6aにおけるドレインおよびソースとに共通接続されている。ノード11cは、第3のNMOSトランジスタ6aのソースと、第2のNMOSトランジスタ6におけるドレインおよびゲートとに共通接続されている。

【0072】

ノード12aは、第2のPMOSトランジスタ8におけるソースおよびゲートと、第3のPMOSトランジスタ8aにおけるソースおよびバックゲートとに共通接続されている。ノード12bは、第1のPMOSトランジスタ7におけるソースおよびバックゲートと、第3のPMOSトランジスタ8aにおけるドレインおよびゲートとに共通接続されている。ノード12cは、第1のPMOSトランジスタ7におけるドレインおよびゲートと、第1〜第3のNMOSトランジスタ5、6、6aのそれぞれにおけるバックゲートとに共通接続されており、かつ、接地されている。

【0073】

図8に示した本実施形態による半導体装置のその他の構成は、図2に示した本発明の第1の実施形態による半導体装置の場合と同様であるので、さらなる詳細な説明を省略する。

【0074】

図8に示した本実施形態による半導体装置の動作について説明する。まず、振幅制御回路部10は、直列に接続されたMOSトランジスタの総数が増えているものの、基本的には本発明の第1〜第3の実施形態の場合と同様に動作する。すなわち、振幅制御回路部10は、電源電圧VDDと、MOSトランジスタ5、6、6a、7、8、8aのスレッショルド電圧Vt5、Vt6、Vt6a、Vt7、Vt8、Vt8aの比率とに応じた電圧を、ノード11a、11b、11c、12a、12b、12cからそれぞれ出力する。

【0075】

より具体的には、ノード11aの電圧V11a、ノード11bの電圧V11b、ノード11cの電圧V11c、ノード12aの電圧V12a、ノード12bの電圧V12b、ノード12cの電圧V12cは、次の式のように求められる。

V11a=VDD

V11b=VDD×(Vt6+Vt6a+Vt7+Vt8+Vt8a)/ΣVt

V11c=VDD×(Vt6+Vt7+Vt8+Vt8a)/ΣVt

V12a=VDD×(Vt7+Vt8a)/ΣVt

V12b=VDD×(Vt7)/ΣVt

V12c=0

ただし、

ΣVt=Vt5+Vt6+Vt6a+Vt7+Vt8+Vt8a

とする。ここで、例えば、電圧V11bは、電圧11aと、電圧11cとの中間程度であり、電圧V12bは、電圧12aと、電圧12cとの中間程度であるものとする。

【0076】

次に、検知回路部46は、発振ゲート回路部20が出力する電圧の振幅に基づいて第1、第2の制御信号を生成する。第1のセレクタ回路部44は、第1の制御信号に基づいて、ノード11a、11b、11cからいずれか1つを選択してノード11に接続する。同様に、第2のセレクタ回路部45は、第2の制御信号に基づいて、ノード12a、12b、12cからいずれか1つを選択してノード12に接続する。

【0077】

本実施形態による半導体装置の初期状態では、すなわち発振ゲート回路部20の発振が開始する直前までは、第1のセレクタ回路部44がノード11aをノード11に接続するような第1の制御信号を、検知回路部46が生成するものとする。同様に、初期状態では、第2のセレクタ回路部45がノード12cをノード12に接続するような第2の制御信号を、検知回路部46が生成するものとする。こうすることで、図7に示した本発明の第3の実施形態の場合と同様に、発振ゲート回路部20に対して、電源電圧VDDにほぼ等しい電圧を供給することが出来る。すなわち、発振ゲート回路部20が高い電圧を供給されることで、発振の開始をより確実にすることが出来る。

【0078】

本実施形態による半導体装置の発振安定状態では、すなわち発振ゲート回路部20の発振が安定して持続している間は、第1のセレクタ回路部44がノード11cをノード11に接続するような第1の制御信号を、検知回路部46が生成するものとする。同様に、定常状態では、第2のセレクタ回路部45がノード12aをノード12に接続するような第2の制御信号を、検知回路部46が生成するものとする。こうすることで、本発明の他の実施形態の場合と同様に、発振ゲート回路部20に供給する電圧を削減することが可能となる。

【0079】

さらに、本実施形態の特徴として、電源電圧VDDが何らかの原因によって降下するなどして、発振ゲート回路部20が出力する電圧の振幅が減少した発振不安定状態では、発振ゲート回路部20に供給する電圧を一時的に上昇させることが可能である。発振不安定状態では、第1のセレクタ回路部44がノード11bノード11に接続するような第1の制御信号を、検知回路部46が生成するものとする。同様に、発振不安定状態では、第2のセレクタ回路部45がノード12bをノード12に接続するような第2の制御信号を、検知回路部46が生成するものとする。こうすることで、発振ゲート回路部20への供給電圧をなるべく節約しつつ、半導体装置を発振安定状態に戻すことが可能となる。

【0080】

なお、本実施形態による振幅制御回路部10は、合計6個のMOSトランジスタを直列に接続して具備しているが、これらMOSトランジスタの総数は本発明を限定するものではない。これらのMOSトランジスタの総数をさらに増やし、ノード11、ノード12に印加する電圧をさらに細かく制御しても良い。こうすることで、発振ゲート回路部20の安定性を確保しながら、必要最小限な供給電圧の値をさらに柔軟に制御することが可能となる。

【0081】

以上に説明した、本発明による第1〜第4の実施形態による半導体装置の特徴は、技術的に矛盾しない範囲において、自由に組み合わせることが可能である。

【符号の説明】

【0082】

1 PMOSトランジスタ

2 NMOSトランジスタ

3 帰還抵抗

4 振動子

5 NMOSトランジスタ

6 NMOSトランジスタ

6a NMOSトランジスタ

7 PMOSトランジスタ

8 PMOSトランジスタ

8a PMOSトランジスタ

10 振幅制御回路部

11 ノード

11a〜11c ノード

12 ノード

12a〜12c ノード

20 発振ゲート回路部

36 制御回路部

37 PMOSトランジスタ

38 インバータ回路部

39 NMOSトランジスタ

40 セレクタ回路部

42、43 レイアウト

44 セレクタ回路部

45 セレクタ回路部

46 検知回路部

61〜64 レイアウト

71 半導体装置

72 半導体装置

73 回路部

74 回路部

101 PMOSトランジスタ

102 NMOSトランジスタ

103 帰還抵抗

104 振動子

107 PMOSトランジスタ

108 NMOSトランジスタ

109 振幅増幅回路

111 PMOSトランジスタ

112 NMOSトランジスタ

120 発振ゲート回路部

130 ダイオード

131 ダイオード

132 PMOSトランジスタ

133 NMOSトランジスタ

134 電流源

135 電流源

151 振幅制御回路

152 振幅制御回路

C1 入力側コンデンサ

C2 出力側コンデンサ

C101 入力側コンデンサ

C102 出力側コンデンサ

VCC 電源

VDD 電源

【特許請求の範囲】

【請求項1】

第1の電源電圧を供給する第1の電源部(VDD)と、

第2の電源電圧を供給する第2の電源部(GND)と、

前記第1および前記第2の電源電圧(VDD、GND)を入力して第1および第2の供給電圧(V11、V12)を生成する振幅制御回路部(10)と、

第1および第2の入力部(11、12)から前記第1および前記第2の供給電圧(V11、V12)をそれぞれ入力して発振する発振回路部(20、3、4、C1、C2)と

を具備し、

前記振幅制御回路部(10)は、

前記第1および前記第2の電源部(VDD、GND)の間に直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタ(5〜8)と、

前記複数のMOSトランジスタ(5〜8)のドレインまたはソースに接続されて、前記第1の供給電圧(V11)を出力する第1の出力部(11)と、

前記複数のMOSトランジスタ(5〜8)の他のドレインまたは他のソースに接続されて、前記第2の供給電圧(V12)を出力する第2の出力部(12)と

を具備する

半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記複数のMOSトランジスタ(5〜8)のうち、少なくとも1つのMOSトランジスタにおいて、バックゲートがソースに接続されている

半導体装置。

【請求項3】

請求項1に記載の半導体装置において、

前記複数のMOSトランジスタ(5〜8)は、

前記第1の電源部(VDD)に接続された第1のNMOSトランジスタ(5)と、

前記第2の電源部(GND)に接続された第1のPMOSトランジスタ(7)と、

前記第1のNMOSトランジスタ(5)と、前記第1のPMOSトランジスタとの間に接続されて、かつ、前記第1の出力部に接続された第2のNMOSトランジスタ(6)と、

前記第1のPMOSトランジスタ(7)と、前記第2のNMOSトランジスタとの間に接続されて、かつ、前記第2の出力部に接続された第2のPMOSトランジスタ(8)と

を具備し、

前記第1および前記第2のNMOSトランジスタ(5、6)のそれぞれにおいて、バックゲートは前記第2の電源部(GND)に接続されており、

前記第1のPMOSトランジスタ(7)において、バックゲートは前記第1の電源部(VDD)に接続されており、

前記第2のPMOSトランジスタ(8)において、バックゲートはソースに接続されている

半導体装置。

【請求項4】

請求項1に記載の半導体装置において、

前記複数のMOSトランジスタ(5〜8)は、

前記第1の電源部(VDD)に接続された第1のNMOSトランジスタ(5)と、

前記第2の電源部(GND)に接続された第1のPMOSトランジスタ(7)と、

前記第1のNMOSトランジスタ(5)と、前記第1のPMOSトランジスタとの間に接続されて、かつ、前記第1の出力部に接続された第2のNMOSトランジスタ(6)と、

前記第1のPMOSトランジスタ(7)と、前記第2のNMOSトランジスタとの間に接続されて、かつ、前記第2の出力部に接続された第2のPMOSトランジスタ(8)と

を具備し、

前記第1および前記第2のPMOSトランジスタ(7、8)のそれぞれにおいて、バックゲートは前記第1の電源部(VDD)に接続されており、

前記第1のNMOSトランジスタ(5)において、バックゲートは前記第2の電源部(GND)に接続されており、

前記第2のNMOSトランジスタ(6)において、バックゲートはソースに接続されている

半導体装置。

【請求項5】

請求項1または2に記載の半導体装置において、

前記発振回路部の発振が安定するまでは前記第1の電源電圧を前記第1の入力部に供給し、かつ、前記発振が安定している間は前記第1の供給電圧を前記第1の入力部に供給する第1のスイッチ回路部(37)と、

前記発振が安定するまでは前記第2の電源電圧を前記第2の入力部に供給し、かつ、前記発振が安定している間は前記第2の供給電圧を前記第2の入力部に供給する第2のスイッチ回路部(37)と

をさらに具備する

半導体装置。

【請求項6】

請求項3または4に記載の半導体装置において、

前記発振回路部の後段に接続されて、前記発振回路部の発振が安定するまでは第1状態の制御信号を生成し、かつ、前記発振が安定している間は第2状態の前記制御信号を生成する制御回路(36)と、

前記制御信号が第1状態である場合に前記第1の電源部を前記第1の入力部に接続し、かつ、前記制御信号が第2状態である場合に前記第1の出力部を前記第1の入力部に接続する第1のスイッチ回路部(37)と、

前記制御信号が第1状態である場合に前記第2の電源部を前記第2の入力部に接続し、かつ、前記制御信号が第2状態である場合に前記第2の出力部を前記第2の入力部に接続する第2のスイッチ回路部(38)と

をさらに具備する

半導体装置。

【請求項7】

請求項5に記載の半導体装置において、

前記振幅制御回路部10は、

前記第1の電源電圧と、前記第1の供給電圧との間にある第3の供給電圧を出力する第3の出力部と、

前記第2の電源電圧と、前記第2の供給電圧との間にある第4の供給電圧を出力する第4の出力部と

をさらに具備し、

前記第1のスイッチ回路部は、前記発振が不安定である場合に前記第3の供給電圧を前記第1の入力部に供給し、

前記第2のスイッチ回路部は、前記発振が不安定である場合に前記第4の供給電圧を前記第2の入力部に供給する

半導体装置。

【請求項8】

請求項3または4に記載の半導体装置において、

前記振幅制御回路部10は、

前記第1のNMOSトランジスタ(5)と、前記第2のNMOSトランジスタ(6)との間に接続された第3のNMOSトランジスタ(6a)と、

前記第3のNMOSトランジスタ(6a)に接続された第3の出力部と、

前記第1のPMOSトランジスタ(7)と、前記第2のPMOSトランジスタ(8)との間に接続された第3のPMOSトランジスタ(8a)と、

前記第3のPMOSトランジスタ(8a)に接続された第4の出力部と

をさらに具備し、

前記発振回路部の後段に接続されて、前記発振回路部の発振が安定するまでは第1状態の第1制御信号および第1状態の第2制御信号を生成し、前記発振が安定している間は第2状態の前記第1制御信号および第2状態の前記第2制御信号を生成し、かつ、前記発振が不安定である場合は第3状態の前記第1制御信号および第3状態の前記第2制御信号を生成する制御回路(46)と、

前記第1制御信号が前記第1状態である場合に前記第1の電源部を前記第1の入力部に接続し、前記第1制御信号が前記第2状態である場合に前記第1の出力部を前記第1の入力部に接続し、かつ、前記第1制御信号が前記第3状態である場合に前記第3の出力部を前記第1の入力部に接続する第1のセレクタ回路部と、

前記第2制御信号が前記第1状態である場合に前記第2の電源部を前記第2の入力部に接続し、前記第2制御信号が前記第2状態である場合に前記第2の出力部を前記第2の入力部に接続し、かつ、前記第2制御信号が前記第3状態である場合に前記第4の出力部を前記第2の入力部に接続する第2のセレクタ回路部と

をさらに具備する

半導体装置。

【請求項1】

第1の電源電圧を供給する第1の電源部(VDD)と、

第2の電源電圧を供給する第2の電源部(GND)と、

前記第1および前記第2の電源電圧(VDD、GND)を入力して第1および第2の供給電圧(V11、V12)を生成する振幅制御回路部(10)と、

第1および第2の入力部(11、12)から前記第1および前記第2の供給電圧(V11、V12)をそれぞれ入力して発振する発振回路部(20、3、4、C1、C2)と

を具備し、

前記振幅制御回路部(10)は、

前記第1および前記第2の電源部(VDD、GND)の間に直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタ(5〜8)と、

前記複数のMOSトランジスタ(5〜8)のドレインまたはソースに接続されて、前記第1の供給電圧(V11)を出力する第1の出力部(11)と、

前記複数のMOSトランジスタ(5〜8)の他のドレインまたは他のソースに接続されて、前記第2の供給電圧(V12)を出力する第2の出力部(12)と

を具備する

半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記複数のMOSトランジスタ(5〜8)のうち、少なくとも1つのMOSトランジスタにおいて、バックゲートがソースに接続されている

半導体装置。

【請求項3】

請求項1に記載の半導体装置において、

前記複数のMOSトランジスタ(5〜8)は、

前記第1の電源部(VDD)に接続された第1のNMOSトランジスタ(5)と、

前記第2の電源部(GND)に接続された第1のPMOSトランジスタ(7)と、

前記第1のNMOSトランジスタ(5)と、前記第1のPMOSトランジスタとの間に接続されて、かつ、前記第1の出力部に接続された第2のNMOSトランジスタ(6)と、

前記第1のPMOSトランジスタ(7)と、前記第2のNMOSトランジスタとの間に接続されて、かつ、前記第2の出力部に接続された第2のPMOSトランジスタ(8)と

を具備し、

前記第1および前記第2のNMOSトランジスタ(5、6)のそれぞれにおいて、バックゲートは前記第2の電源部(GND)に接続されており、

前記第1のPMOSトランジスタ(7)において、バックゲートは前記第1の電源部(VDD)に接続されており、

前記第2のPMOSトランジスタ(8)において、バックゲートはソースに接続されている

半導体装置。

【請求項4】

請求項1に記載の半導体装置において、

前記複数のMOSトランジスタ(5〜8)は、

前記第1の電源部(VDD)に接続された第1のNMOSトランジスタ(5)と、

前記第2の電源部(GND)に接続された第1のPMOSトランジスタ(7)と、

前記第1のNMOSトランジスタ(5)と、前記第1のPMOSトランジスタとの間に接続されて、かつ、前記第1の出力部に接続された第2のNMOSトランジスタ(6)と、

前記第1のPMOSトランジスタ(7)と、前記第2のNMOSトランジスタとの間に接続されて、かつ、前記第2の出力部に接続された第2のPMOSトランジスタ(8)と

を具備し、

前記第1および前記第2のPMOSトランジスタ(7、8)のそれぞれにおいて、バックゲートは前記第1の電源部(VDD)に接続されており、

前記第1のNMOSトランジスタ(5)において、バックゲートは前記第2の電源部(GND)に接続されており、

前記第2のNMOSトランジスタ(6)において、バックゲートはソースに接続されている

半導体装置。

【請求項5】

請求項1または2に記載の半導体装置において、

前記発振回路部の発振が安定するまでは前記第1の電源電圧を前記第1の入力部に供給し、かつ、前記発振が安定している間は前記第1の供給電圧を前記第1の入力部に供給する第1のスイッチ回路部(37)と、

前記発振が安定するまでは前記第2の電源電圧を前記第2の入力部に供給し、かつ、前記発振が安定している間は前記第2の供給電圧を前記第2の入力部に供給する第2のスイッチ回路部(37)と

をさらに具備する

半導体装置。

【請求項6】

請求項3または4に記載の半導体装置において、

前記発振回路部の後段に接続されて、前記発振回路部の発振が安定するまでは第1状態の制御信号を生成し、かつ、前記発振が安定している間は第2状態の前記制御信号を生成する制御回路(36)と、

前記制御信号が第1状態である場合に前記第1の電源部を前記第1の入力部に接続し、かつ、前記制御信号が第2状態である場合に前記第1の出力部を前記第1の入力部に接続する第1のスイッチ回路部(37)と、

前記制御信号が第1状態である場合に前記第2の電源部を前記第2の入力部に接続し、かつ、前記制御信号が第2状態である場合に前記第2の出力部を前記第2の入力部に接続する第2のスイッチ回路部(38)と

をさらに具備する

半導体装置。

【請求項7】

請求項5に記載の半導体装置において、

前記振幅制御回路部10は、

前記第1の電源電圧と、前記第1の供給電圧との間にある第3の供給電圧を出力する第3の出力部と、

前記第2の電源電圧と、前記第2の供給電圧との間にある第4の供給電圧を出力する第4の出力部と

をさらに具備し、

前記第1のスイッチ回路部は、前記発振が不安定である場合に前記第3の供給電圧を前記第1の入力部に供給し、

前記第2のスイッチ回路部は、前記発振が不安定である場合に前記第4の供給電圧を前記第2の入力部に供給する

半導体装置。

【請求項8】

請求項3または4に記載の半導体装置において、

前記振幅制御回路部10は、

前記第1のNMOSトランジスタ(5)と、前記第2のNMOSトランジスタ(6)との間に接続された第3のNMOSトランジスタ(6a)と、

前記第3のNMOSトランジスタ(6a)に接続された第3の出力部と、

前記第1のPMOSトランジスタ(7)と、前記第2のPMOSトランジスタ(8)との間に接続された第3のPMOSトランジスタ(8a)と、

前記第3のPMOSトランジスタ(8a)に接続された第4の出力部と

をさらに具備し、

前記発振回路部の後段に接続されて、前記発振回路部の発振が安定するまでは第1状態の第1制御信号および第1状態の第2制御信号を生成し、前記発振が安定している間は第2状態の前記第1制御信号および第2状態の前記第2制御信号を生成し、かつ、前記発振が不安定である場合は第3状態の前記第1制御信号および第3状態の前記第2制御信号を生成する制御回路(46)と、

前記第1制御信号が前記第1状態である場合に前記第1の電源部を前記第1の入力部に接続し、前記第1制御信号が前記第2状態である場合に前記第1の出力部を前記第1の入力部に接続し、かつ、前記第1制御信号が前記第3状態である場合に前記第3の出力部を前記第1の入力部に接続する第1のセレクタ回路部と、

前記第2制御信号が前記第1状態である場合に前記第2の電源部を前記第2の入力部に接続し、前記第2制御信号が前記第2状態である場合に前記第2の出力部を前記第2の入力部に接続し、かつ、前記第2制御信号が前記第3状態である場合に前記第4の出力部を前記第2の入力部に接続する第2のセレクタ回路部と

をさらに具備する

半導体装置。

【図1】

【図2】

【図3A】

【図3B】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3A】

【図3B】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−62755(P2013−62755A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−201303(P2011−201303)

【出願日】平成23年9月15日(2011.9.15)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月15日(2011.9.15)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]