半導体装置

【課題】フリップチップ実装の半導体装置において、パッケージ外部の設計を変更せずに、特定の端子の電位を変更できる半導体装置を提供する。

【解決手段】本発明の半導体装置は、外部端子にバンプを備えるICチップと、前記ICチップを搭載するパッケージとを備え、前記パッケージは、前記外部端子に第1の信号又は第2の信号を印加するインナーリード部を備える。前記インナーリード部は、前記ICチップの搭載位置により、前記外部端子に印加する信号を、前記第1の信号又は前記第2の信号に変更可能なインナーリードのパターンを有する。

【解決手段】本発明の半導体装置は、外部端子にバンプを備えるICチップと、前記ICチップを搭載するパッケージとを備え、前記パッケージは、前記外部端子に第1の信号又は第2の信号を印加するインナーリード部を備える。前記インナーリード部は、前記ICチップの搭載位置により、前記外部端子に印加する信号を、前記第1の信号又は前記第2の信号に変更可能なインナーリードのパターンを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、チップの外部端子がバンプである半導体装置に関する。

【背景技術】

【0002】

半導体装置において、一部の入力端子(制御端子)を、Hi、又はLoに設定することにより、動作モードを切り替えて使用できるものが知られている。このような半導体装置は、1つのIC(Integrated Circuit)チップで、ユーザに合わせた機能を切り替えて使用できるため、ICチップの開発コストを抑えることができる。

【0003】

一般に、ICチップの特定の端子をHi、又はLoに設定するためには、その端子を半導体装置のパッケージの外部端子にして電位を設定する。外部端子に、Hi、又はLoの電位を供給する方法は、半導体装置に接続する接続基板で電位を設定する方法、又は、接続基板上の他のデバイスで電位を設定する方法がある。例えば、半導体装置が、LCD(Liquid Crystal Display)表示装置の場合には、タイミングコントローラに接続する。これらの方法は、ユーザの機能に合わせた異なるICチップの開発に比べれば、接続基板の変更、又は接続基板上の他のデバイスの設定変更であるため、開発コストは安価になり、開発期間は短期間になる。しかし、接続基板の変更、又は接続基板上の他のデバイスの設定変更を、半導体装置メーカーの半導体装置の製造上の都合で、ユーザ側に強いることはできない。そのため、半導体装置メーカーでは、半導体装置のパッケージングの段階で、特定の端子の電位を切り替えることにより、半導体装置外部での設定変更を不要にする試みがなされている。

【0004】

本発明の分野における文献公知発明としては、特開2003−152009号公報(特許文献1)、及び特開平6−97319号公報(特許文献2)がある。

【0005】

図1は、特許文献1の半導体装置を説明するための図である。特開2003−152009号公報(特許文献1)では、2つのリード103a、103cをチップ下で延在し、制御端子101、102の接続先を、延在した先の端子にワイヤーボンディングする(図1(A))か、延在元の端子にワイヤーボンディングする(図1(B))かを切り替えることができる発明が開示されている。この発明によれば、同一チップ、同一パターンの半導体装置に対して、ボンディング位置のみで、半導体装置の動作モードを変更することができる。

【0006】

図2は、特許文献2の半導体装置を説明するための図である。特開平6−97319号公報(特許文献2)では、チップ111の搭載領域周辺に相互に絶縁された帯状の導体片(補助リード)113a、113bが配置されている。外部端子123は、チップ111の左下領域に最も近い位置にあるが、外部端子123から伸びたインナーリード113から補助リード113aに接続(ボンディング)し、補助リード113aからワイヤ115により、チップ111の右上の領域のパッドにボンディングできる。また、外部端子126は、チップ111の右上領域に最も近い位置にあるが、補助リード113bにボンディングすることで、補助リード113bを通して、チップ左下の領域のパッドにボンディングできる。この発明によれば、半導体チップのボンディングパッド配列に関係なく、パッケージのピン配列を設定することができる。

【0007】

このような従来技術は、ワイヤーボンディングが必須であるため、ワイヤーの分だけパッケージの厚さが厚くなり、厚さの薄いパッケージに適用することができない。例えば、厚さが薄いパッケージの代表であるTAB(Tape Automated Bonding)パッケージでは、ICチップ上に設けられた突起電極(バンプ)と、テープ上の端子とを直接接続(フリップチップボンディング)するため、ボンディングワイヤーで接続を切り替える従来技術を適用することができない。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−152009号公報

【特許文献2】特開平6−97319号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

フリップチップ実装の半導体装置において、パッケージ外部の設計を変更せずに、特定の端子に与える信号を変更できる半導体装置が求められている。

【課題を解決するための手段】

【0010】

上記の課題を解決するために、本発明は、以下に述べられる手段を採用する。その手段を構成する技術的事項の記述には、[特許請求の範囲]の記載と[発明を実施するための形態]の記載との対応関係を明らかにするために、[発明を実施するための形態]で使用される番号・符号が付加されている。ただし、付加された番号・符号は、[特許請求の範囲]に記載されている発明の技術的範囲を限定的に解釈するために用いてはならない。

【0011】

本発明の半導体装置は、外部端子にバンプを備えるICチップ(1)と、前記ICチップを搭載するパッケージ(2)とを備え、前記パッケージ(2)は、前記外部端子に第1の信号又は第2の信号を印加するインナーリード部(25)を備える。前記インナーリード部(25)は、前記ICチップ(1)の搭載位置により、前記外部端子に印加する信号を、前記第1の信号又は前記第2の信号に変更可能なインナーリードのパターンを有する。

【発明の効果】

【0012】

本発明によれば、フリップチップ実装の半導体装置において、パッケージ外部の設計を変更せずに、特定の端子に与える信号を変更できる半導体装置を提供することができる。

【図面の簡単な説明】

【0013】

【図1】図1は、特許文献1の半導体装置を説明するための平面図である。

【図2】図2は、特許文献2の半導体装置を説明するための平面図である。

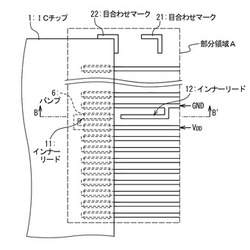

【図3】図3は、本発明の実施形態1における半導体装置の平面図である。

【図4A】図4Aは、インナーリード部25の部分領域Aの第1実施形態におけるインナーリードパターンの平面図である。

【図4B】図4Bは、図4Aに図示されたB−B’軸における部分領域AのB−B’断面図である。

【図5A】図5Aは、図4Aに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をVDDに接続した場合を説明するための図である。

【図5B】図5Bは、図4Bに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をVDDに接続した場合を説明するための図である。

【図6A】図6Aは、図4Aに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をGNDに接続した場合を説明するための図である。

【図6B】図6Bは、図4Bに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をGNDに接続した場合を説明するための図である。

【図7】図7は、図4Aのインナーリードパターンの変形例1である。

【図8】図8は、図4Aのインナーリードパターンの変形例2である。

【図9A】図9Aは、図3の部分領域Aの第2実施形態におけるインナーリードパターンの平面図である。

【図9B】図9Bは、図9Aのインナーリード11と接続されるICチップ1の入力端子の等価回路図である。

【図10】図10は、図3の部分領域Aの第3実施形態におけるインナーリードパターンの平面図である。

【図11】図11は、図4の部分領域Aの第4実施形態におけるインナーリードパターンの平面図である。

【図12】図12は、本発明の実施形態5における半導体装置の平面図である。

【図13A】図13Aは、本発明の実施形態5における半導体装置のパッケージ2の部分領域Eの平面図である。

【図13B】図13Bは、本発明の実施形態5における半導体装置のICチップ1の部分領域Eの平面図である。

【図14A】図14Aは、本発明の実施形態5における半導体装置の制御端子8を、目合わせマーク22に合わせることにより、Hi(VDD)に設定した場合の図である。

【図14B】図14Bは、本発明の実施形態5における半導体装置の制御端子8を、目合わせマーク21に合わせることにより、Lo(GND)に設定した場合の図である。

【発明を実施するための形態】

【0014】

(第1実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。

【0015】

はじめに、本実施形態における半導体装置の構成の説明を行う。

【0016】

図3は、本発明の実施形態における半導体装置の平面図である。本実施形態の半導体装置は、ICチップ1とパッケージ2とを備える。パッケージ2は、ICチップ1の保護、及びICチップ1と他の外部デバイスが搭載された接続基板とを電気的に接続する役割を持つ。パッケージ2は、外部端子として、複数の入力端子4、及び複数の出力端子5とを備える。パッケージ2内において、外部端子からリード3を介して、ICチップ1と他の外部デバイスが電気的に接続される。ICチップ1とリード3の接続は、ICチップの外部電極である突起電極(バンプ)と、ICチップ1と重なるリード3の部分(インナーリード部25)とを接続することにより行われる。一般に、バンプとインナーリードは、熱圧着等で接続される。その後、インナーリード部25とICチップ1下面の間に封止樹脂が流し込まれ、機械的にパッケージ2とICチップ1が接着されるとともに、外的環境から保護される。

【0017】

例えば、半導体装置が表示装置のドライバの場合には、入力端子4は、タイミングコントローラと呼ばれる外部デバイスや、電源を搭載する接続基板に接続し、出力端子5は、表示パネルに接続する。入力端子4には、ICチップ1の入力端子に接続するものや、ICチップ1の電源端子に電力を供給する電源端子がある。製品によっては、接続基板へ信号を出力する出力端子を含む場合がある。図3の半導体装置の例は、作図の都合で外部端子の本数が少ないが、例えば、半導体装置が表示装置のドライバである場合は、入力端子4は数十本から百本程度あり、出力端子5は数百本から千本を超えるものまである。

【0018】

本発明の実施形態では、パッケージ2の有するインナーリードのパターンが重要である。図4Aは、インナーリード部25の部分領域Aの第1実施形態におけるインナーリードパターンの平面図である。目合わせマーク21及び目合わせマーク22は、パッケージ2にICチップ1を搭載する際の位置合わせに使用するマークである。インナーリード11は、VDDに接続され、インナーリード12は、GNDに接続されている。インナーリード11の形状は、図4Aで図示されているように、インナーリードを2箇所で折り曲げ、B−B’軸に対し、B’方向へ折り返すことにより形成されている。インナーリード12の形状は、図4Aで図示されているように、分岐させたインナーリードを折り曲げて、B−B’軸に対して、B方向へ伸ばすことにより形成されている。インナーリード11とインナーリード12は、B−B’軸上において、対峙するように配線され、互いに絶縁されている。

【0019】

図4Bは、図4Aに図示されたB−B’軸における部分領域AのB−B’断面図である。パッケージ2の上面にインナーリードが積層してある。互いに絶縁されたインナーリードの左側がVDDに接続されるインナーリード11であり、右側がGNDに接続されるインナーリード12である。

【0020】

図5Aは、図4Aに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をVDDに接続した場合を説明するための図である。ICチップ1を、目合わせマーク22に合わせて配置することにより、ICチップ1の外部端子(制御端子)とインナーリード11を電気的に接続している。

【0021】

図5Bは、図4Bに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をVDDに接続した場合を説明するための図である。ICチップ1の制御端子と、VDDに接続されたインナーリード11とが、ICチップ1の制御端子上に形成されたバンプ6により電気的に接続されている。

【0022】

図6Aは、図4Aに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をGNDに接続した場合を説明するための図である。ICチップ1を、目合わせマーク21に合わせて配置することにより、ICチップ1の制御端子とインナーリード12を電気的に接続している。

【0023】

図6Bは、図4Bに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をGNDに接続した場合を説明するための図である。ICチップ1の制御端子と、GNDに接続されたインナーリード12とが、ICチップ1の制御端子上に形成されたバンプ6により電気的に接続されている。

【0024】

なお、図5A、図6Aに図示されているように、インナーリード11の折り曲げ部分は、バンプの接続位置よりICチップ1の内側にあり、インナーリード12の枝分かれ部分は、ICチップ1の外側にあるように設計されている。これは、封止樹脂を流し込んでICチップ1とパッケージ2を接着する際に、樹脂の流れを妨げないようにするためである。

【0025】

なお、目合わせマーク21、目合わせマーク22は、説明し易さを考慮し、ICチップ1の角に合わせる例で説明したが、実際には、ICチップ1の角はICチップ1をウェハーから切り出すダイシングの工程で、その位置に誤差を含む。そのため、インナーリードのピッチが細かい場合には、より精度の高い方法を採る。例えば、パッケージ2の基材が半透明のTABテープの場合は、ICチップ1及びパッケージ2に位置合わせ精度のよいマークを設置する。パッケージ2のICチップ1を搭載する面の裏面から、光学的にマーク同士を合わせることにより、より精度の高い位置合わせを行うことができる。また、目合わせマークは、図4Aのように、ICチップ1上の1つの角だけでなく、対角線上等の他の位置にも設置し、回転方向の位置合わせ精度を上げてもよい。また、特別な目合わせマークを使用せずに、インナーリードとバンプの接続状況を、直接光学的に観測することにより位置を合わせてもよい。

【0026】

なお、図3のICチップ1の短辺のバンプに接続しているインナーリードは、ICチップ1を、どちらの目合わせマークに合わせても、同じバンプに接続できるようにしておく必要がある。例えば、短辺のバンプに接続しているインナーリードに、ICチップ1の短辺に平行に、目合わせマーク0と目合わせマーク1の間隔以上の長さのバンプとの接続部分を持たせる。または、後に本発明の実施形態5(図13A〜14B)で述べるインナーリード17及びインナーリード19のように、目合わせマーク0に合わせた時の接続部分と、目合わせマーク1に合わせた時の接続部分の両方を、同じリードに接続するようにする方法等が考えられる。

【0027】

本実施形態の半導体装置によれば、同一のICチップ1とパッケージ2とをフリップチップ接続する場合でも、ICチップ1と合わせる目合わせマークを変えることで、特定の入力端子(制御端子)の電位をHi(VDD)、又はLo(GND)に設定することができる。これにより、ICチップ1が、2つの動作モードを持つ場合に、動作モードをパッケージングの段階で選択でき、短期間で、複数種類の半導体装置を製造することができる。また、ICチップ1及びパッケージ2が同一のため、これらの製造コストをより小さくし、量産効果によるコストダウンを実現することができる。

【0028】

なお、本実施形態の半導体装置の効果は、図4Bの断面構造があれば得ることができるため、図4Aのインナーリードのパターンに限定されるものではない。

【0029】

図7は、図4Aのインナーリードパターンの変形例1である。インナーリード11は、VDDに接続され、インナーリード12は、GNDに接続されている。インナーリード11の形状は、図7に図示されているように、分岐させたインナーリードを、B−B’軸に対して、B方向へ伸ばすことにより形成されている。インナーリード12の形状は、図7に図示されているように、分岐させたインナーリードを折り曲げて、B−B’軸に対して、B方向へ伸ばし、分岐元のインナーリード方向に、再度、折り曲げて合流させることにより形成されている(ループ形状)。インナーリード部25とICチップ1下面の間の封止樹脂の流れを横切るインナーリードの配線が問題にならない場合は、このような形状で設計することも可能である。

【0030】

図8は、図4Aのインナーリードパターンの変形例2である。インナーリード11は、VDDに接続され、インナーリード12は、GNDに接続されている。インナーリードの幅を広げることで、インナーリード11とインナーリード12を形成し、B−B’軸において、インナーリード11とインナーリード12を対峙させている。

【0031】

部分領域Aが、図7及び図8のようなインナーリードのパターンを有していても、図4Bの断面構造となるため、本実施形態の半導体装置の効果を得ることができる。

【0032】

(第2実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。本実施形態における半導体装置の構成は、第1実施形態の図3と同様であるため、説明を省略する。

【0033】

図9Aは、図3の部分領域Aの第2実施形態におけるインナーリードパターンの平面図である。インナーリード11は、オープン状態になる入力端子4の制御端子のバンプ6を接続するためのダミー用のリードである。インナーリード12は、GNDに接続されている。インナーリード12の形状は、第1実施形態の図4Aのインナーリード12と同様である。

【0034】

本実施形態の半導体装置では、ICチップ1を目合わせマーク22に合わせた場合は、インナーリード11に接続されるバンプに対応する、ICチップ1の制御端子がオープン状態になる。そのため、ICチップ1の制御端子をVDDにプルアップし、Hi(VDD)に設定する。図9Bは、図9Aのインナーリード11と接続されるICチップ1の入力端子(制御端子)の等価回路図である。図9Bの等価回路は、ESD(Electro−Static Discharge)保護回路31、プルアップ抵抗32及びバッファ33を備える。オープン状態となるICチップ1の制御端子は、VDDに接続されたプルアップ抵抗32と接続され、入力信号がHi(VDD)に設定される。

【0035】

本実施形態の半導体装置では、ICチップ1を目合わせマーク21に合わせた場合は、図6Aと同様に、ICチップ1の制御端子のバンプは、GNDであるインナーリード12に接続される。この場合、バッファ33の入力端子には、VDDに接続するプルアップ抵抗32とESD保護素子31を介してGNDに接続する制御端子との分圧によって発生する電圧レベルが印加される。ESD保護素子31の直流抵抗は、プルアップ抵抗32の直流抵抗に対して十分に小さいため、ほぼGNDに近いロー(Lo)レベルの電圧が印加されることになる。

【0036】

このように、本発明の第2実施形態でもICチップの搭載位置によって外部端子に印加する信号を変更することが可能になる。

【0037】

なお、インナーリード11は制御端子をインナーリード12に接続した時は、電圧を設定しないオープンの状態でパッケージ2上に存在することになる。ICチップをパッケージ2に搭載する際に問題が無ければ、インナーリード11を具備しない構成にすることで、制御端子のバンプがどこにも接続しない状態になるようにしても構わない。というのも、インナーリードのようにパターン間の間隔が最小寸法であるところに電圧を設定しない配線パターンがあると、表示装置のESD耐量を弱くしてしまうことがあるからである。

【0038】

なお、図9A及び図9Bにおいて、インナーリード11に接続した際にオープン状態となるICチップ1の制御端子を、VDDに接続したプルダウン抵抗32の代わりに、GNDに接続されたプルダウン抵抗に接続して、入力信号をLo(GND)に設定してもよい。その場合には、インナーリード12をVDDに接続し、目合わせマーク21又は目合わせマーク22の選択により、ICチップ1の制御端子の電位をHi(VDD)、又はLo(GND)に切り替える。

【0039】

第2実施形態の半導体装置では、第1実施形態とは異なり、動作モードの変更のために必要となるインナーリードは、Hi(VDD)、又はLo(GND)のいずれか一方に接続されていればよい。そのため、第2実施形態の半導体装置によれば、VDDに接続されたインナーリードと、GNDに接続されたインナーリードを、並べて配置する必要がなく、外部端子の位置をより自由に設計することができる。

【0040】

(第3実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。本実施形態における半導体装置の構成は、第1実施形態の図3と同様であるため、説明を省略する。

【0041】

図10は、図3の部分領域Aの第3実施形態におけるインナーリードパターンの平面図である。本実施形態の半導体装置では、目合わせマークが3つ存在する点が、第1実施形態の半導体装置とは異なる。図10に図示されているように、本実施形態の半導体装置のインナーリードのパターンでは、第1実施形態のインナーリード11とインナーリード12との間に、インナーリード13が追加されている。また、インナーリード13にバンプを合わせるための目合わせマーク23が追加されている。インナーリード11は、VDDに接続される。インナーリード12は、GNDに接続される。インナーリード13は、ICチップ1に対する制御信号を送信するための電極に接続される。インナーリード11、インナーリード12及びインナーリード13は、図10に図示されているように、B−B’軸上に配線され、互いに絶縁されている。

【0042】

ICチップ1を目合わせマーク21に合わせた場合は、第1実施形態の半導体装置と同様に、外部端子(制御端子)は、Lo(GND)に設定される。ICチップ1を目合わせマーク22に合わせた場合は、第1実施形態の半導体装置と同様に、外部端子は、Hi(VDD)に設定される。ICチップ1を目合わせマーク23に合わせた場合は、制御信号を外部から与えることにより、外部端子の論理値を外部から切り替えることができる。

【0043】

本実施形態の半導体装置によれば、インナーリード13を介して、外部からの制御信号により、ICチップ1の動作モードを容易に変更することができる。これにより、同一のICチップ1とパッケージ2の組み合わせによる半導体製品を、ICチップ1の2つの動作モードのどちらか一方を必要とするカスタマ、および2つのモードを使い分けるカスタマの3者に提供することができる。

【0044】

(第4実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。本実施形態における半導体装置の構成は、第1実施形態の図3と同様であるため、説明を省略する。

【0045】

図11は、図4の部分領域Aの第4実施形態におけるインナーリードパターンの平面図である。本実施形態の半導体装置では、目合わせマークが4つ存在し、2つの外部端子(制御端子)の信号の組み合わせを切り替えることができる点が、他の実施形態とは異なる。インナーリード14a〜14cは、VDDに接続された1本のインナーリードを、図11に図示されているように分岐させることにより形成されている。インナーリード15は、GNDに接続されたインナーリードを、図11に図示されているように分岐させることにより形成されている。インナーリード16a、16bは、図11に図示されているように、GNDに接続されたインナーリードを2箇所で分岐させることにより形成されている。インナーリード15、インナーリード14bは、図11に図示されているように、C−C’軸上に配線され、互いに絶縁されている。インナーリード16a、インナーリード14a、インナーリード16b及びインナーリード14cは、図11に図示されているように、D−D’軸上に配線され、互いに絶縁されている。

【0046】

ICチップ1を目合わせマーク21に合わせた場合は、インナーリード15に接続される外部端子は、Lo(GND)に設定され、インナーリード16aに接続される外部端子は、Lo(GND)に設定される。

【0047】

ICチップ1を目合わせマーク22に合わせた場合は、インナーリード15に接続される外部端子は、Lo(GND)に設定され、インナーリード14aに接続される外部端子は、Hi(VDD)に設定される。

【0048】

ICチップ1を目合わせマーク23に合わせた場合は、インナーリード14bに接続される外部端子は、Hi(VDD)に設定され、インナーリード16bに接続される外部端子は、Lo(GND)に設定される。

【0049】

ICチップ1を目合わせマーク24に合わせた場合は、インナーリード14bに接続される外部端子は、Hi(VDD)に設定され、インナーリード14cに接続される外部端子は、Hi(VDD)に設定される。

【0050】

本実施形態の半導体装置によれば、ICチップ1と、パッケージ2との接続位置を変えることにより、異なる2ビット幅の制御信号をICチップ1に与えることができ、ICチップ1に対して、4通りの動作モードを切り替えることができる。なお、制御信号の切り替えに使用するインナーリードの部位を増やすことにより、2ビット幅の制御信号の場合と同様の方法で、3ビット以上のビット幅の制御信号による動作モードの切り替えを行うことも可能である。

【0051】

(第5実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。図12は、本発明の実施形態5における半導体装置の平面図である。本実施形態は、ICチップ1の長辺側ではなく、短辺側(図12の部分領域E)において、本発明の実施する形態について説明する。本実施形態における半導体装置の構成は、第1実施形態の図3と同様であるため、説明を省略する。

【0052】

図13Aは、本発明の実施形態5における半導体装置のパッケージ2の部分領域Eの平面図である。パッケージ2の部分領域Eは、目合わせマーク21、目合わせマーク22、インナーリード17、インナーリード18及びインナーリード19を備える。インナーリード17及びインナーリード19の枝分かれ部分は、ICチップ1の接続箇所の外側に存在しており、ICチップ1をどちらの目合わせマークに合わせても、同一のリードにバンプが接続される。インナーリード18は、図13Aに示されるように、コの字型に形成されている。本実施形態の半導体装置では、ICチップ1の短辺側にて、パッケージ2との接続位置を変更する。そのため、目合わせマーク21と目合わせマーク22のどちらに接続しても、同一のバンプに接続できるように、ICチップ1の長辺側の外部端子に接続されるインナーリードには、十分な長さの接続可能領域を確保する必要がある。

【0053】

図13Bは、本発明の実施形態5における半導体装置のICチップ1の部分領域Eの平面図である。GND出力端子7は、Lo(GND)を出力する端子である。制御端子8は、Lo(GND)、又はHi(VDD)に接続される端子である。VDD出力端子9は、Hi(VDD)を出力する端子である。図13Bに図示されているように、制御端子8の両側に、GND出力端子7及びVDD出力端子9が配置されている。外部端子10a及び外部端子10bは、一般の端子である。

【0054】

図14Aは、本発明の実施形態5における半導体装置の制御端子8を、目合わせマーク22に合わせることにより、Hi(VDD)に設定した場合の図である。図14Aに図示されているように、制御端子8のバンプとVDD出力端子9のバンプとが、コの字型のインナーリード18によって接続されることにより、制御端子8が、Hi(VDD)に設定されている。

【0055】

図14Bは、本発明の実施形態5における半導体装置の制御端子8を、目合わせマーク21に合わせることにより、Lo(GND)に設定した場合の図である。図14Bに図示されているように、制御端子8のバンプとGND出力端子7のバンプとが、コの字型のインナーリード18によって接続されることにより、制御端子8が、Lo(GND)に設定されている。

【0056】

図14A及び図14B、どちらの場合においても、外部端子10aは、同一のインナーリード17に接続されている。同様に、外部端子10bは、同一のインナーリード19に接続されている。

【0057】

本実施形態の半導体装置によれば、制御端子8をICチップ1の短辺側に配置することができる。また、図13Bに図示されているように、GND出力端子7、制御端子8及びVDD出力端子9において、ICチップ1とパッケージ2との接続位置を、バンプのピッチ分だけ移動させることにより、設定を変えることができる。

【0058】

本実施形態では、制御端子に与える信号をICチップ1の外部端子7および9から与えている。これは、図12から明らかなように、短辺の外側には出力信号のリード3が存在するため、安価な1層配線のパッケージ2では、外部から電源(VDD,GND)のリードを引き込むことによって配線できないからである。

【0059】

逆に、実施形態1から4までの制御端子に与える信号は外部からリードを介して与えたが、本実施形態のようにICチップの出力信号を使用することが可能である。

【0060】

以上、本発明の実施の形態が添付の図面を参照することにより説明された。但し、本発明は、上述の実施の形態に限定されず、要旨を逸脱しない範囲で当業者により適宜変更され得る。

【符号の説明】

【0061】

1 ICチップ

2 パッケージ

3 リード

4 入力端子

5 出力端子

6 バンプ

7 GND出力端子

8 制御端子

9 VDD出力端子

10a,10b 外部端子

11〜13 インナーリード

14a〜14c インナーリード

15 インナーリード

16a,16b インナーリード

17〜19 インナーリード

21〜24 目合わせマーク

25 インナーリード部

31 (Electro−Static Discharge)保護回路

32 プルアップ抵抗

33 バッファ

100 ICチップ

101 制御端子

102 制御端子

103a〜103f リード

104 ボンディングワイヤ

111 ICチップ

112 パッケージ

113 リード

113a〜113b 補助リード

115 ワイヤ

121〜124 ピン

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、チップの外部端子がバンプである半導体装置に関する。

【背景技術】

【0002】

半導体装置において、一部の入力端子(制御端子)を、Hi、又はLoに設定することにより、動作モードを切り替えて使用できるものが知られている。このような半導体装置は、1つのIC(Integrated Circuit)チップで、ユーザに合わせた機能を切り替えて使用できるため、ICチップの開発コストを抑えることができる。

【0003】

一般に、ICチップの特定の端子をHi、又はLoに設定するためには、その端子を半導体装置のパッケージの外部端子にして電位を設定する。外部端子に、Hi、又はLoの電位を供給する方法は、半導体装置に接続する接続基板で電位を設定する方法、又は、接続基板上の他のデバイスで電位を設定する方法がある。例えば、半導体装置が、LCD(Liquid Crystal Display)表示装置の場合には、タイミングコントローラに接続する。これらの方法は、ユーザの機能に合わせた異なるICチップの開発に比べれば、接続基板の変更、又は接続基板上の他のデバイスの設定変更であるため、開発コストは安価になり、開発期間は短期間になる。しかし、接続基板の変更、又は接続基板上の他のデバイスの設定変更を、半導体装置メーカーの半導体装置の製造上の都合で、ユーザ側に強いることはできない。そのため、半導体装置メーカーでは、半導体装置のパッケージングの段階で、特定の端子の電位を切り替えることにより、半導体装置外部での設定変更を不要にする試みがなされている。

【0004】

本発明の分野における文献公知発明としては、特開2003−152009号公報(特許文献1)、及び特開平6−97319号公報(特許文献2)がある。

【0005】

図1は、特許文献1の半導体装置を説明するための図である。特開2003−152009号公報(特許文献1)では、2つのリード103a、103cをチップ下で延在し、制御端子101、102の接続先を、延在した先の端子にワイヤーボンディングする(図1(A))か、延在元の端子にワイヤーボンディングする(図1(B))かを切り替えることができる発明が開示されている。この発明によれば、同一チップ、同一パターンの半導体装置に対して、ボンディング位置のみで、半導体装置の動作モードを変更することができる。

【0006】

図2は、特許文献2の半導体装置を説明するための図である。特開平6−97319号公報(特許文献2)では、チップ111の搭載領域周辺に相互に絶縁された帯状の導体片(補助リード)113a、113bが配置されている。外部端子123は、チップ111の左下領域に最も近い位置にあるが、外部端子123から伸びたインナーリード113から補助リード113aに接続(ボンディング)し、補助リード113aからワイヤ115により、チップ111の右上の領域のパッドにボンディングできる。また、外部端子126は、チップ111の右上領域に最も近い位置にあるが、補助リード113bにボンディングすることで、補助リード113bを通して、チップ左下の領域のパッドにボンディングできる。この発明によれば、半導体チップのボンディングパッド配列に関係なく、パッケージのピン配列を設定することができる。

【0007】

このような従来技術は、ワイヤーボンディングが必須であるため、ワイヤーの分だけパッケージの厚さが厚くなり、厚さの薄いパッケージに適用することができない。例えば、厚さが薄いパッケージの代表であるTAB(Tape Automated Bonding)パッケージでは、ICチップ上に設けられた突起電極(バンプ)と、テープ上の端子とを直接接続(フリップチップボンディング)するため、ボンディングワイヤーで接続を切り替える従来技術を適用することができない。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−152009号公報

【特許文献2】特開平6−97319号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

フリップチップ実装の半導体装置において、パッケージ外部の設計を変更せずに、特定の端子に与える信号を変更できる半導体装置が求められている。

【課題を解決するための手段】

【0010】

上記の課題を解決するために、本発明は、以下に述べられる手段を採用する。その手段を構成する技術的事項の記述には、[特許請求の範囲]の記載と[発明を実施するための形態]の記載との対応関係を明らかにするために、[発明を実施するための形態]で使用される番号・符号が付加されている。ただし、付加された番号・符号は、[特許請求の範囲]に記載されている発明の技術的範囲を限定的に解釈するために用いてはならない。

【0011】

本発明の半導体装置は、外部端子にバンプを備えるICチップ(1)と、前記ICチップを搭載するパッケージ(2)とを備え、前記パッケージ(2)は、前記外部端子に第1の信号又は第2の信号を印加するインナーリード部(25)を備える。前記インナーリード部(25)は、前記ICチップ(1)の搭載位置により、前記外部端子に印加する信号を、前記第1の信号又は前記第2の信号に変更可能なインナーリードのパターンを有する。

【発明の効果】

【0012】

本発明によれば、フリップチップ実装の半導体装置において、パッケージ外部の設計を変更せずに、特定の端子に与える信号を変更できる半導体装置を提供することができる。

【図面の簡単な説明】

【0013】

【図1】図1は、特許文献1の半導体装置を説明するための平面図である。

【図2】図2は、特許文献2の半導体装置を説明するための平面図である。

【図3】図3は、本発明の実施形態1における半導体装置の平面図である。

【図4A】図4Aは、インナーリード部25の部分領域Aの第1実施形態におけるインナーリードパターンの平面図である。

【図4B】図4Bは、図4Aに図示されたB−B’軸における部分領域AのB−B’断面図である。

【図5A】図5Aは、図4Aに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をVDDに接続した場合を説明するための図である。

【図5B】図5Bは、図4Bに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をVDDに接続した場合を説明するための図である。

【図6A】図6Aは、図4Aに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をGNDに接続した場合を説明するための図である。

【図6B】図6Bは、図4Bに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をGNDに接続した場合を説明するための図である。

【図7】図7は、図4Aのインナーリードパターンの変形例1である。

【図8】図8は、図4Aのインナーリードパターンの変形例2である。

【図9A】図9Aは、図3の部分領域Aの第2実施形態におけるインナーリードパターンの平面図である。

【図9B】図9Bは、図9Aのインナーリード11と接続されるICチップ1の入力端子の等価回路図である。

【図10】図10は、図3の部分領域Aの第3実施形態におけるインナーリードパターンの平面図である。

【図11】図11は、図4の部分領域Aの第4実施形態におけるインナーリードパターンの平面図である。

【図12】図12は、本発明の実施形態5における半導体装置の平面図である。

【図13A】図13Aは、本発明の実施形態5における半導体装置のパッケージ2の部分領域Eの平面図である。

【図13B】図13Bは、本発明の実施形態5における半導体装置のICチップ1の部分領域Eの平面図である。

【図14A】図14Aは、本発明の実施形態5における半導体装置の制御端子8を、目合わせマーク22に合わせることにより、Hi(VDD)に設定した場合の図である。

【図14B】図14Bは、本発明の実施形態5における半導体装置の制御端子8を、目合わせマーク21に合わせることにより、Lo(GND)に設定した場合の図である。

【発明を実施するための形態】

【0014】

(第1実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。

【0015】

はじめに、本実施形態における半導体装置の構成の説明を行う。

【0016】

図3は、本発明の実施形態における半導体装置の平面図である。本実施形態の半導体装置は、ICチップ1とパッケージ2とを備える。パッケージ2は、ICチップ1の保護、及びICチップ1と他の外部デバイスが搭載された接続基板とを電気的に接続する役割を持つ。パッケージ2は、外部端子として、複数の入力端子4、及び複数の出力端子5とを備える。パッケージ2内において、外部端子からリード3を介して、ICチップ1と他の外部デバイスが電気的に接続される。ICチップ1とリード3の接続は、ICチップの外部電極である突起電極(バンプ)と、ICチップ1と重なるリード3の部分(インナーリード部25)とを接続することにより行われる。一般に、バンプとインナーリードは、熱圧着等で接続される。その後、インナーリード部25とICチップ1下面の間に封止樹脂が流し込まれ、機械的にパッケージ2とICチップ1が接着されるとともに、外的環境から保護される。

【0017】

例えば、半導体装置が表示装置のドライバの場合には、入力端子4は、タイミングコントローラと呼ばれる外部デバイスや、電源を搭載する接続基板に接続し、出力端子5は、表示パネルに接続する。入力端子4には、ICチップ1の入力端子に接続するものや、ICチップ1の電源端子に電力を供給する電源端子がある。製品によっては、接続基板へ信号を出力する出力端子を含む場合がある。図3の半導体装置の例は、作図の都合で外部端子の本数が少ないが、例えば、半導体装置が表示装置のドライバである場合は、入力端子4は数十本から百本程度あり、出力端子5は数百本から千本を超えるものまである。

【0018】

本発明の実施形態では、パッケージ2の有するインナーリードのパターンが重要である。図4Aは、インナーリード部25の部分領域Aの第1実施形態におけるインナーリードパターンの平面図である。目合わせマーク21及び目合わせマーク22は、パッケージ2にICチップ1を搭載する際の位置合わせに使用するマークである。インナーリード11は、VDDに接続され、インナーリード12は、GNDに接続されている。インナーリード11の形状は、図4Aで図示されているように、インナーリードを2箇所で折り曲げ、B−B’軸に対し、B’方向へ折り返すことにより形成されている。インナーリード12の形状は、図4Aで図示されているように、分岐させたインナーリードを折り曲げて、B−B’軸に対して、B方向へ伸ばすことにより形成されている。インナーリード11とインナーリード12は、B−B’軸上において、対峙するように配線され、互いに絶縁されている。

【0019】

図4Bは、図4Aに図示されたB−B’軸における部分領域AのB−B’断面図である。パッケージ2の上面にインナーリードが積層してある。互いに絶縁されたインナーリードの左側がVDDに接続されるインナーリード11であり、右側がGNDに接続されるインナーリード12である。

【0020】

図5Aは、図4Aに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をVDDに接続した場合を説明するための図である。ICチップ1を、目合わせマーク22に合わせて配置することにより、ICチップ1の外部端子(制御端子)とインナーリード11を電気的に接続している。

【0021】

図5Bは、図4Bに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をVDDに接続した場合を説明するための図である。ICチップ1の制御端子と、VDDに接続されたインナーリード11とが、ICチップ1の制御端子上に形成されたバンプ6により電気的に接続されている。

【0022】

図6Aは、図4Aに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をGNDに接続した場合を説明するための図である。ICチップ1を、目合わせマーク21に合わせて配置することにより、ICチップ1の制御端子とインナーリード12を電気的に接続している。

【0023】

図6Bは、図4Bに図示されたインナーリードパターンにおいて、ICチップ1の外部端子をGNDに接続した場合を説明するための図である。ICチップ1の制御端子と、GNDに接続されたインナーリード12とが、ICチップ1の制御端子上に形成されたバンプ6により電気的に接続されている。

【0024】

なお、図5A、図6Aに図示されているように、インナーリード11の折り曲げ部分は、バンプの接続位置よりICチップ1の内側にあり、インナーリード12の枝分かれ部分は、ICチップ1の外側にあるように設計されている。これは、封止樹脂を流し込んでICチップ1とパッケージ2を接着する際に、樹脂の流れを妨げないようにするためである。

【0025】

なお、目合わせマーク21、目合わせマーク22は、説明し易さを考慮し、ICチップ1の角に合わせる例で説明したが、実際には、ICチップ1の角はICチップ1をウェハーから切り出すダイシングの工程で、その位置に誤差を含む。そのため、インナーリードのピッチが細かい場合には、より精度の高い方法を採る。例えば、パッケージ2の基材が半透明のTABテープの場合は、ICチップ1及びパッケージ2に位置合わせ精度のよいマークを設置する。パッケージ2のICチップ1を搭載する面の裏面から、光学的にマーク同士を合わせることにより、より精度の高い位置合わせを行うことができる。また、目合わせマークは、図4Aのように、ICチップ1上の1つの角だけでなく、対角線上等の他の位置にも設置し、回転方向の位置合わせ精度を上げてもよい。また、特別な目合わせマークを使用せずに、インナーリードとバンプの接続状況を、直接光学的に観測することにより位置を合わせてもよい。

【0026】

なお、図3のICチップ1の短辺のバンプに接続しているインナーリードは、ICチップ1を、どちらの目合わせマークに合わせても、同じバンプに接続できるようにしておく必要がある。例えば、短辺のバンプに接続しているインナーリードに、ICチップ1の短辺に平行に、目合わせマーク0と目合わせマーク1の間隔以上の長さのバンプとの接続部分を持たせる。または、後に本発明の実施形態5(図13A〜14B)で述べるインナーリード17及びインナーリード19のように、目合わせマーク0に合わせた時の接続部分と、目合わせマーク1に合わせた時の接続部分の両方を、同じリードに接続するようにする方法等が考えられる。

【0027】

本実施形態の半導体装置によれば、同一のICチップ1とパッケージ2とをフリップチップ接続する場合でも、ICチップ1と合わせる目合わせマークを変えることで、特定の入力端子(制御端子)の電位をHi(VDD)、又はLo(GND)に設定することができる。これにより、ICチップ1が、2つの動作モードを持つ場合に、動作モードをパッケージングの段階で選択でき、短期間で、複数種類の半導体装置を製造することができる。また、ICチップ1及びパッケージ2が同一のため、これらの製造コストをより小さくし、量産効果によるコストダウンを実現することができる。

【0028】

なお、本実施形態の半導体装置の効果は、図4Bの断面構造があれば得ることができるため、図4Aのインナーリードのパターンに限定されるものではない。

【0029】

図7は、図4Aのインナーリードパターンの変形例1である。インナーリード11は、VDDに接続され、インナーリード12は、GNDに接続されている。インナーリード11の形状は、図7に図示されているように、分岐させたインナーリードを、B−B’軸に対して、B方向へ伸ばすことにより形成されている。インナーリード12の形状は、図7に図示されているように、分岐させたインナーリードを折り曲げて、B−B’軸に対して、B方向へ伸ばし、分岐元のインナーリード方向に、再度、折り曲げて合流させることにより形成されている(ループ形状)。インナーリード部25とICチップ1下面の間の封止樹脂の流れを横切るインナーリードの配線が問題にならない場合は、このような形状で設計することも可能である。

【0030】

図8は、図4Aのインナーリードパターンの変形例2である。インナーリード11は、VDDに接続され、インナーリード12は、GNDに接続されている。インナーリードの幅を広げることで、インナーリード11とインナーリード12を形成し、B−B’軸において、インナーリード11とインナーリード12を対峙させている。

【0031】

部分領域Aが、図7及び図8のようなインナーリードのパターンを有していても、図4Bの断面構造となるため、本実施形態の半導体装置の効果を得ることができる。

【0032】

(第2実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。本実施形態における半導体装置の構成は、第1実施形態の図3と同様であるため、説明を省略する。

【0033】

図9Aは、図3の部分領域Aの第2実施形態におけるインナーリードパターンの平面図である。インナーリード11は、オープン状態になる入力端子4の制御端子のバンプ6を接続するためのダミー用のリードである。インナーリード12は、GNDに接続されている。インナーリード12の形状は、第1実施形態の図4Aのインナーリード12と同様である。

【0034】

本実施形態の半導体装置では、ICチップ1を目合わせマーク22に合わせた場合は、インナーリード11に接続されるバンプに対応する、ICチップ1の制御端子がオープン状態になる。そのため、ICチップ1の制御端子をVDDにプルアップし、Hi(VDD)に設定する。図9Bは、図9Aのインナーリード11と接続されるICチップ1の入力端子(制御端子)の等価回路図である。図9Bの等価回路は、ESD(Electro−Static Discharge)保護回路31、プルアップ抵抗32及びバッファ33を備える。オープン状態となるICチップ1の制御端子は、VDDに接続されたプルアップ抵抗32と接続され、入力信号がHi(VDD)に設定される。

【0035】

本実施形態の半導体装置では、ICチップ1を目合わせマーク21に合わせた場合は、図6Aと同様に、ICチップ1の制御端子のバンプは、GNDであるインナーリード12に接続される。この場合、バッファ33の入力端子には、VDDに接続するプルアップ抵抗32とESD保護素子31を介してGNDに接続する制御端子との分圧によって発生する電圧レベルが印加される。ESD保護素子31の直流抵抗は、プルアップ抵抗32の直流抵抗に対して十分に小さいため、ほぼGNDに近いロー(Lo)レベルの電圧が印加されることになる。

【0036】

このように、本発明の第2実施形態でもICチップの搭載位置によって外部端子に印加する信号を変更することが可能になる。

【0037】

なお、インナーリード11は制御端子をインナーリード12に接続した時は、電圧を設定しないオープンの状態でパッケージ2上に存在することになる。ICチップをパッケージ2に搭載する際に問題が無ければ、インナーリード11を具備しない構成にすることで、制御端子のバンプがどこにも接続しない状態になるようにしても構わない。というのも、インナーリードのようにパターン間の間隔が最小寸法であるところに電圧を設定しない配線パターンがあると、表示装置のESD耐量を弱くしてしまうことがあるからである。

【0038】

なお、図9A及び図9Bにおいて、インナーリード11に接続した際にオープン状態となるICチップ1の制御端子を、VDDに接続したプルダウン抵抗32の代わりに、GNDに接続されたプルダウン抵抗に接続して、入力信号をLo(GND)に設定してもよい。その場合には、インナーリード12をVDDに接続し、目合わせマーク21又は目合わせマーク22の選択により、ICチップ1の制御端子の電位をHi(VDD)、又はLo(GND)に切り替える。

【0039】

第2実施形態の半導体装置では、第1実施形態とは異なり、動作モードの変更のために必要となるインナーリードは、Hi(VDD)、又はLo(GND)のいずれか一方に接続されていればよい。そのため、第2実施形態の半導体装置によれば、VDDに接続されたインナーリードと、GNDに接続されたインナーリードを、並べて配置する必要がなく、外部端子の位置をより自由に設計することができる。

【0040】

(第3実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。本実施形態における半導体装置の構成は、第1実施形態の図3と同様であるため、説明を省略する。

【0041】

図10は、図3の部分領域Aの第3実施形態におけるインナーリードパターンの平面図である。本実施形態の半導体装置では、目合わせマークが3つ存在する点が、第1実施形態の半導体装置とは異なる。図10に図示されているように、本実施形態の半導体装置のインナーリードのパターンでは、第1実施形態のインナーリード11とインナーリード12との間に、インナーリード13が追加されている。また、インナーリード13にバンプを合わせるための目合わせマーク23が追加されている。インナーリード11は、VDDに接続される。インナーリード12は、GNDに接続される。インナーリード13は、ICチップ1に対する制御信号を送信するための電極に接続される。インナーリード11、インナーリード12及びインナーリード13は、図10に図示されているように、B−B’軸上に配線され、互いに絶縁されている。

【0042】

ICチップ1を目合わせマーク21に合わせた場合は、第1実施形態の半導体装置と同様に、外部端子(制御端子)は、Lo(GND)に設定される。ICチップ1を目合わせマーク22に合わせた場合は、第1実施形態の半導体装置と同様に、外部端子は、Hi(VDD)に設定される。ICチップ1を目合わせマーク23に合わせた場合は、制御信号を外部から与えることにより、外部端子の論理値を外部から切り替えることができる。

【0043】

本実施形態の半導体装置によれば、インナーリード13を介して、外部からの制御信号により、ICチップ1の動作モードを容易に変更することができる。これにより、同一のICチップ1とパッケージ2の組み合わせによる半導体製品を、ICチップ1の2つの動作モードのどちらか一方を必要とするカスタマ、および2つのモードを使い分けるカスタマの3者に提供することができる。

【0044】

(第4実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。本実施形態における半導体装置の構成は、第1実施形態の図3と同様であるため、説明を省略する。

【0045】

図11は、図4の部分領域Aの第4実施形態におけるインナーリードパターンの平面図である。本実施形態の半導体装置では、目合わせマークが4つ存在し、2つの外部端子(制御端子)の信号の組み合わせを切り替えることができる点が、他の実施形態とは異なる。インナーリード14a〜14cは、VDDに接続された1本のインナーリードを、図11に図示されているように分岐させることにより形成されている。インナーリード15は、GNDに接続されたインナーリードを、図11に図示されているように分岐させることにより形成されている。インナーリード16a、16bは、図11に図示されているように、GNDに接続されたインナーリードを2箇所で分岐させることにより形成されている。インナーリード15、インナーリード14bは、図11に図示されているように、C−C’軸上に配線され、互いに絶縁されている。インナーリード16a、インナーリード14a、インナーリード16b及びインナーリード14cは、図11に図示されているように、D−D’軸上に配線され、互いに絶縁されている。

【0046】

ICチップ1を目合わせマーク21に合わせた場合は、インナーリード15に接続される外部端子は、Lo(GND)に設定され、インナーリード16aに接続される外部端子は、Lo(GND)に設定される。

【0047】

ICチップ1を目合わせマーク22に合わせた場合は、インナーリード15に接続される外部端子は、Lo(GND)に設定され、インナーリード14aに接続される外部端子は、Hi(VDD)に設定される。

【0048】

ICチップ1を目合わせマーク23に合わせた場合は、インナーリード14bに接続される外部端子は、Hi(VDD)に設定され、インナーリード16bに接続される外部端子は、Lo(GND)に設定される。

【0049】

ICチップ1を目合わせマーク24に合わせた場合は、インナーリード14bに接続される外部端子は、Hi(VDD)に設定され、インナーリード14cに接続される外部端子は、Hi(VDD)に設定される。

【0050】

本実施形態の半導体装置によれば、ICチップ1と、パッケージ2との接続位置を変えることにより、異なる2ビット幅の制御信号をICチップ1に与えることができ、ICチップ1に対して、4通りの動作モードを切り替えることができる。なお、制御信号の切り替えに使用するインナーリードの部位を増やすことにより、2ビット幅の制御信号の場合と同様の方法で、3ビット以上のビット幅の制御信号による動作モードの切り替えを行うことも可能である。

【0051】

(第5実施形態)

添付図面を参照して、本実施形態による半導体装置を以下に説明する。図12は、本発明の実施形態5における半導体装置の平面図である。本実施形態は、ICチップ1の長辺側ではなく、短辺側(図12の部分領域E)において、本発明の実施する形態について説明する。本実施形態における半導体装置の構成は、第1実施形態の図3と同様であるため、説明を省略する。

【0052】

図13Aは、本発明の実施形態5における半導体装置のパッケージ2の部分領域Eの平面図である。パッケージ2の部分領域Eは、目合わせマーク21、目合わせマーク22、インナーリード17、インナーリード18及びインナーリード19を備える。インナーリード17及びインナーリード19の枝分かれ部分は、ICチップ1の接続箇所の外側に存在しており、ICチップ1をどちらの目合わせマークに合わせても、同一のリードにバンプが接続される。インナーリード18は、図13Aに示されるように、コの字型に形成されている。本実施形態の半導体装置では、ICチップ1の短辺側にて、パッケージ2との接続位置を変更する。そのため、目合わせマーク21と目合わせマーク22のどちらに接続しても、同一のバンプに接続できるように、ICチップ1の長辺側の外部端子に接続されるインナーリードには、十分な長さの接続可能領域を確保する必要がある。

【0053】

図13Bは、本発明の実施形態5における半導体装置のICチップ1の部分領域Eの平面図である。GND出力端子7は、Lo(GND)を出力する端子である。制御端子8は、Lo(GND)、又はHi(VDD)に接続される端子である。VDD出力端子9は、Hi(VDD)を出力する端子である。図13Bに図示されているように、制御端子8の両側に、GND出力端子7及びVDD出力端子9が配置されている。外部端子10a及び外部端子10bは、一般の端子である。

【0054】

図14Aは、本発明の実施形態5における半導体装置の制御端子8を、目合わせマーク22に合わせることにより、Hi(VDD)に設定した場合の図である。図14Aに図示されているように、制御端子8のバンプとVDD出力端子9のバンプとが、コの字型のインナーリード18によって接続されることにより、制御端子8が、Hi(VDD)に設定されている。

【0055】

図14Bは、本発明の実施形態5における半導体装置の制御端子8を、目合わせマーク21に合わせることにより、Lo(GND)に設定した場合の図である。図14Bに図示されているように、制御端子8のバンプとGND出力端子7のバンプとが、コの字型のインナーリード18によって接続されることにより、制御端子8が、Lo(GND)に設定されている。

【0056】

図14A及び図14B、どちらの場合においても、外部端子10aは、同一のインナーリード17に接続されている。同様に、外部端子10bは、同一のインナーリード19に接続されている。

【0057】

本実施形態の半導体装置によれば、制御端子8をICチップ1の短辺側に配置することができる。また、図13Bに図示されているように、GND出力端子7、制御端子8及びVDD出力端子9において、ICチップ1とパッケージ2との接続位置を、バンプのピッチ分だけ移動させることにより、設定を変えることができる。

【0058】

本実施形態では、制御端子に与える信号をICチップ1の外部端子7および9から与えている。これは、図12から明らかなように、短辺の外側には出力信号のリード3が存在するため、安価な1層配線のパッケージ2では、外部から電源(VDD,GND)のリードを引き込むことによって配線できないからである。

【0059】

逆に、実施形態1から4までの制御端子に与える信号は外部からリードを介して与えたが、本実施形態のようにICチップの出力信号を使用することが可能である。

【0060】

以上、本発明の実施の形態が添付の図面を参照することにより説明された。但し、本発明は、上述の実施の形態に限定されず、要旨を逸脱しない範囲で当業者により適宜変更され得る。

【符号の説明】

【0061】

1 ICチップ

2 パッケージ

3 リード

4 入力端子

5 出力端子

6 バンプ

7 GND出力端子

8 制御端子

9 VDD出力端子

10a,10b 外部端子

11〜13 インナーリード

14a〜14c インナーリード

15 インナーリード

16a,16b インナーリード

17〜19 インナーリード

21〜24 目合わせマーク

25 インナーリード部

31 (Electro−Static Discharge)保護回路

32 プルアップ抵抗

33 バッファ

100 ICチップ

101 制御端子

102 制御端子

103a〜103f リード

104 ボンディングワイヤ

111 ICチップ

112 パッケージ

113 リード

113a〜113b 補助リード

115 ワイヤ

121〜124 ピン

【特許請求の範囲】

【請求項1】

外部端子にバンプを備えるICチップと、

前記ICチップを搭載するパッケージとを備え、

前記パッケージは、

前記外部端子に第1の信号又は第2の信号を印加するインナーリード部を備え、ここで、前記インナーリード部は、前記ICチップの搭載位置により、前記外部端子に印加する信号を、前記第1の信号又は前記第2の信号に変更可能なインナーリードのパターンを有する

半導体装置。

【請求項2】

前記第1の信号は、第1の電圧の電源により生成され、前記第2の信号は、前記第1の電圧とは異なる第2の電圧の電源により生成される

請求項1に記載の半導体装置。

【請求項3】

前記パッケージは、前記搭載位置を示す目合わせマークを複数有し、

前記ICチップと合わせる前記目合わせマークを選択することにより、前記バンプと前記インナーリード部との接続位置を合わせる

請求項1又は2に記載の半導体装置。

【請求項4】

前記インナーリードのパターンは、

前記インナーリードの向きを変える折り曲げパターン

を含む請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記インナーリードのパターンは、

単一の前記インナーリードから、複数の前記インナーリードに分岐する分岐パターン

を含む請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

前記インナーリードのパターンは、

前記分岐パターンにより分岐した前記インナーリードが、合流する合流パターン

を含む請求項5に記載の半導体装置。

【請求項7】

前記インナーリードのパターンは、

部位によって幅の異なる前記インナーリードを含む

請求項1乃至6のいずれか1項に記載の半導体装置。

【請求項1】

外部端子にバンプを備えるICチップと、

前記ICチップを搭載するパッケージとを備え、

前記パッケージは、

前記外部端子に第1の信号又は第2の信号を印加するインナーリード部を備え、ここで、前記インナーリード部は、前記ICチップの搭載位置により、前記外部端子に印加する信号を、前記第1の信号又は前記第2の信号に変更可能なインナーリードのパターンを有する

半導体装置。

【請求項2】

前記第1の信号は、第1の電圧の電源により生成され、前記第2の信号は、前記第1の電圧とは異なる第2の電圧の電源により生成される

請求項1に記載の半導体装置。

【請求項3】

前記パッケージは、前記搭載位置を示す目合わせマークを複数有し、

前記ICチップと合わせる前記目合わせマークを選択することにより、前記バンプと前記インナーリード部との接続位置を合わせる

請求項1又は2に記載の半導体装置。

【請求項4】

前記インナーリードのパターンは、

前記インナーリードの向きを変える折り曲げパターン

を含む請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記インナーリードのパターンは、

単一の前記インナーリードから、複数の前記インナーリードに分岐する分岐パターン

を含む請求項1乃至4のいずれか1項に記載の半導体装置。

【請求項6】

前記インナーリードのパターンは、

前記分岐パターンにより分岐した前記インナーリードが、合流する合流パターン

を含む請求項5に記載の半導体装置。

【請求項7】

前記インナーリードのパターンは、

部位によって幅の異なる前記インナーリードを含む

請求項1乃至6のいずれか1項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図5A】

【図5B】

【図6A】

【図6B】

【図7】

【図8】

【図9A】

【図9B】

【図10】

【図11】

【図12】

【図13A】

【図13B】

【図14A】

【図14B】

【図2】

【図3】

【図4A】

【図4B】

【図5A】

【図5B】

【図6A】

【図6B】

【図7】

【図8】

【図9A】

【図9B】

【図10】

【図11】

【図12】

【図13A】

【図13B】

【図14A】

【図14B】

【公開番号】特開2013−65673(P2013−65673A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2011−203005(P2011−203005)

【出願日】平成23年9月16日(2011.9.16)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成23年9月16日(2011.9.16)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]