半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、HKMG構造を有するトランジスタを備える半導体装置に関する。

【背景技術】

【0002】

ゲート絶縁膜とゲート絶縁膜上に形成されたゲート電極とを有するMISFET(Metal-Insulator-Semiconductor Field-Effect Transistor)においては、ゲート絶縁膜としてSi02からなるシリコン酸化膜を使用し、ゲート電極としてポリシリコン膜を使用するのが一般的であった。

【0003】

近年、MISFETの微細化に伴い、ゲート絶縁膜の薄膜化が進んでいる。ゲート絶縁膜の薄膜化が進むことで、ゲート電極にかかる電場が相対的に強くなり、ポリシリコン膜を使用したゲート電極の空乏化が問題となっている。また、ゲート絶縁膜の薄膜化が進むことで、チャネルを流れる電子がシリコン酸化膜によって形成される障壁をトンネルしてゲート電極に流れる、いわゆるトンネル電流の発生が問題となっている。

【0004】

そこで、特許文献1(特開2007−329237号公報)および特許文献2(特開2006−024594号公報)には、SiO2よりも誘電率の高い高誘電率材料からなる高誘電率ゲート絶縁膜(High−k絶縁膜)と金属材料からなるメタルゲート電極とを有するMISFETが開示されている。このMISFETによれば、メタルゲート電極によりゲート電極の空乏化を抑制することができ、また、High−k絶縁膜によりトンネル電流の発生を抑制することができる。High−k絶縁膜とメタルゲート電極とを有するMISFETを、HKMG構造を有するMISFETと称する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−329237号公報

【特許文献2】特開2006−024594号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

以下では、HKMG構造を有し、閾値電圧の異なる第1および第2のMISFETを半導体基板上に形成する工程について簡単に説明する。なお、半導体基板上の第1の領域に第1のMISFETが形成され、第1の領域に並ぶ第2の領域に第2のMISFETが形成されるものとする。

【0007】

まず、半導体基板上にHigh−k絶縁膜が堆積された後、第1のMISFETのメタルゲート電極の電極材料が堆積される。第1の領域以外に堆積された電極材料は除去され、第1の領域には、High−k絶縁膜と第1のMISFETのメタルゲート電極の電極材料とが積層された第1のゲートスタック層(第1のGS層)が形成される。

【0008】

次に、第2のMISFETのメタルゲート電極の電極材料が堆積された後、第2の領域以外に堆積された電極材料は除去され、第2の領域には、High−k絶縁膜と第2のMISFETのメタルゲート電極の電極材料とが積層された第2のゲートスタック層(第2のGS層)が形成される。その後、第1および第2のGS層に対して、MISFETのゲートとするために、エッチングなどのゲート加工が行われる。

【0009】

ここで、本願発明者は、ゲート加工時にGS層の残渣が生じ、その残渣により配線ショートが発生する可能性があるという問題を見出した。

【0010】

一般に、第1の領域以外に堆積された第1のMISFETのメタルゲート電極の電極材料は、High−k絶縁膜へのダメージを抑制するために、ウェットエッチングにより除去される。ここで、ウェットエッチングにより第1の領域側の電極材料までエッチングされ、第1の領域側の電極材料がえぐられたようなオーバーハング部が形成されることがある。オーバーハング部が形成されると、第2のMISFETのメタルゲート電極の電極材料の堆積時にオーバーハング部への入り込みが生じる。オーバーハング部に入り込んだ電極材料によりゲート加工時のエッチングが阻害され、第1の領域と第2の領域との境界にGS層の残渣が生じる。残渣にはメタルゲート電極の電極材料が含まれるため導電性を有しており、残渣が電位の異なる2つの配線と接するとショートが発生する。

【課題を解決するための手段】

【0011】

本発明の半導体装置は、

半導体基板と、

高誘電率材料を含む第1のゲート絶縁膜と前記第1のゲート絶縁膜上に形成された第1のメタルゲート電極とを備える第1のトランジスタが形成される前記半導体基板上の第1の領域と、

高誘電率材料を含む第2のゲート絶縁膜と前記第2のゲート絶縁膜上に形成された第2のメタルゲート電極とを備え、前記第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される前記半導体基板上の前記第1の領域に並ぶ第2の領域と、

電位の異なる第1および第2の配線と、を有し、

前記第1の領域と前記第2の領域との境界が、前記第1および第2の配線の少なくとも一方としか重ならない。

【発明の効果】

【0012】

本発明によれば、HKMG構造を有する第1のトランジスタが形成される第1の領域と、HKMG構造を有し、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される第2の領域との境界が、電位の異なる第1および第2の配線の少なくとも一方としか重ならないため、第1の領域と第2の領域との境界に残渣が発生しても、第1の配線と第2の配線との間でショートが発生するのを防ぐことができる。

【図面の簡単な説明】

【0013】

【図1】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図2】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図3】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図4】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図5】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図6】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図7】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図8】残渣により配線ショートが生じるメカニズムを説明するための図である。

【図9】本発明の一実施形態の半導体装置の構成を示すブロック図である。

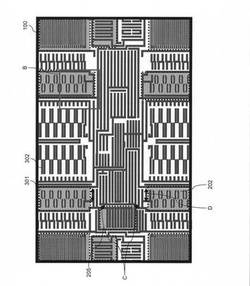

【図10】図9に示す半導体装置の回路レイアウトの一例を示す図である。

【図11】関連する半導体装置における第1および第2のGS層のパターンと半導体基板上のウェルとの関係を示す図である。

【図12】図11に示す矩形領域の拡大図である。

【図13】本発明の一実施形態の半導体装置における第1および第2のGS層のパターンと半導体基板上のウェルとの関係を示す図である。

【図14】図13に示す矩形領域の拡大図である。

【図15】残渣によるショートの発生を防ぐ方法を説明するための図である。

【図16A】残渣によるショートの発生を防ぐ方法を説明するための図である。

【図16B】残渣によるショートの発生を防ぐ方法を説明するための図である。

【図17A】残渣によるショートの発生を防ぐ方法を説明するための図である。

【図17B】残渣によるショートの発生を防ぐ方法を説明するための図である。

【発明を実施するための形態】

【0014】

以下に、本発明を実施するための形態について図面を参照して説明する。

【0015】

まず、上述した残渣が生じるメカニズムを図1から図7を参照して詳細に説明する。なお、図1から図7において、同様の構成については同じ符号を付し、説明を省略する。

【0016】

図1に示すように、半導体基板としてのSi基板1に素子分離領域であるSTI(Shallow Trench Isolation)2が形成される。

【0017】

STI2の形成後、インターレイヤーとして、熱酸化によりシリコン酸化膜(SiO2)3が形成される。シリコン酸化膜3の形成後、SiO2よりも誘電率の高いHfO(酸化ハフニウム)、HfSiO(ハフニウムシリケート)などの高誘電率材料からなるHigh−k絶縁膜4が堆積される。

【0018】

High−k絶縁膜4の堆積後、第1のMISFETのメタルゲート電極の電極材料である窒化チタン膜(TiN)5が堆積される。窒化チタン膜5の堆積後、ポリシリコン膜6が堆積される。ポリシリコン膜6の堆積後、加工用のマスク材料としてシリコン酸化膜(SiO2)7が堆積される。シリコン酸化膜7の堆積後、第1の領域上にレジスト8が堆積される。

【0019】

図2に示すように、レジスト8の堆積後、リソグラフィなどによりパターニングが行われる。パターニング後、ドライエッチングによりシリコン酸化膜7の加工が行われる。その後、第1の領域以外に堆積されたシリコン酸化膜7を除去するために、ドライエッチングが行われる。シリコン酸化膜7の除去後、第1の領域以外に堆積された窒化チタン膜5およびポリシリコン膜6を除去するために、ウェットエッチングが行われる。具体的には、まず、アンモニア水によりポリシリコン膜6がエッチングされ、次に、APM(アンモニア過酸化水素水)により窒化チタン膜5がエッチングされる。

【0020】

ウェットエッチングにより第1の領域以外に堆積された窒化チタン膜5およびポリシリコン膜6は除去され、第1の領域には、第1の絶縁膜としてのHigh−k絶縁膜4、第1のメタルゲート電極としての窒化チタン膜5、ポリシリコン膜6が積層された第1のGS層9が形成される。

【0021】

ここで、図2に示すように、ウェットエッチングにより第1の領域に堆積されたポリシリコン膜6などもエッチングされ、オーバーハング部10が形成される。

【0022】

第1のGS層9の形成後、図3に示すように、酸化アルミニウム膜(AlO)11が堆積される。酸化アルミニウム膜11の堆積後、第2のMISFETのメタルゲート電極の電極材料である、窒化チタン膜5とは組成の異なる窒化チタン膜12が堆積される。酸化アルミニウム膜11および窒化チタン膜12が堆積されることで、第1のMISFETの閾値電圧と第2のMISFETの閾値電圧とが異なるものとなる。

【0023】

窒化チタン膜12の堆積後、ポリシリコン膜13が堆積される。ここで、図3に示すように、酸化アルミニウム膜11、窒化チタン膜12およびポリシリコン膜13のオーバーハング部10への入り込みが生じる。

【0024】

次に、図4に示すように、第2の領域上にレジスト14が堆積される。レジスト14の堆積後、リソグラフィなどによりパターニングが行われる。

【0025】

パターニング後、図5に示すように、第2の領域以外に堆積されたシリコン酸化膜7、酸化アルミニウム膜11、窒化チタン膜12およびポリシリコン膜13を除去するためにドライエッチングが行われ、第2の領域には、第2のゲート絶縁膜としてのHigh−k絶縁膜4、酸化アルミニウム膜11、第2のメタルゲート電極としての窒化チタン膜12、ポリシリコン膜13が積層された第2のGS層15が形成される。また、第1のGS層9と第2のGS層15との間には溝が形成され、この溝の底部に堆積されたシリコン酸化膜3、High−k絶縁膜4も除去される。ここで、図5に示すように、オーバーハング部10に入り込んだ酸化アルミニウム膜11、窒化チタン膜12およびポリシリコン膜13はエッチングされず、第1のGS層9の端部16に残る。

【0026】

第1のGS層9および第2のGS層15の形成後、図6に示すように、これらのGS層の間に形成された溝を埋めるように、ポリシリコン膜17が堆積される。なお、図6においては、ポリシリコン膜17は、第1および第2のGS層を覆うように堆積されているが、これらのGS層の間に形成された溝を埋めるようにだけ堆積されてもよい。

【0027】

ポリシリコン膜17の堆積後、W(タングステン)、WN(窒化タングステン)、WSi(タングステンシリサイド)からなるW/WN/WSi膜18が堆積される。W/WN/WSi膜18は配線となる。なお、ポリシリコン膜17が第1および第2のGS層の間に形成された溝を埋めるようにだけ堆積されている場合、配線となるのはW/WN/WSi膜18だけとなる。このような構造をBLG(Bit Line Gate)構造と称する。

【0028】

W/WN/WSi膜18の堆積後、加工用のマスク材料として、シリコン窒化膜(SiN)19が堆積され、その後、シリコン酸化膜(SiO)20が堆積される。シリコン酸化膜20の堆積後、レジスト21が堆積される。

【0029】

レジスト21の堆積後、リソグラフィなどによりシリコン窒化膜19およびシリコン酸化膜20のパターニングが行われる。パターニング後、図7に示すように、エッチングにより、第1のGS層9および第2のGS層15それぞれに対するゲート加工が行われる。

【0030】

ここで、上述したように、オーバーハング部10には、酸化アルミニウム膜11、窒化チタン膜12およびポリシリコン膜13といった第2のGS層15の材料の入り込みが生じている。オーバーハング部10に入り込んだ第2のGS層15の材料、特に、酸化アルミニウム膜11によりエッチングが阻害され、図7に示すように、第1のGS層9の端部に残渣22が生じる。なお、図7においては、簡略化のため、残渣22が第1のGS層9の端部に均一に生じているように記載しているが、実際には、不均一に生じる。また、残渣22の断面形状は、図7に示すような三角状に限定されるものではない。

【0031】

次に、残渣22により配線ショートが生じるメカニズムについて説明する。

【0032】

図8は、図7におけるシリコン膜窒化19、シリコン酸化膜20を除去した状態を示す図である。

【0033】

図8においては、電位の異なる2本の配線31a,31bが形成されているものとする。なお、配線31a,31bはそれぞれ、High−k絶縁膜4、窒化チタン膜5、ポリシリコン膜6、酸化アルミニウム膜11、窒化チタン膜12、ポリシリコン膜13,16、W/WN/WSi膜18などが積層されたものであるが、これらの記載は省略する。

【0034】

上述したように、図8においては点線で示される、第1のGS層の端部、すなわち、第1の領域と第2の領域との境界に残渣22が生じる。残渣22にはTiNなどが含まれているため導電性を有する。

【0035】

ここで、図8に示すように、残渣22が配線31aおよび配線31bと接すると、ポリシリコン膜13,16を介して配線31a,31bと電気的に接続され、これらの配線間でショートが発生する。

【0036】

次に、本実施形態における半導体装置の構成について説明する。

【0037】

図9は、本実施形態における半導体装置100の構成を示すブロック図である。

【0038】

図9に示す半導体装置100は、メモリセルアレイ(Memory Cell Array)101−1〜101−4と、ロウデコーダ(X Dec)102と、カラムデコーダ(Y Dec)103と、サブワード制御回路(SWC:Sub-word Control Circuit)104−1〜104−4と、サブワードドライバ(SWD:Sub-word Driver)105−1〜105−4と、BLEQ(Bit Line Equalizing)回路106−1〜106−4と、センスアンプ107−1〜107−4と、カラムスイッチ(Y-Switch)108−1〜108−4と、データアンプ(Data Amplifier)109と、出力回路(Output Circuit)110と、を有する。

【0039】

なお、メモリセルアレイ101−1に対応して、サブワード制御回路104−1、サブワードドライバ105−1、BLEQ回路106−1、センスアンプ107−1、および、カラムスイッチ(Y-Switch)108−1の各部が設けられている。また、メモリセルアレイ101−2〜101−4それぞれに対応して、上述した各部が同様の対応関係にて設けられている。そのため、以下では、メモリセルアレイ101−1とそれに対応する構成についてのみ説明する。また、図9においては、記載を省略したが、メモリセルアレイ101−1に対応して、複数のセンスアンプ107−1が設けられている。

【0040】

外部から与えられたアドレス信号および制御信号は、ロウデコーダ102、カラムデコーダ103、および、サブワード制御回路104−1に入力される。

【0041】

メモリセルアレイ101−1においては、複数のサブワード線と複数のビット線とが交差しており、この交点にメモリセルが配置されている。

【0042】

ロウデコーダ102は、外部から与えられた信号に基づき、メモリセルアレイ101に含まれるサブワード線のいずれかを選択する。

【0043】

カラムデコーダ103は、外部から与えられた信号に基づき、複数のセンスアンプのいずれかを選択する。

【0044】

サブワード制御回路104−1は、外部から与えられた信号に基づき、サブワードドライバ105−1、BLEQ回路106−1およびカラムスイッチ108−1に動作指示を行う。

【0045】

サブワードドライバ105−1は、サブワード制御回路104−1からの指示を受けて、ロウデコーダ102により選択されたサブワード線を駆動させる。

【0046】

BLEQ回路106−1は、サブワード制御回路104−1からの指示を受けて、センスアンプ107−1に電源を供給するための配線の電位をイコライズする。

【0047】

センスアンプ107−1は、カラムデコーダ103により選択されると、メモリセルアレイ101−1の対応するビット線に接続され、サブワード線およびビット線を介して出力されたデータを増幅して出力する。

【0048】

カラムスイッチ108−1は、ビット線とデータ入出力線との間に設けられ、サブワード制御回路104−1からの指示を受けて、オンまたはオフとなる。カラムスイッチ108−1がオンになると、センスアンプ107−1から出力されたデータが、データアンプ109に出力される。

【0049】

データアンプ109は、センスアンプ107−1から出力されたデータを増幅し、出力回路110に出力する。

【0050】

出力回路110は、データアンプ109から出力されたデータを半導体装置100の外部に出力する。

【0051】

図10は、図9に示す構成の半導体装置の回路レイアウトの一例を示す図である。

【0052】

図10に示すように、メモリセルアレイ101が形成される領域201の周辺に、センスアンプ107を構成するPチャネル型トランジスタが形成される領域202、センスアンプ107、BLEQ回路106を構成するNチャネル型トランジスタが形成される領域203、カラムスイッチ108を構成するPチャネル型トランジスタが形成される領域204、サブワード制御回路104を構成するPチャネル型トランジスタが形成される領域205、サブワード制御回路104を構成するNチャネル型トランジスタが形成される領域206、サブワードドライバ105を構成するPチャネル型トランジスタが形成される領域207、および、サブワードドライバ105を構成するNチャネル型トランジスタが形成される領域208が配置される。

【0053】

なお、図10においては、ロウデコーダ102、カラムデコーダ103、データアンプ109、および、出力回路110については記載を省略する。

【0054】

図10に示すような導電型の異なるトランジスタを形成する場合にも、一導電型としてのPチャネル型MISFETのための第1のGS層が形成される第1の領域と、他導電型としてのNチャネル型MISFETのための第2のGS層が形成される第2の領域と、の境界に残渣が生じることがある。

【0055】

図11は、図10に示す半導体装置における第1および第2のGS層のパターンと半導体基板上のウェル(素子領域)との関係の一例を示す図である。

【0056】

図11において、斜線で示される領域301は、nウェル領域を示す。

【0057】

一般に、設計の効率化のためにnウェルパターン上に、Pチャネル型MISFETのための第1のGS層が積層される。また、nウェルパターンは、Pチャネル型MISFETが形成される領域を接続するようにレイアウトされる。そのため、第1のGS層のパターンもnウェル領域のパターンに沿って延在する。その結果、第1のGS層のパターンの境界は、図11の点線で示されるようになる。

【0058】

上述したように、第1および第2のGS層の境界において残渣が生じるので、図11に示す点線に沿って残渣が生じる。残渣が電位の異なる複数の配線302に重なると、その配線間でショートが発生する。図11に示すnウェルパターンのレイアウトにおいては、実線矢印で示す複数の箇所で、第1のGS層の境界が電位の異なる2つの配線302と重なっており、これらの箇所では、配線間でショートが発生する可能性がある。

【0059】

図12は、図11に示す矩形領域Aの拡大図である。

【0060】

配線302−1は、内部電位Vppの配線であり、また、配線302−2は、電位VBLEQ(Bit Line Equalizing Voltage)、あるいは、電位VBLP(Bit Line Pre-charge Voltage)の配線である。なお、例えば、電位VBLEQは1.3Vであり、電位VBLPは0.48Vであり、電位Vppとは異なる電位である。

【0061】

拡散層303は、Pチャネル型MISFETあるいはNチャネル型MISFETのソース、ドレインとなる拡散層、コンタクトを介してウェルの電位を設定するための拡散層などを示す。

【0062】

図12に示すように、点線で示される第1のGS層の境界が、配線302−1および配線302−2と重なっている。なお、図12において、実線丸印は配線302−1と第1のGS層の境界との交点を示し、点線丸印は配線302−2と第1のGS層の境界との交点を示す。ここで、配線302−1と第1のGS層の境界との交点と、配線302−2と第1のGS層の境界との交点と、の間に第1のGS層の境界に沿って残渣が生じると、配線302−1と配線302−2との間でショートが発生するおそれがある。

【0063】

次に、本実施形態の半導体装置100における第1および第2のGS層のパターンと半導体基板上のウェルとの関係について説明する。

【0064】

図13は、本実施形態の半導体装置100における第1および第2のGS層のパターンと半導体基板上のウェルとの関係を示す図である。なお、図13において、図11と同様の構成については同じ符号を付し、説明を省略する。

【0065】

本実施形態の半導体装置100は、図11に示す半導体装置と比較して、第1のGS層が積層されるnウェルパターンが連続しておらず、島状に離れて形成されている点が異なる。nウェルパターンを島状に形成することで、第1のGS層の境界が電位の異なる2つの配線と重ならないようにすることができる。

【0066】

図14は、図13に示す矩形領域Bの拡大図である。なお、矩形領域Aと矩形領域Bとは、対応する位置関係にある。また、図14において、図12と同様の構成については同じ符号を付し、説明を省略する。

【0067】

上述したように、nウェルパターン、つまり、Pチャネル型MISFETが形成される領域は島状に離れて形成されている。そのため、図14に示すように、第1のGS層の境界が第1の配線としての配線302−1とは重なるが、第2の配線としての配線302−2とは重ならない。そのため、第1のGS層の境界に残渣が生じても、その残渣により配線302−1と配線302−2との間でショートが発生することを防ぐことができる。

【0068】

なお、nウェルパターンを島状に形成するようにしても、図13に示す、領域205の周辺箇所(箇所C)および領域202の周辺箇所(箇所D)において、残渣によるショートが発生する可能性がある。

【0069】

以下では、上述した箇所C,Dにおいて、残渣によるショートが発生しないようにする方法について説明する。

【0070】

まず、上述した箇所Cにおいて、残渣によるショートが発生しないようにするための方法について説明する。

【0071】

図15は、図13に示す箇所C付近の拡大図である。

【0072】

図15に示すように、電位の異なる配線302−3と配線302−4とが隣接している部分がある。この部分において、第1のGS層の境界が配線302−3および配線302−4と重なると、これらの配線間でショートが発生する可能性がある。ここで、一般に、配線302−3と配線302−4との間には180μm程度の間隔がある。そのため、ショートの発生を防ぐためには、その180μm程度の間隔に第1のGS層の境界が位置するようにすればよい。180μm程度の間隔にGS層の境界を位置させることは、例えば、KrF(エキシマレーザ)露光機を用いて実現可能である。

【0073】

次に、上述した箇所Dにおいて、残渣によるショートが発生しないようにするための方法について説明する。

【0074】

図16Aは、図13に示す箇所D付近の拡大図である。

【0075】

図16Aにおいて、配線302−5はnウェル電位の配線であり、配線302−6は電位VBLPの配線である。また、実線丸印は、配線302−5と第1のGS層の境界との交点を示し、点線丸印は、配線302−6と第1のGS層の境界との交点を示す。

【0076】

図16Aに示すように、第1のGS層の境界が、配線302−5および配線302−6と重なっている。ここで、配線302−5と第1のGS層の境界との交点と、配線302−6と第1のGS層の境界との交点と、の間に第1のGS層の境界に沿って残渣が生じると、これらの配線間でショートが発生する。

【0077】

そこで、図16Bに示すように、配線302−5および配線302−6のレイアウトを変更することで、第1のGS層の境界に残渣が生じても、ショートが発生しないようにすることができる。具体的には、図16Aにおいて、配線302−6の右側の領域に延在する配線302−5を無くし、その領域に図16Bに示すように、配線302−6が延在するようにレイアウト変更することで、第1のGS層の境界が配線302−5とは重なるが、配線302−6とは重ならないようにすることができる。そのため、第1のGS層の境界で残渣が生じても、ショートが発生するのを防ぐことができる。

【0078】

上述した箇所Dにおいて残渣によるショートが生じないようにするための方法についてより詳細に説明する。

【0079】

図17Aは、図16Aに示す矩形領域Eの拡大図である。

【0080】

図17Aにおいては、配線302−5,302−6とは異なる層に形成された配線304および配線304と配線302−5,302−6とを接続するコンタクト305を記載している。なお、配線304としては、nウェル電位の配線や、電位VBLPの配線などがある。配線302−5は、配線304のうち、nウェル電位の配線とコンタクト305−1を介して接続され、nウェル電位となる。また、配線302−6は、電位VBLPの配線とコンタクト305−2を介して接続され、電位VBLPとなる。

【0081】

図17Bは、図16Bに示す矩形領域Fの拡大図である。なお、矩形領域Fは矩形領域Eに対応する領域である。

【0082】

図16Bに示すように、配線302−5および配線302−6のレイアウトを変更することで、第1のGS層の境界が配線302−5としか重ならないようにしている。配線302−5および配線302−6のレイアウトの変更に伴い、コンタクト305−1,305−2のレイアウトも変更する必要がある。具体的には、図17Aの破線で囲まれる配線302−6が延在していた領域に設けられていたコンタクト305−2の位置を、図17Bの実線で囲まれる領域に変更する。なお、図17Aと図17Bとで、2つのコンタクト305−2の間隔は保持されている。また、図17Aの点線で囲まれる領域に設けられていた、配線302−6の右側に延在していた配線302−5とnウェル電位の配線304とを接続するコンタクト305−1を削除する。こうすることで、配線302−5はnウェル電位とし、配線302−6は電位VBLPとすることができる。

【0083】

このように本実施形態によれば、半導体装置100は、高誘電率材料を含むHigh−k絶縁膜とHigh−k絶縁膜上に形成されたメタルゲート電極とを備える第1のトランジスタが形成されるSi基板1上の第1の領域と、High−k絶縁膜とHigh−k絶縁膜上に形成されたメタルゲート電極とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成されるSi基板1上の第2の領域と、電位の異なる第1および第2の配線と、を有し、第1および第2の領域の境界が、第1および第2の配線の少なくとも一方としか重ならない。

【0084】

そのため、第1および第2の領域の境界に沿って残渣が生じても、その残渣が電位の異なる2つの配線と接することがなくなるので、配線間でショートが発生するのを防ぐことができる。

【符号の説明】

【0085】

1 Si基板

2 STI

3 シリコン酸化膜

4 High−k絶縁膜

5 窒化チタン膜

6 ポリシリコン膜

7 シリコン酸化膜

8,14,21 レジスト

9 第1のGS層

10 オーバーハング部

11 酸化アルミニウム膜

12 窒化チタン膜

13 ポリシリコン膜

15 第2のGS層

16 第1のGS層の端部

17 ポリシリコン膜

18 W/WN/WSi膜

19 シリコン窒化膜

20 シリコン酸化膜

22 残渣

31a,31b 配線

100 半導体装置

101−1〜101−4 メモリセルアレイ

102 ロウデコーダ

103 カラムデコーダ

104−1〜104−4 サブワード制御回路

105−1〜105−4 サブワードドライバ

106−1〜106−4 BLEQ回路

107−1〜107−4 センスアンプ

108−1〜108−4 カラムスイッチ

109 データアンプ

110 出力回路

201 メモリセルアレイ形成領域

202,204,205,207 Pチャネル型トランジスタ形成領域

203,206,208 Nチャネル型トランジスタ形成領域

301 nウェル領域

302,302−1〜302−6 配線

303 拡散層

304 配線

305−1,305−2 コンタクト

【技術分野】

【0001】

本発明は、HKMG構造を有するトランジスタを備える半導体装置に関する。

【背景技術】

【0002】

ゲート絶縁膜とゲート絶縁膜上に形成されたゲート電極とを有するMISFET(Metal-Insulator-Semiconductor Field-Effect Transistor)においては、ゲート絶縁膜としてSi02からなるシリコン酸化膜を使用し、ゲート電極としてポリシリコン膜を使用するのが一般的であった。

【0003】

近年、MISFETの微細化に伴い、ゲート絶縁膜の薄膜化が進んでいる。ゲート絶縁膜の薄膜化が進むことで、ゲート電極にかかる電場が相対的に強くなり、ポリシリコン膜を使用したゲート電極の空乏化が問題となっている。また、ゲート絶縁膜の薄膜化が進むことで、チャネルを流れる電子がシリコン酸化膜によって形成される障壁をトンネルしてゲート電極に流れる、いわゆるトンネル電流の発生が問題となっている。

【0004】

そこで、特許文献1(特開2007−329237号公報)および特許文献2(特開2006−024594号公報)には、SiO2よりも誘電率の高い高誘電率材料からなる高誘電率ゲート絶縁膜(High−k絶縁膜)と金属材料からなるメタルゲート電極とを有するMISFETが開示されている。このMISFETによれば、メタルゲート電極によりゲート電極の空乏化を抑制することができ、また、High−k絶縁膜によりトンネル電流の発生を抑制することができる。High−k絶縁膜とメタルゲート電極とを有するMISFETを、HKMG構造を有するMISFETと称する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−329237号公報

【特許文献2】特開2006−024594号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

以下では、HKMG構造を有し、閾値電圧の異なる第1および第2のMISFETを半導体基板上に形成する工程について簡単に説明する。なお、半導体基板上の第1の領域に第1のMISFETが形成され、第1の領域に並ぶ第2の領域に第2のMISFETが形成されるものとする。

【0007】

まず、半導体基板上にHigh−k絶縁膜が堆積された後、第1のMISFETのメタルゲート電極の電極材料が堆積される。第1の領域以外に堆積された電極材料は除去され、第1の領域には、High−k絶縁膜と第1のMISFETのメタルゲート電極の電極材料とが積層された第1のゲートスタック層(第1のGS層)が形成される。

【0008】

次に、第2のMISFETのメタルゲート電極の電極材料が堆積された後、第2の領域以外に堆積された電極材料は除去され、第2の領域には、High−k絶縁膜と第2のMISFETのメタルゲート電極の電極材料とが積層された第2のゲートスタック層(第2のGS層)が形成される。その後、第1および第2のGS層に対して、MISFETのゲートとするために、エッチングなどのゲート加工が行われる。

【0009】

ここで、本願発明者は、ゲート加工時にGS層の残渣が生じ、その残渣により配線ショートが発生する可能性があるという問題を見出した。

【0010】

一般に、第1の領域以外に堆積された第1のMISFETのメタルゲート電極の電極材料は、High−k絶縁膜へのダメージを抑制するために、ウェットエッチングにより除去される。ここで、ウェットエッチングにより第1の領域側の電極材料までエッチングされ、第1の領域側の電極材料がえぐられたようなオーバーハング部が形成されることがある。オーバーハング部が形成されると、第2のMISFETのメタルゲート電極の電極材料の堆積時にオーバーハング部への入り込みが生じる。オーバーハング部に入り込んだ電極材料によりゲート加工時のエッチングが阻害され、第1の領域と第2の領域との境界にGS層の残渣が生じる。残渣にはメタルゲート電極の電極材料が含まれるため導電性を有しており、残渣が電位の異なる2つの配線と接するとショートが発生する。

【課題を解決するための手段】

【0011】

本発明の半導体装置は、

半導体基板と、

高誘電率材料を含む第1のゲート絶縁膜と前記第1のゲート絶縁膜上に形成された第1のメタルゲート電極とを備える第1のトランジスタが形成される前記半導体基板上の第1の領域と、

高誘電率材料を含む第2のゲート絶縁膜と前記第2のゲート絶縁膜上に形成された第2のメタルゲート電極とを備え、前記第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される前記半導体基板上の前記第1の領域に並ぶ第2の領域と、

電位の異なる第1および第2の配線と、を有し、

前記第1の領域と前記第2の領域との境界が、前記第1および第2の配線の少なくとも一方としか重ならない。

【発明の効果】

【0012】

本発明によれば、HKMG構造を有する第1のトランジスタが形成される第1の領域と、HKMG構造を有し、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される第2の領域との境界が、電位の異なる第1および第2の配線の少なくとも一方としか重ならないため、第1の領域と第2の領域との境界に残渣が発生しても、第1の配線と第2の配線との間でショートが発生するのを防ぐことができる。

【図面の簡単な説明】

【0013】

【図1】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図2】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図3】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図4】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図5】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図6】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図7】HKMG構造を有する第1および第2のMISFETのためのゲートスタック層を形成する工程を示す図である。

【図8】残渣により配線ショートが生じるメカニズムを説明するための図である。

【図9】本発明の一実施形態の半導体装置の構成を示すブロック図である。

【図10】図9に示す半導体装置の回路レイアウトの一例を示す図である。

【図11】関連する半導体装置における第1および第2のGS層のパターンと半導体基板上のウェルとの関係を示す図である。

【図12】図11に示す矩形領域の拡大図である。

【図13】本発明の一実施形態の半導体装置における第1および第2のGS層のパターンと半導体基板上のウェルとの関係を示す図である。

【図14】図13に示す矩形領域の拡大図である。

【図15】残渣によるショートの発生を防ぐ方法を説明するための図である。

【図16A】残渣によるショートの発生を防ぐ方法を説明するための図である。

【図16B】残渣によるショートの発生を防ぐ方法を説明するための図である。

【図17A】残渣によるショートの発生を防ぐ方法を説明するための図である。

【図17B】残渣によるショートの発生を防ぐ方法を説明するための図である。

【発明を実施するための形態】

【0014】

以下に、本発明を実施するための形態について図面を参照して説明する。

【0015】

まず、上述した残渣が生じるメカニズムを図1から図7を参照して詳細に説明する。なお、図1から図7において、同様の構成については同じ符号を付し、説明を省略する。

【0016】

図1に示すように、半導体基板としてのSi基板1に素子分離領域であるSTI(Shallow Trench Isolation)2が形成される。

【0017】

STI2の形成後、インターレイヤーとして、熱酸化によりシリコン酸化膜(SiO2)3が形成される。シリコン酸化膜3の形成後、SiO2よりも誘電率の高いHfO(酸化ハフニウム)、HfSiO(ハフニウムシリケート)などの高誘電率材料からなるHigh−k絶縁膜4が堆積される。

【0018】

High−k絶縁膜4の堆積後、第1のMISFETのメタルゲート電極の電極材料である窒化チタン膜(TiN)5が堆積される。窒化チタン膜5の堆積後、ポリシリコン膜6が堆積される。ポリシリコン膜6の堆積後、加工用のマスク材料としてシリコン酸化膜(SiO2)7が堆積される。シリコン酸化膜7の堆積後、第1の領域上にレジスト8が堆積される。

【0019】

図2に示すように、レジスト8の堆積後、リソグラフィなどによりパターニングが行われる。パターニング後、ドライエッチングによりシリコン酸化膜7の加工が行われる。その後、第1の領域以外に堆積されたシリコン酸化膜7を除去するために、ドライエッチングが行われる。シリコン酸化膜7の除去後、第1の領域以外に堆積された窒化チタン膜5およびポリシリコン膜6を除去するために、ウェットエッチングが行われる。具体的には、まず、アンモニア水によりポリシリコン膜6がエッチングされ、次に、APM(アンモニア過酸化水素水)により窒化チタン膜5がエッチングされる。

【0020】

ウェットエッチングにより第1の領域以外に堆積された窒化チタン膜5およびポリシリコン膜6は除去され、第1の領域には、第1の絶縁膜としてのHigh−k絶縁膜4、第1のメタルゲート電極としての窒化チタン膜5、ポリシリコン膜6が積層された第1のGS層9が形成される。

【0021】

ここで、図2に示すように、ウェットエッチングにより第1の領域に堆積されたポリシリコン膜6などもエッチングされ、オーバーハング部10が形成される。

【0022】

第1のGS層9の形成後、図3に示すように、酸化アルミニウム膜(AlO)11が堆積される。酸化アルミニウム膜11の堆積後、第2のMISFETのメタルゲート電極の電極材料である、窒化チタン膜5とは組成の異なる窒化チタン膜12が堆積される。酸化アルミニウム膜11および窒化チタン膜12が堆積されることで、第1のMISFETの閾値電圧と第2のMISFETの閾値電圧とが異なるものとなる。

【0023】

窒化チタン膜12の堆積後、ポリシリコン膜13が堆積される。ここで、図3に示すように、酸化アルミニウム膜11、窒化チタン膜12およびポリシリコン膜13のオーバーハング部10への入り込みが生じる。

【0024】

次に、図4に示すように、第2の領域上にレジスト14が堆積される。レジスト14の堆積後、リソグラフィなどによりパターニングが行われる。

【0025】

パターニング後、図5に示すように、第2の領域以外に堆積されたシリコン酸化膜7、酸化アルミニウム膜11、窒化チタン膜12およびポリシリコン膜13を除去するためにドライエッチングが行われ、第2の領域には、第2のゲート絶縁膜としてのHigh−k絶縁膜4、酸化アルミニウム膜11、第2のメタルゲート電極としての窒化チタン膜12、ポリシリコン膜13が積層された第2のGS層15が形成される。また、第1のGS層9と第2のGS層15との間には溝が形成され、この溝の底部に堆積されたシリコン酸化膜3、High−k絶縁膜4も除去される。ここで、図5に示すように、オーバーハング部10に入り込んだ酸化アルミニウム膜11、窒化チタン膜12およびポリシリコン膜13はエッチングされず、第1のGS層9の端部16に残る。

【0026】

第1のGS層9および第2のGS層15の形成後、図6に示すように、これらのGS層の間に形成された溝を埋めるように、ポリシリコン膜17が堆積される。なお、図6においては、ポリシリコン膜17は、第1および第2のGS層を覆うように堆積されているが、これらのGS層の間に形成された溝を埋めるようにだけ堆積されてもよい。

【0027】

ポリシリコン膜17の堆積後、W(タングステン)、WN(窒化タングステン)、WSi(タングステンシリサイド)からなるW/WN/WSi膜18が堆積される。W/WN/WSi膜18は配線となる。なお、ポリシリコン膜17が第1および第2のGS層の間に形成された溝を埋めるようにだけ堆積されている場合、配線となるのはW/WN/WSi膜18だけとなる。このような構造をBLG(Bit Line Gate)構造と称する。

【0028】

W/WN/WSi膜18の堆積後、加工用のマスク材料として、シリコン窒化膜(SiN)19が堆積され、その後、シリコン酸化膜(SiO)20が堆積される。シリコン酸化膜20の堆積後、レジスト21が堆積される。

【0029】

レジスト21の堆積後、リソグラフィなどによりシリコン窒化膜19およびシリコン酸化膜20のパターニングが行われる。パターニング後、図7に示すように、エッチングにより、第1のGS層9および第2のGS層15それぞれに対するゲート加工が行われる。

【0030】

ここで、上述したように、オーバーハング部10には、酸化アルミニウム膜11、窒化チタン膜12およびポリシリコン膜13といった第2のGS層15の材料の入り込みが生じている。オーバーハング部10に入り込んだ第2のGS層15の材料、特に、酸化アルミニウム膜11によりエッチングが阻害され、図7に示すように、第1のGS層9の端部に残渣22が生じる。なお、図7においては、簡略化のため、残渣22が第1のGS層9の端部に均一に生じているように記載しているが、実際には、不均一に生じる。また、残渣22の断面形状は、図7に示すような三角状に限定されるものではない。

【0031】

次に、残渣22により配線ショートが生じるメカニズムについて説明する。

【0032】

図8は、図7におけるシリコン膜窒化19、シリコン酸化膜20を除去した状態を示す図である。

【0033】

図8においては、電位の異なる2本の配線31a,31bが形成されているものとする。なお、配線31a,31bはそれぞれ、High−k絶縁膜4、窒化チタン膜5、ポリシリコン膜6、酸化アルミニウム膜11、窒化チタン膜12、ポリシリコン膜13,16、W/WN/WSi膜18などが積層されたものであるが、これらの記載は省略する。

【0034】

上述したように、図8においては点線で示される、第1のGS層の端部、すなわち、第1の領域と第2の領域との境界に残渣22が生じる。残渣22にはTiNなどが含まれているため導電性を有する。

【0035】

ここで、図8に示すように、残渣22が配線31aおよび配線31bと接すると、ポリシリコン膜13,16を介して配線31a,31bと電気的に接続され、これらの配線間でショートが発生する。

【0036】

次に、本実施形態における半導体装置の構成について説明する。

【0037】

図9は、本実施形態における半導体装置100の構成を示すブロック図である。

【0038】

図9に示す半導体装置100は、メモリセルアレイ(Memory Cell Array)101−1〜101−4と、ロウデコーダ(X Dec)102と、カラムデコーダ(Y Dec)103と、サブワード制御回路(SWC:Sub-word Control Circuit)104−1〜104−4と、サブワードドライバ(SWD:Sub-word Driver)105−1〜105−4と、BLEQ(Bit Line Equalizing)回路106−1〜106−4と、センスアンプ107−1〜107−4と、カラムスイッチ(Y-Switch)108−1〜108−4と、データアンプ(Data Amplifier)109と、出力回路(Output Circuit)110と、を有する。

【0039】

なお、メモリセルアレイ101−1に対応して、サブワード制御回路104−1、サブワードドライバ105−1、BLEQ回路106−1、センスアンプ107−1、および、カラムスイッチ(Y-Switch)108−1の各部が設けられている。また、メモリセルアレイ101−2〜101−4それぞれに対応して、上述した各部が同様の対応関係にて設けられている。そのため、以下では、メモリセルアレイ101−1とそれに対応する構成についてのみ説明する。また、図9においては、記載を省略したが、メモリセルアレイ101−1に対応して、複数のセンスアンプ107−1が設けられている。

【0040】

外部から与えられたアドレス信号および制御信号は、ロウデコーダ102、カラムデコーダ103、および、サブワード制御回路104−1に入力される。

【0041】

メモリセルアレイ101−1においては、複数のサブワード線と複数のビット線とが交差しており、この交点にメモリセルが配置されている。

【0042】

ロウデコーダ102は、外部から与えられた信号に基づき、メモリセルアレイ101に含まれるサブワード線のいずれかを選択する。

【0043】

カラムデコーダ103は、外部から与えられた信号に基づき、複数のセンスアンプのいずれかを選択する。

【0044】

サブワード制御回路104−1は、外部から与えられた信号に基づき、サブワードドライバ105−1、BLEQ回路106−1およびカラムスイッチ108−1に動作指示を行う。

【0045】

サブワードドライバ105−1は、サブワード制御回路104−1からの指示を受けて、ロウデコーダ102により選択されたサブワード線を駆動させる。

【0046】

BLEQ回路106−1は、サブワード制御回路104−1からの指示を受けて、センスアンプ107−1に電源を供給するための配線の電位をイコライズする。

【0047】

センスアンプ107−1は、カラムデコーダ103により選択されると、メモリセルアレイ101−1の対応するビット線に接続され、サブワード線およびビット線を介して出力されたデータを増幅して出力する。

【0048】

カラムスイッチ108−1は、ビット線とデータ入出力線との間に設けられ、サブワード制御回路104−1からの指示を受けて、オンまたはオフとなる。カラムスイッチ108−1がオンになると、センスアンプ107−1から出力されたデータが、データアンプ109に出力される。

【0049】

データアンプ109は、センスアンプ107−1から出力されたデータを増幅し、出力回路110に出力する。

【0050】

出力回路110は、データアンプ109から出力されたデータを半導体装置100の外部に出力する。

【0051】

図10は、図9に示す構成の半導体装置の回路レイアウトの一例を示す図である。

【0052】

図10に示すように、メモリセルアレイ101が形成される領域201の周辺に、センスアンプ107を構成するPチャネル型トランジスタが形成される領域202、センスアンプ107、BLEQ回路106を構成するNチャネル型トランジスタが形成される領域203、カラムスイッチ108を構成するPチャネル型トランジスタが形成される領域204、サブワード制御回路104を構成するPチャネル型トランジスタが形成される領域205、サブワード制御回路104を構成するNチャネル型トランジスタが形成される領域206、サブワードドライバ105を構成するPチャネル型トランジスタが形成される領域207、および、サブワードドライバ105を構成するNチャネル型トランジスタが形成される領域208が配置される。

【0053】

なお、図10においては、ロウデコーダ102、カラムデコーダ103、データアンプ109、および、出力回路110については記載を省略する。

【0054】

図10に示すような導電型の異なるトランジスタを形成する場合にも、一導電型としてのPチャネル型MISFETのための第1のGS層が形成される第1の領域と、他導電型としてのNチャネル型MISFETのための第2のGS層が形成される第2の領域と、の境界に残渣が生じることがある。

【0055】

図11は、図10に示す半導体装置における第1および第2のGS層のパターンと半導体基板上のウェル(素子領域)との関係の一例を示す図である。

【0056】

図11において、斜線で示される領域301は、nウェル領域を示す。

【0057】

一般に、設計の効率化のためにnウェルパターン上に、Pチャネル型MISFETのための第1のGS層が積層される。また、nウェルパターンは、Pチャネル型MISFETが形成される領域を接続するようにレイアウトされる。そのため、第1のGS層のパターンもnウェル領域のパターンに沿って延在する。その結果、第1のGS層のパターンの境界は、図11の点線で示されるようになる。

【0058】

上述したように、第1および第2のGS層の境界において残渣が生じるので、図11に示す点線に沿って残渣が生じる。残渣が電位の異なる複数の配線302に重なると、その配線間でショートが発生する。図11に示すnウェルパターンのレイアウトにおいては、実線矢印で示す複数の箇所で、第1のGS層の境界が電位の異なる2つの配線302と重なっており、これらの箇所では、配線間でショートが発生する可能性がある。

【0059】

図12は、図11に示す矩形領域Aの拡大図である。

【0060】

配線302−1は、内部電位Vppの配線であり、また、配線302−2は、電位VBLEQ(Bit Line Equalizing Voltage)、あるいは、電位VBLP(Bit Line Pre-charge Voltage)の配線である。なお、例えば、電位VBLEQは1.3Vであり、電位VBLPは0.48Vであり、電位Vppとは異なる電位である。

【0061】

拡散層303は、Pチャネル型MISFETあるいはNチャネル型MISFETのソース、ドレインとなる拡散層、コンタクトを介してウェルの電位を設定するための拡散層などを示す。

【0062】

図12に示すように、点線で示される第1のGS層の境界が、配線302−1および配線302−2と重なっている。なお、図12において、実線丸印は配線302−1と第1のGS層の境界との交点を示し、点線丸印は配線302−2と第1のGS層の境界との交点を示す。ここで、配線302−1と第1のGS層の境界との交点と、配線302−2と第1のGS層の境界との交点と、の間に第1のGS層の境界に沿って残渣が生じると、配線302−1と配線302−2との間でショートが発生するおそれがある。

【0063】

次に、本実施形態の半導体装置100における第1および第2のGS層のパターンと半導体基板上のウェルとの関係について説明する。

【0064】

図13は、本実施形態の半導体装置100における第1および第2のGS層のパターンと半導体基板上のウェルとの関係を示す図である。なお、図13において、図11と同様の構成については同じ符号を付し、説明を省略する。

【0065】

本実施形態の半導体装置100は、図11に示す半導体装置と比較して、第1のGS層が積層されるnウェルパターンが連続しておらず、島状に離れて形成されている点が異なる。nウェルパターンを島状に形成することで、第1のGS層の境界が電位の異なる2つの配線と重ならないようにすることができる。

【0066】

図14は、図13に示す矩形領域Bの拡大図である。なお、矩形領域Aと矩形領域Bとは、対応する位置関係にある。また、図14において、図12と同様の構成については同じ符号を付し、説明を省略する。

【0067】

上述したように、nウェルパターン、つまり、Pチャネル型MISFETが形成される領域は島状に離れて形成されている。そのため、図14に示すように、第1のGS層の境界が第1の配線としての配線302−1とは重なるが、第2の配線としての配線302−2とは重ならない。そのため、第1のGS層の境界に残渣が生じても、その残渣により配線302−1と配線302−2との間でショートが発生することを防ぐことができる。

【0068】

なお、nウェルパターンを島状に形成するようにしても、図13に示す、領域205の周辺箇所(箇所C)および領域202の周辺箇所(箇所D)において、残渣によるショートが発生する可能性がある。

【0069】

以下では、上述した箇所C,Dにおいて、残渣によるショートが発生しないようにする方法について説明する。

【0070】

まず、上述した箇所Cにおいて、残渣によるショートが発生しないようにするための方法について説明する。

【0071】

図15は、図13に示す箇所C付近の拡大図である。

【0072】

図15に示すように、電位の異なる配線302−3と配線302−4とが隣接している部分がある。この部分において、第1のGS層の境界が配線302−3および配線302−4と重なると、これらの配線間でショートが発生する可能性がある。ここで、一般に、配線302−3と配線302−4との間には180μm程度の間隔がある。そのため、ショートの発生を防ぐためには、その180μm程度の間隔に第1のGS層の境界が位置するようにすればよい。180μm程度の間隔にGS層の境界を位置させることは、例えば、KrF(エキシマレーザ)露光機を用いて実現可能である。

【0073】

次に、上述した箇所Dにおいて、残渣によるショートが発生しないようにするための方法について説明する。

【0074】

図16Aは、図13に示す箇所D付近の拡大図である。

【0075】

図16Aにおいて、配線302−5はnウェル電位の配線であり、配線302−6は電位VBLPの配線である。また、実線丸印は、配線302−5と第1のGS層の境界との交点を示し、点線丸印は、配線302−6と第1のGS層の境界との交点を示す。

【0076】

図16Aに示すように、第1のGS層の境界が、配線302−5および配線302−6と重なっている。ここで、配線302−5と第1のGS層の境界との交点と、配線302−6と第1のGS層の境界との交点と、の間に第1のGS層の境界に沿って残渣が生じると、これらの配線間でショートが発生する。

【0077】

そこで、図16Bに示すように、配線302−5および配線302−6のレイアウトを変更することで、第1のGS層の境界に残渣が生じても、ショートが発生しないようにすることができる。具体的には、図16Aにおいて、配線302−6の右側の領域に延在する配線302−5を無くし、その領域に図16Bに示すように、配線302−6が延在するようにレイアウト変更することで、第1のGS層の境界が配線302−5とは重なるが、配線302−6とは重ならないようにすることができる。そのため、第1のGS層の境界で残渣が生じても、ショートが発生するのを防ぐことができる。

【0078】

上述した箇所Dにおいて残渣によるショートが生じないようにするための方法についてより詳細に説明する。

【0079】

図17Aは、図16Aに示す矩形領域Eの拡大図である。

【0080】

図17Aにおいては、配線302−5,302−6とは異なる層に形成された配線304および配線304と配線302−5,302−6とを接続するコンタクト305を記載している。なお、配線304としては、nウェル電位の配線や、電位VBLPの配線などがある。配線302−5は、配線304のうち、nウェル電位の配線とコンタクト305−1を介して接続され、nウェル電位となる。また、配線302−6は、電位VBLPの配線とコンタクト305−2を介して接続され、電位VBLPとなる。

【0081】

図17Bは、図16Bに示す矩形領域Fの拡大図である。なお、矩形領域Fは矩形領域Eに対応する領域である。

【0082】

図16Bに示すように、配線302−5および配線302−6のレイアウトを変更することで、第1のGS層の境界が配線302−5としか重ならないようにしている。配線302−5および配線302−6のレイアウトの変更に伴い、コンタクト305−1,305−2のレイアウトも変更する必要がある。具体的には、図17Aの破線で囲まれる配線302−6が延在していた領域に設けられていたコンタクト305−2の位置を、図17Bの実線で囲まれる領域に変更する。なお、図17Aと図17Bとで、2つのコンタクト305−2の間隔は保持されている。また、図17Aの点線で囲まれる領域に設けられていた、配線302−6の右側に延在していた配線302−5とnウェル電位の配線304とを接続するコンタクト305−1を削除する。こうすることで、配線302−5はnウェル電位とし、配線302−6は電位VBLPとすることができる。

【0083】

このように本実施形態によれば、半導体装置100は、高誘電率材料を含むHigh−k絶縁膜とHigh−k絶縁膜上に形成されたメタルゲート電極とを備える第1のトランジスタが形成されるSi基板1上の第1の領域と、High−k絶縁膜とHigh−k絶縁膜上に形成されたメタルゲート電極とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成されるSi基板1上の第2の領域と、電位の異なる第1および第2の配線と、を有し、第1および第2の領域の境界が、第1および第2の配線の少なくとも一方としか重ならない。

【0084】

そのため、第1および第2の領域の境界に沿って残渣が生じても、その残渣が電位の異なる2つの配線と接することがなくなるので、配線間でショートが発生するのを防ぐことができる。

【符号の説明】

【0085】

1 Si基板

2 STI

3 シリコン酸化膜

4 High−k絶縁膜

5 窒化チタン膜

6 ポリシリコン膜

7 シリコン酸化膜

8,14,21 レジスト

9 第1のGS層

10 オーバーハング部

11 酸化アルミニウム膜

12 窒化チタン膜

13 ポリシリコン膜

15 第2のGS層

16 第1のGS層の端部

17 ポリシリコン膜

18 W/WN/WSi膜

19 シリコン窒化膜

20 シリコン酸化膜

22 残渣

31a,31b 配線

100 半導体装置

101−1〜101−4 メモリセルアレイ

102 ロウデコーダ

103 カラムデコーダ

104−1〜104−4 サブワード制御回路

105−1〜105−4 サブワードドライバ

106−1〜106−4 BLEQ回路

107−1〜107−4 センスアンプ

108−1〜108−4 カラムスイッチ

109 データアンプ

110 出力回路

201 メモリセルアレイ形成領域

202,204,205,207 Pチャネル型トランジスタ形成領域

203,206,208 Nチャネル型トランジスタ形成領域

301 nウェル領域

302,302−1〜302−6 配線

303 拡散層

304 配線

305−1,305−2 コンタクト

【特許請求の範囲】

【請求項1】

半導体基板と、

高誘電率材料を含む第1のゲート絶縁膜と前記第1のゲート絶縁膜上に形成された第1のメタルゲート電極とを備える第1のトランジスタが形成される前記半導体基板上の第1の領域と、

高誘電率材料を含む第2のゲート絶縁膜と前記第2のゲート絶縁膜上に形成された第2のメタルゲート電極とを備え、前記第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される前記半導体基板上の前記第1の領域に並ぶ第2の領域と、

電位の異なる第1および第2の配線と、を有し、

前記第1の領域と前記第2の領域との境界が、前記第1および第2の配線の少なくとも一方としか重ならないことを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置において、

前記第1のゲート絶縁膜と前記第2のゲート絶縁膜とは同じ高誘電率材料からなり、

前記第1のトランジスタのゲートは、前記高誘電率材料が前記半導体基板上に堆積された後、前記第1のメタルゲート電極の電極材料が堆積され、前記第1の領域以外に堆積された前記第1のメタルゲート電極の電極材料が除去されることで形成され、

前記第2のトランジスタのゲートは、前記第1のメタルゲート電極の電極材料の除去後、前記第2のメタルゲート電極の電極材料が堆積され、前記第2の領域以外に堆積された前記第2のメタルゲート電極の電極材料が除去されることで形成されることを特徴とする半導体装置。

【請求項3】

請求項1または2記載の半導体装置において、

前記第1および第2のトランジスタは、導電型が異なることを特徴とする半導体装置。

【請求項1】

半導体基板と、

高誘電率材料を含む第1のゲート絶縁膜と前記第1のゲート絶縁膜上に形成された第1のメタルゲート電極とを備える第1のトランジスタが形成される前記半導体基板上の第1の領域と、

高誘電率材料を含む第2のゲート絶縁膜と前記第2のゲート絶縁膜上に形成された第2のメタルゲート電極とを備え、前記第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される前記半導体基板上の前記第1の領域に並ぶ第2の領域と、

電位の異なる第1および第2の配線と、を有し、

前記第1の領域と前記第2の領域との境界が、前記第1および第2の配線の少なくとも一方としか重ならないことを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置において、

前記第1のゲート絶縁膜と前記第2のゲート絶縁膜とは同じ高誘電率材料からなり、

前記第1のトランジスタのゲートは、前記高誘電率材料が前記半導体基板上に堆積された後、前記第1のメタルゲート電極の電極材料が堆積され、前記第1の領域以外に堆積された前記第1のメタルゲート電極の電極材料が除去されることで形成され、

前記第2のトランジスタのゲートは、前記第1のメタルゲート電極の電極材料の除去後、前記第2のメタルゲート電極の電極材料が堆積され、前記第2の領域以外に堆積された前記第2のメタルゲート電極の電極材料が除去されることで形成されることを特徴とする半導体装置。

【請求項3】

請求項1または2記載の半導体装置において、

前記第1および第2のトランジスタは、導電型が異なることを特徴とする半導体装置。

【図9】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16A】

【図16B】

【図17A】

【図17B】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16A】

【図16B】

【図17A】

【図17B】

【公開番号】特開2013−69863(P2013−69863A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−207329(P2011−207329)

【出願日】平成23年9月22日(2011.9.22)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月22日(2011.9.22)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]