半導体装置

【課題】電子走行層にFeが入り込むことを抑制し、半導体層等にクラックの発生が抑制される電界効果型トランジスタを提供する。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関するものである。

【背景技術】

【0002】

窒化物半導体であるGaN、AlN、InN等または、これらの混晶である材料は、広いバンドギャップを有しており、高出力電子デバイスまたは短波長発光デバイス等として用いられている。このうち、高出力デバイスとしては、電界効果型トランジスタ(FET:Field-Effect Transistor)、特に、高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)に関する技術が開発されている(例えば、特許文献1)。このような窒化物半導体を用いたHEMTは、高出力・高効率増幅器、大電力スイッチングデバイス等に用いられる。

【0003】

このような窒化物半導体を用いたHEMTは、基板上に、窒化アルミニウムガリウム/窒化ガリウム(AlGaN/GaN)ヘテロ構造が形成されており、GaN層を電子走行層とするものである。尚、基板としては、サファイア、シリコンカーバイド(SiC)、窒化ガリウム(GaN)、シリコン(Si)等の基板が用いられる。

【0004】

窒化物半導体において、GaNは、高い飽和電子速度や広いバンドギャップを有しており、高い耐圧特性を得ることができるため、優れた電気的特性を有している。また、GaNは、結晶構造がウルツ鉱型であるため、c軸に平行な<0001>方向に極性を有しており、更に、AlGaN/GaNのヘテロ構造を形成した場合には、AlGaN層には、AlGaNとGaNとの格子歪みによるピエゾ分極が励起される。このため、チャネルとなる界面近傍には、高濃度の2DEG(Two-Dimensional Electron Gas:2次元電子ガス)が生じる。よって、このようなGaNを用いたHEMTは、高周波・電力用デバイスとして有望とされている。

【0005】

ところで、GaN系の半導体層においては、適量のFeをドーピングすることにより、高抵抗化させることができることが知られている。これは、GaNの価電子帯近傍において、Feにより深いアクセプタ準位が形成されることに起因している。このため、GaN等の半導体材料を用いたHEMTにおいては、電子走行層の下層にFeをドーピングすることにより、縦リークの防止、ピンチオフ特性の改善等をすることができるため、HEMTの特性を向上させることができる。

【0006】

図1には、GaNを用いたHEMTにおいて、Feがドープされている高抵抗層が設けられている構造のものを示す。具体的には、基板911上に、AlN等により形成された核形成層912、AlGaN等により形成されたバッファ層913が形成され、この上に、高抵抗層914、電子走行層915、電子供給層916がエピタキシャル成長により形成されている。高抵抗層914はFeがドープされているGaN(FeドープGaN)等により形成されており、電子走行層915はGaN等により形成されており、電子供給層916はAlGaN等により形成されている。電子供給層916の上には、ゲート電極921、ソース電極922及びドレイン電極923が形成されている。このような構造のGaNを用いたHEMTにおいては、高抵抗層914にドープされるFeが表面に偏析しており、電子走行層915の成長中に順次取り込まれるため、電子走行層915中にもFeが入り込んでしまう。このように電子走行層915中に多くのFeが入り込んでしまうと、チャネル電子がトラップされ、2DEG濃度の低下や不純物散乱効果による移動度の低下等を招き、電気的特性が低下してしまう。

【0007】

このため、Feがドープされる高抵抗層914と電子走行層915との間に、Feの取り込み効果の高いAlNやAlGaNにより形成された中間層を形成することにより、電子走行層915にFeが入り込むことを防いだ構造のものが開示されている(例えば、特許文献2、3)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−359256号公報

【特許文献2】特開2010−182872号公報

【特許文献3】特開2010−232297号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、電子走行層にFeが入り込むことを防ぐためには、AlNやAlGaNにより形成された中間層の膜厚をある程度厚く形成する必要がある。また、中間層をAlGaNにより形成する場合には、Al組成比が高い方が好ましく、引用文献2においてはAlの組成比は0.4以上のもの、引用文献3においてはAlの組成比は0.3以上のものが記載されている。

【0010】

ところで、基板にGaNとの格子不整合率の高い基板、例えば、Si基板を用いた場合には、基板となるSi基板の上に、GaNよりも格子定数の小さいAlNやAlGaN等のバッファ層を形成し、バッファ層の上に、GaN等の電子走行層が形成されている。このように、バッファ層を形成することにより、Si基板の上に形成されているGaN等の半導体積層膜と基板全体の応力とのバランスをとり、基板の反りや半導体積層膜等におけるクラックの発生を抑制することができる。この中間層は、結晶成長によりバッファ層の上に形成されるが、中間層がAlNや比較的Al組成の高いAlGaNの場合、中間層は、中間層よりも格子定数の大きなバッファ層の上に形成される。このため、中間層は、バッファ層から受ける引張歪により無歪状態よりも格子間隔が広がるため、中間層等にクラックを発生させることなく、所望の膜厚を形成することは困難である。尚、AlNの格子定数は、a軸3.11Å、c軸4.98Åであり、GaNの格子定数は、a軸3.18Å、c軸5.17Åである。

【0011】

よって、半導体材料としてGaN等の窒化物半導体を用いた電界効果トランジスタ等の半導体装置において、電子走行層にFeが入り込むことが抑制されており、また、半導体層におけるクラック等の発生を防ぐことのできる半導体装置が求められている。

【課題を解決するための手段】

【0012】

本実施の形態の一観点によれば、基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、前記高抵抗層の上に形成された多層中間層と、前記多層中間層の上に半導体材料により形成された電子走行層と、前記電子走行層の上に半導体材料により形成された電子供給層と、を有し、前記多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする。

【0013】

また、本実施の形態の他の一観点によれば、基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、前記高抵抗層の上に形成された中間層と、前記中間層の上に半導体材料により形成された電子走行層と、前記電子走行層の上に半導体材料により形成された電子供給層と、を有し、前記中間層はAlGaNにより形成されており、AlXGa1−XNとした場合、0<X<0.3であることを特徴とする。

【発明の効果】

【0014】

開示の半導体装置によれば、電界効果型トランジスタ等において、電子走行層にFeが入り込むことを抑制することができ、また、半導体層のクラック等の発生を防ぐことができるため、歩留りが高く良好な電気的特性を得ることができる。

【図面の簡単な説明】

【0015】

【図1】Feがドープされた層を有する半導体装置の構造図

【図2】AlNなし半導体積層膜とAlNありの半導体積層膜の説明図

【図3】半導体積層膜のSIMSによる分析結果

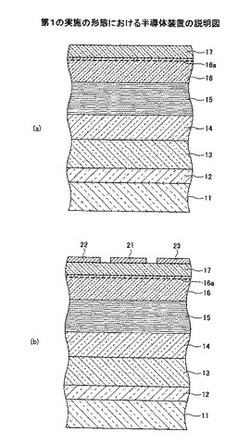

【図4】第1の実施の形態における半導体装置の説明図

【図5】多層中間層の構造図

【図6】第1の実施の形態における半導体装置におけるFeの入り込みの説明図

【図7】第2の実施の形態における半導体装置の説明図

【図8】第3の実施の形態における半導体装置の構造図

【図9】第4の実施の形態における半導体装置の構造図

【図10】第5の実施の形態におけるディスクリートパッケージされた半導体デバイスの説明図

【図11】第5の実施の形態における電源装置の回路図

【図12】第5の実施の形態における高出力増幅器の構造図

【発明を実施するための形態】

【0016】

実施するための形態について、以下に説明する。尚、同じ部材等については、同一の符号を付して説明を省略する。

【0017】

〔第1の実施の形態〕

最初に、AlN層を設けられている場合と、設けられていない場合において、電子走行層へのFeの入り込み量について説明する。図2に示されHEMTを形成するための半導体積層膜において、AlN層が設けられているものとAlNが設けられていないものとを作製し、SIMS(Secondary Ion-microprobe Mass Spectrometer:2次イオン質量分析)による測定を行なった。図3には、これらの半導体積層膜におけるSIMSにより測定された深さ方向におけるFe濃度のプロファイルを示す。図2(a)は、AlN層が設けられていない半導体積層膜(AlNなし半導体積層膜)の構造を示すものであり、基板911上に、核形成層912、バッファ層913、高抵抗層914、電子走行層915、電子供給層916が形成されているものである。図2(b)は、AlN層が設けられている半導体積層膜(AlNあり半導体積層膜)の構造を示すものであり、基板911上に、核形成層912、バッファ層913、高抵抗層914、中間層930、電子走行層915、電子供給層916が形成されているものである。尚、高抵抗層914は、不純物元素としてFeがドープされているGaNにより形成されており、膜厚が約300nmであり、ドープされているFeの濃度は、約1×1018cm−3である。また、電子走行層915は、膜厚が約600nmのGaNにより形成されており、電子供給層916は、膜厚が約20nmのAlGaNにより形成されている。また、図2(b)に示されるAlNあり半導体積層膜の場合には、中間層930は、約5nmのAlNにより形成されている。図3は、電子走行層916からバッファ層913までの間において、深さ方向にSIMSにより測定した結果を示すものである。尚、図3において図示はされていないが、AlNあり半導体積層膜の場合においては、高抵抗層914と電子走行層915との間に中間層930が形成されている。

【0018】

AlNなし半導体積層膜の場合では、電子供給層916と電子走行層915との界面近傍までFeが入り込んでおり、このFeの濃度は、2×1016cm−3よりも多い。これに対し、AlNあり半導体積層膜の場合では、Feの濃度は、高抵抗層914と電子走行層915との間に形成されたAlNにより形成されている中間層930が形成されている領域にピークを示しており、中間層930にFeが多く取り込まれている。このため、電子走行層915に入り込んでいるFeの量は、AlNなし半導体積層膜と比べると少なくなっている。このように、AlNにより形成されている中間層930を設けることにより、電子走行層915にFeが入り込む量を減らすことができる。

【0019】

(半導体装置)

次に、第1の実施の形態における半導体装置について説明する。本実施の形態における半導体装置は、AlGaN/GaNシングルへテロ構造のHEMTである。

【0020】

本実施の形態における半導体装置は、最初に、図4(a)に示すように、基板11上に、窒化物半導体層である核形成層12、バッファ層13、高抵抗層14、多層中間層15、電子走行層16、電子供給層17を順次積層形成する。具体的には、まず、基板11を水素雰囲気中で数分間熱処理を行なう。この後、基板11上に、核形成層12、バッファ層13、高抵抗層14、多層中間層15、電子走行層16、電子供給層17をMOVPE(Metal Organic Vapor Phase Epitaxy)法によりエピタキシャル成長させることにより形成する。これにより、電子走行層16において、電子走行層16と電子供給層17との界面近傍には、2DEG16aが形成される。この際、Gaの原料ガスにはTMG(トリメチルガリウム)が用いられ、Alの原料ガスにはTMA(トリメチルアルミニウム)が用いられ、Nの原料ガスにはNH3(アンモニア)が用いられる。また、不純物元素としてドープされるFeの原料ガスにはCp2Fe(シクロペンタジエニル鉄、通常、フェロセン)が用いられる。尚、これらの原料ガスは、水素(H2)をキャリアガスとしてMOVPE装置の反応炉に供給される。

【0021】

基板11は、サファイア、Si、SiC等の材料により形成されており、本実施の形態では、例えば、Si等により形成されている。尚、基板11側への電流リークを防ぐため抵抗の高いものを用いることが好ましい。

【0022】

核形成層12は、膜厚が100〜200nmのAlN層により形成されている。

【0023】

バッファ層13は、AlGaN層により形成されており、本実施の形態では、Al組成比の異なるAlGaNを積層することにより形成されている。具体的には、最初に、Al組成比が相対的に高いAl0.7Ga0.3Nにより形成される層を形成し、この後、Al組成比が相対的に低いAl0.3Ga0.7Nにより形成される層を形成する。尚、バッファ層13は、組成比の異なる3層以上のAlGaNにより形成してもよい。また、このような構造以外にも、GaN/AlNを交互に形成した周期構造を有する超格子バッファや、AlNからGaNに至るまでAlの組成比を変化させた組成傾斜構造により形成してもよい。基板11に起因する転位を低減するためには、バッファ層13の膜厚は厚ほど好ましいが、クラックの発生を防ぐためには、あまり厚くない方が好ましい。よって、バッファ層13の膜厚は、200〜1000nmが好ましい。

【0024】

高抵抗層14は、膜厚が100〜300nmであって、高抵抗となる不純物元素としてFeがドープされているGaN、AlNまたは、AlGaNにより形成されている。高抵抗層14におけるFeのドーピング濃度は、5×1017〜1×1019cm−3、より好ましくは、1×1018cm−3である。尚、本願において高抵抗となる不純物元素とは、GaN、AlNまたは、AlGaN等の窒化物半導体にドープすることにより、窒化物半導体における抵抗を高くすることのできる不純物元素を意味する。

【0025】

多層中間層15は、図5に示されるように、GaN層15aとAlN層15bとを交互に積層形成した構造のものであり、膜厚が500〜1000nmとなるように形成されている。多層中間層15においては、基板11を含む全体の応力バランスの低下を防ぐため、GaN層15aの膜厚はAlN層15bの膜厚よりも厚く形成されていることが好ましい。具体的には、GaN層15aの膜厚は20〜50nmが好ましく、AlN層15bの膜厚は2〜5nmが好ましい。尚、本実施の形態においては、多層中間層15は、膜厚が約20nmのGaN層15aと、膜厚が約2nmのAlN層15bとを交互に20周期以上成長させることにより形成する。また、Feが電子走行層16に入り込むことを効果的に防ぐためには、積算されるAlN層15bは一定の膜厚以上形成されていることが好ましく、経験等に基づくならば、積算されるAlN層15bの膜厚が40nm以上となるように形成されていることが好ましい。

【0026】

電子走行層16は、GaNにより形成されており、転位等に起因する電子濃度や移動度の低下を避けるためには、所定の値以上の膜厚で形成されていることが好ましく、膜厚が500〜1000nmとなるように形成されている。

【0027】

電子供給層17は、膜厚が約20nmのAlGaNにより形成されている。尚、電子供給層17は、格子不整合による結晶性低下を避けるため、AlXGa1−XNと表現した場合に、Xの値が0.3以下となるように形成されている。

【0028】

次に、図4(b)に示すように、電子供給層17の上に、ゲート電極21、ソース電極22及びドレイン電極23を形成する。これにより、本実施の形態における半導体装置を作製することができる。

【0029】

図6は、本実施の形態における半導体装置であるHEMTと図1に示される構造のHEMTについて、高抵抗層と電子走行層との間におけるFe濃度を示すものである。図6に示されるように、本実施の形態におけるHEMT5Aにおいては、多層中間層15におけるAlN層15bにおいてFeが多く取り込まれる。よって、HEMT5Aにおける電子走行層16に入り込むFeの濃度は、図1に示される構造のHEMT5Bにおける電子走行層915に入り込むFeの濃度よりも低くすることができる。これにより、本実施の形態における半導体装置であるHEMTは、電子走行層16を高抵抗化させることはなく、電気的特性の低下を防ぐことができる。

【0030】

また、本実施の形態では、GaN層15aとAlN層15bを交互に積層した多層構造の多層中間層15を形成しているため、応力の発生が少なく、基板11の反りや半導体層等におけるクラックの発生を抑制することができる。

【0031】

よって、本実施の形態における半導体装置においては、歩留りが高く良好な電気的特性を得ることができる。

【0032】

〔第2の実施の形態〕

次に、第2の実施の形態における半導体装置について説明する。本実施の形態における半導体装置は、AlGaN/GaNシングルへテロ構造のHEMTである。

【0033】

本実施の形態における半導体装置は、最初に、図7(a)に示すように、基板11上に、窒化物半導体層を積層形成する。即ち、基板11上に、核形成層12、バッファ層13、第1の高抵抗層114、第1の多層中間層115、第2の高抵抗層124、第2の多層中間層125、電子走行層16、電子供給層17を順次積層形成する。具体的には、まず、基板11を水素雰囲気中で数分間熱処理を行なう。この後、基板11上に、核形成層12、バッファ層13、第1の高抵抗層114、第1の多層中間層115、第2の高抵抗層124、第2の多層中間層125、電子走行層16、電子供給層17をMOVPE法によりエピタキシャル成長させることにより形成する。これにより、電子走行層16において、電子走行層16と電子供給層17との界面近傍には、2DEG16aが形成される。この際、Gaの原料ガスにはTMGが用いられ、Alの原料ガスにはTMAが用いられ、Nの原料ガスにはNH3が用いられる。また、不純物元素としてドープされるFeの原料ガスにはCp2Feが用いられる。尚、これらの原料ガスは、水素をキャリアガスとしてMOVPE装置の反応炉に供給される。

【0034】

第1の高抵抗層114は、膜厚が100〜300nmであって、高抵抗となる不純物元素としてFeがドープされているGaN、AlNまたは、AlGaNにより形成されている。第1の高抵抗層114におけるFeのドーピング濃度は、5×1017〜1×1019cm−3、より好ましくは、1×1018cm−3である。

【0035】

第1の多層中間層115は、図5に示されるように、GaN層15aとAlN層15bとを交互に積層形成した構造のものであり、膜厚が500〜1000nmとなるように形成されている。第1の多層中間層115においては、基板11を含む全体の応力バランスの低下を防ぐため、GaN層15aの膜厚はAlN層15bの膜厚よりも厚く形成されていることが好ましい。具体的には、GaN層15aの20〜50nmが好ましく、AlN層15bの膜厚は2〜5nmが好ましい。尚、本実施の形態においては、第1の多層中間層115は、膜厚が約20nmのGaN層15aと膜厚が約2nmのAlN層15bとを交互に20周期以上成長させることにより形成されている。また、Feが電子走行層16に入り込むことを効果的に防ぐためには、積算されるAlN層15bは一定の膜厚以上形成されていることが好ましく、経験等に基づくならば、積算されるAlN層15bの膜厚が40nm以上となるように形成されていることが好ましい。

【0036】

第2の高抵抗層124は、膜厚が50〜100nmであって、高抵抗となる不純物元素としてFeがドープされているGaN、AlNまたは、AlGaNにより形成されている。第2の高抵抗層124におけるFeのドーピング濃度は、1×1017〜1×1018cm−3である。第2の高抵抗層124は、電子走行層16において、Feが過剰に取り込まれることによる走行電子に与える悪影響を避けるため、第1の高抵抗層114よりもFeのドーピング濃度が低く形成されている。具体的には、例えば、Feのドーピング濃度が、5×1017cm−3となるように形成されている。また、第2の高抵抗層124の膜厚は、第1の高抵抗層114の膜厚よりも薄く形成されていることが好ましい。

【0037】

第2の多層中間層125は、図5に示すように、GaN層15aとAlN層15bとを交互に積層形成した構造のものであり、膜厚が125〜500nmとなるように形成されている。第2の多層中間層125においては、GaN層15aの膜厚はAlN層15bの膜厚よりも厚く形成されていることが好ましく、具体的には、GaN層15aの20〜50nmが好ましく、AlN層15bの膜厚は2〜5nmが好ましい。尚、本実施の形態においては、第2の多層中間層125は、膜厚が約30nmのGaN層15aと膜厚が約2nmのAlN層15bとを交互に5〜10周期成長させることにより形成されている。また、本実施の形態では、第1の高抵抗層114よりも第2の高抵抗層124におけるFeの濃度が低いため、第2の多層中間層125におけるAlN層15bの膜厚の比率は、第1の多層中間層115におけるAlN層15bの膜厚の比率よりも小さくなっている。言い換えるならば、第2の多層中間層125における(GaN層の膜厚)/(AlN層の膜厚)の膜厚比は、第1の多層中間層115における(GaN層の膜厚)/(AlN層の膜厚)の膜厚比よりも、大きくなるように形成されている。

【0038】

電子走行層16は、GaNにより形成されており、転位等に起因する電子濃度や移動度の低下を避けるためには、所定の値以上の膜厚で形成されていることが好ましく、膜厚が500〜800nmとなるように形成されている。本実施の形態では、第1の多層膜中間層115及び第2の多層中間層125等を形成することにより転位の発生が大きく抑制されるため、第1の実施の形態における半導体装置よりも、電子走行層16の膜厚を薄くすることができる。よって、本実施の形態における半導体装置は、電子走行層16の結晶性を確保しつつ、電子走行層16の膜厚を薄くすることができるため、ピンチオフ特性を改善することができる。

【0039】

次に、図7(b)に示すように、電子供給層17の上に、ゲート電極21、ソース電極22及びドレイン電極23を形成する。これにより、本実施の形態における半導体装置を作製することができる。

【0040】

本実施の形態では、第1の高抵抗層114及び第2の高抵抗層124を設けることのより、縦リークを抑制することができ、電子走行層16の膜厚を薄くすることができるため、ピンチオフ特性を改善することができる。

【0041】

尚、上記以外の内容については、第1の実施の形態と同様である。

【0042】

〔第3の実施の形態〕

次に、第3の実施の形態について説明する。本実施の形態における半導体装置は、第1の実施の形態における多層中間層15に代えて、AlNとGaNとの混晶により形成された混晶中間層を有するものである。

【0043】

図8に基づき本実施の形態における半導体装置について説明する。本実施の形態における半導体装置は、基板11上に、核形成層12、バッファ層13、高抵抗層14、混晶中間層215、電子走行層16、電子供給層17を順次積層形成したものである。

【0044】

混晶中間層215は、膜厚が500〜1000nmのAlNとGaNとの混晶により形成されており、混晶中間層215の組成は、AlXGa1−XNとすると、0<X<0.3、より好ましくは、0.04≦X≦0.25となるように形成されている。混晶中間層215において僅かでもAlを含んでいれば、Feを取り込むことができ、電子走行層16にFeが入り込むことを防ぐことができる。また、X<0.3であれば、応力の発生も少ないため、基板11の反りや積層されている半導体層におけるクラックの発生を抑制することができる。

【0045】

尚、上記以外の内容については、第1の実施の形態と同様である。

【0046】

〔第4の実施の形態〕

次に、第3の実施の形態における半導体装置について、図9に基づき説明する。本実施の形態における半導体装置は、電子供給層17上にゲート絶縁膜となる絶縁膜330が形成されている構造のものである。このような絶縁膜330を形成することにより、ゲートリーク電流を減らすことができる。絶縁膜330としては、例えば、Al2O3(酸化アルミニウム)等が用いられる。

【0047】

本実施の形態における半導体装置は、第1の実施の形態における図4(a)まで形成したものの電子供給層17上に、ソース電極22及びドレイン電極23を形成し、この後、ゲート絶縁膜となる絶縁膜330を形成する。絶縁膜330の形成方法としては、CVD(Chemical Vapor Deposition)、ALD(Atomic Layer Deposition)、スパッタリング等が挙げられる。

【0048】

この後、絶縁膜330上の所定の領域に、ゲート電極21を形成する。これにより、本実施の形態における半導体装置を製造することができる。また、ゲート電極21が形成される領域に凹形状のゲートリセスを形成し、ゲートリセスの内部を含む領域にゲート電極21を形成したものであってもよい。

【0049】

尚、上記以外の内容は、第1の実施の形態と同様である。また、本実施の形態は、第2の実施の形態及び第3の実施の形態における半導体装置においても、同様に適用することができる。

【0050】

〔第5の実施の形態〕

次に、第5の実施の形態について説明する。本実施の形態は、半導体デバイス、電源装置及び高周波増幅器である。

【0051】

本実施の形態における半導体デバイスは、第1から第4の実施の形態におけるいずれかの半導体装置をディスクリートパッケージしたものであり、このようにディスクリートパッケージされた半導体デバイスについて、図10に基づき説明する。尚、図10は、ディスクリートパッケージされた半導体装置の内部を模式的に示すものであり、電極の配置等については、第1から第4の実施の形態に示されているものとは、異なっている。

【0052】

最初に、第1から第4の実施の形態において製造された半導体装置をダイシング等により切断することにより、GaN系の半導体材料のHEMTの半導体チップ410を形成する。この半導体チップ410をリードフレーム420上に、ハンダ等のダイアタッチ剤430により固定する。尚、この半導体チップ410は、第1から第4の実施の形態における半導体装置に相当するものである。

【0053】

次に、ゲート電極411をゲートリード421にボンディングワイヤ431により接続し、ソース電極412をソースリード422にボンディングワイヤ432により接続し、ドレイン電極413をドレインリード423にボンディングワイヤ433により接続する。尚、ボンディングワイヤ431、432、433はAl等の金属材料により形成されている。また、本実施の形態においては、ゲート電極411はゲート電極パッドであり、第1から第4の実施の形態における半導体装置のゲート電極21と接続されている。また、ソース電極412はソース電極パッドであり、第1から第4の実施の形態における半導体装置のソース電極22と接続されている。また、ドレイン電極413はドレイン電極パッドであり、第1から第4の実施の形態における半導体装置のドレイン電極23と接続されている。

【0054】

次に、トランスファーモールド法によりモールド樹脂440による樹脂封止を行なう。このようにして、GaN系の半導体材料を用いたHEMTのディスクリートパッケージされている半導体デバイスを作製することができる。

【0055】

次に、本実施の形態における電源装置及び高周波増幅器について説明する。本実施の形態における電源装置及び高周波増幅器は、第1から第4の実施の形態における半導体装置のいずれかを用いた電源装置及び高周波増幅器である。

【0056】

最初に、図11に基づき、本実施の形態における電源装置について説明する。本実施の形態における電源装置460は、高圧の一次側回路461、低圧の二次側回路462及び一次側回路461と二次側回路462との間に配設されるトランス463を備えている。一次側回路461は、交流電源464、いわゆるブリッジ整流回路465、複数のスイッチング素子(図11に示す例では4つ)466及び一つのスイッチング素子467等を備えている。二次側回路462は、複数のスイッチング素子(図11に示す例では3つ)468を備えている。図11に示す例では、第1から第4の実施の形態における半導体装置を一次側回路461のスイッチング素子466及び467として用いている。尚、一次側回路461のスイッチング素子466及び467は、ノーマリーオフの半導体装置であることが好ましい。また、二次側回路462において用いられているスイッチング素子468はシリコンにより形成される通常のMISFET(metal insulator semiconductor field effect transistor)を用いている。

【0057】

次に、図12に基づき、本実施の形態における高周波増幅器について説明する。本実施の形態における高周波増幅器470は、例えば、携帯電話の基地局用パワーアンプに適用してもよい。この高周波増幅器470は、ディジタル・プレディストーション回路471、ミキサー472、パワーアンプ473及び方向性結合器474を備えている。ディジタル・プレディストーション回路471は、入力信号の非線形歪みを補償する。ミキサー472は、非線形歪みが補償された入力信号と交流信号とをミキシングする。パワーアンプ473は、交流信号とミキシングされた入力信号を増幅する。図12に示す例では、パワーアンプ473は、第1から第4の実施の形態における半導体装置を有している。方向性結合器474は、入力信号や出力信号のモニタリング等を行なう。図12に示す回路では、例えば、スイッチの切り替えにより、ミキサー472により出力信号を交流信号とミキシングしてディジタル・プレディストーション回路471に送出することが可能である。

【0058】

以上、実施の形態について詳述したが、特定の実施形態に限定されるものではなく、特許請求の範囲に記載された範囲内において、種々の変形及び変更が可能である。

【0059】

上記の説明に関し、更に以下の付記を開示する。

(付記1)

基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、

前記高抵抗層の上に形成された多層中間層と、

前記多層中間層の上に半導体材料により形成された電子走行層と、

前記電子走行層の上に半導体材料により形成された電子供給層と、

を有し、

前記多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(付記2)

前記多層中間層において、GaN層の膜厚はAlN層の膜厚よりも厚いことを特徴とする付記1に記載の半導体装置。

(付記3)

前記多層中間層において、GaN層の膜厚が20〜50nmであり、AlN層の膜厚が2〜5nmであることを特徴とする付記1または2に記載の半導体装置。

(付記4)

前記多層中間層において、GaN層とAlN層とを積層することにより形成される周期は、20周期以上であることを特徴とする付記1から3のいずれかに記載の半導体装置。

(付記5)

前記多層中間層の膜厚は、500〜1000nmであることを特徴とする付記1から4のいずれかに記載の半導体装置。

(付記6)

基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、

前記高抵抗層の上に形成された中間層と、

前記中間層の上に半導体材料により形成された電子走行層と、

前記電子走行層の上に半導体材料により形成された電子供給層と、

を有し、

前記中間層はAlGaNにより形成されており、AlXGa1−XNとした場合、0<X<0.3であることを特徴とする半導体装置。

(付記7)

前記高抵抗層、前記多層中間層または前記中間層、前記電子走行層及び前記電子供給層は、MOVPEにより形成されたものであることを特徴とする付記1から6のいずれかに記載の半導体装置。

(付記8)

前記高抵抗層は、GaN、AlN、AlGaNのうちから選ばれるいずれか1つを含む材料に、高抵抗となる不純物元素がドープされているものにより形成されていることを特徴とする付記1から7のいずれかに記載の半導体装置。

(付記9)

前記高抵抗層は第1の高抵抗層であり、前記多層中間層は第1の多層中間層であって、

前記第1の多層中間層の上に形成された半導体材料に高抵抗となる不純物元素がドープされた第2の高抵抗層と、

前記第2の高抵抗層の上に形成された第2の多層中間層と、

を有し、前記電子走行層は、前記第2の多層中間層の上に形成されるものであって、

前記第2の多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする付記1から5のいずれかに記載の半導体装置。

(付記10)

前記第2の高抵抗層における高抵抗となる不純物元素のドーピング濃度は、前記第1の高抵抗層における高抵抗となる不純物元素のドーピング濃度よりも低いことを特徴とする付記9に記載の半導体装置。

(付記11)

前記第2の高抵抗層の膜厚は、前記第1の高抵抗層の膜厚よりも薄いことを特徴とする付記10に記載の半導体装置。

(付記12)

前記第2の多層中間層の膜厚は、前記第1の多層中間層の膜厚の膜厚よりも薄いことを特徴とする付記9から11のいずれかに記載の半導体装置。

(付記13)

前記第2の多層中間層における(GaN層の膜厚)/(AlN層の膜厚)の膜厚比は、前記第1の多層中間層における(GaN層の膜厚)/(AlN層の膜厚)の膜厚比よりも大きいことを特徴とする付記9から12のいずれかに記載の半導体装置。

(付記14)

前記高抵抗となる不純物元素は、Feであることを特徴とする付記1から13のいずれかに記載の半導体装置。

(付記15)

前記基板の上にはバッファ層が形成されており、前記バッファ層の上には前記高抵抗層が形成されているものであって、

前記バッファ層は、AlNまたはAlGaNにより形成されているものであることを特徴とする付記1から14のいずれかに記載の半導体装置。

(付記16)

前記電子走行層は、GaNを含む材料により形成されていることを特徴とする付記1から15のいずれかに記載の半導体装置。

(付記17)

前記電子供給層は、AlGaNを含む材料により形成されていることを特徴とする付記1から16のいずれかに記載の半導体装置。

(付記18)

前記電子供給層の上には、ゲート電極、ソース電極及びドレイン電極が形成されているものであることを特徴とする付記1から17のいずれかに記載の半導体装置。

(付記19)

付記1から18のいずれかに記載の半導体装置を有することを特徴とする電源装置。

(付記20)

付記1から18のいずれかに記載の半導体装置を有することを特徴とする増幅器。

【符号の説明】

【0060】

11 基板

12 核形成層

13 バッファ層

14 高抵抗層

15 多層中間層

16 電子走行層

16a 2DEG

17 電子供給層

21 ゲート電極

22 ソース電極

23 ドレイン電極

【技術分野】

【0001】

本発明は、半導体装置に関するものである。

【背景技術】

【0002】

窒化物半導体であるGaN、AlN、InN等または、これらの混晶である材料は、広いバンドギャップを有しており、高出力電子デバイスまたは短波長発光デバイス等として用いられている。このうち、高出力デバイスとしては、電界効果型トランジスタ(FET:Field-Effect Transistor)、特に、高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)に関する技術が開発されている(例えば、特許文献1)。このような窒化物半導体を用いたHEMTは、高出力・高効率増幅器、大電力スイッチングデバイス等に用いられる。

【0003】

このような窒化物半導体を用いたHEMTは、基板上に、窒化アルミニウムガリウム/窒化ガリウム(AlGaN/GaN)ヘテロ構造が形成されており、GaN層を電子走行層とするものである。尚、基板としては、サファイア、シリコンカーバイド(SiC)、窒化ガリウム(GaN)、シリコン(Si)等の基板が用いられる。

【0004】

窒化物半導体において、GaNは、高い飽和電子速度や広いバンドギャップを有しており、高い耐圧特性を得ることができるため、優れた電気的特性を有している。また、GaNは、結晶構造がウルツ鉱型であるため、c軸に平行な<0001>方向に極性を有しており、更に、AlGaN/GaNのヘテロ構造を形成した場合には、AlGaN層には、AlGaNとGaNとの格子歪みによるピエゾ分極が励起される。このため、チャネルとなる界面近傍には、高濃度の2DEG(Two-Dimensional Electron Gas:2次元電子ガス)が生じる。よって、このようなGaNを用いたHEMTは、高周波・電力用デバイスとして有望とされている。

【0005】

ところで、GaN系の半導体層においては、適量のFeをドーピングすることにより、高抵抗化させることができることが知られている。これは、GaNの価電子帯近傍において、Feにより深いアクセプタ準位が形成されることに起因している。このため、GaN等の半導体材料を用いたHEMTにおいては、電子走行層の下層にFeをドーピングすることにより、縦リークの防止、ピンチオフ特性の改善等をすることができるため、HEMTの特性を向上させることができる。

【0006】

図1には、GaNを用いたHEMTにおいて、Feがドープされている高抵抗層が設けられている構造のものを示す。具体的には、基板911上に、AlN等により形成された核形成層912、AlGaN等により形成されたバッファ層913が形成され、この上に、高抵抗層914、電子走行層915、電子供給層916がエピタキシャル成長により形成されている。高抵抗層914はFeがドープされているGaN(FeドープGaN)等により形成されており、電子走行層915はGaN等により形成されており、電子供給層916はAlGaN等により形成されている。電子供給層916の上には、ゲート電極921、ソース電極922及びドレイン電極923が形成されている。このような構造のGaNを用いたHEMTにおいては、高抵抗層914にドープされるFeが表面に偏析しており、電子走行層915の成長中に順次取り込まれるため、電子走行層915中にもFeが入り込んでしまう。このように電子走行層915中に多くのFeが入り込んでしまうと、チャネル電子がトラップされ、2DEG濃度の低下や不純物散乱効果による移動度の低下等を招き、電気的特性が低下してしまう。

【0007】

このため、Feがドープされる高抵抗層914と電子走行層915との間に、Feの取り込み効果の高いAlNやAlGaNにより形成された中間層を形成することにより、電子走行層915にFeが入り込むことを防いだ構造のものが開示されている(例えば、特許文献2、3)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−359256号公報

【特許文献2】特開2010−182872号公報

【特許文献3】特開2010−232297号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、電子走行層にFeが入り込むことを防ぐためには、AlNやAlGaNにより形成された中間層の膜厚をある程度厚く形成する必要がある。また、中間層をAlGaNにより形成する場合には、Al組成比が高い方が好ましく、引用文献2においてはAlの組成比は0.4以上のもの、引用文献3においてはAlの組成比は0.3以上のものが記載されている。

【0010】

ところで、基板にGaNとの格子不整合率の高い基板、例えば、Si基板を用いた場合には、基板となるSi基板の上に、GaNよりも格子定数の小さいAlNやAlGaN等のバッファ層を形成し、バッファ層の上に、GaN等の電子走行層が形成されている。このように、バッファ層を形成することにより、Si基板の上に形成されているGaN等の半導体積層膜と基板全体の応力とのバランスをとり、基板の反りや半導体積層膜等におけるクラックの発生を抑制することができる。この中間層は、結晶成長によりバッファ層の上に形成されるが、中間層がAlNや比較的Al組成の高いAlGaNの場合、中間層は、中間層よりも格子定数の大きなバッファ層の上に形成される。このため、中間層は、バッファ層から受ける引張歪により無歪状態よりも格子間隔が広がるため、中間層等にクラックを発生させることなく、所望の膜厚を形成することは困難である。尚、AlNの格子定数は、a軸3.11Å、c軸4.98Åであり、GaNの格子定数は、a軸3.18Å、c軸5.17Åである。

【0011】

よって、半導体材料としてGaN等の窒化物半導体を用いた電界効果トランジスタ等の半導体装置において、電子走行層にFeが入り込むことが抑制されており、また、半導体層におけるクラック等の発生を防ぐことのできる半導体装置が求められている。

【課題を解決するための手段】

【0012】

本実施の形態の一観点によれば、基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、前記高抵抗層の上に形成された多層中間層と、前記多層中間層の上に半導体材料により形成された電子走行層と、前記電子走行層の上に半導体材料により形成された電子供給層と、を有し、前記多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする。

【0013】

また、本実施の形態の他の一観点によれば、基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、前記高抵抗層の上に形成された中間層と、前記中間層の上に半導体材料により形成された電子走行層と、前記電子走行層の上に半導体材料により形成された電子供給層と、を有し、前記中間層はAlGaNにより形成されており、AlXGa1−XNとした場合、0<X<0.3であることを特徴とする。

【発明の効果】

【0014】

開示の半導体装置によれば、電界効果型トランジスタ等において、電子走行層にFeが入り込むことを抑制することができ、また、半導体層のクラック等の発生を防ぐことができるため、歩留りが高く良好な電気的特性を得ることができる。

【図面の簡単な説明】

【0015】

【図1】Feがドープされた層を有する半導体装置の構造図

【図2】AlNなし半導体積層膜とAlNありの半導体積層膜の説明図

【図3】半導体積層膜のSIMSによる分析結果

【図4】第1の実施の形態における半導体装置の説明図

【図5】多層中間層の構造図

【図6】第1の実施の形態における半導体装置におけるFeの入り込みの説明図

【図7】第2の実施の形態における半導体装置の説明図

【図8】第3の実施の形態における半導体装置の構造図

【図9】第4の実施の形態における半導体装置の構造図

【図10】第5の実施の形態におけるディスクリートパッケージされた半導体デバイスの説明図

【図11】第5の実施の形態における電源装置の回路図

【図12】第5の実施の形態における高出力増幅器の構造図

【発明を実施するための形態】

【0016】

実施するための形態について、以下に説明する。尚、同じ部材等については、同一の符号を付して説明を省略する。

【0017】

〔第1の実施の形態〕

最初に、AlN層を設けられている場合と、設けられていない場合において、電子走行層へのFeの入り込み量について説明する。図2に示されHEMTを形成するための半導体積層膜において、AlN層が設けられているものとAlNが設けられていないものとを作製し、SIMS(Secondary Ion-microprobe Mass Spectrometer:2次イオン質量分析)による測定を行なった。図3には、これらの半導体積層膜におけるSIMSにより測定された深さ方向におけるFe濃度のプロファイルを示す。図2(a)は、AlN層が設けられていない半導体積層膜(AlNなし半導体積層膜)の構造を示すものであり、基板911上に、核形成層912、バッファ層913、高抵抗層914、電子走行層915、電子供給層916が形成されているものである。図2(b)は、AlN層が設けられている半導体積層膜(AlNあり半導体積層膜)の構造を示すものであり、基板911上に、核形成層912、バッファ層913、高抵抗層914、中間層930、電子走行層915、電子供給層916が形成されているものである。尚、高抵抗層914は、不純物元素としてFeがドープされているGaNにより形成されており、膜厚が約300nmであり、ドープされているFeの濃度は、約1×1018cm−3である。また、電子走行層915は、膜厚が約600nmのGaNにより形成されており、電子供給層916は、膜厚が約20nmのAlGaNにより形成されている。また、図2(b)に示されるAlNあり半導体積層膜の場合には、中間層930は、約5nmのAlNにより形成されている。図3は、電子走行層916からバッファ層913までの間において、深さ方向にSIMSにより測定した結果を示すものである。尚、図3において図示はされていないが、AlNあり半導体積層膜の場合においては、高抵抗層914と電子走行層915との間に中間層930が形成されている。

【0018】

AlNなし半導体積層膜の場合では、電子供給層916と電子走行層915との界面近傍までFeが入り込んでおり、このFeの濃度は、2×1016cm−3よりも多い。これに対し、AlNあり半導体積層膜の場合では、Feの濃度は、高抵抗層914と電子走行層915との間に形成されたAlNにより形成されている中間層930が形成されている領域にピークを示しており、中間層930にFeが多く取り込まれている。このため、電子走行層915に入り込んでいるFeの量は、AlNなし半導体積層膜と比べると少なくなっている。このように、AlNにより形成されている中間層930を設けることにより、電子走行層915にFeが入り込む量を減らすことができる。

【0019】

(半導体装置)

次に、第1の実施の形態における半導体装置について説明する。本実施の形態における半導体装置は、AlGaN/GaNシングルへテロ構造のHEMTである。

【0020】

本実施の形態における半導体装置は、最初に、図4(a)に示すように、基板11上に、窒化物半導体層である核形成層12、バッファ層13、高抵抗層14、多層中間層15、電子走行層16、電子供給層17を順次積層形成する。具体的には、まず、基板11を水素雰囲気中で数分間熱処理を行なう。この後、基板11上に、核形成層12、バッファ層13、高抵抗層14、多層中間層15、電子走行層16、電子供給層17をMOVPE(Metal Organic Vapor Phase Epitaxy)法によりエピタキシャル成長させることにより形成する。これにより、電子走行層16において、電子走行層16と電子供給層17との界面近傍には、2DEG16aが形成される。この際、Gaの原料ガスにはTMG(トリメチルガリウム)が用いられ、Alの原料ガスにはTMA(トリメチルアルミニウム)が用いられ、Nの原料ガスにはNH3(アンモニア)が用いられる。また、不純物元素としてドープされるFeの原料ガスにはCp2Fe(シクロペンタジエニル鉄、通常、フェロセン)が用いられる。尚、これらの原料ガスは、水素(H2)をキャリアガスとしてMOVPE装置の反応炉に供給される。

【0021】

基板11は、サファイア、Si、SiC等の材料により形成されており、本実施の形態では、例えば、Si等により形成されている。尚、基板11側への電流リークを防ぐため抵抗の高いものを用いることが好ましい。

【0022】

核形成層12は、膜厚が100〜200nmのAlN層により形成されている。

【0023】

バッファ層13は、AlGaN層により形成されており、本実施の形態では、Al組成比の異なるAlGaNを積層することにより形成されている。具体的には、最初に、Al組成比が相対的に高いAl0.7Ga0.3Nにより形成される層を形成し、この後、Al組成比が相対的に低いAl0.3Ga0.7Nにより形成される層を形成する。尚、バッファ層13は、組成比の異なる3層以上のAlGaNにより形成してもよい。また、このような構造以外にも、GaN/AlNを交互に形成した周期構造を有する超格子バッファや、AlNからGaNに至るまでAlの組成比を変化させた組成傾斜構造により形成してもよい。基板11に起因する転位を低減するためには、バッファ層13の膜厚は厚ほど好ましいが、クラックの発生を防ぐためには、あまり厚くない方が好ましい。よって、バッファ層13の膜厚は、200〜1000nmが好ましい。

【0024】

高抵抗層14は、膜厚が100〜300nmであって、高抵抗となる不純物元素としてFeがドープされているGaN、AlNまたは、AlGaNにより形成されている。高抵抗層14におけるFeのドーピング濃度は、5×1017〜1×1019cm−3、より好ましくは、1×1018cm−3である。尚、本願において高抵抗となる不純物元素とは、GaN、AlNまたは、AlGaN等の窒化物半導体にドープすることにより、窒化物半導体における抵抗を高くすることのできる不純物元素を意味する。

【0025】

多層中間層15は、図5に示されるように、GaN層15aとAlN層15bとを交互に積層形成した構造のものであり、膜厚が500〜1000nmとなるように形成されている。多層中間層15においては、基板11を含む全体の応力バランスの低下を防ぐため、GaN層15aの膜厚はAlN層15bの膜厚よりも厚く形成されていることが好ましい。具体的には、GaN層15aの膜厚は20〜50nmが好ましく、AlN層15bの膜厚は2〜5nmが好ましい。尚、本実施の形態においては、多層中間層15は、膜厚が約20nmのGaN層15aと、膜厚が約2nmのAlN層15bとを交互に20周期以上成長させることにより形成する。また、Feが電子走行層16に入り込むことを効果的に防ぐためには、積算されるAlN層15bは一定の膜厚以上形成されていることが好ましく、経験等に基づくならば、積算されるAlN層15bの膜厚が40nm以上となるように形成されていることが好ましい。

【0026】

電子走行層16は、GaNにより形成されており、転位等に起因する電子濃度や移動度の低下を避けるためには、所定の値以上の膜厚で形成されていることが好ましく、膜厚が500〜1000nmとなるように形成されている。

【0027】

電子供給層17は、膜厚が約20nmのAlGaNにより形成されている。尚、電子供給層17は、格子不整合による結晶性低下を避けるため、AlXGa1−XNと表現した場合に、Xの値が0.3以下となるように形成されている。

【0028】

次に、図4(b)に示すように、電子供給層17の上に、ゲート電極21、ソース電極22及びドレイン電極23を形成する。これにより、本実施の形態における半導体装置を作製することができる。

【0029】

図6は、本実施の形態における半導体装置であるHEMTと図1に示される構造のHEMTについて、高抵抗層と電子走行層との間におけるFe濃度を示すものである。図6に示されるように、本実施の形態におけるHEMT5Aにおいては、多層中間層15におけるAlN層15bにおいてFeが多く取り込まれる。よって、HEMT5Aにおける電子走行層16に入り込むFeの濃度は、図1に示される構造のHEMT5Bにおける電子走行層915に入り込むFeの濃度よりも低くすることができる。これにより、本実施の形態における半導体装置であるHEMTは、電子走行層16を高抵抗化させることはなく、電気的特性の低下を防ぐことができる。

【0030】

また、本実施の形態では、GaN層15aとAlN層15bを交互に積層した多層構造の多層中間層15を形成しているため、応力の発生が少なく、基板11の反りや半導体層等におけるクラックの発生を抑制することができる。

【0031】

よって、本実施の形態における半導体装置においては、歩留りが高く良好な電気的特性を得ることができる。

【0032】

〔第2の実施の形態〕

次に、第2の実施の形態における半導体装置について説明する。本実施の形態における半導体装置は、AlGaN/GaNシングルへテロ構造のHEMTである。

【0033】

本実施の形態における半導体装置は、最初に、図7(a)に示すように、基板11上に、窒化物半導体層を積層形成する。即ち、基板11上に、核形成層12、バッファ層13、第1の高抵抗層114、第1の多層中間層115、第2の高抵抗層124、第2の多層中間層125、電子走行層16、電子供給層17を順次積層形成する。具体的には、まず、基板11を水素雰囲気中で数分間熱処理を行なう。この後、基板11上に、核形成層12、バッファ層13、第1の高抵抗層114、第1の多層中間層115、第2の高抵抗層124、第2の多層中間層125、電子走行層16、電子供給層17をMOVPE法によりエピタキシャル成長させることにより形成する。これにより、電子走行層16において、電子走行層16と電子供給層17との界面近傍には、2DEG16aが形成される。この際、Gaの原料ガスにはTMGが用いられ、Alの原料ガスにはTMAが用いられ、Nの原料ガスにはNH3が用いられる。また、不純物元素としてドープされるFeの原料ガスにはCp2Feが用いられる。尚、これらの原料ガスは、水素をキャリアガスとしてMOVPE装置の反応炉に供給される。

【0034】

第1の高抵抗層114は、膜厚が100〜300nmであって、高抵抗となる不純物元素としてFeがドープされているGaN、AlNまたは、AlGaNにより形成されている。第1の高抵抗層114におけるFeのドーピング濃度は、5×1017〜1×1019cm−3、より好ましくは、1×1018cm−3である。

【0035】

第1の多層中間層115は、図5に示されるように、GaN層15aとAlN層15bとを交互に積層形成した構造のものであり、膜厚が500〜1000nmとなるように形成されている。第1の多層中間層115においては、基板11を含む全体の応力バランスの低下を防ぐため、GaN層15aの膜厚はAlN層15bの膜厚よりも厚く形成されていることが好ましい。具体的には、GaN層15aの20〜50nmが好ましく、AlN層15bの膜厚は2〜5nmが好ましい。尚、本実施の形態においては、第1の多層中間層115は、膜厚が約20nmのGaN層15aと膜厚が約2nmのAlN層15bとを交互に20周期以上成長させることにより形成されている。また、Feが電子走行層16に入り込むことを効果的に防ぐためには、積算されるAlN層15bは一定の膜厚以上形成されていることが好ましく、経験等に基づくならば、積算されるAlN層15bの膜厚が40nm以上となるように形成されていることが好ましい。

【0036】

第2の高抵抗層124は、膜厚が50〜100nmであって、高抵抗となる不純物元素としてFeがドープされているGaN、AlNまたは、AlGaNにより形成されている。第2の高抵抗層124におけるFeのドーピング濃度は、1×1017〜1×1018cm−3である。第2の高抵抗層124は、電子走行層16において、Feが過剰に取り込まれることによる走行電子に与える悪影響を避けるため、第1の高抵抗層114よりもFeのドーピング濃度が低く形成されている。具体的には、例えば、Feのドーピング濃度が、5×1017cm−3となるように形成されている。また、第2の高抵抗層124の膜厚は、第1の高抵抗層114の膜厚よりも薄く形成されていることが好ましい。

【0037】

第2の多層中間層125は、図5に示すように、GaN層15aとAlN層15bとを交互に積層形成した構造のものであり、膜厚が125〜500nmとなるように形成されている。第2の多層中間層125においては、GaN層15aの膜厚はAlN層15bの膜厚よりも厚く形成されていることが好ましく、具体的には、GaN層15aの20〜50nmが好ましく、AlN層15bの膜厚は2〜5nmが好ましい。尚、本実施の形態においては、第2の多層中間層125は、膜厚が約30nmのGaN層15aと膜厚が約2nmのAlN層15bとを交互に5〜10周期成長させることにより形成されている。また、本実施の形態では、第1の高抵抗層114よりも第2の高抵抗層124におけるFeの濃度が低いため、第2の多層中間層125におけるAlN層15bの膜厚の比率は、第1の多層中間層115におけるAlN層15bの膜厚の比率よりも小さくなっている。言い換えるならば、第2の多層中間層125における(GaN層の膜厚)/(AlN層の膜厚)の膜厚比は、第1の多層中間層115における(GaN層の膜厚)/(AlN層の膜厚)の膜厚比よりも、大きくなるように形成されている。

【0038】

電子走行層16は、GaNにより形成されており、転位等に起因する電子濃度や移動度の低下を避けるためには、所定の値以上の膜厚で形成されていることが好ましく、膜厚が500〜800nmとなるように形成されている。本実施の形態では、第1の多層膜中間層115及び第2の多層中間層125等を形成することにより転位の発生が大きく抑制されるため、第1の実施の形態における半導体装置よりも、電子走行層16の膜厚を薄くすることができる。よって、本実施の形態における半導体装置は、電子走行層16の結晶性を確保しつつ、電子走行層16の膜厚を薄くすることができるため、ピンチオフ特性を改善することができる。

【0039】

次に、図7(b)に示すように、電子供給層17の上に、ゲート電極21、ソース電極22及びドレイン電極23を形成する。これにより、本実施の形態における半導体装置を作製することができる。

【0040】

本実施の形態では、第1の高抵抗層114及び第2の高抵抗層124を設けることのより、縦リークを抑制することができ、電子走行層16の膜厚を薄くすることができるため、ピンチオフ特性を改善することができる。

【0041】

尚、上記以外の内容については、第1の実施の形態と同様である。

【0042】

〔第3の実施の形態〕

次に、第3の実施の形態について説明する。本実施の形態における半導体装置は、第1の実施の形態における多層中間層15に代えて、AlNとGaNとの混晶により形成された混晶中間層を有するものである。

【0043】

図8に基づき本実施の形態における半導体装置について説明する。本実施の形態における半導体装置は、基板11上に、核形成層12、バッファ層13、高抵抗層14、混晶中間層215、電子走行層16、電子供給層17を順次積層形成したものである。

【0044】

混晶中間層215は、膜厚が500〜1000nmのAlNとGaNとの混晶により形成されており、混晶中間層215の組成は、AlXGa1−XNとすると、0<X<0.3、より好ましくは、0.04≦X≦0.25となるように形成されている。混晶中間層215において僅かでもAlを含んでいれば、Feを取り込むことができ、電子走行層16にFeが入り込むことを防ぐことができる。また、X<0.3であれば、応力の発生も少ないため、基板11の反りや積層されている半導体層におけるクラックの発生を抑制することができる。

【0045】

尚、上記以外の内容については、第1の実施の形態と同様である。

【0046】

〔第4の実施の形態〕

次に、第3の実施の形態における半導体装置について、図9に基づき説明する。本実施の形態における半導体装置は、電子供給層17上にゲート絶縁膜となる絶縁膜330が形成されている構造のものである。このような絶縁膜330を形成することにより、ゲートリーク電流を減らすことができる。絶縁膜330としては、例えば、Al2O3(酸化アルミニウム)等が用いられる。

【0047】

本実施の形態における半導体装置は、第1の実施の形態における図4(a)まで形成したものの電子供給層17上に、ソース電極22及びドレイン電極23を形成し、この後、ゲート絶縁膜となる絶縁膜330を形成する。絶縁膜330の形成方法としては、CVD(Chemical Vapor Deposition)、ALD(Atomic Layer Deposition)、スパッタリング等が挙げられる。

【0048】

この後、絶縁膜330上の所定の領域に、ゲート電極21を形成する。これにより、本実施の形態における半導体装置を製造することができる。また、ゲート電極21が形成される領域に凹形状のゲートリセスを形成し、ゲートリセスの内部を含む領域にゲート電極21を形成したものであってもよい。

【0049】

尚、上記以外の内容は、第1の実施の形態と同様である。また、本実施の形態は、第2の実施の形態及び第3の実施の形態における半導体装置においても、同様に適用することができる。

【0050】

〔第5の実施の形態〕

次に、第5の実施の形態について説明する。本実施の形態は、半導体デバイス、電源装置及び高周波増幅器である。

【0051】

本実施の形態における半導体デバイスは、第1から第4の実施の形態におけるいずれかの半導体装置をディスクリートパッケージしたものであり、このようにディスクリートパッケージされた半導体デバイスについて、図10に基づき説明する。尚、図10は、ディスクリートパッケージされた半導体装置の内部を模式的に示すものであり、電極の配置等については、第1から第4の実施の形態に示されているものとは、異なっている。

【0052】

最初に、第1から第4の実施の形態において製造された半導体装置をダイシング等により切断することにより、GaN系の半導体材料のHEMTの半導体チップ410を形成する。この半導体チップ410をリードフレーム420上に、ハンダ等のダイアタッチ剤430により固定する。尚、この半導体チップ410は、第1から第4の実施の形態における半導体装置に相当するものである。

【0053】

次に、ゲート電極411をゲートリード421にボンディングワイヤ431により接続し、ソース電極412をソースリード422にボンディングワイヤ432により接続し、ドレイン電極413をドレインリード423にボンディングワイヤ433により接続する。尚、ボンディングワイヤ431、432、433はAl等の金属材料により形成されている。また、本実施の形態においては、ゲート電極411はゲート電極パッドであり、第1から第4の実施の形態における半導体装置のゲート電極21と接続されている。また、ソース電極412はソース電極パッドであり、第1から第4の実施の形態における半導体装置のソース電極22と接続されている。また、ドレイン電極413はドレイン電極パッドであり、第1から第4の実施の形態における半導体装置のドレイン電極23と接続されている。

【0054】

次に、トランスファーモールド法によりモールド樹脂440による樹脂封止を行なう。このようにして、GaN系の半導体材料を用いたHEMTのディスクリートパッケージされている半導体デバイスを作製することができる。

【0055】

次に、本実施の形態における電源装置及び高周波増幅器について説明する。本実施の形態における電源装置及び高周波増幅器は、第1から第4の実施の形態における半導体装置のいずれかを用いた電源装置及び高周波増幅器である。

【0056】

最初に、図11に基づき、本実施の形態における電源装置について説明する。本実施の形態における電源装置460は、高圧の一次側回路461、低圧の二次側回路462及び一次側回路461と二次側回路462との間に配設されるトランス463を備えている。一次側回路461は、交流電源464、いわゆるブリッジ整流回路465、複数のスイッチング素子(図11に示す例では4つ)466及び一つのスイッチング素子467等を備えている。二次側回路462は、複数のスイッチング素子(図11に示す例では3つ)468を備えている。図11に示す例では、第1から第4の実施の形態における半導体装置を一次側回路461のスイッチング素子466及び467として用いている。尚、一次側回路461のスイッチング素子466及び467は、ノーマリーオフの半導体装置であることが好ましい。また、二次側回路462において用いられているスイッチング素子468はシリコンにより形成される通常のMISFET(metal insulator semiconductor field effect transistor)を用いている。

【0057】

次に、図12に基づき、本実施の形態における高周波増幅器について説明する。本実施の形態における高周波増幅器470は、例えば、携帯電話の基地局用パワーアンプに適用してもよい。この高周波増幅器470は、ディジタル・プレディストーション回路471、ミキサー472、パワーアンプ473及び方向性結合器474を備えている。ディジタル・プレディストーション回路471は、入力信号の非線形歪みを補償する。ミキサー472は、非線形歪みが補償された入力信号と交流信号とをミキシングする。パワーアンプ473は、交流信号とミキシングされた入力信号を増幅する。図12に示す例では、パワーアンプ473は、第1から第4の実施の形態における半導体装置を有している。方向性結合器474は、入力信号や出力信号のモニタリング等を行なう。図12に示す回路では、例えば、スイッチの切り替えにより、ミキサー472により出力信号を交流信号とミキシングしてディジタル・プレディストーション回路471に送出することが可能である。

【0058】

以上、実施の形態について詳述したが、特定の実施形態に限定されるものではなく、特許請求の範囲に記載された範囲内において、種々の変形及び変更が可能である。

【0059】

上記の説明に関し、更に以下の付記を開示する。

(付記1)

基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、

前記高抵抗層の上に形成された多層中間層と、

前記多層中間層の上に半導体材料により形成された電子走行層と、

前記電子走行層の上に半導体材料により形成された電子供給層と、

を有し、

前記多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(付記2)

前記多層中間層において、GaN層の膜厚はAlN層の膜厚よりも厚いことを特徴とする付記1に記載の半導体装置。

(付記3)

前記多層中間層において、GaN層の膜厚が20〜50nmであり、AlN層の膜厚が2〜5nmであることを特徴とする付記1または2に記載の半導体装置。

(付記4)

前記多層中間層において、GaN層とAlN層とを積層することにより形成される周期は、20周期以上であることを特徴とする付記1から3のいずれかに記載の半導体装置。

(付記5)

前記多層中間層の膜厚は、500〜1000nmであることを特徴とする付記1から4のいずれかに記載の半導体装置。

(付記6)

基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、

前記高抵抗層の上に形成された中間層と、

前記中間層の上に半導体材料により形成された電子走行層と、

前記電子走行層の上に半導体材料により形成された電子供給層と、

を有し、

前記中間層はAlGaNにより形成されており、AlXGa1−XNとした場合、0<X<0.3であることを特徴とする半導体装置。

(付記7)

前記高抵抗層、前記多層中間層または前記中間層、前記電子走行層及び前記電子供給層は、MOVPEにより形成されたものであることを特徴とする付記1から6のいずれかに記載の半導体装置。

(付記8)

前記高抵抗層は、GaN、AlN、AlGaNのうちから選ばれるいずれか1つを含む材料に、高抵抗となる不純物元素がドープされているものにより形成されていることを特徴とする付記1から7のいずれかに記載の半導体装置。

(付記9)

前記高抵抗層は第1の高抵抗層であり、前記多層中間層は第1の多層中間層であって、

前記第1の多層中間層の上に形成された半導体材料に高抵抗となる不純物元素がドープされた第2の高抵抗層と、

前記第2の高抵抗層の上に形成された第2の多層中間層と、

を有し、前記電子走行層は、前記第2の多層中間層の上に形成されるものであって、

前記第2の多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする付記1から5のいずれかに記載の半導体装置。

(付記10)

前記第2の高抵抗層における高抵抗となる不純物元素のドーピング濃度は、前記第1の高抵抗層における高抵抗となる不純物元素のドーピング濃度よりも低いことを特徴とする付記9に記載の半導体装置。

(付記11)

前記第2の高抵抗層の膜厚は、前記第1の高抵抗層の膜厚よりも薄いことを特徴とする付記10に記載の半導体装置。

(付記12)

前記第2の多層中間層の膜厚は、前記第1の多層中間層の膜厚の膜厚よりも薄いことを特徴とする付記9から11のいずれかに記載の半導体装置。

(付記13)

前記第2の多層中間層における(GaN層の膜厚)/(AlN層の膜厚)の膜厚比は、前記第1の多層中間層における(GaN層の膜厚)/(AlN層の膜厚)の膜厚比よりも大きいことを特徴とする付記9から12のいずれかに記載の半導体装置。

(付記14)

前記高抵抗となる不純物元素は、Feであることを特徴とする付記1から13のいずれかに記載の半導体装置。

(付記15)

前記基板の上にはバッファ層が形成されており、前記バッファ層の上には前記高抵抗層が形成されているものであって、

前記バッファ層は、AlNまたはAlGaNにより形成されているものであることを特徴とする付記1から14のいずれかに記載の半導体装置。

(付記16)

前記電子走行層は、GaNを含む材料により形成されていることを特徴とする付記1から15のいずれかに記載の半導体装置。

(付記17)

前記電子供給層は、AlGaNを含む材料により形成されていることを特徴とする付記1から16のいずれかに記載の半導体装置。

(付記18)

前記電子供給層の上には、ゲート電極、ソース電極及びドレイン電極が形成されているものであることを特徴とする付記1から17のいずれかに記載の半導体装置。

(付記19)

付記1から18のいずれかに記載の半導体装置を有することを特徴とする電源装置。

(付記20)

付記1から18のいずれかに記載の半導体装置を有することを特徴とする増幅器。

【符号の説明】

【0060】

11 基板

12 核形成層

13 バッファ層

14 高抵抗層

15 多層中間層

16 電子走行層

16a 2DEG

17 電子供給層

21 ゲート電極

22 ソース電極

23 ドレイン電極

【特許請求の範囲】

【請求項1】

基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、

前記高抵抗層の上に形成された多層中間層と、

前記多層中間層の上に半導体材料により形成された電子走行層と、

前記電子走行層の上に半導体材料により形成された電子供給層と、

を有し、

前記多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

【請求項2】

前記多層中間層において、GaN層の膜厚はAlN層の膜厚よりも厚いことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記多層中間層において、GaN層とAlN層とを積層することにより形成される周期は、20周期以上であることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、

前記高抵抗層の上に形成された中間層と、

前記中間層の上に半導体材料により形成された電子走行層と、

前記電子走行層の上に半導体材料により形成された電子供給層と、

を有し、

前記中間層はAlGaNにより形成されており、AlXGa1−XNとした場合、0<X<0.3であることを特徴とする半導体装置。

【請求項5】

前記高抵抗層、前記多層中間層または前記中間層、前記電子走行層及び前記電子供給層は、MOVPEにより形成されたものであることを特徴とする請求項1から4のいずれかに記載の半導体装置。

【請求項6】

前記高抵抗層は、GaN、AlN、AlGaNのうちから選ばれるいずれか1つを含む材料に、高抵抗となる不純物元素がドープされているものにより形成されていることを特徴とする請求項1から5のいずれかに記載の半導体装置。

【請求項7】

前記高抵抗層は第1の高抵抗層であり、前記多層中間層は第1の多層中間層であって、

前記第1の多層中間層の上に形成された半導体材料に高抵抗となる不純物元素がドープされた第2の高抵抗層と、

前記第2の高抵抗層の上に形成された第2の多層中間層と、

を有し、前記電子走行層は、前記第2の多層中間層の上に形成されるものであって、

前記第2の多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする請求項1から3のいずれかに記載の半導体装置。

【請求項8】

前記第2の高抵抗層における高抵抗となる不純物元素のドーピング濃度は、前記第1の高抵抗層における高抵抗となる不純物元素のドーピング濃度よりも低いことを特徴とする請求項7に記載の半導体装置。

【請求項9】

前記高抵抗となる不純物元素は、Feであることを特徴とする請求項1から8のいずれかに記載の半導体装置。

【請求項10】

前記基板の上にはバッファ層が形成されており、前記バッファ層の上には前記高抵抗層が形成されているものであって、

前記バッファ層は、AlNまたはAlGaNにより形成されているものであることを特徴とする請求項1から9のいずれかに記載の半導体装置。

【請求項1】

基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、

前記高抵抗層の上に形成された多層中間層と、

前記多層中間層の上に半導体材料により形成された電子走行層と、

前記電子走行層の上に半導体材料により形成された電子供給層と、

を有し、

前記多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

【請求項2】

前記多層中間層において、GaN層の膜厚はAlN層の膜厚よりも厚いことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記多層中間層において、GaN層とAlN層とを積層することにより形成される周期は、20周期以上であることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

基板の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層と、

前記高抵抗層の上に形成された中間層と、

前記中間層の上に半導体材料により形成された電子走行層と、

前記電子走行層の上に半導体材料により形成された電子供給層と、

を有し、

前記中間層はAlGaNにより形成されており、AlXGa1−XNとした場合、0<X<0.3であることを特徴とする半導体装置。

【請求項5】

前記高抵抗層、前記多層中間層または前記中間層、前記電子走行層及び前記電子供給層は、MOVPEにより形成されたものであることを特徴とする請求項1から4のいずれかに記載の半導体装置。

【請求項6】

前記高抵抗層は、GaN、AlN、AlGaNのうちから選ばれるいずれか1つを含む材料に、高抵抗となる不純物元素がドープされているものにより形成されていることを特徴とする請求項1から5のいずれかに記載の半導体装置。

【請求項7】

前記高抵抗層は第1の高抵抗層であり、前記多層中間層は第1の多層中間層であって、

前記第1の多層中間層の上に形成された半導体材料に高抵抗となる不純物元素がドープされた第2の高抵抗層と、

前記第2の高抵抗層の上に形成された第2の多層中間層と、

を有し、前記電子走行層は、前記第2の多層中間層の上に形成されるものであって、

前記第2の多層中間層は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする請求項1から3のいずれかに記載の半導体装置。

【請求項8】

前記第2の高抵抗層における高抵抗となる不純物元素のドーピング濃度は、前記第1の高抵抗層における高抵抗となる不純物元素のドーピング濃度よりも低いことを特徴とする請求項7に記載の半導体装置。

【請求項9】

前記高抵抗となる不純物元素は、Feであることを特徴とする請求項1から8のいずれかに記載の半導体装置。

【請求項10】

前記基板の上にはバッファ層が形成されており、前記バッファ層の上には前記高抵抗層が形成されているものであって、

前記バッファ層は、AlNまたはAlGaNにより形成されているものであることを特徴とする請求項1から9のいずれかに記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−74211(P2013−74211A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−213473(P2011−213473)

【出願日】平成23年9月28日(2011.9.28)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月28日(2011.9.28)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]