半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、簡単な回路構成により誤動作を防止できる半導体装置に関する。

【背景技術】

【0002】

モータなどの負荷の電力制御にはブリッジ回路や3相交流インバータ回路などの半導体装置が用いられる。これらの半導体装置は、電源電位と接地電位の間にトーテムポール接続された2つのパワー素子と、それらを駆動する駆動回路とを有する。2つのパワー素子の中点は負荷と接続され、2つのパワー素子のオン・オフの制御により負荷を制御する(例えば、特許文献1参照)。

【0003】

図12は、従来の半導体装置を示す回路図である。パワー素子Q1のターンオン時に、パワー素子Q2のコレクタ・エミッタ間にdV/dtが印加される。この場合にパワー素子Q2のゲート・コレクタ間の寄生容量Cresを充電する電流が流れるため、パワー素子Q2のゲート電圧が上昇する(ゲート浮き)。このゲート浮きによりパワー素子Q2のゲート電圧が閾値電圧を越えると、パワー素子Q2が誤オンし、短絡電流が流れてしまう。

【0004】

そこで、パワー素子Q2がオフ時に、負電圧用電源を用いてパワー素子Q2のゲートに負電圧V‐を印加する。これにより、パワー素子Q2のゲート電圧がエミッタ電圧(GND)より低くなるため、ゲート浮きが発生してもパワー素子Q2のゲート電圧が閾値電圧まで上昇し難くなる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−178579号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の半導体装置は、複数の電源が必要であり、回路構成が複雑になるという問題があった。

【0007】

本発明は、上述のような課題を解決するためになされたもので、その目的は簡単な回路構成により誤動作を防止できる半導体装置を得るものである。

【課題を解決するための手段】

【0008】

本発明に係る半導体装置は、制御端子と、第1端子と、第2端子とを有する第1のパワー素子と、前記第1のパワー素子にトーテムポール接続された第2のパワー素子と、電源に接続された高圧端子と、低圧端子とを有し、第1の入力信号に応じて前記第1のパワー素子を駆動する第1の駆動回路と、第2の入力信号に応じて前記第2のパワー素子を駆動する第2の駆動回路と、一端が前記第1のパワー素子の前記第2端子に接続され、他端が前記第1の駆動回路の前記低圧端子に接続された抵抗と、前記第1の駆動回路の前記高圧端子と前記抵抗の前記一端との間に接続され、前記第1の入力信号又は前記第2の入力信号に応じてオン・オフするスイッチング素子とを備え、前記第1の入力信号がオフ信号の場合に、前記第1の駆動回路は前記低圧端子の電圧を前記第1のパワー素子の前記制御端子に供給して前記第1のパワー素子はオフし、前記第1の入力信号がオフ信号又は前記第2の入力信号がオン信号の場合に、前記スイッチング素子はオンすることを特徴とする。

【発明の効果】

【0009】

本発明により、簡単な回路構成により誤動作を防止できる。

【図面の簡単な説明】

【0010】

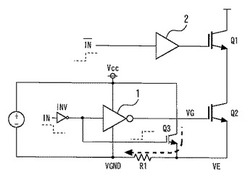

【図1】本発明の実施の形態1に係る半導体装置を示す回路図である。

【図2】図1の半導体装置の動作を示すタイミングチャートである。

【図3】本発明の実施の形態2に係る半導体装置を示す回路図である。

【図4】図3の半導体装置の動作を示すタイミングチャートである。

【図5】本発明の実施の形態3に係る半導体装置を示す回路図である。

【図6】図5の半導体装置の動作を示すタイミングチャートである。

【図7】本発明の実施の形態4に係る半導体装置を示す回路図である。

【図8】本発明の実施の形態5に係る半導体装置を示す回路図である。

【図9】本発明の実施の形態6に係る半導体装置を示す回路図である。

【図10】本発明の実施の形態7に係る半導体装置を示す回路図である。

【図11】本発明の実施の形態8に係る半導体装置を示す回路図である。

【図12】従来の半導体装置を示す回路図である。

【発明を実施するための形態】

【0011】

本発明の実施の形態に係る半導体装置について図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

【0012】

実施の形態1.

図1は、本発明の実施の形態1に係る半導体装置を示す回路図である。電源電位と接地電位の間にパワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。

【0013】

駆動回路1は、電源に接続された高圧端子と、接地された低圧端子とを有する。インバータINVが入力信号INを反転して出力し、その出力信号を駆動回路1が反転増幅してパワー素子Q2のゲートに供給する。

【0014】

抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。このスイッチング素子Q3のゲートにはインバータINVの出力信号が供給され、スイッチング素子Q3は入力信号INに応じてオン・オフする。

【0015】

図2は、図1の半導体装置の動作を示すタイミングチャートである。このタイミングチャートを参照して図1の半導体装置の動作を説明する。入力信号/INは入力信号INを反転したものであるが、両者の間にはデッドタイムが存在する。

【0016】

入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。この場合に入力信号/INはオン信号となるため、駆動回路2は高電圧をパワー素子Q1のゲートに供給してパワー素子Q1はオンする。

【0017】

一方、入力信号INがオン信号の場合に、駆動回路1は高圧端子の電圧をパワー素子Q2のゲートに供給してパワー素子Q2はオンする。この場合に入力信号/INはオフ信号となるため、駆動回路2は低電圧をパワー素子Q1のゲートに供給してパワー素子Q1はオフする。

【0018】

入力信号INがオフ信号の場合に、スイッチング素子Q3はオンし、抵抗R1に電流が流れる。これにより、駆動回路1の低圧端子の電圧VGNDが、パワー素子Q2のエミッタ電圧VEよりも抵抗R1の電圧降下分だけ低くなる。従って、パワー素子Q2のオフ時のゲート電圧VGがエミッタ電圧VEに対して負電圧になるため、ゲート浮きが発生してもパワー素子Q2のゲート電圧が閾値電圧まで上昇し難くなる。よって、負電圧用電源を必要としない簡単な回路構成により誤動作を防止できる。

【0019】

実施の形態2.

図3は、本発明の実施の形態2に係る半導体装置を示す回路図である。ワンショット回路3は、入力信号INのターンオフ時にスイッチング素子Q3のゲートにパルス信号を供給する。

【0020】

図4は、図3の半導体装置の動作を示すタイミングチャートである。ワンショット回路3からのパルス信号により、スイッチング素子Q3は、パワー素子Q1のターンオンが完了するまでの所定期間だけオンする。従って、実施の形態1に比べてスイッチング素子Q3のオン期間が短くなるため、電源の消費電力を削減することができる。

【0021】

実施の形態3.

図5は、本発明の実施の形態3に係る半導体装置を示す回路図である。遅延回路4がインバータINVの出力信号を遅延させる。AND回路5のa端子にパワー素子Q2のゲートの電圧が入力され、b端子に遅延回路4の出力電圧が入力される。スイッチング素子Q3はAND回路5の出力信号に応じてオン・オフする。

【0022】

図6は、図5の半導体装置の動作を示すタイミングチャートである。AND回路5は、入力信号INがオフ信号であり、かつパワー素子Q2のゲートの電圧が低圧端子の電圧VGNDより高くなった場合(ゲート浮き期間)にだけ、スイッチング素子Q3をオンさせる。これにより、スイッチング素子Q3のオン期間が更に短くなるため、電源の消費電力を大幅に削減することができる。また、保護期間が広くなる。

【0023】

また、パワー素子Q2のターンオフ期間にはパワー素子Q2のゲートの電圧が高電圧となる。そこで、パワー素子Q2のターンオフ期間に保護動作を行わないように、遅延回路4を設けている。

【0024】

実施の形態4.

図7は、本発明の実施の形態4に係る半導体装置を示す回路図である。実施の形態1とは異なり、スイッチング素子Q3のゲートには入力信号/INが供給され、スイッチング素子Q3は入力信号/INに応じてオン・オフする。入力信号/INがオン信号の場合にスイッチング素子Q3はオンする。これにより、デッドタイムにスイッチング素子Q3がオンしないため、実施の形態1に比べて電源の消費電力を削減することができる。その他、実施の形態1と同様の効果を得ることができる。

【0025】

実施の形態5.

図8は、本発明の実施の形態5に係る半導体装置を示す回路図である。この半導体装置は、実施の形態4の半導体装置にワンショット回路3を追加したものである。ワンショット回路3は、入力信号/INのターンオン時にスイッチング素子Q3のゲートにパルス信号を供給する。これにより、スイッチング素子Q3はパワー素子Q1のターンオンが完了するまでの所定期間だけオンする。さらに、スイッチング素子Q3のオン期間は実施の形態2に比べて短くなる。この結果、電源の消費電力を大幅に削減することができる。

【0026】

実施の形態6.

図9は、本発明の実施の形態6に係る半導体装置を示す回路図である。AND回路5のa端子にパワー素子Q2のゲートの電圧が入力され、b端子に入力信号/INが入力される。AND回路5は、入力信号/INがオン信号であり、かつパワー素子Q2のゲートの電圧VGが低圧端子の電圧VGNDより高くなった場合(ゲート浮き期間)にだけ、スイッチング素子Q3をオンさせる。これにより、実施の形態3と同様の効果を得ることができる。

【0027】

また、AND回路5のb端子に入力する入力信号/INは入力信号INのターンオフからデッドタイムだけ遅れてターンオンするため、実施の形態3の遅延回路4は不要となる。

【0028】

実施の形態7.

図10は、本発明の実施の形態7に係る半導体装置を示す回路図である。ダイオードZ1が抵抗R1に並列に接続されている。その他の構成は実施の形態1と同様である。

【0029】

実施の形態1ではパワー素子Q2のゲートの放電電流が抵抗R1を流れるため、放電スピードが遅くなる。これに対して、本実施の形態では、パワー素子Q2のゲートの放電電流がダイオードZ1を流れるため、放電スピードが速くなる。なお、実施の形態2〜6の構成にダイオードZ1を追加しても同様の効果を得ることができる。

【0030】

実施の形態8.

図11は、本発明の実施の形態8に係る半導体装置を示す回路図である。ツェナーダイオードZ2が抵抗R1に並列に接続されている。その他の構成は実施の形態1と同様である。ツェナーダイオードZ2が負電圧をクランプするため、過度な負電圧を防止することができる。なお、実施の形態2〜6の構成にツェナーダイオードZ2を追加しても同様の効果を得ることができる。

【0031】

なお、上記の実施の形態1〜5において、Nサイドのパワー素子Q2のゲート電圧を負電圧にする場合について説明したが、これに限らずPサイドのパワー素子Q1のゲート電圧を負電圧にする場合にも本発明を適用することができる。

【0032】

また、パワー素子Q1,Q2及びスイッチング素子Q3はIGBT(Insulated Gate Bipolar Transistor)であるが、これに限らずパワーMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)等のパワースイッチング素子でもよい。

【0033】

また、パワー素子Q1,Q2及びスイッチング素子Q3は、珪素によって形成されたものに限らず、珪素に比べてバンドギャップが大きいワイドバンドギャップ半導体によって形成されたものでもよい。ワイドバンドギャップ半導体は、例えば、炭化珪素、窒化ガリウム系材料、又はダイヤモンドである。このようなワイドバンドギャップ半導体によって形成されたパワー半導体素子は、耐電圧性や許容電流密度が高いため、小型化できる。この小型化された素子を用いることで、この素子を組み込んだ半導体モジュールも小型化できる。また、素子の耐熱性が高いため、ヒートシンクの放熱フィンを小型化でき、水冷部を空冷化できるので、半導体モジュールを更に小型化できる。また、素子の電力損失が低く高効率であるため、半導体モジュールを高効率化できる。

【符号の説明】

【0034】

1 駆動回路(第1の駆動回路)

2 駆動回路(第2の駆動回路)

5 AND回路(制御回路)

IN 入力信号(第1の入力信号)

/IN 入力信号(第2の入力信号)

Q1 パワー素子(第2のパワー素子)

Q2 パワー素子(第1のパワー素子)

Q3 スイッチング素子

R1 抵抗

Z1 ダイオード

Z2 ツェナーダイオード

【技術分野】

【0001】

本発明は、簡単な回路構成により誤動作を防止できる半導体装置に関する。

【背景技術】

【0002】

モータなどの負荷の電力制御にはブリッジ回路や3相交流インバータ回路などの半導体装置が用いられる。これらの半導体装置は、電源電位と接地電位の間にトーテムポール接続された2つのパワー素子と、それらを駆動する駆動回路とを有する。2つのパワー素子の中点は負荷と接続され、2つのパワー素子のオン・オフの制御により負荷を制御する(例えば、特許文献1参照)。

【0003】

図12は、従来の半導体装置を示す回路図である。パワー素子Q1のターンオン時に、パワー素子Q2のコレクタ・エミッタ間にdV/dtが印加される。この場合にパワー素子Q2のゲート・コレクタ間の寄生容量Cresを充電する電流が流れるため、パワー素子Q2のゲート電圧が上昇する(ゲート浮き)。このゲート浮きによりパワー素子Q2のゲート電圧が閾値電圧を越えると、パワー素子Q2が誤オンし、短絡電流が流れてしまう。

【0004】

そこで、パワー素子Q2がオフ時に、負電圧用電源を用いてパワー素子Q2のゲートに負電圧V‐を印加する。これにより、パワー素子Q2のゲート電圧がエミッタ電圧(GND)より低くなるため、ゲート浮きが発生してもパワー素子Q2のゲート電圧が閾値電圧まで上昇し難くなる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−178579号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の半導体装置は、複数の電源が必要であり、回路構成が複雑になるという問題があった。

【0007】

本発明は、上述のような課題を解決するためになされたもので、その目的は簡単な回路構成により誤動作を防止できる半導体装置を得るものである。

【課題を解決するための手段】

【0008】

本発明に係る半導体装置は、制御端子と、第1端子と、第2端子とを有する第1のパワー素子と、前記第1のパワー素子にトーテムポール接続された第2のパワー素子と、電源に接続された高圧端子と、低圧端子とを有し、第1の入力信号に応じて前記第1のパワー素子を駆動する第1の駆動回路と、第2の入力信号に応じて前記第2のパワー素子を駆動する第2の駆動回路と、一端が前記第1のパワー素子の前記第2端子に接続され、他端が前記第1の駆動回路の前記低圧端子に接続された抵抗と、前記第1の駆動回路の前記高圧端子と前記抵抗の前記一端との間に接続され、前記第1の入力信号又は前記第2の入力信号に応じてオン・オフするスイッチング素子とを備え、前記第1の入力信号がオフ信号の場合に、前記第1の駆動回路は前記低圧端子の電圧を前記第1のパワー素子の前記制御端子に供給して前記第1のパワー素子はオフし、前記第1の入力信号がオフ信号又は前記第2の入力信号がオン信号の場合に、前記スイッチング素子はオンすることを特徴とする。

【発明の効果】

【0009】

本発明により、簡単な回路構成により誤動作を防止できる。

【図面の簡単な説明】

【0010】

【図1】本発明の実施の形態1に係る半導体装置を示す回路図である。

【図2】図1の半導体装置の動作を示すタイミングチャートである。

【図3】本発明の実施の形態2に係る半導体装置を示す回路図である。

【図4】図3の半導体装置の動作を示すタイミングチャートである。

【図5】本発明の実施の形態3に係る半導体装置を示す回路図である。

【図6】図5の半導体装置の動作を示すタイミングチャートである。

【図7】本発明の実施の形態4に係る半導体装置を示す回路図である。

【図8】本発明の実施の形態5に係る半導体装置を示す回路図である。

【図9】本発明の実施の形態6に係る半導体装置を示す回路図である。

【図10】本発明の実施の形態7に係る半導体装置を示す回路図である。

【図11】本発明の実施の形態8に係る半導体装置を示す回路図である。

【図12】従来の半導体装置を示す回路図である。

【発明を実施するための形態】

【0011】

本発明の実施の形態に係る半導体装置について図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

【0012】

実施の形態1.

図1は、本発明の実施の形態1に係る半導体装置を示す回路図である。電源電位と接地電位の間にパワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。

【0013】

駆動回路1は、電源に接続された高圧端子と、接地された低圧端子とを有する。インバータINVが入力信号INを反転して出力し、その出力信号を駆動回路1が反転増幅してパワー素子Q2のゲートに供給する。

【0014】

抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。このスイッチング素子Q3のゲートにはインバータINVの出力信号が供給され、スイッチング素子Q3は入力信号INに応じてオン・オフする。

【0015】

図2は、図1の半導体装置の動作を示すタイミングチャートである。このタイミングチャートを参照して図1の半導体装置の動作を説明する。入力信号/INは入力信号INを反転したものであるが、両者の間にはデッドタイムが存在する。

【0016】

入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。この場合に入力信号/INはオン信号となるため、駆動回路2は高電圧をパワー素子Q1のゲートに供給してパワー素子Q1はオンする。

【0017】

一方、入力信号INがオン信号の場合に、駆動回路1は高圧端子の電圧をパワー素子Q2のゲートに供給してパワー素子Q2はオンする。この場合に入力信号/INはオフ信号となるため、駆動回路2は低電圧をパワー素子Q1のゲートに供給してパワー素子Q1はオフする。

【0018】

入力信号INがオフ信号の場合に、スイッチング素子Q3はオンし、抵抗R1に電流が流れる。これにより、駆動回路1の低圧端子の電圧VGNDが、パワー素子Q2のエミッタ電圧VEよりも抵抗R1の電圧降下分だけ低くなる。従って、パワー素子Q2のオフ時のゲート電圧VGがエミッタ電圧VEに対して負電圧になるため、ゲート浮きが発生してもパワー素子Q2のゲート電圧が閾値電圧まで上昇し難くなる。よって、負電圧用電源を必要としない簡単な回路構成により誤動作を防止できる。

【0019】

実施の形態2.

図3は、本発明の実施の形態2に係る半導体装置を示す回路図である。ワンショット回路3は、入力信号INのターンオフ時にスイッチング素子Q3のゲートにパルス信号を供給する。

【0020】

図4は、図3の半導体装置の動作を示すタイミングチャートである。ワンショット回路3からのパルス信号により、スイッチング素子Q3は、パワー素子Q1のターンオンが完了するまでの所定期間だけオンする。従って、実施の形態1に比べてスイッチング素子Q3のオン期間が短くなるため、電源の消費電力を削減することができる。

【0021】

実施の形態3.

図5は、本発明の実施の形態3に係る半導体装置を示す回路図である。遅延回路4がインバータINVの出力信号を遅延させる。AND回路5のa端子にパワー素子Q2のゲートの電圧が入力され、b端子に遅延回路4の出力電圧が入力される。スイッチング素子Q3はAND回路5の出力信号に応じてオン・オフする。

【0022】

図6は、図5の半導体装置の動作を示すタイミングチャートである。AND回路5は、入力信号INがオフ信号であり、かつパワー素子Q2のゲートの電圧が低圧端子の電圧VGNDより高くなった場合(ゲート浮き期間)にだけ、スイッチング素子Q3をオンさせる。これにより、スイッチング素子Q3のオン期間が更に短くなるため、電源の消費電力を大幅に削減することができる。また、保護期間が広くなる。

【0023】

また、パワー素子Q2のターンオフ期間にはパワー素子Q2のゲートの電圧が高電圧となる。そこで、パワー素子Q2のターンオフ期間に保護動作を行わないように、遅延回路4を設けている。

【0024】

実施の形態4.

図7は、本発明の実施の形態4に係る半導体装置を示す回路図である。実施の形態1とは異なり、スイッチング素子Q3のゲートには入力信号/INが供給され、スイッチング素子Q3は入力信号/INに応じてオン・オフする。入力信号/INがオン信号の場合にスイッチング素子Q3はオンする。これにより、デッドタイムにスイッチング素子Q3がオンしないため、実施の形態1に比べて電源の消費電力を削減することができる。その他、実施の形態1と同様の効果を得ることができる。

【0025】

実施の形態5.

図8は、本発明の実施の形態5に係る半導体装置を示す回路図である。この半導体装置は、実施の形態4の半導体装置にワンショット回路3を追加したものである。ワンショット回路3は、入力信号/INのターンオン時にスイッチング素子Q3のゲートにパルス信号を供給する。これにより、スイッチング素子Q3はパワー素子Q1のターンオンが完了するまでの所定期間だけオンする。さらに、スイッチング素子Q3のオン期間は実施の形態2に比べて短くなる。この結果、電源の消費電力を大幅に削減することができる。

【0026】

実施の形態6.

図9は、本発明の実施の形態6に係る半導体装置を示す回路図である。AND回路5のa端子にパワー素子Q2のゲートの電圧が入力され、b端子に入力信号/INが入力される。AND回路5は、入力信号/INがオン信号であり、かつパワー素子Q2のゲートの電圧VGが低圧端子の電圧VGNDより高くなった場合(ゲート浮き期間)にだけ、スイッチング素子Q3をオンさせる。これにより、実施の形態3と同様の効果を得ることができる。

【0027】

また、AND回路5のb端子に入力する入力信号/INは入力信号INのターンオフからデッドタイムだけ遅れてターンオンするため、実施の形態3の遅延回路4は不要となる。

【0028】

実施の形態7.

図10は、本発明の実施の形態7に係る半導体装置を示す回路図である。ダイオードZ1が抵抗R1に並列に接続されている。その他の構成は実施の形態1と同様である。

【0029】

実施の形態1ではパワー素子Q2のゲートの放電電流が抵抗R1を流れるため、放電スピードが遅くなる。これに対して、本実施の形態では、パワー素子Q2のゲートの放電電流がダイオードZ1を流れるため、放電スピードが速くなる。なお、実施の形態2〜6の構成にダイオードZ1を追加しても同様の効果を得ることができる。

【0030】

実施の形態8.

図11は、本発明の実施の形態8に係る半導体装置を示す回路図である。ツェナーダイオードZ2が抵抗R1に並列に接続されている。その他の構成は実施の形態1と同様である。ツェナーダイオードZ2が負電圧をクランプするため、過度な負電圧を防止することができる。なお、実施の形態2〜6の構成にツェナーダイオードZ2を追加しても同様の効果を得ることができる。

【0031】

なお、上記の実施の形態1〜5において、Nサイドのパワー素子Q2のゲート電圧を負電圧にする場合について説明したが、これに限らずPサイドのパワー素子Q1のゲート電圧を負電圧にする場合にも本発明を適用することができる。

【0032】

また、パワー素子Q1,Q2及びスイッチング素子Q3はIGBT(Insulated Gate Bipolar Transistor)であるが、これに限らずパワーMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)等のパワースイッチング素子でもよい。

【0033】

また、パワー素子Q1,Q2及びスイッチング素子Q3は、珪素によって形成されたものに限らず、珪素に比べてバンドギャップが大きいワイドバンドギャップ半導体によって形成されたものでもよい。ワイドバンドギャップ半導体は、例えば、炭化珪素、窒化ガリウム系材料、又はダイヤモンドである。このようなワイドバンドギャップ半導体によって形成されたパワー半導体素子は、耐電圧性や許容電流密度が高いため、小型化できる。この小型化された素子を用いることで、この素子を組み込んだ半導体モジュールも小型化できる。また、素子の耐熱性が高いため、ヒートシンクの放熱フィンを小型化でき、水冷部を空冷化できるので、半導体モジュールを更に小型化できる。また、素子の電力損失が低く高効率であるため、半導体モジュールを高効率化できる。

【符号の説明】

【0034】

1 駆動回路(第1の駆動回路)

2 駆動回路(第2の駆動回路)

5 AND回路(制御回路)

IN 入力信号(第1の入力信号)

/IN 入力信号(第2の入力信号)

Q1 パワー素子(第2のパワー素子)

Q2 パワー素子(第1のパワー素子)

Q3 スイッチング素子

R1 抵抗

Z1 ダイオード

Z2 ツェナーダイオード

【特許請求の範囲】

【請求項1】

制御端子と、第1端子と、第2端子とを有する第1のパワー素子と、

前記第1のパワー素子にトーテムポール接続された第2のパワー素子と、

電源に接続された高圧端子と、低圧端子とを有し、第1の入力信号に応じて前記第1のパワー素子を駆動する第1の駆動回路と、

第2の入力信号に応じて前記第2のパワー素子を駆動する第2の駆動回路と、

一端が前記第1のパワー素子の前記第2端子に接続され、他端が前記第1の駆動回路の前記低圧端子に接続された抵抗と、

前記第1の駆動回路の前記高圧端子と前記抵抗の前記一端との間に接続され、前記第1の入力信号又は前記第2の入力信号に応じてオン・オフするスイッチング素子とを備え、

前記第1の入力信号がオフ信号の場合に、前記第1の駆動回路は前記低圧端子の電圧を前記第1のパワー素子の前記制御端子に供給して前記第1のパワー素子はオフし、

前記第1の入力信号がオフ信号又は前記第2の入力信号がオン信号の場合に、前記スイッチング素子はオンすることを特徴とする半導体装置。

【請求項2】

前記スイッチング素子は、前記第2のパワー素子のターンオンが完了するまでの所定期間だけオンすることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1の入力信号がオフ信号又は前記第2の入力信号がオン信号であり、かつ前記第1のパワー素子の前記制御端子の電圧が前記低圧端子の電圧より高くなった場合にだけ、前記スイッチング素子をオンさせる制御回路を更に備えることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記抵抗に並列に接続されたダイオード又はツェナーダイオードを更に備えることを特徴とする請求項1〜3の何れか1項に記載の半導体装置。

【請求項1】

制御端子と、第1端子と、第2端子とを有する第1のパワー素子と、

前記第1のパワー素子にトーテムポール接続された第2のパワー素子と、

電源に接続された高圧端子と、低圧端子とを有し、第1の入力信号に応じて前記第1のパワー素子を駆動する第1の駆動回路と、

第2の入力信号に応じて前記第2のパワー素子を駆動する第2の駆動回路と、

一端が前記第1のパワー素子の前記第2端子に接続され、他端が前記第1の駆動回路の前記低圧端子に接続された抵抗と、

前記第1の駆動回路の前記高圧端子と前記抵抗の前記一端との間に接続され、前記第1の入力信号又は前記第2の入力信号に応じてオン・オフするスイッチング素子とを備え、

前記第1の入力信号がオフ信号の場合に、前記第1の駆動回路は前記低圧端子の電圧を前記第1のパワー素子の前記制御端子に供給して前記第1のパワー素子はオフし、

前記第1の入力信号がオフ信号又は前記第2の入力信号がオン信号の場合に、前記スイッチング素子はオンすることを特徴とする半導体装置。

【請求項2】

前記スイッチング素子は、前記第2のパワー素子のターンオンが完了するまでの所定期間だけオンすることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1の入力信号がオフ信号又は前記第2の入力信号がオン信号であり、かつ前記第1のパワー素子の前記制御端子の電圧が前記低圧端子の電圧より高くなった場合にだけ、前記スイッチング素子をオンさせる制御回路を更に備えることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記抵抗に並列に接続されたダイオード又はツェナーダイオードを更に備えることを特徴とする請求項1〜3の何れか1項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−81137(P2013−81137A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2011−221157(P2011−221157)

【出願日】平成23年10月5日(2011.10.5)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成23年10月5日(2011.10.5)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]