半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

近年、半導体装置は、ますます微細化が進み、配線層間および配線間の寄生容量が無視できない。例えば、電圧制御発振回路のような高速で動作させる必要のあるリングオシレータにおいては、出力部の接点容量が大きいと高速動作ができない。

【0003】

この問題に対して、特許文献1に、トランジスタの接点容量を削減する方法が開示されている。この文献に開示された発明では、トランジスタの出力部に隣接するソース領域にダミートランジスタを配置することで、出力部およびソース領域間のカップリング容量を削減し、出力部の接点容量を削減している。

【0004】

特許文献2には、ソースおよびドレインのコンタクトの数を減らし、交互に配置したトランジスタのパターンレイアウトが開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−278952号公報

【特許文献2】特開2010−10515号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に開示された方法では、寄生容量を削減する効果が得られるが、ダミートランジスタのゲート本数を増やす度に寄生容量の削減効果が低減し、削減量が飽和してしまう傾向がある。また、ダミートランジスタが設けられる面積が大きくなってしまう問題もある。ダミートランジスタを配置して寄生容量の削減を図るのには限界があり、面積を拡大しても得られる効果は大きくない。また、特許文献2に開示された方法も、十分な効果が得られない。

【課題を解決するための手段】

【0007】

本発明の第1の側面の半導体装置は、

それぞれが、ドレイン拡散層と、該ドレイン拡散層を挟んで両側に配設される一対のソース拡散層と、前記ドレイン拡散層と前記一対のソース拡散層との間にそれぞれ配設される一対のゲート電極とを有し、列方向に配列される複数のトランジスタと、

前記一対のソース拡散層の内の一方を含む互いに隣接する2つのソース拡散層の間に配列され、該2つのソース拡散層と同電位に維持されている第1のダミーゲート電極と、

前記一対のソース拡散層の内の他方を含む互いに隣接する2つのソース拡散層の間に配列され、該2つのソース拡散層と同電位に維持されている第2のダミーゲート電極と、

複数の第1のビアを介して前記ドレイン拡散層に接続する第1の金属配線と、

前記一対のソース拡散層の一方であって前記互いに隣接する2つのソース拡散層の両方にそれぞれ対応する複数の第1のビアを介して接続する第2の金属配線と、

前記一対のソース拡散層の他方であって前記互いに隣接する2つのソース拡散層の両方にそれぞれ対応する複数の第1のビアを介して接続する第3の金属配線と、

前記第1乃至第3の金属配線にそれぞれ対応する複数の第2のビアを介して接続する第4乃至第6の金属配線と、を備え、

前記第2及び第3の金属配線の前記列方向におけるそれぞれの幅は、対応する前記2つのソース拡散層にそれぞれ接続する複数の第1のビアの両方を含む第1の幅と、前記第1のビアを含まず前記第1の幅よりも短い第2の幅と、を有し、

前記第1及び第2の金属配線の間、並びに前記第1及び第3の金属配線の間のそれぞれのギャップは、前記第1の幅に対応する第1のギャップと、前記第2の幅に対応する前記第1のギャップよりも大きな第2のギャップと、を有する。

【0008】

本発明では、第2の金属配線および第3の金属配線のそれぞれのパターンは、第1の幅よりも短い第2の幅の部位を有しているので、ソース電極に接続される第2の金属配線および第3の金属配線のそれぞれとドレイン電極に接続される第1の金属配線の配線間距離として、第1のギャップよりも長い第2のギャップSP2が存在する。そのため、少なくともソース電極およびドレイン電極間の配線間容量が低減する。

【0009】

本発明の第2の側面の半導体装置は、

トランジスタのソース電極またはドレイン電極を構成し、それぞれ第1の方向に延在する第1乃至第5の拡散部を含む拡散層と、

前記トランジスタのゲート電極を構成し、前記第1の方向に延在する第1及び第2のゲート配線、並びに前記第1の方向に延在する第1及び第2のダミーゲート配線を含むゲート層と、

前記第1の方向に延在する第1乃至第3の金属配線を含む第1の金属層と、

前記第1の方向に延在する第4から第6の金属配線を含む第2の金属層と、

前記第1の方向に展開して配置される複数の第1のビアを含み、前記拡散層と前記第1の金属層を接続する第1のビア層と、

前記第1の方向に展開して配置される複数の第2のビアを含み、前記第1及び第2の金属層を接続する第2のビア層と、を備え、

第1のトランジスタは、前記第1のゲート配線、前記第1及び第2の拡散部で構成され、

第2のトランジスタは、前記第2のゲート配線、前記第1及び第3の拡散部で構成され、前記第1のトランジスタに隣接して前記第1の方向と直交する第2の方向へ配置され、

第3のトランジスタは、前記1のダミーゲート配線、並びに、前記第2及び第4の拡散部で構成され、前記第1のトランジスタに隣接して、前記第2の方向とは反対の第3の方向に配置され、更に前記1のダミーゲート配線、並びに、前記第3及び第4の拡散部は、同電位であり、

第4のトランジスタは、前記2のダミーゲート配線、並びに、前記第3及び第5の拡散部で構成され、前記第2のトランジスタに隣接して前記第2の方向に配置され、更に前記2のダミーゲート配線、並びに、前記第3及び第5の拡散部は、同電位であり、

それぞれが、少なくとも一つの前記第1のビアをセットとする複数の第1セットが、第1のピッチで前記第1の拡散部に配置され、

それぞれが、少なくとも一つの前記第1のビアをセットとする複数の第2セットが、第2のピッチで前記第2乃至第5の拡散部にそれぞれ配置され、

前記第1の金属配線は、前記第1の拡散部に関連する複数の第1のビアを覆うように前記第1の拡散部の領域に配置され、

前記第2の金属配線は、前記第2及び第4の拡散部にそれぞれ関連する複数の第1のビアを一体として覆うように前記第3のトランジスタの領域に配置され、

前記第3の金属配線は、前記第3及び第5の拡散部にそれぞれ関連する複数の第1のビアを一体として覆うように前記第4のトランジスタの領域に配置され、

それぞれが、少なくとも一つの前記第2のビアをセットとする複数の第3セットが、第3のピッチで前記第1の金属配線に配置され、

それぞれが、少なくとも一つの前記第2のビアをセットとする複数の第4セットが、第4のピッチで前記第2及び第3の金属配線にそれぞれ配置され、

前記第4の金属配線は、前記第1の金属配線に関連する複数の第2のビアを覆うように前記第1の拡散部の領域に配置され、

前記第5の金属配線は、前記第2の金属配線に関連する複数の第2のビアを覆うように前記第3のトランジスタの領域に配置され、

前記第6の金属配線は、前記第3の金属配線に関連する複数の第2のビアを覆うように前記第4のトランジスタの領域に配置され、

前記第2の金属配線の前記第3の方向における幅は、前記第2の拡散部に関連する前記第1のビア及び前記第4の拡散部に関連する前記第1のビアの両方を含む第1の幅と、前記第1の幅よりも短い第2の幅と、を有し、

前記第3の金属配線の前記第2の方向における幅は、前記第3の拡散部に関連する前記第1のビア及び前記第5の拡散部に関連する前記第1のビアの両方を含む前記第1の幅と、前記第2の幅と、を有し、

前記第4乃至第6の金属配線の前記第2の方向におけるそれぞれの幅は、前記第1の幅よりも短い第3の幅を有し、

前記第1及び第2の金属配線の間、並びに前記第1及び第3の金属配線の間のそれぞれのギャップは、前記第1の幅に対応する第1のギャップと、前記第2の幅に対応する前記第1のギャップよりも大きな第2のギャップと、を有する。

【発明の効果】

【0010】

本発明によれば、トランジスタおよびダミートランジスタの面積を拡大せずに寄生容量を削減できる。ゲート狭ピッチプロセスにおいても、チップ面積を最小限に抑えながら、寄生容量を削減できる。

【図面の簡単な説明】

【0011】

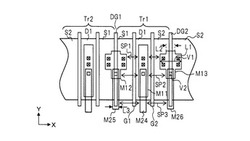

【図1】本実施形態の半導体装置の一構成例を示す平面図である。

【図2】実施例1の半導体装置の一構成例を示すブロックダイアグラムである。

【図3A】実施例1の半導体装置に設けられたリングオシレータの一構成例を示す回路パターン図である。

【図3B】実施例1の回路図である。

【図4】実施例1において、図3Aに示したリングオシレータに含まれるP−Trのパターンの一例を示す平面図である。

【図5】図4に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。

【図6A】図4に示す線分AAの部位の断面図である。

【図6B】図4に示す線分BBの部位の断面図である。

【図7】図4に示したP−Trの形成過程の一例を示す平面図である。

【図8】図4に示したP−Trの形成過程の一例を示す平面図である。

【図9】実施例2において、図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。

【図10】図9に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。

【図11A】図9に示す線分AAの部位の断面図である。

【図11B】図9に示す線分BBの部位の断面図である。

【図12】実施例3において、図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。

【図13】図12に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。

【図14A】図12に示す線分AAの部位の断面図である。

【図14B】図12に示す線分BBの部位の断面図である。

【図15】実施例4において、図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。

【図16】図15に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。

【図17A】図15に示す線分AAの部位の断面図である。

【図17B】図15に示す線分BBの部位の断面図である。

【発明を実施するための形態】

【0012】

本発明の課題を解決する技術思想(コンセプト)の代表的な一例は、以下に示される。ただし、本願の請求内容は、この技術思想に限られず、本願の請求項に記載の内容であることは言うまでもない。

【0013】

本発明の半導体装置は、トランジスタのドレイン領域にビアを介して接続される第1金属配線とダミーゲートが接続されるソース領域にビアを介して接続される第2金属配線とのギャップのうち、最も小さなギャップが短くなるように、第1金属配線および第2金属配線のパターンレイアウト、ならびにそれぞれの金属配線に対応するビアの配置が設定されていることを特徴とする。

【0014】

図1は本実施形態の半導体装置の一構成例を示す平面図である。

【0015】

図1に示すように、本実施形態の半導体装置は、X軸方向に配置された複数のMOS(Metal Oxide Semiconductor)FET(Field Effect Transistor)(以下では、単にトランジスタと称する)Tr1、Tr2を有する。トランジスタTr1、Tr2は同様な構成であるため、トランジスタTr1の構成について説明する。また、X軸方向は、トランジスタTr1、Tr2が配列される方向なのでX軸方向を「列方向」と称し、列方向に垂直方向となるY軸方向を「行方向」と称する。

【0016】

トランジスタTr1は、ドレイン拡散層D1と、ドレイン拡散層D1を挟んで両側に配設される一対のソース拡散層S1、S2と、ドレイン拡散層D1と一対のソース拡散層S1、S2との間にそれぞれ配設される一対のゲート電極G1、G2とを有する。

【0017】

トランジスタTr1のソース拡散層S1は、ダミーゲート電極DG1を介してトランジスタTr2が有するソース拡散層S1と隣接する。これら2つのソース拡散層S1とダミーゲート電極DG1は、同電位が供給される。

【0018】

トランジスタTr1のソース拡散層S2は、ダミーゲート電極DG2を介してトランジスタTr3(不図示)が有するソース拡散層S2と隣接する。これら2つのソース拡散層S2とダミーゲート電極DG2は、同電位が供給される。

【0019】

ゲート電極G1、G2よりも上層に、第1金属配線M11、第2金属配線M12および第3金属配線M13を含む第1金属配線層が設けられている。第1金属配線M11は複数の第1ビアV1を介してドレイン拡散層D1に接続されている。第2金属配線M12は、ダミーゲート電極DG1を介して互いに隣接する2つのソース拡散層の両方S1にそれぞれ対応する複数の第1ビアV1を介して接続されている。第3金属配線M13は、ダミーゲート電極DG2を介して互いに隣接する2つのソース拡散層の両方S2にそれぞれ対応する複数の第1ビアV1を介して接続されている。

【0020】

また、第1金属配線層よりも上層に、第4金属配線M24、第5金属配線M25および第6金属配線26を含む第2金属配線層が設けられている。第4金属配線M24〜第6金属配線M26のそれぞれは第2ビアV2を介して第1金属配線M11〜第3金属配線M13のそれぞれと接続されている。

【0021】

第2金属配線M12および第3金属配線M13のX軸方向におけるそれぞれの幅は、対応する2つのソース拡散層S1、S2にそれぞれ接続する複数の第1ビアV1のサイズの両方を含む第1の幅L1と、第1ビアV1のサイズを含まず、第1の幅L1よりも短い第2の幅L2と、を有する。

【0022】

第1金属配線M11および第2金属配線M12の間、ならびに第1金属配線M11および第3金属配線M13の間のそれぞれのギャップは、第1の幅L1に対応する第1のギャップSP1と、第2の幅L2に対応する、第1のギャップSP1よりも大きな第2のギャップSP2と、を有する。

【0023】

第4金属配線M24〜第6金属配線M26のX軸方向におけるそれぞれの幅は、第1の幅L1よりも短い第3の幅L3を有する。そして、第4金属配線M24および第5金属配線M25の間、ならびに第4金属配線M24および第6金属配線M26の間のそれぞれのギャップは、第2のギャップSP2よりも更に大きな第3のギャップSP3を有する構成である。

【0024】

本実施形態では、第2金属配線M12および第3金属配線M13のそれぞれのパターンは、幅L1よりも短い幅L2の部位を有するので、ソース電極に接続される第2金属配線M12および第3金属配線M13のそれぞれとドレイン電極に接続される第1金属配線M11の配線間距離として、第1のギャップSP1よりも長い第2のギャップSP2が存在する。そのため、2つのソース電極および1つのドレイン電極間の配線間容量(寄生容量)が低減する。

【0025】

さらに、ソース電極に接続される第5金属配線M25および第6金属配線M26のそれぞれとドレイン電極に接続される第4金属配線M24の配線間距離に相当する第3のギャップSP3が第2のギャップSP2よりも大きいので、2つのソース電極および1つのドレイン電極間の配線間容量(寄生容量)がそれぞれ低減する。

【0026】

なお、図1では、第1金属配線M11に接続される第1ビアV1が、第2金属配線M12および第3金属配線M13のそれぞれに接続される第1ビアV1と、Y軸方向の位置が同一で、対向する位置に配置されている場合を示しているが、Y軸方向の位置が異なっていてもよい。

【0027】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について詳細に説明する。

【実施例1】

【0028】

本実施例の半導体装置の一構成例を説明する。本実施例では、半導体装置がメモリデバイスの場合で説明する。

【0029】

図2は本実施例の半導体装置の一構成例を示すブロックダイアグラムである。

【0030】

図2に示すように、本実施例の半導体装置10は、複数のメモリ素子を含むメモリセルアレイ21と、アドレス信号にしたがって制御対象のメモリ素子を特定するロウデコーダ22およびカラムデコーダ23と、メモリ素子に蓄積された情報に対応する信号を増幅するセンスアンプ24と、データ入出力部25と、各部にクロック信号を提供するクロック生成部26と、信号およびデータを入出力するための複数の外部端子とを有する。クロック生成部26はリングオシレータを有する。リングオシレータの回路の一例が、後述する図3Bに開示されている。

【0031】

複数の外部端子として、アドレス信号を入力するための複数の入力端子を含むアドレス入力端子群31と、コマンドを入力するための複数の入力端子を含むコマンド入力端子群32と、データを入出力するための複数の端子を含むデータ入出力端子群33とが設けられている。

【0032】

図3Aは本実施例の半導体装置に設けられたリングオシレータの一構成例を示す回路パターン図である。図3Bはその回路図である。

【0033】

図3Aに示すリングオシレータは、3つのP型チャネルMOSFET(以下では、P−Trと表記する)111〜113が設けられたNウェル領域101と、3つのN型チャネルMOSFET(以下では、N−Trと表記する)121〜123が設けられたPウェル領域102とを有する。Nウェル領域101には、半導体基板の主表面からN型導電性不純物が拡散されている。Pウェル領域102には、半導体基板の主表面からP型導電性不純物が拡散されている。

【0034】

P−Tr111およびN−Tr121で1つのインバータ回路が構成される。P−Tr112およびN−Tr122で1つのインバータ回路が構成される。P−Tr113およびN−Tr123で1つのインバータ回路が構成される。

【0035】

P−Tr111およびN−Tr121のそれぞれのゲート電極が配線131で接続され、P−Tr111およびN−Tr121のそれぞれのドレイン電極が配線141で接続されている。P−Tr112およびN−Tr122のそれぞれのゲート電極が配線132で接続され、P−Tr112およびN−Tr122のそれぞれのドレイン電極が配線142で接続されている。P−Tr113およびN−Tr123のそれぞれのゲート電極が配線133で接続され、P−Tr113およびN−Tr123のそれぞれのドレイン電極が配線143で接続されている。

【0036】

図3Aに示すように、配線131がビアを介して配線142と接続され、配線132がビアを介して配線143と接続されている。配線133は、ビアおよび配線151を介して配線141と接続されている。なお、配線131〜133はゲート電極と同一層に形成され、配線141〜143は第2金属配線層に形成され、配線151は第1金属配線層に形成されている。

【0037】

図3Aに示すリングオシレータのパターンレイアウト及びその一部である図1を、図3Bの回路図で示す。

【0038】

各トランジスタにはその名前の一部に「Tr」の符号が付されている。P型トランジスタにはその名前の一部に「P」の符号が付されている。N型トランジスタにはその名前の一部に「N」の符号が付されている。ダミーゲートとしての機能を有するトランジスタ(ダミートランジスタ)にはその名前の一部に「DTr」の符号が付されている。各トランジスタのゲート電極にはその名前の一部に「G」の符号が付されている。各トランジスタのソース電極(ソース拡散層)にはその名前の一部に「S」の符号が付されている。各トランジスタのドレイン電極(ドレイン拡散層)にはその名前の一部に「D」の符号が付されている。なお、ゲート電極は制御端子であり、ソース電極は被制御端子の一方、ドレイン電極は被制御端子の他方である。

【0039】

各トランジスタのバックゲート(ウェル)は、矢印で示される。リングオシレータの各ノード(配線)は3桁の数字で示される。高電位電源はVDD、低電位電源はVSSで示される。リングオシレータは、それぞれP型トランジスタ及びN型トランジスタをペアとする複数の相補トランジスタで構成される。一つの相補トランジスタにおいて、P型トランジスタは2つのトランジスタ、N型トランジスタは2つのトランジスタで構成される。2つのトランジスタは、ドレイン拡散層が共通であるが、ソース拡散層は異なる。詳細には、2つのトランジスタは、異なるゲート配線層を介して異なるソース拡散層を有する。異なるソース拡散層は、それぞれ対応する2つのダミートランジスタの拡散層として共用される。2つのダミートランジスタのそれぞれは、前段のトランジスタ(2つのトランジスタの一方)のソース拡散層と後段のトランジスタ(2つのトランジスタの他方)のソース拡散層を2つの被制御端子とし、制御端子(ゲート電極)を有するトランジスタである。制御端子及び2つの被制御端子は、同一の電位が供給される。よって、ダミートランジスタと呼称されている。電気的な視点において、異なる拡散層は対応する共通な電源に接続される。

【0040】

次に、図3Aに示したリングオシレータの動作を簡単に説明する。

【0041】

配線143に現われている第1の電位が配線143から外部に出力される。この配線143に現われる電位を外部に出力するための出力端子の符号をOUT1で表す。配線143の第1の電位は、出力端子OUT1から出力されるだけでなく、配線132を介してP−Tr112およびN−Tr122のそれぞれのゲート電極に印加される。第1の電位がP−Tr112およびN−Tr122のそれぞれのゲート電極に印加されることで、第1の電位の反転電位である第2の電位が配線142に出力される。配線142に現われた第2の電位が配線131を介してP−Tr111およびN−Tr121のそれぞれのゲート電極に印加されると、第2の電位が反転して第1の電位が配線141に出力される。

【0042】

続いて、配線141に現われた第1の電位が配線151および配線133を介してP−Tr113およびN−Tr123のそれぞれのゲート電極に印加されると、第1の電位が反転して第2の電位が配線143に出力される。配線143に出力された第2の電位は、出力端子OUT1を介して外部に出力されるとともに配線132に印加される。このようにして、第1の電位および第2の電位が所定の時間間隔で交互に、出力端子OUT1を介して外部に出力される。

【0043】

次に、図3Aに示したリングオシレータに含まれるP−Tr111〜113およびN−Tr121〜123のパターンレイアウトについて詳しく説明する。

【0044】

なお、P−Tr111〜113とN−Tr121〜123とはドレイン電極およびソース電極における導電性不純物のタイプが異なるだけなので、P−Tr111〜113の構成について説明する。また、P−Tr111〜113のそれぞれの構成は同様なので、P−Tr111〜113のいずれか一つのトランジスタを中心にしたパターンレイアウトについて説明する。N−Tr121〜123についても、本発明を適用できることは言うまでもない。

【0045】

図4は図3Aに示したリングオシレータに含まれるP−Trのパターンの一例を示す平面図である。図4では、Nウェル領域101を図に示すことを省略している。図5は図4に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。図4および図5に示す平面図において、図の左右方向をX軸方向とし、図の上下方向をY軸方向とする。

【0046】

図5に示すように、P−Trは、制御電極であるゲート電極G1、G2と、被制御電極である拡散層D1と、被制御電極である拡散層S1、S2とを有する。拡散層D1はドレイン電極に相当し、P型導電性不純物が拡散されている。拡散層S1、S2はソース電極に相当し、P型導電性不純物が拡散されている。拡散層D、S1、S2における導電性不純物の濃度は、図3Aに示したPウェル領域102の濃度よりも高い。

【0047】

ゲート電極G1、G2のそれぞれの外側には、ダミーゲート電極DG1、DG2がそれぞれ設けられている。ダミーゲート電極DG1、DG2は、図に示さない配線を介してソース電極に接続されている。本実施例では、ゲート電極G1、G2およびダミーゲート電極DG1、DG2のそれぞれのパターンは同一である。また、ゲート電極G1、G2およびダミーゲート電極DG1、DG2のパターンは、ゲート電極のパターンのX軸方向の長さ(以下では、ゲート長(またはチャネル長)と称する)がY軸方向に対して均一に、Y軸方向に延在している。

【0048】

ゲート電極G1、G2およびダミーゲート電極DG1、DG2のX軸方向の間隔が等しい構成である。つまり、ダミーゲート電極DG1およびゲート電極G1の距離と、ダミーゲート電極DG2およびゲート電極G2の距離のそれぞれが、ゲート電極G1およびゲート電極G2の距離と等しい。この間隔は、図3Aに示したP−Tr111〜113のように、複数のトランジスタがX軸方向に配置されている場合でも保たれている。

【0049】

これらのダミーゲート電極およびゲート電極の間隔を等しくすることで、半導体装置の製造過程で、ゲート電極のパターニング時における、ゲート長のばらつきを抑制できる。

【0050】

図4および図5に示す第1金属配線M11、第2金属配線M12および第3金属配線M13は第1金属配線層に設けられている。第1金属配線M11は第1ビアV1を介して拡散層D1と接続されている。第2金属配線M12は第1ビアV1を介して拡散層S1と接続され、第3金属配線M13は第1ビアV1を介して拡散層S2と接続されている。

【0051】

図4に示す第4金属配線M24、第5金属配線M25および第6金属配線M26は、第1金属配線層よりも上層に位置する第2金属配線層に設けられている。第4金属配線M24は第2ビアV2を介して第1金属配線M11と接続されている。第5金属配線M25は第2ビアV2を介して第2金属配線M12と接続され、第6金属配線M26は第2ビアV2を介して第3金属配線M13と接続されている。第4金属配線M24は、P−Tr111のドレイン電極に相当する拡散層D1に接続されているので、P−Tr111の出力端子OUT1に相当する。

【0052】

図4に示すように、本実施例では、第1ビアV1と第2ビアV2のパターンはマスク上においては正方形(製造後では円形)であり、第1ビアV1の1辺の長さが第2ビアV2の1辺の長さよりも小さい。そのため、パターン面積は、第2ビアV2の方が第2ビアV1よりも大きい。なお、本実施例では、第1ビアV1と第2ビアV2のパターンが正方形の場合で説明するが、これらのパターンは正方形に限定されず、楕円や円であってもよい。また、以下では、第1ビアV1および第2ビアV2のパターンのXY平面における最長箇所の長さをパターンサイズと称する。

【0053】

次に、第1金属配線M11〜第3金属配線M13のパターンと第1ビアV1の配置について、図5を参照して詳しく説明する。

【0054】

図5に示すように、第1金属配線M11のパターンは、第1金属配線M11のX軸方向の長さ(以下では、この長さを幅と呼ぶ)がY軸方向に対して均一に、Y軸方向に延在している。第1金属配線M11は、X軸方向に対して、ダミーゲート電極DG1およびダミーゲート電極DG2の間の距離の中央に配置されている。第2金属配線M12および第3金属配線M13のパターンは、第1ビアV1が接続される部位の幅の方が、第1ビアV1が接続されない部位の幅よりも長い。

【0055】

第1ビアV1が接続される部位の幅をW1と表し、第1ビアV1が接続されない部位の幅をW2と表すと、図5に示すように、W1>W2の関係になっている。本実施例では、第1金属配線M11の幅がW2に等しい。

【0056】

続いて、図5において、第1金属配線M11および第2金属配線M12の配線間距離に注目する。第2金属配線M12における幅W1の部位と第1金属配線M11との距離をGap1とし、第2金属配線M12における幅W2の部位と第1金属配線M11との距離をGap2とすると、図5を見てわかるように、Gap2>Gap1の関係になっている。この関係は、第1金属配線M11および第3金属配線M13の配線間隔についても同様である。

【0057】

次に、図5において、第1金属配線M11に接続される第1ビアV1の配置と第2金属配線M12に接続される第1ビアV1の配置に注目する。

【0058】

ここで、例えば、図5の第1金属配線M11を見ると、複数の第1ビアV1がY軸方向に配置されているが、隣り合う第1ビアV1の距離は、短いところと長いところの2種類がある。短い距離で隣り合う2つの第1ビアV1を1つの組と考え、この組を「第1ビアの組」と称する。

【0059】

第1金属配線M11では、第1ビアの組がY軸方向に等間隔に配置されている。図5では、その間隔をYL1で表している。第2金属配線M12においても、第1ビアの組が間隔YL1で配置されているが、Y軸方向の座標が第1金属配線M11に接続される第1ビアの組と異なっている。つまり、Y軸方向に対して、第1金属配線M11に接続される第1ビアの組と第2金属配線M12に接続される第1ビアの組とが交互に配置されている。また、第2金属配線M12では、複数の第1ビアの組が等間隔でY軸方向に配置される列が、ダミーゲート電極DG1の両側に、ダミーゲート電極DG1から同じ距離の位置に設けられている。

【0060】

図5において、第3金属配線M13に接続される第1ビアV1を見ると、第3金属配線M13における第1ビアの組の配置は、第2金属配線M12における第1ビアの組の配置と同等である。そのため、第2金属配線M12の場合と同様に、Y軸方向に対して、第1金属配線M11に接続される第1ビアの組と第3金属配線M13に接続される第1ビアの組とが交互に配置されている。

【0061】

次に、第4金属配線M24、第5金属配線M25および第6金属配線M26のパターンについて、図4を参照して説明する。

【0062】

図4に示すように、第4金属配線M24〜第6金属配線26のパターンは、同一であり、各パターンのX軸方向の長さ(この長さを幅と称する)がY軸方向に対して均一に、Y軸方向に延在している。この幅を図4にW3で示す。X軸方向に対して、第5金属配線M25および第6金属配線26の幅のそれぞれの中心がダミーゲート電極DG1、DG2のそれぞれの中心に一致するように、第5金属配線M25および第6金属配線26が配置されている。また、X軸方向に対して、第4金属配線M24の幅の中心が複数の第1ビアの組が配置された列の中心に一致するように、第4金属配線M24が配置されている。

【0063】

第4金属配線M24および第5金属配線M25の配線間距離をGap3で表すと、第4金属配線M24および第6金属配線M26の配線間距離もGap3となる。W3<W2なので、Gap3>Gap2の関係になっている。

【0064】

次に、図4および図5を参照して説明した配線間距離について、P−Tr111の断面図で説明する。

【0065】

図6Aは図4に示す線分AAの部位の断面図を示し、図6Bは図4に示す線分BBの部位の断面図を示す。これらの断面図では、膜の積層方向をZ軸方向としている。

【0066】

図6Aおよび図6Bに示すように、半導体基板100の表面近傍に、ソース電極に相当する拡散層S1、S2と、ドレイン電極に相当する拡散層D1が設けられている。なお、図6Aおよび図6Bの断面図では、Nウェル領域を図に示すことを省略している。このことは、他の実施例で参照する断面図についても同様である。

【0067】

半導体基板100の上にはゲート絶縁膜(不図示)を介してゲート電極G1、G2およびダミーゲート電極DG1、DG2が設けられ、これらのゲート電極を覆うように第1絶縁膜161がゲート絶縁膜上に設けられている。

【0068】

第1絶縁膜161の上には第1金属配線M11〜第3金属配線M13が設けられている。第1絶縁膜161には、第1絶縁膜161を貫通する第1ビアV1が設けられている。図6Aに示すように、第2金属配線M12が第1ビアV1を介して拡散層S1と接続されている。第3金属配線M13が第1ビアV1を介して拡散層S2と接続されている。図6Bに示すように、第1金属配線M11が第1ビアV1を介して拡散層D1と接続されている。

【0069】

第1絶縁膜161の上には、第1金属配線M11〜第3金属配線M13を覆うように第2絶縁膜162が設けられている。第2絶縁膜162の上には第4金属配線M24〜第6金属配線M26が設けられている。第2絶縁膜162には、第2絶縁膜162を貫通する第2ビアV2が設けられている。

【0070】

図6Aおよび図6Bに示すように、第5金属配線M25が第2ビアV2を介して第2金属配線M12と接続されている。第4金属配線M24が第2ビアV2を介して第1金属配線M11と接続されている。第6金属配線M26が第2ビアV2を介して第3金属配線M13と接続されている。第2絶縁膜162の上には、第4金属配線M24〜第6金属配線M26を覆うように第3絶縁膜163が設けられている。

【0071】

図6Aおよび図6Bを見比べると、Gap2>Gap1の関係になっていることが明らかである。図6Aでは、第2金属配線M12および第3金属配線M13のそれぞれに接続される第1ビアV1が図に示されているが、第1金属配線M11に第1ビアV1は接続されていない。その反対に、図6Bでは、第1金属配線M11に接続される第1ビアV1が図に示されているが、第2金属配線M12および第3金属配線M13に第1ビアV1は接続されていない。これは、図4および図5を参照して説明したように、第1金属配線M11に接続される第1ビアの組と、第2金属配線M12または第3金属配線M13に接続される第1ビアの組とがY軸方向に対して交互に配置されているからである。

【0072】

よって、第1金属配線M11と第2金属配線M12との間の寄生容量C1、第1金属配線M11と第3金属配線M13との間の寄生容量C2、第4金属配線M24と第5金属配線M25との間の寄生容量C3、第4金属配線M24と第6金属配線M26との間の寄生容量C4、第1金属配線M11と第5金属配線M25との間の寄生容量C5、第1金属配線M11と第6金属配線M26との間の寄生容量C6、第2金属配線M12と第4金属配線M24との間の寄生容量C7、及び第3金属配線M13と第4金属配線M24との間の寄生容量C8のそれぞれの値が、削減されていることが理解できる。それぞれの金属配線とその他のノード(例えばゲートや被制御端子)との寄生容量値も、それぞれ低減されることは言うまでもない。

【0073】

次に、本実施例の半導体装置の製造方法を説明する。ここでは、図4に示したP−Trの形成方法を、図4〜図6B、図7および図8を参照して説明する。

【0074】

図7および図8は図4に示したP−Trの形成過程の一例を示す平面図である。図7はゲート電極形成後の平面図であり、図8は第1ビア形成後の平面図である。

【0075】

図6Aに示した半導体基板100に対して、活性領域を分離するための素子分離領域と、Nウェル領域およびPウェル領域とを形成した後、半導体基板100の表面にゲート絶縁膜(不図示)を形成する。その後、導電性材料膜をゲート絶縁膜上に形成し、リソグラフィ工程により、図7に示すように、導電性材料膜でゲート電極G1、G2およびダミーゲート電極DG1、DG2をパターニングする(図7参照)。

【0076】

続いて、ゲート電極G1、G2およびダミーゲート電極DG1、DG2をマスクに、N型導電性不純物を半導体基板100に打ち込むイオン注入工程を行い、その後、熱処理を行う。これにより、図6Aおよび図6Bに示した拡散層D1および拡散層S1、S2が半導体基板100の表面近傍に形成される。なお、この熱処理は、イオン注入工程の直後でなくても、イオン注入工程の後であれば、半導体装置の製造過程において、いずれのタイミングで行ってもよい。

【0077】

上記のイオン注入工程の後、図6Aおよび図6Bに示したように、ゲート絶縁膜(不図示)の上に、ゲート電極G1、G2およびダミーゲート電極DG1、DG2を覆う第1絶縁膜161をCVD(Chemical Vapor Deposition)法で形成する。そして、リソグラフィ工程により第1絶縁膜161に開口を形成し、形成した開口に導電性材料を埋め込むことで、第1ビアV1を第1絶縁膜161に形成する(図6A、図6Bおよび図8参照)。

【0078】

第1絶縁膜161の上に第1金属配線層を形成し、リソグラフィ工程により第1金属配線層で第1金属配線M11〜第3金属配線M13を形成する(図5参照)。続いて、第1絶縁膜161の上に、第1金属配線M11〜第3金属配線M13を覆う第2絶縁膜162をCVD法で形成する。そして、リソグラフィ工程により第2絶縁膜162に開口を形成し、形成した開口に導電性材料を埋め込むことで、第2ビアV2を第2絶縁膜162に形成する(図6A、図6Bおよび図4参照)。

【0079】

その後、第2絶縁膜162の上に第2金属配線層を形成し、リソグラフィ工程により第2金属配線層で第4金属配線M24〜第6金属配線M26を形成する(図4参照)。そして、第2絶縁膜162の上に、第4金属配線M24〜第6金属配線M26を覆う第3絶縁膜163をCVD法で形成する。

【0080】

本実施例によれば、第1金属配線層の隣り合う配線間で、これらの配線に接続される第1ビアの組が交互に配置されているので、配線間容量が削減される。また、ソース電極に相当する拡散層S1、S2に接続される第1ビアを配置していない部位では、第2金属配線および第3金属配線の幅を短くして、余分な部位を削除している。配線間隔が広くなる部位では、配線間の寄生容量が削減される。

【0081】

本実施例の構成でダミートランジスタを4本設けた場合、カップリング容量は6.91fFから5.97fF(86.4パーセント)に低減した。

【実施例2】

【0082】

本実施例は、実施例1と同様に、第1金属配線層の配線間容量を削減するものであるが、さらに配線間容量を削減可能にした構成である。

【0083】

本実施例の半導体装置の構成を説明する。本実施例においても、実施例1と同様に、リングオシレータに用いられるP−Trの構成について説明する。また、本実施例では、実施例1と同様な構成についての詳細な説明を省略し、実施例1と異なる点を中心に説明する。

【0084】

図9は図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。図10は図9に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。図9および図10に示す平面図において、図の左右方向をX軸方向とし、図の上下方向をY軸方向とする。

【0085】

図9に示すように、第1金属配線M11に接続される第2ビアV2の数が実施例1の場合よりも少ない。また、図10に示すように、第1金属配線M11のパターンと第1金属配線M11に接続される第1ビアV1の配置が実施例1と異なっている。以下に、実施例1との違いを、図10を参照して詳しく説明する。

【0086】

第1金属配線M11に接続される第1ビアの組は、実施例1の場合と同様に等間隔で配置されているが、Y軸方向の位置が第2金属配線M12および第3金属配線M13のそれぞれに接続される第1ビアの組と対向して配置されている。

【0087】

また、第1金属配線M11のパターンにおいて、第2ビアV2が接続される部位の幅が図5に示した幅W2よりも小さいW5である。幅W5は、第2ビアV2のパターンサイズ以上であればよい。幅W5は、第2ビアV2のパターンサイズ以上であり、第2ビアV2の配置およびパターンサイズのばらつきを含む値であってもよい。このばらつきの値は、リソグラフィ工程における製造ばらつきによって決まる。本実施例では、幅W5は図4に示した幅W3に等しい。さらに、第1金属配線M11のパターンにおいて、第1ビアV1が接続される部位の幅がW5よりも小さいW4である。

【0088】

上述した構成の本実施例と実施例1との違いを、第1金属配線M11および第3金属配線M13の配線間距離に注目して説明する。

【0089】

図10において、第1金属配線M11における幅W5の部位と第3金属配線M13との距離をGap4とし、第1金属配線M11における幅W4の部位と第3金属配線M13との距離をGap5とする。図5と図10を見比べると、Gap4>Gap2、Gap5>Gap1となっている。そのため、第1金属配線M11および第3金属配線M13の配線間容量が、実施例1の構成に比べて、さらに低減する。

【0090】

なお、第1金属配線M11および第3金属配線M13の配線間距離に注目して説明したが、上述した構成は、第1金属配線M11および第2金属配線M12の配線間距離についても同様である。また、本実施例では、W3=W5の場合で説明したが、W3≠W5であってもよく、W3<W2であれば、配線間容量低減の効果が得られる。

【0091】

次に、図10を参照して説明した配線間距離について、P−Tr111の断面図で説明する。

【0092】

図11Aは図9に示す線分AAの部位の断面図を示し、図11Bは図9に示す線分BBの部位の断面図を示す。これらの断面図では、膜の積層方向をZ軸方向としている。

【0093】

図11Aと図6Aを見比べると、第1金属配線M11に接続される第2ビアV2が図6Aには現われているが、図11Aには現われていない。一方、第1金属配線M11に接続される第1ビアV1が図6Aには現われていないが、図11Aには現われている。これらの断面図に示す部位において、本実施例では、第1金属配線M11は、第2ビアV2の代わりに、第2ビアV2よりもパターンサイズの小さい第1ビアV1と接続されている。そのため、第1金属配線M11の幅をW2より短いW4にすることが可能となる。その結果、第1金属配線M11および第3金属配線M13の配線間距離Gap5が、実施例1の場合の配線間距離Gap1よりも長くなっている。

【0094】

図11Bと図6Bを見比べると、どちらの場合も、第1金属配線M11に接続される第1ビアV2が現われているが、これらの断面図の部位において、本実施例では、第1金属配線M11の幅W5は、第2ビアV2のパターンサイズ以上であるが、W2よりも小さい。そのため、第1金属配線M11および第3金属配線M13の配線間距離Gap4が、実施例1の場合の配線間距離Gap2よりも長くなっている。

【0095】

本実施例によれば、実施例1の構成に比べて、第1金属配線において、第1ビアおよび第2ビアのそれぞれが接続される部位の幅を短くしているので、ドレイン電極に接続される第1金属配線とソース電極に接続される第2金属配線および第3金属配線のそれぞれとの配線間距離が長くなっている場所が増える。そのため、配線間の寄生容量の低減効果がさらに向上する。

【0096】

本実施例の構成でダミートランジスタを4本設けた場合、カップリング容量は6.91fFから5.91fF(85.5パーセント)に低減した。

【実施例3】

【0097】

本実施例は、実施例1の構成に対し、第1金属配線に接続される第1ビアの数を減らし、第1ビアを配置しない部位を削除して配線間容量の削減するものである。

【0098】

本実施例の半導体装置の構成を説明する。本実施例においても、実施例1および実施例2と同様に、リングオシレータに用いられるP−Trの構成について説明する。また、本実施例では、実施例1または実施例2と同様な構成についての詳細な説明を省略し、これらの実施例と異なる点を中心に説明する。

【0099】

図12は図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。図13は図12に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。図12および図13に示す平面図において、図の左右方向をX軸方向とし、図の上下方向をY軸方向とする。

【0100】

図12に示すように、第1金属配線M11に接続される第2ビアV2の数と配置は実施例2の場合と同様であるが、第1ビアV1が第2ビアV2の位置に重ねて配置されている。また、実施例1と同様に、第1金属配線M11に接続される第1ビアの組が、第2金属配線M12および第3金属配線M13のそれぞれに接続される第1ビアの組と、Y軸方向に対して交互に配置されている。さらに、第1金属配線M11のパターンが実施例1および実施例2のいずれとも異なっている。以下に、実施例2との違いを、図13を参照して詳しく説明する。

【0101】

本実施例の第1金属配線M11のパターンは、図13に示すように、図5に示したパターンが第1ビアV1の組毎に、第1ビアV1の組を囲む領域で切り離され、複数に分けられている。以下では、第1ビアV1の組を囲む、1つのパターンを第1サブ金属配線と称する。複数の第1サブ金属配線がY軸方向に等間隔で配置されており、その間隔を図13にYL2と示している。本実施例では、第1金属配線M11の各第1サブ金属配線の幅はW5である。各第1サブ金属配線のパターンのX軸方向の長さは、第1ビアV1のパターンサイズと第2ビアV2のパターンサイズの最大値以上である。各第1サブ金属配線のパターンのY軸方向の長さは、第1ビアの組における2つの第1ビアV1のY軸方向の長さと第2ビアV2のパターンサイズの最大値以上である。

【0102】

なお、各第1サブ金属配線のパターンのX軸方向およびY軸方向のそれぞれの長さについても、第1ビアの組および第2ビアV2の配置とそれぞれのパターンサイズのばらつきを見込んだ長さを含むようにしてもよい。

【0103】

続いて、図13において、第1金属配線M11および第2金属配線M12の配線間距離に注目してみる。

【0104】

図13に示すように、第1金属配線M11の第1サブ金属配線と第2金属配線M12との配線間距離は、大部分がGap4である。第1金属配線M11の第1サブ金属配線と第2金属配線M12との配線間距離は、最も短いところで、Gap4より短いGap6である。しかし、Gap6は、第1金属配線M11の第1サブ金属配線の角と第2金属配線M12のパターンの角の距離であり、配線間容量に大きな影響はない。

【0105】

一方、第1サブ金属配線が配置されていない部位では、第1金属配線層において、第2金属配線M12と第3金属配線M13の間に配線が配置されていないので、第2金属配線M12と第3金属配線M13の間に配線間距離Gap7が確保される。なお、第1金属配線M11および第2金属配線M12の配線間距離に注目して説明したが、上述した構成は、第1金属配線M11および第3金属配線M13の配線間距離についても同様である。

【0106】

次に、図13を参照して説明した配線間距離について、P−Tr111の断面図で説明する。

【0107】

図14Aは図12に示す線分AAの部位の断面図を示し、図14Bは図12に示す線分BBの部位の断面図を示す。これらの断面図では、膜の積層方向をZ軸方向としている。

【0108】

図14Aに示す部位では、第1金属配線M11が配置されていないので、第2金属配線M12または第3金属配線M13と第1金属配線M11との配線間容量は生じない。ソース電極およびドレイン電極間の配線間容量としては、第2金属配線M12および第4金属配線M24の配線間容量と、第3金属配線M13および第4金属配線M24の配線間容量となる。図14Bに示す部位では、図11Bに示した部位と同様に、第1金属配線M11と第1金属配線M12および第3金属配線M13のそれぞれとの配線間距離Gap4が確保されている。

【0109】

本実施例では、第1金属配線に接続される第1ビアの数を減らし、第1金属配線のうち、第1ビアを配置しない部位を削除している。そのため、実施例1や実施例2の場合に比べて、配線間の寄生容量の低減効果が向上する。

【0110】

本実施例の構成でダミートランジスタを4本設けた場合、カップリング容量は6.91fFから5.20fF(75.3パーセント)に低減した。

【実施例4】

【0111】

本実施例は、実施例3の構成に対し、第1金属配線に接続される第1ビアの数をさらに減らし、第2金属配線および第3金属配線に接続される第1ビアの数を減らして配線間容量を削減するものである。

【0112】

本実施例の半導体装置の構成を説明する。本実施例においても、実施例1から実施例3と同様に、リングオシレータに用いられるP−Trの構成について説明する。また、本実施例では、実施例3と同様な構成についての詳細な説明を省略し、実施例3と異なる点を中心に説明する。

【0113】

図15は図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。図16は図15に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。図15および図16に示す平面図において、図の左右方向をX軸方向とし、図の上下方向をY軸方向とする。

【0114】

図16に示すように、本実施例では、実施例3と比べて、第1金属配線M11に相当する複数の第1サブ金属配線の数が少なく、その配置間隔YL3がYL2よりも長い。図15に示すように、実施例3と比べて、第2金属配線M12および第3金属配線M13のそれぞれに接続する第1ビアの組の数が少ない。第2金属配線M12および第3金属配線M13のそれぞれに接続する第1ビアの組の配置間隔は、図16に示すように、第1サブ金属配線の配置間隔と同じYL3である。

【0115】

続いて、図16において、第1金属配線M11および第2金属配線M12の配線間距離に注目してみる。

【0116】

図16に示すように、第1金属配線M11の第1サブ金属配線と第2金属配線M12との配線間距離はGap4である。本実施例では、実施例3の図13に示したGap6のような箇所はない。第1サブ金属配線が配置されていない部位では、第1金属配線層において、第2金属配線M12と第3金属配線M13の間に配線が配置されていないので、実施例3と同様に、第2金属配線M12と第3金属配線M13の間に配線間距離Gap7が確保される。また、本実施例では、図16に示すように、第2金属配線M12と第3金属配線M13の間に配線間距離がGap7よりも大きいGap8となる部位が存在している。

【0117】

なお、第1金属配線M11および第2金属配線M12の配線間距離に注目して説明したが、上述した構成は、第1金属配線M11および第3金属配線M13の配線間距離についても同様である。

【0118】

次に、図16を参照して説明した配線間距離について、P−Tr111の断面図で説明する。

【0119】

図17Aは図15に示す線分AAの部位の断面図を示し、図17Bは図15に示す線分BBの部位の断面図を示す。これらの断面図では、膜の積層方向をZ軸方向としている。

【0120】

図17Aに示す部位では、第1金属配線M11が配置されていないので、第2金属配線M12または第3金属配線M13と第1金属配線M11との配線間容量は生じない。ソース電極およびドレイン電極間の配線間容量としては、第2金属配線M12および第4金属配線M24の配線間容量と、第3金属配線M13および第4金属配線M24の配線間容量となる。図17Bに示す部位では、図14Bに示した部位と同様に、第1金属配線M11と第1金属配線M12および第3金属配線M13のそれぞれとの配線間距離Gap4が確保されている。

【0121】

本実施例では、実施例3の構成に比べて、第1金属配線に接続される第1ビアの数をさらに減らし、第2金属配線および第3金属配線に接続される第1ビアの数を減らしている。そして、第1金属配線から第3金属配線のそれぞれにおいて、第1ビアの配置しない部位を削除している。そのため、実施例3の構成に比べて、配線間の寄生容量の低減効果が向上する。

【0122】

本実施例の構成でダミートランジスタを4本設けた場合、カップリング容量は6.91fFから4.49fF(65.0パーセント)に低減した。

【0123】

上述した実施例1から実施例4では、コンタクト数によるTr能力の変化と、寄生容量の削減との相殺効果を有する。要求される回路特性に対応して、実施例1から実施例4から最適なレイアウトを選択すればよい。

【0124】

将来、半導体装置はさらなる微細化と高速化が進み、ますます寄生容量の削減が重要になる。寄生容量値が回路特性に与える影響を考慮しなければならないセンシティブな回路、例えば電圧制御発振回路のような回路においては、本発明をベースとした改良対策が必須となるので、本発明は非常に重要な技術となる。

【0125】

また、上述の実施例1から実施例4では、金属配線層が2層の場合で説明したが、将来のプロセスでは配線層が3層以上の多段化も考えられる。この場合においても高速動作回路の接点容量削減には、本発明が有効である。

【0126】

さらに、本発明を、電圧制御発振回路以外の機能素子等の回路に適用してもよい。

【0127】

本願の技術思想は、複数の電界効果トランジスタで構成する回路を有する半導体装置に適用できる。更に、図面で開示した各回路ブロック内の回路形式は、実施例が開示する回路形式限られない。

【0128】

本発明の半導体装置の技術思想は、様々な半導体装置に適用することができる。例えば、CPU(Central Processing Unit)、MCU(Micro Control Unit)、DSP(Digital Signal Processor)、ASIC(Application Specific Integrated Circuit)、ASSP(Application Specific Standard Product)、メモリ(Memory)等の半導体装置全般に、本発明を適用することができる。このような本発明が適用された半導体装置の製品形態としては、例えば、SOC(システムオンチップ)、MCP(マルチチップパッケージ)やPOP(パッケージオンパッケージ)などが挙げられる。これらの任意の製品形態、パッケージ形態を有する半導体装置に対して本発明を適用することができる。

【0129】

また、トランジスタは、電界効果トランジスタ(Field Effect Transistor; FET)であれば良く、MOS(Metal Oxide Semiconductor)以外にもMIS(Metal-Insulator Semiconductor)、TFT(Thin Film Transistor)等の様々なFETに適用できる。トランジスタ等の様々なFETに適用できる。更に、装置内に一部のバイポーラ型トランジスタを有しても良い。

【0130】

更に、NMOSトランジスタ(N型チャネルMOSトランジスタ)は、第1導電型のトランジスタ、PMOSトランジスタ(P型チャネルMOSトランジスタ)は、第2導電型のトランジスタの代表例である。

【0131】

また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせ乃至選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0132】

10 半導体装置

26 クロック生成部

111〜113 P型チャネルMOSFET(P−Tr)

121〜123 N型チャネルMOSFET(N−Tr)

D1、S1、S2 拡散層

G1、G2 ゲート電極

DG1、DG2 ダミーゲート電極

V1 第1ビア

V2 第2ビア

M11 第1金属配線

M12 第2金属配線

M13 第3金属配線

M24 第4金属配線

M25 第5金属配線

M26 第6金属配線

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

近年、半導体装置は、ますます微細化が進み、配線層間および配線間の寄生容量が無視できない。例えば、電圧制御発振回路のような高速で動作させる必要のあるリングオシレータにおいては、出力部の接点容量が大きいと高速動作ができない。

【0003】

この問題に対して、特許文献1に、トランジスタの接点容量を削減する方法が開示されている。この文献に開示された発明では、トランジスタの出力部に隣接するソース領域にダミートランジスタを配置することで、出力部およびソース領域間のカップリング容量を削減し、出力部の接点容量を削減している。

【0004】

特許文献2には、ソースおよびドレインのコンタクトの数を減らし、交互に配置したトランジスタのパターンレイアウトが開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−278952号公報

【特許文献2】特開2010−10515号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に開示された方法では、寄生容量を削減する効果が得られるが、ダミートランジスタのゲート本数を増やす度に寄生容量の削減効果が低減し、削減量が飽和してしまう傾向がある。また、ダミートランジスタが設けられる面積が大きくなってしまう問題もある。ダミートランジスタを配置して寄生容量の削減を図るのには限界があり、面積を拡大しても得られる効果は大きくない。また、特許文献2に開示された方法も、十分な効果が得られない。

【課題を解決するための手段】

【0007】

本発明の第1の側面の半導体装置は、

それぞれが、ドレイン拡散層と、該ドレイン拡散層を挟んで両側に配設される一対のソース拡散層と、前記ドレイン拡散層と前記一対のソース拡散層との間にそれぞれ配設される一対のゲート電極とを有し、列方向に配列される複数のトランジスタと、

前記一対のソース拡散層の内の一方を含む互いに隣接する2つのソース拡散層の間に配列され、該2つのソース拡散層と同電位に維持されている第1のダミーゲート電極と、

前記一対のソース拡散層の内の他方を含む互いに隣接する2つのソース拡散層の間に配列され、該2つのソース拡散層と同電位に維持されている第2のダミーゲート電極と、

複数の第1のビアを介して前記ドレイン拡散層に接続する第1の金属配線と、

前記一対のソース拡散層の一方であって前記互いに隣接する2つのソース拡散層の両方にそれぞれ対応する複数の第1のビアを介して接続する第2の金属配線と、

前記一対のソース拡散層の他方であって前記互いに隣接する2つのソース拡散層の両方にそれぞれ対応する複数の第1のビアを介して接続する第3の金属配線と、

前記第1乃至第3の金属配線にそれぞれ対応する複数の第2のビアを介して接続する第4乃至第6の金属配線と、を備え、

前記第2及び第3の金属配線の前記列方向におけるそれぞれの幅は、対応する前記2つのソース拡散層にそれぞれ接続する複数の第1のビアの両方を含む第1の幅と、前記第1のビアを含まず前記第1の幅よりも短い第2の幅と、を有し、

前記第1及び第2の金属配線の間、並びに前記第1及び第3の金属配線の間のそれぞれのギャップは、前記第1の幅に対応する第1のギャップと、前記第2の幅に対応する前記第1のギャップよりも大きな第2のギャップと、を有する。

【0008】

本発明では、第2の金属配線および第3の金属配線のそれぞれのパターンは、第1の幅よりも短い第2の幅の部位を有しているので、ソース電極に接続される第2の金属配線および第3の金属配線のそれぞれとドレイン電極に接続される第1の金属配線の配線間距離として、第1のギャップよりも長い第2のギャップSP2が存在する。そのため、少なくともソース電極およびドレイン電極間の配線間容量が低減する。

【0009】

本発明の第2の側面の半導体装置は、

トランジスタのソース電極またはドレイン電極を構成し、それぞれ第1の方向に延在する第1乃至第5の拡散部を含む拡散層と、

前記トランジスタのゲート電極を構成し、前記第1の方向に延在する第1及び第2のゲート配線、並びに前記第1の方向に延在する第1及び第2のダミーゲート配線を含むゲート層と、

前記第1の方向に延在する第1乃至第3の金属配線を含む第1の金属層と、

前記第1の方向に延在する第4から第6の金属配線を含む第2の金属層と、

前記第1の方向に展開して配置される複数の第1のビアを含み、前記拡散層と前記第1の金属層を接続する第1のビア層と、

前記第1の方向に展開して配置される複数の第2のビアを含み、前記第1及び第2の金属層を接続する第2のビア層と、を備え、

第1のトランジスタは、前記第1のゲート配線、前記第1及び第2の拡散部で構成され、

第2のトランジスタは、前記第2のゲート配線、前記第1及び第3の拡散部で構成され、前記第1のトランジスタに隣接して前記第1の方向と直交する第2の方向へ配置され、

第3のトランジスタは、前記1のダミーゲート配線、並びに、前記第2及び第4の拡散部で構成され、前記第1のトランジスタに隣接して、前記第2の方向とは反対の第3の方向に配置され、更に前記1のダミーゲート配線、並びに、前記第3及び第4の拡散部は、同電位であり、

第4のトランジスタは、前記2のダミーゲート配線、並びに、前記第3及び第5の拡散部で構成され、前記第2のトランジスタに隣接して前記第2の方向に配置され、更に前記2のダミーゲート配線、並びに、前記第3及び第5の拡散部は、同電位であり、

それぞれが、少なくとも一つの前記第1のビアをセットとする複数の第1セットが、第1のピッチで前記第1の拡散部に配置され、

それぞれが、少なくとも一つの前記第1のビアをセットとする複数の第2セットが、第2のピッチで前記第2乃至第5の拡散部にそれぞれ配置され、

前記第1の金属配線は、前記第1の拡散部に関連する複数の第1のビアを覆うように前記第1の拡散部の領域に配置され、

前記第2の金属配線は、前記第2及び第4の拡散部にそれぞれ関連する複数の第1のビアを一体として覆うように前記第3のトランジスタの領域に配置され、

前記第3の金属配線は、前記第3及び第5の拡散部にそれぞれ関連する複数の第1のビアを一体として覆うように前記第4のトランジスタの領域に配置され、

それぞれが、少なくとも一つの前記第2のビアをセットとする複数の第3セットが、第3のピッチで前記第1の金属配線に配置され、

それぞれが、少なくとも一つの前記第2のビアをセットとする複数の第4セットが、第4のピッチで前記第2及び第3の金属配線にそれぞれ配置され、

前記第4の金属配線は、前記第1の金属配線に関連する複数の第2のビアを覆うように前記第1の拡散部の領域に配置され、

前記第5の金属配線は、前記第2の金属配線に関連する複数の第2のビアを覆うように前記第3のトランジスタの領域に配置され、

前記第6の金属配線は、前記第3の金属配線に関連する複数の第2のビアを覆うように前記第4のトランジスタの領域に配置され、

前記第2の金属配線の前記第3の方向における幅は、前記第2の拡散部に関連する前記第1のビア及び前記第4の拡散部に関連する前記第1のビアの両方を含む第1の幅と、前記第1の幅よりも短い第2の幅と、を有し、

前記第3の金属配線の前記第2の方向における幅は、前記第3の拡散部に関連する前記第1のビア及び前記第5の拡散部に関連する前記第1のビアの両方を含む前記第1の幅と、前記第2の幅と、を有し、

前記第4乃至第6の金属配線の前記第2の方向におけるそれぞれの幅は、前記第1の幅よりも短い第3の幅を有し、

前記第1及び第2の金属配線の間、並びに前記第1及び第3の金属配線の間のそれぞれのギャップは、前記第1の幅に対応する第1のギャップと、前記第2の幅に対応する前記第1のギャップよりも大きな第2のギャップと、を有する。

【発明の効果】

【0010】

本発明によれば、トランジスタおよびダミートランジスタの面積を拡大せずに寄生容量を削減できる。ゲート狭ピッチプロセスにおいても、チップ面積を最小限に抑えながら、寄生容量を削減できる。

【図面の簡単な説明】

【0011】

【図1】本実施形態の半導体装置の一構成例を示す平面図である。

【図2】実施例1の半導体装置の一構成例を示すブロックダイアグラムである。

【図3A】実施例1の半導体装置に設けられたリングオシレータの一構成例を示す回路パターン図である。

【図3B】実施例1の回路図である。

【図4】実施例1において、図3Aに示したリングオシレータに含まれるP−Trのパターンの一例を示す平面図である。

【図5】図4に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。

【図6A】図4に示す線分AAの部位の断面図である。

【図6B】図4に示す線分BBの部位の断面図である。

【図7】図4に示したP−Trの形成過程の一例を示す平面図である。

【図8】図4に示したP−Trの形成過程の一例を示す平面図である。

【図9】実施例2において、図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。

【図10】図9に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。

【図11A】図9に示す線分AAの部位の断面図である。

【図11B】図9に示す線分BBの部位の断面図である。

【図12】実施例3において、図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。

【図13】図12に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。

【図14A】図12に示す線分AAの部位の断面図である。

【図14B】図12に示す線分BBの部位の断面図である。

【図15】実施例4において、図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。

【図16】図15に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。

【図17A】図15に示す線分AAの部位の断面図である。

【図17B】図15に示す線分BBの部位の断面図である。

【発明を実施するための形態】

【0012】

本発明の課題を解決する技術思想(コンセプト)の代表的な一例は、以下に示される。ただし、本願の請求内容は、この技術思想に限られず、本願の請求項に記載の内容であることは言うまでもない。

【0013】

本発明の半導体装置は、トランジスタのドレイン領域にビアを介して接続される第1金属配線とダミーゲートが接続されるソース領域にビアを介して接続される第2金属配線とのギャップのうち、最も小さなギャップが短くなるように、第1金属配線および第2金属配線のパターンレイアウト、ならびにそれぞれの金属配線に対応するビアの配置が設定されていることを特徴とする。

【0014】

図1は本実施形態の半導体装置の一構成例を示す平面図である。

【0015】

図1に示すように、本実施形態の半導体装置は、X軸方向に配置された複数のMOS(Metal Oxide Semiconductor)FET(Field Effect Transistor)(以下では、単にトランジスタと称する)Tr1、Tr2を有する。トランジスタTr1、Tr2は同様な構成であるため、トランジスタTr1の構成について説明する。また、X軸方向は、トランジスタTr1、Tr2が配列される方向なのでX軸方向を「列方向」と称し、列方向に垂直方向となるY軸方向を「行方向」と称する。

【0016】

トランジスタTr1は、ドレイン拡散層D1と、ドレイン拡散層D1を挟んで両側に配設される一対のソース拡散層S1、S2と、ドレイン拡散層D1と一対のソース拡散層S1、S2との間にそれぞれ配設される一対のゲート電極G1、G2とを有する。

【0017】

トランジスタTr1のソース拡散層S1は、ダミーゲート電極DG1を介してトランジスタTr2が有するソース拡散層S1と隣接する。これら2つのソース拡散層S1とダミーゲート電極DG1は、同電位が供給される。

【0018】

トランジスタTr1のソース拡散層S2は、ダミーゲート電極DG2を介してトランジスタTr3(不図示)が有するソース拡散層S2と隣接する。これら2つのソース拡散層S2とダミーゲート電極DG2は、同電位が供給される。

【0019】

ゲート電極G1、G2よりも上層に、第1金属配線M11、第2金属配線M12および第3金属配線M13を含む第1金属配線層が設けられている。第1金属配線M11は複数の第1ビアV1を介してドレイン拡散層D1に接続されている。第2金属配線M12は、ダミーゲート電極DG1を介して互いに隣接する2つのソース拡散層の両方S1にそれぞれ対応する複数の第1ビアV1を介して接続されている。第3金属配線M13は、ダミーゲート電極DG2を介して互いに隣接する2つのソース拡散層の両方S2にそれぞれ対応する複数の第1ビアV1を介して接続されている。

【0020】

また、第1金属配線層よりも上層に、第4金属配線M24、第5金属配線M25および第6金属配線26を含む第2金属配線層が設けられている。第4金属配線M24〜第6金属配線M26のそれぞれは第2ビアV2を介して第1金属配線M11〜第3金属配線M13のそれぞれと接続されている。

【0021】

第2金属配線M12および第3金属配線M13のX軸方向におけるそれぞれの幅は、対応する2つのソース拡散層S1、S2にそれぞれ接続する複数の第1ビアV1のサイズの両方を含む第1の幅L1と、第1ビアV1のサイズを含まず、第1の幅L1よりも短い第2の幅L2と、を有する。

【0022】

第1金属配線M11および第2金属配線M12の間、ならびに第1金属配線M11および第3金属配線M13の間のそれぞれのギャップは、第1の幅L1に対応する第1のギャップSP1と、第2の幅L2に対応する、第1のギャップSP1よりも大きな第2のギャップSP2と、を有する。

【0023】

第4金属配線M24〜第6金属配線M26のX軸方向におけるそれぞれの幅は、第1の幅L1よりも短い第3の幅L3を有する。そして、第4金属配線M24および第5金属配線M25の間、ならびに第4金属配線M24および第6金属配線M26の間のそれぞれのギャップは、第2のギャップSP2よりも更に大きな第3のギャップSP3を有する構成である。

【0024】

本実施形態では、第2金属配線M12および第3金属配線M13のそれぞれのパターンは、幅L1よりも短い幅L2の部位を有するので、ソース電極に接続される第2金属配線M12および第3金属配線M13のそれぞれとドレイン電極に接続される第1金属配線M11の配線間距離として、第1のギャップSP1よりも長い第2のギャップSP2が存在する。そのため、2つのソース電極および1つのドレイン電極間の配線間容量(寄生容量)が低減する。

【0025】

さらに、ソース電極に接続される第5金属配線M25および第6金属配線M26のそれぞれとドレイン電極に接続される第4金属配線M24の配線間距離に相当する第3のギャップSP3が第2のギャップSP2よりも大きいので、2つのソース電極および1つのドレイン電極間の配線間容量(寄生容量)がそれぞれ低減する。

【0026】

なお、図1では、第1金属配線M11に接続される第1ビアV1が、第2金属配線M12および第3金属配線M13のそれぞれに接続される第1ビアV1と、Y軸方向の位置が同一で、対向する位置に配置されている場合を示しているが、Y軸方向の位置が異なっていてもよい。

【0027】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について詳細に説明する。

【実施例1】

【0028】

本実施例の半導体装置の一構成例を説明する。本実施例では、半導体装置がメモリデバイスの場合で説明する。

【0029】

図2は本実施例の半導体装置の一構成例を示すブロックダイアグラムである。

【0030】

図2に示すように、本実施例の半導体装置10は、複数のメモリ素子を含むメモリセルアレイ21と、アドレス信号にしたがって制御対象のメモリ素子を特定するロウデコーダ22およびカラムデコーダ23と、メモリ素子に蓄積された情報に対応する信号を増幅するセンスアンプ24と、データ入出力部25と、各部にクロック信号を提供するクロック生成部26と、信号およびデータを入出力するための複数の外部端子とを有する。クロック生成部26はリングオシレータを有する。リングオシレータの回路の一例が、後述する図3Bに開示されている。

【0031】

複数の外部端子として、アドレス信号を入力するための複数の入力端子を含むアドレス入力端子群31と、コマンドを入力するための複数の入力端子を含むコマンド入力端子群32と、データを入出力するための複数の端子を含むデータ入出力端子群33とが設けられている。

【0032】

図3Aは本実施例の半導体装置に設けられたリングオシレータの一構成例を示す回路パターン図である。図3Bはその回路図である。

【0033】

図3Aに示すリングオシレータは、3つのP型チャネルMOSFET(以下では、P−Trと表記する)111〜113が設けられたNウェル領域101と、3つのN型チャネルMOSFET(以下では、N−Trと表記する)121〜123が設けられたPウェル領域102とを有する。Nウェル領域101には、半導体基板の主表面からN型導電性不純物が拡散されている。Pウェル領域102には、半導体基板の主表面からP型導電性不純物が拡散されている。

【0034】

P−Tr111およびN−Tr121で1つのインバータ回路が構成される。P−Tr112およびN−Tr122で1つのインバータ回路が構成される。P−Tr113およびN−Tr123で1つのインバータ回路が構成される。

【0035】

P−Tr111およびN−Tr121のそれぞれのゲート電極が配線131で接続され、P−Tr111およびN−Tr121のそれぞれのドレイン電極が配線141で接続されている。P−Tr112およびN−Tr122のそれぞれのゲート電極が配線132で接続され、P−Tr112およびN−Tr122のそれぞれのドレイン電極が配線142で接続されている。P−Tr113およびN−Tr123のそれぞれのゲート電極が配線133で接続され、P−Tr113およびN−Tr123のそれぞれのドレイン電極が配線143で接続されている。

【0036】

図3Aに示すように、配線131がビアを介して配線142と接続され、配線132がビアを介して配線143と接続されている。配線133は、ビアおよび配線151を介して配線141と接続されている。なお、配線131〜133はゲート電極と同一層に形成され、配線141〜143は第2金属配線層に形成され、配線151は第1金属配線層に形成されている。

【0037】

図3Aに示すリングオシレータのパターンレイアウト及びその一部である図1を、図3Bの回路図で示す。

【0038】

各トランジスタにはその名前の一部に「Tr」の符号が付されている。P型トランジスタにはその名前の一部に「P」の符号が付されている。N型トランジスタにはその名前の一部に「N」の符号が付されている。ダミーゲートとしての機能を有するトランジスタ(ダミートランジスタ)にはその名前の一部に「DTr」の符号が付されている。各トランジスタのゲート電極にはその名前の一部に「G」の符号が付されている。各トランジスタのソース電極(ソース拡散層)にはその名前の一部に「S」の符号が付されている。各トランジスタのドレイン電極(ドレイン拡散層)にはその名前の一部に「D」の符号が付されている。なお、ゲート電極は制御端子であり、ソース電極は被制御端子の一方、ドレイン電極は被制御端子の他方である。

【0039】

各トランジスタのバックゲート(ウェル)は、矢印で示される。リングオシレータの各ノード(配線)は3桁の数字で示される。高電位電源はVDD、低電位電源はVSSで示される。リングオシレータは、それぞれP型トランジスタ及びN型トランジスタをペアとする複数の相補トランジスタで構成される。一つの相補トランジスタにおいて、P型トランジスタは2つのトランジスタ、N型トランジスタは2つのトランジスタで構成される。2つのトランジスタは、ドレイン拡散層が共通であるが、ソース拡散層は異なる。詳細には、2つのトランジスタは、異なるゲート配線層を介して異なるソース拡散層を有する。異なるソース拡散層は、それぞれ対応する2つのダミートランジスタの拡散層として共用される。2つのダミートランジスタのそれぞれは、前段のトランジスタ(2つのトランジスタの一方)のソース拡散層と後段のトランジスタ(2つのトランジスタの他方)のソース拡散層を2つの被制御端子とし、制御端子(ゲート電極)を有するトランジスタである。制御端子及び2つの被制御端子は、同一の電位が供給される。よって、ダミートランジスタと呼称されている。電気的な視点において、異なる拡散層は対応する共通な電源に接続される。

【0040】

次に、図3Aに示したリングオシレータの動作を簡単に説明する。

【0041】

配線143に現われている第1の電位が配線143から外部に出力される。この配線143に現われる電位を外部に出力するための出力端子の符号をOUT1で表す。配線143の第1の電位は、出力端子OUT1から出力されるだけでなく、配線132を介してP−Tr112およびN−Tr122のそれぞれのゲート電極に印加される。第1の電位がP−Tr112およびN−Tr122のそれぞれのゲート電極に印加されることで、第1の電位の反転電位である第2の電位が配線142に出力される。配線142に現われた第2の電位が配線131を介してP−Tr111およびN−Tr121のそれぞれのゲート電極に印加されると、第2の電位が反転して第1の電位が配線141に出力される。

【0042】

続いて、配線141に現われた第1の電位が配線151および配線133を介してP−Tr113およびN−Tr123のそれぞれのゲート電極に印加されると、第1の電位が反転して第2の電位が配線143に出力される。配線143に出力された第2の電位は、出力端子OUT1を介して外部に出力されるとともに配線132に印加される。このようにして、第1の電位および第2の電位が所定の時間間隔で交互に、出力端子OUT1を介して外部に出力される。

【0043】

次に、図3Aに示したリングオシレータに含まれるP−Tr111〜113およびN−Tr121〜123のパターンレイアウトについて詳しく説明する。

【0044】

なお、P−Tr111〜113とN−Tr121〜123とはドレイン電極およびソース電極における導電性不純物のタイプが異なるだけなので、P−Tr111〜113の構成について説明する。また、P−Tr111〜113のそれぞれの構成は同様なので、P−Tr111〜113のいずれか一つのトランジスタを中心にしたパターンレイアウトについて説明する。N−Tr121〜123についても、本発明を適用できることは言うまでもない。

【0045】

図4は図3Aに示したリングオシレータに含まれるP−Trのパターンの一例を示す平面図である。図4では、Nウェル領域101を図に示すことを省略している。図5は図4に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。図4および図5に示す平面図において、図の左右方向をX軸方向とし、図の上下方向をY軸方向とする。

【0046】

図5に示すように、P−Trは、制御電極であるゲート電極G1、G2と、被制御電極である拡散層D1と、被制御電極である拡散層S1、S2とを有する。拡散層D1はドレイン電極に相当し、P型導電性不純物が拡散されている。拡散層S1、S2はソース電極に相当し、P型導電性不純物が拡散されている。拡散層D、S1、S2における導電性不純物の濃度は、図3Aに示したPウェル領域102の濃度よりも高い。

【0047】

ゲート電極G1、G2のそれぞれの外側には、ダミーゲート電極DG1、DG2がそれぞれ設けられている。ダミーゲート電極DG1、DG2は、図に示さない配線を介してソース電極に接続されている。本実施例では、ゲート電極G1、G2およびダミーゲート電極DG1、DG2のそれぞれのパターンは同一である。また、ゲート電極G1、G2およびダミーゲート電極DG1、DG2のパターンは、ゲート電極のパターンのX軸方向の長さ(以下では、ゲート長(またはチャネル長)と称する)がY軸方向に対して均一に、Y軸方向に延在している。

【0048】

ゲート電極G1、G2およびダミーゲート電極DG1、DG2のX軸方向の間隔が等しい構成である。つまり、ダミーゲート電極DG1およびゲート電極G1の距離と、ダミーゲート電極DG2およびゲート電極G2の距離のそれぞれが、ゲート電極G1およびゲート電極G2の距離と等しい。この間隔は、図3Aに示したP−Tr111〜113のように、複数のトランジスタがX軸方向に配置されている場合でも保たれている。

【0049】

これらのダミーゲート電極およびゲート電極の間隔を等しくすることで、半導体装置の製造過程で、ゲート電極のパターニング時における、ゲート長のばらつきを抑制できる。

【0050】

図4および図5に示す第1金属配線M11、第2金属配線M12および第3金属配線M13は第1金属配線層に設けられている。第1金属配線M11は第1ビアV1を介して拡散層D1と接続されている。第2金属配線M12は第1ビアV1を介して拡散層S1と接続され、第3金属配線M13は第1ビアV1を介して拡散層S2と接続されている。

【0051】

図4に示す第4金属配線M24、第5金属配線M25および第6金属配線M26は、第1金属配線層よりも上層に位置する第2金属配線層に設けられている。第4金属配線M24は第2ビアV2を介して第1金属配線M11と接続されている。第5金属配線M25は第2ビアV2を介して第2金属配線M12と接続され、第6金属配線M26は第2ビアV2を介して第3金属配線M13と接続されている。第4金属配線M24は、P−Tr111のドレイン電極に相当する拡散層D1に接続されているので、P−Tr111の出力端子OUT1に相当する。

【0052】

図4に示すように、本実施例では、第1ビアV1と第2ビアV2のパターンはマスク上においては正方形(製造後では円形)であり、第1ビアV1の1辺の長さが第2ビアV2の1辺の長さよりも小さい。そのため、パターン面積は、第2ビアV2の方が第2ビアV1よりも大きい。なお、本実施例では、第1ビアV1と第2ビアV2のパターンが正方形の場合で説明するが、これらのパターンは正方形に限定されず、楕円や円であってもよい。また、以下では、第1ビアV1および第2ビアV2のパターンのXY平面における最長箇所の長さをパターンサイズと称する。

【0053】

次に、第1金属配線M11〜第3金属配線M13のパターンと第1ビアV1の配置について、図5を参照して詳しく説明する。

【0054】

図5に示すように、第1金属配線M11のパターンは、第1金属配線M11のX軸方向の長さ(以下では、この長さを幅と呼ぶ)がY軸方向に対して均一に、Y軸方向に延在している。第1金属配線M11は、X軸方向に対して、ダミーゲート電極DG1およびダミーゲート電極DG2の間の距離の中央に配置されている。第2金属配線M12および第3金属配線M13のパターンは、第1ビアV1が接続される部位の幅の方が、第1ビアV1が接続されない部位の幅よりも長い。

【0055】

第1ビアV1が接続される部位の幅をW1と表し、第1ビアV1が接続されない部位の幅をW2と表すと、図5に示すように、W1>W2の関係になっている。本実施例では、第1金属配線M11の幅がW2に等しい。

【0056】

続いて、図5において、第1金属配線M11および第2金属配線M12の配線間距離に注目する。第2金属配線M12における幅W1の部位と第1金属配線M11との距離をGap1とし、第2金属配線M12における幅W2の部位と第1金属配線M11との距離をGap2とすると、図5を見てわかるように、Gap2>Gap1の関係になっている。この関係は、第1金属配線M11および第3金属配線M13の配線間隔についても同様である。

【0057】

次に、図5において、第1金属配線M11に接続される第1ビアV1の配置と第2金属配線M12に接続される第1ビアV1の配置に注目する。

【0058】

ここで、例えば、図5の第1金属配線M11を見ると、複数の第1ビアV1がY軸方向に配置されているが、隣り合う第1ビアV1の距離は、短いところと長いところの2種類がある。短い距離で隣り合う2つの第1ビアV1を1つの組と考え、この組を「第1ビアの組」と称する。

【0059】

第1金属配線M11では、第1ビアの組がY軸方向に等間隔に配置されている。図5では、その間隔をYL1で表している。第2金属配線M12においても、第1ビアの組が間隔YL1で配置されているが、Y軸方向の座標が第1金属配線M11に接続される第1ビアの組と異なっている。つまり、Y軸方向に対して、第1金属配線M11に接続される第1ビアの組と第2金属配線M12に接続される第1ビアの組とが交互に配置されている。また、第2金属配線M12では、複数の第1ビアの組が等間隔でY軸方向に配置される列が、ダミーゲート電極DG1の両側に、ダミーゲート電極DG1から同じ距離の位置に設けられている。

【0060】

図5において、第3金属配線M13に接続される第1ビアV1を見ると、第3金属配線M13における第1ビアの組の配置は、第2金属配線M12における第1ビアの組の配置と同等である。そのため、第2金属配線M12の場合と同様に、Y軸方向に対して、第1金属配線M11に接続される第1ビアの組と第3金属配線M13に接続される第1ビアの組とが交互に配置されている。

【0061】

次に、第4金属配線M24、第5金属配線M25および第6金属配線M26のパターンについて、図4を参照して説明する。

【0062】

図4に示すように、第4金属配線M24〜第6金属配線26のパターンは、同一であり、各パターンのX軸方向の長さ(この長さを幅と称する)がY軸方向に対して均一に、Y軸方向に延在している。この幅を図4にW3で示す。X軸方向に対して、第5金属配線M25および第6金属配線26の幅のそれぞれの中心がダミーゲート電極DG1、DG2のそれぞれの中心に一致するように、第5金属配線M25および第6金属配線26が配置されている。また、X軸方向に対して、第4金属配線M24の幅の中心が複数の第1ビアの組が配置された列の中心に一致するように、第4金属配線M24が配置されている。

【0063】

第4金属配線M24および第5金属配線M25の配線間距離をGap3で表すと、第4金属配線M24および第6金属配線M26の配線間距離もGap3となる。W3<W2なので、Gap3>Gap2の関係になっている。

【0064】

次に、図4および図5を参照して説明した配線間距離について、P−Tr111の断面図で説明する。

【0065】

図6Aは図4に示す線分AAの部位の断面図を示し、図6Bは図4に示す線分BBの部位の断面図を示す。これらの断面図では、膜の積層方向をZ軸方向としている。

【0066】

図6Aおよび図6Bに示すように、半導体基板100の表面近傍に、ソース電極に相当する拡散層S1、S2と、ドレイン電極に相当する拡散層D1が設けられている。なお、図6Aおよび図6Bの断面図では、Nウェル領域を図に示すことを省略している。このことは、他の実施例で参照する断面図についても同様である。

【0067】

半導体基板100の上にはゲート絶縁膜(不図示)を介してゲート電極G1、G2およびダミーゲート電極DG1、DG2が設けられ、これらのゲート電極を覆うように第1絶縁膜161がゲート絶縁膜上に設けられている。

【0068】

第1絶縁膜161の上には第1金属配線M11〜第3金属配線M13が設けられている。第1絶縁膜161には、第1絶縁膜161を貫通する第1ビアV1が設けられている。図6Aに示すように、第2金属配線M12が第1ビアV1を介して拡散層S1と接続されている。第3金属配線M13が第1ビアV1を介して拡散層S2と接続されている。図6Bに示すように、第1金属配線M11が第1ビアV1を介して拡散層D1と接続されている。

【0069】

第1絶縁膜161の上には、第1金属配線M11〜第3金属配線M13を覆うように第2絶縁膜162が設けられている。第2絶縁膜162の上には第4金属配線M24〜第6金属配線M26が設けられている。第2絶縁膜162には、第2絶縁膜162を貫通する第2ビアV2が設けられている。

【0070】

図6Aおよび図6Bに示すように、第5金属配線M25が第2ビアV2を介して第2金属配線M12と接続されている。第4金属配線M24が第2ビアV2を介して第1金属配線M11と接続されている。第6金属配線M26が第2ビアV2を介して第3金属配線M13と接続されている。第2絶縁膜162の上には、第4金属配線M24〜第6金属配線M26を覆うように第3絶縁膜163が設けられている。

【0071】

図6Aおよび図6Bを見比べると、Gap2>Gap1の関係になっていることが明らかである。図6Aでは、第2金属配線M12および第3金属配線M13のそれぞれに接続される第1ビアV1が図に示されているが、第1金属配線M11に第1ビアV1は接続されていない。その反対に、図6Bでは、第1金属配線M11に接続される第1ビアV1が図に示されているが、第2金属配線M12および第3金属配線M13に第1ビアV1は接続されていない。これは、図4および図5を参照して説明したように、第1金属配線M11に接続される第1ビアの組と、第2金属配線M12または第3金属配線M13に接続される第1ビアの組とがY軸方向に対して交互に配置されているからである。

【0072】

よって、第1金属配線M11と第2金属配線M12との間の寄生容量C1、第1金属配線M11と第3金属配線M13との間の寄生容量C2、第4金属配線M24と第5金属配線M25との間の寄生容量C3、第4金属配線M24と第6金属配線M26との間の寄生容量C4、第1金属配線M11と第5金属配線M25との間の寄生容量C5、第1金属配線M11と第6金属配線M26との間の寄生容量C6、第2金属配線M12と第4金属配線M24との間の寄生容量C7、及び第3金属配線M13と第4金属配線M24との間の寄生容量C8のそれぞれの値が、削減されていることが理解できる。それぞれの金属配線とその他のノード(例えばゲートや被制御端子)との寄生容量値も、それぞれ低減されることは言うまでもない。

【0073】

次に、本実施例の半導体装置の製造方法を説明する。ここでは、図4に示したP−Trの形成方法を、図4〜図6B、図7および図8を参照して説明する。

【0074】

図7および図8は図4に示したP−Trの形成過程の一例を示す平面図である。図7はゲート電極形成後の平面図であり、図8は第1ビア形成後の平面図である。

【0075】

図6Aに示した半導体基板100に対して、活性領域を分離するための素子分離領域と、Nウェル領域およびPウェル領域とを形成した後、半導体基板100の表面にゲート絶縁膜(不図示)を形成する。その後、導電性材料膜をゲート絶縁膜上に形成し、リソグラフィ工程により、図7に示すように、導電性材料膜でゲート電極G1、G2およびダミーゲート電極DG1、DG2をパターニングする(図7参照)。

【0076】

続いて、ゲート電極G1、G2およびダミーゲート電極DG1、DG2をマスクに、N型導電性不純物を半導体基板100に打ち込むイオン注入工程を行い、その後、熱処理を行う。これにより、図6Aおよび図6Bに示した拡散層D1および拡散層S1、S2が半導体基板100の表面近傍に形成される。なお、この熱処理は、イオン注入工程の直後でなくても、イオン注入工程の後であれば、半導体装置の製造過程において、いずれのタイミングで行ってもよい。

【0077】

上記のイオン注入工程の後、図6Aおよび図6Bに示したように、ゲート絶縁膜(不図示)の上に、ゲート電極G1、G2およびダミーゲート電極DG1、DG2を覆う第1絶縁膜161をCVD(Chemical Vapor Deposition)法で形成する。そして、リソグラフィ工程により第1絶縁膜161に開口を形成し、形成した開口に導電性材料を埋め込むことで、第1ビアV1を第1絶縁膜161に形成する(図6A、図6Bおよび図8参照)。

【0078】

第1絶縁膜161の上に第1金属配線層を形成し、リソグラフィ工程により第1金属配線層で第1金属配線M11〜第3金属配線M13を形成する(図5参照)。続いて、第1絶縁膜161の上に、第1金属配線M11〜第3金属配線M13を覆う第2絶縁膜162をCVD法で形成する。そして、リソグラフィ工程により第2絶縁膜162に開口を形成し、形成した開口に導電性材料を埋め込むことで、第2ビアV2を第2絶縁膜162に形成する(図6A、図6Bおよび図4参照)。

【0079】

その後、第2絶縁膜162の上に第2金属配線層を形成し、リソグラフィ工程により第2金属配線層で第4金属配線M24〜第6金属配線M26を形成する(図4参照)。そして、第2絶縁膜162の上に、第4金属配線M24〜第6金属配線M26を覆う第3絶縁膜163をCVD法で形成する。

【0080】

本実施例によれば、第1金属配線層の隣り合う配線間で、これらの配線に接続される第1ビアの組が交互に配置されているので、配線間容量が削減される。また、ソース電極に相当する拡散層S1、S2に接続される第1ビアを配置していない部位では、第2金属配線および第3金属配線の幅を短くして、余分な部位を削除している。配線間隔が広くなる部位では、配線間の寄生容量が削減される。

【0081】

本実施例の構成でダミートランジスタを4本設けた場合、カップリング容量は6.91fFから5.97fF(86.4パーセント)に低減した。

【実施例2】

【0082】

本実施例は、実施例1と同様に、第1金属配線層の配線間容量を削減するものであるが、さらに配線間容量を削減可能にした構成である。

【0083】

本実施例の半導体装置の構成を説明する。本実施例においても、実施例1と同様に、リングオシレータに用いられるP−Trの構成について説明する。また、本実施例では、実施例1と同様な構成についての詳細な説明を省略し、実施例1と異なる点を中心に説明する。

【0084】

図9は図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。図10は図9に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。図9および図10に示す平面図において、図の左右方向をX軸方向とし、図の上下方向をY軸方向とする。

【0085】

図9に示すように、第1金属配線M11に接続される第2ビアV2の数が実施例1の場合よりも少ない。また、図10に示すように、第1金属配線M11のパターンと第1金属配線M11に接続される第1ビアV1の配置が実施例1と異なっている。以下に、実施例1との違いを、図10を参照して詳しく説明する。

【0086】

第1金属配線M11に接続される第1ビアの組は、実施例1の場合と同様に等間隔で配置されているが、Y軸方向の位置が第2金属配線M12および第3金属配線M13のそれぞれに接続される第1ビアの組と対向して配置されている。

【0087】

また、第1金属配線M11のパターンにおいて、第2ビアV2が接続される部位の幅が図5に示した幅W2よりも小さいW5である。幅W5は、第2ビアV2のパターンサイズ以上であればよい。幅W5は、第2ビアV2のパターンサイズ以上であり、第2ビアV2の配置およびパターンサイズのばらつきを含む値であってもよい。このばらつきの値は、リソグラフィ工程における製造ばらつきによって決まる。本実施例では、幅W5は図4に示した幅W3に等しい。さらに、第1金属配線M11のパターンにおいて、第1ビアV1が接続される部位の幅がW5よりも小さいW4である。

【0088】

上述した構成の本実施例と実施例1との違いを、第1金属配線M11および第3金属配線M13の配線間距離に注目して説明する。

【0089】

図10において、第1金属配線M11における幅W5の部位と第3金属配線M13との距離をGap4とし、第1金属配線M11における幅W4の部位と第3金属配線M13との距離をGap5とする。図5と図10を見比べると、Gap4>Gap2、Gap5>Gap1となっている。そのため、第1金属配線M11および第3金属配線M13の配線間容量が、実施例1の構成に比べて、さらに低減する。

【0090】

なお、第1金属配線M11および第3金属配線M13の配線間距離に注目して説明したが、上述した構成は、第1金属配線M11および第2金属配線M12の配線間距離についても同様である。また、本実施例では、W3=W5の場合で説明したが、W3≠W5であってもよく、W3<W2であれば、配線間容量低減の効果が得られる。

【0091】

次に、図10を参照して説明した配線間距離について、P−Tr111の断面図で説明する。

【0092】

図11Aは図9に示す線分AAの部位の断面図を示し、図11Bは図9に示す線分BBの部位の断面図を示す。これらの断面図では、膜の積層方向をZ軸方向としている。

【0093】

図11Aと図6Aを見比べると、第1金属配線M11に接続される第2ビアV2が図6Aには現われているが、図11Aには現われていない。一方、第1金属配線M11に接続される第1ビアV1が図6Aには現われていないが、図11Aには現われている。これらの断面図に示す部位において、本実施例では、第1金属配線M11は、第2ビアV2の代わりに、第2ビアV2よりもパターンサイズの小さい第1ビアV1と接続されている。そのため、第1金属配線M11の幅をW2より短いW4にすることが可能となる。その結果、第1金属配線M11および第3金属配線M13の配線間距離Gap5が、実施例1の場合の配線間距離Gap1よりも長くなっている。

【0094】

図11Bと図6Bを見比べると、どちらの場合も、第1金属配線M11に接続される第1ビアV2が現われているが、これらの断面図の部位において、本実施例では、第1金属配線M11の幅W5は、第2ビアV2のパターンサイズ以上であるが、W2よりも小さい。そのため、第1金属配線M11および第3金属配線M13の配線間距離Gap4が、実施例1の場合の配線間距離Gap2よりも長くなっている。

【0095】

本実施例によれば、実施例1の構成に比べて、第1金属配線において、第1ビアおよび第2ビアのそれぞれが接続される部位の幅を短くしているので、ドレイン電極に接続される第1金属配線とソース電極に接続される第2金属配線および第3金属配線のそれぞれとの配線間距離が長くなっている場所が増える。そのため、配線間の寄生容量の低減効果がさらに向上する。

【0096】

本実施例の構成でダミートランジスタを4本設けた場合、カップリング容量は6.91fFから5.91fF(85.5パーセント)に低減した。

【実施例3】

【0097】

本実施例は、実施例1の構成に対し、第1金属配線に接続される第1ビアの数を減らし、第1ビアを配置しない部位を削除して配線間容量の削減するものである。

【0098】

本実施例の半導体装置の構成を説明する。本実施例においても、実施例1および実施例2と同様に、リングオシレータに用いられるP−Trの構成について説明する。また、本実施例では、実施例1または実施例2と同様な構成についての詳細な説明を省略し、これらの実施例と異なる点を中心に説明する。

【0099】

図12は図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。図13は図12に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。図12および図13に示す平面図において、図の左右方向をX軸方向とし、図の上下方向をY軸方向とする。

【0100】

図12に示すように、第1金属配線M11に接続される第2ビアV2の数と配置は実施例2の場合と同様であるが、第1ビアV1が第2ビアV2の位置に重ねて配置されている。また、実施例1と同様に、第1金属配線M11に接続される第1ビアの組が、第2金属配線M12および第3金属配線M13のそれぞれに接続される第1ビアの組と、Y軸方向に対して交互に配置されている。さらに、第1金属配線M11のパターンが実施例1および実施例2のいずれとも異なっている。以下に、実施例2との違いを、図13を参照して詳しく説明する。

【0101】

本実施例の第1金属配線M11のパターンは、図13に示すように、図5に示したパターンが第1ビアV1の組毎に、第1ビアV1の組を囲む領域で切り離され、複数に分けられている。以下では、第1ビアV1の組を囲む、1つのパターンを第1サブ金属配線と称する。複数の第1サブ金属配線がY軸方向に等間隔で配置されており、その間隔を図13にYL2と示している。本実施例では、第1金属配線M11の各第1サブ金属配線の幅はW5である。各第1サブ金属配線のパターンのX軸方向の長さは、第1ビアV1のパターンサイズと第2ビアV2のパターンサイズの最大値以上である。各第1サブ金属配線のパターンのY軸方向の長さは、第1ビアの組における2つの第1ビアV1のY軸方向の長さと第2ビアV2のパターンサイズの最大値以上である。

【0102】

なお、各第1サブ金属配線のパターンのX軸方向およびY軸方向のそれぞれの長さについても、第1ビアの組および第2ビアV2の配置とそれぞれのパターンサイズのばらつきを見込んだ長さを含むようにしてもよい。

【0103】

続いて、図13において、第1金属配線M11および第2金属配線M12の配線間距離に注目してみる。

【0104】

図13に示すように、第1金属配線M11の第1サブ金属配線と第2金属配線M12との配線間距離は、大部分がGap4である。第1金属配線M11の第1サブ金属配線と第2金属配線M12との配線間距離は、最も短いところで、Gap4より短いGap6である。しかし、Gap6は、第1金属配線M11の第1サブ金属配線の角と第2金属配線M12のパターンの角の距離であり、配線間容量に大きな影響はない。

【0105】

一方、第1サブ金属配線が配置されていない部位では、第1金属配線層において、第2金属配線M12と第3金属配線M13の間に配線が配置されていないので、第2金属配線M12と第3金属配線M13の間に配線間距離Gap7が確保される。なお、第1金属配線M11および第2金属配線M12の配線間距離に注目して説明したが、上述した構成は、第1金属配線M11および第3金属配線M13の配線間距離についても同様である。

【0106】

次に、図13を参照して説明した配線間距離について、P−Tr111の断面図で説明する。

【0107】

図14Aは図12に示す線分AAの部位の断面図を示し、図14Bは図12に示す線分BBの部位の断面図を示す。これらの断面図では、膜の積層方向をZ軸方向としている。

【0108】

図14Aに示す部位では、第1金属配線M11が配置されていないので、第2金属配線M12または第3金属配線M13と第1金属配線M11との配線間容量は生じない。ソース電極およびドレイン電極間の配線間容量としては、第2金属配線M12および第4金属配線M24の配線間容量と、第3金属配線M13および第4金属配線M24の配線間容量となる。図14Bに示す部位では、図11Bに示した部位と同様に、第1金属配線M11と第1金属配線M12および第3金属配線M13のそれぞれとの配線間距離Gap4が確保されている。

【0109】

本実施例では、第1金属配線に接続される第1ビアの数を減らし、第1金属配線のうち、第1ビアを配置しない部位を削除している。そのため、実施例1や実施例2の場合に比べて、配線間の寄生容量の低減効果が向上する。

【0110】

本実施例の構成でダミートランジスタを4本設けた場合、カップリング容量は6.91fFから5.20fF(75.3パーセント)に低減した。

【実施例4】

【0111】

本実施例は、実施例3の構成に対し、第1金属配線に接続される第1ビアの数をさらに減らし、第2金属配線および第3金属配線に接続される第1ビアの数を減らして配線間容量を削減するものである。

【0112】

本実施例の半導体装置の構成を説明する。本実施例においても、実施例1から実施例3と同様に、リングオシレータに用いられるP−Trの構成について説明する。また、本実施例では、実施例3と同様な構成についての詳細な説明を省略し、実施例3と異なる点を中心に説明する。

【0113】

図15は図3Aに示したリングオシレータに用いられるP−Trのパターンの一例を示す平面図である。図16は図15に示したP−Trのパターンから第2金属配線層および第2ビアのパターンを取り除いた場合の平面図である。図15および図16に示す平面図において、図の左右方向をX軸方向とし、図の上下方向をY軸方向とする。

【0114】

図16に示すように、本実施例では、実施例3と比べて、第1金属配線M11に相当する複数の第1サブ金属配線の数が少なく、その配置間隔YL3がYL2よりも長い。図15に示すように、実施例3と比べて、第2金属配線M12および第3金属配線M13のそれぞれに接続する第1ビアの組の数が少ない。第2金属配線M12および第3金属配線M13のそれぞれに接続する第1ビアの組の配置間隔は、図16に示すように、第1サブ金属配線の配置間隔と同じYL3である。

【0115】

続いて、図16において、第1金属配線M11および第2金属配線M12の配線間距離に注目してみる。

【0116】

図16に示すように、第1金属配線M11の第1サブ金属配線と第2金属配線M12との配線間距離はGap4である。本実施例では、実施例3の図13に示したGap6のような箇所はない。第1サブ金属配線が配置されていない部位では、第1金属配線層において、第2金属配線M12と第3金属配線M13の間に配線が配置されていないので、実施例3と同様に、第2金属配線M12と第3金属配線M13の間に配線間距離Gap7が確保される。また、本実施例では、図16に示すように、第2金属配線M12と第3金属配線M13の間に配線間距離がGap7よりも大きいGap8となる部位が存在している。

【0117】

なお、第1金属配線M11および第2金属配線M12の配線間距離に注目して説明したが、上述した構成は、第1金属配線M11および第3金属配線M13の配線間距離についても同様である。

【0118】

次に、図16を参照して説明した配線間距離について、P−Tr111の断面図で説明する。

【0119】

図17Aは図15に示す線分AAの部位の断面図を示し、図17Bは図15に示す線分BBの部位の断面図を示す。これらの断面図では、膜の積層方向をZ軸方向としている。

【0120】

図17Aに示す部位では、第1金属配線M11が配置されていないので、第2金属配線M12または第3金属配線M13と第1金属配線M11との配線間容量は生じない。ソース電極およびドレイン電極間の配線間容量としては、第2金属配線M12および第4金属配線M24の配線間容量と、第3金属配線M13および第4金属配線M24の配線間容量となる。図17Bに示す部位では、図14Bに示した部位と同様に、第1金属配線M11と第1金属配線M12および第3金属配線M13のそれぞれとの配線間距離Gap4が確保されている。

【0121】

本実施例では、実施例3の構成に比べて、第1金属配線に接続される第1ビアの数をさらに減らし、第2金属配線および第3金属配線に接続される第1ビアの数を減らしている。そして、第1金属配線から第3金属配線のそれぞれにおいて、第1ビアの配置しない部位を削除している。そのため、実施例3の構成に比べて、配線間の寄生容量の低減効果が向上する。

【0122】

本実施例の構成でダミートランジスタを4本設けた場合、カップリング容量は6.91fFから4.49fF(65.0パーセント)に低減した。

【0123】

上述した実施例1から実施例4では、コンタクト数によるTr能力の変化と、寄生容量の削減との相殺効果を有する。要求される回路特性に対応して、実施例1から実施例4から最適なレイアウトを選択すればよい。

【0124】

将来、半導体装置はさらなる微細化と高速化が進み、ますます寄生容量の削減が重要になる。寄生容量値が回路特性に与える影響を考慮しなければならないセンシティブな回路、例えば電圧制御発振回路のような回路においては、本発明をベースとした改良対策が必須となるので、本発明は非常に重要な技術となる。

【0125】

また、上述の実施例1から実施例4では、金属配線層が2層の場合で説明したが、将来のプロセスでは配線層が3層以上の多段化も考えられる。この場合においても高速動作回路の接点容量削減には、本発明が有効である。

【0126】

さらに、本発明を、電圧制御発振回路以外の機能素子等の回路に適用してもよい。

【0127】

本願の技術思想は、複数の電界効果トランジスタで構成する回路を有する半導体装置に適用できる。更に、図面で開示した各回路ブロック内の回路形式は、実施例が開示する回路形式限られない。

【0128】

本発明の半導体装置の技術思想は、様々な半導体装置に適用することができる。例えば、CPU(Central Processing Unit)、MCU(Micro Control Unit)、DSP(Digital Signal Processor)、ASIC(Application Specific Integrated Circuit)、ASSP(Application Specific Standard Product)、メモリ(Memory)等の半導体装置全般に、本発明を適用することができる。このような本発明が適用された半導体装置の製品形態としては、例えば、SOC(システムオンチップ)、MCP(マルチチップパッケージ)やPOP(パッケージオンパッケージ)などが挙げられる。これらの任意の製品形態、パッケージ形態を有する半導体装置に対して本発明を適用することができる。

【0129】

また、トランジスタは、電界効果トランジスタ(Field Effect Transistor; FET)であれば良く、MOS(Metal Oxide Semiconductor)以外にもMIS(Metal-Insulator Semiconductor)、TFT(Thin Film Transistor)等の様々なFETに適用できる。トランジスタ等の様々なFETに適用できる。更に、装置内に一部のバイポーラ型トランジスタを有しても良い。

【0130】

更に、NMOSトランジスタ(N型チャネルMOSトランジスタ)は、第1導電型のトランジスタ、PMOSトランジスタ(P型チャネルMOSトランジスタ)は、第2導電型のトランジスタの代表例である。

【0131】

また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせ乃至選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0132】

10 半導体装置

26 クロック生成部

111〜113 P型チャネルMOSFET(P−Tr)

121〜123 N型チャネルMOSFET(N−Tr)

D1、S1、S2 拡散層

G1、G2 ゲート電極

DG1、DG2 ダミーゲート電極

V1 第1ビア

V2 第2ビア

M11 第1金属配線

M12 第2金属配線

M13 第3金属配線

M24 第4金属配線

M25 第5金属配線

M26 第6金属配線

【特許請求の範囲】

【請求項1】

それぞれが、ドレイン拡散層と、該ドレイン拡散層を挟んで両側に配設される一対のソース拡散層と、前記ドレイン拡散層と前記一対のソース拡散層との間にそれぞれ配設される一対のゲート電極とを有し、列方向に配列される複数のトランジスタと、

前記一対のソース拡散層の内の一方を含む互いに隣接する2つのソース拡散層の間に配列され、該2つのソース拡散層と同電位に維持されている第1のダミーゲート電極と、

前記一対のソース拡散層の内の他方を含む互いに隣接する2つのソース拡散層の間に配列され、該2つのソース拡散層と同電位に維持されている第2のダミーゲート電極と、

複数の第1のビアを介して前記ドレイン拡散層に接続する第1の金属配線と、

前記一対のソース拡散層の一方であって前記互いに隣接する2つのソース拡散層の両方にそれぞれ対応する複数の第1のビアを介して接続する第2の金属配線と、

前記一対のソース拡散層の他方であって前記互いに隣接する2つのソース拡散層の両方にそれぞれ対応する複数の第1のビアを介して接続する第3の金属配線と、

前記第1乃至第3の金属配線にそれぞれ対応する複数の第2のビアを介して接続する第4乃至第6の金属配線と、を備え、

前記第2及び第3の金属配線の前記列方向におけるそれぞれの幅は、対応する前記2つのソース拡散層にそれぞれ接続する複数の第1のビアの両方を含む第1の幅と、前記第1のビアを含まず前記第1の幅よりも短い第2の幅と、を有し、

前記第1及び第2の金属配線の間、並びに前記第1及び第3の金属配線の間のそれぞれのギャップは、前記第1の幅に対応する第1のギャップと、前記第2の幅に対応する前記第1のギャップよりも大きな第2のギャップと、を有し、

前記第4乃至第6の金属配線の前記列方向におけるそれぞれの幅は、前記第1の幅よりも短い第3の幅を有する、半導体装置。

【請求項2】

請求項1記載の半導体装置において、

前記第4及び第5の金属配線の間、並びに前記第4及び第6の金属配線の間のそれぞれのギャップは、前記第1のギャップよりも更に大きな第3のギャップを有する、半導体装置。

【請求項3】

請求項1又は2記載の半導体装置において、

前記第2のビアのサイズは、前記第1のビアのサイズよりも大きく、

前記第1の金属配線の前記列方向における幅は、前記第1のビアを含む第4の幅と、前記第2のビアを含む第5の幅と、の少なくともいずれか一方を有する、半導体装置。

【請求項4】

請求項3記載の半導体装置において、

前記第1の金属配線に対応する前記複数の第1のビアと、前記第2及び第3の金属配線にそれぞれ対応する前記複数の第1のビアとは、前記列方向に垂直な行方向の視点において互いに交互に配置される、半導体装置。

【請求項5】

請求項3記載の半導体装置において、

前記第1の金属配線は、前記第4及び第5の幅の両方を有し、

前記第1の金属配線に対応する前記複数の第1のビアと、前記第2及び第3の金属配線にそれぞれ対応する前記複数の第1のビアとは、前記列方向に垂直な行方向の視点において互いに対向に配置され、

前記第1のギャップは、前記第1の幅と前記第4の幅とのギャップであり、

前記第2のギャップは、前記第2の幅と前記第5の幅とのギャップである、半導体装置。

【請求項6】

請求項3または4記載の半導体装置において、

前記第1の金属配線は、前記複数の第1のビアを介してそれぞれ前記ドレイン拡散層に接続し、前記行方向に展開してセパレートに配置される複数の第1のサブ金属配線で構成される、半導体装置。

【請求項7】

請求項6記載の半導体装置において、

前記第2及び第3の金属配線がそれぞれ有する前記第1の幅の間を示す第4のギャップをさらに有する、半導体装置。

【請求項8】

請求項6記載の半導体装置において、

前記第2及び第3の金属配線がそれぞれ有する前記第2の幅の間を示す第5のギャップをさらに有する、半導体装置。

【請求項9】

請求項1から8のいずれか1項記載の半導体装置において、

前記第3の幅は、前記第2の幅よりも短い、半導体装置。

【請求項10】

請求項9記載の半導体装置において、

前記第4及び第5の金属配線の間、並びに前記第4及び第6の金属配線の間のそれぞれのギャップは、前記第1のギャップよりも更に大きな第3のギャップを有し、

前記第3のギャップは、前記第2のギャップよりも大きい、半導体装置。

【請求項11】

請求項1から10のいずれか1項記載の半導体装置において、

前記第1及び第4の金属配線は、前記ドレイン拡散層の領域に配置され、

前記第2及び第5の金属配線、並びに前記第3及び第6の金属配線は、それぞれ対応する前記第1及び第2のダミーゲート電極の上に配置される、半導体装置。

【請求項12】

請求項11記載の半導体装置において、

前記第5及び6の金属配線にそれぞれ対応する前記複数の第2のビアは、それぞれ対応する前記第1及び第2のダミーゲート電極の上に配置される、半導体装置。

【請求項13】

トランジスタのソース電極またはドレイン電極を構成し、それぞれ第1の方向に延在する第1乃至第5の拡散部を含む拡散層と、

前記トランジスタのゲート電極を構成し、前記第1の方向に延在する第1及び第2のゲート配線、並びに前記第1の方向に延在する第1及び第2のダミーゲート配線を含むゲート層と、

前記第1の方向に延在する第1乃至第3の金属配線を含む第1の金属層と、

前記第1の方向に延在する第4から第6の金属配線を含む第2の金属層と、

前記第1の方向に展開して配置される複数の第1のビアを含み、前記拡散層と前記第1の金属層を接続する第1のビア層と、

前記第1の方向に展開して配置される複数の第2のビアを含み、前記第1及び第2の金属層を接続する第2のビア層と、を備え、

第1のトランジスタは、前記第1のゲート配線、前記第1及び第2の拡散部で構成され、

第2のトランジスタは、前記第2のゲート配線、前記第1及び第3の拡散部で構成され、前記第1のトランジスタに隣接して前記第1の方向と直交する第2の方向へ配置され、

第3のトランジスタは、前記1のダミーゲート配線、並びに、前記第2及び第4の拡散部で構成され、前記第1のトランジスタに隣接して、前記第2の方向とは反対の第3の方向に配置され、更に前記1のダミーゲート配線、並びに、前記第3及び第4の拡散部は、同電位であり、

第4のトランジスタは、前記2のダミーゲート配線、並びに、前記第3及び第5の拡散部で構成され、前記第2のトランジスタに隣接して前記第2の方向に配置され、更に前記2のダミーゲート配線、並びに、前記第3及び第5の拡散部は、同電位であり、

それぞれが、少なくとも一つの前記第1のビアをセットとする複数の第1セットが、第1のピッチで前記第1の拡散部に配置され、

それぞれが、少なくとも一つの前記第1のビアをセットとする複数の第2セットが、第2のピッチで前記第2乃至第5の拡散部にそれぞれ配置され、

前記第1の金属配線は、前記第1の拡散部に関連する複数の第1のビアを覆うように前記第1の拡散部の領域に配置され、

前記第2の金属配線は、前記第2及び第4の拡散部にそれぞれ関連する複数の第1のビアを一体として覆うように前記第3のトランジスタの領域に配置され、

前記第3の金属配線は、前記第3及び第5の拡散部にそれぞれ関連する複数の第1のビアを一体として覆うように前記第4のトランジスタの領域に配置され、

それぞれが、少なくとも一つの前記第2のビアをセットとする複数の第3セットが、第3のピッチで前記第1の金属配線に配置され、

それぞれが、少なくとも一つの前記第2のビアをセットとする複数の第4セットが、第4のピッチで前記第2及び第3の金属配線にそれぞれ配置され、

前記第4の金属配線は、前記第1の金属配線に関連する複数の第2のビアを覆うように前記第1の拡散部の領域に配置され、

前記第5の金属配線は、前記第2の金属配線に関連する複数の第2のビアを覆うように前記第3のトランジスタの領域に配置され、

前記第6の金属配線は、前記第3の金属配線に関連する複数の第2のビアを覆うように前記第4のトランジスタの領域に配置され、

前記第2の金属配線の前記第3の方向における幅は、前記第2の拡散部に関連する前記第1のビア及び前記第4の拡散部に関連する前記第1のビアの両方を含む第1の幅と、前記第1の幅よりも短い第2の幅と、を有し、

前記第3の金属配線の前記第2の方向における幅は、前記第3の拡散部に関連する前記第1のビア及び前記第5の拡散部に関連する前記第1のビアの両方を含む前記第1の幅と、前記第2の幅と、を有し、

前記第4乃至第6の金属配線の前記第2の方向におけるそれぞれの幅は、前記第1の幅よりも短い第3の幅を有し、

前記第1及び第2の金属配線の間、並びに前記第1及び第3の金属配線の間のそれぞれのギャップは、前記第1の幅に対応する第1のギャップと、前記第2の幅に対応する前記第1のギャップよりも大きな第2のギャップと、を有する、半導体装置。

【請求項14】

請求項13記載の半導体装置において、

前記第4及び第5の金属配線の間、並びに前記第4及び第6の金属配線の間のそれぞれのギャップは、前記第1のギャップよりも更に大きな第3のギャップを有する、半導体装置。

【請求項15】

請求項13又は14記載の半導体装置において、

前記第2のビアのサイズは、前記第1のビアのサイズよりも大きく、

前記第1の金属配線の前記第2の方向における幅は、前記第1のビアを含む第4の幅と、前記第2のビアを含む第5の幅と、の少なくともいずれか一方を有する、半導体装置。

【請求項16】

請求項13から15のいずれか1項記載の半導体装置において、

前記第3の幅は、前記第2の幅よりも短い、半導体装置。

【請求項17】

請求項13から16のいずれか1項記載の半導体装置において、

前記第4及び第5の金属配線の間、並びに前記第4及び第6の金属配線の間のそれぞれのギャップは、前記第1のギャップよりも更に大きな第3のギャップを有し、

前記第3のギャップは、前記第2のギャップよりも大きい、半導体装置。

【請求項18】

請求項13から17のいずれか1項記載の半導体装置において、

前記第1及び第4の金属配線は、前記第1の拡散部に配置され、

前記第2及び第5の金属配線、並びに前記第3及び第6の金属配線は、それぞれ対応する前記第1及び第2のダミーゲート配線の上に配置される、半導体装置。

【請求項19】

請求項18記載の半導体装置において、

前記第5及び6の金属配線にそれぞれ対応する前記複数の第2のビアは、それぞれ対応する前記第1及び第2のダミーゲート配線の上に配置される、半導体装置。

【請求項1】

それぞれが、ドレイン拡散層と、該ドレイン拡散層を挟んで両側に配設される一対のソース拡散層と、前記ドレイン拡散層と前記一対のソース拡散層との間にそれぞれ配設される一対のゲート電極とを有し、列方向に配列される複数のトランジスタと、

前記一対のソース拡散層の内の一方を含む互いに隣接する2つのソース拡散層の間に配列され、該2つのソース拡散層と同電位に維持されている第1のダミーゲート電極と、

前記一対のソース拡散層の内の他方を含む互いに隣接する2つのソース拡散層の間に配列され、該2つのソース拡散層と同電位に維持されている第2のダミーゲート電極と、

複数の第1のビアを介して前記ドレイン拡散層に接続する第1の金属配線と、

前記一対のソース拡散層の一方であって前記互いに隣接する2つのソース拡散層の両方にそれぞれ対応する複数の第1のビアを介して接続する第2の金属配線と、

前記一対のソース拡散層の他方であって前記互いに隣接する2つのソース拡散層の両方にそれぞれ対応する複数の第1のビアを介して接続する第3の金属配線と、

前記第1乃至第3の金属配線にそれぞれ対応する複数の第2のビアを介して接続する第4乃至第6の金属配線と、を備え、

前記第2及び第3の金属配線の前記列方向におけるそれぞれの幅は、対応する前記2つのソース拡散層にそれぞれ接続する複数の第1のビアの両方を含む第1の幅と、前記第1のビアを含まず前記第1の幅よりも短い第2の幅と、を有し、

前記第1及び第2の金属配線の間、並びに前記第1及び第3の金属配線の間のそれぞれのギャップは、前記第1の幅に対応する第1のギャップと、前記第2の幅に対応する前記第1のギャップよりも大きな第2のギャップと、を有し、

前記第4乃至第6の金属配線の前記列方向におけるそれぞれの幅は、前記第1の幅よりも短い第3の幅を有する、半導体装置。

【請求項2】

請求項1記載の半導体装置において、

前記第4及び第5の金属配線の間、並びに前記第4及び第6の金属配線の間のそれぞれのギャップは、前記第1のギャップよりも更に大きな第3のギャップを有する、半導体装置。

【請求項3】

請求項1又は2記載の半導体装置において、

前記第2のビアのサイズは、前記第1のビアのサイズよりも大きく、

前記第1の金属配線の前記列方向における幅は、前記第1のビアを含む第4の幅と、前記第2のビアを含む第5の幅と、の少なくともいずれか一方を有する、半導体装置。

【請求項4】

請求項3記載の半導体装置において、

前記第1の金属配線に対応する前記複数の第1のビアと、前記第2及び第3の金属配線にそれぞれ対応する前記複数の第1のビアとは、前記列方向に垂直な行方向の視点において互いに交互に配置される、半導体装置。

【請求項5】

請求項3記載の半導体装置において、

前記第1の金属配線は、前記第4及び第5の幅の両方を有し、

前記第1の金属配線に対応する前記複数の第1のビアと、前記第2及び第3の金属配線にそれぞれ対応する前記複数の第1のビアとは、前記列方向に垂直な行方向の視点において互いに対向に配置され、

前記第1のギャップは、前記第1の幅と前記第4の幅とのギャップであり、

前記第2のギャップは、前記第2の幅と前記第5の幅とのギャップである、半導体装置。

【請求項6】

請求項3または4記載の半導体装置において、

前記第1の金属配線は、前記複数の第1のビアを介してそれぞれ前記ドレイン拡散層に接続し、前記行方向に展開してセパレートに配置される複数の第1のサブ金属配線で構成される、半導体装置。

【請求項7】

請求項6記載の半導体装置において、

前記第2及び第3の金属配線がそれぞれ有する前記第1の幅の間を示す第4のギャップをさらに有する、半導体装置。

【請求項8】

請求項6記載の半導体装置において、

前記第2及び第3の金属配線がそれぞれ有する前記第2の幅の間を示す第5のギャップをさらに有する、半導体装置。

【請求項9】

請求項1から8のいずれか1項記載の半導体装置において、

前記第3の幅は、前記第2の幅よりも短い、半導体装置。

【請求項10】

請求項9記載の半導体装置において、

前記第4及び第5の金属配線の間、並びに前記第4及び第6の金属配線の間のそれぞれのギャップは、前記第1のギャップよりも更に大きな第3のギャップを有し、

前記第3のギャップは、前記第2のギャップよりも大きい、半導体装置。

【請求項11】

請求項1から10のいずれか1項記載の半導体装置において、

前記第1及び第4の金属配線は、前記ドレイン拡散層の領域に配置され、

前記第2及び第5の金属配線、並びに前記第3及び第6の金属配線は、それぞれ対応する前記第1及び第2のダミーゲート電極の上に配置される、半導体装置。

【請求項12】

請求項11記載の半導体装置において、

前記第5及び6の金属配線にそれぞれ対応する前記複数の第2のビアは、それぞれ対応する前記第1及び第2のダミーゲート電極の上に配置される、半導体装置。

【請求項13】

トランジスタのソース電極またはドレイン電極を構成し、それぞれ第1の方向に延在する第1乃至第5の拡散部を含む拡散層と、

前記トランジスタのゲート電極を構成し、前記第1の方向に延在する第1及び第2のゲート配線、並びに前記第1の方向に延在する第1及び第2のダミーゲート配線を含むゲート層と、

前記第1の方向に延在する第1乃至第3の金属配線を含む第1の金属層と、

前記第1の方向に延在する第4から第6の金属配線を含む第2の金属層と、

前記第1の方向に展開して配置される複数の第1のビアを含み、前記拡散層と前記第1の金属層を接続する第1のビア層と、

前記第1の方向に展開して配置される複数の第2のビアを含み、前記第1及び第2の金属層を接続する第2のビア層と、を備え、

第1のトランジスタは、前記第1のゲート配線、前記第1及び第2の拡散部で構成され、

第2のトランジスタは、前記第2のゲート配線、前記第1及び第3の拡散部で構成され、前記第1のトランジスタに隣接して前記第1の方向と直交する第2の方向へ配置され、

第3のトランジスタは、前記1のダミーゲート配線、並びに、前記第2及び第4の拡散部で構成され、前記第1のトランジスタに隣接して、前記第2の方向とは反対の第3の方向に配置され、更に前記1のダミーゲート配線、並びに、前記第3及び第4の拡散部は、同電位であり、

第4のトランジスタは、前記2のダミーゲート配線、並びに、前記第3及び第5の拡散部で構成され、前記第2のトランジスタに隣接して前記第2の方向に配置され、更に前記2のダミーゲート配線、並びに、前記第3及び第5の拡散部は、同電位であり、

それぞれが、少なくとも一つの前記第1のビアをセットとする複数の第1セットが、第1のピッチで前記第1の拡散部に配置され、

それぞれが、少なくとも一つの前記第1のビアをセットとする複数の第2セットが、第2のピッチで前記第2乃至第5の拡散部にそれぞれ配置され、

前記第1の金属配線は、前記第1の拡散部に関連する複数の第1のビアを覆うように前記第1の拡散部の領域に配置され、

前記第2の金属配線は、前記第2及び第4の拡散部にそれぞれ関連する複数の第1のビアを一体として覆うように前記第3のトランジスタの領域に配置され、

前記第3の金属配線は、前記第3及び第5の拡散部にそれぞれ関連する複数の第1のビアを一体として覆うように前記第4のトランジスタの領域に配置され、

それぞれが、少なくとも一つの前記第2のビアをセットとする複数の第3セットが、第3のピッチで前記第1の金属配線に配置され、

それぞれが、少なくとも一つの前記第2のビアをセットとする複数の第4セットが、第4のピッチで前記第2及び第3の金属配線にそれぞれ配置され、

前記第4の金属配線は、前記第1の金属配線に関連する複数の第2のビアを覆うように前記第1の拡散部の領域に配置され、

前記第5の金属配線は、前記第2の金属配線に関連する複数の第2のビアを覆うように前記第3のトランジスタの領域に配置され、

前記第6の金属配線は、前記第3の金属配線に関連する複数の第2のビアを覆うように前記第4のトランジスタの領域に配置され、

前記第2の金属配線の前記第3の方向における幅は、前記第2の拡散部に関連する前記第1のビア及び前記第4の拡散部に関連する前記第1のビアの両方を含む第1の幅と、前記第1の幅よりも短い第2の幅と、を有し、

前記第3の金属配線の前記第2の方向における幅は、前記第3の拡散部に関連する前記第1のビア及び前記第5の拡散部に関連する前記第1のビアの両方を含む前記第1の幅と、前記第2の幅と、を有し、

前記第4乃至第6の金属配線の前記第2の方向におけるそれぞれの幅は、前記第1の幅よりも短い第3の幅を有し、

前記第1及び第2の金属配線の間、並びに前記第1及び第3の金属配線の間のそれぞれのギャップは、前記第1の幅に対応する第1のギャップと、前記第2の幅に対応する前記第1のギャップよりも大きな第2のギャップと、を有する、半導体装置。

【請求項14】

請求項13記載の半導体装置において、

前記第4及び第5の金属配線の間、並びに前記第4及び第6の金属配線の間のそれぞれのギャップは、前記第1のギャップよりも更に大きな第3のギャップを有する、半導体装置。

【請求項15】

請求項13又は14記載の半導体装置において、

前記第2のビアのサイズは、前記第1のビアのサイズよりも大きく、

前記第1の金属配線の前記第2の方向における幅は、前記第1のビアを含む第4の幅と、前記第2のビアを含む第5の幅と、の少なくともいずれか一方を有する、半導体装置。

【請求項16】

請求項13から15のいずれか1項記載の半導体装置において、

前記第3の幅は、前記第2の幅よりも短い、半導体装置。

【請求項17】

請求項13から16のいずれか1項記載の半導体装置において、

前記第4及び第5の金属配線の間、並びに前記第4及び第6の金属配線の間のそれぞれのギャップは、前記第1のギャップよりも更に大きな第3のギャップを有し、

前記第3のギャップは、前記第2のギャップよりも大きい、半導体装置。

【請求項18】

請求項13から17のいずれか1項記載の半導体装置において、

前記第1及び第4の金属配線は、前記第1の拡散部に配置され、

前記第2及び第5の金属配線、並びに前記第3及び第6の金属配線は、それぞれ対応する前記第1及び第2のダミーゲート配線の上に配置される、半導体装置。

【請求項19】

請求項18記載の半導体装置において、

前記第5及び6の金属配線にそれぞれ対応する前記複数の第2のビアは、それぞれ対応する前記第1及び第2のダミーゲート配線の上に配置される、半導体装置。

【図1】

【図2】

【図3A】

【図3B】

【図4】

【図5】

【図6A】

【図6B】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図12】

【図13】

【図14A】

【図14B】

【図15】

【図16】

【図17A】

【図17B】

【図2】

【図3A】

【図3B】

【図4】

【図5】

【図6A】

【図6B】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図12】

【図13】

【図14A】

【図14B】

【図15】

【図16】

【図17A】

【図17B】

【公開番号】特開2013−84656(P2013−84656A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−221789(P2011−221789)

【出願日】平成23年10月6日(2011.10.6)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月6日(2011.10.6)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]